# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

Date: Jul. 08, 2009

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category    | MPU&MCU                                                                                                                                                    |           | Document<br>No.         | TN-R8C-A002B/E         | Rev. | 2.00 |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|------------------------|------|------|

| Title                  | Specification Changes in the R8C/L35<br>R8C/L35B Group, R8C/L36A Group, R8C/L3<br>R8C/L38A Group, R8C/L38B Group, R8C/L3<br>R8C/L3AB Group Hardware Manual | 6B Group, | Information<br>Category | Technical Notification |      |      |

|                        | R8C/L35A Group, R8C/L35B Group                                                                                                                             | Lot No.   |                         |                        |      |      |

| Applicable<br>Products | R8C/L36A Group, R8C/L36B Group<br>R8C/L38A Group, R8C/L38B Group<br>R8C/L3AA Group and R8C/L3AB Group                                                      |           | Reference<br>Document   | Described below        |      |      |

(8) in section 1-1 and section 2-8 have been revised in Revision 2.00.

### 1. Overview

The below changes have been made to the specifications described in the datasheet and hardware manual of the R8C/L3AA Group, R8C/L3AB Group, R

### 1-1. Changes

- (1) Removed the high-speed on-chip oscillator

- (2) Changed the flash memory suspend function specifications

- (3) Changed the flash memory suspend electrical characteristics

- (4) Changed the timer RG specifications

- (5) Changed the LCD port specifications

- (6) Removed the voltage monitor 0 reset/power-on reset

- (7) Removed the voltage monitor 1 /comparator A1 and voltage monitor 2 / comparator A2 functions

- (8) Note on reducing power current

### 1-2. Reference Documents

The information in this document applies to the R8C/L35A Group, R8C/L35B Group, R8C/L36A Group, R8C/L36B Group

## 2. Description

### 2-1. Removed the High-Speed On-Chip Oscillator

The high-speed on-chip oscillator function has been removed.

Do NOT select the high-speed on-chip oscillator as the clock source for the CPU clock or peripheral functions.

Descriptions regarding the high-speed on-chip oscillator in the reference documents shown in 1-2, other than descriptions shown in this technical update, are invalid.

Date: Jul. 08, 2009

- 2-1-1. Register Settings Related to the Clock Generation Circuit

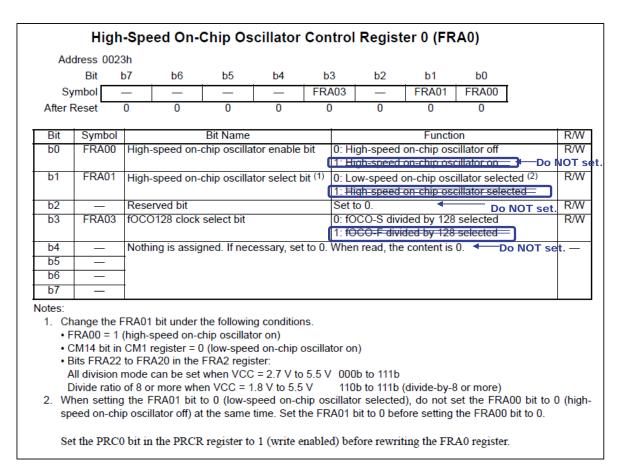

- 2-1-1-1. High-Speed On-Chip Oscillator Control Register 0 (FRA0)

- (1) Do NOT set FRA00 bit to 1 (high-speed on-chip oscillator on) [refer to Figure 2-1]

- (2) Do NOT set FRA01 bit to 1 (high-speed on-chip oscillator selected as fOCO clock source) [refer to Figure 2-1]. The fOCO is a clock source of timer RA.

- (3) Do NOT set FRA03 bit to 1 (fOCO-F divided by 128 selected as a clock source of fOCO128) [refer to Figure 2-1]. fOCO128 is used as an input-capture signal of timers RC and RD.

- 2-1-1-2. System Clock Control Register 3 (CM3)

- (1) Do NOT set bits CM37 to CM36 bits to 10b (high-speed on-chip oscillator selected as CPU clock when the MCU exits wait mode or stop mode) [refer to Figure 2-2].

- 2-1-1-3. High-Speed On-Chip Oscillator Control Register i (FRAi) (i = 1 to 7)

- (1) Do NOT set the register related to the high-speed on-chip oscillator division select (FRA2) or registers related to frequency adjustment (FRA1 and FRA3 to FRA7).

- 2-1-2. Register Settings Related to Timer RA

- 2-1-2-1. High-Speed On-chip Oscillator Control Register 0 (FRA0)

- (1) Do NOT set the FRA01 bit to 1 (high-speed on-chip oscillator selected for the fOCO clock) [refer to Figure 2-1]. The high-speed on-chip oscillator clock cannot be selected as the timer RA count source.

- 2-1-3 Register Settings Related to Timer RC

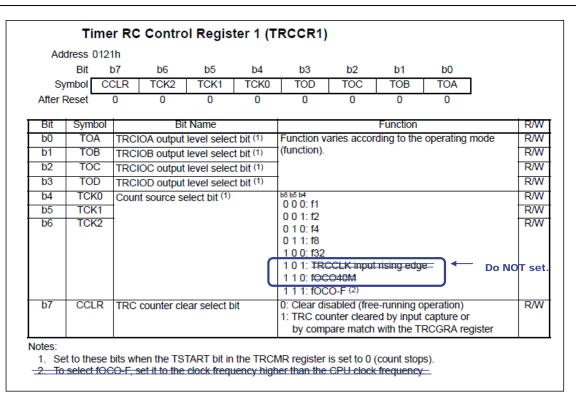

- 2-1-3-1. Timer RC Control Register 1 (TRCCR1)

- (1) Do NOT set bits TCK2 to TCK0 to 110b (fOCO40M selected as the timer RC count source) [refer to Figure 2-3].

- (2) Do NOT set bits TCK2 to TCK0 to 111b (fOCO-F selected as the timer RC count source) [refer to Figure 2-3].

- 2-1-3-2. High-speed On-Chip Oscillator Control Register 0 (FRA0)

- (1) Do NOT set the FRA03 bit to 1 (fOCO-F divided by 128 selected as the fOCO 128 clock) [refer to Figure 2-1]. For the timer RC input-capture function, fOCO-F divided by 128 cannot be selected for the input-capture trigger input of the TRCGRA register.

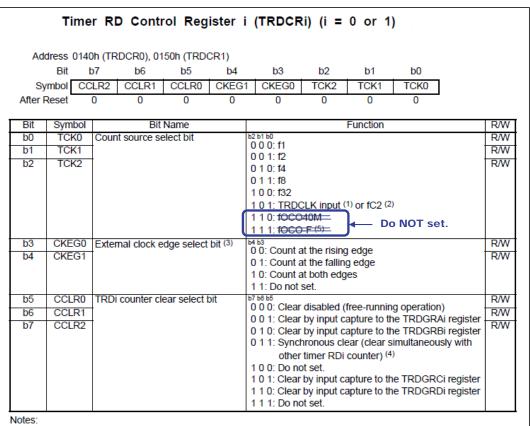

- 2-1-4. Register Settings Related to Timer RD

- 2-1-4-1. Timer RD Control Register 0, 1 (TRDCR0, TRDCR1)

- (1) Do NOT set bits TCK2 to TCK0 to 110b (fOCO40M selected as the timer RD count source) [refer to Figure 2-4].

- (2) Do NOT set bits TCK2 to TCK0 to 111b (fOCO-F selected as the timer RD count source) [refer to Figure 2-4].

- 2-1-4-2. High-speed On-Chip Oscillator Control Register 0 (FRA0)

- (1) Do NOT set the FRA03 bit to 1 (fOCO-F divided by 128 cannot be selected for the input-capture trigger input of the TRDGRA0 register [refer to Figure 2-1]. For the timer RD input-capture function, fOCO-F divided by 128 cannot be selected for the input-capture trigger input of the TRDGRA register.

- 2-1-5. Timer RG Control Register Settings

- 2-1-5-1. Timer RG Control Register (TRGCR)

- (1) Do NOT set bits TCK2 to TCK0, the count source select bits in the timer RG control register (TRGCR), to 110b (fOCO40M selected as a count source of timer RG) [refer to Figure 2-5].

- 2-1-6. Register Settings for the A/D Converter

- 2-1-6-1. A/D Mode Register (ADMOD)

- (1) Do NOT set the CKS2 bit to 1 (fOCO-F selected as the A/D converter operating clock source) [refer to Figure 2-6].

Figure 2-1.High-Speed On-Chip Oscillator Control Register 0 (FRA0) Setting

### System Clock Control Register 3 (CM3)

Address 0009h

| Bit         | b7   | b6   | b5   | b4 | b3 | b2 | b1 | b0   |

|-------------|------|------|------|----|----|----|----|------|

| Symbol      | CM37 | CM36 | CM35 | _  | _  | _  | _  | CM30 |

| After Reset | 0    | 0    | 0    | 0  | 0  | 0  | 0  | 0    |

| Bit      | Symbol       | Bit Name                                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W        |

|----------|--------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| b0       | CM30         | Wait control bit (1)                                           | 0: Other than wait mode<br>1: MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W        |

| b1       | _            | Nothing is assigned. If necessary, se                          | et to 0. When read, the content is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _          |

| b2<br>b3 | _            | Reserved bits                                                  | Set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W        |

| b4       | -            |                                                                | O. Fallanda and the same and th | DAM        |

| b5       | CM35         | CPU clock division ratio select bit when exiting wait mode (2) | Following settings are enabled:     CM06 bit in CM0 register     Bits CM16 and CM17 in CM1 register     No division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W        |

| b6<br>b7 | CM36<br>CM37 | System clock select bit when exiting wait or stop mode         | b7 b8     0 0: MCU exits with the CPU clock used immediately before entering wait or stop mode     0 1: Do not set.     1 0: High-speed on-chip oscillator clock selected (3)     1 1: XIN clock selected (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W<br>R/W |

### Notes:

- 1. When the MCU exits wait mode by a peripheral function interrupt, the CM30 bit is set to 0 (other than wait mode).

- Set the CM35 bit to 0 in stop mode. When the MCU enters wait mode, if the CM35 bit is set to 1 (no division), the CM06 bit in the CM0 register is set to 0 (bits CM16 and CM17 enabled) and bits CM17 and CM16 in the CM1 register is set to 00b (no division mode).

- When bits CM37 to CM36 are set to 10b (high-speed on-chip oscillator clock selected), the following will be set when the MCU exits wait mode or stop mode:

- OCD2 bit in OCD register = 1 (on-chip oscillator selected)

- FRA00 bit in FRA0 register = 1 (high speed on chip oscillator on)

- FRA01 bit in FRA0 register = 1 (high-speed on-chip oscillator selected)

- When bits CM37 to CM36 are set to 11b (XIN clock selected), the following will be set when the MCU exits wait mode or stop mode.

- · OM05 bit in OM0 register = 1 (XIN clock oscillates)

- OM13 bit in OM1 register = 1 (XIN-XOUT pin)

- OCD2 bit in OCD register = 0 (XIN clock selected)

When the MCU enters wait mode while the CM05 bit in the CM0 register is 1 (XIN clock stops), if the XIN clock is selected as the CPU clock when exiting wait mode, set the CM06 bit to 1 (divide-by-8 mode) and the CM35 bit to 0.

However, if an externally generated clock is used as the XIN clock, do not set bits CM37 to CM36 to 11b (XIN clock selected).

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the CM3 register.

Figure 2-2. System Clock Control Register 3 (CM3) Setting

Figure 2-3. Timer RC Control Register 1 (TRCCR1) Setting

- Enabled when the ITCLKi bit in the TRDECR register is set to 0 (TRDCLK input) and the STCLK bit in the TRDFCR register is 1 (external clock input enabled).

- 2. Enabled when the ITCLKi bit in the TRDECR register is set to 1 (fC2) in timer mode.

- Enabled when bits TCK2 to TCK0 are set to 101b (TRDCLK input or fC2), the ITCLKi bit in the TRDECR is set to 0 (TRDCLK input), and the STCLK bit in the TRDFCR register is set to 1 (external clock input enabled).

- Enabled when the SYNC bit in the TRDMR register is set to 1 (registers TRD0 and TRD1 operate synchronously).

- 5. To select fOCO-F, set it to the clock frequency higher than the CPU clock frequency.

Figure 2-4. Timer RD Control Register 0,1 (TRDCR0, TRDCR1) Setting

### Timer RG Control Register (TRGCR) Address 0172h Bit b6 b5 b3 b2 b1 b0 b4 CCLR1 CCLR0 CKEG1 CKEG0 TCK2 TCK1 TCK0 Symbol After Reset Bit Name Function Symbol b0 TCK0 R/W Count source select bit (1) 0 0 0: f1 TCK1 R/W b1 0 0 1: f2 Do NOT set. See 2-4. TCK2 R/W h2 0 1 0: f4 0 1 1: f8 1 0 0: f32 1 0 1: TRGCLKA input 1 1 0: fOCO40M Do NOT set. See 2-1-5-1. 1 1 1: TRGCLKB input R/W CKEG0 External clock active edge b3 0 0: Count at the rising edge CKEG1 select bit (1) h4 R/W 0 1: Count at the falling edge 1 0: Count at both the rising/falling edges 1 1: Do not set. CCLR0 TRG register clear source R/W b5 0 0: Clear disabled select bit b6 CCLR1 R/W 0 1: TRG register cleared by input capture or compare match with TRGGRA register 1 0: TRG register cleared by input capture or compare match with TRGGRB register 1 1: Do not set. Nothing is assigned. If necessary, set to 0. When read, the content is 1. b7 Note:

1. In phase counting mode, the settings of bits TCK0 to TCK2 and bits CKEG0 and CKEG1 are disabled and

the operation of phase counting mode has priority.

Figure 2-5. Timer RG Control Register (TRGCR) Setting

|       | A/      | D N | lode   | Regist       | er (ADI     | MOD)                  |            |                    |              |                       |    |

|-------|---------|-----|--------|--------------|-------------|-----------------------|------------|--------------------|--------------|-----------------------|----|

| Ad    | dress 0 | 0D4 | h      |              |             |                       |            |                    |              |                       |    |

|       | Bit     | b   | 7      | b6           | b5          | b4                    | b3         | b2                 | b1           | b0                    |    |

| S     | ymbol   | ADC | AP1    | ADCAP0       | MD2         | MD1                   | MD0        | CKS2               | CKS1         | CKS0                  |    |

| After | Reset   | (   | )      | 0            | 0           | 0                     | 0          | 0                  | 0            | 0                     |    |

| Bit   | Symb    | ool |        | Bit Nam      | е           |                       |            | Fun                | ction        |                       | R/ |

| b0    | CKS     | 0   | Divisi | on select bi | t           | 61 b0                 | divided by | 0                  |              |                       | R/ |

| b1    | CKS     | 1   |        |              |             | 1                     | divided by |                    |              |                       | R/ |

|       |         |     |        |              |             | 1                     | divided by |                    |              |                       |    |

|       |         |     |        |              |             | 1                     |            | -<br>1 (no divisio | on)          |                       |    |

| b2    | CKS     | 2   | Clock  | source sel   | ect bit (1) | 0: f1 selec           |            | •                  | ,            |                       | R/ |

|       |         |     |        |              |             | 1: f <del>0CO-l</del> | selected   | <b>-</b>           |              | Do NOT set.           |    |

| b3    | MD      | - 1 |        | perating m   | ode         | b5 b4 b3              | e-shot mo  | do                 |              |                       | R/ |

| b4    | MD.     | 1   | select | bit          |             | 0 0 0. On             |            | ie                 |              |                       | R/ |

| b5    | MD:     | 2   |        |              |             |                       | peat mode  | 0                  |              |                       | R/ |

|       |         |     |        |              |             | 1                     | peat mode  |                    |              |                       |    |

|       |         |     |        |              |             | 1 0 0: Sin            | igle sweep | mode               |              |                       |    |

|       |         |     |        |              |             | 1 0 1: Do             | not set.   |                    |              |                       |    |

|       |         |     |        |              |             |                       | peat swee  | o mode             |              |                       |    |

|       |         |     |        |              |             | 1 1 1: Do             | not set.   |                    |              |                       |    |

| b6    |         |     |        | onversion t  | rigger      | 67 b8<br>0 0: A/D (   | conversion | starts by s        | oftware tric | ger (ADST bit in      | R/ |

| b7    | ADCA    | P1  | select | TIC          |             | 1                     | ON0 regist |                    |              | 3 ( 7 1               | R۸ |

|       |         |     |        |              |             | 1                     | _          | ,                  | onversion t  | trigger from timer RD |    |

|       |         |     |        |              |             |                       |            |                    |              | trigger from timer RC |    |

|       |         |     |        |              |             | 1 1: A/D              | conversion | starts by e        | xtemal trig  | ger (ADTRG)           |    |

Note:

If the content of the ADMOD register is rewritten during A/D conversion, the conversion result is undefined.

Figure 2-6. A/D Mode Register (ADMOD) Setting

### 2-2. Changes in the Flash Memory Suspend Function

Flash programming operation is disabled when the auto-erasure is suspended while using the flash memory suspend

### **Executable Operation during Suspend** Operation during Suspend Data flash Data flash Program ROM Program ROM (Block during erasure (Block during erasure (Block during no eragure Block during no erasure execution before execution before execution before execution before entering suspend) entering suspend) entering suspend) entering suspend) Erase Program Read Erase Program Read Erase Program Read Erase Program Read Data Areas during **(5)** 0 0 flash erasure execution before Program 0 0 × × × -0 0 × entering suspend ROM

- 1. O indicates operation is enabled by using the suspend function, X indicates operation is disabled, and indicates no combination is available

- 2. Operation cannot be suspended during programming.

- 3. The block erase command can be executed for erasure. The program, lock bit program, and read lock bit status commands can be executed for programming.

- The clear status register command can be executed when the FST7 bit in the FST register is set to 1 (ready). The operation of block blank check is disabled during suspend.

- The MCU enters read array mode immediately after entering erase-suspend.

- The program ROM area can be read with the BGO function while programming or block erasing data flash.

Program is also not available with Data Flash driver in condition indicated in

Figure 2-7. Flash Memory Suspend Function

### 2-3. Changes in the Flash Memory Suspend Function Electrical Characteristics

Wait for at least 33 ms after the erase start/restart request before the making the next erase/suspend request. This is described as the "Interval from erase start/restart until suspend" in the hardware manual [refer to Figure 2-7].

|   | Flash Memory (Program ROM) Charac<br>(Vcc = 2.7 to 5.5 V and Topr = 0 to 60°C      |                       | pecified | i.)              |                      |

|---|------------------------------------------------------------------------------------|-----------------------|----------|------------------|----------------------|

| - | Interval from erase start/restart until following suspend request                  | <del>=0</del><br>→33  | -        | -                | <del>μs</del><br>→ m |

| - | Suspend interval necessary for auto-<br>erasure to complete                        | 33                    | -        | -                | ms                   |

| ÷ | Flash Memory (Data flash Block A to B                                              | lock D) Characteristi | cs       |                  | -                    |

| - | · · · · · · · · · · · · · · · · · · ·                                              |                       |          | D version)       | , unless             |

| - | Flash Memory (Data flash Block A to B<br>(VCC = 2.7 to 5.5 V and Topr = –20 to 85° |                       |          | D version).<br>_ | , unless<br>→ m      |

Figure 2-8. Flash Memory Suspend Electrical Characteristics

### Date: Jul. 08, 2009

### 2-4. Change in the Timer RG Function

Do NOT set the count source select bits (TCK2 to TCK0) in the timer RG control register (TRGCR) to 001b (f2 selected as the count source of timer RG) [refer to Figure 2-5].

### 2-5. Changes in the LCD Port Function

### 2-5-1. LCD Port Select Register 0 (LSE0)

This information applies to the R8C/L35A Group, R8C/L36A Group, R8C/L35B Group, and R8C/L36B Group.

Do NOT set bits LSE06 and LSE07 to 1 (SEG6 and SEG7 port functions selected). P0\_6/SEG6 and P0\_7/SEG7 cannot be used as segment pins SEG6 and SEG7. P0\_6/SEG6 and P0\_7/SEG7 can be used as I/O ports P0\_6 and P0\_7.

### 2-5-2. LCD Port Select Register 2 (LSE2)

This information applies to the R8C/L38A Group and R8C/L38B Group.

Do NOT set the LSE16 bit to 1 (SEG16 port function selected). P2\_0/SEG16/KI0 cannot be used as segment pin SEG16. P2\_0/SEG16/KI0 can be used as I/O port P0\_2 and KI0.

### 2-6. Voltage Monitor 0 Reset and Power-On Reset

The voltage monitor 0 reset and power-on reset cannot be used. Use a hardware reset to reset the MCU. In the documents listed in section 1-2, descriptions of the voltage monitor 0 reset and power-on reset are invalid.

2-7. Removed the Voltage Monitor 1 / Comparator A1 Interrupt and Voltage Monitor 2 / Comparator A2 Interrupt Functions

Voltage monitor 1 / comparator A1 and voltage monitor 2 / comparator A2 cannot be used. In the documents listed in section

1-2, description of the voltage monitor 0 reset or power-on reset are invalid.

### 2-8. Note on Reducing Power Current

Write 00h to the POMCR0 register (address 0020h) by a program. Current consumption may increase until 00h is written to the POMCR0 register.

Sample code: MOV.B #00H, 0020H

### 3. Other Note

Note regarding pins P12\_1 and P12\_0.

P12\_1 and P12\_0 are shared with XIN and XOUT. When XIN is used as a clock, these ports cannot be used as I/O ports.

## 4. Slated Changes

Contact the Renesas Technology sales department for schedule and products with high-speed on-chip oscillator.

- End of description -