# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                  |          | Document<br>No.         | TN-RZ*-A0095A/E                                                                      | Rev. | 1.00 |  |  |

|-----------------------|--------------------------------------------------------------------------|----------|-------------------------|--------------------------------------------------------------------------------------|------|------|--|--|

| Title                 | RZ/G2H, G2M V1.3, G2M V3.0, G2N and G2<br>Document Correction for CAN-FD | ≧E       | Information<br>Category | Technical Notification                                                               |      |      |  |  |

|                       | RZ/G Series, 2nd Generation                                              | Lot No.  |                         |                                                                                      |      |      |  |  |

| Applicable<br>Product | RZ/G2H<br>RZ/G2M V1.3, V3.0<br>RZ/G2N<br>RZ/G2E                          | All lots | Reference<br>Document   | RZ/G Series, 2nd Generation<br>User's Manual: Hardware Rev.1.10<br>(R01UH0808EJ0110) |      |      |  |  |

| This technical update describes document correction of RZ/G Series, 2nd Generation produ |

|------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------|

[Summary]

Document correction for "RZ/G Series, 2nd Generation User's Manual: Hardware Rev.1.10".

[Priority level]

Importance: "Normal"

Urgency: "Normal"

[Products]

RZ/G2H

RZ/G2M V1.3, V3.0

RZ/G2N

RZ/G2E

[Section number and title]

Section 48. CAN-FD

# [Correction]

1. Section 48. CAN-FD, Page 48-2, 48.1.1 Functional Overview, Table 48.1, Buffer descriptions. "Transmit FIFO: 3 FIFO per channel" description is removed.

# Current (from):

| Current (from):                |                                                                                                                   |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Item                           | Specification                                                                                                     |

| Buffer                         | <ul> <li>Individual buffers: 32 buffers (16 buffers x 2 channels)</li> </ul>                                      |

|                                | Transmit buffer: 16 buffers per channel                                                                           |

|                                | Transmit FIFO: 3 FIFO per channel                                                                                 |

|                                | Transmit queue: Single queue per channel (shared with the transmit buffer; up to 16 buffers allocated)            |

|                                | Shared buffers: 128 buffers for all channels                                                                      |

|                                | Receive buffer: 32 buffers                                                                                        |

|                                | Receive FIFO: 8 FIFO (up to 128 buffers allocated to each)                                                        |

|                                | Transmit/receive FIFO buffer: 3 FIFO buffers per channel (up to 128 buffers allocated to each)                    |

|                                | ECC included                                                                                                      |

| Reception function             | Receives data frames and remote frames.                                                                           |

|                                | <ul> <li>Selects ID format (standard ID, extended ID, or both IDs) to be received.</li> </ul>                     |

|                                | Sets interrupt enable/disable for each FIFO.                                                                      |

|                                | <ul> <li>Mirror function (reception of messages transmitted from the own CAN node)</li> </ul>                     |

|                                | Timestamp function (to record message reception time as a 16-bit timer value)                                     |

| Reception filter function      | Selects receive messages according to 1 receive rule.                                                             |

|                                | Sets the number of receive rules (0 to 128) for each channel.                                                     |

|                                | Acceptance filter processing: Sets ID and mask for each receive rule.                                             |

|                                | DLC filter processing: Enables DLC filter check for each acceptance rule.                                         |

| Receive message transfer       | Routing function                                                                                                  |

| unction                        | Transfers receive messages to arbitrary destinations (can be transferred to up to 8 buffers)                      |

|                                | Transfer destination: Receive buffer, receive FIFO buffer, and/or transmit/receive FIFO buffer                    |

|                                | Label addition function                                                                                           |

|                                | Stores label information together with a message in a receive buffer and FIFO buffer.                             |

| Transmission function          | Transmits data frames and remote frames.                                                                          |

|                                | Selects ID format (standard ID, extended ID, or both IDs) to be transmitted.                                      |

|                                | Sets interrupt enable/disable for each transmit buffer and transmit/receive FIFO buffer.                          |

|                                | Selects ID priority transmission or transmit buffer number priority transmission.                                 |

|                                | Transmit request can be aborted (possible to confirm with a flag)                                                 |

|                                | One-shot transmission function                                                                                    |

| Interval transmission function | Transmit messages at configurable intervals (transmit mode or gateway mode of transmit/receive FIFO buffers)      |

| Transmit queue function        | Transmits all stored messages according to the ID priority.                                                       |

| Transmit history function      | Stores the history information of transmission-completed messages                                                 |

|                                | Adds the timestamp to the history information (records the 16-bit timer value for the message transmission time). |

| Gateway function               | Transmits a received message automatically.                                                                       |

| Bus off recovery mode          | Selects the method for returning from bus off state.                                                              |

| selection                      | • ISO11898-1 compliant                                                                                            |

|                                | Automatic entry to channel halt mode at bus-off entry                                                             |

|                                | Automatic entry to channel halt mode at bus-off end                                                               |

|                                | Transition to channel standby mode by program request                                                             |

|                                |                                                                                                                   |

| Correction (to):               |                                                                                                                   |  |  |  |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                |                                                                                                                   |  |  |  |  |  |  |  |

|                                |                                                                                                                   |  |  |  |  |  |  |  |

| Item                           | Specification                                                                                                     |  |  |  |  |  |  |  |

| Buffer                         | Individual buffers: 32 buffers (16 buffers × 2 channels)                                                          |  |  |  |  |  |  |  |

| Danoi                          | Transmit buffer: 16 buffers per channel                                                                           |  |  |  |  |  |  |  |

|                                | Transmit gueue: Single queue per channel (shared with the transmit buffer; up to 16 buffers                       |  |  |  |  |  |  |  |

|                                | allocated)                                                                                                        |  |  |  |  |  |  |  |

|                                | Shared buffers: 128 buffers for all channels                                                                      |  |  |  |  |  |  |  |

|                                | Receive buffer: 32 buffers                                                                                        |  |  |  |  |  |  |  |

|                                | Receive FIFO: 8 FIFO (up to 128 buffers allocated to each)                                                        |  |  |  |  |  |  |  |

|                                | Transmit/receive FIFO buffer: 3 FIFO buffers per channel (up to 128 buffers allocated to each)                    |  |  |  |  |  |  |  |

|                                | ECC included                                                                                                      |  |  |  |  |  |  |  |

| Reception function             | Receives data frames and remote frames.                                                                           |  |  |  |  |  |  |  |

| · · ·                          | <ul> <li>Selects ID format (standard ID, extended ID, or both IDs) to be received.</li> </ul>                     |  |  |  |  |  |  |  |

|                                | Sets interrupt enable/disable for each FIFO.                                                                      |  |  |  |  |  |  |  |

|                                | Mirror function (reception of messages transmitted from the own CAN node)                                         |  |  |  |  |  |  |  |

|                                | Timestamp function (to record message reception time as a 16-bit timer value)                                     |  |  |  |  |  |  |  |

| Reception filter function      | Selects receive messages according to 1 receive rule.                                                             |  |  |  |  |  |  |  |

|                                | Sets the number of receive rules (0 to 128) for each channel.                                                     |  |  |  |  |  |  |  |

|                                | Acceptance filter processing: Sets ID and mask for each receive rule.                                             |  |  |  |  |  |  |  |

|                                | DLC filter processing: Enables DLC filter check for each acceptance rule.                                         |  |  |  |  |  |  |  |

| Receive message transfer       | Routing function                                                                                                  |  |  |  |  |  |  |  |

| function                       | Transfers receive messages to arbitrary destinations (can be transferred to up to 8 buffers)                      |  |  |  |  |  |  |  |

|                                | Transfer destination: Receive buffer, receive FIFO buffer, and/or transmit/receive FIFO buffer                    |  |  |  |  |  |  |  |

|                                | Label addition function                                                                                           |  |  |  |  |  |  |  |

|                                | Stores label information together with a message in a receive buffer and FIFO buffer.                             |  |  |  |  |  |  |  |

| Transmission function          | Transmits data frames and remote frames.                                                                          |  |  |  |  |  |  |  |

|                                | <ul> <li>Selects ID format (standard ID, extended ID, or both IDs) to be transmitted.</li> </ul>                  |  |  |  |  |  |  |  |

|                                | <ul> <li>Sets interrupt enable/disable for each transmit buffer and transmit/receive FIFO buffer.</li> </ul>      |  |  |  |  |  |  |  |

|                                | Selects ID priority transmission or transmit buffer number priority transmission.                                 |  |  |  |  |  |  |  |

|                                | Transmit request can be aborted (possible to confirm with a flag)                                                 |  |  |  |  |  |  |  |

|                                | One-shot transmission function                                                                                    |  |  |  |  |  |  |  |

| Interval transmission function | Transmit messages at configurable intervals (transmit mode or gateway mode of transmit/receive FIFO buffers)      |  |  |  |  |  |  |  |

| Transmit queue function        | Transmits all stored messages according to the ID priority.                                                       |  |  |  |  |  |  |  |

| Transmit history function      | Stores the history information of transmission-completed messages                                                 |  |  |  |  |  |  |  |

|                                | Adds the timestamp to the history information (records the 16-bit timer value for the message transmission time). |  |  |  |  |  |  |  |

| Gateway function               | Transmits a received message automatically.                                                                       |  |  |  |  |  |  |  |

| Bus off recovery mode          | Selects the method for returning from bus off state.                                                              |  |  |  |  |  |  |  |

| selection                      | ISO11898-1 compliant                                                                                              |  |  |  |  |  |  |  |

|                                | Automatic entry to channel halt mode at bus-off entry                                                             |  |  |  |  |  |  |  |

|                                | Automatic entry to channel halt mode at bus-off end                                                               |  |  |  |  |  |  |  |

|                                | Transition to channel standby mode by program request                                                             |  |  |  |  |  |  |  |

|                                | • Transition to the error-active state by program request (forcible return from the bus off state)                |  |  |  |  |  |  |  |

# RENESAS TECHNICAL UPDATE TN-RZ\*-A0095A/E

| [Description]                                                                                |

|----------------------------------------------------------------------------------------------|

| "Transmit FIFO: 3 FIFO per channel" description is removed from the overview of Buffer item. |

| [Reason for Correction]                                                                      |

| General error correction.                                                                    |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

Date: Aug. 30, 2022

[Correction]

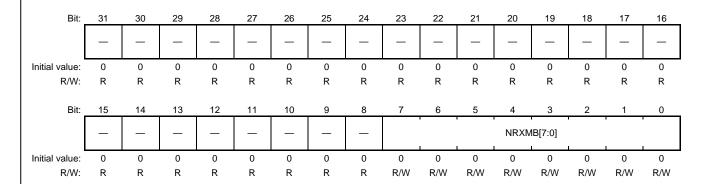

2. Section 48. CAN-FD, Page 48-49, 48.7.5.1 RSCFDnRMNB - Receive Buffer Number Register, Bit NRXMB[7:0] description setting value corrected.

Current (from):

#### 48.7.5 Details of Receive Buffer Related Registers

#### 48.7.5.1 RSCFDnRMNB - Receive Buffer Number Register

Access: RSCFDnRMNB register can be read/written in 32-bit units

RSCFDnRMNBL, RSCFDnRMNBH registers can be read/written in 16-bit units

RSCFDnRMNBLL, RSCFDnRMNBLH, RSCFDnRMNBHL, RSCFDnRMNBHH registers can be read/written in

8-bit units

Address: RSCFDnRMNB: <RSCFDn\_base> + H'00A4

RSCFDnRMNBL: <RSCFDn\_base> + H'00A4, RSCFDnRMNBH: <RSCFDn\_base> + H'00A6

RSCFDnRMNBLL: <RSCFDn\_base> + H'00A4, RSCFDnRMNBLH: <RSCFDn\_base> + H'00A5,

RSCFDnRMNBHL: <RSCFDn\_base> + H'00A6, RSCFDnRMNBHH: <RSCFDn\_base> + H'00A7

Value after reset: H'0000 0000

| Bit     | Bit Name   | Initial Value | R/W | Description                                                                                                                                           |

|---------|------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 8 | Reserved   | All 0         | R   | These bits are read as the value after reset.                                                                                                         |

|         |            |               |     | The write value should be the value after reset.                                                                                                      |

| 7 to 0  | NRXMB[7:0] | H'00          | R/W | Receive Buffer Number Configuration                                                                                                                   |

|         |            |               |     | These bits are used to set the total number of receive buffers of the RS-CANFD module. The maximum value is $16 \times (\text{number of channels})$ . |

|         |            |               |     | Setting these bits all to 0 makes receive buffers unavailable.                                                                                        |

|         |            |               |     | Set a value of 0 to 96.                                                                                                                               |

Modify the RSCFDnRMNB register only in global reset mode.

#### 48.7.5 Details of Receive Buffer Related Registers

## 48.7.5.1 RSCFDnRMNB - Receive Buffer Number Register

Access: RSCFDnRMNB register can be read/written in 32-bit units

RSCFDnRMNBL, RSCFDnRMNBH registers can be read/written in 16-bit units

RSCFDnRMNBLL, RSCFDnRMNBLH, RSCFDnRMNBHL, RSCFDnRMNBHH registers can be read/written in

8-bit units

Address: RSCFDnRMNB: <RSCFDn\_base> + H'00A4

RSCFDnRMNBL: <RSCFDn\_base> + H'00A4, RSCFDnRMNBH: <RSCFDn\_base> + H'00A6

RSCFDnRMNBLL: <RSCFDn\_base> + H'00A4, RSCFDnRMNBLH: <RSCFDn\_base> + H'00A5,

RSCFDnRMNBHL: <RSCFDn\_base> + H'00A6, RSCFDnRMNBHH: <RSCFDn\_base> + H'00A7

Value after reset: H'0000 0000

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22  | 21  | 20   | 19      | 18  | 17  | 16  |

|----------------|----|----|----|----|----|----|----|----|-----|-----|-----|------|---------|-----|-----|-----|

|                | l  | _  | _  | l  | _  | _  | _  | l  | _   | _   | _   | ı    | ı       | _   | l   | _   |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R   | R   | R   | R    | R       | R   | R   | R   |

|                |    |    |    |    |    |    |    |    |     |     |     |      |         |     |     |     |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|                |    | _  | _  |    | _  | _  | _  |    |     | ı   | ı   | NRXM | IB[7:0] | ı   | ı   | 1   |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Bit     | Bit Name   | Initial Value | R/W | Description                                                                                                                                           |

|---------|------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 8 | Reserved   | All 0         | R   | These bits are read as the value after reset.                                                                                                         |

|         |            |               |     | The write value should be the value after reset.                                                                                                      |

| 7 to 0  | NRXMB[7:0] | H'00          | R/W | Receive Buffer Number Configuration                                                                                                                   |

|         |            |               |     | These bits are used to set the total number of receive buffers of the RS-CANFD module. The maximum value is $16 \times (\text{number of channels})$ . |

|         |            |               |     | Setting these bits all to 0 makes receive buffers unavailable.                                                                                        |

|         |            |               |     | Set a value of 0 to 32.                                                                                                                               |

Modify the RSCFDnRMNB register only in global reset mode.

[Description]

The setting range described in Description of NRXMB[7:0] is corrected.

[Reason for Correction]

General error correction.

[Correction]

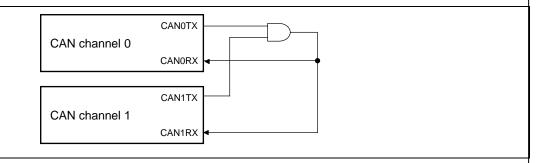

3. Section 48. CAN-FD, Page 48-119, 48.7.13.1 RSCFDnGTSTCFG - Global Test Configuration Register, Bit 22 to 16, RTMPS[6:0], setting value range corrected.

Current (from):

#### 48.7.13 Details of Test Related Registers

#### 48.7.13.1 RSCFDnGTSTCFG - Global Test Configuration Register

Access: RSCFDnGTSTCFG register can be read/written in 32-bit units

RSCFDnGTSTCFGL, RSCFDnGTSTCFGH registers can be read/written in 16-bit units

RSCFDnGTSTCFGLL, RSCFDnGTSTCFGLH, RSCFDnGTSTCFGHL, RSCFDnGTSTCFGHH registers can be

read/written in 8-bit units

Address: RSCFDnGTSTCFG: <RSCFDn\_base> + H'0468

RSCFDnGTSTCFGL: <RSCFDn\_base> + H'0468, RSCFDnGTSTCFGH: <RSCFDn\_base> + H'046A RSCFDnGTSTCFGLL: <RSCFDn\_base> + H'0468, RSCFDnGTSTCFGLH: <RSCFDn\_base> + H'0469, RSCFDnGTSTCFGHL: <RSCFDn\_base> + H'046A, RSCFDnGTSTCFGHH: <RSCFDn\_base> + H'046B

Value after reset: H'0000 0000

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20     | 19      | 18  | 17          | 16          |

|----------------|----|----|----|----|----|----|----|----|----|-----|-----|--------|---------|-----|-------------|-------------|

|                | _  | _  | _  | _  | _  | _  | _  | _  |    |     | 1   | r<br>R | TMPS[6: | 0]  | 1           | 1           |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0      | 0       | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R  | R/W | R/W | R/W    | R/W     | R/W | R/W         | R/W         |

|                |    |    |    |    |    |    |    |    |    |     |     |        |         |     |             |             |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5   | 4      | 3       | 2   | 1           | 0           |

|                | _  | _  | _  | _  | _  | _  | _  | _  | _  | _   | _   | _      | _       | _   | C1ICB<br>CE | C0ICB<br>CE |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0      | 0       | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R  | R   | R   | R      | R       | R   | R/W         | R/W         |

| Bit      | Bit Name   | Initial Value | R/W | Description                                                                                                                   |

|----------|------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 31 to 23 | Reserved   | All 0         | R   | When read, the value after reset is returned.                                                                                 |

|          |            |               |     | When writing to these bits, write the value after reset.                                                                      |

| 22 to 16 | RTMPS[6:0] | H'00          | R/W | RAM Test Page Configuration                                                                                                   |

|          |            |               |     | These bits are used to set the RAM test target page number for RAM test. Set a value in the range of H'00 to H'38, inclusive. |

| 15 to 2  | Reserved   | All 0         | R   | When read, the value after reset is returned.                                                                                 |

|          |            |               |     | When writing to these bits, write the value after reset.                                                                      |

| 1        | C1ICBCE    | 0             | R/W | CAN1 Inter-Channel Communication Test Enable                                                                                  |

|          |            |               |     | Setting this bit to 1 enables the channel 1 inter-channel communication test.                                                 |

|          |            |               |     | 0: CAN1 inter-channel communication test is disabled.                                                                         |

|          |            |               |     | 1: CAN1 inter-channel communication test is enabled.                                                                          |

| 0        | COICBCE    | 0             | R/W | CAN0 Inter-Channel Communication Test Enable                                                                                  |

|          |            |               |     | Setting this bit to 1 enables the channel 0 inter-channel communication test.                                                 |

|          |            |               |     | 0: CAN0 inter-channel communication test is disabled.                                                                         |

|          |            |               |     | 1: CAN0 inter-channel communication test is enabled.                                                                          |

Modify the RSCFDnGTSTCFG register only in global test mode.

## 48.7.13 Details of Test Related Registers

## 48.7.13.1 RSCFDnGTSTCFG - Global Test Configuration Register

Access: RSCFDnGTSTCFG register can be read/written in 32-bit units

RSCFDnGTSTCFGL, RSCFDnGTSTCFGH registers can be read/written in 16-bit units

RSCFDnGTSTCFGLL, RSCFDnGTSTCFGLH, RSCFDnGTSTCFGHL, RSCFDnGTSTCFGHH registers can be

read/written in 8-bit units

Address: RSCFDnGTSTCFG: <RSCFDn\_base> + H'0468

RSCFDnGTSTCFGL: <RSCFDn\_base> + H'0468, RSCFDnGTSTCFGH: <RSCFDn\_base> + H'046A RSCFDnGTSTCFGLL: <RSCFDn\_base> + H'0468, RSCFDnGTSTCFGLH: <RSCFDn\_base> + H'0469, RSCFDnGTSTCFGHL: <RSCFDn\_base> + H'046A, RSCFDnGTSTCFGHH: <RSCFDn\_base> + H'046B

Value after reset: H'0000 0000

| Bit:           | 31 | 30 | 29 | 28 | 27  | 26 | 25  | 24 | 23     | 22  | 21       | 20     | 19       | 18  | 17          | 16          |

|----------------|----|----|----|----|-----|----|-----|----|--------|-----|----------|--------|----------|-----|-------------|-------------|

|                |    | _  | _  |    | _   | _  | _   | _  | _      |     | 1        | r<br>R | TMPS[6:  | 0]  | 1           |             |

| Initial value: | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0      | 0   | 0        | 0      | 0        | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R   | R  | R   | R  | R      | R/W | R/W      | R/W    | R/W      | R/W | R/W         | R/W         |

| Bit:           | 15 | 14 | 13 | 12 | 11  | 10 | 9   | 8  | 7      | 6   | 5        | 4      | 3        | 2   | 1           | 0           |

| DII.           | 13 | 14 | 13 | 12 | 1 I | 10 | e e | 0  | ,<br>I | 0   | <u> </u> | 4      | <u> </u> |     | l<br>I      |             |

|                | _  | _  | _  | _  | _   | _  | _   | _  | _      | _   | _        | _      | _        | _   | C1ICB<br>CE | COICB<br>CE |

| Initial value: | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0      | 0   | 0        | 0      | 0        | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R   | R  | R   | R  | R      | R   | R        | R      | R        | R   | R/W         | R/W         |

| Bit      | Bit Name   | Initial Value | R/W | Description                                                                                                                   |

|----------|------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 31 to 23 | Reserved   | All 0         | R   | When read, the value after reset is returned.                                                                                 |

|          |            |               |     | When writing to these bits, write the value after reset.                                                                      |

| 22 to 16 | RTMPS[6:0] | H'00          | R/W | RAM Test Page Configuration                                                                                                   |

|          |            |               |     | These bits are used to set the RAM test target page number for RAM test. Set a value in the range of H'00 to H'13, inclusive. |

| 15 to 2  | Reserved   | All 0         | R   | When read, the value after reset is returned.                                                                                 |

|          |            |               |     | When writing to these bits, write the value after reset.                                                                      |

| 1        | C1ICBCE    | 0             | R/W | CAN1 Inter-Channel Communication Test Enable                                                                                  |

|          |            |               |     | Setting this bit to 1 enables the channel 1 inter-channel communication test.                                                 |

|          |            |               |     | 0: CAN1 inter-channel communication test is disabled.                                                                         |

|          |            |               |     | 1: CAN1 inter-channel communication test is enabled.                                                                          |

| 0        | COICBCE    | 0             | R/W | CAN0 Inter-Channel Communication Test Enable                                                                                  |

|          |            |               |     | Setting this bit to 1 enables the channel 0 inter-channel communication test.                                                 |

|          |            |               |     | 0: CAN0 inter-channel communication test is disabled.                                                                         |

|          |            |               |     | 1: CAN0 inter-channel communication test is enabled.                                                                          |

Modify the RSCFDnGTSTCFG register only in global test mode.

| [Description] The setting range described in Description of RTMPS [6:0] is corrected. |

|---------------------------------------------------------------------------------------|

| [Reason for Correction] General error correction.                                     |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

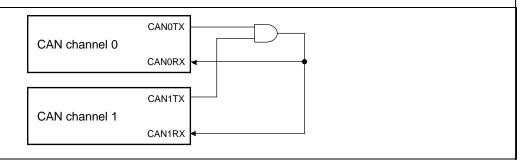

4. Section 48. CAN-FD, Page 48-257, 48.9.14.1 RSCFDnCFDGTSTCFG — Global Test Configuration Register, Bit RTMPS[6:0] description setting value corrected.

Current (from):

## 48.9.14 Details of Test Related Registers

## 48.9.14.1 RSCFDnCFDGTSTCFG — Global Test Configuration Register

Access: RSCFDnCFDGTSTCFG register can be read/written in 32-bit units

RSCFDnCFDGTSTCFGL, RSCFDnCFDGTSTCFGH registers can be read/written in 16-bit units

RSCFDnCFDGTSTCFGLL, RSCFDnCFDGTSTCFGHH, RSCFDnCFDGTSTCFGHH, RSCFDnCFDGTSTCFGHH

registers can be read/written in 8-bit units

Address: RSCFDnCFDGTSTCFG: <RSCFDn\_base> + H'0468

RSCFDnCFDGTSTCFGL: <RSCFDn\_base> + H'0468, RSCFDnCFDGTSTCFGH: <RSCFDn\_base> + H'046A RSCFDnCFDGTSTCFGLL: <RSCFDn\_base> + H'0468, RSCFDnCFDGTSTCFGLH: <RSCFDn\_base> + H'0469, RSCFDnCFDGTSTCFGHL: <RSCFDn\_base> + H'046A, RSCFDnCFDGTSTCFGHH: <RSCFDn\_base> + H'046B

Value after reset: H'0000 0000

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20  | 19      | 18  | 17          | 16          |

|----------------|----|----|----|----|----|----|----|----|----|-----|-----|-----|---------|-----|-------------|-------------|

|                | _  | _  | _  | _  | _  | _  | _  | _  | _  |     |     | R   | TMPS[6: | 0]  |             | .           |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0       | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R  | R/W | R/W | R/W | R/W     | R/W | R/W         | R/W         |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5   | 4   | 3       | 2   | 1           | 0           |

|                | _  | _  | _  | _  | _  | _  | _  | _  | _  | _   | _   | _   | _       | _   | C1ICB<br>CE | COICB<br>CE |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0       | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R  | R   | R   | R   | R       | R   | R/W         | R/W         |

| Bit      | Bit Name   | Initial Value | R/W | Description                                                                                                                   |

|----------|------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 31 to 23 | Reserved   | All 0         | R   | When read, the value after reset is returned.                                                                                 |

|          |            |               |     | When writing to these bits, write the value after reset.                                                                      |

| 22 to 16 | RTMPS[6:0] | H'00          | R/W | RAM Test Page Configuration                                                                                                   |

|          |            |               |     | These bits are used to set the RAM test target page number for RAM test. Set a value in the range of H'00 to H'53, inclusive. |

| 15 to 2  | Reserved   | All 0         | R   | When read, the value after reset is returned.                                                                                 |

|          |            |               |     | When writing to these bits, write the value after reset.                                                                      |

| 1        | C1ICBCE    | 0             | R/W | CAN1 Inter-Channel Communication Test Enable                                                                                  |

|          |            |               |     | Setting this bit to 1 enables the channel 1 inter-channel communication test.                                                 |

|          |            |               |     | 0: CAN1 inter-channel communication test is disabled.                                                                         |

|          |            |               |     | 1: CAN1 inter-channel communication test is enabled.                                                                          |

| 0        | C0ICBCE    | 0             | R/W | CAN0 Inter-Channel Communication Test Enable                                                                                  |

|          |            |               |     | Setting this bit to 1 enables the channel 0 inter-channel communication test.                                                 |

|          |            |               |     | 0: CAN0 inter-channel communication test is disabled.                                                                         |

|          |            |               |     | 1: CAN0 inter-channel communication test is enabled.                                                                          |

Modify the RSCFDnCFDGTSTCFG register only in global test mode.

## 48.9.14 Details of Test Related Registers

## 48.9.14.1 RSCFDnCFDGTSTCFG — Global Test Configuration Register

Access: RSCFDnCFDGTSTCFG register can be read/written in 32-bit units

RSCFDnCFDGTSTCFGL, RSCFDnCFDGTSTCFGH registers can be read/written in 16-bit units

RSCFDnCFDGTSTCFGLL, RSCFDnCFDGTSTCFGHH, RSCFDnCFDGTSTCFGHH

registers can be read/written in 8-bit units

Address: RSCFDnCFDGTSTCFG: <RSCFDn\_base> + H'0468

RSCFDnCFDGTSTCFGL: <RSCFDn\_base> + H'0468, RSCFDnCFDGTSTCFGH: <RSCFDn\_base> + H'046A RSCFDnCFDGTSTCFGLL: <RSCFDn\_base> + H'0468, RSCFDnCFDGTSTCFGLH: <RSCFDn\_base> + H'0469, RSCFDnCFDGTSTCFGHL: <RSCFDn\_base> + H'046A, RSCFDnCFDGTSTCFGHH: <RSCFDn\_base> + H'046B

Value after reset: H'0000 0000

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20     | 19      | 18  | 17          | 16          |

|----------------|----|----|----|----|----|----|----|----|----|-----|-----|--------|---------|-----|-------------|-------------|

|                | -  | _  | _  | _  | _  | _  | _  | _  | _  |     | 1   | r<br>R | TMPS[6: | 0]  |             |             |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0      | 0       | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R  | R/W | R/W | R/W    | R/W     | R/W | R/W         | R/W         |

|                |    |    |    |    |    |    |    |    |    |     |     |        |         |     |             |             |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5   | 4      | 3       | 2   | 1           | 0           |

|                | -  | _  | _  | _  | _  | _  | _  | _  | _  | _   | _   | _      | _       | _   | C1ICB<br>CE | COICB<br>CE |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0      | 0       | 0   | 0           | 0           |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R  | R   | R   | R      | R       | R   | R/W         | R/W         |

| Bit Name   | Initial Value                           | R/W                                                        | Description                                                                                                                                                       |

|------------|-----------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved   | All 0                                   | R                                                          | When read, the value after reset is returned.                                                                                                                     |

|            |                                         |                                                            | When writing to these bits, write the value after reset.                                                                                                          |

| RTMPS[6:0] | H'00                                    | R/W                                                        | RAM Test Page Configuration                                                                                                                                       |

|            |                                         |                                                            | These bits are used to set the RAM test target page number for RAM test. Set a value in the range of H'00 to H'1B, inclusive.                                     |

| Reserved   | All 0                                   | R                                                          | When read, the value after reset is returned.                                                                                                                     |

|            |                                         |                                                            | When writing to these bits, write the value after reset.                                                                                                          |

| C1ICBCE    | 0                                       | R/W                                                        | CAN1 Inter-Channel Communication Test Enable                                                                                                                      |

|            |                                         |                                                            | Setting this bit to 1 enables the channel 1 inter-channel communication test.                                                                                     |

|            |                                         |                                                            | 0: CAN1 inter-channel communication test is disabled.                                                                                                             |

|            |                                         |                                                            | 1: CAN1 inter-channel communication test is enabled.                                                                                                              |

| C0ICBCE    | 0                                       | R/W                                                        | CAN0 Inter-Channel Communication Test Enable                                                                                                                      |

|            |                                         |                                                            | Setting this bit to 1 enables the channel 0 inter-channel communication test.                                                                                     |

|            |                                         |                                                            | 0: CAN0 inter-channel communication test is disabled.                                                                                                             |

|            |                                         |                                                            | 1: CAN0 inter-channel communication test is enabled.                                                                                                              |

|            | Reserved  RTMPS[6:0]  Reserved  C1ICBCE | Reserved All 0  RTMPS[6:0] H'00  Reserved All 0  C1ICBCE 0 | Reserved         All 0         R           RTMPS[6:0]         H'00         R/W           Reserved         All 0         R           C1ICBCE         0         R/W |

Modify the RSCFDnCFDGTSTCFG register only in global test mode.

| [Description] The setting range described in Description of RTMPS [6:0] is corrected.  [Reason for Correction] General error correction. |

|------------------------------------------------------------------------------------------------------------------------------------------|

| [Reason for Correction]                                                                                                                  |

|                                                                                                                                          |

| General error correction.                                                                                                                |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

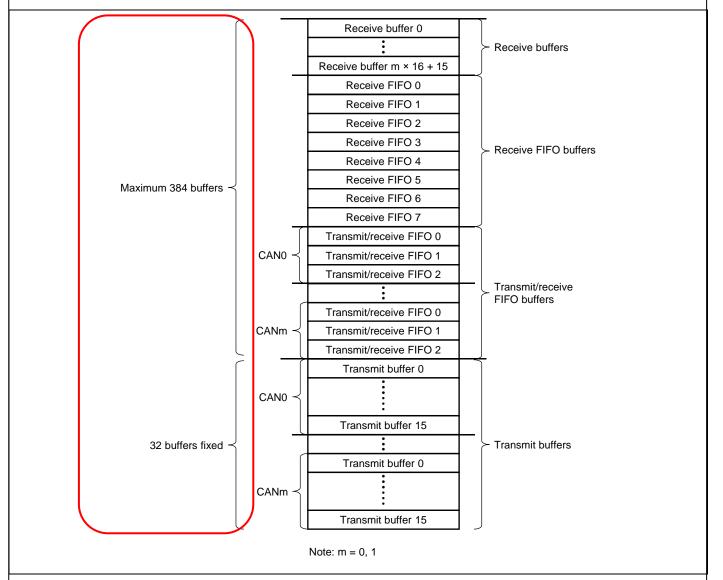

Section 48. CAN-FD, Page 48-272, 48.11.3 registers Initialized by Transition to CAN Mode, Table 48.33 Registers

Initialized in Global Reset Mode or Channel Reset Mode, RSCFDn(CFD)GTINTSTS1 register, Bit/Flag removed.

Current (from):

## 48.11.3 Registers Initialized by Transition to CAN Mode

Table 48.33 shows bits and flags initialized by transition to channel reset mode. These bits and flags are also initialized by transition to global reset mode. Table 48.34 shows bits and flags that are only initialized by transition to global reset mode.

Table 48.33 Registers Initialized in Global Reset Mode or Channel Reset Mode

| RSCFDn(CFD)CmCTR register  RSCFDn(CFD)CmSTS register  RSCFDn(CFD)CmERFL register  CRCREG[14:0], ADERR, BOERR, B1ERR, CERR, AERR, FERR, SERR, ALF, BLF, OVLF, BOEF, BOEF, EPF, EWF, BEF  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDSTS register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDCRC register  RSCFDnCFDCmFDCRC register  RSCFDnCFDCMFDCRC register  RSCFDn(CFD)CFCCk register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFE  RSCFDn(CFD)CFTISTS register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF  RSCFDn(CFD)TMCT register  TMMM, TMTAR, TMTR  RSCFDn(CFD)TMTSTS register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTSTSy register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTCSTSy register  TMTARSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMCCTN register  TXQE  RSCFDn(CFD)TXQCCm register  TXQE  RSCFDn(CFD)TXQCTm register  TXQE  RSCFDn(CFD)THLCTM register  TXQIF, TXQFLL, TXQEMP  RSCFDn(CFD)THLSTSM register  THLE  RSCFDn(CFD)THLSTSM register  TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)  TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                      | Register                      | Bit / Flag                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------|

| RSCFDn(CFD)CmERFL register  CRCREG[14:0], ADERR, B0ERR, B1ERR, CERR, AERR, FERR, SERR, ALF, BLF, OVLF, BORF, BOEF, EPF, EWF, BEF  RSCFDnCFDCmFDCTR register  RSCFDnCFDCmFDSTS register  SOC[7:0], EOC[7:0], SOCO, EOCO, TDCVF, TDCR[6:0]  RSCFDnCFDCmFDCRC register  RSCFDn(CFD)CFCCk register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFE  RSCFDn(CFD)CFSTSk register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF  RSCFDn(CFD)CFTISTS register  CFkTXIF  RSCFDn(CFD)TMCp register  TMOM, TMTAR, TMTR  RSCFDn(CFD)TMSTSp register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTRSTSy register  TMTARTSP (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSO register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSO register  TMTASTSP (Bits of correspon | RSCFDn(CFD)CmCTR register     | (ROM), CRCT, CTMS[1:0], CTME, CHMDC[1:0]                                         |

| OVLF, BORF, BOEF, EWF, BEF  RSCFDnCFDCmFDCTR register EOCCLR, SOCCLR  RSCFDnCFDCmFDSTS register SOC[7:0], EOC[7:0], SOCO, EOCO, TDCVF, TDCR[6:0]  RSCFDnCFDCmFDCRC register CRCREG[20:0]  RSCFDn(CFD)CFCCk register When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFE  RSCFDn(CFD)CFSTSk register When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF  RSCFDn(CFD)CFTISTS register CFkTXIF  RSCFDn(CFD)TMCp register TMOM, TMTAR, TMTR  RSCFDn(CFD)TMSTSp register TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTRSTSy register TMTRSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTARSTSy register TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TXQCCm register TXQE  RSCFDn(CFD)TXQSTSm register TXQIF, TXQFLL, TXQEMP  RSCFDn(CFD)THLCCm register TLLE  RSCFDn(CFD)THLSTSm register THLE  RSCFDn(CFD)TINTSTS0 register TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RSCFDn(CFD)CmSTS register     |                                                                                  |

| RSCFDnCFDCmFDSTS register  RSCFDnCFDCmFDCRC register  RSCFDn(CFD)CFCCk register  RSCFDn(CFD)CFCK register  RSCFDn(CFD)CFSTSk register  RSCFDn(CFD)CFTISTS register  RSCFDn(CFD)TMCp register  RSCFDn(CFD)TMTRSTSy register  RSCFDn(CFD)TMTRSTSy register  RSCFDn(CFD)TMTARSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTARSTSy register  RSCFDn(CFD)TMTARSTSy register  RSCFDn(CFD)TMTARSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTCSTSy register  RSCFDn(CFD)TMTCSTSy register  TMTARSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSP (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSP (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTASTSP (Bits of corresponding channel are initialized in channel reset mode.)  TMTASTSP (BITSTS)  | RSCFDn(CFD)CmERFL register    |                                                                                  |

| RSCFDnCFDCmFDCRC register  RSCFDn(CFD)CFCCk register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFE  RSCFDn(CFD)CFSTSk register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF  RSCFDn(CFD)CFTISTS register  RSCFDn(CFD)TMCp register  TMOM, TMTAR, TMTR  RSCFDn(CFD)TMSTSp register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTRSTSy register  TMTARSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TXQE  RSCFDn(CFD)TXQCCm register  TXQE  RSCFDn(CFD)TXQSTSm register  TXQIF, TXQFLL, TXQEMP  RSCFDn(CFD)THLCCm register  THLE  RSCFDn(CFD)THLSTSm register  THLMC[4:0], THLIF, THLELT, THLFLL, THLEMP  RSCFDn(CFD)GTINTSTSO register  TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RSCFDnCFDCmFDCTR register     | EOCCLR, SOCCLR                                                                   |

| RSCFDn(CFD)CFCCk register When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFE RSCFDn(CFD)CFSTSk register When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF RSCFDn(CFD)CFTISTS register CFkTXIF RSCFDn(CFD)TMCp register TMOM, TMTAR, TMTR RSCFDn(CFD)TMSTSp register TMTARM, TMTRM, TMTRF[1:0], TMTSTS RSCFDn(CFD)TMTRSTSy register TMTRSTSp (Bits of corresponding channel are initialized in channel reset mode.) RSCFDn(CFD)TMTARSTSy register TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.) RSCFDn(CFD)TMTCSTSy register TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.) RSCFDn(CFD)TMTASTSy register TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.) RSCFDn(CFD)TMCCCm register TXQE RSCFDn(CFD)TXQCCm register TXQIF, TXQFLL, TXQEMP RSCFDn(CFD)THLCCm register TXQIF, TXQFLL, TXQEMP RSCFDn(CFD)THLSTSm register THLE RSCFDn(CFD)THLSTSm register THLMC[4:0], THLIF, THLELT, THLFLL, THLEMP RSCFDn(CFD)GTINTSTSO register TSIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RSCFDnCFDCmFDSTS register     | SOC[7:0], EOC[7:0], SOCO, EOCO, TDCVF, TDCR[6:0]                                 |

| RSCFDn(CFD)CFSTSk register  When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF  RSCFDn(CFD)CFTISTS register  RSCFDn(CFD)TMCp register  TMOM, TMTAR, TMTR  RSCFDn(CFD)TMSTSp register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTRSTSy register  TMTRSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TXQCCm register  TXQE  RSCFDn(CFD)TXQSTSm register  TXQIF, TXQFLL, TXQEMP  RSCFDn(CFD)THLCCm register  THLE  RSCFDn(CFD)THLSTSm register  THLMC[4:0], THLIF, THLELT, THLFLL, THLEMP  RSCFDn(CFD)GTINTSTS0 register  TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RSCFDnCFDCmFDCRC register     | CRCREG[20:0]                                                                     |

| CFFLL, CFEMP, CFMLT, CFRXIF, CFTXIF  RSCFDn(CFD)CFTISTS register  RSCFDn(CFD)TMCp register  TMOM, TMTAR, TMTR  RSCFDn(CFD)TMSTSp register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTRSTSy register  TMTARSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTARSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TXQCCm register  TXQE  RSCFDn(CFD)TXQSTSm register  TXQIF, TXQFLL, TXQEMP  RSCFDn(CFD)THLCCm register  THLE  RSCFDn(CFD)THLSTSm register  THLMC[4:0], THLIF, THLELT, THLFLL, THLEMP  RSCFDn(CFD)GTINTSTSO register  TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RSCFDn(CFD)CFCCk register     | When transmit/receive FIFO buffer is in transmit mode or gateway mode: CFE       |

| RSCFDn(CFD)TMCp register  TMOM, TMTAR, TMTR  RSCFDn(CFD)TMSTSp register  TMTARM, TMTRM, TMTRF[1:0], TMTSTS  RSCFDn(CFD)TMTRSTSy register  TMTRSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTARSTSy register  TMTARSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTCSTSy register  TMTCSTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TMTASTSy register  TMTASTSp (Bits of corresponding channel are initialized in channel reset mode.)  RSCFDn(CFD)TXQCCm register  TXQE  RSCFDn(CFD)TXQSTSm register  TXQIF, TXQFLL, TXQEMP  RSCFDn(CFD)THLCCm register  THLE  RSCFDn(CFD)THLSTSm register  THLE  RSCFDn(CFD)THLSTSm register  TSIFm, TAIFm, TQIFm, CFTIFm, THIFm (m = 0 or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RSCFDn(CFD)CFSTSk register    |                                                                                  |