# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                   |         | Document<br>No.         | TN-R8C-A058B/E                     | Rev.       | 2.00 |

|-----------------------|---------------------------------------------------------------------------|---------|-------------------------|------------------------------------|------------|------|

| Title                 | Caution on using wait mode and stop mode                                  |         | Information<br>Category | Technical Notification             |            |      |

| Applicable<br>Product | R8C/54E, R8C/54F, R8C/54G, R8C/54H,<br>R8C/56E, R8C/56F, R8C/56G, R8C/56H | Lot No. | Reference<br>Document   | Latest user's Manual c<br>products | of applica | ble  |

This caution below applies to wait mode and stop mode in the above mentioned Applicable Products.

#### 1. Description

The interrupt request flag may not be set to "1", when two or more interrupt requests are generated simultaneously under the condition that there are two or more peripheral functions and their operations in wait mode/stop mode are enabled <sup>Note 1</sup>. In this case, the interrupt request flag isn't set to "1" even though another same interrupt source is generated.

Note 1. The peripheral functions, the interrupt request flag (the IR bit in the corresponding interrupt control register) of which is set to "1" (interrupt requested) in wait mode/stop mode.

#### 2. Conditions

This caution shall be applied when all the following conditions are met.

- (1) In Wait mode/Stop mode

- (2) There are two or more peripheral functions and their operations in wait mode/stop mode are enabled.

- (3) An interrupt source A, which is used to exit wait mode/stop mode, is generated and then an enabled peripheral function interrupt source B is generated just when the CPU is started by interrupt source A.

#### 3. Countermeasure

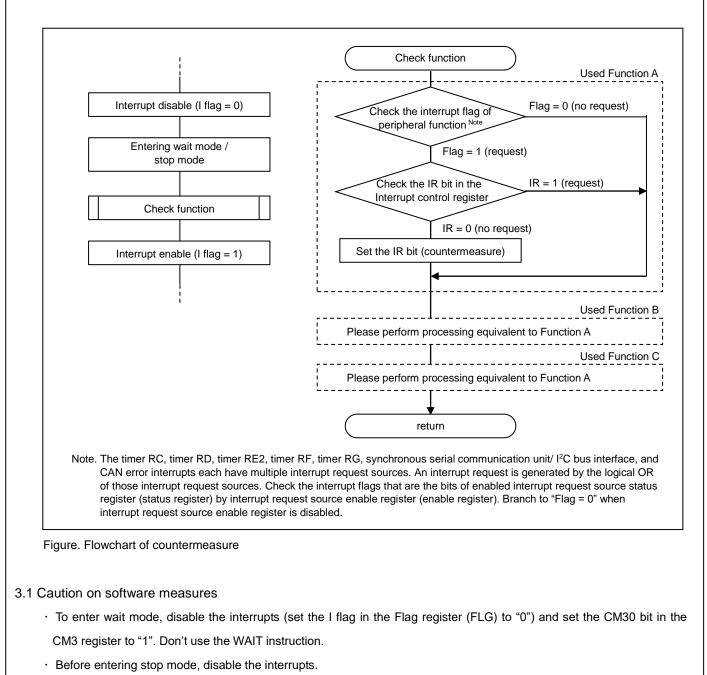

Execute the following countermeasure in your software.

• Disable the interrupt (setting the I flag in the Flag register to "0") before entering wait mode/stop mode. After exiting wait mode/stop mode, compare the interrupt request flag of the peripheral function, the operation of which is enabled, with the interrupt request bit corresponding to the peripheral function. If the peripheral function interrupt flag is set to "1" and the IR bit in the corresponding interrupt control register is set to "0" (no interrupt requested), set the IR bit in the interrupt control register to "1". And then, enable the interrupts (set the I flag to "1"). In this way, the interrupts which have been generated can be processed properly.

- Use the MOV instruction when setting the IR bit in the interrupt control register to "1" as a measure for this caution (caution on using wait mode and stop mode).

- When an "interrupt-judging function" is called as a measure for this caution (caution on using wait mode and stop mode), the stack area are consumed.

#### 3.2 Description of judgement bit

| Interrupt Source                                  | Interrupt flag of the peripheral functions | Interrupt request bit            |

|---------------------------------------------------|--------------------------------------------|----------------------------------|

| Timer RJ_1                                        | LINIF bit in the LINIR_1 register Note 2   | IR bit in the TRJIC_1 register   |

| INT4                                              | INT4S bit in the INTSTS register Note 2    | IR bit in the INT4IC register    |

| Timer RC_0                                        | Each bit in the TRCSR_0 register Note 4    | IR bit in the TRCIC_0 register   |

| <br>Timer RD0_0                                   | Each bit in the TRDSR0_0 register Note 4   | IR bit in the TRD0IC_0 register  |

| Timer RD1_0                                       | Each bit in the TRDSR1_0 register Note 4   | IR bit in the TRD1IC_0 register  |

| UART2 transmit                                    | U2TIF bit in the U2IR register Note 2      | IR bit in the U2TIC register     |

| UART2 receive                                     | U2RIF bit in the U2IR register Note 2      | IR bit in the U2RIC register     |

| Key input                                         | KIIS bit in the KIS register Note 2        | IR bit in the KUPIC register     |

| Synchronous serial communication                  | Each bit in the SISR_0 register Note 4     | IR bit in the SSUIC_0/           |

| unit/ I <sup>2</sup> C bus interface (SSU0/ IIC0) |                                            | IICIC_0 register                 |

| Timer RF/ Compare 0/                              | Each bit in the TRFSR register Note 4      | IR bit in the TRFIC register     |

| Compare 1/Capture Note1                           |                                            |                                  |

| UART0_0 transmit                                  | U0TIF bit in the U0IR_0 register Note 2    | IR bit in the U0TIC_0 register   |

| UART0_0 receive                                   | U0RIF bit in the U0IR_0 register Note 2    | IR bit in the U0RIC_0 register   |

| UART0_1 transmit                                  | U0TIF bit in the U0IR_1 register Note 2    | IR bit in the U0TIC_1 register   |

| UART0_1 receive                                   | U0RIF bit in the U0IR_1 register Note 2    | IR bit in the U0RIC_1 register   |

| INT2                                              | INT2S bit in the INTSTS register Note 2    | IR bit in the INT2IC register    |

| Timer RJ_0                                        | LINIF bit in the LINIR_0 register Note 2   | IR bit in the TRJIC_0 register   |

| Timer RB2_0                                       | TRBIF bit in the TRBIR_0 register          | IR bit in the TRB2IC_0 register  |

| INT1                                              | INT1S bit in the INTSTS register Note 2    | IR bit in the INT1IC register    |

| INT3                                              | INT3S bit in the INTSTS register Note 2    | IR bit in the INT3IC register    |

| INTO                                              | INT0S bit in the INTSTS register Note 2    | IR bit in the INT0IC register    |

| UART2 bus collision detection                     | U2BCNIF bit in the U2IR register Note 2    | IR bit in the U2BCNIC register   |

| Timer RG Note 1                                   | Each bit in the TRGSR register Note 4      | IR bit in the TRGIC register     |

| CAN_0 error                                       | WKUP bit in the CANISR_0 register Note 4   | IR bit in the CANERIC_0 register |

| Voltage monitor 1 Note 3                          | VW1C2 bit in the VW1C register             | IR bit in the VCMP1IC register   |

| Voltage monitor 2 Note 3                          | VW2C2 bit in the VW2C register             | IR bit in the VCMP2IC register   |

| Synchronous serial communication                  | Each bit in the SISR_1 register Note 4     | IR bit in the SSUIC_1/           |

| unit/ I <sup>2</sup> C bus interface (SSU1/ IIC1) |                                            | IICIC_1 register                 |

| Timer RC_1 Note 1                                 | Each bit in the TRCSR_1 register Note 4    | IR bit in the TRCIC_1 register   |

Note:

1. Provided only in R8C/56E, R8C/56F, R8C/56G and R8C/56H products.

2. Refer to "3.3 Register and flag used in a judgement" for the details on the applicable registers and bits.

3. The interrupt source is enabled only when the maskable interrupt is selected.

4. The bits of status register that the corresponding interrupt enable bits are set to 1.

3.3 Register and flag used in a judgement

The red words (registers and flags) are not described in Hardware manual. In the case of not applicable, the setting of these registers and flags is unnecessary.

#### (1) UART0 Interrupt Flag and Enable Register (U0IR)

| Address: 00088h (U0IR_0), 00098h (U0IR_1) |         |       |                 |                |              |                      |                                 |                      |        |  |  |

|-------------------------------------------|---------|-------|-----------------|----------------|--------------|----------------------|---------------------------------|----------------------|--------|--|--|

|                                           | Bit     | b7    | b6              | b5             | b4           | b3                   | b2                              | b1                   | b0     |  |  |

|                                           | Symbol  | U0TIF | UORIF           | -              | -            | U0TIE                | UORIE                           | -                    | -      |  |  |

| Afte                                      | r Reset | 0     | 0               | 0              | 0            | 0                    | 0                               | 0                    | 0      |  |  |

| Bit                                       | Symb    | ol    | E               | Bit Name       |              |                      | Functio                         | n                    | R/W    |  |  |

| b0-b1                                     | -       | No    | thing is assigr | ed. The write  | e value must | be 0. The re         | ad value is 0                   |                      | -      |  |  |

| b2                                        | UORI    | E UA  | RT0 receive in  | nterrupt enab  | ole bit      |                      | interrupt disa<br>interrupt ena |                      | R/W    |  |  |

| b3                                        | UOTII   | E UA  | RT0 transmit    | interrupt ena  | ble bit      |                      | interrupt dis<br>interrupt ena  |                      | R/W    |  |  |

| b4-b5                                     | -       | No    | thing is assigr | ed. The write  | e value must | be 0. The re-        | ad value is 0                   |                      | -      |  |  |

| b6                                        | UORI    | F UA  | RT0 receive in  | nterrupt requ  | est flag     | • When the 0 from 1. | IR bit of the<br>Witten to the  | se flag becom        | es R/W |  |  |

| b7                                        | UOTII   | F UA  | RT0 transmit    | interrupt requ | uest flag    | -                    | for setting to interrupt req    | 1]<br>Juest of these | R/W    |  |  |

#### (2) Timer RJ/ LIN Interrupt Request Register (LINIR)

|       | Bit                                                                    | b7 | b6               | b5            | b4      | b3                                                               | b2                                                          | b1                             | b0        |  |

|-------|------------------------------------------------------------------------|----|------------------|---------------|---------|------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-----------|--|

|       | Symbol                                                                 | -  | -                | -             | -       | -                                                                | -                                                           | -                              | TRJIF     |  |

| Afte  | r Reset                                                                | Х  | Х                | Х             | Х       | Х                                                                | Х                                                           | Х                              | 0         |  |

| Bit   | Symbo                                                                  | bl | E                | Bit Name      |         |                                                                  | Functio                                                     | n                              | R/W       |  |

| b0    | LINIF                                                                  | т  | imer RJ/ LIN int | terrupt reque | st flag | When the<br>0 from 1.     When 0 is<br>reading it<br>[Condition] | s written to th<br>as 1.<br>for setting to<br>interrupt req | se flag become<br>is bit after | es<br>R/W |  |

| b1-b7 | - Nothing is assigned. The write value must be 0. The read value is 0. |    |                  |               |         |                                                                  |                                                             |                                |           |  |

#### (3) UART2 Interrupt Status Register (U2IR)

Address: 000D8h (U2IR)

| Bit         | b7    | b6    | b5 | b4      | b3 | b2 | b1 | b0 |

|-------------|-------|-------|----|---------|----|----|----|----|

| Symbol      | U2TIF | U2RIF | -  | U2BCNIF | -  | -  | -  | -  |

| After Reset | 0     | 0     | 0  | 0       | 0  | 0  | 0  | 0  |

| Bit       | Symbol  | Bit Name                                       | Function                                                   | R/W |

|-----------|---------|------------------------------------------------|------------------------------------------------------------|-----|

| b0-b3     | -       | Reserved                                       | Set to 0.                                                  | R/W |

| b4        | U2BCNIF | Bus collision detection interrupt request flag | 0: No interrupt requested Note 1<br>1: Interrupt requested | R/W |

| b5        | -       | Reserved                                       | Set to 0.                                                  | R/W |

| <b>b6</b> | U2RIF   | Receive interrupt request flag                 | 0: No interrupt requested Note 1                           | R/W |

| b7        | U2TIF   | Transmit interrupt request flag                | 1: Interrupt requested                                     | R/W |

Note 1. The flag is set to 0 only when 0 is written after reading 1.

[Conditions for setting to 0]

• When the IR bit of these flag becomes 0 from 1.

• When 0 is written to this bit after reading it as 1.

[Condition for setting to 1]

• When the interrupt request of these flag occurs.

| Address: 0                                                    |                                                                                                             |                                             | * · · · · · · · · · · · · · · · · · · ·                                                                                         |                                                                                                                   |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |                                                                                                        |                                                                               |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 0                                                             | Bit                                                                                                         | b7                                          |                                                                                                                                 | b5                                                                                                                | b4                                                                                                                                                                                                                                                                       | b3                                                                                                                                                                                                                                                           | b2                                                                                                                                                                                                                    | b1                                                                                                     | b0                                                                            |

|                                                               | Symbol<br>Reset                                                                                             | - 0                                         | - 0                                                                                                                             | - 0                                                                                                               | <u>INT4S</u><br>0                                                                                                                                                                                                                                                        | INT3S                                                                                                                                                                                                                                                        | INT2S<br>0                                                                                                                                                                                                            | INT1S<br>0                                                                                             | INT0<br>0                                                                     |

| Allei                                                         | Reset                                                                                                       | 0                                           | 0                                                                                                                               | 0                                                                                                                 | 0                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                     | 0                                                                                                      | 0                                                                             |

| Bit                                                           | Symbol                                                                                                      |                                             | Bit Na                                                                                                                          | ame                                                                                                               |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                              | Function                                                                                                                                                                                                              |                                                                                                        | F                                                                             |

| b0                                                            | INT0S                                                                                                       |                                             | INT0 interrupt re                                                                                                               | quest flag                                                                                                        | [Conditi                                                                                                                                                                                                                                                                 | ons for setting                                                                                                                                                                                                                                              | g to 0]                                                                                                                                                                                                               |                                                                                                        | F                                                                             |

| b1                                                            | INT1S                                                                                                       |                                             | INT1 interrupt re                                                                                                               | quest flag                                                                                                        | • When the IR bit of these flag becomes 0 from 1.                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |                                                                                                        |                                                                               |

| b2                                                            | INT2S                                                                                                       |                                             | INT2 interrupt re                                                                                                               | quest flag                                                                                                        |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       | r reading it as                                                                                        |                                                                               |

| b3                                                            | INT3S                                                                                                       |                                             | INT3 interrupt re                                                                                                               | · •                                                                                                               |                                                                                                                                                                                                                                                                          | on for setting                                                                                                                                                                                                                                               |                                                                                                                                                                                                                       |                                                                                                        | F                                                                             |

| b4                                                            | INT4S                                                                                                       |                                             | INT4 interrupt re                                                                                                               | quest flag                                                                                                        |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                              | equest of th                                                                                                                                                                                                          | iese flag occu                                                                                         |                                                                               |

| b5-b7                                                         | -                                                                                                           |                                             | Reserved                                                                                                                        |                                                                                                                   | Set to 0                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |                                                                                                        | F                                                                             |

| ey Input Inte<br>Address: 0                                   |                                                                                                             |                                             | gister (KIS)                                                                                                                    |                                                                                                                   |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |                                                                                                        |                                                                               |

|                                                               | Bit                                                                                                         | b7                                          | b6                                                                                                                              | b5                                                                                                                | b4                                                                                                                                                                                                                                                                       | b3                                                                                                                                                                                                                                                           | b2                                                                                                                                                                                                                    | b1                                                                                                     | b0                                                                            |

| S                                                             | Symbol                                                                                                      | KIIS                                        | 6 -                                                                                                                             | -                                                                                                                 | -                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                     | -                                                                                                      | -                                                                             |

| After                                                         | Reset                                                                                                       | 0                                           | 0                                                                                                                               | 0                                                                                                                 | 0                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                     | 0                                                                                                      | 0                                                                             |

| Bit                                                           | Symbol                                                                                                      |                                             | Bit Na                                                                                                                          | ame                                                                                                               |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                              | Function                                                                                                                                                                                                              |                                                                                                        | F                                                                             |

| b0-b6                                                         | -                                                                                                           |                                             | Reserved                                                                                                                        |                                                                                                                   | Set to 0                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |                                                                                                        |                                                                               |

| b7                                                            | b7 KIIS Key input interrupt request fla                                                                     |                                             |                                                                                                                                 |                                                                                                                   | <ul> <li>[Conditions for setting to 0]</li> <li>When the IR bit of these flag becomes 0 from 1.</li> <li>When 0 is written to this bit after reading it as 1.</li> <li>[Condition for setting to 1]</li> <li>When the interrupt request of these flag occurs.</li> </ul> |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |                                                                                                        |                                                                               |

| /oltage Monit                                                 |                                                                                                             | it Con                                      | ntrol Register (VW                                                                                                              |                                                                                                                   | [Conditi                                                                                                                                                                                                                                                                 | on for setting                                                                                                                                                                                                                                               | to 1]                                                                                                                                                                                                                 | -                                                                                                      |                                                                               |

| /oltage Monit<br>Address: 0                                   | tor 1 Circui<br>00039h (VV                                                                                  | V1C)                                        | ntrol Register (VM                                                                                                              | /1C)                                                                                                              | [Conditi<br>• When                                                                                                                                                                                                                                                       | on for setting<br>the interrupt r                                                                                                                                                                                                                            | to 1]<br>request of th                                                                                                                                                                                                | ese flag occu                                                                                          | rs.                                                                           |

| Address: 0                                                    | tor 1 Circui<br>00039h (VV<br>Bit                                                                           | W1C)<br>b7                                  | ntrol Register (VM                                                                                                              | /1C)<br>b5                                                                                                        | [Conditi<br>• When                                                                                                                                                                                                                                                       | on for setting<br>the interrupt r<br>b3                                                                                                                                                                                                                      | to 1]<br>request of th<br>b2                                                                                                                                                                                          | b1                                                                                                     | rs.                                                                           |

| Address: 0                                                    | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol                                                                 | V1C)                                        | ntrol Register (VM                                                                                                              | /1C)                                                                                                              | [Conditi<br>• When                                                                                                                                                                                                                                                       | on for setting<br>the interrupt r                                                                                                                                                                                                                            | to 1]<br>request of th                                                                                                                                                                                                | ese flag occu                                                                                          | rs.                                                                           |

| Address: 0<br>S<br>After                                      | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset                                                        | V1C)<br>b7<br>VW10<br>1                     | ntrol Register (VW<br>b6<br>C7 -<br>0                                                                                           | /1C)<br>                                                                                                          | [Conditi<br>• When<br>b4<br>VW1F0                                                                                                                                                                                                                                        | on for setting<br>the interrupt r<br>b3<br>VW1C3                                                                                                                                                                                                             | to 1]<br>request of th<br>b2<br>VW1C2<br>0                                                                                                                                                                            | b1<br>VW1C1<br>1                                                                                       | rs.<br>b0<br>VW10<br>0                                                        |

| Address: 0                                                    | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol                                                                 | V1C)<br>b7<br>VW10<br>1                     | ntrol Register (VW<br>b6<br>C7 -<br>0                                                                                           | /1C)<br>                                                                                                          | [Conditi<br>• When<br>b4<br>VW1F0                                                                                                                                                                                                                                        | b3<br>VW1C3                                                                                                                                                                                                                                                  | to 1]<br>equest of th<br>b2<br>VW1C2<br>0<br>Functio                                                                                                                                                                  | b1<br>VW1C1<br>1                                                                                       | <u>b0</u><br>VW10<br>0                                                        |

| Address: 0<br>S<br>After                                      | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset                                                        | V1C)<br>b7<br>VW10<br>1                     | ntrol Register (VW<br>b6<br>C7 -<br>0                                                                                           | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name                                                                              | b4<br>VW1F0<br>0                                                                                                                                                                                                                                                         | b3<br>VW1C3<br>1<br>0: Disabled                                                                                                                                                                                                                              | to 1]<br>equest of th<br>b2<br>VW1C2<br>0<br>Functio                                                                                                                                                                  | b1<br>VW1C1<br>1                                                                                       | rs.<br>b0<br>VW10                                                             |

| Address: 0<br>S<br>After<br>Bit                               | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset<br>Symbol                                              | V1C)<br>b7<br>VW10<br>1                     | htrol Register (VM<br>b6<br>C7 -<br>0                                                                                           | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name<br>1 interrupt ena                                                           | [Conditi       • When       b4       VW1F0       0                                                                                                                                                                                                                       | on for setting<br>the interrupt r<br>b3<br>VW1C3<br>1<br>0: Disabled<br>1: Enabled<br>0: Digital fil<br>(digital fil<br>1: Digital fil                                                                                                                       | to 1]<br>request of th<br>b2<br>VW1C2<br>0<br>Functio                                                                                                                                                                 | b1<br>VW1C1<br>1<br>mode<br>nabled)<br>mode                                                            | b0<br>VW10<br>0<br>F                                                          |

| Address: 0<br>S<br>After<br>Bit<br>b0                         | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset<br><br>Symbol<br><br>VW1C0                             | V1C)<br>b7<br>VW1(<br>1<br>I                | htrol Register (VW<br><u>b6</u><br>C7 <u>-</u><br>0<br>Voltage monitor                                                          | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name<br>1 interrupt ena<br>1 digital filter m                                     | [Conditi       • When       b4       VW1F0       0                                                                                                                                                                                                                       | on for setting<br>the interrupt r<br>b3<br>VW1C3<br>1<br>0: Disabled<br>1: Enabled<br>0: Digital fil<br>(digital fil<br>(digital fil<br>(digital fil<br>0: Not dete<br>1: Detected                                                                           | to 1]<br>equest of the<br>b2<br>VW1C2<br>0<br>Function<br>ter enabled<br>ter circuit er<br>ter disabled<br>ter circuit dis<br>cted<br>I by passing                                                                    | b1<br>VW1C1<br>1<br>mode<br>nabled)<br>mode                                                            | rs.<br>b0<br>VW10<br>F<br>F<br>F                                              |

| Address: 0<br>S<br>After<br>Bit<br>b0<br>b1                   | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset<br><br>VW1C0<br><br>VW1C1                              | V1C)<br>b7<br>VW10<br>1<br>1<br>0           | htrol Register (VW<br>b6<br>C7 -<br>0<br>Voltage monitor<br>Voltage monitor<br>select bit                                       | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name<br>1 interrupt ena<br>1 digital filter m<br>detection flag                   | [Conditi<br>• When<br>b4<br>VW1F0<br>0<br>ble bit<br>hode                                                                                                                                                                                                                | on for setting<br>the interrupt r<br>b3<br>VW1C3<br>1<br>0: Disabled<br>1: Enabled<br>0: Digital fil<br>(digital fil<br>1: Digital fil<br>(digital fil<br>0: Not dete<br>1: Detected<br>0: VCC < V                                                           | to 1]<br>equest of the<br>b2<br>VW1C2<br>0<br>Function<br>ter enabled<br>ter circuit er<br>ter disabled<br>ter circuit dis<br>cted<br>I by passing<br>det1<br>det1 or volta                                           | b1<br>VW1C1<br>1<br>mode<br>nabled)<br>mode<br>sabled)                                                 | rs.<br>b0<br>VW10<br>0<br>F<br>F<br>1<br>F                                    |

| Address: 0<br>S<br>After<br>Bit<br>b0<br>b1<br>b1<br>b2       | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset<br><br>VW1C0<br><br>VW1C1                              | V1C)<br>b7<br>VW10<br>1<br>1<br>1<br>2<br>3 | htrol Register (VW<br>b6<br>C7 -<br>0<br>Voltage monitor<br>Voltage monitor<br>select bit<br>Voltage change<br>Voltage detectio | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name<br>1 interrupt ena<br>1 digital filter m<br>detection flag<br>n 1 signal mon | [Conditi<br>• When<br>b4<br>VW1F0<br>0<br>ble bit<br>hode                                                                                                                                                                                                                | on for setting<br>the interrupt r<br>b3<br>VW1C3<br>1<br>0: Disabled<br>1: Enabled<br>0: Digital fil<br>(digital fil<br>1: Digital fil<br>(digital fil<br>0: Not deter<br>1: Detected<br>0: VCC < V<br>1: VCC ≥ V<br>circuit dis<br>00B: fLOCC<br>01B: fLOCC | to 1]<br>equest of the<br>b2<br>VW1C2<br>0<br>Function<br>ter enabled<br>ter circuit er<br>ter disabled<br>ter circuit dis<br>cted<br>I by passing<br>det1<br>det1 or volta<br>sabled<br>D divided by<br>D divided by | b1<br>VW1C1<br>1<br>on<br>mode<br>habled)<br>mode<br>sabled)<br>through Vdet<br>age detection          | rs.<br>b0<br>VW10<br>0<br>F<br>F<br>1<br>1                                    |

| Address: 0<br>S<br>After<br>Bit<br>b0<br>b1<br>b1<br>b2<br>b3 | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset<br>Symbol<br>VW1C0<br>VW1C1<br>VW1C2<br>VW1C2          | V1C)<br>b7<br>VW1(<br>1<br>)                | htrol Register (VM<br>b6<br>C7 -<br>0<br>Voltage monitor<br>Voltage monitor<br>select bit<br>Voltage change                     | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name<br>1 interrupt ena<br>1 digital filter m<br>detection flag<br>n 1 signal mon | [Conditi<br>• When<br>b4<br>VW1F0<br>0<br>ble bit<br>hode                                                                                                                                                                                                                | b3<br>VW1C3<br>1<br>0: Disabled<br>1: Enabled<br>0: Digital fill<br>(digital fill<br>1: Detected<br>0: VCC < V<br>1: VCC ≥ V<br>circuit dis<br>00B: fLOCC<br>10B: fLOCC                                                                                      | to 1]<br>equest of the<br>b2<br>VW1C2<br>0<br>Function<br>ter enabled<br>ter circuit er<br>ter disabled<br>ter circuit dis<br>cited<br>I by passing<br>det1<br>det1 or volta<br>sabled<br>D divided by                | b1<br>VW1C1<br>1<br>mode<br>habled)<br>mode<br>sabled)<br>through Vdet<br>age detection<br>1<br>2<br>4 | b0           VW10           0           F           1           F           1 |

| Address: 0<br>S<br>After<br>Bit<br>b0<br>b1<br>b2<br>b3<br>b4 | tor 1 Circui<br>00039h (VV<br>Bit<br>Symbol<br>Reset<br>Symbol<br>VW1C0<br>VW1C1<br>VW1C2<br>VW1C3<br>VW1C3 | V1C)<br>b7<br>VW1(<br>1<br>)                | htrol Register (VW<br>b6<br>C7 -<br>0<br>Voltage monitor<br>Voltage monitor<br>select bit<br>Voltage change<br>Voltage detectio | /1C)<br>b5<br>VW1F1<br>0<br>Bit Name<br>1 interrupt ena<br>1 digital filter m<br>detection flag<br>n 1 signal mon | [Conditi<br>• When<br>b4<br>VW1F0<br>0<br>ble bit<br>hode                                                                                                                                                                                                                | b3<br>VW1C3<br>1<br>0: Disabled<br>1: Enabled<br>0: Digital filt<br>(digital filt<br>(digital filt<br>(digital filt<br>0: Not deter<br>1: Detected<br>0: VCC < V<br>1: VCC ≥ V<br>circuit dis<br>00B: fLOCC<br>10B: fLOCC                                    | to 1]<br>equest of the<br>b2<br>VW1C2<br>0<br>Function<br>ter enabled<br>ter circuit er<br>ter disabled<br>ter circuit dis<br>cted<br>I by passing<br>det1<br>det1 or volta<br>sabled<br>D divided by<br>D divided by | b1<br>VW1C1<br>1<br>mode<br>habled)<br>mode<br>sabled)<br>through Vdet<br>age detection<br>1<br>2<br>4 | rs.<br>b0<br>VW10<br>0<br>F<br>F<br>1<br>F                                    |

(7) Voltage Monitor 2 Circuit Control Register (VW2C)

|                                                                      | Bit     | b7   |         | b6                                                                                             | b5                                                             | b4         | b3                                                                          | b2                                                                     | b1             | b0   |

|----------------------------------------------------------------------|---------|------|---------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|------|

|                                                                      | Symbol  | VW20 | 27      | -                                                                                              | VW2F1                                                          | VW2F0      | VW2C3                                                                       | VW2C2                                                                  | VW2C1          | VW20 |

| Afte                                                                 | r Reset | 1    |         | 0                                                                                              | 0                                                              | 0          | 1                                                                           | 0                                                                      | 1              | 0    |

| Bit                                                                  | Symt    | bol  |         |                                                                                                | Bit Name                                                       |            | Function                                                                    |                                                                        |                |      |

| b0 VW2C0                                                             |         |      | Voltage | e monitor                                                                                      | 2 interrupt er                                                 | able bit   | 0: Disabled<br>1: Enabled                                                   | l                                                                      |                | F    |

| b1 VW2C1 Voltage mor<br>select bit                                   |         |      |         |                                                                                                | 2 digital filter                                               | mode       | (digital fil<br>1: Digital fil                                              | ter enabled r<br>Iter circuit en<br>ter disabled i<br>Iter circuit dis | abled)<br>mode | F    |

| b2                                                                   | VW2     | C2   | Voltage | Itage change detection flag       0: Not detected         1: Detected by passing through Vdet2 |                                                                |            |                                                                             | 2 F                                                                    |                |      |

| b3                                                                   | VW2     | C3   | Voltage | e detectio                                                                                     | on 2 signal mo                                                 | nitor flag | 0: VCC < Vdet2<br>1: VCC ≥ Vdet2 or voltage detection 2<br>circuit disabled |                                                                        |                |      |

| b4                                                                   | VW2     | -    | o       |                                                                                                | 1                                                              |            |                                                                             | O divided by<br>O divided by                                           |                | F    |

| b5                                                                   | VW2     |      | Sampli  | ng clock                                                                                       | select bits                                                    |            | 10B: fLOCO divided by 4<br>11B: fLOCO divided by 8                          |                                                                        |                |      |

| b6                                                                   | -       |      | Reserv  | ved                                                                                            |                                                                |            | Set to 0.                                                                   |                                                                        |                | F    |

| b7 VW2C7 Voltage monitor 2 interrupt generation condition select bit |         |      |         | eneration                                                                                      | 0: VCC reaches Vdet2 or above<br>1: VCC reaches Vdet2 or below |            |                                                                             | F                                                                      |                |      |

## (8) SI Status Register (SISR)

SSU Function:

Address: 000EAh (SISR\_0), 000FAh (SISR\_1)

|      | Bit                           | b7                 | 7    | b6             | b5                                           | b4                                                                                                                     | b3                                                                                                                                                                         | b2       | b1  | b0     |  |  |

|------|-------------------------------|--------------------|------|----------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|--------|--|--|

|      | Symbol                        | TDF                | RE   | TEND           | RDRF                                         | NACKF                                                                                                                  | STOP                                                                                                                                                                       | ORER_AL  | AAS | CE_ADZ |  |  |

| Afte | er Reset                      | 0                  |      | 0              | 0                                            | 0                                                                                                                      | 0                                                                                                                                                                          | 0        | 0   | 0      |  |  |

| Bit  | Symt                          | loc                |      | Bit Na         | me                                           |                                                                                                                        |                                                                                                                                                                            | Function |     | R/W    |  |  |

| b0   | CE_A                          | CE_ADZ Conflict er |      |                | ag 0: No conflict error<br>1: Conflict error |                                                                                                                        |                                                                                                                                                                            |          |     | R/W    |  |  |

| b1   | AAS                           | S                  | Res  | erved          |                                              | Set to 0.                                                                                                              |                                                                                                                                                                            |          |     | R/W    |  |  |

| b2   | ORER                          |                    |      |                |                                              | 0: No ov<br>1: Overr                                                                                                   | errun error<br>un error                                                                                                                                                    |          |     | R/W    |  |  |

| b3   | STO                           | P                  | Res  | erved          |                                              | Set to 0.                                                                                                              |                                                                                                                                                                            |          |     | R/W    |  |  |

| b4   | NAC                           | KF                 | Res  | erved          |                                              | Set to 0.                                                                                                              | Set to 0.                                                                                                                                                                  |          |     |        |  |  |

| b5   | RDR                           | ۲F                 | Rec  | eive data reg  | ister full flag                              |                                                                                                                        | 0: No data in the SIRDR register<br>1: Data present in the SIRDR register                                                                                                  |          |     |        |  |  |

| b6   | TEN                           | D                  | Trar | nsmit end flag | I                                            | data is<br>1: The T                                                                                                    | <ul> <li>0: The TDRE bit is 0 when the last bit of transmit data is transmitted</li> <li>1: The TDRE bit is 1 when the last bit of transmit data is transmitted</li> </ul> |          |     |        |  |  |

| b7   | TDRE Transmit data empty flag |                    |      | npty flag      | SISDF<br>1: Data i                           | 0: Data is not transferred from registers SITDR to<br>SISDR<br>1: Data is transferred from registers SITDR to<br>SISDR |                                                                                                                                                                            |          |     |        |  |  |

| I <sup>2</sup> C | bus Fund | ction:    |       |                                |              |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |                                                                                         |                                                                                                                                |       |  |

|------------------|----------|-----------|-------|--------------------------------|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|--|

|                  | Address: | 000EAh (S | SISR_ | 0), 000                        | FAh (SISR    | _1)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |                                                                                         |                                                                                                                                |       |  |