Date: Mar. 24, 2017

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                                                                                                          | Document<br>No.      | TN-RIN-A017           | A/E                                                                          | Rev. | 1.00    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------------------------------------------------------------------------------|------|---------|

| Title                 | Notification of R-IN32M3 Series User's Peripheral Modules (Rev.9.00 to Rev.10 Revised contents: Corrections and new | v.9.00 to Rev.10.00) |                       | Information Category Technical Notification                                  |      |         |

|                       | Lot No.                                                                                                             |                      |                       | R-IN32M3 Serie                                                               |      | Manual: |

| Applicable<br>Product | See following                                                                                                       | All lots             | Reference<br>Document | Peripheral Mode<br>R-IN32M3-EC,<br>R-IN32M3-CL<br>Rev. 10.00<br>(R18UZ0007EJ |      |         |

R-IN32M3 Series User's Manual Peripheral Modules Rev. 10.00 (R18UZ0007EJ1000) has been released on Renesas website. This technical update follows revision 9.00 and includes the entirety of revised items. For details, refer to "2. Documentation Updates" given below. Please take note that items marked with "\*note" may have severe impact on the specification and limitation of corresponding devices.

#### 1 Applicable Product

| Product Type   | Model Marking   | Product Code         |

|----------------|-----------------|----------------------|

|                | MC-10287F1      | MC-10287F1-HN4-A     |

| R-IN32M3-EC    | WC-10207F1      | MC-10287F1-HN4-M1-A  |

| K-IN32IVI3-EC  | MC-10287BF1     | MC-10287BF1-HN4-A    |

|                | IVIC-10207 BF 1 | MC-10287BF1-HN4-M1-A |

|                | D60510F1        | UPD60510F1-HN4-A     |

| R-IN32M3-CL    | D00310F1        | UPD60510F1-HN4-M1-A  |

| K-IINOZIVIO-GL | D60510BF1       | UPD60510BF1-HN4-A    |

|                | DOUGIUDEI       | UPD60510BF1-HN4-M1-A |

#### 2 Documentation Updates

(1/3)

| No | Applicable Item (Rev. 10.00 Section)                                            | Applicable<br>Page<br>(Rev. 10.00) | Contents             |

|----|---------------------------------------------------------------------------------|------------------------------------|----------------------|

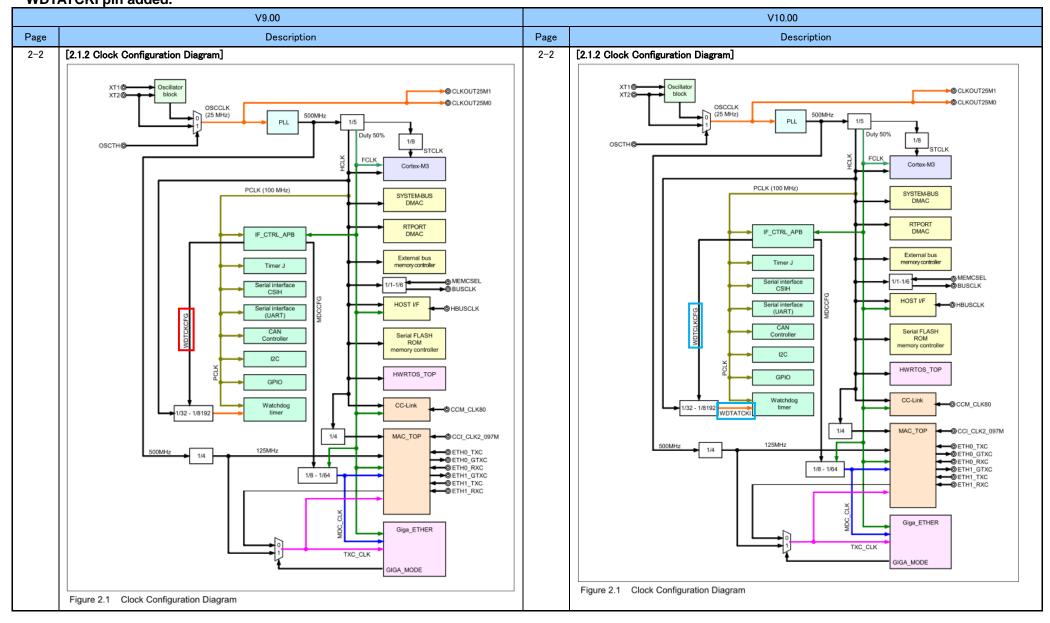

| 1  | 2.1.2 Clock Configuration Diagram                                               | 2-2                                | Complement           |

| 2  | 3.4.1 Outline of Features                                                       | 3-3                                | New function         |

| 3  | 3.5.1 Outline of Features                                                       | 3-4                                | New function         |

| 4  | 3.6.1 Outline of Features                                                       | 3-5                                | New function         |

| 5  | 7.3.4.1 MIIM Register (GMAC_MIIM)                                               | 7-9                                | Complement           |

| 6  | 7.3.4.3 TX Result Register (GMAC_TXRESULT)                                      | 7-11                               | Complement           |

| 7  | 7.3.4.5 RX Mode Register (GMAC_RXMODE) *note                                    | 7-12 to 7-13                       | Error correction     |

| 8  | 7.3.4.6 TX Mode Register (GMAC_TXMODE) *note                                    | 7-14 to 7-15                       | Error correction     |

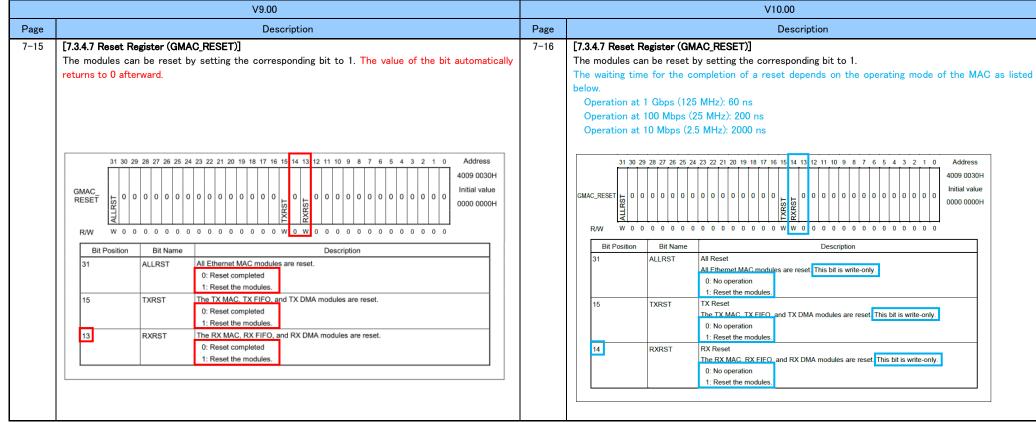

| 9  | 7.3.4.7 Reset Register (GMAC_RESET) *note                                       | 7-16                               | Error correction     |

| 10 | 7.3.4.9 RX Flow Control Register (GMAC_FLWCTL)                                  | 7-18                               | Error correction     |

| 11 | 7.3.4.10 Pause Packet Register (GMAC_PAUSPKT)                                   | 7-19                               | Complement           |

| 12 | 7.3.4.12 RX FIFO Status Register (GMAC_RXFIFO) *note                            | 7-21                               | Error correction     |

| 13 | 7.3.4.13 TX FIFO Status Register (GMAC_TXFIFO)                                  | 7-22                               | New function         |

| 14 | 7.3.4.14 TCPIPACC Register (GMAC_ACC)                                           | 7-23                               | Expression alignment |

| 15 | 7.3.4.16 LPI mode control register (GMAC_LPI_MODE)                              | 7-24                               | Complement           |

| 16 | 7.3.4.18 Receive Buffer Information Register (BUFID)                            | 7-25                               | Complement           |

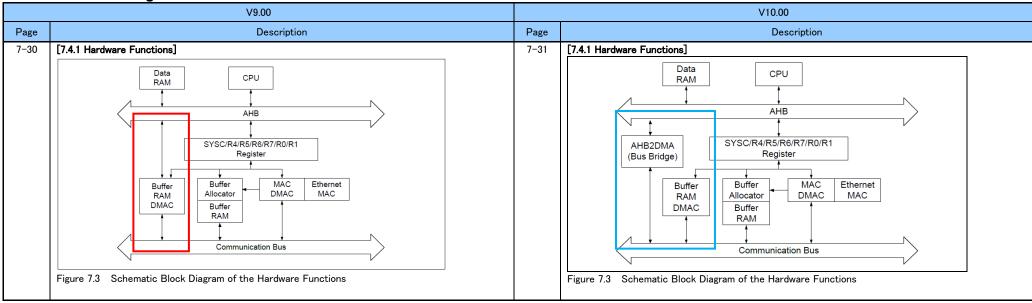

| 17 | 7.4.1 Hardware Functions                                                        | 7-31                               | Expression alignment |

| 18 | 7.4.1.1 Initial Settings *note                                                  | 7-32                               | Error correction     |

| 19 | 7.4.1.3(1) Functional Overview                                                  | 7-33                               | Complement           |

| 20 | 7.4.1.3(2)(e) List of hardware function calls                                   | 7-36                               | Complement           |

| 21 | 7.4.1.3(2)(e) List of hardware function calls                                   | 7-39                               | Expression alignment |

| 22 | 7.4.1.4(2) DMA for the Reception MAC *note                                      | 7-41                               | Error correction     |

| 23 | 7.4.1.4(2)(a) Description of the Individual functions of the MAC DMA controller | 7-42                               | Complement           |

| 24 | 7.4.1.4(2)(a) Description of the Individual functions of the MAC DMA controller | 7-43                               | Error correction     |

| 25 | 7.4.1.4(2)(b) Usage                                                             | 7-44                               | Error correction     |

| 26 | 7.4.1.4(2)(c) List of hardware function calls                                   | 7-45                               | Error correction     |

| 27 | 7.4.1.4(2)(c) List of hardware function calls                                   | 7-46                               | Error correction     |

0 (0)

Date: Mar. 24, 2017

|                                                                                                                                              | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NI.                                                                                                                                          | Angliachte Hage (Day 40 00 Casting)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Applicable                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| No                                                                                                                                           | Applicable Item (Rev. 10.00 Section)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page<br>(Rev. 10.00)                                                                                                                                         | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 28                                                                                                                                           | 7.4.1.4(2)(c) List of hardware function calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-47                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29                                                                                                                                           | 7.4.1.4(3)(d) List of hardware function calls *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-50                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 30                                                                                                                                           | 7.4.1.5(2)(a) Transfer between the buffer RAM and the data RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-51                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31                                                                                                                                           | 7.4.1.5(2)(b) Replacing data in the buffer RAM or data RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-51                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 32                                                                                                                                           | 7.4.1.5(2)(c) Transfer between the buffer RAMs *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-51                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 33                                                                                                                                           | 7.4.1.5(2)(d) List of hardware function calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-52                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 34                                                                                                                                           | 7.4.1.5(2)(d) List of hardware function calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-53                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 35                                                                                                                                           | 7.4.2 Interrupts *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-56                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 36                                                                                                                                           | 7.4.2 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-58                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 37                                                                                                                                           | 7.4.3.1 Acquiring a Transmit Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-60                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

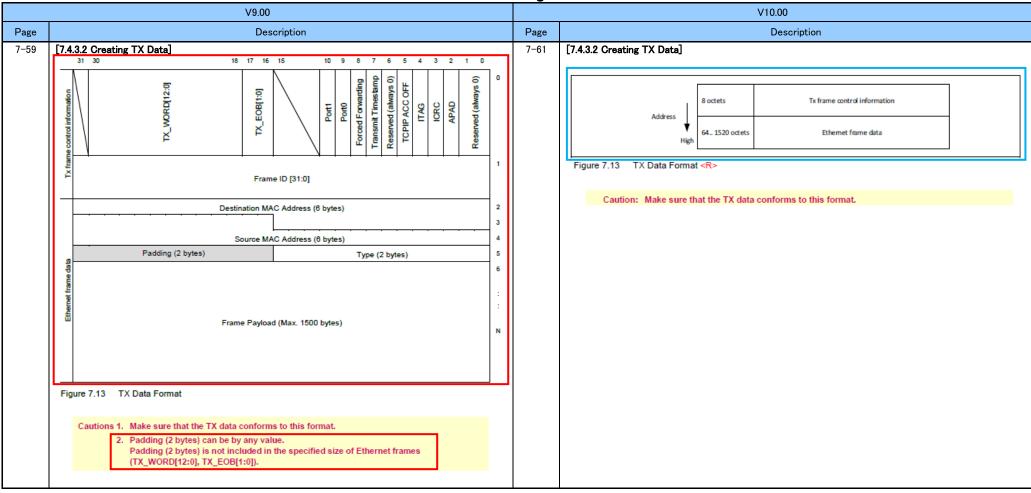

| 38                                                                                                                                           | 7.4.3.2 Creating TX Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-61                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 39                                                                                                                                           | 7.4.3.2(1) Tx frame control information *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-63                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 40                                                                                                                                           | 7.4.3.2(1) Tx frame control information *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-63                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 41                                                                                                                                           | 7.4.3.2(2) Ethernet frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-64                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 42                                                                                                                                           | 7.4.3.2(2) Ethernet frame *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-65 to 7-66                                                                                                                                                 | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 43                                                                                                                                           | 7.4.3.3 Creating TX Descriptors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-67                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 44                                                                                                                                           | 7.4.3.5 Completion of Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-68                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 45                                                                                                                                           | 7.4.3.3 Completion of Transmission 7.4.4 Receiving Ethernet Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-69                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-09                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

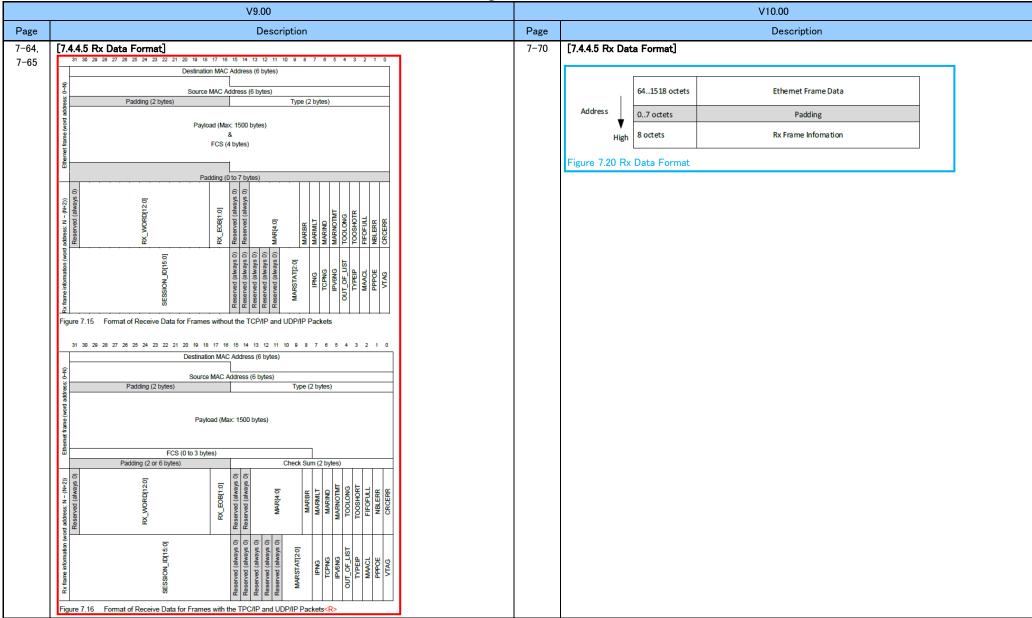

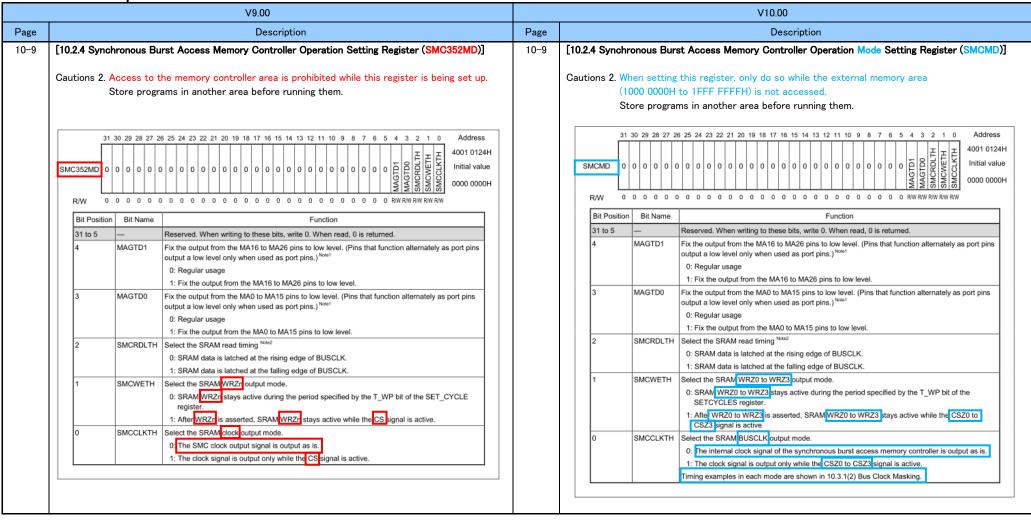

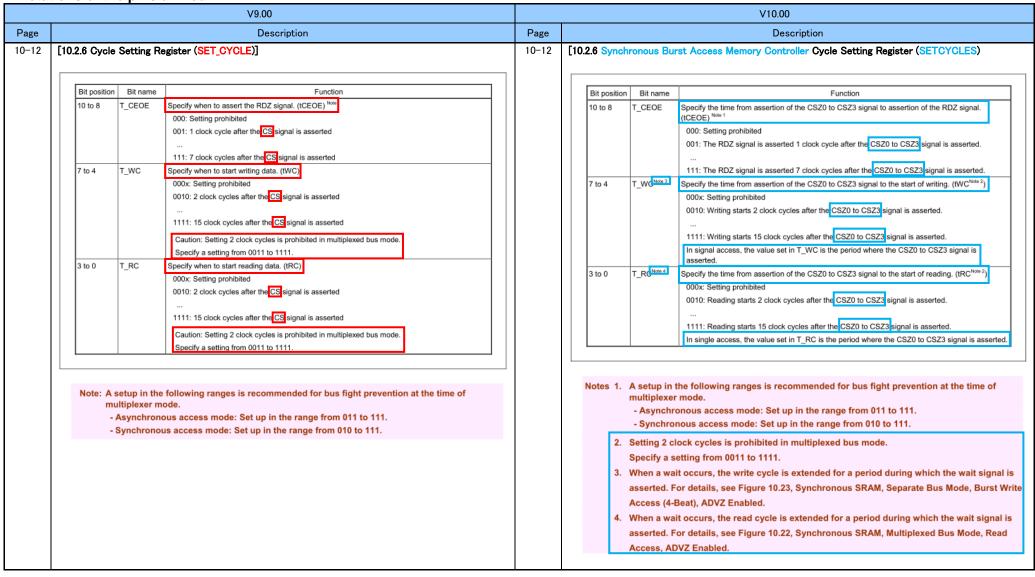

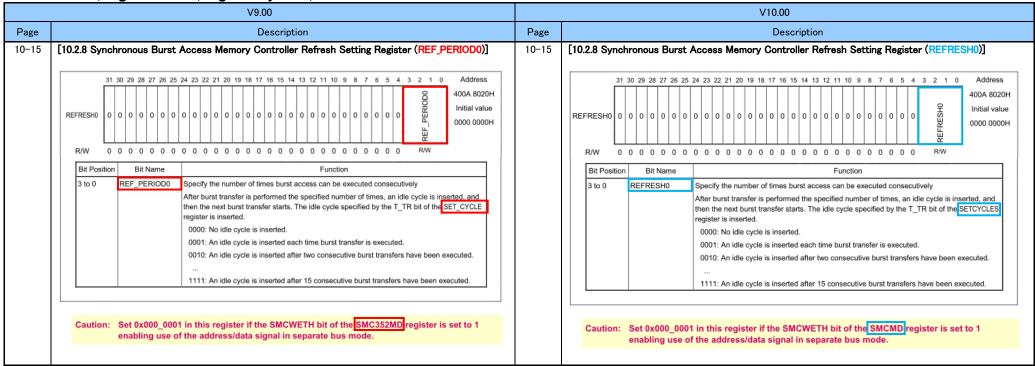

| 46                                                                                                                                           | 7.4.4.5 Rx Data Format *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-70                                                                                                                                                         | Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 47                                                                                                                                           | 7.4.4.5 Rx Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 48                                                                                                                                           | 7.4.4.5(1) Rx frame information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-71                                                                                                                                                         | Expression alignmen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 49                                                                                                                                           | 7.4.4.5(1) Rx frame information *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-71 to 7-72                                                                                                                                                 | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 50                                                                                                                                           | 7.4.4.5(1) Rx frame information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-72                                                                                                                                                         | Expression alignmen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 51                                                                                                                                           | 7.4.4.5(2) Rx Ethernet frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-73                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 52                                                                                                                                           | 7.4.4.5(2) Rx Ethernet frame *note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-74                                                                                                                                                         | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |