# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                                                                                                                                    | em LSI Document No. TN-RIN-A008A/E |                         | 3A/E                   | Rev.     | 1.00    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------|------------------------|----------|---------|

| Title                 | Notification of R-IN32M3 Series User's Manual Peripheral<br>Modules (Rev.7.00 to Rev.8.00)<br>Revised contents: Corrections and new functions |                                    | Information<br>Category | Technical Notification |          |         |

|                       |                                                                                                                                               | Lot No.                            |                         | R-IN32M3 Serie         | s User's | Manual: |

| Applicable<br>Product | See following                                                                                                                                 | All lots                           | Reference<br>Document   | R-IN32M3-EC_R-IN32M3-  |          | 3-CL    |

R-IN32M3 Series User's Manual Peripheral Modules Rev. 8.00 (R18UZ0007EJ0800) has been released on Renesas website. For details, see "2. Documentation Updates" as below. In addition, as the item marked with "caution needed" may cause a failure on the device. Please confirm the item if it corresponds to your usage.

## 1 Applicable Product

| Product Type  | Model Marking | Product Code         |

|---------------|---------------|----------------------|

|               | MC-10287F1    | MC-10287F1-HN4-A     |

| R-IN32M3-EC   | MC-10287F1    | MC-10287F1-HN4-M1-A  |

| R-IN32WI3-EC  | MC-10287BF1   | MC-10287BF1-HN4-A    |

|               | MC-10207 BF 1 | MC-10287BF1-HN4-M1-A |

|               | D60510F1      | UPD60510F1-HN4-A     |

| R-IN32M3-CL   | DOUSTOFT      | UPD60510F1-HN4-M1-A  |

| R-INSZIVIS-CL | D60510BF1     | UPD60510BF1-HN4-A    |

|               | DOUSTUBET     | UPD60510BF1-HN4-M1-A |

### 2 Documentation Updates

|    |                                                                      |                              | Contents                 |                            |  |

|----|----------------------------------------------------------------------|------------------------------|--------------------------|----------------------------|--|

| No | Applicable Item (Rev.8.00 Section)                                   | Applicable<br>Page (Rev8.00) | MC-10287F1<br>UPD60510F1 | MC-10287BF1<br>UPD60510BF1 |  |

| 1  | 1.1 Type Names of R-IN32M3-Series Products                           | p.1-1                        | Complement               | ÷                          |  |

| I  | 1.2 Base Addresses of the System Registers Area                      | p.1-1                        | Complement               | <del>(</del>               |  |

| 2  | 2.2.2 Clock Control Registers (CLKGTD0, CLKGTD1)                     | p.2-5                        | Errors corrected         | <del>(</del>               |  |

| 3  | 2.3.1 Overview                                                       | p.2-6                        | Complement               | ÷                          |  |

|    | 2.3.2 (1) Reset by signal input from a pin                           | p.2-6                        | Errors corrected         | ÷                          |  |

| 4  | 2.3.2 (3) Reset by using software                                    | p.2-6                        | Errors corrected         | ÷                          |  |

|    | 2.3.2 (5) Reset output (RSTOUTZ output)                              | p.2-7                        | Complement               | <del>(</del>               |  |

| 5  | 2.3.3 (1) System Reset Register (SYSRESET)                           | p.2-8                        | Errors corrected         | ÷                          |  |

| 6  | 2.3.4 Operations for Reset                                           | p.2-9                        | Complement               | <del>(</del>               |  |

| 7  | 4.1 Bus Occupancy by the Cortex-M3                                   | p.4-2                        | -                        | Functions newly added      |  |

| 8  | 8.3.1(1) Management registers                                        | p.8-3                        | -                        | Functions newl<br>added    |  |

| 9  | 8.3.2.4 Ethernet Switch 10-Mbps Half-Duplex Mode<br>Setting Register | p.8-9                        | -                        | Functions newl<br>added    |  |

| 10 | 8.4.2.4 Hub Receive Filtering                                        | p.8-73                       | Errors corrected         | ÷                          |  |

| 11 | 11. External MCU Interface                                           | p.11-1                       | Complement               | <del>(</del>               |  |

| 12 | 11.1 Memory MAP                                                      | p.11-3                       | Complement               | <del>(</del>               |  |

| 13 | 11.2.2(3) Synchronous Mode and Asynchronous Mode                     | p.11-7                       | Errors corrected         | ÷                          |  |

| 14 | 11.2.3 Basic Motion Timing of External MCU Interface                 | p.11-9 to 11-11              | Errors corrected         | ÷                          |  |

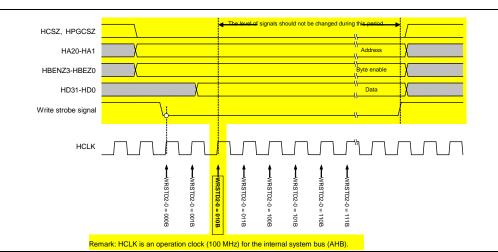

| 15 | 11.2.4(2) Timing adjustment (SRAM writing)                           | p.11-13                      | Errors corrected         | ÷                          |  |

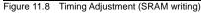

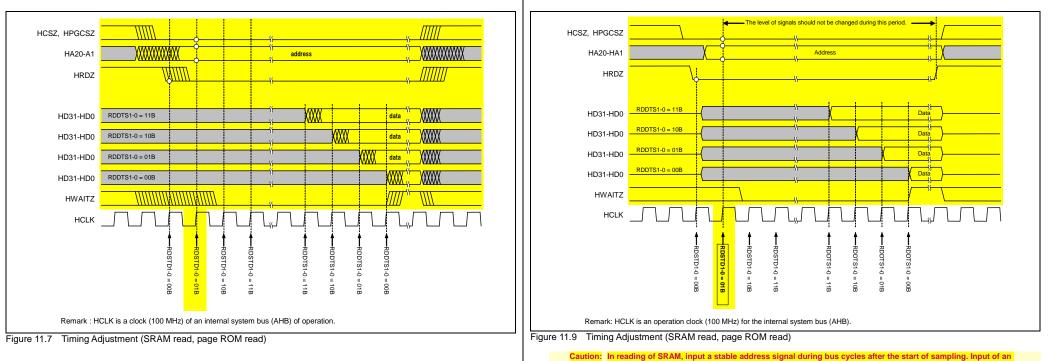

| 16 | 11.2.4(3) Timing adjustment<br>(SRAM read, page ROM read)            | p.11-14                      | Errors corrected         | ÷                          |  |

(- : Excluded,  $\leftarrow$  : same as on the left )

## RENESAS TECHNICAL UPDATE TN-RIN-A008A/E

|    |                                                                                              |                              |                          | (2/2)                      |  |  |

|----|----------------------------------------------------------------------------------------------|------------------------------|--------------------------|----------------------------|--|--|

|    |                                                                                              | Applicable<br>Page (Rev8.00) | Contents                 |                            |  |  |

| No | Applicable Item (Rev.8.00 Section)                                                           |                              | MC-10287F1<br>UPD60510F1 | MC-10287BF1<br>UPD60510BF1 |  |  |

| 17 | 14.1 R-IN32M3 TAUJ2 Features                                                                 | p.14-2                       | Complement               | <del>(</del>               |  |  |

| 18 | 14.1.1 Timer operation functions                                                             | p.14-3                       | Functions newly added    | ÷                          |  |  |

| 19 | 14.3.3(3) TAUJ2CMORm<br>- TAUJ2 channel mode OS register                                     | p.14-15 to 14-18             | Functions newly added    | ÷                          |  |  |

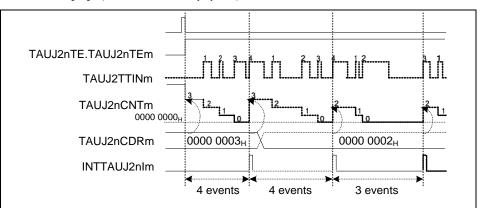

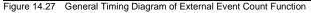

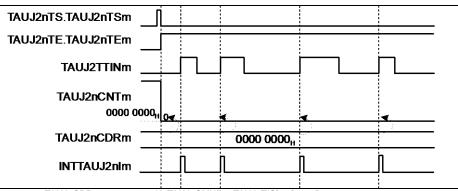

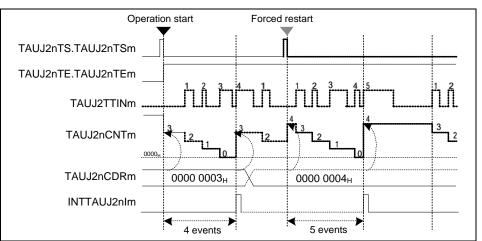

| 20 | 14.7.6 External Event Count Function                                                         | p.14-74 to 14-79             | Functions newly added    | ÷                          |  |  |

| 21 | 15.3.2(2) WDTA Mode Register (WDTAnMD)                                                       | p.15-4                       | Errors corrected         | <del>(</del>               |  |  |

| 22 | 17.1 Features of R-IN32M3 CSIH                                                               | p.17-2                       | Complement               | ÷                          |  |  |

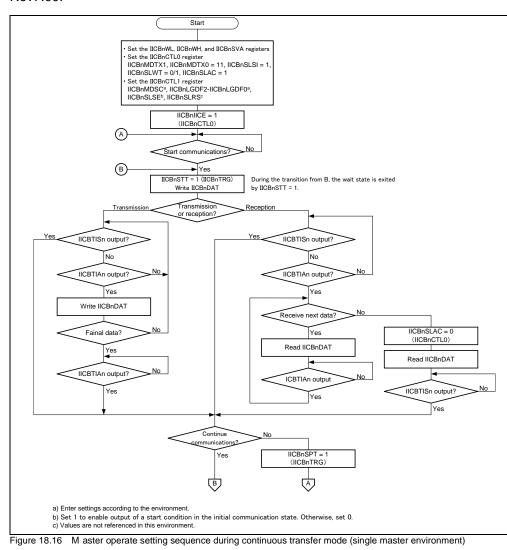

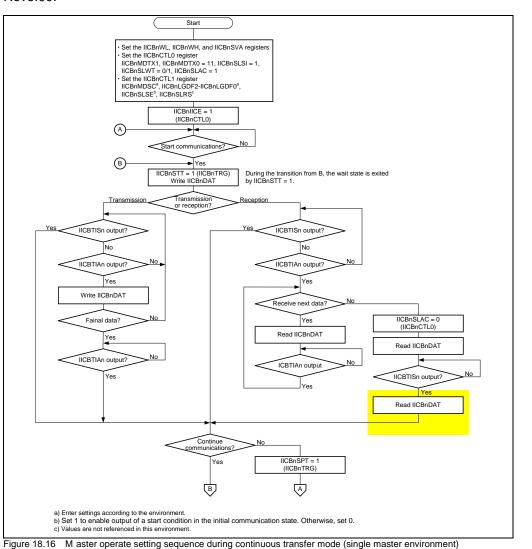

| 23 | 18.9.1(3) Master operate setting sequence during<br>continuous transfer mode *caution needed | p.18-120                     | Errors corrected         | ÷                          |  |  |

| 24 | 19.1 FCN Features of R-IN32-M3                                                               | p.19-2                       | Complement               | ÷                          |  |  |

| 25 | 19.13.2 Representative examples of baud rate settings<br>*caution needed                     | p.19-114                     | Errors corrected         | ÷                          |  |  |

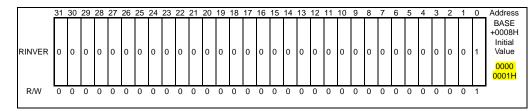

| 26 | 21.1 Registers                                                                               | p.21-2                       | -                        | Functions newly<br>added   |  |  |

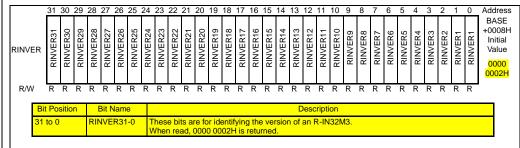

| 27 | 21.4 Version register (RINVER)                                                               | p.21-4                       | -                        | Functions newly<br>added   |  |  |

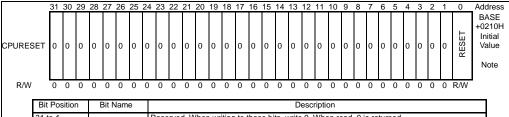

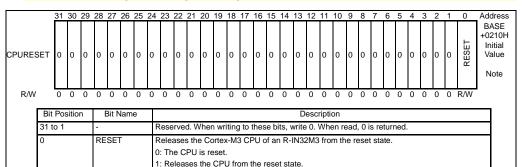

| 28 | 21.6 CPURESET register (CPURESET),                                                           | p.21-6                       | Complement               | <del>(</del>               |  |  |

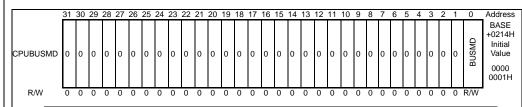

| 29 | 21.12 CPU Bus Operating Mode Register (CPUBUSMD)                                             | p.21-31                      | -                        | Functions newly<br>added   |  |  |

(- : Excluded,  $\leftarrow$  : same as on the left)

Incorrect and correct: highlighted in Yellow

## 1. <u>1. Introduction</u>

"1.1 Type names of R-IN32M3-Series Products", added.

## "1. Introduction", the second subsequent paragraphs moved and modified to "1.2 Base Addresses of the System Registers Area". (p.1-1)

Rev7.00:

1. Introduction

This document has indicated the built-in peripheral function carried in industrial Ethernet-work LSI "R-IN32M3" series.

The register addresses shown below are relative addresses from the base address.

When accessing these registers via the external microcontroller interface, the base address is D\_0000H. When accessing these registers from the CPU or DMA controller, the base address is 4001\_0000H.

- When accessing from the CPU or DMA controller

- BASE = 4001\_0000H

- When accessing via the external microcontroller interface  $\mathsf{BASE}=\mathsf{D}\_0000\mathsf{H}$

Rev8.00:

#### 1. Introduction

This document describes the internal peripheral modules of the R-IN32M3 series of industrial Ethernet network LSI chips.

#### 1.1 Type Names of R-IN32M3-Series Products

In the type names of R-IN32M3-series (R-IN32M3-EC and R-IN32M3-CL) products, those of the current products include "B" while those of the old products do not.

Unless specially stated otherwise, the products mentioned in this manual are the current products.

#### Table 1.1 Type Names of R-IN32M3-Series Products

| Product Name | Designation      | Type Name                                 | Features                                                |

|--------------|------------------|-------------------------------------------|---------------------------------------------------------|

| R-IN32M3-EC  | Current products | MC-10287BF1-HN4-A<br>MC-10287BF1-HN4-M1-A | EtherCAT slave controller supported version             |

|              | Old products     | MC-10287F1-HN4-A<br>MC-10287F1-HN4-M1-A   |                                                         |

| R-IN32M3-CL  | Current products | UPD60510BF1-HN4-A<br>UPD60510BF1-HN4-M1-A | CC-Link IE intelligent device station supported version |

|              | Old products     | UPD60510F1-HN4-A<br>UPD60510F1-HN4-M1-A   |                                                         |

Caution: In the current products, the ETHSW10HDEN and CPUBUSMD registers have been newly added and the initial value of the RINVER register has been changed from that in the old products. For details, see the description of the following sections. 8.3.2.4, Ethernet Switch 10-Mbps Half-Duplex Mode Setting Register 21.4, Version register (RINVER) 21.12, CPU Bus Operating Mode Register (CPUBUSMD)

#### 1.2 Base Addresses of the System Registers Area

This document has indicated the built-in peripheral function carried in industrial Ethernet-work LSI "R-IN32M3" series. The register addresses shown below are relative addresses from the base address.

When accessing these registers via the external microcontroller interface, the base address is D\_0000H. When accessing these registers from the CPU or DMA controller, the base address is 4001\_0000H.

- When accessing from the CPU or DMA controller

BASE = 4001\_0000H

- When accessing via the external microcontroller interface

BASE = D\_0000H

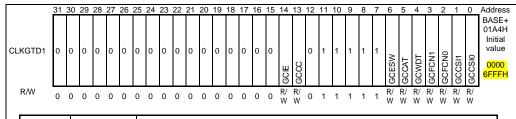

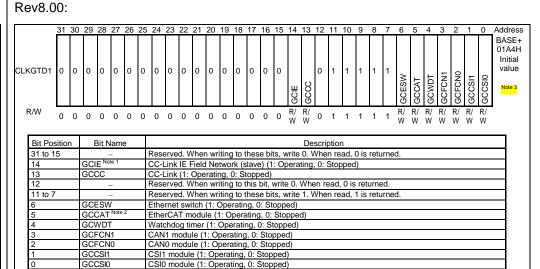

## 2. 2.2.2 Clock Control Registers (CLKGTD0, CLKGTD1)

"Initial value" of CLKGTD1 register, modified. Note3 added. (p.2-5) Rev7.00:

| Bit Position | Bit Name     | Description                                                              |  |

|--------------|--------------|--------------------------------------------------------------------------|--|

| 31 to 15     | -            | Reserved. When writing to these bits, write 0. When read, 0 is returned. |  |

| 14           | GCIE Note 1  | CC-Link IE Field Network (slave) (1: Operating, 0: Stopped)              |  |

| 13           | GCCC         | CC-Link (1: Operating, 0: Stopped)                                       |  |

| 12           | -            | Reserved. When writing to this bit, write 0. When read, 0 is returned.   |  |

| 11 to 7      | -            | Reserved. When writing to these bits, write 1. When read, 1 is returned. |  |

| 6            | GCESW        | Ethernet switch (1: Operating, 0: Stopped)                               |  |

| 5            | GCCAT Note 2 | EtherCAT module (1: Operating, 0: Stopped)                               |  |

| 4            | GCWDT        | Watchdog timer (1: Operating, 0: Stopped)                                |  |

| 3            | GCFCN1       | CAN1 module (1: Operating, 0: Stopped)                                   |  |

| 2            | GCFCN0       | CAN0 module (1: Operating, 0: Stopped)                                   |  |

| 1            | GCCSI1       | CSI1 module (1: Operating, 0: Stopped)                                   |  |

| 0            | GCCSI0       | CSI0 module (1: Operating, 0: Stopped)                                   |  |

- Notes1. This function is only available in the R-IN32M3-CL. When using a product other than the R-IN32M3-CL, write 0 to this bit. When read, 0 is returned.

- 2. This function is only available in the R-IN32M3-EC. When using a product other than the R-IN32M3-EC, write 0 to this bit. When read, 0 is returned.

- Cautions1. Once the clock supply is stopped by using the CLKGTD register, it cannot be resumed To supply the clock signal again, reset the system.

- 2. Access to stopped modules is prohibited. Operation is not guaranteed if an attempt is made to access these modules.

Notes1. This function is only available in the R-IN32M3-CL. When using a product other than the R-IN32M3-CL, write 0 to this bit. When read, 0 is returned.

- 2. This function is only available in the R-IN32M3-EC. When using a product other than the R-IN32M3-EC, write 0 to this bit. When read, 0 is returned.

- 3. The initial value depends on the product you are using.

- R-IN32M3-CL: 0000 6FDFH R-IN32M3-EC: 0000 2FFFH

Cautions1. Once the clock supply is stopped by using the CLKGTD register, it cannot be resumed To supply the clock signal again, reset the system.

2. Access to stopped modules is prohibited. Operation is not guaranteed if an attempt is made to access these modules.

## 3. 2.3.1 Overview

## Note added to HOTRESETZ. (p.2-6)

Rev7.00:

#### 2.3.1 Overview

- Reset input via the RESETZ pin

- Power-on reset (including initialization of R-IN32M3 internal RAM) input via the PONRZ pin

- Reset input via the HOTRESETZ pin (available only in R-IN32M3-CL)

- Noise elimination for external reset pins based on analog delay (Applicable pins: RESETZ, PONRZ, HOTRESETZ Note, and TRSTZ)

- Reset control by using software

Reset control by using watchdog timer (WDT)

- Reset output

Note: The HOTRESETZ pin is only available in the R-IN32M3-CL.

## Rev8.00:

#### 2.3.1 Overview

- Reset by signal input from the RESETZ pin

- Power-on reset by signal input from the PONRZ pin (including initialization of internal RAM of the R-IN32M3)

- Reset by signal input from the HOTRESETZ pin Note

- Noise elimination for external reset pins based on analog delay (Applicable pins: RESETZ, PONRZ, HOTRESETZ Note, and TRSTZ)

- Reset control by using software

- Reset control by using watchdog timer (WDT)

- Reset output

Note: The HOTRESETZ pin is only available in the R-IN32M3-CL.

#### 4. 2.3.2 Features

"(1) Reset input via a pin", part of description modified.

"(3) Reset by using software", RESETZ pin corrected to HOTRESETZ pin.

## "Table 2.1 Reset Source and Targets to be Reset", Note2 added to CATRESET register. (p.2-6 to 2-7)

Rev7.00:

#### 2.3.2 Features

(1) Reset input via a pin

When the reset signal PONRZ, RESETZ, or HOTRESETZ<sup>Note</sup> is input, the CPU core and on-chip peripheral functions are initialized. Note that inputting HOTRESETZ <sup>Note</sup> does not reset the internal PLL.

The low-level width of each reset signal must be at least 1 ms. However, in order for the external oscillator clock (25 MHz) to stabilize, the oscillation stabilization time must be included in the low level width of each reset pin. Also, at least two cycles of the external oscillator clock (25 MHz) must be supplied between when the low level of each reset pin is input and when the reset ends.

TRSTZ is only connected to the Cortex-M3 debugging unit. When resetting the CPU core and on-chip peripheral functions from the in-circuit emulator (ICE), connect the target reset signal (nTRST) input via the ICE connector to the RESETZ pin by using logic such as wired OR. In case of ICE half pitch connector, TRSTZ should be open. For details, see 22."Debugging".

#### Note: The HOTRESETZ pin is only available in the R-IN32M3-CL.

#### (2) Noise elimination for input reset signals

Noise at the external reset pins PONRZ, RESETZ, HOTRESETZ Note, and TRSTZ is eliminated based on analog delay. Signals shorter than 100 ns can be eliminated as noise.

#### Note: The HOTRESETZ pin is only available in the R-IN32M3-CL.

#### (3) Reset by using software

The R-IN32M3 can be reset by using the system reset register (SYSRESET). This reset is equivalent to a reset executed by inputting a signal to the **RESETZ** pin. With this method, the internal RAM is not reset.

#### (4) Reset by using the watchdog timer (WDT)

When a reset request is generated by the on-chip watchdog timer (WDT), the CPU core and on-chip peripheral functions are initialized. This reset is equivalent to a reset executed by inputting a signal to the RESETZ pin. With this method, the internal RAM is not reset.

#### (5) Reset output (RSTOUTZ output)

When a reset is generated in the R-IN32M3, a low-level signal is output from the RSTOUTZ pin. This reset can be used as a general reset for external devices.

#### Table 2.1 Reset Source and Targets to be Reset

|                      |                                           | Target to be Reset |                                                      |         |          |                            |                                 |

|----------------------|-------------------------------------------|--------------------|------------------------------------------------------|---------|----------|----------------------------|---------------------------------|

| Reset Source         | Instruction RAM<br>Data RAM<br>Buffer RAM | PLL                | CC-Link IE<br>Field Network Note 1<br>Power on reset | CC-Link | EtherCAT | CPU's<br>debugging<br>unit | Other<br>peripheral<br>circuits |

| PONRZ pin            | 0                                         | 0                  | 0                                                    | 0       | 0        | -                          | 0                               |

| RESETZ pin           | -                                         | 0                  | 0                                                    | 0       | 0        | -                          | 0                               |

| HOTRESETZ pin Note 1 | -                                         | -                  | -                                                    | 0       | 0        | -                          | 0                               |

| TRSTZ pin            | -                                         | -                  | -                                                    | -       | -        | 0                          | -                               |

| Watchdog timer       | -                                         | -                  | -                                                    | 0       | 0        | -                          | 0                               |

| SYSRESET register    | -                                         | -                  | -                                                    | 0       | 0        | -                          | 0                               |

| CPU reset            | -                                         | -                  | -                                                    | 0       | 0        | -                          | 0                               |

| CCRES register       | -                                         | -                  | -                                                    | 0       | -        | -                          | -                               |

| CATRESET register    | -                                         | -                  | -                                                    | -       | 0        | -                          | -                               |

Notes 1 Only the R-IN32M3-CL has. 2 Only the R-IN32M3-EC has. Rev8.00:

#### 2.3.2 Features

(1) Reset input via a pin

When the reset signal PONRZ, RESETZ, or HOTRESETZ <sup>Note</sup> is input, the CPU core and internal peripheral modules are initialized. Note that the input of HOTRESETZ <sup>Note</sup> does not reset the internal PLL.

The width at low level of each reset signal must be at least 1 us. However, in order for oscillation to produce the external oscillator clock (25 MHz) to become stable, the oscillation stabilization time must be included in the width at low level for the signal on each reset pin.

TRSTZ is only connected to the Cortex-M3 debugging unit. When resetting the CPU core and internal peripheral modules from the in-circuit emulator (ICE), connect the target reset signal (nTRST) input via the ICE connector to the RESETZ pin by using logic such as wired OR. When using a half pitch connector as the ICE connector, it is recommended that TRSTZ should be open. For an example of the connection, see section 22 Debugging.

#### (2) Noise elimination for input reset signals

Noise at the external reset pins PONRZ, RESETZ, HOTRESETZ Note, and TRSTZ is eliminated based on analog delay. Signals shorter than 100 ns can be eliminated as noise.

#### (3) Reset by using software

The R-IN32M3 can be reset by using the system reset register (SYSRESET). This reset is equivalent to a reset executed by the input of a signal to the HOTRESETZ pin. The internal RAM is not initialized.

#### (4) Reset by using the watchdog timer (WDT)

When a reset request is generated by the on-chip watchdog timer (WDT), the CPU core and internal peripheral modules are initialized. This reset is equivalent to a reset executed by the input of a signal to the RESETZ pin. The internal RAM is not initialized.

Note: The HOTRESETZ pin is only available in the R-IN32M3-CL.

#### (5) Reset output (RSTOUTZ output)

When a reset is generated in the R-IN32M3, a low-level signal is output from the RSTOUTZ pin. This reset can be used as a general reset for external devices.

#### Table 2.1 Reset Source and Targets to be Reset

|                          |                             |     | Targe                              | t to be Reset |          |                    |                     |

|--------------------------|-----------------------------|-----|------------------------------------|---------------|----------|--------------------|---------------------|

|                          | Instruction RAM<br>Data RAM |     | CC-Link IE<br>Field Network Note 1 |               | EtherCAT | CPU's<br>debugging | Other<br>peripheral |

| Reset Source             | Buffer RAM                  | PLL | Power on reset                     | CC-Link       | Note 2   | unit               | circuits            |

| PONRZ pin                | ✓                           | ~   | √                                  | ✓             | ~        | -                  | ~                   |

| RESETZ pin               | -                           | ~   | √                                  | ✓             | ~        | -                  | ~                   |

| HOTRESETZ pin Note 1     | -                           | •   | -                                  | ~             | ~        | -                  | ~                   |

| TRSTZ pin                | -                           | •   | -                                  | -             | -        | ~                  | -                   |

| Watchdog timer           | -                           | -   | -                                  | ~             | ~        | -                  | ~                   |

| SYSRESET register        | -                           | -   | -                                  | ✓             | ~        | -                  | ~                   |

| CPU reset                | -                           | •   | -                                  | ~             | ~        | -                  | ~                   |

| CCRES register           | -                           | -   | -                                  | ~             | -        | -                  | -                   |

| CATRESET register Note 2 | -                           | -   | -                                  | -             | ~        | -                  | -                   |

#### Notes 1 This is only provided in the R-IN32M3-CL. 2 This is only provided in the R-IN32M3-EC.

## 5. <u>2.3.3(1)</u> System reset register (SYSRESET)

| HOTRESETZ input pin in the text corrected to HOTRESETZ input pin. (p.2-8)                                                                                                                                                                                           |                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev7.00:                                                                                                                                                                                                                                                            | Rev8.00:                                                                                                                                                                                                                               |

| (1) System reset register (SYSRESET)<br>R-IN32M3 is reset (an equivalent for a <u>RESETZ</u> input terminal). The register of the object of a PONRZ terminal is not reset. Reset release of this register is performed when carrying out reset release of R-IN32M3. | (1) System Reset Register (SYSRESET)<br>This register resets the R-IN32M3 (equivalent to the HOTRESETZ input pin). The register for the PONRZ pin is not reset. This register is used<br>to release the R-IN32M3 from the reset state. |

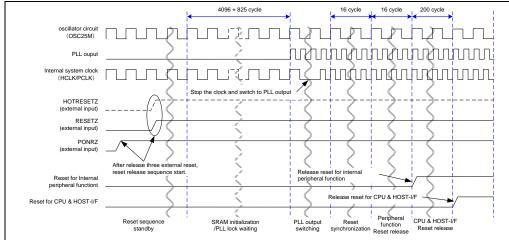

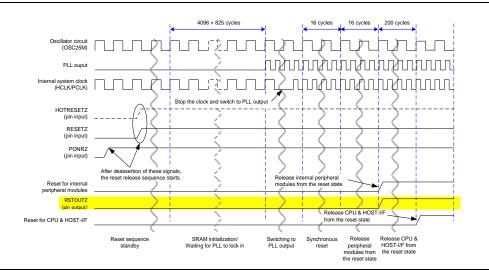

## 6. 2.3.4 Operations for Reset

"Figure 2.2 Timing of Reset at Power On", RSTOUTZ waveform added. (p.2-9) Rev7.00:

#### 2.3.4 Reset behavior

Below charts shows reset behavior at power on and system reset of R-IN32M3 series.

Figure 2.2 Timing of Reset at Power On

Rev8.00:

#### 2.3.4 Operations for Reset

The charts below show the timing of the reset at power on and when a system reset is issued for the R-IN32M3 series.

Figure 2.2 Timing of Reset at Power On

7. <u>4.1 Bus Occupancy by the Cortex-M3</u> "4.1 Bus Occupancy by the Cortex-M3", added. (p.4-2) Rev7.00:

No descriptions.

## Rev8.00:

4.1 Bus Occupancy by the Cortex-M3

By default, when the Cortex-M3 of an R-IN32M3-series device successively copies data within a given memory, it proceeds with burst transfer of the required length and occupies the bus over that period, making other masters wait for access to the memory. The period over which another master must wait for access thus depends on the period of continuous access by the Cortex-M3.

To reduce the period over which other masters are kept waiting for access, set the CPU bus operation mode register (CPUBUSMD) to change the form of transfer by the Cortex-M3 to single transfer. This allows access by other masters even during continuous access by the Cortex-M3.

8. <u>8.3.1(1) Management registers</u> "(1) Management registers", ETHSW10HDEN register added. (p.8-3) Rev7.00:

#### (1) Management registers

| Register name                                   | Symbol    | Address      |

|-------------------------------------------------|-----------|--------------|

| Ethernet PHY LINK mode resister                 | ETHPHYLNK | BASE + 0614H |

| Ethernet switch management TAG control register | ETHSWMTC  | BASE + 0680H |

| Ethernet switch operating mode setting register | ETHSWMD   | BASE + 0684H |

Rev8.00:

(1) Management registers

| Register name                                             | Symbol      | Address      |

|-----------------------------------------------------------|-------------|--------------|

| Ethernet PHY LINK mode resister                           | ETHPHYLNK   | BASE + 0614H |

| Ethernet switch management TAG control register           | ETHSWMTC    | BASE + 0680H |

| Ethernet switch operating mode setting register           | ETHSWMD     | BASE + 0684H |

| Ethernet switch 10-Mbps half-duplex mode setting register | ETHSW10HDEN | BASE + 060C  |

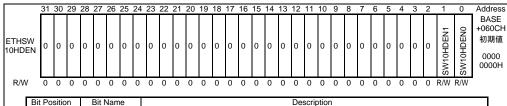

#### 9. 8.3.2.4 Ethernet Switch 10-Mbps Half-Duplex Mode Setting Register

"8.3.2.4 Ethernet Switch 10-Mbps Half-Duplex Mode Setting Register", added. (p.8-9)

Rev7.00:

No descriptions.

Rev8.00:

•

8.3.2.4 Ethernet Switch 10-Mbps Half-Duplex Mode Setting Register

This register is for disabling the looping back of received frames by the Ethernet PHY layer during transmission when the Ethernet switch is used for 10-Mbps half-duplex communications.

The Ethernet PHY layer of the R-IN32M3-EC loops back transmitted data to received data in 10-Mbps half-duplex transfer. If Ethernet switching by this LSI chip is used to set up a loopback between two ports, transfer is mutually repeated between these ports, and Ethernet transfer does not proceed successfully.

Access This register can be read and written in 32- or 16-bit units.

Cautions 1. This register is only writable after protection has been released by a special sequence of writing to the system protection command register (SYSPCMD). For how to release protection, see the description of the system protection command register (SYSPCMD). No special sequence is required for reading the register.

Only select disabling of received frames while the Ethernet PHY layer is linked in half-duplex communications at 10 Mbps. If this is done in another linked state, some correct received frames may also be disabled.

| Bit Position | Description |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31 to 2 –    |             | Reserved. When writing to these bits, write 0. If read, 0 is returned.                                                                                                                                                                                                                                                                                       |  |  |  |

| 1            | SW10HDEN1   | <ul> <li>Disables looping back of received frames during transmission from Ethernet port 1.</li> <li>0: Disabling is not selected (this should be set when operation is other than for 10-Mbps half-duplex communications).</li> <li>1: Disabling is selected (this should only be set when operation is for 10-Mbps half-duplex communications).</li> </ul> |  |  |  |

| 0            | SW10HDEN0   | <ul> <li>Disables looping back of received frames during transmission from Ethernet port 0.</li> <li>0: Disabling is not selected (this should be set when operation is other than for 10-Mbps half-duplex communications).</li> <li>1: Disabling is selected (this should only be set when operation is for 10-Mbps half-duplex communications).</li> </ul> |  |  |  |

Notes 1. This register is only supported by the R-IN32M3-EC.

2. The old products do not support this register.

For details of the old products, see section 1.1, Type Names of R-IN32M3-Series Products <R>.

10. <u>8.4.2.4 Hub Receive Filtering</u> "Table 8.7 Typical HUB MAC Filter Setup", entries under "Notes", corrected. (p.8-73) Rev7.00:

#### Table 8.7 Typical HUB MAC Filter Setup

Rev8.00:

| Table 6.7 Typical TIOB MAC                    |      | P             |                                                                                                                                                      |

|-----------------------------------------------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAC Address                                   | Mask | Force Forward | Notes                                                                                                                                                |

| 01-80-c2-00-00-00                             | 0xC0 | 0             | Filters all frames in range 01-80-c2-00-00-{003F} The register settings for MAClo/hi would be:                                                       |

|                                               |      |               | HUB_FLT_MACnlo= 0x00C28001<br>HUB_FLT_MACnhi= 0x00C00000                                                                                             |

| 01-1b-19-00-00-00                             | 0xFF | 0             | Filters only this address (PTPv2)                                                                                                                    |

| 01-00-5e-00-01-80                             | 0xF8 | 0             | Filters 01-00-5e-00-01-{8087}(224.0.1.{128135})                                                                                                      |

| 01-00-5e-00-00-00                             | 0xFC | 0             | Filters 01-00-5e-00-00-{0003} (224.0.0.{03})                                                                                                         |

| <local address="" node="" unicast=""></local> | 0xFF | 0             | Should be entered to avoid unnecessary forwarding of frames that are directed to the node only.                                                      |

| 01-21-6C-00-00-01                             | 0xFF | 1             | Should be force forwarded through the HUB. The register settings for<br>MAClo/hi would be:<br>HUB_FLT_MACnd= 0x006C2101<br>HUB_FLT_MACnd= 0x01FF0100 |

| MAC Address                                   | Mask | Force Forward | Notes                                                                                                                                                         |

|-----------------------------------------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01-80-c2-00-00-00                             | 0xC0 | 0             | Filters all frames in range 01-80-c2-00-00-{003F} The register settings<br>for MAClo/hi would be:<br>HUB_FLT_MACnol= 0x00C28001<br>HUB_FLT_MACnhi= 0x00C00000 |

| 01-1b-19-00-00-00                             | 0xFF | 0             | Filters only this address (PTPv2)                                                                                                                             |

| 01-00-5e-00-01-80                             | 0xF8 | 0             | Filters 01-00-5e-00-01-{8087}(224.0.1.{128135})                                                                                                               |

| 01-00-5e-00-00-00                             | 0xFC | 0             | Filters 01-00-5e-00-00-{0003} (224.0.0.{03})                                                                                                                  |

| <local address="" node="" unicast=""></local> | 0xFF | 0             | Should be entered to avoid unnecessary forwarding of frames that are<br>directed to the node only.                                                            |

| 01-21-6C-00-00-01                             | 0xFF | 1             | Should be force forwarded through the HUB. The register settings for<br>MACIo/hi would be:<br>HUB_FLT_MAC610= 0x006C2101<br>HUB_FLT_MAC611= 0x01FF0100        |

#### 11. 11. External MCU Interface

## "Table 11.1 Mode of the External MCU Interface Selected by the Level on the Operating Mode Setting Pin", added (p.11-1)

Rev7.00:

#### 11. External MCU Interface

In order to use the internal resource of the external host MPU to an R-IN32M3, the external MCU interface is established.

The external MCU interface is interface to connect external MPU. External MCU I/F's signal is assigned same ports to both use with Asynchronous SRAM MEMC and synchronous burst access MEMC, and can be used as external MCU interface in case of setting MEMIFSEL to High level. Please set MEMIFSEL pin level until to release reset from the later one of PONRZ or RESETZ after power supply. The dynamic switching isn't supported.

When using an external MCU interface, the boot of an R-IN32M3 can use external MCU boot or serial flash ROM boot. However, an external memory accessing function (external ROM/SRAM) cannot be used.

The external MCU interface is equivalent to the asynchronous SRAM interface and the synchronous SRAM interface. When the level of a HIFSYNC pin is high-level, it becomes a synchronous SRAM interface, and when HIFSYNC is a low level, it becomes an asynchronous SRAM interface.

Moreover, the external MCU interface supports the synchronous SRAM type transmission of a clock synchronizer type so that mass data can be accessed at high speed. MEMIFSEL pin and MEMCSEL pin can be used by making it high-level.

#### Rev8.00:

#### 11. External MCU Interface

In order to use the internal resource of the external host MPU to an R-IN32M3, the external MCU interface is established.

Table 11.1 Mode of the External MCU Interface Selected by the Level on the Operating Mode Setting Pin

The external MCU interface is interface to connect external MPU. External MCU I/F's signal is assigned same ports to both use with Asynchronous SRAM MEMC and synchronous burst access MEMC, and can be used as external MCU interface in case of setting MEMIFSEL to High level. Please set MEMIFSEL pin level until to release reset from the later one of PONRZ or RESETZ after power supply. The dynamic switching isn't supported.

When using an external MCU interface, the boot of an R-IN32M3 can use external MCU boot or serial flash ROM boot. However, an external memory accessing function (external ROM/SRAM) cannot be used.

The external MCU interface is equivalent to the asynchronous SRAM interface and the synchronous SRAM interface. When the level of a HIFSYNC pin is high-level, it becomes a synchronous SRAM interface, and when HIFSYNC is a low level, it becomes an asynchronous SRAM interface.

Moreover, the external MCU interface supports the synchronous SRAM type transmission of a clock synchronizer type so that mass data can be accessed at high speed. MEMIFSEL pin and MEMCSEL pin can be used by making it high-level.

| MEMIFSEL | MEMCSEL | HIFSYNC | ADMUXMODE | Function                                                                                                                  |

|----------|---------|---------|-----------|---------------------------------------------------------------------------------------------------------------------------|

| Low      | —       | -       | -         | Not accessible from the external MCU (operating mode of the<br>external memory interface)                                 |

| High     | Low     | Low     | Low       | Asynchronous SRAM interface mode is entered.<br>Connection of the bus clock signal to HBUSCLK is not required.            |

|          |         |         | High      | Setting prohibited                                                                                                        |

|          |         | High    | Low       | Synchronous SRAM interface mode is entered.<br>Connection of the bus clock signal to HBUSCLK is required. <sup>Note</sup> |

|          |         |         | High      | Setting prohibited                                                                                                        |

|          | High    | Low     | Low       | Setting prohibited                                                                                                        |

|          |         |         | High      | Setting prohibited                                                                                                        |

|          |         | High    | Low       | Setting prohibited                                                                                                        |

|          |         |         | High      | Synchronous SRAM type transfer mode is entered.                                                                           |

Note: For access to the CC-Link IE field, synchronous SRAM interface mode must be set (MEMIFSEL = high, MEMCSEL = low, HIFSYNC = high). The CC-Link IE field is only included in the R-IN32M3-CL.

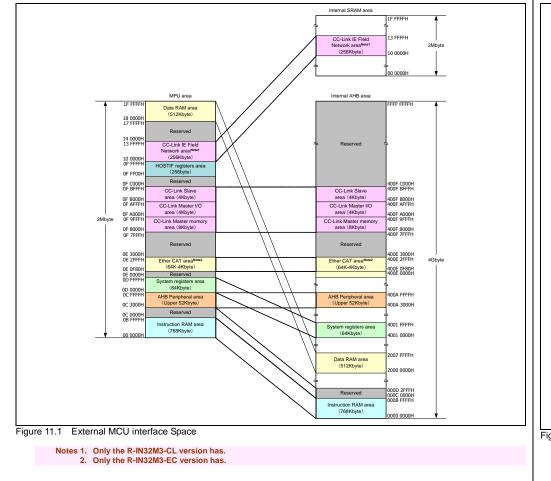

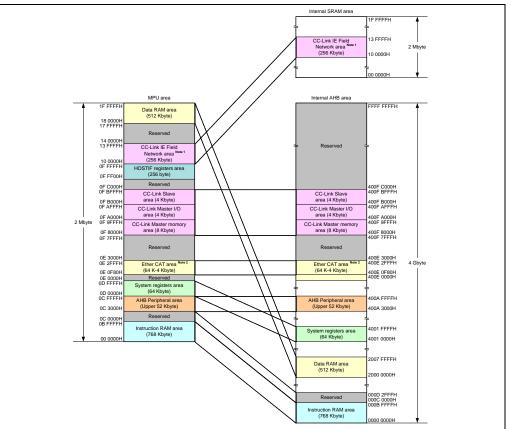

## 12. <u>11.1 Memory MAP</u>

"Figure 11.1 External MCU interface Space", Note3 added. (p.11-3) Rev7.00:

## 11.1 Memory MAP

2M byte area is prepared as an external microcomputer interface.

Rev8.00:

## 11.1 Memory MAP

A 2 Mbyte space is provided as the external MCU interface.

Figure 11.1 External MCU interface Space

Notes 1. This is only provided in the R-IN32M3-CL.

- 2. This is only provided in the R-IN32M3-EC.

- 3. The upper 52 Kbytes of the AHB peripheral registers area covers the range from the GPIO area to the

- synchronous burst memory controller control registers. For details, see the memory map of the R-IN32M3 Series User's Manual.

## 13. 11.2.2(3) Synchronous Mode and Asynchronous Mode

"Table11.4 Synchronous relation of an external MCU interface", changed. (p.11-7)

Rev7.00:

Table11.4 Synchronous relation of an external MCU interface

|                               |        | HIFSYNC (Synchronor  | us Relation Selection) |

|-------------------------------|--------|----------------------|------------------------|

| Signal Name                   | I/O    | H (Synchronous Mode) | L (Asynchronous Mode)  |

| HCSZ                          | Input  | HBUSCLK synchronous  | Asynchronous           |

| HPGCSZ                        | Input  | HBUSCLK synchronous  | Asynchronous           |

| HA20-HA1                      | Input  | HBUSCLK synchronous  | Asynchronous           |

| HRDZ                          | Input  | HBUSCLK synchronous  | Asynchronous           |

| HWRSTBZ                       | Input  | HBUSCLK synchronous  | Asynchronous           |

| HWRZ3-HWRZ0,<br>HBENZ3-HBENZ0 | Input  | HBUSCLK synchronous  | Asynchronous           |

| HD31-HD0 (input)              | Input  | HBUSCLK synchronous  | Asynchronous           |

| HD31-HD0 (output)             | Output | Asynchronous         | Asynchronous           |

| HWAITZ                        | Output | HBUSCLK synchronous  | Asynchronous           |

| HERROUTZ                      | Output | Asynchronous         |                        |

Rev8.00:

Table11.4 Synchronous relation of an external MCU interface

|                               |        | HIFSYNC (Synchronous Relation Selection) |              |                      |  |  |  |  |  |  |

|-------------------------------|--------|------------------------------------------|--------------|----------------------|--|--|--|--|--|--|

|                               |        | H (Synchronou                            |              |                      |  |  |  |  |  |  |

| Signal Name                   | I/O    | Write                                    | Read         | L (Asynchronous Mode |  |  |  |  |  |  |

| HCSZ                          | Input  | HBUSCLK synchronous                      | Asynchronous | Asynchronous         |  |  |  |  |  |  |

| HPGCSZ                        | Input  | HBUSCLK synchronous                      | Asynchronous | Asynchronous         |  |  |  |  |  |  |

| HA20-HA1                      | Input  | HBUSCLK synchronous                      | Asynchronous | Asynchronous         |  |  |  |  |  |  |

| HRDZ                          | Input  | —                                        | Asynchronous | Asynchronous         |  |  |  |  |  |  |

| HWRSTBZ                       | Input  | HBUSCLK synchronous                      | —            | Asynchronous         |  |  |  |  |  |  |

| HWRZ3-HWRZ0,<br>HBENZ3-HBENZ0 | Input  | HBUSCLK synchronous                      | -            | Asynchronous         |  |  |  |  |  |  |

| HD31-HD0 (input)              | Input  | HBUSCLK synchronous                      | —            | Asynchronous         |  |  |  |  |  |  |

| HD31-HD0 (output)             | Output | —                                        | Asynchronous | Asynchronous         |  |  |  |  |  |  |

| HWAITZ                        | Output | HBUSCLK synchronous                      |              | Asynchronous         |  |  |  |  |  |  |

| HERROUTZ                      | Output | Asynchronous                             |              |                      |  |  |  |  |  |  |

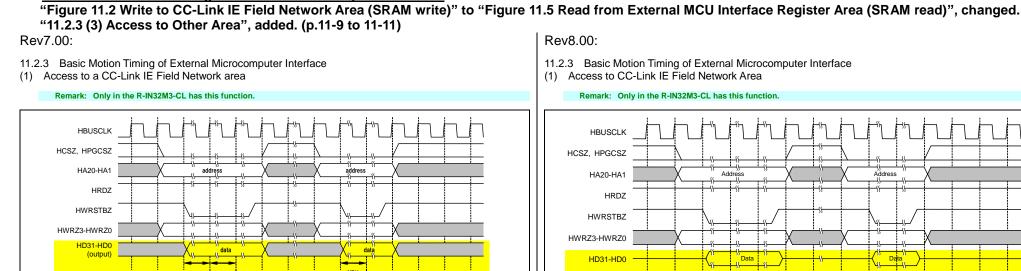

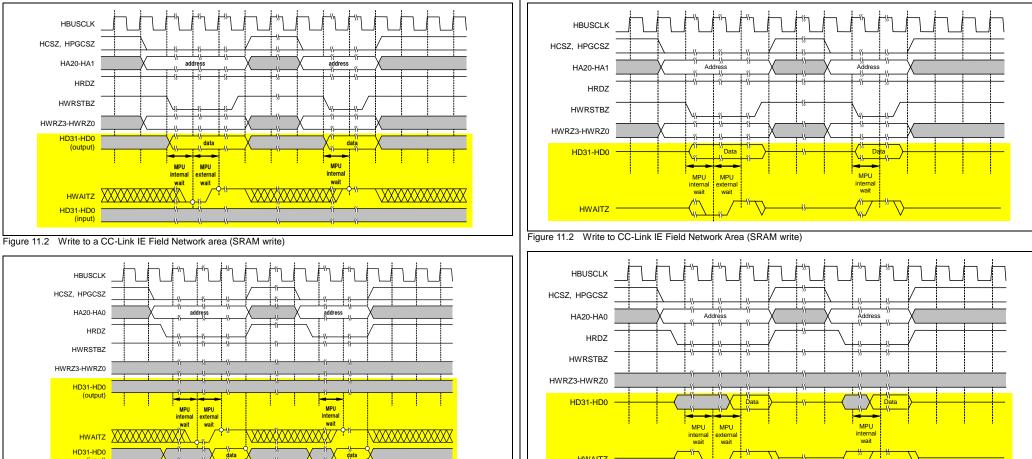

14. 11.2.3 Basic Motion Timing of External Microcomputer Interface

11.2.3 Basic Motion Timing of External Microcomputer Interface

(1) Access to CC-Link IE Field Network Area

Remark: Only in the R-IN32M3-CL has this function.

Figure 11.3 Read from CC-Link IE Field Network Area (SRAM read)

HWAITZ

Figure 11.3 Read from CC-Link IE Field Network area (SRAM read)

(input)

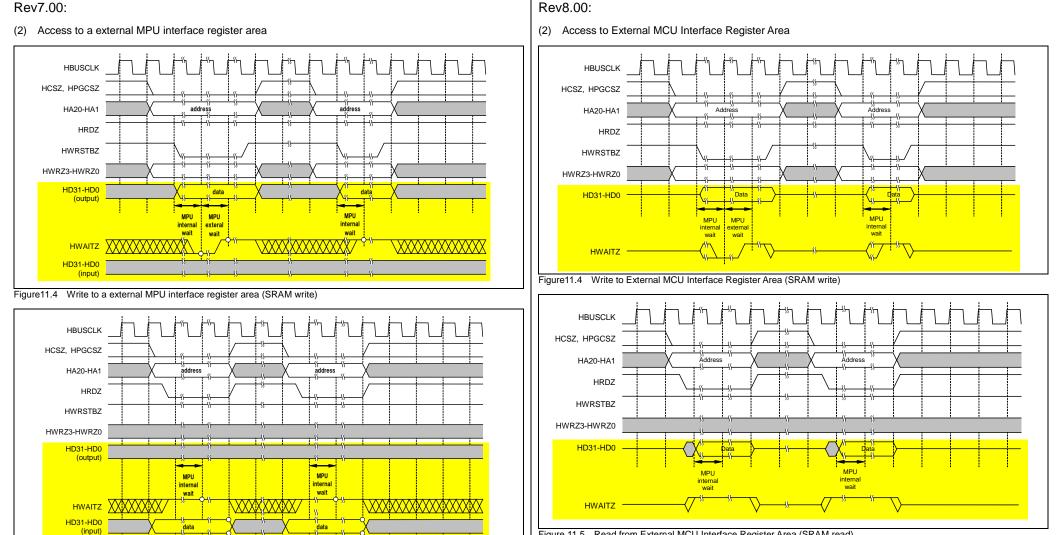

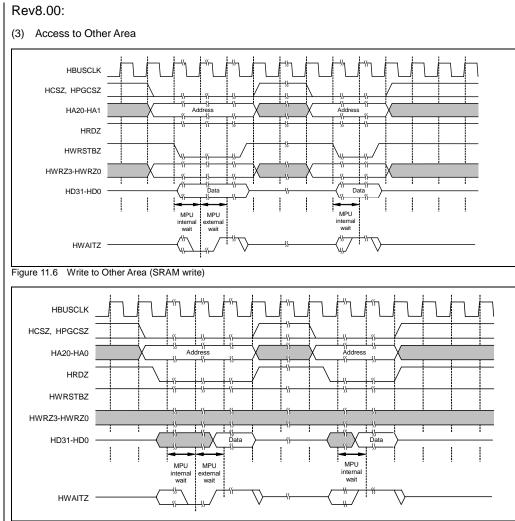

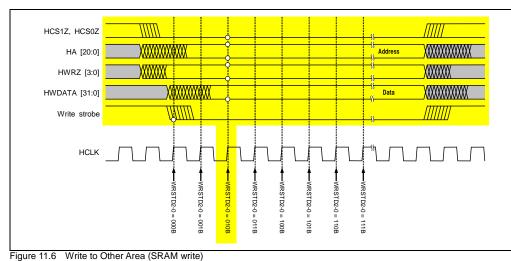

## 14. 11.2.3 Basic Motion Timing of External Microcomputer Interface

"Figure 11.2 Write to CC-Link IE Field Network Area (SRAM write)" to "Figure 11.5 Read from External MCU Interface Register Area (SRAM read)", changed. "11.2.3 (3) Access to Other Area", added. (p.11-9 to 11-11) continued

Figure 11.5 Read from External MCU Interface Register Area (SRAM read)

Figure 11.5 Read from external MPU interface register area (SRAM read)

## 14. 11.2.3 Basic Motion Timing of External Microcomputer Interface

"Figure 11.2 Write to CC-Link IE Field Network Area (SRAM write)" to "Figure 11.5 Read from External MCU Interface Register Area (SRAM read)", changed. "11.2.3 (3) Access to Other Area", added. (p.11-9 to 11-11) continued

Rev7.00:

No descriptions.

Figure 11.7 Read from Other Area (SRAM read)

Rev8.00:

## 15. 11.2.4(2) Timing adjustment (SRAM writing)

"Figure 11.8 Timing Adjustment (SRAM writing)", changed. (p.11-13) Rev7.00:

(c) 2016. Renesas Electronics Corporation. All rights reserved.

## 16. 11.2.4(3) Timing adjustment (SRAM read, page ROM read)

"Figure 11.9 Timing Adjustment (SRAM read, page ROM read)", changed. (p.11-14) Rev7.00:

ion; In reading of SRAM, input a stable address signal during bus cycles after the start of sampling. Input of an unstable address signal may create a possibility of incorrect data being read and completion of the bus cycle not being possible without the HWAITZ signal de-asserted.

17. <u>14.1 R-IN32M3 TAUJ2 Features</u> "Table14.3 TAUJ2 Interrupt signals", entry added to the table. (p.14-2) Rev7.00:

#### Table14.3 TAUJ2 Interrupt signals

| TAUJ2 signal | Function            | Connected to                                        |

|--------------|---------------------|-----------------------------------------------------|

| INTTAUJ2I0   | Channel 0 interrupt | Interrupt Controller INTTAUJ2I0                     |

|              |                     | DMA Controller trigger 0 (DTFR)                     |

|              |                     | Timer Capture trigger 0 (TTFR)                      |

|              |                     | Real-time Port trigger 0 (RPTFR)                    |

| INTTAUJ2I1   | Channel 1 interrupt | Interrupt Controller INTTAUJ2I1                     |

|              |                     | DMA Controller trigger 1 (DTFR)                     |

|              |                     | Timer Capture trigger 1 (TTFR)                      |

|              |                     | Real-time Port trigger 1 (RPTFR)                    |

| INTTAUJ2I2   | Channel 2 interrupt | Interrupt Controller INTTAUJ212                     |

|              |                     | <ul> <li>DMA Controller trigger 2 (DTFR)</li> </ul> |

|              |                     | Timer Capture trigger 2 (TTFR)                      |

|              |                     | Real-time Port trigger 2 (RPTFR)                    |

| INTTAUJ2I3   | Channel 3 interrupt | Interrupt Controller INTTAUJ2I3                     |

|              |                     | DMA Controller trigger 3 (DTFR)                     |

|              |                     | <ul> <li>Timer Capture trigger 3 (TTFR)</li> </ul>  |

|              |                     | Real-time Port trigger 3 (RPTFR)                    |

Rev8.00:

#### Table14.3 TAUJ2 Interrupt signals

| TAUJ2 signal | Function            | Connected to                                             |

|--------------|---------------------|----------------------------------------------------------|

| INTTAUJ2I0   | Channel 0 interrupt | <ul> <li>Interrupt Controller INTTAUJ2I0</li> </ul>      |

|              |                     | <ul> <li>DMA Controller trigger (DTFR/RTDFTR)</li> </ul> |

|              |                     | <ul> <li>Timer Capture trigger (TMTFR)</li> </ul>        |

|              |                     | <ul> <li>Real-time Port trigger (RPTFR)</li> </ul>       |

|              |                     | <ul> <li>HW-RTOS (Hardware ISR)</li> </ul>               |

| INTTAUJ2I1   | Channel 1 interrupt | Interrupt Controller INTTAUJ2I1                          |

|              |                     | <ul> <li>DMA Controller trigger (DTFR/RTDFTR)</li> </ul> |

|              |                     | <ul> <li>Timer Capture trigger (TMTFR)</li> </ul>        |

|              |                     | <ul> <li>Real-time Port trigger (RPTFR)</li> </ul>       |

|              |                     | HW-RTOS (Hardware ISR)                                   |

| INTTAUJ2I2   | Channel 2 interrupt | Interrupt Controller INTTAUJ2I2                          |

|              |                     | <ul> <li>DMA Controller trigger (DTFR/RTDFTR)</li> </ul> |

|              |                     | <ul> <li>Timer Capture trigger (TMTFR)</li> </ul>        |

|              |                     | <ul> <li>Real-time Port trigger (RPTFR)</li> </ul>       |

|              |                     | <ul> <li>HW-RTOS (Hardware ISR)</li> </ul>               |

| INTTAUJ2I3   | Channel 3 interrupt | Interrupt Controller INTTAUJ2I3                          |

|              |                     | <ul> <li>DMA Controller trigger (DTFR/RTDFTR)</li> </ul> |

|              |                     | <ul> <li>Timer Capture trigger (TMTFR)</li> </ul>        |

|              |                     | · Real-time Port trigger (RPTFR)                         |

|              |                     | <ul> <li>HW-RTOS (Hardware ISR)</li> </ul>               |

## 18. 14.1.1.1 Timer operation functions

"Table 14.4 TAUJ2 operation functions", External Event Count Function added. (p.14-3) Rev7.00:

Table 14.4 TAUJ2 operation functions

| Independent channel operation function                           | Object item                                                                                             |  |  |  |  |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Independent channel operation functions                          | · · · · · · · · · · · · · · · · · · ·                                                                   |  |  |  |  |  |  |

| 14.7.1 [Interval Timer Function]                                 | Interrupt is output every regular interval.                                                             |  |  |  |  |  |  |

| 14.7.2 TAUJ2TTINm Input Interval Timer Function                  | Interrupt is output by valid edge of every the regular internal or external input.                      |  |  |  |  |  |  |

| 14.7.3 [Delay Count Function]                                    | The interrupt to which fixed delay was added is output to an effective<br>input edge of external input. |  |  |  |  |  |  |

| 14.7.4 TAUJ2TTINm Input Pulse Interval Measurement<br>Function J | Time of the input space of the outside input signal is measured.                                        |  |  |  |  |  |  |

| 14.7.5 TAUJ2TTINm Input Signal Width Measurement<br>Function J   | The signal width of the outside input signal is measured.                                               |  |  |  |  |  |  |

| Synchronous channel operation function                           |                                                                                                         |  |  |  |  |  |  |

| 14.8.1 「PWM Output Function」                                     | A corrugation is output.                                                                                |  |  |  |  |  |  |

## Rev8.00:

Table 14.4 TAUJ2 operation functions

| Independent channel operation function                           | Object item                                                                                                                                                                   |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Independent channel operation functions                          |                                                                                                                                                                               |

| 14.7.1 "Interval Timer Function"                                 | Interrupts are output at regular intervals.                                                                                                                                   |

| 14.7.2 "TAUJ2TTINm Input Interval Timer Function"                | Interrupts are output at regular intervals or when an effective edge of<br>the external input signal is detected.                                                             |

| 14.7.3 "Delay Count Function"                                    | Interrupts which have a defined delay to the effective edge of the<br>external input signal are output.                                                                       |

| 14.7.4 "TAUJ2TTINm Input Pulse Interval Measurement<br>Function" | The interval of the external input signal is measured.                                                                                                                        |

| 14.7.5 "TAUJ2TTINm Input Signal Width Measurement<br>Function"   | The signal width of the external input signal is measured.                                                                                                                    |

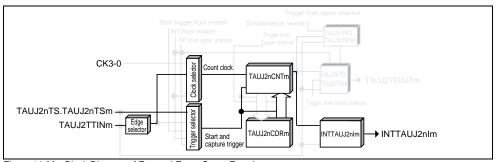

| 14.7.6 "External Event Count Function"                           | This function is used as an event timer, which generates an interrupt in<br>response to detection of the specified number of effective edges of the<br>external input signal. |

| Synchronous channel operation function                           |                                                                                                                                                                               |

| 14.8.1 "PWM Output Function"                                     | PWM waveform is output.                                                                                                                                                       |

## **RENESAS TECHNICAL UPDATE**

## 19. 14.3.3(3) TAUJ2CMORm - TAUJ2 channel mode OS register

"Function" of TAUJ2CCS bit and TAUJ2MD bit, modified. (p.14-15 to 14-18)

## Rev7.00:

#### (3) TAUJ2CMORm - TAUJ2 channel mode OS register

This register controls channel m operation.

• Access This register can be read or written in 16-bit units. Writing is only possible while the counter is stopped (TAUJ2TE.TAUJ2TEm = 0).

|                | 15  | 14           | 13     | 12            | 11                    | 10               | 9              | 8                        | 7        | 6          | 5      | 4            | 3    | 2    | 1    | 0      | Address                            | Initia<br>Valu |

|----------------|-----|--------------|--------|---------------|-----------------------|------------------|----------------|--------------------------|----------|------------|--------|--------------|------|------|------|--------|------------------------------------|----------------|

| TAUJ2<br>CMORm |     | JJ2<br>[1:0] |        | UJ2<br>S[1:0] | TAUJ2MAS              | ТА               | UJ2S<br>[2:0]  | J2STS TAUJ<br>2:0] COS[1 |          |            | 0      | TAUJ2MD[4:0] |      |      |      | 0]     | 4000 0080H<br>+ m×4H               | 0000           |

| R/W            | R/  | W            | R      | W             | R/W                   |                  | R/W            |                          | R/       | W          | R      |              |      | R/V  | V    |        |                                    |                |

| Bit positio    | n   | Bit n        | ame    |               |                       |                  |                |                          |          | Fun        | ction  |              |      |      |      |        |                                    |                |

| 15, 14         | TAU | JJ2CK        | 5[1:0] | Т             | sed as the cour       | ock is<br>t cloc | used<br>k depe | endin                    | g on bit | s TAU      | J2CN   | ÍÖR          | m.C  | ČCS  | [1:0 | ].     | circuit. It can a                  | lso be         |

|                |     |              |        |               | TAUJ2CI               | KS1              | TA             |                          | CKS0     |            | Select | ted          | pre  | scal | er o | utput  | :                                  |                |

|                |     |              |        |               | 0                     |                  | -              | 0                        |          | CK0<br>CK1 |        |              |      |      |      |        |                                    |                |

|                |     |              |        |               | 1                     |                  |                | 0                        |          | CK2        |        |              |      |      |      |        |                                    |                |

|                |     |              |        |               | 1                     |                  |                | 1                        |          | CK3        |        |              |      |      |      |        |                                    |                |

| 13, 12         | TAI | JJ2CC        | S[1:0] | s             | elects the coun       | t clock          | for T          | AUJ2                     | CNTm     | counte     | er.    |              |      |      |      |        |                                    |                |

|                |     |              |        |               | TAUJ2C0               | CS1              | TA             | UJ20                     | CS0      |            |        | Se           | ect  | ed c | oun  | t cloo | ck                                 |                |

|                |     |              |        |               | 0                     |                  |                | 0                        |          |            | scaler |              |      |      |      |        |                                    |                |

|                |     |              |        |               | 1                     |                  |                | 0                        |          | Sett       | ing pi | rohi         | bite | d    |      |        |                                    |                |

|                |     |              |        |               | 1                     |                  |                | 0                        |          |            |        |              |      |      |      |        |                                    |                |

|                |     |              |        |               | 1                     |                  |                | 1                        |          |            |        |              |      |      |      |        |                                    |                |

| 11             | TAI | JJ2MA        | S      | т             | 0: Slave<br>1: Master |                  |                |                          |          |            |        | Ū            |      |      |      |        | annel operation<br>(CHm_odd), it i |                |

## Rev8.00:

(3) TAUJ2CMORm - TAUJ2 channel mode OS register

This register controls channel m operation.

• Access This register can be read or written in 16-bit units. Writing is only possible while the counter is stopped (TAUJ2TE.TAUJ2TEm = 0).

|                | 15         | 14    | 13     | 12           |                   | 11                                            | 10                | 9                       | 8     | 7        | 6          | 5                | 4            | 3    | 2    | 1    | 0              | Add | ress      | Init<br>Val |

|----------------|------------|-------|--------|--------------|-------------------|-----------------------------------------------|-------------------|-------------------------|-------|----------|------------|------------------|--------------|------|------|------|----------------|-----|-----------|-------------|

| TAUJ2<br>CMORm | TAL<br>CKS |       |        | JJ2<br>[1:0] | TA                | UJ2MAS                                        | ΤA                | UJ2STS TAI<br>[2:0] COS |       |          |            | 0                | TAUJ2MD[4:0] |      |      | l:0] | 4000 (<br>+ m; |     | 000       |             |

| R/W            | R/\        | N     | R/     | W            | R/W R/W R/W R R/W |                                               |                   |                         |       |          |            | -                |              |      |      |      |                |     |           |             |

| Bit positio    | n          | Bit n | ame    |              |                   |                                               |                   |                         |       |          | Fun        | ction            |              |      |      |      |                |     |           |             |

| 15, 14         | IAC        | JZCK  | S[1:0] | -            | The op            | s the opera<br>peration cl<br>as the cour     | ock is<br>it cloc | usec<br>k dep           | endin | g on bit | s TAU      | J2CM             | İÖR          | m.(  | сc   | S[1: | 0].            |     | t can als | so be       |

|                |            |       |        |              |                   | TAUJ2CI                                       | KS1               | T.                      | AUJ20 | CKS0     |            | Select           | ted          | pre  | SCa  | ler  | outpu          | ut  |           |             |

|                |            |       |        |              |                   | 0                                             |                   |                         | 0     |          | CK0        |                  |              |      |      |      |                |     |           |             |

|                |            |       |        |              | -                 | 0                                             |                   | -                       | 1     |          | CK1<br>CK2 |                  |              |      |      |      |                |     |           |             |

|                |            |       |        |              | F                 | 1                                             |                   | -                       | 1     |          | CK3        |                  |              |      |      |      |                |     |           |             |

| 13, 12         | TAU        | IJ2CC | S[1:0] | \$           | Select            | s the coun                                    |                   | -                       | AUJ2  | -        | counte     |                  | Sel          | ect  | ed   | cou  | nt clc         | ock |           |             |

|                |            |       |        |              |                   | 0                                             |                   |                         | 0     |          |            | scaler<br>JJ2CN  |              |      |      |      |                |     |           |             |

|                |            |       |        |              |                   | 0                                             |                   |                         | 1     |          |            | ctive<br>ut sign |              | еo   | f T/ | 1UJ  | 2TTII          | Nm  |           |             |

|                |            |       |        |              |                   | 1                                             |                   |                         | 0     |          | Sett       | ting pr          | rohil        | bite | d    |      |                |     |           |             |

|                |            |       |        |              | L                 | 1                                             |                   |                         | 1     |          |            |                  |              |      |      |      |                |     |           |             |

| 11             | TAU        | IJ2MA | S      |              | 0: S<br>1: M      | ies the cha<br>lave<br>laster<br>it is only v |                   |                         |       |          |            |                  | U            | ,    |      |      |                |     |           | fixed       |

## 19. 14.3.3(3) TAUJ2CMORm - TAUJ2 channel mode OS register

"Function" of TAUJ2CCS bit and TAUJ2MD bit, modified. (p.14-15 to 14-18) continued Rev7.00: Rev8.00:

| —<br>AT       | -<br>AUJ2MD[4:0] | Rese<br>Speci                  | TAUJ2<br>MD4<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | TAUJ2<br>MD3<br>0<br>0<br>0<br>0<br>1 | TAUJ2<br>MD2<br>0<br>1<br>1 | TAUJ2<br>MD1<br>0<br>1<br>0 | TAUJ2<br>MD0<br>1/0<br>1/0<br>1/0 | Description<br>Interval Timer mode<br>Setting prohibited |  |  |  |

|---------------|------------------|--------------------------------|------------------------------------------------------|---------------------------------------|-----------------------------|-----------------------------|-----------------------------------|----------------------------------------------------------|--|--|--|

| AT            | AUJ2MD[4:0]      | Speci                          | TAUJ2<br>MD4<br>0<br>0<br>0<br>0<br>0<br>0<br>0      | TAUJ2<br>MD3<br>0<br>0<br>0<br>0<br>1 | TAUJ2<br>MD2<br>0<br>1<br>1 | MD1<br>0<br>1<br>0          | MD0<br>1/0<br>1/0                 | Interval Timer mode<br>Setting prohibited                |  |  |  |

|               |                  |                                | TAUJ2<br>MD4<br>0<br>0<br>0<br>0<br>0<br>0<br>0      | TAUJ2<br>MD3<br>0<br>0<br>0<br>0<br>1 | TAUJ2<br>MD2<br>0<br>1<br>1 | MD1<br>0<br>1<br>0          | MD0<br>1/0<br>1/0                 | Interval Timer mode<br>Setting prohibited                |  |  |  |

|               |                  |                                | MD4<br>0<br>0<br>0<br>0<br>0<br>0<br>0               | MD3<br>0<br>0<br>0<br>0<br>1          | MD2<br>0<br>0<br>1<br>1     | MD1<br>0<br>1<br>0          | MD0<br>1/0<br>1/0                 | Interval Timer mode<br>Setting prohibited                |  |  |  |

|               |                  |                                | 0<br>0<br>0<br>0<br>0                                | 0<br>0<br>0<br>1                      | 0<br>1<br>1                 | 1                           | 1/0                               | Interval Timer mode<br>Setting prohibited                |  |  |  |

|               |                  |                                | 0<br>0<br>0<br>0                                     | 0<br>0<br>1                           | 1                           | 1                           | 1/0                               |                                                          |  |  |  |

|               |                  |                                | 0 0 0 0                                              | 0                                     | 1                           | -                           | 1/0                               |                                                          |  |  |  |

|               |                  |                                | 0                                                    | 1                                     |                             |                             | 1/0                               | Capture mode                                             |  |  |  |

|               |                  |                                | 0                                                    |                                       | <u>^</u>                    | 1                           | 1/0                               | Setting prohibited                                       |  |  |  |

|               |                  |                                | -                                                    |                                       | 0                           | 0                           | 1/0                               | One Count mode                                           |  |  |  |

|               |                  |                                | 0                                                    | 1                                     | 0                           | 1                           | 1/0                               | Setting prohibited                                       |  |  |  |

|               |                  |                                | 0                                                    | 1                                     | 1                           | 0                           | 0                                 | Capture & One Count mode                                 |  |  |  |

|               |                  |                                | 0                                                    | 1                                     | 1                           | 1                           | 1/0                               | Setting prohibited                                       |  |  |  |

|               |                  |                                | 1                                                    | 0                                     | 0                           | 0                           |                                   |                                                          |  |  |  |

|               |                  |                                | 1                                                    | 0                                     | 0                           | 1                           |                                   |                                                          |  |  |  |

|               |                  | -                              | 1                                                    | 0                                     | 1                           | 0                           | 4/0                               | Occurrent Occurrence and a                               |  |  |  |

|               |                  | -                              | 1                                                    | 0                                     | 1                           | 1                           | 1/0<br>1/0                        | Count Capture mode                                       |  |  |  |

|               |                  |                                | 1                                                    | 1                                     | 0                           | 0                           | 0                                 | Setting prohibited<br>Capture & Gate Count mode          |  |  |  |

|               |                  | L                              | I                                                    | 1                                     | 0                           | I                           | 0                                 | Capture & Gate Count mode                                |  |  |  |

| _             |                  |                                |                                                      |                                       |                             |                             |                                   |                                                          |  |  |  |

| N             | Mode             | T                              |                                                      |                                       |                             | Role of the                 | MD0 bit                           |                                                          |  |  |  |

| Interval Time |                  | Spec                           | ifies wheth                                          | her the INT                           |                             |                             |                                   | the counter starts counting (when                        |  |  |  |