# RENESAS TECHNICAL UPDATE

〒211-8668 神奈川県川崎市中原区下沼部 1753

ルネサス エレクトロニクス株式会社

問合せ窓口 <http://japan.renesas.com/contact/>

E-mail: csc@renesas.com

| 製品分類 | MPU & MCU                                      | 発行番号   | TN-V85-A025A/J | Rev.        | 第1版  |

|------|------------------------------------------------|--------|----------------|-------------|------|

| 題名   | クロック同期シリアル・インターフェース (CSIG) の RY 出力遅延時間に関する注意事項 |        |                | 情報分類        | 技術情報 |

| 適用製品 | V850E2/Dx4 シリーズ<br>V850E2/Dx4-H シリーズ           | 対象ロット等 | 関連資料           | 適用製品のデータシート |      |

|      |                                                | 全ロット   |                |             |      |

クロック同期シリアル・インターフェース (CSIG) の電気的特性 (CSIG0RY output delay time) におきまして、記載事項の変更がありますので、ご連絡いたします。以下、変更内容およびマニュアル修正内容を記載いたします。

## 1. 変更内容

### (1) CSIG スレーブモード時の電気的特性 (CSIG0RY output delay time) の変更

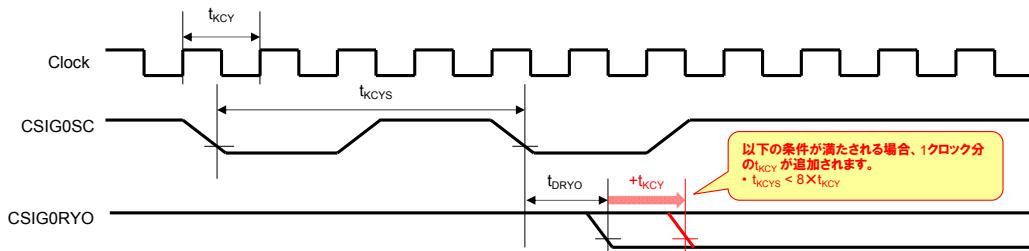

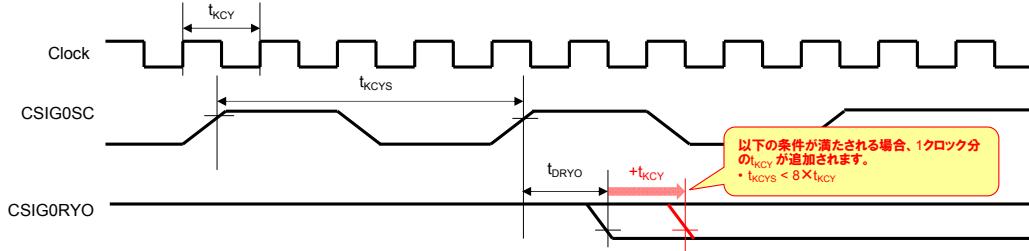

下図 1 の通り、CSIGnSC サイクル時間( $t_{KCYS}$ )が、マクロクロックサイクルタイム( $t_{KCY}$ )の 8 倍よりも小さい場合、CSIG0RY output delay time ( $t_{DRYO}$ )の最大値に対し、1 クロック分の  $t_{KCY}$  が追加されます。

8 倍以上の場合は、スペック変更はありません

※レジスタ、ビットの詳細は各製品のユーザーズマニュアルを参照下さい。

#### ■ CSIG (CSIG0CFG0.CSIGOCKP / CSIGnCTL1.CSIGnCKR = 0/0 or 1/1)

#### ■ CSIG (CSIG0CFG0.CSIGOCKP / CSIGnCTL1.CSIGnCKR = 0/1 or 1/0)

図 1. CSIG0SC 及び CSIG0RY のタイミングチャート図

2. マニュアル修正内容

## (1) CSIG 電気的特性 変更内容

CSIG0RY output delay time (tDRYO)の説明を、以下の通り変更します。

| Parameter                                                                                     | CT | Symbol | Condition                    | Ratings             |      |                                 | Unit |

|-----------------------------------------------------------------------------------------------|----|--------|------------------------------|---------------------|------|---------------------------------|------|

|                                                                                               |    |        |                              | MIN.                | TYP. | MAX.                            |      |

| Ready / Busy output signal (CSIGORY)<br>output delay time (vs.<br>CSIG0SC input) <sup>d</sup> | DS | tDRYO  | filtered (DNF) <sup>a</sup>  | tKCYS $\geq$ 8×tKCY |      | 30 +<br>tdDNFSCL(max)           | ns   |

|                                                                                               |    |        |                              | tKCYS < 8×tKCY      |      | 30 +<br>tdDNFSCL(max)<br>+ tKCY | ns   |

|                                                                                               |    |        | filter-bypassed <sup>c</sup> | tKCYS $\geq$ 8×tKCY |      | 30                              | ns   |

|                                                                                               |    |        |                              | tKCYS < 8×tKCY      |      | 30+tKCY                         | ns   |

以上