# **RENESAS TECHNICAL UPDATE**

#### 1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category     | MPU & MCU                                   |                                               |             | Document<br>No.                                                                                                                                              | TN-16C-A220                                       | )A/E                                                          | Rev.    | 1.00    |

|-------------------------|---------------------------------------------|-----------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------|---------|---------|

| Title                   | Descriptions Changed in the M16C/<br>Manual |                                               | C Group     | Information<br>Category                                                                                                                                      | Technical Notif                                   | ication                                                       |         |         |

|                         |                                             |                                               | Lot No.     |                                                                                                                                                              |                                                   |                                                               |         |         |

| pplicable<br>Product    | M16C/6C Group                               |                                               |             | Reference<br>Document                                                                                                                                        | M16C/6C Group<br>User's Manual: Hardware Rev.2.10 |                                                               |         | 2.10    |

| •                       | ecifications of the                         | e M16C/6C Group hav                           | ve been cha | nged. MCU us                                                                                                                                                 | age and setting                                   | procedu                                                       | res hav | /e also |

| When in r<br>Table 11.7 |                                             | on mode, the value of<br>for Each Processor M | ode         |                                                                                                                                                              |                                                   | Mem                                                           | iory    |         |

|                         |                                             | Memory Expansion Mode of                      |             | -                                                                                                                                                            |                                                   | Expansion Mode                                                |         |         |

| Bits PM05 to PM04       |                                             | 00b (separate bus) the c                      |             | $(\overline{CS2}$ is for multiplexed bus and<br>others are for separate bus)<br>$(\overline{CS1}$ is for multiplexed bus and<br>others are for separate bus) |                                                   | 11b (the entire $\overline{CS}$ space is for multiplexed bus) |         | 5       |

| Data bus width          |                                             | 8 bits 8 bits                                 |             | S                                                                                                                                                            |                                                   | 8 bits                                                        |         |         |

| (omissior               | )                                           |                                               |             |                                                                                                                                                              | 1                                                 |                                                               |         |         |

| P3_0                    |                                             | A8 A8                                         |             |                                                                                                                                                              |                                                   | Undefined value<br>is output <sup>(1)</sup>                   |         | •       |

| (omissior               | )                                           |                                               |             |                                                                                                                                                              |                                                   |                                                               |         |         |

| Note:<br>1. Th          | e change is indic                           | cated in bold text.                           |             |                                                                                                                                                              |                                                   |                                                               |         |         |

| 2. Time                 | er S                                        |                                               |             |                                                                                                                                                              |                                                   |                                                               |         |         |

- 2.1 G1BT Register in Timer S

- ➔ 20.2.5 Base Timer Register (G1BT)

Do not write to this register.

The G1BT register becomes 0000h when the BTS bit in the G1BCR1 register is set to 0 (base timer reset). This function works same as before without any change.

## 2.2 Interrupt Request When Selecting Time Measurement Function

➔ 20.5.6 Interrupt Request When Selecting Time Measurement Function

When the FSCj bit (j = 0 to 7) in the G1FS register is set to 1, and the IFEj bit in the G1FE register is also set to 1, the G1IRj bit in the G1IR register, or the IR bits in registers ICOCiIC (i = 0, 1) or ICOCHJIC (j = 0 to 3) may become 1 (interrupt requested) after a maximum of two fBT1 cycles.

When using IC/OC interrupt i or IC/OC channel j interrupt, set bits FSCj and IFEj to 1, then perform the following:

- (1) Wait for two or more fBT1 cycles.

- (2) Set the IR bit in the ICOCiIC register and/or the ICOCHJIC register to 0.

- (3) Wait for three or more fBT1 cycles after the time measurement function is selected. Set the G1IR register to 00h after setting the IR bit in the ICOCiIC register to 0.

- 3. USB Function

- 3.1 USBSTS Bit in the USBMC Register

The bit explanation has been partially changed.

→ 24.2.33 USB Module Control Register (USBMC), USBSTS (USB module status flag) (b6)

### Premodification:

After setting the USBE bit to 0 (USB clock supplied) and <u>a stable USB clock is supplied</u>, the USBSTS bit becomes 0 (USB module enabled). Access USB associated registers other than the USBMC register when the USBSTS bit is 0 (USB module enabled).

Post modification:

<u>When the USB module is enabled</u> after setting the USBE bit to 0 (USB clock supplied), the USBSTS bit becomes 0 (USB module enabled). Access USB associated registers other than the USBMC register when the USBE bit is 0 and the USBSTS bit is 0 (USB module enabled).

Once the USBSTS bit becomes 0, then it remains 0 even if the USBE bit is set to 1.

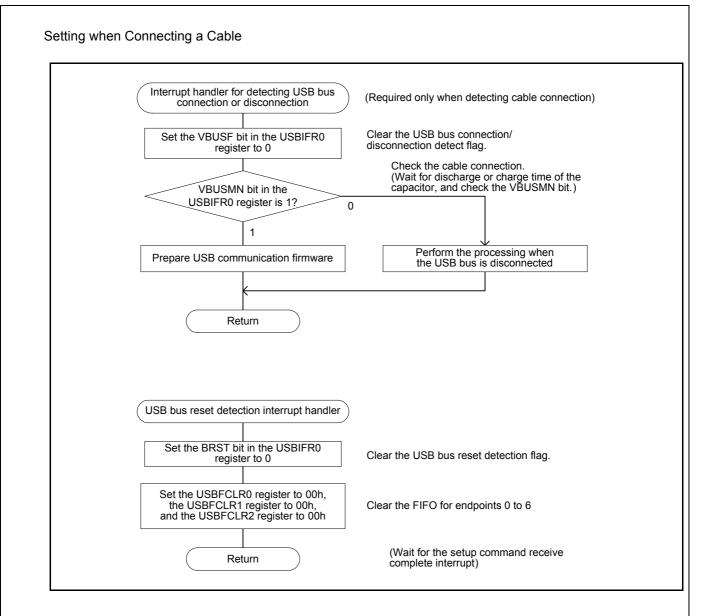

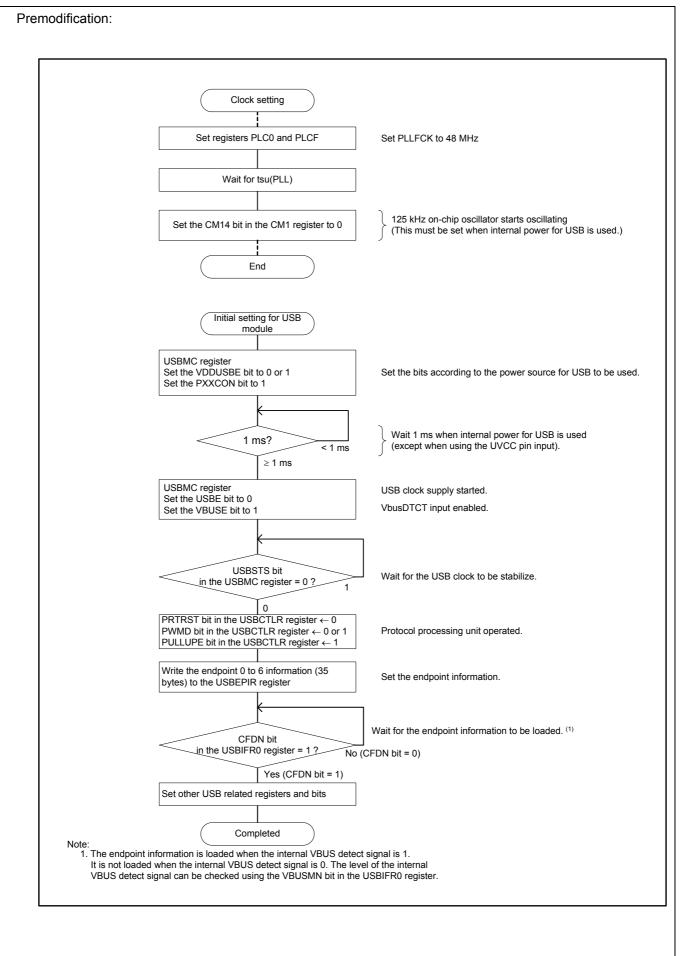

### 3.2 USB Initial Setting

Conditions for the initial setting and when connecting a cable are now described separately. The procedures also have been changed.

→24.3.7 USB Initial Setting, Figure 24.6 USB Module Initial Setting, Figure 24.7 Setting when Connecting the Cable

Post modification:

#### Initial Setting

| USB initial setting                                                                            |                                                                                                               |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Set registers PLC0 and PLCF                                                                    | Set PLLFCK to 48 MHz.<br>PLLFCK generation enabled                                                            |

| Wait for tsu(PLL)                                                                              | Wait until PLL oscillation stabilizes.                                                                        |

| Set the CM14 bit in the CM1 register to 0                                                      | 125 kHz on-chip oscillator starts oscillating.<br>(This must be set when internal power for the USB is used.) |

| Set the VDDUSBE bit to 1 and<br>the PXXCON bit to 1 in the USBMC register                      | Provide 3.3 V of internal power for the USB.<br>(This must be set when internal power for the USB is used.)   |

| 1 ms? < 1 ms                                                                                   | Wait for 1 ms.<br>(Wait is necessary when internal power for the USB is used.)                                |

| ≥ 1 ms<br>Set the USBE bit to 0 and<br>the VBUSE bit to 1 in the USBMC register                | USB clock supplied (USB module enabled)<br>VbusDTCT input enabled                                             |

| USBSTS bit<br>in the USBMC register is 0? 1<br>0                                               | Wait until the USB module is enabled.                                                                         |

| Set registers USBIER0 to USBIER3,<br>USBISR0 to USBISR3, USBINT0IC,<br>USBINT1IC, and USBRSMIC | Set registers associated with interrupts.                                                                     |

| Set the PRTRST bit to 0, set the PWMD bit to 0<br>or 1 in the USBCTLR register                 | Protocol processing unit operating state<br>Select self-powered mode or bus powered mode                      |

| Write information of endpoints 0 to 6 (35 bytes)<br>to the USBEPIR register                    | Set endpoint information.                                                                                     |

| Set the PULLUPE bit in the USBCTLR<br>register to 1                                            | ATTACH output ON (D + pulled up)                                                                              |

| Completed                                                                                      | (USB module waits for cable to be connected)                                                                  |