# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 32 R32

# R32C/100 SERIES

# SOFTWARE MANUAL

RENESAS MCU M16C FAMILY / R32C/100 SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

# The Notation in This Manual

For detailed explications of the R32C/100 Series's operation, the notation based on specific rules is used throughout this manual as shown below.

| Category      | Notation                                        | Description/Meaning                                                                                                                                                |

|---------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbols       | IMM                                             | Immediate value                                                                                                                                                    |

|               | IMMEX                                           | Immediate value to be sign-extended                                                                                                                                |

|               | abs                                             | Absolute value of absolute addressing mode                                                                                                                         |

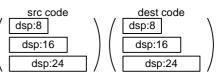

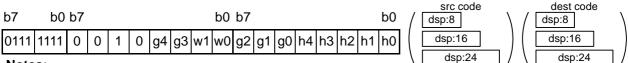

|               | dsp                                             | Displacement value of relative addressing mode                                                                                                                     |

|               | []                                              | Indirect addressing mode                                                                                                                                           |

|               | label                                           | Specified address as Label used in program counter relative<br>addressing mode.<br>Write a label when programming. An address can be written<br>directly, as well. |

|               | bit                                             | Specified bit number.                                                                                                                                              |

|               |                                                 | Write a numeric value in the actual program.                                                                                                                       |

| Numbers       | R0L <u>B</u> , R0 <u>B</u> , R2R0 <u>B</u> etc. | Bank1 register (with " <u>B</u> " appended)<br>Binary number (with " <u>b</u> " appended)                                                                          |

| Numbers       | 00 <u>b</u><br>0000 <u>h</u>                    | Hexadecimal number (with " <u>h</u> " appended). For a numeric                                                                                                     |

|               | 0000 <u>n</u>                                   | number beginning with an alphabetic letter, add 0 before the letter. For example, FFh should be written as 0FFh.                                                   |

|               | 100                                             | Decimal number (BCD)                                                                                                                                               |

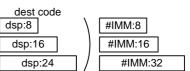

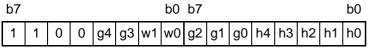

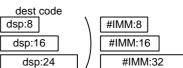

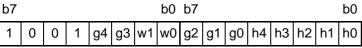

| Bit length    | #IMM <u>:8</u> etc.                             | The underlined part indicates an effective bit length for the operand.                                                                                             |

|               | :3                                              | Effective bit length is 3.                                                                                                                                         |

|               | :4                                              | Effective bit length is 4.                                                                                                                                         |

|               | :8                                              | Effective bit length is 8.                                                                                                                                         |

|               | :16                                             | Effective bit length is 16.                                                                                                                                        |

|               | :24                                             | Effective bit length is 24.                                                                                                                                        |

|               | :32                                             | Effective bit length is 32.                                                                                                                                        |

| Instruction   | MOV. B <u>:S</u> etc.                           | The underlined part specifies instruction format.                                                                                                                  |

| formats       | :G                                              | Generic format                                                                                                                                                     |

|               | :Q                                              | Quick format                                                                                                                                                       |

|               | :S                                              | Short format                                                                                                                                                       |

|               | :Z                                              | Zero format                                                                                                                                                        |

| Data size for | MOV <u>.W</u> etc.                              | The underlined part specifies data size for operation.                                                                                                             |

| operation     | .В                                              | Byte (8 bits)                                                                                                                                                      |

|               | .W                                              | Word (16 bits)                                                                                                                                                     |

|               | .L                                              | Long word (32 bits)                                                                                                                                                |

|               | .BW                                             | Byte to Word                                                                                                                                                       |

|               | .BL                                             | Byte to Long word                                                                                                                                                  |

|               | .WL                                             | Word to Long word                                                                                                                                                  |

| Category                                                                                                                                                                                                                                    | Notation                                                   | Description/Meaning                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Jump distance                                                                                                                                                                                                                               | JMP <u>.A</u> etc.                                         | Underlined part specifies effective bit length of jump relative distance.                                                                 |

|                                                                                                                                                                                                                                             | .S                                                         | 3-bit PC forward relative. The effective value is 1 to 8.                                                                                 |

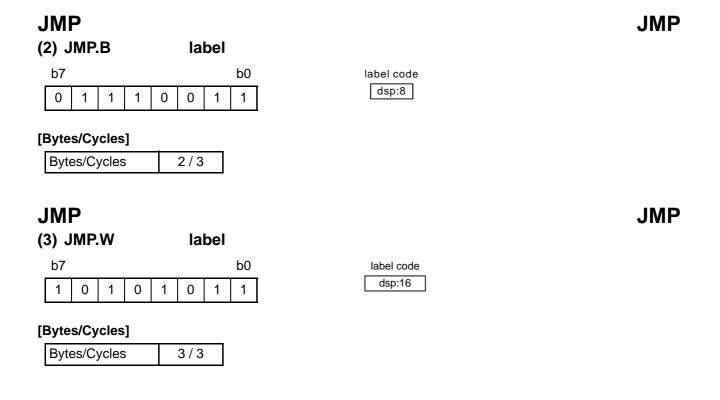

|                                                                                                                                                                                                                                             | .В                                                         | 8-bit PC relative. The effective value is -128 to 127.                                                                                    |

|                                                                                                                                                                                                                                             | .W                                                         | 16-bit PC relative. The effective value is -32768 to 32767.                                                                               |

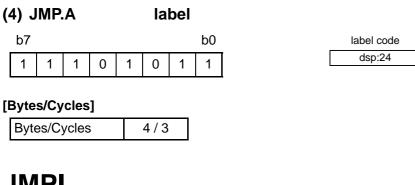

|                                                                                                                                                                                                                                             | .А                                                         | 24-bit PC forward relative. The effective value is -8388608 to 8388607.                                                                   |

| Operators                                                                                                                                                                                                                                   |                                                            | C language syntax is applied in principle. The notations used in this manual are shown as below.                                          |

|                                                                                                                                                                                                                                             | =                                                          | Assignment operator.<br>Assign the value on the right side to the left.                                                                   |

|                                                                                                                                                                                                                                             | -                                                          | Unary minus or subtraction                                                                                                                |

| 1                                                                                                                                                                                                                                           | +                                                          | Addition                                                                                                                                  |

|                                                                                                                                                                                                                                             | *                                                          | Dereferencing operator or multiplication                                                                                                  |

|                                                                                                                                                                                                                                             | /                                                          | Division                                                                                                                                  |

|                                                                                                                                                                                                                                             | %                                                          | Modulus                                                                                                                                   |

|                                                                                                                                                                                                                                             | ~                                                          | Bitwise NOT                                                                                                                               |

|                                                                                                                                                                                                                                             | &                                                          | Bitwise AND                                                                                                                               |

|                                                                                                                                                                                                                                             |                                                            | Bitwise OR                                                                                                                                |

|                                                                                                                                                                                                                                             | ٨                                                          | Bitwise XOR (exclusive or)                                                                                                                |

| -                                                                                                                                                                                                                                           | (float)                                                    | Cast operator                                                                                                                             |

|                                                                                                                                                                                                                                             | ;                                                          | End of a statement                                                                                                                        |

|                                                                                                                                                                                                                                             | {}                                                         | Start and end of compound statements.                                                                                                     |

|                                                                                                                                                                                                                                             |                                                            | More than two statements can be described in {}.                                                                                          |

|                                                                                                                                                                                                                                             | if (expression)<br>statement 1 else<br>statement 2         | If the conditional expression evaluates to true, statement 1 is executed, otherwise statement 2 is executed.                              |

|                                                                                                                                                                                                                                             | for (statement<br>1;expression;statement<br>2) {loop body} | After statement 1 is executed, the loop body is executed followed by statement 2 as long as the conditional expression evaluates to true. |

|                                                                                                                                                                                                                                             | do statement while<br>(expression);                        | The statement is executed until the expression evaluates to false. The loop body is executed at least once whether true or not.           |

|                                                                                                                                                                                                                                             | while (expression)<br>statement                            | The statement is executed until the expression evaluates to false.                                                                        |

|                                                                                                                                                                                                                                             | ==, !=                                                     | Equal, not equal comparisons                                                                                                              |

|                                                                                                                                                                                                                                             | >, <                                                       | Greater-than, less-than comparisons                                                                                                       |

|                                                                                                                                                                                                                                             | >=, <=                                                     | Greater-than or equal to, less-than or equal to comparisons                                                                               |

|                                                                                                                                                                                                                                             | &&,                                                        | Logical AND, logical OR<br>The operators guarantee left-to-right evaluation.                                                              |

| Keyword                                                                                                                                                                                                                                     | true                                                       | Non-C language notation.<br>If the condition specified by <i>Cnd</i> is true, 1 is obtained.                                              |

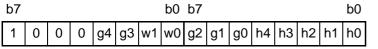

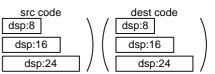

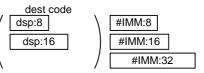

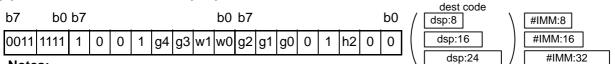

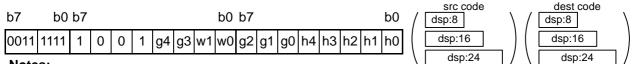

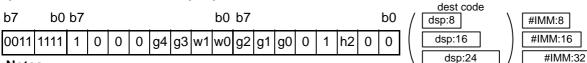

| Available src/       #IMMEX       #IMMEX:8 or #IMMEX:16 can be specified.         dest       #IMM       Either #IMM:8, #IMM:16 or #IMM:32 can be specified         depending on data size for operation. Either #IMM:3 or #is not included. |                                                            | #IMMEX:8 or #IMMEX:16 can be specified.                                                                                                   |

|                                                                                                                                                                                                                                             |                                                            | depending on data size for operation. Either #IMM:3 or #IMM:4                                                                             |

# TABLE OF CONTENTS

| 1. | Ove  | rview                |                     | 1   |

|----|------|----------------------|---------------------|-----|

|    | 1.1  | R32C/100 Series      | Overview            | . 2 |

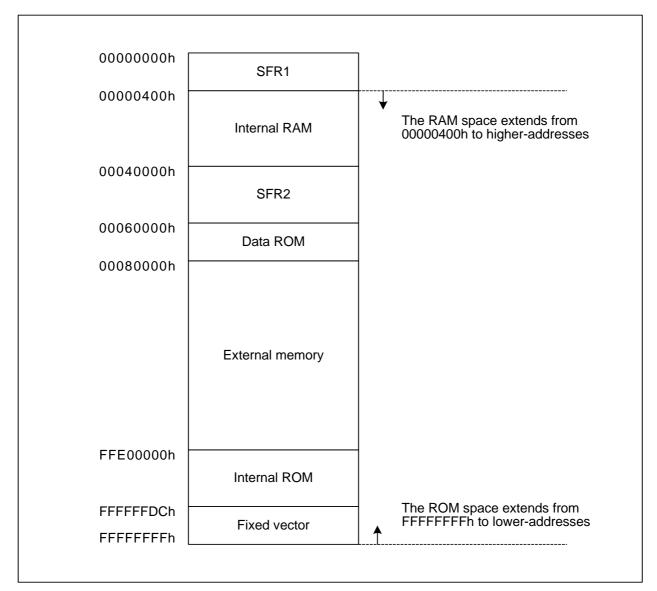

|    | 1.2  | Address Space        |                     | . 3 |

|    | 1.3  | Register Set         |                     | . 4 |

|    | 1.3. | General Purp         | pose Registers      | . 5 |

|    | 1.3. | Fast Interrupt       | t Registers         | . 6 |

|    | 1.3. | DMAC-assoc           | ciated Registers    | . 6 |

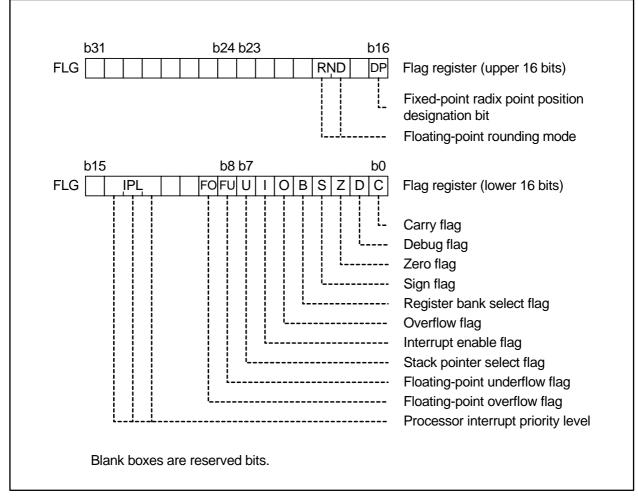

|    | 1.3. | Flag Register        | r (FLG)             | . 7 |

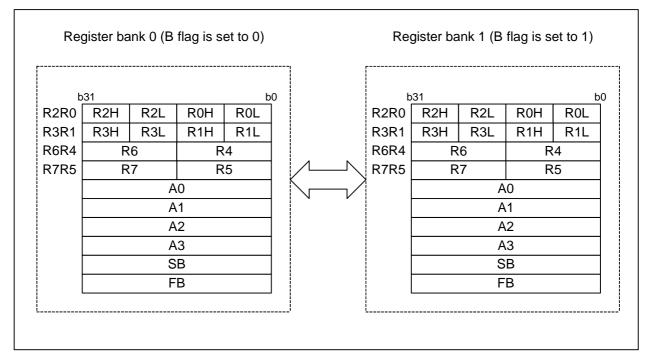

|    | 1.3. | Register Ban         | 1k                  | . 9 |

|    | 1.3. | Internal Regis       | ister Values        | 10  |

|    | 1.4  | Data Types           |                     | 11  |

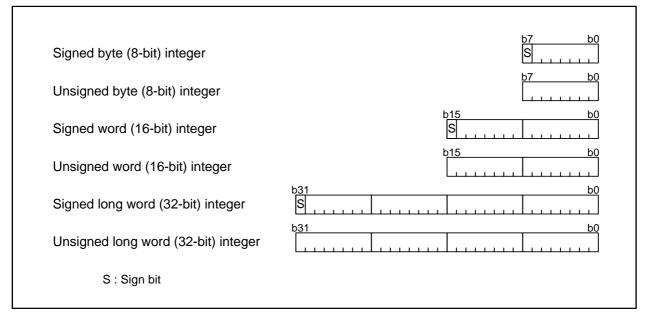

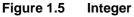

|    | 1.4. | Integer              |                     | 11  |

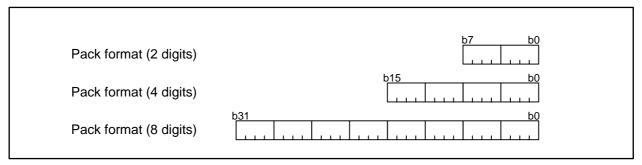

|    | 1.4. | Decimal              |                     | 11  |

|    | 1.4. | Fixed-point N        | Number              | 12  |

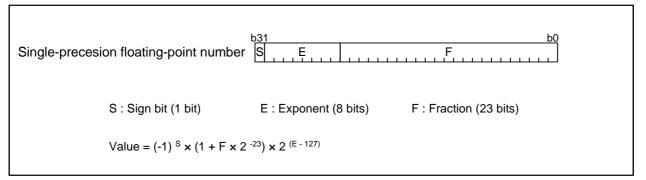

|    | 1.4. | Floating-poin        | nt Number           | 12  |

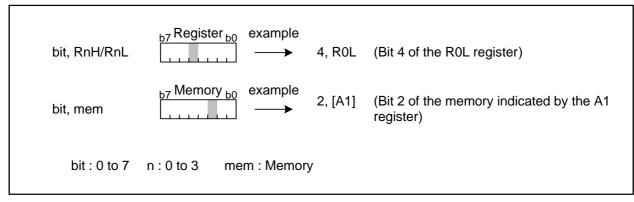

|    | 1.4. | Bit                  |                     | 13  |

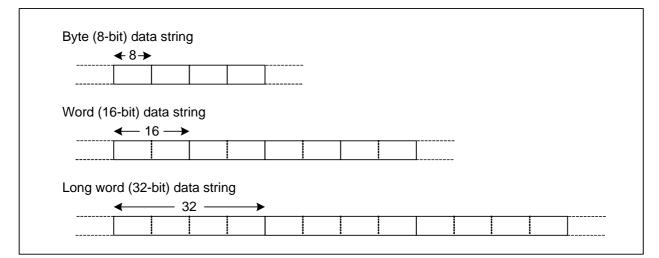

|    | 1.4. | String               |                     | 13  |

|    | 1.5  | Data Configuratio    | on                  | 14  |

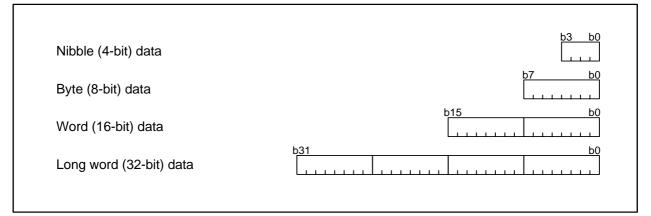

|    | 1.5. | Data Configu         | uration in Register | 14  |

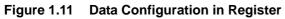

|    | 1.5. | Data Configu         | uration in Memory   | 14  |

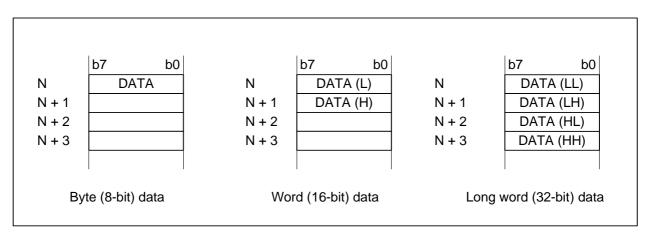

|    | 1.6  | Instruction Forma    | ats                 | 15  |

|    | 1.6. | Opcode               |                     | 16  |

|    | 1.6. | Operand              |                     | 16  |

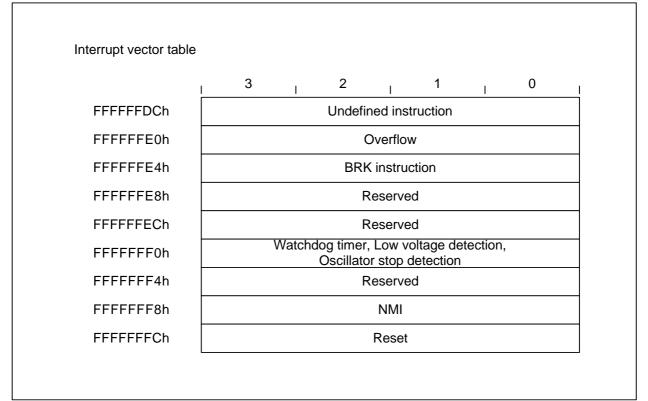

|    | 1.7  | Interrupt Vector Ta  | able                | 17  |

|    | 1.7. |                      | Table               |     |

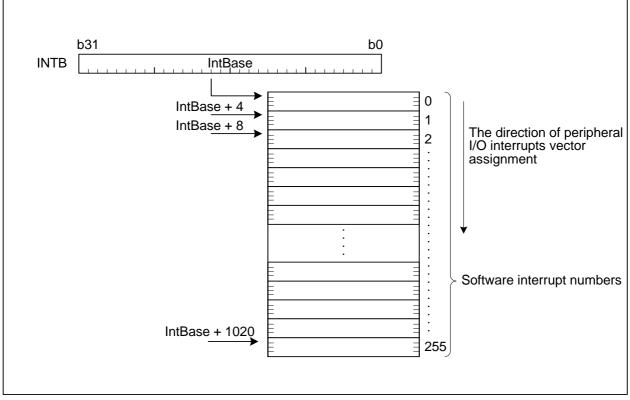

|    | 1.7. | Relocatable \        | Vector Table        | 18  |

| 2. | Ado  | ressing Mode         | 1                   | 19  |

|    | 2.1  | Addressing Mode      |                     | 20  |

|    | 2.2  | Guide to This Cha    | apter               | 21  |

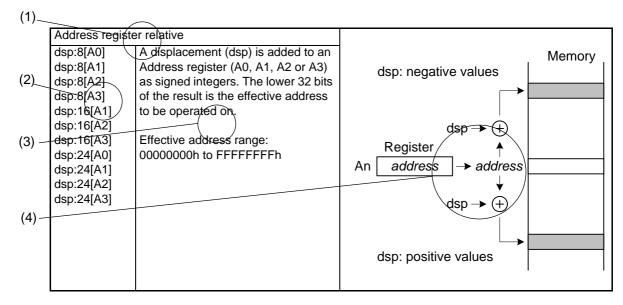

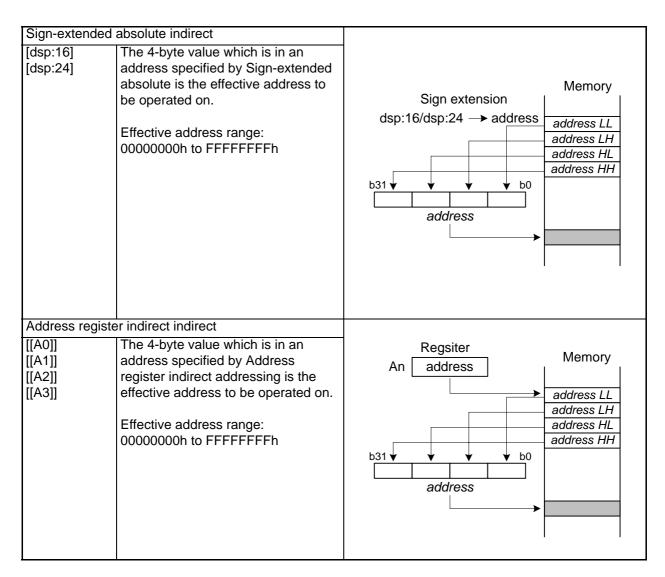

|    | 2.3  |                      | on Addressing       |     |

|    | 2.4  | Indirect Instruction | n Addressing        | 25  |

|    | 2.5  | Extended Instruct    | tion Addressing     | 28  |

|    | 2.6  | Special Instructior  | n Addressing        | 30  |

|    | 2.7  | Bit Instruction Add  | dressing            | 32  |

| 3. | Inst | ruction              |                     | 35  |

| 5. | 3.1  |                      | apter               |     |

|    | 3.2  |                      | S                   |     |

|    | 3.3  |                      | n                   |     |

|    |      |                      |                     |     |

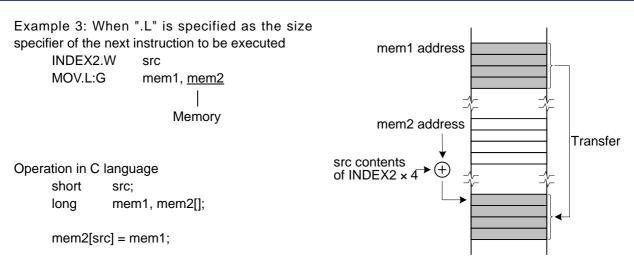

|      | 3.3.1  | INDEXB.size src                                                      |     |

|------|--------|----------------------------------------------------------------------|-----|

|      | 3.3.2  | INDEX1.size src                                                      |     |

|      | 3.3.3  | INDEX2.size src                                                      |     |

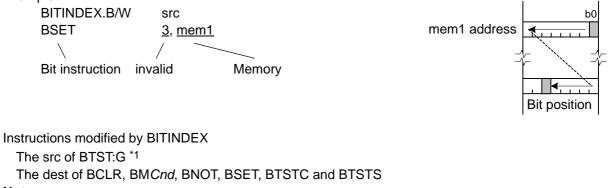

|      | 3.3.4  | BITINDEX.size src                                                    |     |

|      | 3.3.5  | Enabled Instruction List to Be Executed Next to INDEX Instruction    | 170 |

|      | 3.3.6  | Addressing Mode                                                      | 171 |

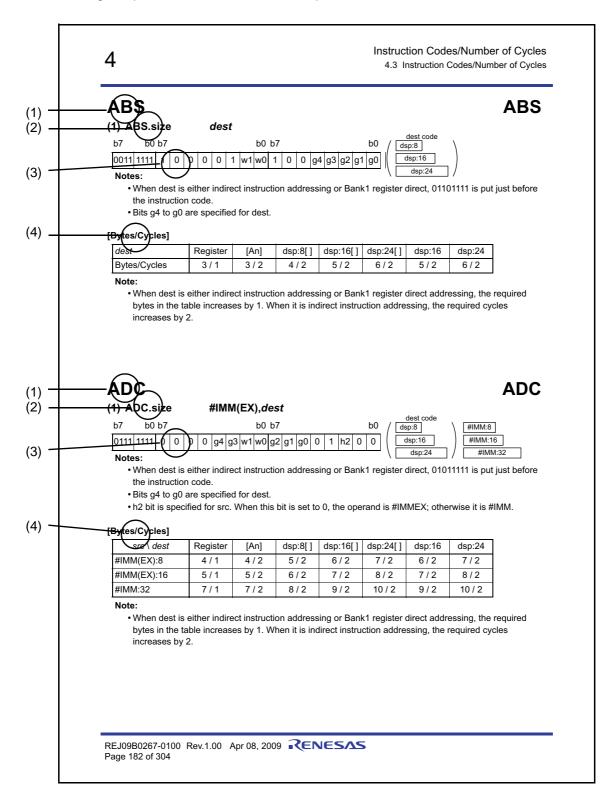

| 4.   | Instru | ction Codes/Number of Cycles                                         | 173 |

| 4.   | 1 G    | uide to This Chapter                                                 |     |

| 4.2  | 2 A    | ddressing                                                            | 176 |

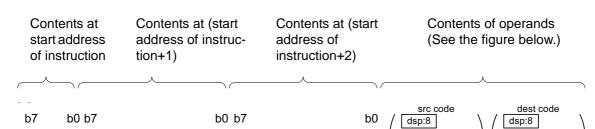

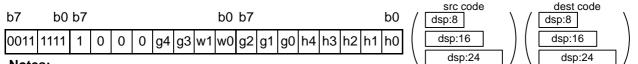

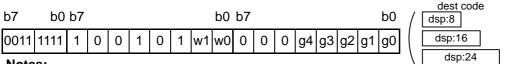

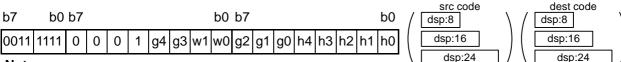

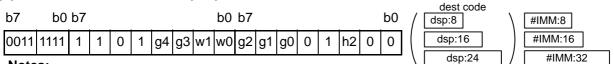

|      | 4.2.1  | Specifying Operation Length                                          | 176 |

|      | 4.2.2  | Specifying the Operand                                               | 176 |

|      | 4.2.3  | Specifying Conditions                                                |     |

| 4.3  | 3 In   | struction Codes/Number of Cycles                                     |     |

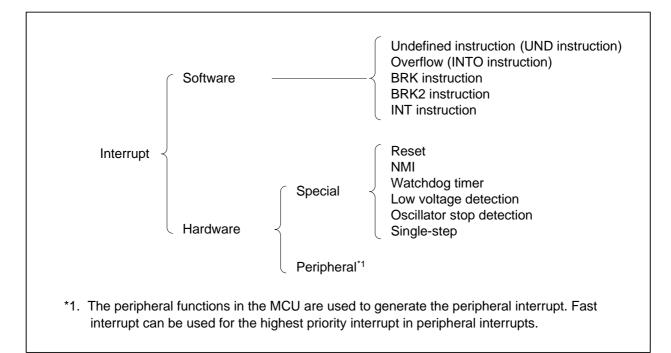

| 5.   | Interr | upts                                                                 | 287 |

| 5.   | 1 0    | verview                                                              |     |

|      | 5.1.1  | Interrupt Types                                                      |     |

|      | 5.1.2  | Software Interrupts                                                  |     |

|      | 5.1.3  | Hardware Interrupts                                                  |     |

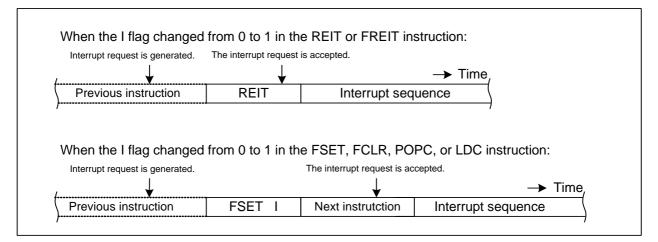

| 5.2  | 2 In   | terrupt Control                                                      |     |

|      | 5.2.1  | Interrupt Enable Flag (I Flag)                                       |     |

|      | 5.2.2  | Interrupt Request Bit                                                |     |

|      | 5.2.3  | Interrupt Request Level and Processor Interrupt Priority Level (IPL) |     |

|      | 5.2.4  | Rewrite the Interrupt Control Register                               |     |

| 5.   | 3 In   | terrupt Sequence                                                     |     |

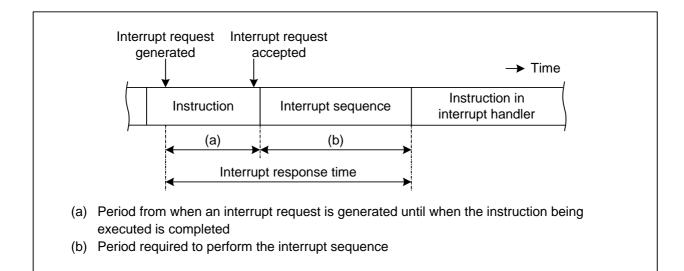

|      | 5.3.1  | Interrupt Response Time                                              |     |

|      | 5.3.2  | IPL After Interrupt Request Acceptance                               |     |

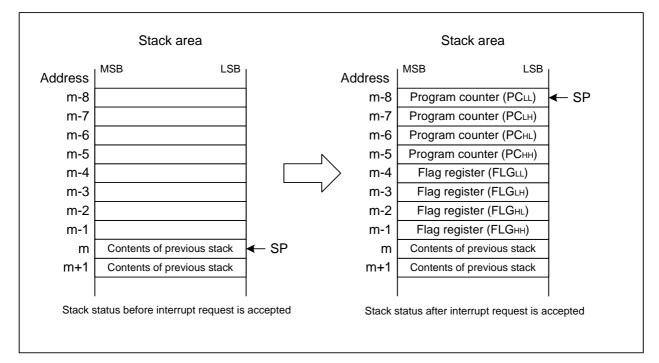

|      | 5.3.3  | Register Saving                                                      |     |

| 5.4  | 4 R    | egister Restoring                                                    |     |

| 5.   | 5 In   | terrupt Priority                                                     |     |

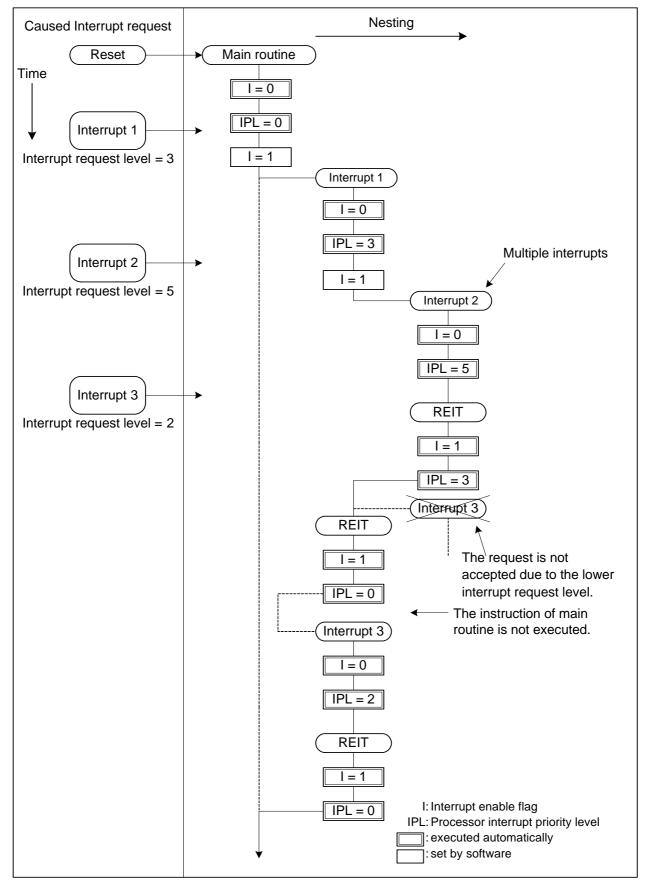

| 5.   | 6 M    | ultiple Interrupts                                                   |     |

| 5.   | 7 N    | otes on Interrupts                                                   |     |

| Inde | х      |                                                                      | 301 |

# R32C/100 SERIES INSTRUCTION SET

| Table C.1 | Instruction Set - Alphabetical | (1 / 5) |

|-----------|--------------------------------|---------|

|-----------|--------------------------------|---------|

| Mnemonic | Instruction Full Name                               | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|----------|-----------------------------------------------------|----------------------|----------------------------------------------------|

| ABS      | Absolute                                            | 42                   | 182                                                |

| ADC      | Add with Carry                                      | 43                   | 182                                                |

| ADCF     | Add Carry Flag                                      | 44                   | 183                                                |

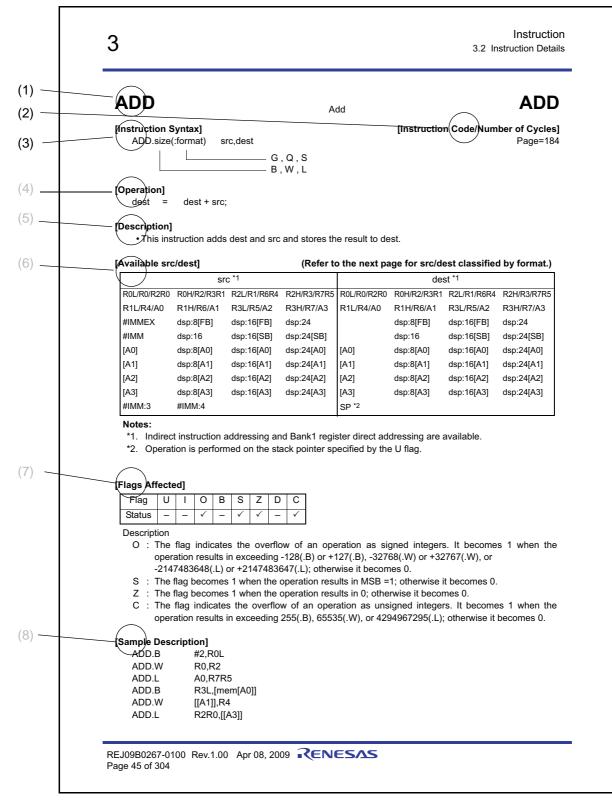

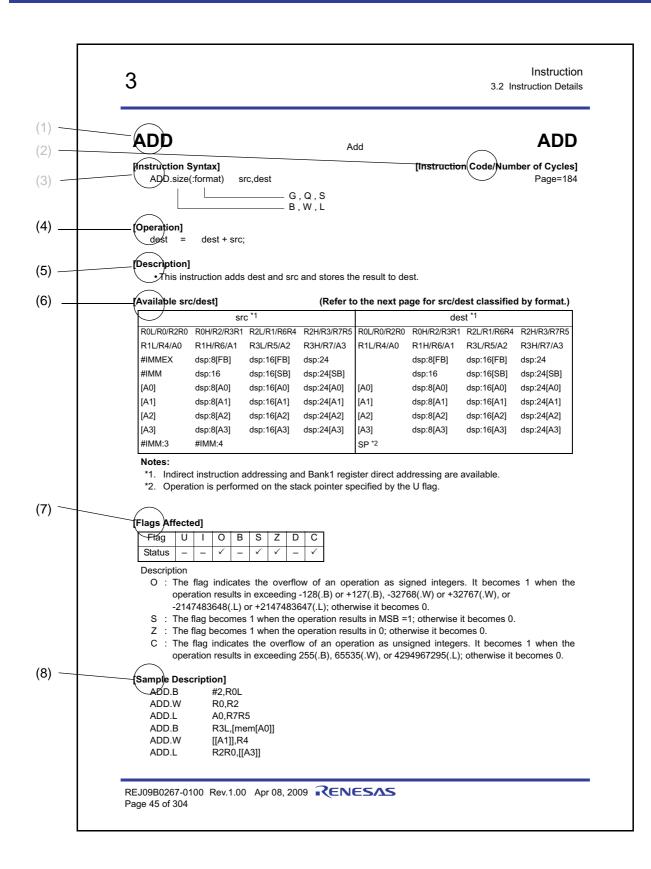

| ADD      | Add                                                 | 45                   | 184                                                |

| ADDF     | Add Floating-point                                  | 47                   | 187                                                |

| ADSF     | Add Sign Flag                                       | 48                   | 188                                                |

| AND      | And Logical                                         | 49                   | 189                                                |

| BCLR     | Clear a Bit                                         | 51                   | 191                                                |

| BITINDEX | Index next Bit Instruction                          | 52                   | 192                                                |

| BMCnd    | Move a Bit Conditionally (conditions listed below)  | 53                   | 192                                                |

| BMC      | Move a bit if the C flag is 1                       | 53                   | 192                                                |

| BMEQ     | Move a bit if equal                                 | 53                   | 192                                                |

| BMGE     | Move a bit if greater as signed integers or equal   | 53                   | 192                                                |

| BMGEU    | Move a bit if greater as unsigned integers or equal | 53                   | 192                                                |

| BMGT     | Move a bit if greater as signed integers            | 53                   | 192                                                |

| BMGTU    | Move a bit if greater as unsigned integers          | 53                   | 192                                                |

| BMLE     | Move a bit if less as signed integers or equal      | 53                   | 192                                                |

| BMLEU    | Move a bit if less as unsigned integers or equal    | 53                   | 192                                                |

| BMLT     | Move a bit if less as signed integers               | 53                   | 192                                                |

| BMLTU    | Move a bit if less as unsigned integers             | 53                   | 192                                                |

| BMN      | Move a bit if value is negative                     | 53                   | 192                                                |

| BMNC     | Move a bit if the C flag is 0                       | 53                   | 192                                                |

| BMNE     | Move a bit if not equal                             | 53                   | 192                                                |

| BMNO     | Move a bit if the O flag is 0                       | 53                   | 192                                                |

| BMNZ     | Move a bit if the Z flag is 0                       | 53                   | 192                                                |

| BMO      | Move a bit if the O flag is 1                       | 53                   | 192                                                |

| BMPZ     | Move a bit if value is positive or 0                | 53                   | 192                                                |

| BMZ      | Move a bit if the Z flag is 1                       | 53                   | 192                                                |

| BNOT     | Not a Bit                                           | 55                   | 193                                                |

| BRK      | Break                                               | 56                   | 193                                                |

| BRK2     | Break 2                                             | 57                   | 193                                                |

| BSET     | Set a Bit                                           | 58                   | 194                                                |

| BTST     | Test a Bit                                          | 59                   | 194                                                |

| BTSTC    | Test a Bit and Clear                                | 60                   | 195                                                |

| Mnemonic  | Instruction Full Name                         | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|-----------|-----------------------------------------------|----------------------|----------------------------------------------------|

| BTSTS     | Test a Bit and Set                            | 61                   | 196                                                |

| CLIP      | Clip                                          | 62                   | 196                                                |

| CMP       | Compare                                       | 63                   | 197                                                |

| CMPF      | Compare Floating-point                        | 65                   | 199                                                |

| CNVIF     | Convert Integer to Floating-point             | 66                   | 201                                                |

| DADC      | Add Decimal with Carry                        | 67                   | 203                                                |

| DADD      | Add Decimal                                   | 68                   | 205                                                |

| DEC       | Decrement                                     | 69                   | 206                                                |

| DIV       | Signed Divide                                 | 70                   | 207                                                |

| DIVF      | Divide Floating-point                         | 71                   | 209                                                |

| DIVU      | Unsigned Divide                               | 72                   | 211                                                |

| DIVX      | Signed Divide extra                           | 73                   | 213                                                |

| DSBB      | Subtract Decimal with Borrow                  | 74                   | 215                                                |

| DSUB      | Subtract Decimal                              | 75                   | 217                                                |

| EDIV      | Extended Signed Divide with Remainder         | 76                   | 219                                                |

| EDIVU     | Extended Unsigned Divide with Remainder       | 77                   | 220                                                |

| EDIVX     | Extended Signed Divide extra with Remainder   | 78                   | 221                                                |

| EMUL      | Extended Signed Multiply                      | 79                   | 222                                                |

| EMULU     | Extended Unsigned Multiply                    | 80                   | 223                                                |

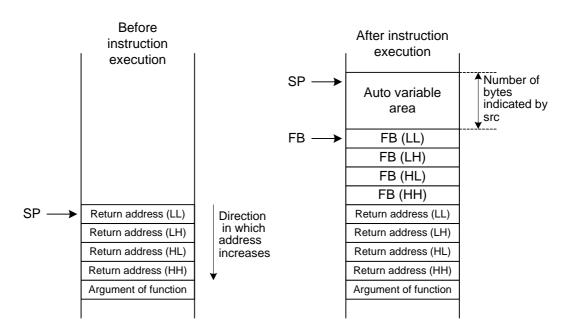

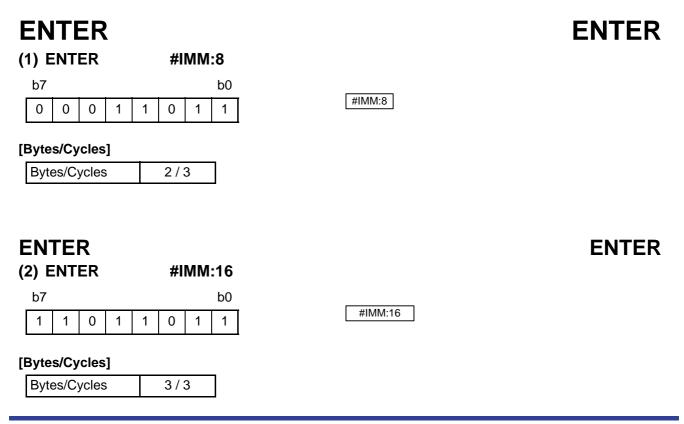

| ENTER     | Enter and Create Stack Frame                  | 81                   | 223                                                |

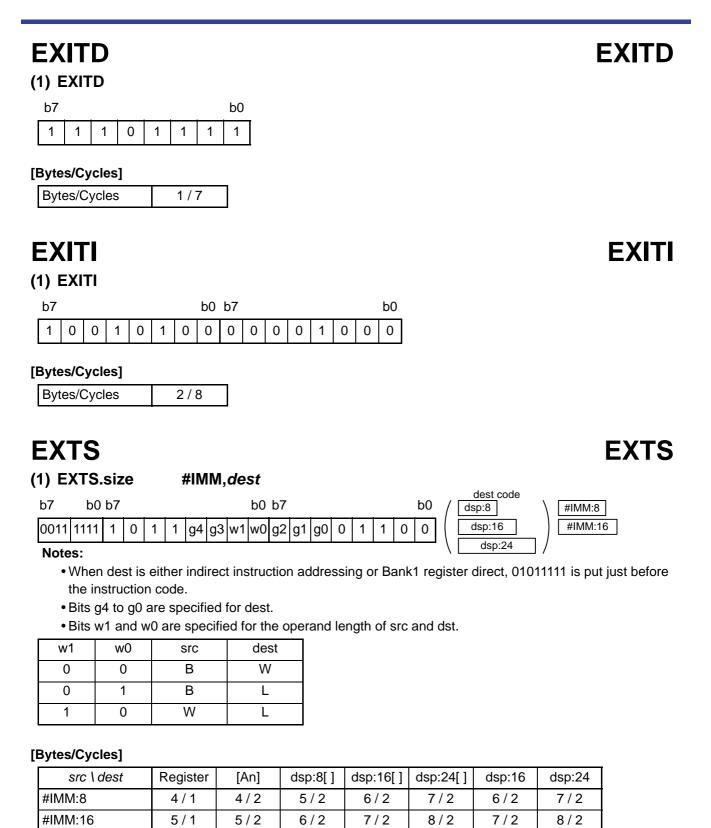

| EXITD     | Exit and Deallocate Stack Frame               | 82                   | 224                                                |

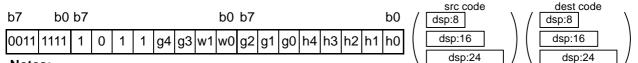

| EXITI     | Exit Interrupt and Deallocate Stack Frame     | 83                   | 224                                                |

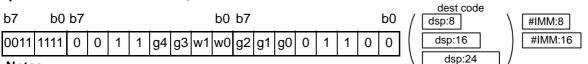

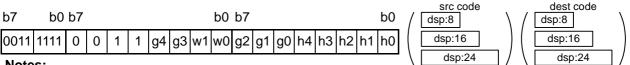

| EXTS      | Sign Extend                                   | 84                   | 224                                                |

| EXTZ      | Zero Extend                                   | 85                   | 226                                                |

| FCLR      | Set a Flag                                    | 87                   | 228                                                |

| FREIT     | Return from Fast Interrupt                    | 88                   | 228                                                |

| FSET      | Set a Flag                                    | 89                   | 229                                                |

| INC       | Increment                                     | 90                   | 229                                                |

| INDEXType | Index (types listed below)                    | 91                   | 230                                                |

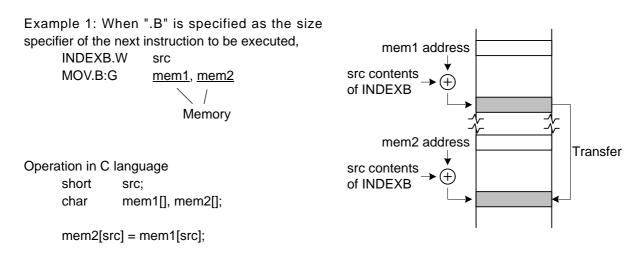

| INDEXB    | Add to the first and second operands          | 91                   | 231                                                |

| INDEX1    | Add to the first operand                      | 91                   | 230                                                |

| INDEX2    | Add to the second operand                     | 91                   | 230                                                |

| INT       | Interrupt                                     | 92                   | 231                                                |

| INTO      | Interrupt on Overflow                         | 93                   | 231                                                |

| JCnd      | Jump Conditionally (conditions listed below)  | 94                   | 232                                                |

| JC        | Jump if the C flag is 1                       | 94                   | 232                                                |

| JEQ       | Jump if equal                                 | 94                   | 232                                                |

| JGE       | Jump if greater as signed integers or equal   | 94                   | 232                                                |

| JGEU      | Jump if greater as unsigned integers or equal | 94                   | 232                                                |

#### Table C.1 Instruction Set - Alphabetical (2 / 5)

| Mnemonic | Instruction Full Name                      | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|----------|--------------------------------------------|----------------------|----------------------------------------------------|

| JGT      | Jump if greater as signed integers         | 94                   | 232                                                |

| JGTU     | Jump if greater as unsigned integers       | 94                   | 232                                                |

| JLE      | Jump if less as signed integers or equal   | 94                   | 232                                                |

| JLEU     | Jump if less as unsigned integers or equal | 94                   | 232                                                |

| JLT      | Jump if less as signed integers            | 94                   | 232                                                |

| JLTU     | Jump if less as unsigned integers          | 94                   | 232                                                |

| JN       | Jump if a negative value                   | 94                   | 232                                                |

| JNC      | Jump if the C flag is 0                    | 94                   | 232                                                |

| JNE      | Jump if not equal                          | 94                   | 232                                                |

| JNO      | Jump if the O flag is 0                    | 94                   | 232                                                |

| JNZ      | Jump if the Z flag is 0                    | 94                   | 232                                                |

| JO       | Jump if the O flag is 1                    | 94                   | 232                                                |

| JPZ      | Jump if a positive value or 0              | 94                   | 232                                                |

| JZ       | Jump if the Z flag is 1                    | 94                   | 232                                                |

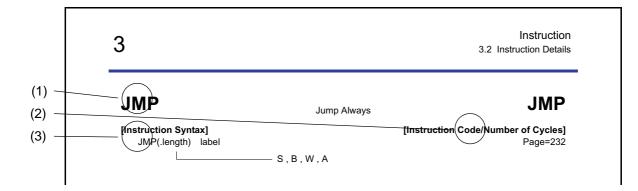

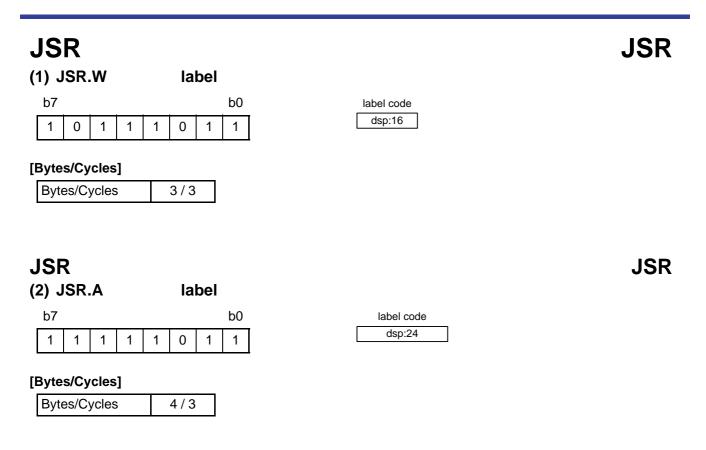

| JMP      | Jump Always                                | 95                   | 232                                                |

| JMPI     | Jump Indirectly                            | 96                   | 233                                                |

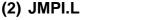

| JSR      | Jump to Subroutine                         | 97                   | 234                                                |

| JSRI     | Jump to Subroutine Indirectly              | 98                   | 234                                                |

| LDC      | Load into Control Register                 | 99                   | 235                                                |

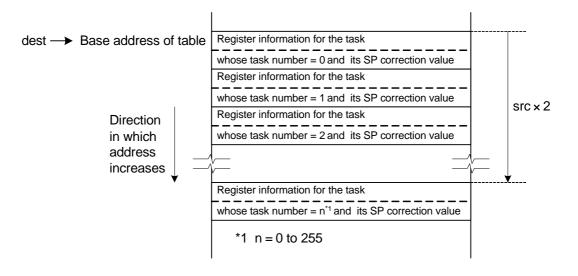

| LDCTX    | Load Context                               | 100                  | 236                                                |

| LDIPL    | Load Interrupt Priority Level              | 102                  | 237                                                |

| MAX      | Select Maximum Value                       | 103                  | 237                                                |

| MIN      | Select Minimum Value                       | 104                  | 239                                                |

| MOV      | Move                                       | 105                  | 241                                                |

| MOVA     | Move Effective Address                     | 108                  | 246                                                |

| MOVDir   | Move Nibble Data (directions listed below) | 109                  | 247                                                |

| MOVHH    | Move upper src to upper dest               | 109                  | 247                                                |

| MOVHL    | Move upper src to lower dest               | 109                  | 247                                                |

| MOVLH    | Move lower src to upper dest               | 109                  | 247                                                |

| MOVLL    | Move lower src to lower dest               | 109                  | 247                                                |

| MUL      | Signed Multiply                            | 111                  | 249                                                |

| MULF     | Multiply Floating-point                    | 112                  | 251                                                |

| MULU     | Unsigned Multiply                          | 113                  | 253                                                |

| MULX     | Signed Multiply and Round                  | 114                  | 255                                                |

| NEG      | Negate                                     | 116                  | 255                                                |

| NOP      | No Operation                               | 117                  | 256                                                |

| NOT      | Logical Complement                         | 118                  | 256                                                |

| OR       | Or Logical                                 | 119                  | 257                                                |

| POP      | Pop Data off the Stack                     | 120                  | 258                                                |

| POPC     | Pop Control Register off the Stack         | 121                  | 259                                                |

Table C.1

Instruction Set - Alphabetical (3 / 5)

| Mnemonic | Instruction Full Name                                   | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|----------|---------------------------------------------------------|----------------------|----------------------------------------------------|

| POPM     | Pop Registers off the Stack                             | 122                  | 259                                                |

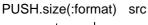

| PUSH     | Push Data on the Stack                                  | 123                  | 260                                                |

| PUSHA    | Push Effective Address on the Stack                     | 125                  | 262                                                |

| PUSHC    | Push Control Register on the Stack                      | 126                  | 262                                                |

| PUSHM    | Push Registers on the Stack                             | 127                  | 262                                                |

| REIT     | Return from Interrupt                                   | 128                  | 263                                                |

| RMPA     | Repeat Multiply and Accumulation                        | 129                  | 263                                                |

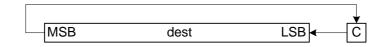

| ROLC     | Rotate the bits to the Left with Carry                  | 130                  | 263                                                |

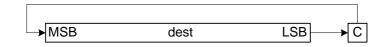

| RORC     | Rotate the bits to the Right with Carry                 | 131                  | 264                                                |

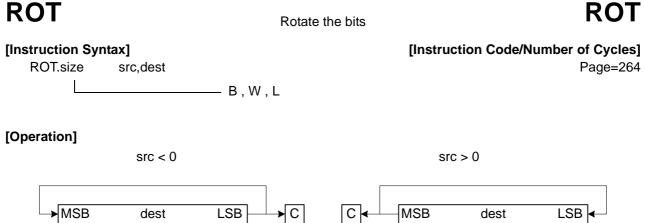

| ROT      | Rotate the bits                                         | 132                  | 264                                                |

| ROUND    | Round Floating-point to Integer                         | 133                  | 265                                                |

| RTS      | Return from Subroutine                                  | 134                  | 266                                                |

| SBB      | Subtract with Borrow                                    | 135                  | 267                                                |

| SCCnd    | Store Condition Conditionally (conditions listed below) | 136                  | 268                                                |

| SCC      | Store 1 if the C flag is 1                              | 136                  | 268                                                |

| SCEQ     | Store 1 if equal                                        | 136                  | 268                                                |

| SCGE     | Store 1 if greater as signed integers or equal          | 136                  | 268                                                |

| SCGEU    | Store 1 if greater as unsigned integers or equal        | 136                  | 268                                                |

| SCGT     | Store 1 if greater as signed integers                   | 136                  | 268                                                |

| SCGTU    | Store1 if greater as unsigned integers                  | 136                  | 268                                                |

| SCLE     | Store 1 if less as signed integers or equal             | 136                  | 268                                                |

| SCLEU    | Store 1 if less as unsigned integers or equal           | 136                  | 268                                                |

| SCLT     | Store 1 if less as signed integers                      | 136                  | 268                                                |

| SCLTU    | Store 1 if less as unsigned integers                    | 136                  | 268                                                |

| SCN      | Store 1 if a negative value                             | 136                  | 268                                                |

| SCNC     | Store 1 if the C flag is 0                              | 136                  | 268                                                |

| SCNE     | Store 1 if not equal                                    | 136                  | 268                                                |

| SCNO     | Store 1 if the O flag is 0                              | 136                  | 268                                                |

| SCNZ     | Store 1 if the Z flag is 0                              | 136                  | 268                                                |

| SCO      | Store 1 if the O flag is 1                              | 136                  | 268                                                |

| SCPZ     | Store 1 if a positive value or 0                        | 136                  | 268                                                |

| SCZ      | Store 1 if the Z flag is 1                              | 136                  | 268                                                |

| SCMPU    | Compare Strings until not equal                         | 138                  | 269                                                |

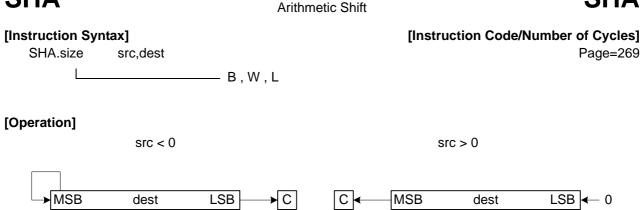

| SHA      | Arithmetic Shift                                        | 139                  | 269                                                |

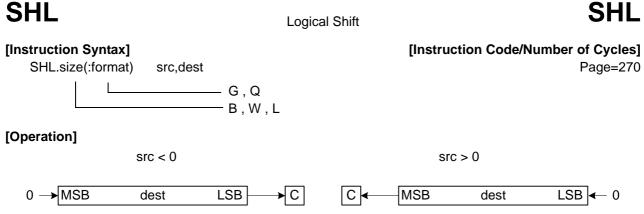

| SHL      | Logical Shift                                           | 140                  | 270                                                |

| SIN      | Input Strings                                           | 142                  | 272                                                |

| SMOVB    | Move Strings Backward                                   | 143                  | 272                                                |

| SMOVF    | Move Strings Forward                                    | 144                  | 272                                                |

Table C.1

Instruction Set - Alphabetical (4 / 5)

| Mnemonic | Instruction Full Name              | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|----------|------------------------------------|----------------------|----------------------------------------------------|

| SMOVU    | Move Strings While Unequal to Zero | 145                  | 273                                                |

| SOUT     | Output Strings                     | 146                  | 273                                                |

| SSTR     | Store Strings                      | 147                  | 274                                                |

| STC      | Store from Control Register        | 148                  | 274                                                |

| STCTX    | Store Context                      | 149                  | 275                                                |

| STNZ     | Store on Not Zero                  | 151                  | 276                                                |

| STOP     | Stop                               | 152                  | 276                                                |

| STZ      | Store on Zero                      | 153                  | 277                                                |

| STZX     | Store according to Zero Flag       | 154                  | 277                                                |

| SUB      | Subtract                           | 155                  | 278                                                |

| SUBF     | Subtract Floating-point            | 156                  | 280                                                |

| SUNTIL   | Search Equal String                | 157                  | 281                                                |

| SWHILE   | Search Unequal String              | 158                  | 282                                                |

| TST      | Test Logical                       | 159                  | 282                                                |

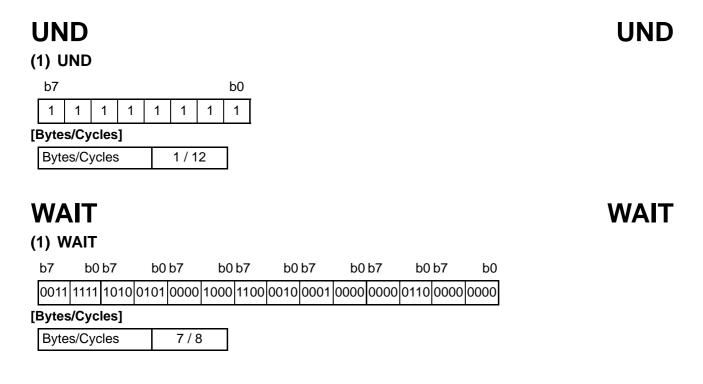

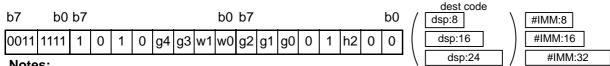

| UND      | Undefined Instruction Interrupt    | 160                  | 283                                                |

| WAIT     | Wait                               | 161                  | 283                                                |

| XCHG     | Exchange                           | 162                  | 284                                                |

| XOR      | Exclusive Or Logical               | 163                  | 284                                                |

| Table C.1 | Instruction Set - Alphabetical (5 / 5) |

|-----------|----------------------------------------|

|           |                                        |

| Function   | Mnemonic | Instruction Full Name                   | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|------------|----------|-----------------------------------------|----------------------|----------------------------------------------------|

| Move       | MOV      | Move                                    | 105                  | 241                                                |

|            | MOVA     | Move Effective Address                  | 108                  | 246                                                |

|            | MOVDir   | Move Nibble Data                        | 109                  | 247                                                |

|            | POP      | Pop Data off the Stack                  | 120                  | 258                                                |

|            | РОРМ     | Pop Registers off the Stack             | 122                  | 259                                                |

|            | PUSH     | Push Data on the Stack                  | 123                  | 260                                                |

|            | PUSHA    | Push Effective Address on the<br>Stack  | 125                  | 262                                                |

|            | PUSHM    | Push Registers on the Stack             | 127                  | 262                                                |

|            | STNZ     | Store on Not Zero                       | 151                  | 276                                                |

|            | STZ      | Store on Zero                           | 153                  | 277                                                |

|            | STZX     | Store according to Zero Flag            | 154                  | 277                                                |

|            | XCHG     | Exchange                                | 162                  | 284                                                |

| Bit pro-   | BCLR     | Clear a Bit                             | 51                   | 191                                                |

| cessing    | BITINDEX | Index next Bit Instruction              | 52                   | 192                                                |

|            | BMCnd    | Move a Bit Conditionally                | 53                   | 192                                                |

|            | BNOT     | Not a Bit                               | 55                   | 193                                                |

|            | BSET     | Set a Bit                               | 58                   | 194                                                |

|            | BTST     | Test a Bit                              | 59                   | 194                                                |

|            | BTSTC    | Test a Bit and Clear                    | 60                   | 195                                                |

|            | BTSTS    | Test a Bit and Set                      | 61                   | 196                                                |

| Shift      | ROLC     | Rotate the bits to the Left with Carry  | 130                  | 263                                                |

|            | RORC     | Rotate the bits to the Right with Carry | 131                  | 264                                                |

|            | ROT      | Rotate the bits                         | 132                  | 264                                                |

|            | SHA      | Arithmetic Shift                        | 139                  | 269                                                |

|            | SHL      | Logical Shift                           | 140                  | 270                                                |

| Arithmetic | ABS      | Absolute                                | 42                   | 182                                                |

| operation  | ADC      | Add with Carry                          | 43                   | 182                                                |

|            | ADCF     | Add Carry Flag                          | 44                   | 183                                                |

|            | ADD      | Add                                     | 45                   | 184                                                |

|            | ADSF     | Add Sign Flag                           | 48                   | 188                                                |

|            | CLIP     | Clip                                    | 62                   | 196                                                |

|            | CMP      | Compare                                 | 63                   | 197                                                |

|            | DEC      | Decrement                               | 69                   | 206                                                |

|            | DIV      | Signed Divide                           | 70                   | 207                                                |

|            | DIVU     | Unsigned Divide                         | 72                   | 211                                                |

Table C.2

Instruction Set - Functional (1 / 3)

| Function                        | Mnemonic | Instruction Full Name                       | Page for<br>Function | Page for Instruction<br>Codes/<br>Number of Cycles |

|---------------------------------|----------|---------------------------------------------|----------------------|----------------------------------------------------|

| Arithmetic                      | DIVX     | Signed Divide extra                         | 73                   | 213                                                |

| operation                       | EDIV     | Extended Signed Divide with Remainder       | 76                   | 219                                                |

|                                 | EDIVU    | Extended Unsigned Divide with Remainder     | 77                   | 220                                                |

|                                 | EDIVX    | Extended Signed Divide extra with Remainder | 78                   | 221                                                |

|                                 | EMUL     | Extended Signed Multiply                    | 79                   | 222                                                |

|                                 | EMULU    | Extended Unsigned Multiply                  | 80                   | 223                                                |

|                                 | EXTS     | Sign Extend                                 | 84                   | 224                                                |

|                                 | EXTZ     | Zero Extend                                 | 85                   | 226                                                |

|                                 | INC      | Increment                                   | 90                   | 229                                                |

|                                 | MAX      | Select Maximum Value                        | 103                  | 237                                                |

|                                 | MIN      | Select Minimum Value                        | 104                  | 239                                                |

|                                 | MUL      | Signed Multiply                             | 111                  | 249                                                |

|                                 | MULU     | Unsigned Multiply                           | 113                  | 253                                                |

|                                 | MULX     | Signed Multiply and Round                   | 114                  | 255                                                |

|                                 | NEG      | Negate                                      | 116                  | 255                                                |

|                                 | SBB      | Subtract with Borrow                        | 135                  | 267                                                |

|                                 | SUB      | Subtract                                    | 155                  | 278                                                |

| Decimal                         | DADC     | Add Decimal with Carry                      | 67                   | 203                                                |

| operation                       | DADD     | Add Decimal                                 | 68                   | 205                                                |

|                                 | DSBB     | Subtract Decimal with Borrow                | 74                   | 215                                                |

|                                 | DSUB     | Subtract Decimal                            | 75                   | 217                                                |

| Froating                        | ADDF     | Add Floating-point                          | 47                   | 187                                                |

| point oper-                     | CMPF     | Compare Floating-point                      | 65                   | 199                                                |

| ation                           | CNVIF    | Convert Integer to Floating-point           | 66                   | 201                                                |