## RC210xx

This document describes the functional description, register organization, and byte addresses of the RC210xx. Detailed register definitions can be located by following the links in the document.

## Contents

|                                                                |           |

|----------------------------------------------------------------|-----------|

| <b>1. Functional Description</b> .....                         | <b>3</b>  |

| 1.1 Power-Up, Configuration, and Serial Interfaces .....       | 3         |

| 1.2 Input Clocks .....                                         | 3         |

| 1.2.1 Crystal/Reference Input .....                            | 3         |

| 1.2.2 Clock Inputs .....                                       | 3         |

| 1.3 APLL .....                                                 | 4         |

| 1.3.1 APLL Lock Detector .....                                 | 4         |

| 1.4 Output Dividers .....                                      | 4         |

| 1.4.1 Integer Output Dividers .....                            | 4         |

| 1.4.2 Fractional Output Dividers .....                         | 4         |

| 1.5 Clock Outputs .....                                        | 5         |

| 1.5.1 Output Types .....                                       | 5         |

| 1.5.2 Output Banks .....                                       | 6         |

| 1.6 Output Enable Control .....                                | 6         |

| <b>2. Serial Interfaces</b> .....                              | <b>7</b>  |

| 2.1 1-Byte and 2-Byte Offset Mode .....                        | 7         |

| <b>3. I2C Slave</b> .....                                      | <b>8</b>  |

| 3.1 1-Byte Offset Mode .....                                   | 8         |

| 3.2 2-Byte Offset Mode .....                                   | 8         |

| <b>4. SPI Slave</b> .....                                      | <b>9</b>  |

| <b>5. SMBus Slave</b> .....                                    | <b>10</b> |

| 5.1 SMBus 1-Byte/2-Byte Offset Mode Programming Examples ..... | 10        |

| <b>6. Example of Programming Process</b> .....                 | <b>11</b> |

| 6.1 Getting Register Value from rbs Setting File .....         | 11        |

| 6.2 Example of I2C 1-Byte Offset Mode Programming .....        | 11        |

| 6.3 Example of I2C 2-Byte Offset Mode Programming .....        | 12        |

| <b>7. Example of Changing Output Frequency</b> .....           | <b>13</b> |

| 7.1 Output Frequency Calculation .....                         | 13        |

| 7.2 Feedback Divider .....                                     | 14        |

| 7.3 Integer Output Divider .....                               | 14        |

| 7.4 Fractional Output Dividers .....                           | 15        |

| <b>8. Example of Device Programming with the Driver</b> .....  | <b>16</b> |

| 8.1 Example of Python Code .....                               | 16        |

| 8.2 Example of DOS Batch File .....                            | 16        |

| <b>9. Register Organization</b> .....                          | <b>17</b> |

| 9.1 Overview .....                                             | 17        |

| 9.2 Register Block Offsets .....                               | 17        |

| 9.3 Register Offsets .....                                     | 18        |

---

|            |                                    |           |

|------------|------------------------------------|-----------|

| 9.3.1      | Global Address Map                 | 18        |

| 9.3.2      | SSI Address Map                    | 18        |

| 9.3.3      | Crystal Address Map                | 18        |

| 9.3.4      | Clock Input Address Map            | 19        |

| 9.3.5      | LOS Monitor Address Map            | 19        |

| 9.3.6      | APLL Address Map                   | 19        |

| 9.3.7      | IOD Address Map                    | 20        |

| 9.3.8      | FOD Address Map                    | 20        |

| 9.3.9      | SSC Address Map                    | 20        |

| 9.3.10     | Output Bank Address Map            | 20        |

| 9.3.11     | Clock Output Driver Address Map    | 20        |

| 9.3.12     | GPI Address Map                    | 20        |

| 9.3.13     | GPIO Address Map                   | 21        |

| 9.3.14     | Interrupt Address Map              | 21        |

| <b>10.</b> | <b>Physical Register Addresses</b> | <b>21</b> |

| 10.1       | Global Block                       | 21        |

| 10.2       | SSI Block                          | 22        |

| 10.3       | XO Block                           | 22        |

| 10.4       | CLKIN Block                        | 22        |

| 10.5       | LOSMON Block                       | 23        |

| 10.6       | APLL Block                         | 24        |

| 10.7       | IOD Block                          | 25        |

| 10.8       | FOD Block                          | 26        |

| 10.9       | OUT Block                          | 27        |

| 10.10      | BANK Block                         | 28        |

| 10.11      | GPI Block                          | 28        |

| 10.12      | GPIO Block                         | 28        |

| 10.13      | SSC Block                          | 29        |

| 10.14      | INT Block                          | 29        |

| <b>11.</b> | <b>Register Descriptions</b>       | <b>30</b> |

| 11.1       | Global Registers                   | 30        |

| 11.2       | SSI Registers                      | 39        |

| 11.3       | XO Register                        | 42        |

| 11.4       | CLKIN Register                     | 43        |

| 11.5       | LOSMON Registers                   | 44        |

| 11.6       | FREQMON Registers                  | 47        |

| 11.7       | TDC APLL Registers                 | 48        |

| 11.8       | APLL Registers                     | 50        |

| 11.9       | IOD Registers                      | 61        |

| 11.10      | FOD Registers                      | 63        |

| 11.11      | SSC Register                       | 65        |

| 11.12      | BANK Register                      | 66        |

| 11.13      | OUT Registers                      | 67        |

| 11.14      | GPI Registers                      | 69        |

| 11.15      | GPIO Registers                     | 71        |

| 11.16      | EEPROM Registers                   | 73        |

| 11.17      | INT Registers                      | 77        |

| <b>12.</b> | <b>Revision History</b>            | <b>80</b> |

# 1. Functional Description

The RC210xx is a small-form factor, fully integrated, low-power, high-performance frequency synthesizer providing excellent PCIe and Ethernet phase jitter, while covering a wide range of output frequencies up to 650MHz. It can simultaneously provide low phase jitter non-spreading clocks for Ethernet and storage applications, while providing spread-spectrum PCIe Gen6 clocks.

The following sections provide an overview of the RC210xx.

## 1.1 Power-Up, Configuration, and Serial Interfaces

The RC210xx can be powered up and configured in three ways:

- From internal non-volatile memory using OTP user configurations (UserCfgs)

- From its slave serial interface

- From an external I2C EEPROM

The power-up sequence loads one of up to 27 *internal* UserCfgs from OTP. This configuration can be selected via external GPIO pins or by programming a field to select the default configuration to load. This is useful when external GPIO are not used to select the UserCfg at power-up. After the device is powered up, the slave serial interface can be used to select preprogrammed UserCfgs or load entirely new UserCfgs stored outside the device.

The RC210xx supports three slave serial interfaces: I2C, SPI, SMBUS, and one serial master interface (I2C).

These interfaces share the same pins so only one is available at a time. The I2C master interface that is used to load UserCfgs from an external I2C EEPROM is only active after loading an OTP UserCfg that indicates a further load from external I2C EEPROM. An external master (I2C, SPI, SMBUS) can be used to access internal registers. If the slave serial port is configured as SPI then loading from external EEPROM is not available.

## 1.2 Input Clocks

The RC210xx supports one crystal/reference input and up to two differential or four single-ended clock inputs.

### 1.2.1 Crystal/Reference Input

The crystal input supports crystal frequencies of 8MHz to 80MHz. It has programmable internal load capacitors to support crystals with  $CL = 6\text{pF}$  to  $12\text{pF}$ . Internal crystal variants of RC210xx support a trim value in OTP that can be set during ATE to compensate for initial frequency offset of the internal crystal. The crystal input supports being overdriven with a clipped sine-wave TCXO with 0.8VPP signal.

If an external square wave clock is used to drive the `XIN_REFIN` pin, the default is amplitude limit is 1.2V. If `sel_ib_xo` is set to 0 and `xo_ib_cmos_sel` is set to 1 amplitude limitations are determined by the `VDDX` supply rail.

The crystal input can be overdriven with differential or single-ended inputs with proper external terminations. The supported frequency range is same as reference clock inputs:

- 1kHz to 650MHz in differential mode

- 1kHz to 200MHz in single-ended mode

An available LOS monitor detects the loss of signal on crystal input.

### 1.2.2 Clock Inputs

There are two differential clock inputs that support LVDS, HCSL, or single-ended CMOS logic levels without external terminations. LVPECL or CML clock inputs can be supported with external terminations and/or AC coupling. Internal terminations are available for both HCSL and LVDS logic levels. Additionally, HCSL input terminations support both 100ohm and 85ohm operating environments.

If the `cmos_sel` register bit is set to single-ended type, the differential inputs turn into two single-ended inputs. `CLKIN0` drives `clkin0` internally, `CLKIN0b` drives `clkin1` internally. `CLKIN1` drives `clkin2` internally, and `CLKIN1b`

drives clkin3 internally. If set to differential type, CLKIN0/CLKIN0b pair drives clkin0, while CLKIN1/CLKIN1b pair drives clkin2. Internal biasing is available for AC-coupled applications. The two clock inputs can be left floating when unused. An available LOS monitor detects the loss of signal on crystal input. The LOS status is stored in register bits and can also be steered to a GPIO pin.

## 1.3 APLL

The APLL is fractional LC-VCO based PLL with an operating range from 9.5GHz to 10.7GHz. Any of the available input clocks can be selected to drive the APLL, and the input clock can be frequency doubled for increased performance. The APLL is temperature compensated for the utmost frequency stability. For synchronous, deterministic requirements, the APLL also supports ZDB mode where CLKIN0 is used for the feedback input.

### 1.3.1 APLL Lock Detector

The APLL lock detector indicates whether the APLL is locked to a functioning crystal or reference input by monitoring the phase errors. Lock status can be sent on to a GPIO pin and register [apll\\_lock\\_sts](#). The falling edge of [apll\\_lock\\_sts](#) sets [apll\\_lol](#) event sticky bit. The [apll\\_lol](#) event also increments a 7-bit loss of lock counter that starts from power on. The counter values represents the total number of loss of lock since power on and can be read back from register [apll\\_lol\\_cnt](#).

## 1.4 Output Dividers

The RC210xx provides four integer and three fractional output dividers.

### 1.4.1 Integer Output Dividers

All four IODs are identical and use a 25-bit divider to provide output frequencies from 1kHz to 650MHz derived from the VCO clock. Changing IOD values results in an immediate change to the new frequency. Glitch-less squelch and release of the IOD clock is supported with an [iod\\_squelch](#) bit. When enabled, this mimics a gapped clock behavior when an IOD frequency is changed.

### 1.4.2 Fractional Output Dividers

There are three fractional output dividers (FOD). Each FOD can divide down the VCO clock to provide frequencies of 1kHz to 650MHz. Each FOD is implemented in two stages. The first stage is an 8-bit fractional divider with Digital Control Delay (DCD) correction followed by a divide-by-2. The DCD FOD allows a divide down of the VCO clock from 30MHz to 657MHz. The FOD's second stage divider is a 17-bit integer divider with minimum divide ratio of 4. This allows output frequencies lower than 30MHz. For output frequencies above 30MHz, this second-stage divider may be bypassed.

#### 1.4.2.1 Spread-Spectrum Clocking (SSC)

FOD0 and FOD1 support spread-spectrum clocking.

If spreading is enabled by setting [ssc\\_en](#) to 1, the spread-spectrum engine generates a triangular frequency modulation on to FOD's divider ratio. The modulation amplitude is programmable in [ssc\\_ampl](#) register fields. The modulation can be programmed to either down spread or center spread in register [ssc\\_mode](#). The peak-to-peak amplitude is two times of [ssc\\_ampl](#) for center spreading, and one [ssc\\_ampl](#) for down spreading. The supported modulation frequency is from 30kHz to 63kHz. It can be set by programming register [ssc\\_step](#) based on the equations provided in the register description.

When turning off spread, it stops when the current spreading cycle's modulation returns to zero.

If FOD0 and FOD1 SSC are programmed to the same modulation frequency, the register bit [ssc\\_share](#) can be set to 1 to ensure that SSC for FOD0 and FOD1 are in phase. The modulation amplitude and mode (down or center spread) can be set differently. The spread engine of FOD0 will act as the master for the spread engine of FOD1 with respect to synchronization. The zero crossing of the spread triangles is where the synchronization occurs. If the center spread is used on FOD0, then the zero crossing of the upwards frequency ramp of the triangle is the synchronization point. When [ssc\\_share](#) is set to 1, then FOD1 [ssc\\_en](#) must be set to 1 before FOD0 [ssc\\_en](#) is set

to 1 since FOD1 SSC will start when FOD0 [ssc\\_en](#) is set to 1. This restriction does not apply when loading the device configuration from OTP/EEPROM on startup, but does apply if dynamically changing these settings later through a dynamic configuration load from the OTP/EEPROM, or by writing registers from the serial interface.

The minimum output frequency that can be spread is 33MHz. A spreading output clock meets the PCIe Gen1 to Gen6 standard at 100MHz.

### 1.4.2.2 Sync and Phase Adjustment

Each FOD can adjust its output clock phase with a step size of 1/4 VCO period up to about  $\pm 20$ ns. The amount of phase adjustment is programmed in register [fod\\_phase](#). The adjustment can be of either positive or negative directions. The phase adjustment can be applied immediately if the [fod\\_ph\\_adj\\_now](#) bit is set to 1, and/or it will be applied after each time the divider is synchronized if [fod\\_ph\\_adj\\_post\\_sync](#) is set to 1.

IOD phase adjustment is same as, or maybe mimics, FOD phase adjustment but with a step size of one VCO period. The amount of phase adjustment is programmed in register [iod\\_phase](#). The phase adjustment can be applied immediately if the [iod\\_ph\\_adj\\_now](#) bit is set to 1, and/or it will be applied after each time the divider is synchronized if [iod\\_ph\\_adj\\_post\\_sync](#) is set to 1.

There are two sync groups, group0 and group1. An FOD or IOD can be assigned to either group or none by [fod\\_sync\\_group](#) or [iod\\_sync\\_group](#), respectively. The dividers in the same group can be re-synchronized together after any one of them is re-programmed by writing 1 to [od\\_grp0\\_sync](#) or [od\\_grp1\\_sync](#). To disable all clock outputs sourced from the dividers belonging to sync group 0 or 1 prior to re-programming until re-synchronization completes, first write 1 to [clr\\_grp0\\_oe](#) or [clr\\_grp1\\_oe](#). If no divider exists in neither group then it will not re-synchronize.

Upon power-up, after OTP has been loaded and VCO calibration completes and APPLL gets locked, a sync pulse is generated automatically to all dividers including FODs, IODs, that are assigned to sync group 0 or 1.

A sync pulse can also be initiated by writing 1 to register [divider\\_sync](#) to synchronize all dividers assigned to group 0 and 1, or [od\\_grp0\\_sync](#) and [od\\_grp1\\_sync](#) can be used to synchronize only the dividers assigned to each group.

Writing the [apll\\_reinit](#) bit causes the power-up sequence to restart from the VCO calibration step, which will synchronize the dividers after the APPLL locks.

### 1.4.2.3 Numerically Controlled Oscillator (NCO) Mode

In NCO mode, each FOD can adjust its output clock frequency with a step size of  $1/2^{34}$  or 58.21ppt, and is based on incrementing the numerator while holding the 34-b denominator at a fixed value. This frequency change at the output clock is gradual and without glitches.

## 1.5 Clock Outputs

The RC210xx supports up to 12 differential or 24 single-ended clock outputs, or any combination of differential and single-ended clock outputs. Each differential clock output can be programmed as two single-ended clock outputs.

### 1.5.1 Output Types

Differential outputs can be set to 85ohm HCSL, 100ohm HCSL, or LVDS. The HCSL output types are low-power push-pull HCSL (LPHCSL) with integrated terminations. They do not require external terminations to drive standard HCSL inputs, such as those found in PCIe applications. HCSL outputs have programmable output swing and HCSL outputs also have two slew rate settings (2V/ns to 4V/ns and 3V/ns to 5V/ns). LVDS outputs require only a 100ohm resistor between the true and complement inputs of the clock input being driven. Both LVDS and HCSL provide output swing levels that are compatible with LVPECL and CML with external AC coupling.

If set to single-ended mode, the output pair can drive both pins. If both pins are enabled, they can be in phase or inverted phase. The single-ended outputs support CMOS swings of 1.8V, 2.5V, or 3.3V as determined by their VDDO voltage.

### 1.5.2 Output Banks

The RC210xx maps the internal and external frequency sources to output banks that can be programmed in register `output_bank_src`, according to the following table. There are up to 12 clock outputs arranged in seven output banks. Each bank sits on its own VDDO (each VDDO also supplies an IOD or FOD as listed below).

Table 1. Output Bank Source Mapping

| output_bank_src | Bank 0 | Bank 1 | Bank 2   | Bank 3   | Bank 4   | Bank 5    | Bank 6 |  |  |  |  |  |  |  |

|-----------------|--------|--------|----------|----------|----------|-----------|--------|--|--|--|--|--|--|--|

|                 | OUT0   | OUT1   | OUT[2:3] | OUT[4:7] | OUT[8:9] | OUT10     | OUT11  |  |  |  |  |  |  |  |

| 0x0             | IOD0   |        | N/A      |          | CLKIN1   |           |        |  |  |  |  |  |  |  |

| 0x1             | IOD1   |        |          | N/A      |          | XIN_REFIN | N/A    |  |  |  |  |  |  |  |

| 0x2             | N/A    |        |          | IOD2     |          |           |        |  |  |  |  |  |  |  |

| 0x3             | N/A    |        |          |          | IOD3     |           |        |  |  |  |  |  |  |  |

| 0x4             | FOD0   |        |          | N/A      |          |           |        |  |  |  |  |  |  |  |

| 0x5             | FOD1   |        |          |          |          |           |        |  |  |  |  |  |  |  |

| 0x6             | N/A    |        | FOD2     |          |          |           |        |  |  |  |  |  |  |  |

| 0x7             | N/A    |        |          | CLKIN0   |          |           |        |  |  |  |  |  |  |  |

### 1.6 Output Enable Control

During the power-up sequence, the clock output drivers are tri-stated until the power supplies have stabilized, then both OUTx and OUTxb are held low. After the OTP configuration load completes, the clock output drivers can be enabled or held disabled until the APLL lock according to the setting of `out_startup`. This behavior can be overridden by setting `out_dis_group` to 0x7.

After power-up, the clock output driver is then enabled, either by setting the corresponding `out_dis` register bit or by the designated OE pin, if assigned to an OE group. The output driver is enabled when both the register bit and the OE pin are active. If configured in CMOS mode, OUTx and OUTxb can be enabled or disabled individually through `out_prog3` and `out_prog2`.

There are five OE groups, each output driver can optionally be assigned to a OE group in register `out_dis_group`. A GPIO or GPIO pin can be assigned as OE pin to a OE group in register `gpi_func` or `gpio_func` or can also be assigned as a global OE (GOE) pin with the `goe` register bit.

## 2. Serial Interfaces

The RC210xx can be configured in three ways:

- From internal non-volatile memory using OTP user configurations

- From its slave serial interface and program by a master device

- From an external I2C EEPROM. The device will become master at power-up and load data from I2C EEPROM.

The RC210xx supports three slave serial interfaces: I2C, SPI, and SMBUS. The interface type is selected by the [ssi\\_enable](#) (0x0026[1:0]) register field. If OTP is not programmed, the device powers up in I2C 1-byte offset mode.

These serial interfaces share the same pins so only one is available at a time. The I2C master interface that is used to load User Configurations from an external I2C EEPROM is only active after loading an OTP Configuration with EEPROM function enable. An external master (I2C, SPI, SMBUS) can be used to access internal registers after power-up and the configuration load process is completed.

### 2.1 1-Byte and 2-Byte Offset Mode

The RC210xx has a 912-byte register memory space. It also separates as four pages, and each page is 256 bytes.

The RC210xx supports 1-byte and 2-byte offset mode for all three slave serial interfaces, I2C, SPI, and SMBUS. The user can choose to operate as 1-byte or 2-byte offset mode, and can be configured through register [ssi\\_addr\\_size](#) (0x0026[2]) register field which defaults as 1-byte offset mode. These offsets are used in conjunction with the page register to access registers internal to the device. Because the I2C protocol already includes a read/write bit with the Dev Addr, all bits of the 1-byte or 2-byte offset field can be used to address internal registers.

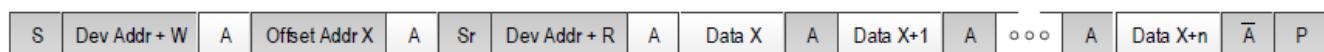

- The 1-byte offset mode – It also called page mode where part of the address offset is provided in each transaction and another part comes from an internal page register in each serial port. For an I2C 1-byte offset mode operation example, see [Figure 1](#).

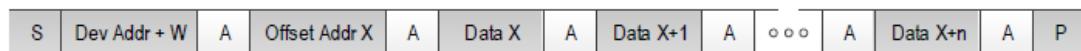

- The 2-Byte offset mode – Use two byte as the serial port providing the full offset address within each burst. For an I2C 2-byte offset mode operation example, see [Figure 2](#).

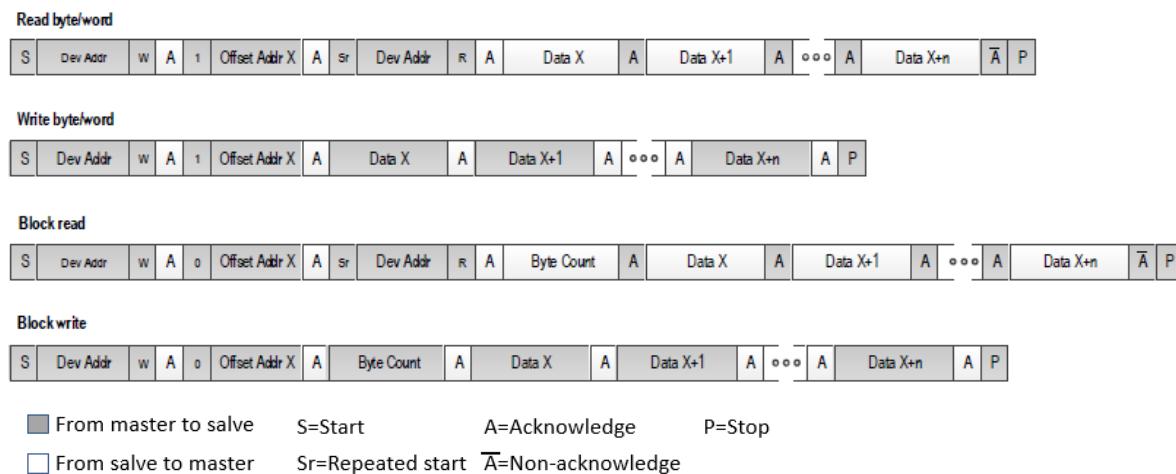

### 3. I2C Slave

The I2C slave protocol complies with the *I2C Specification*, version UM10204 Rev.6, 4 April 2014. The SCL\_SCLK and SDA\_nCS pins are 3.3V tolerant. The Dev Addr shown in the [Figure 1](#) represents the I2C bus address that the device will respond to. This 7-bit value in the i2c\_addr register field defaults to 0x09 if not programmed via the OTP load.

#### 3.1 1-Byte Offset Mode

In 1-byte mode, the lower 8 bits of the register offset address originate from the Offset Addr byte and the upper 8 bits come from the page register. The page register can be accessed at any time using an offset byte value of 0xFD. Write to 0 for page0, 1 for page1, 2 for page2, and 3 for page3.

##### Sequential 8-bit Read

##### Sequential 8-bit Write

From master to slave      S=Start      A=Acknowledge      P=Stop

From slave to master      Sr=Repeated start       $\bar{A}$ =Non-acknowledge

**Figure 1. I2C 1-Byte Offset Mode Slave Sequencing**

#### 3.2 2-Byte Offset Mode

In 2-byte mode, the full 16-bit register address can be obtained from the Offset Addr bytes, so the page register does not need to be set up. The MSB offset address is the page number and the LSB address is the register address.

##### Sequential 16-bit Read

##### Sequential 16-bit Write

From master to slave      S=Start      A=Acknowledge      P=Stop

From slave to master      Sr=Repeated start       $\bar{A}$ =Non-acknowledge

**Figure 2. I2C 2-Byte Offset Mode Slave Sequencing**

**Note:** All serial port configuration will take effect after the write cycle is completed.

## 4. SPI Slave

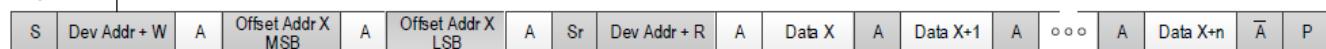

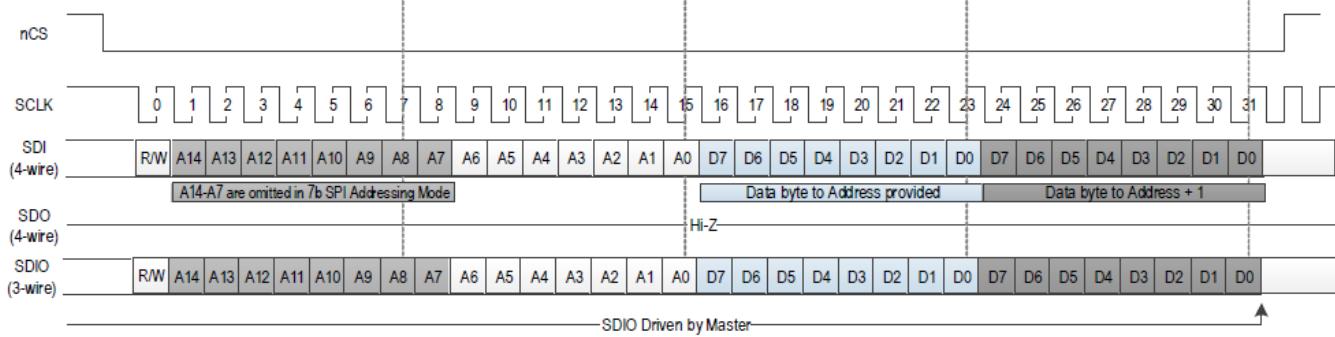

This device supports 4-wire or 3-wire SPI operation as a selectable protocol on the serial port. The 3-wire or 4-wire mode is selected by the spi\_3wire register bit. In 4-wire mode, there are separate data in and data out signals (SDI and SDO, respectively). In 3-wire mode, the SDIO signal is used as a single, bidirectional data signal.

Figure 3 shows the sequencing of address and data on the serial port in both 3-wire and 4-wire SPI mode. 4-wire SPI mode is the default. The R/W bit is high for read cycles and low for write cycles.

### SPI Read Sequence\*

### SPI Write Sequence\*

\* See the timing diagrams for exact timing relationships.

**Figure 3. SPI Sequencing Diagram**

SPI operation can be configured for the following settings through register fields: 1-byte or 2-byte offset addressing (ssi\_addr\_size).

In 1-byte operation, the 16-bit register address is formed by using the 7 bits of address supplied in the SPI access and taking the upper 9 bits from the page register. The page register is accessed using an offset address of 0xFD. For an 1-byte offset operation example, see [Example of I2C 1-Byte Offset Mode Programming](#).

In 2-byte operation, the 16-bit register address is formed by using the 15 bits of address supplied in the SPI access and taking the upper 1-bit from the page register. For an 2-byte offset operation example, see also [Example of I2C 2-Byte Offset Mode Programming](#).

- Data sampling on falling or rising edge of SCLK (spi\_clk\_sel)

- Output (read) data positioning relative to active SCLK edge (spi\_del\_out)

**Note:** SPI burst mode operation is required to ensure data integrity of multi-byte registers. When accessing a multi-byte register, all data bytes must be written or read in a single SPI burst access. Bursts can be of greater length if desired but must not extend beyond the end of the register page. An internal address pointer is incremented automatically as each data byte is written or read.

The SPI interface operating at 10MHz supports a DCO update rate of approximately 200k updates per second.

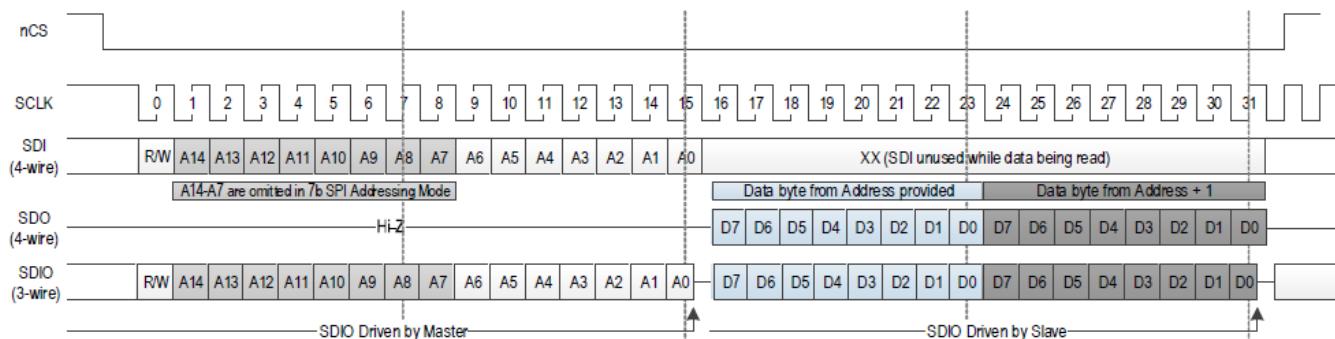

## 5. SMBus Slave

This device supports a standard SMBus v2.0 and v3.1 compliant interface operating at 100kHz, 400kHz, and 1MHz. The SCL\_SCLK and SDA\_nCS pins are 3.3V tolerant.

The SMBus interface supports block write and byte write modes. SMBus only supports 7-bit sub-addresses and the ssi\_addr\_size setting is ignored. A writeable page register selects the upper address bits.

The SMBus slave protocol of the RC210xx complies with the SMBus v2.0 and v3.1 standard.

In the following description, SCL refers to the SCL\_SCLK pin and SDA refers to the SDA\_nCS pin. [Figure 4](#) shows the sequence of states on the SMBus SDA signal for the supported modes of operation.

**Figure 4. I2C Slave Timing Diagram**

The Dev Addr shown in the figure represents the SMBus address that the device will respond to. This 7-bit value in the i2c\_addr register field defaults to 0x09 if not programmed via the OTP load.

In SMBus, the MSB of the offset address is used to determine whether Block mode is selected, and means the address space is only 128 locations. The internal 16-bit register address is formed by using the 7 bits of address supplied in the SMBus access and taking the upper 9 bits from the page register. The page register is accessed using an offset address of 0xFD.

Read byte/word and Write byte/word are essentially the same as the reads and writes in I2C mode. The main difference is in that when this mode is selected, the MSB of the offset address to read is set to 1. Block read and Block write modes are selected when the MSB of the offset address is set to 0. In block mode, the byte count is always the first value of the data phase. The byte count is stored in the byte count register field and defaults to 0x8.

**Note:** Same as for I2C, external to the scope of the SMBus-specific logic, burst mode operation is required to ensure data integrity of multi-byte registers. When accessing a multi-byte register, all data bytes must be written or read in a single SMBus burst access. Bursts can be of greater length if desired, but must not extend the end of the register page (Offset Addr 0x7F). An internal address pointer is incremented automatically as each data byte is written or read.

### 5.1 SMBus 1-Byte/2-Byte Offset Mode Programming Examples

In 1-byte operation, same as I2C 1-byte offset mode operation. For an 1-byte offset operation example, see [Example of I2C 1-Byte Offset Mode Programming](#).

In 2-byte operation, same as I2C 2-byte offset mode operation. For an 2-byte offset operation example, see also [Example of I2C 2-Byte Offset Mode Programming](#).

## 6. Example of Programming Process

The following two examples show how to use the rbs setting file register value and the customer's own I2C master to program the RC210xx:

- The I2C 1-byte offset mode programming with page number for more than 256 register offset addresses.

- The I2C 2-byte offset mode programming will use the most significant offset byte for the page number. It also applies to SMBus and SPI.

There are four steps to program the RC210xx:

1. Program all register values to the device.

2. Complete a VCO calibration for the new setting.

*Note:* This step applies only if the VCO frequency will change.

3. Complete an output divider sync up.

4. Change synchronous serial bus setting. The setting is effective after the write cycle is completed. If no change on synchronous serial bus change, then skip this step.

### 6.1 Getting Register Value from rbs Setting File

The register values of a configuration can be exported from the RICBox GUI when the configuration file is loaded, or it can be retrieved from an rbs file by running a Python script on the configuration file. The register map file is a text file that can be integrated into the user's software (i.e., a head file or a data array), and it will list all of the register values at the beginning of the file (see the following example).

| Offset Number | Binary Value | Hex Value | Offset Number |

|---------------|--------------|-----------|---------------|

| 00            | 00110011     | 33        | 00            |

| 01            | 00010000     | 10        | 01            |

| 02            | 00000000     | 00        | 02            |

| 03            | 00000000     | 00        | 03            |

| 04            | 00100010     | 22        | 04            |

| 05            | 00000001     | 01        | 05            |

| 06            | 10101001     | A9        | 06            |

| 07            | 00000000     | 00        | 07            |

| 08            | 00101010     | 2A        | 08            |

### 6.2 Example of I2C 1-Byte Offset Mode Programming

#### //Step 1 – Program register value

```

write 0x9 fd 00 // Change page number to page 0.

write 0x9 02 data(0x0002 to 0x0019)

write 0x9 28 data(0x0028 to 0x00F7) // Skip register 0x20 to 0x27, the synchronous

serial bus setting at the end.

write 0x9 fd 01 //Change page number to 1:

write 0x9 00 data(0x0100 to 0x01FA)

write 0x9 fd 02 //Change page number to 2:

write 0x9 00 data(0x0200 to 0x01FB)

write 0x9 fd 03 //Change page number to 3:

write 0x9 00 data(0x0300 to 0x031F)

write 0x9 fd 01 //Change page number to 1

```

### //Step 2 – VCO re-calibration

```

write 0x9 3c 20 // Dummy write, delay

write 0x9 3c A0 // Apll re-calibrate

write 0x9 3c 20 // Dummy write, wait for the re-calibrate.

// If the master has wait function, then it can be replay by wait

// command. (Wait about 400us)

write 0x9 3c 20 // Dummy write

```

### //Step 3 – Output divider sync up

```

write 0x9 fd 00 //Change page number to 0

write 0x9 11 30

write 0x9 11 32 // output divider sync up

write 0x9 11 30

```

### //Step 4 – Synchronous serial bus setting

```

write 0x9 00 20 data(0x0020 to 0x0027) //change synchronous serial bus setting. It

will be affected after the write cycle completed.

```

## 6.3 Example of I2C 2-Byte Offset Mode Programming

### //Step 1 Program register value

```

write 0x9 00 02 data(0x0002 to 0x0019) // burst write      //Skip register 0x0020 to

0x0027.

write 0x9 00 28 data(0x0028 to 0x00F7) // burst write

write 0x9 01 00 data(0x0100 to 0x01FA) // burst write

write 0x9 02 00 data(0x0200 to 0x01FB) // burst write

write 0x9 03 00 data(0x0300 to 0x031F) // burst write

```

### //Step 2 VCO re-calibration

```

write 0x9 01 3c 20 // Dummy write, delay

write 0x9 01 3c 20

write 0x9 01 3c A0 // Apll re-calibrate. Change register 0x013C from 20 to A0 to

re-calibrate

write 0x9 01 3c 20 // Dummy write, wait for the re-calibrate.

write 0x9 01 3c 20 // Dummy write

```

```

write 0x9 01 3c 20 // Dummy write

```

**//Step 3 Output divider sync up**

```

write 0x9 00 11 30

write 0x9 00 11 32 // divider sync up

write 0x9 00 11 30

```

**//Step 4 Synchronous serial bus setting**

```

write 0x9 00 20 data(0x0020 to 0x0027) //change synchronous serial bus setting. It

will be affected after the write cycle completed.

```

## 7. Example of Changing Output Frequency

Changing an output frequency does not require all registers to be programmed. Changing an output frequency can be implemented by changing either or both of the following:

- VCO frequency of the APLL

- Output divider

Output dividers include integer output dividers (IODs) and fractional output dividers (FODs). Modifying only the output dividers will result in a glitchless frequency change when the last byte of output divider value is updated by an I2C block write event. The frequency change is instantaneous; one clock cycle is still the old frequency and the next clock cycle is the new frequency. Re-calibration is not required; however, if the VCO frequency is modified, it will trigger a VCO calibration. The resulting output frequency will not be glitchless.

APLL VCO frequency is determined by input clock frequency and the 27-bit Feedback divider. The VCO frequency range is between 9.5GHz and 10.7GHz. With VCO frequency in the range of 9.5GHz to 10.7GHz, the RC210xx supports an output frequency range of 1KHz to 650MHz by choosing a proper output divider value. If the desired output frequency is in an integer relationship with VCO frequency, an IOD is used; otherwise, an FOD is used. FOD provides a frequency resolution up to 1ppt (1 per trillion). There are four IODs (IOD0-3) and three FODs (FOD0-2).

*Note:* If the input frequency or VCO frequency is changed, then re-calibration is required. All changes made through I2C will be temporary. When power is cycled, the original configuration is loaded from OTP memory.

### 7.1 Output Frequency Calculation

The following formulas provide a method to calculate the desired output frequency. With output frequency determined, we then select an output divider to get the VCO frequency, which must be within 9.5GHz to 10.7GHz.

- Output Frequency = VCO Frequency / Output Divider

- VCO Frequency = Input Frequency \* Doubler \* (apll\_fb\_div\_int + (apll\_fb\_div\_frac / 2 ^ 27))

*Note:* If the doubler is enabled, the Doubler=2. If the doubler is disabled, the Doubler = 1.

## 7.2 Feedback Divider

The VCO feedback divider consists of a 10-bit integer and a 27-bit fractional portion. The offset addresses of the feedback divider register are as follows:

Integer:

- FB\_INT\_DIV[9:8] = 0x125[1:0]

- FB\_INT\_DIV[7:0] = 0x124[7:0]

Fractional:

- FB\_FRAC\_DIV[26:24] = 0x123[2:0]

- FB\_FRAC\_DIV[23:16] = 0x122[7:0]

- FB\_FRAC\_DIV[15:8] = 0x121[7:0]

- FB\_FRAC\_DIV[7:0] = 0x120[7:0]

**Example:** Programming a VCO frequency of 10GHz with 60MHz crystal.

With a crystal frequency of 60MHz, in order to make a VCO frequency of 10GHz:

- FB\_DIV = 10GHz / (60MHz x 2) = 83.333333333333333333

- FB\_INT\_DIV = 83

- FB\_FRAC\_DIV = 0.6666666666666667 x 2^27 = 44,739,243 = '0h02 AA AA AB

Program the following registers will make VCO frequency = 10GHz:

- 0x125[1:0] = 0x0

- 0x124[7:0] = 0x53

- 0x123[2:0] = 0x02

- 0x122[7:0] = 0xAA

- 0x121[7:0] = 0xAA

- 0x120[7:0] = 0xAB

## 7.3 Integer Output Divider

Each Integer Output Divider (IOD) is 25 bits with valid values between 14 and 33,554,431 ( $= 2^{25} - 1$ ). A value smaller than 14 causes the output frequency to increase above its maximum 650MHz and the biggest value makes an output frequency below the minimum 1KHz.

IOD0 registers:

- IOD0[24] = Register 0x1C3[0]

- IOD0[23:16] = Register 0x1C2[7:0]

- IOD0[15:8] = Register 0x1C1[7:0]

- IOD0[7:0] = Register 0x1C0[7:0]

Register 0x1C3 only uses bit [0] as IOD0's MSB. All four registers must be written for the IOD value to actually change an output frequency. Register 0x1C3 has remaining bits that have other functions. Remember to keep other bits intact when modifying 0x1C3[0]. Also, read registers 0x1C0~3 to confirm the current value and to know the remaining bits in register 0xC3.

In addition, the other three IODs are taking up the register ranges listed below:

- IOD1[24:0] are in registers 0x1C8, 0x1C9, 0x1CA and 0x1CB.

- IOD2[24:0] are in registers 0x1D0, 0x1D1, 0x1D2 and 0x1D3.

- IOD3[24:0] are in registers 0x1D8, 0x1D9, 0x1DA and 0x1DB.

**Example:** To make OUT0 = 100MHz by change IOD0 to 100 (VCO frequency = 10GHz)

Output Frequency = VCO Frequency / Output Divider

$$100\text{MHz} = 10\text{GHz} / 100$$

Programming the following registers will change the output to 100MHz. Assuming the VCO is 10GHz.

- Register 0x1C0[7:0] value 0x64

- Register 0x1C1[7:0] value 0x00

- Register 0x1C2[7:0] value 0x00

- Register 0x1C3[0] value 0x0

## 7.4 Fractional Output Dividers

The fractional output divider consists of a 9-bit 1<sup>st</sup> integer, a 17-bit 2<sup>nd</sup> integer, and a 34-bit fractional portion. Together, it can provide a frequency resolution better than 1ppt. The 1<sup>st</sup> integer covers values up to 511 and is always used. The 2<sup>nd</sup> integer can cover values up to 131,071 and is used for output frequencies below 33MHz. The formula for the total divider value is as follows:

- $F_{\text{OUT}} > 33\text{MHz}$ : FOD = 1<sup>st</sup> Integer + Fraction

- $F_{\text{OUT}} < 33\text{MHz}$ : FOD = (1<sup>st</sup> Integer + Fraction)  $\times 2 \times 2^{\text{nd}}$  Integer

For output frequencies above 33MHz, where the 2<sup>nd</sup> Integer is not used, the 2<sup>nd</sup> Integer value is set to 1. This causes the 2<sup>nd</sup> Integer and its additional  $\times 2$  to be bypassed. Both integer and fractional registers are as follows.

1<sup>st</sup> Integer:

- FOD0 1<sup>st</sup> Integer [8] = Register 0x1E1[0]

- FOD0 1<sup>st</sup> Integer [7:0] = Register 0x1E0[7:0]

2<sup>nd</sup> Integer:

- FOD0 2<sup>nd</sup> Integer [16:15] = Register 0x1E3[1:0]

- FOD0 2<sup>nd</sup> Integer [14:7] = Register 0x1E2[7:0]

- FOD0 2<sup>nd</sup> Integer [6:0] = Register 0x1E1[7:1]

Fractional:

- FOD0 Fractional [33:30] = Register 0x1E7[3:0]

- FOD0 Fractional [29:22] = Register 0x1E6[7:0]

- FOD0 Fractional [21:14] = Register 0x1E5[7:0]

- FOD0 Fractional [13:6] = Register 0x1E4[7:0]

- FOD0 Fractional [5:0] = Register 0x1E3[7:2]

In addition, FOD1 values are carried by registers 0x1F0 to 0x1F7, and FOD2 is carried by registers in 0x200 to 0x207. For more information, see [Register Offsets](#).

**Example:** Setting OUT0 = 156.25MHz by programming FOD0 = 64 (VCO frequency = 10GHz)

Output Frequency = VCO Frequency / Output Divider

$$156.25\text{MHz} = 10\text{GHz} / 64$$

Program the following registers will change the output to 156.25MHz

- FOD0 Integer Register programming:

- Register 0x1E0[7:0] value 0x40

- Register 0x1E1[7:0] value 0x00

- Register 0x1E2[7:0] value 0x00

- Register 0x1E3[1:0] value 0x00

- FOD0 Fractional register programming:

- Register 0x1E3[7:2] value 0x00

- Register 0x1E4[6:0] value 0x00

- Register 0x1E5[6:0] value 0x00

- Register 0x1E6[6:0] value 0x00

- Register 0x1E7[3:0] value 0x00

## 8. Example of Device Programming with the Driver

For PC or Linux users, they can also leverage the RC210xx Python driver to program the device. The driver will take care of the programming process.

The requirement: Install RICBox and the VC7 plug-in file, or install Python 3.9 and the VC7 driver.

### 8.1 Example of Python Code

Save the following code to “VC7\_Config\_Builder.py”

```

import rbcore

from r_drv_vc7.device_abstraction.config_builder import *

from r_drv_vc7.device_abstraction.versaclock7 import Versaclock7

from rbcore.io.ftdi import FtdiI2cSettings

## Create VC7 device. (VC7_Family, Version)

vc7 = Versaclock7( Versaclock7.create_device(r'RC21012B', 'B'))

## Connect FTDI device, I2C address = 0x9

vc7.connect(FtdiI2cSettings(index='0', address=0x09))

## Program VC7

vc7.program_settings_file(r'RC21012B065_config0.rbs')

```

### 8.2 Example of DOS Batch File

The RICBox VC7 plug-in file comes with the Python 3.9 environment. The following example shows the RICBox environment path. Save the following command to batch file so that it can execute the Python code.

```

Echo off

Echo Start!

C:\Users\%username%\AppData\Roaming\RICBox\venvs\VersaClock7-x64\Scripts\python

VC7_Config_Builder.py

pause

```

## 9. Register Organization

### 9.1 Overview

Register sizes are denoted as:

- byte: 8-bit

- hword: 16-bit

- word: 32-bit

- dword: 64-bit

Register types are defined in the following table.

**Table 2. Register Type Definition**

| Type Indicator | Definition            |

|----------------|-----------------------|

| R/W1C          | Read/Write 1 to Clear |

| R/W1S          | Read/Write 1 to Set   |

| RO             | Read-only             |

| RW             | Read/Write            |

| WO             | Write-only            |

### 9.2 Register Block Offsets

**Table 3. Register Block Offsets**

| Block Offset   | Block Name  | Address Table                 | Registers        |

|----------------|-------------|-------------------------------|------------------|

| 0x000          | GLOBAL      | Global Addresses              | Global Registers |

| 0x020          | SSI         | SSI Addresses                 | SSI Registers    |

| 0x02C          | XO          | Crystal Addresses             | XO Register      |

| 0x030 += 0x004 | CLKIN[0:1]  | Clock Input Addresses         | CLKIN Register   |

| 0x050 += 0x010 | LOSMON[0:4] | LOSMON Monitor Addresses      | LOSMON Registers |

| 0x120          | APLL        | APLL Addresses                | APLL Registers   |

| 0x1C0 += 0x008 | IOD[0:3]    | IOD Addresses                 | IOD Registers    |

| 0x1E0 += 0x010 | FOD[0:2]    | FOD Addresses                 | FOD Registers    |

| 0x240 += 0x004 | OUT[0:11]   | Clock Output Driver Addresses | OUT Registers    |

| 0x280 += 0x004 | BANK[0:6]   | Output Bank Addresses         | BANK Register    |

| 0x29C += 0x004 | GPI[0:3]    | GPI Addresses                 | GPI Registers    |

| 0x2AC += 0x004 | GPIO[0:4]   | GPIO Addresses                | GPIO Registers   |

| 0x300 += 0x004 | SSC[0:1]    | SSC Addresses                 | SSC Register     |

| 0x308          | INT         | Interrupt Addresses           | INT Registers    |

## 9.3 Register Offsets

### 9.3.1 Global Address Map

Table 4. Global Addresses

| Block Offset | Size  | Register Name | Register Description                                    |

|--------------|-------|---------------|---------------------------------------------------------|

| 0x00         | hword | VENDOR_ID     | VENDOR_ID - Vendor ID                                   |

| 0x02         | hword | DEVICE_ID     | DEVICE_ID - Device ID                                   |

| 0x04         | hword | DEVICE_REV    | DEVICE_REV - Device Revision                            |

| 0x06         | hword | DEVICE_PGM    | DEVICE_PGM - Device Programming                         |

| 0x08         | word  | DEVICE_CNFG   | DEVICE_CNFG - Device Configuration                      |

| 0x0E         | byte  | PWR_CTL       | PWR_CTL - Power Control                                 |

| 0x10         | byte  | REG_LOCK      | REG_LOCK - Configuration Register Lock                  |

| 0x11         | byte  | INIT_SYNC     | INIT_SYNC - Initialization and Synchronization Register |

| 0x12         | hword | SW_RESET      | SW_RESET - Software Reset Register                      |

| 0x16         | hword | MISC_CNFG     | MISC_CNFG - Miscellaneous Configuration                 |

| 0x1C         | hword | STARTUP_STS   | STARTUP_STS - Start-up Status                           |

| 0x1E         | hword | DEVICE_STS    | DEVICE_STS - Device Status                              |

### 9.3.2 SSI Address Map

Table 5. SSI Addresses

| Offset | Size | Register Name   | Register Description                       |

|--------|------|-----------------|--------------------------------------------|

| 0x00   | byte | SPI_CNFG        | SPI_CNFG - SPI Configuration               |

| 0x01   | byte | I2C_FLTR_CNFG   | I2C_FLTR_CNFG - I2C Filter Configuration   |

| 0x02   | byte | I2C_TIMING_CNFG | I2C_TIMING_CNFG - I2C Timing Configuration |

| 0x03   | byte | I2C_ADDR_CNFG   | I2C_ADDR_CNFG - I2C Address Configuration  |

| 0x04   | byte | BYTE_CNT        | BYTE_CNT - Byte Count                      |

| 0x05   | byte | SMB_CTL         | SMB_CTL - SMBus Control                    |

| 0x06   | byte | SSI_GLOBAL_CNFG | SSI_GLOBAL_CNFG - SSI Global Configuration |

| 0x07   | byte | SSI_STS         | SSI_STS - Serial Port Status               |

### 9.3.3 Crystal Address Map

Table 6. Crystal Addresses

| Offset | Size | Register Name | Register Description            |

|--------|------|---------------|---------------------------------|

| 0x00   | word | XO_CNFG       | XO_CNFG - Crystal Configuration |

### 9.3.4 Clock Input Address Map

Table 7. Clock Input Addresses

| Offset | Size  | Register Name | Register Description                       |

|--------|-------|---------------|--------------------------------------------|

| 0x00   | hword | CLKIN_CNFG    | CLKIN_CNFG - Clock Input Pad Configuration |

### 9.3.5 LOS Monitor Address Map

Table 8. LOS Monitor Addresses

| Offset | Size  | Register Name  | Register Description                                      |

|--------|-------|----------------|-----------------------------------------------------------|

| 0x00   | hword | LOSMON_WINDOW  | LOSMON_WINDOW - LOS Monitor Window Configuration          |

| 0x02   | hword | LOSMON_NOMINAL | LOSMON_NOMINAL - LOS Monitor Nominal Number Configuration |

| 0x04   | word  | LOSMON_THRESH  | LOSMON_THRESH - LOS Monitor Threshold Configuration       |

| 0x08   | byte  | LOSMON_QUAL    | LOSMON_QUAL - LOS Monitor Qualify Counter Configuration   |

| 0x09   | byte  | LOSMON_STS     | LOSMON_STS - LOS Monitor Status                           |

| 0x0A   | byte  | LOSMON_EVENT   | LOSMON_EVENT - LOS Monitor Event Status                   |

| 0x0B   | byte  | LOSMON_CNT     | LOSMON_CNT - LOS Monitor Count                            |

### 9.3.6 APLL Address Map

Table 9. APLL Addresses

| Offset | Size  | Register Name    | Register Description                                            |

|--------|-------|------------------|-----------------------------------------------------------------|

| 0x00   | word  | APLL_FB_DIV_FRAC | APLL_FB_DIV_FRAC - APLL Feedback Divider Fraction Configuration |

| 0x04   | hword | APLL_FB_DIV_INT  | APLL_FB_DIV_INT - APLL Feedback Divider Integer Configuration   |

| 0x06   | byte  | APLL_FB_SDM_CNFG | APLL_FB_SDM_CNFG - APLL Feedback SDM Configuration              |

| 0x07   | byte  | APLL_CNFG        | APLL_CNFG - APLL Configuration                                  |

| 0x08   | hword | CP_CNFG          | CP_CNFG - APLL Charge Pump Configuration                        |

| 0x0A   | byte  | LPF_CNFG         | LPF_CNFG - APLL Loop Filter Configuration                       |

| 0x0B   | byte  | LPF_3RD_CNFG     | LPF_3RD_CNFG - APLL Loop Filter 3rd Pole Configuration          |

| 0x15   | byte  | APLL_REF_FB_CNFG | APLL_REF_FB_CNFG - APLL Ref and Fb Clock Configuration          |

| 0x18   | word  | BANK_MUX_CLK_EN  | BANK_MUX_CLK_EN - Bank Mux Clock Enable                         |

| 0x1F   | byte  | APLL_STS         | APLL_STS - APLL Status                                          |

| 0x20   | byte  | APLL_EVENT       | APLL_EVENT - APLL Event Status                                  |

| 0x21   | byte  | APLL_LOL_CNT     | APLL_LOL_CNT - APLL Loss-of-Lock Counter                        |

| 0x28   | hword | ANA_SPARE_CNFG   | ANA_SPARE_CNFG - Analog Spare Configuration                     |

| 0x2A   | hword | ANA_SPARE_STS    | ANA_SPARE_STS - Analog Spare Status                             |

### 9.3.7 IOD Address Map

Table 10. IOD Addresses

| Offset | Size  | Register Name  | Register Description                           |

|--------|-------|----------------|------------------------------------------------|

| 0x00   | word  | IOD_INT_CNFG   | IOD_INT_CNFG - IOD Integer Ratio Configuration |

| 0x04   | hword | IOD_PHASE_CNFG | IOD_PHASE_CNFG - IOD Phase Configuration       |

### 9.3.8 FOD Address Map

Table 11. FOD Addresses

| Offset | Size  | Register Name  | Register Description                     |

|--------|-------|----------------|------------------------------------------|

| 0x00   | dword | FOD_INT_CNFG   | FOD_INT_CNFG - FOD Integer Configuration |

| 0x08   | hword | FOD_PHASE_CNFG | FOD_PHASE_CNFG - FOD Phase Configuration |

### 9.3.9 SSC Address Map

Table 12. SSC Addresses

| Offset | Size | Register Name | Register Description                        |

|--------|------|---------------|---------------------------------------------|

| 0x00   | word | SSC_CNFG      | SSC_CNFG - Spectrum Spreading Configuration |

### 9.3.10 Output Bank Address Map

Table 13. Output Bank Addresses

| Offset | Size | Register Name | Register Description                      |

|--------|------|---------------|-------------------------------------------|

| 0x00   | byte | OUT_BANK_CNFG | OUT_BANK_CNFG - Output Bank Configuration |

### 9.3.11 Clock Output Driver Address Map

Table 14. Clock Output Driver Addresses

| Offset | Size  | Register Name | Register Description                    |

|--------|-------|---------------|-----------------------------------------|

| 0x00   | byte  | ODRV_EN       | ODRV_EN - Output Driver Enable          |

| 0x02   | hword | ODRV_CNFG     | ODRV_CNFG - Output Driver Configuration |

### 9.3.12 GPI Address Map

Table 15. GPI Addresses

| Offset | Size  | Register Name | Register Description         |

|--------|-------|---------------|------------------------------|

| 0x00   | hword | GPI_CNFG      | GPI_CNFG - GPI Configuration |

| 0x02   | byte  | GPI_STS       | GPI_STS - GPI Status         |

### 9.3.13 GPIO Address Map

Table 16. GPIO Addresses

| Offset | Size  | Register Name | Register Description           |

|--------|-------|---------------|--------------------------------|

| 0x00   | hword | GPIO_CNFG     | GPIO_CNFG - GPIO Configuration |

| 0x02   | byte  | GPIO_STS      | GPIO_STS - GPIO Status         |

### 9.3.14 Interrupt Address Map

Table 17. Interrupt Addresses

| Offset | Size | Register Name | Register Description                   |

|--------|------|---------------|----------------------------------------|

| 0x00   | word | SCRATCH0      | SCRATCH0 - Software Scratch Register 0 |

| 0x04   | word | INT_EN        | INT_EN - Interrupt Enable              |

| 0x08   | word | INT_STS       | INT_STS - Interrupt Status             |

## 10. Physical Register Addresses

### 10.1 Global Block

Table 18. Global Block Physical Register Addresses

| Address | Block Name | Register       | Type  | Default |

|---------|------------|----------------|-------|---------|

| 0x0     | GLOBAL     | VENDOR_ID[0]   | RO    | 0x33    |

| 0x1     | GLOBAL     | VENDOR_ID[1]   | RO    | 0x10    |

| 0x2     | GLOBAL     | DEVICE_ID[0]   | RW    | 0x00    |

| 0x3     | GLOBAL     | DEVICE_ID[1]   | RW    | 0x00    |

| 0x4     | GLOBAL     | DEVICE_REV[0]  | RO    | 0x22    |

| 0x5     | GLOBAL     | DEVICE_REV[1]  | RO    | 0x01    |

| 0x6     | GLOBAL     | DEVICE_PGM[0]  | RW    | 0x00    |

| 0x7     | GLOBAL     | DEVICE_PGM[1]  | RW    | 0x00    |

| 0x8     | GLOBAL     | DEVICE_CNFG[0] | RW    | 0x2a    |

| 0x9     | GLOBAL     | DEVICE_CNFG[1] | RW    | 0xf0    |

| 0xa     | GLOBAL     | DEVICE_CNFG[2] | RW    | 0x12    |

| 0xb     | GLOBAL     | DEVICE_CNFG[3] | RW    | 0x00    |

| 0xe     | GLOBAL     | PWR_CTL        | RW    | 0x01    |

| 0x10    | GLOBAL     | REG_LOCK       | RW    | 0x00    |

| 0x11    | GLOBAL     | INIT_SYNC      | R/W1S | 0x30    |

| 0x12    | GLOBAL     | SW_RESET[0]    | RW    | 0x00    |

| 0x13    | GLOBAL     | SW_RESET[1]    | RW    | 0x00    |

| 0x16    | GLOBAL     | MISC_CNFG[0]   | RW    | 0x05    |

| 0x17    | GLOBAL     | MISC_CNFG[1]   | RW    | 0x80    |

| 0x1c    | GLOBAL     | STARTUP_STS[0] | RO    | 0x00    |

**Table 18. Global Block Physical Register Addresses (Cont.)**

| Address | Block Name | Register       | Type | Default |

|---------|------------|----------------|------|---------|

| 0x1d    | GLOBAL     | STARTUP_STS[1] | RO   | 0x00    |

| 0x1e    | GLOBAL     | DEVICE_STS[0]  | RO   | 0x00    |

| 0x1f    | GLOBAL     | DEVICE_STS[1]  | RO   | 0x00    |

## 10.2 SSI Block

**Table 19. SSI Block Physical Register Addresses**

| Address | Block Name | Register        | Type  | Default |

|---------|------------|-----------------|-------|---------|

| 0x20    | SSI        | SPI_CNFG        | RW    | 0x00    |

| 0x21    | SSI        | I2C_FLTR_CNFG   | RW    | 0x01    |

| 0x22    | SSI        | I2C_TIMING_CNFG | RW    | 0x22    |

| 0x23    | SSI        | I2C_ADDR_CNFG   | RW    | 0x09    |

| 0x24    | SSI        | BYTE_CNT        | RW    | 0x08    |

| 0x25    | SSI        | SMB_CTL         | RW    | 0x79    |

| 0x26    | SSI        | SSI_GLOBAL_CNFG | RW    | 0x01    |

| 0x27    | SSI        | SSI_STS         | R/W1C | 0x00    |

## 10.3 XO Block

**Table 20. XO Block Physical Register Addresses**

| Address | Block Name | Register   | Type | Default |

|---------|------------|------------|------|---------|

| 0x2c    | XO         | XO_CNFG[0] | RW   | 0x45    |

| 0x2d    | XO         | XO_CNFG[1] | RW   | 0x28    |

| 0x2e    | XO         | XO_CNFG[2] | RW   | 0x68    |

| 0x2f    | XO         | XO_CNFG[3] | RW   | 0x20    |

## 10.4 CLKIN Block

**Table 21. CLKIN Block Physical Register Addresses**

| Address | Block Name | Register      | Type | Default |

|---------|------------|---------------|------|---------|

| 0x30    | CLKIN[0]   | CLKIN_CNFG[0] | RW   | 0x01    |

| 0x31    | CLKIN[0]   | CLKIN_CNFG[1] | RW   | 0x80    |

| 0x34    | CLKIN[1]   | CLKIN_CNFG[0] | RW   | 0x01    |

| 0x35    | CLKIN[1]   | CLKIN_CNFG[1] | RW   | 0x80    |

## 10.5 LOSMON Block

Table 22. LOSMON Block Physical Register Addresses

| Address | Block Name | Register          | Type  | Default |

|---------|------------|-------------------|-------|---------|

| 0x50    | LOSMON[0]  | LOSMON_WINDOW[0]  | RW    | 0x00    |

| 0x51    | LOSMON[0]  | LOSMON_WINDOW[1]  | RW    | 0x00    |

| 0x52    | LOSMON[0]  | LOSMON_NOMINAL[0] | RW    | 0x00    |

| 0x53    | LOSMON[0]  | LOSMON_NOMINAL[1] | RW    | 0x00    |

| 0x54    | LOSMON[0]  | LOSMON_THRESH[0]  | RW    | 0x00    |

| 0x55    | LOSMON[0]  | LOSMON_THRESH[1]  | RW    | 0x00    |

| 0x56    | LOSMON[0]  | LOSMON_THRESH[2]  | RW    | 0x00    |

| 0x57    | LOSMON[0]  | LOSMON_THRESH[3]  | RW    | 0x00    |

| 0x58    | LOSMON[0]  | LOSMON_QUAL       | RW    | 0x44    |

| 0x59    | LOSMON[0]  | LOSMON_STS        | RO    | 0x03    |

| 0x5a    | LOSMON[0]  | LOSMON_EVENT      | R/W1C | 0x01    |

| 0x5b    | LOSMON[0]  | LOSMON_CNT        | RW    | 0x00    |

| 0x60    | LOSMON[1]  | LOSMON_WINDOW[0]  | RW    | 0x00    |

| 0x61    | LOSMON[1]  | LOSMON_WINDOW[1]  | RW    | 0x00    |

| 0x62    | LOSMON[1]  | LOSMON_NOMINAL[0] | RW    | 0x00    |

| 0x63    | LOSMON[1]  | LOSMON_NOMINAL[1] | RW    | 0x00    |

| 0x64    | LOSMON[1]  | LOSMON_THRESH[0]  | RW    | 0x00    |

| 0x65    | LOSMON[1]  | LOSMON_THRESH[1]  | RW    | 0x00    |

| 0x66    | LOSMON[1]  | LOSMON_THRESH[2]  | RW    | 0x00    |

| 0x67    | LOSMON[1]  | LOSMON_THRESH[3]  | RW    | 0x00    |

| 0x68    | LOSMON[1]  | LOSMON_QUAL       | RW    | 0x44    |

| 0x69    | LOSMON[1]  | LOSMON_STS        | RO    | 0x03    |

| 0x6a    | LOSMON[1]  | LOSMON_EVENT      | R/W1C | 0x01    |

| 0x6b    | LOSMON[1]  | LOSMON_CNT        | RW    | 0x00    |

| 0x70    | LOSMON[2]  | LOSMON_WINDOW[0]  | RW    | 0x00    |

| 0x71    | LOSMON[2]  | LOSMON_WINDOW[1]  | RW    | 0x00    |

| 0x72    | LOSMON[2]  | LOSMON_NOMINAL[0] | RW    | 0x00    |

| 0x73    | LOSMON[2]  | LOSMON_NOMINAL[1] | RW    | 0x00    |

| 0x74    | LOSMON[2]  | LOSMON_THRESH[0]  | RW    | 0x00    |

| 0x75    | LOSMON[2]  | LOSMON_THRESH[1]  | RW    | 0x00    |

| 0x76    | LOSMON[2]  | LOSMON_THRESH[2]  | RW    | 0x00    |

| 0x77    | LOSMON[2]  | LOSMON_THRESH[3]  | RW    | 0x00    |

| 0x78    | LOSMON[2]  | LOSMON_QUAL       | RW    | 0x44    |

| 0x79    | LOSMON[2]  | LOSMON_STS        | RO    | 0x03    |

| 0x7a    | LOSMON[2]  | LOSMON_EVENT      | R/W1C | 0x01    |

| 0x7b    | LOSMON[2]  | LOSMON_CNT        | RW    | 0x00    |

**Table 22. LOSMON Block Physical Register Addresses (Cont.)**

| Address | Block Name | Register          | Type  | Default |

|---------|------------|-------------------|-------|---------|

| 0x80    | LOSMON[3]  | LOSMON_WINDOW[0]  | RW    | 0x00    |

| 0x81    | LOSMON[3]  | LOSMON_WINDOW[1]  | RW    | 0x00    |

| 0x82    | LOSMON[3]  | LOSMON_NOMINAL[0] | RW    | 0x00    |

| 0x83    | LOSMON[3]  | LOSMON_NOMINAL[1] | RW    | 0x00    |

| 0x84    | LOSMON[3]  | LOSMON_THRESH[0]  | RW    | 0x00    |

| 0x85    | LOSMON[3]  | LOSMON_THRESH[1]  | RW    | 0x00    |

| 0x86    | LOSMON[3]  | LOSMON_THRESH[2]  | RW    | 0x00    |

| 0x87    | LOSMON[3]  | LOSMON_THRESH[3]  | RW    | 0x00    |

| 0x88    | LOSMON[3]  | LOSMON_QUAL       | RW    | 0x44    |

| 0x89    | LOSMON[3]  | LOSMON_STS        | RO    | 0x03    |

| 0x8a    | LOSMON[3]  | LOSMON_EVENT      | R/W1C | 0x01    |

| 0x8b    | LOSMON[3]  | LOSMON_CNT        | RW    | 0x00    |

| 0x90    | LOSMON[4]  | LOSMON_WINDOW[0]  | RW    | 0x00    |

| 0x91    | LOSMON[4]  | LOSMON_WINDOW[1]  | RW    | 0x00    |

| 0x92    | LOSMON[4]  | LOSMON_NOMINAL[0] | RW    | 0x00    |

| 0x93    | LOSMON[4]  | LOSMON_NOMINAL[1] | RW    | 0x00    |

| 0x94    | LOSMON[4]  | LOSMON_THRESH[0]  | RW    | 0x00    |

| 0x95    | LOSMON[4]  | LOSMON_THRESH[1]  | RW    | 0x00    |

| 0x96    | LOSMON[4]  | LOSMON_THRESH[2]  | RW    | 0x00    |

| 0x97    | LOSMON[4]  | LOSMON_THRESH[3]  | RW    | 0x00    |

| 0x98    | LOSMON[4]  | LOSMON_QUAL       | RW    | 0x44    |

| 0x99    | LOSMON[4]  | LOSMON_STS        | RO    | 0x03    |

| 0x9a    | LOSMON[4]  | LOSMON_EVENT      | R/W1C | 0x01    |

| 0x9b    | LOSMON[4]  | LOSMON_CNT        | RW    | 0x00    |

## 10.6 APLL Block

**Table 23. APLL Block Physical Register Addresses**

| Address | Block Name | Register            | Type | Default |

|---------|------------|---------------------|------|---------|

| 0x120   | APLL       | APLL_FB_DIV_FRAC[0] | RW   | 0x00    |

| 0x121   | APLL       | APLL_FB_DIV_FRAC[1] | RW   | 0x00    |

| 0x122   | APLL       | APLL_FB_DIV_FRAC[2] | RW   | 0x00    |

| 0x123   | APLL       | APLL_FB_DIV_FRAC[3] | RW   | 0x00    |

| 0x124   | APLL       | APLL_FB_DIV_INT[0]  | RW   | 0x69    |

| 0x125   | APLL       | APLL_FB_DIV_INT[1]  | RW   | 0x00    |

| 0x126   | APLL       | APLL_FB_SDM_CNFG    | RW   | 0x03    |

| 0x127   | APLL       | APLL_CNFG           | RW   | 0x01    |

| 0x128   | APLL       | CP_CNFG[0]          | RW   | 0x33    |

**Table 23. APLL Block Physical Register Addresses (Cont.)**

| Address | Block Name | Register         | Type  | Default |

|---------|------------|------------------|-------|---------|

| 0x129   | APLL       | CP_CNFG[1]       | RW    | 0x03    |

| 0x12a   | APLL       | LPF_CNFG         | RW    | 0x74    |

| 0x12b   | APLL       | LPF_3RD_CNFG     | RW    | 0x44    |

| 0x135   | APLL       | APLL_REF_FB_CNFG | RW    | 0x00    |

| 0x13f   | APLL       | APLL_STS         | RO    | 0x00    |

| 0x140   | APLL       | APLL_EVENT       | R/W1C | 0x00    |

| 0x141   | APLL       | APLL_LOL_CNT     | RW    | 0x00    |

## 10.7 IOD Block

**Table 24. IOD Block Physical Register Addresses**

| Address | Block Name | Register          | Type  | Default |

|---------|------------|-------------------|-------|---------|

| 0x1c0   | IOD[0]     | IOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x1c1   | IOD[0]     | IOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x1c2   | IOD[0]     | IOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x1c3   | IOD[0]     | IOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x1c4   | IOD[0]     | IOD_PHASE_CNFG[0] | RW    | 0x00    |

| 0x1c5   | IOD[0]     | IOD_PHASE_CNFG[1] | R/W1S | 0x00    |

| 0x1c8   | IOD[1]     | IOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x1c9   | IOD[1]     | IOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x1ca   | IOD[1]     | IOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x1cb   | IOD[1]     | IOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x1cc   | IOD[1]     | IOD_PHASE_CNFG[0] | RW    | 0x00    |

| 0x1cd   | IOD[1]     | IOD_PHASE_CNFG[1] | R/W1S | 0x00    |

| 0x1d0   | IOD[2]     | IOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x1d1   | IOD[2]     | IOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x1d2   | IOD[2]     | IOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x1d3   | IOD[2]     | IOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x1d4   | IOD[2]     | IOD_PHASE_CNFG[0] | RW    | 0x00    |

| 0x1d5   | IOD[2]     | IOD_PHASE_CNFG[1] | R/W1S | 0x00    |

| 0x1d8   | IOD[3]     | IOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x1d9   | IOD[3]     | IOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x1da   | IOD[3]     | IOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x1db   | IOD[3]     | IOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x1dc   | IOD[3]     | IOD_PHASE_CNFG[0] | RW    | 0x00    |

| 0x1dd   | IOD[3]     | IOD_PHASE_CNFG[1] | R/W1S | 0x00    |

## 10.8 FOD Block

Table 25. FOD Block Physical Register Addresses

| Address | Block Name | Register          | Type  | Default |

|---------|------------|-------------------|-------|---------|

| 0x1e0   | FOD[0]     | FOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x1e1   | FOD[0]     | FOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x1e2   | FOD[0]     | FOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x1e3   | FOD[0]     | FOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x1e4   | FOD[0]     | FOD_INT_CNFG[4]   | RW    | 0x00    |

| 0x1e5   | FOD[0]     | FOD_INT_CNFG[5]   | RW    | 0x00    |

| 0x1e6   | FOD[0]     | FOD_INT_CNFG[6]   | RW    | 0x00    |

| 0x1e7   | FOD[0]     | FOD_INT_CNFG[7]   | RW    | 0x00    |

| 0x1e8   | FOD[0]     | FOD_PHASE_CNFG[0] | RW    | 0xf0    |

| 0x1e9   | FOD[0]     | FOD_PHASE_CNFG[1] | R/W1S | 0x43    |

| 0x1f0   | FOD[1]     | FOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x1f1   | FOD[1]     | FOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x1f2   | FOD[1]     | FOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x1f3   | FOD[1]     | FOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x1f4   | FOD[1]     | FOD_INT_CNFG[4]   | RW    | 0x00    |

| 0x1f5   | FOD[1]     | FOD_INT_CNFG[5]   | RW    | 0x00    |

| 0x1f6   | FOD[1]     | FOD_INT_CNFG[6]   | RW    | 0x00    |

| 0x1f7   | FOD[1]     | FOD_INT_CNFG[7]   | RW    | 0x00    |

| 0x1f8   | FOD[1]     | FOD_PHASE_CNFG[0] | RW    | 0xf0    |

| 0x1f9   | FOD[1]     | FOD_PHASE_CNFG[1] | R/W1S | 0x43    |

| 0x200   | FOD[2]     | FOD_INT_CNFG[0]   | RW    | 0x64    |

| 0x201   | FOD[2]     | FOD_INT_CNFG[1]   | RW    | 0x00    |

| 0x202   | FOD[2]     | FOD_INT_CNFG[2]   | RW    | 0x00    |

| 0x203   | FOD[2]     | FOD_INT_CNFG[3]   | RW    | 0x00    |

| 0x204   | FOD[2]     | FOD_INT_CNFG[4]   | RW    | 0x00    |

| 0x205   | FOD[2]     | FOD_INT_CNFG[5]   | RW    | 0x00    |

| 0x206   | FOD[2]     | FOD_INT_CNFG[6]   | RW    | 0x00    |

| 0x207   | FOD[2]     | FOD_INT_CNFG[7]   | RW    | 0x00    |

| 0x208   | FOD[2]     | FOD_PHASE_CNFG[0] | RW    | 0xf0    |

| 0x209   | FOD[2]     | FOD_PHASE_CNFG[1] | R/W1S | 0x43    |

## 10.9 OUT Block

Table 26. OUT Block Physical Register Addresses

| Address | Block Name | Register     | Type | Default |

|---------|------------|--------------|------|---------|

| 0x240   | OUT[0]     | ODRV_EN      | RW   | 0x06    |

| 0x242   | OUT[0]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x243   | OUT[0]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x244   | OUT[1]     | ODRV_EN      | RW   | 0x06    |

| 0x246   | OUT[1]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x247   | OUT[1]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x248   | OUT[2]     | ODRV_EN      | RW   | 0x06    |

| 0x24a   | OUT[2]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x24b   | OUT[2]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x24c   | OUT[3]     | ODRV_EN      | RW   | 0x06    |

| 0x24e   | OUT[3]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x24f   | OUT[3]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x250   | OUT[4]     | ODRV_EN      | RW   | 0x06    |

| 0x252   | OUT[4]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x253   | OUT[4]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x254   | OUT[5]     | ODRV_EN      | RW   | 0x06    |

| 0x256   | OUT[5]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x257   | OUT[5]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x258   | OUT[6]     | ODRV_EN      | RW   | 0x06    |

| 0x25a   | OUT[6]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x25b   | OUT[6]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x25c   | OUT[7]     | ODRV_EN      | RW   | 0x06    |

| 0x25e   | OUT[7]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x25f   | OUT[7]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x260   | OUT[8]     | ODRV_EN      | RW   | 0x06    |

| 0x262   | OUT[8]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x263   | OUT[8]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x264   | OUT[9]     | ODRV_EN      | RW   | 0x06    |

| 0x266   | OUT[9]     | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x267   | OUT[9]     | ODRV_CNFG[1] | RW   | 0x00    |

| 0x268   | OUT[10]    | ODRV_EN      | RW   | 0x06    |

| 0x26a   | OUT[10]    | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x26b   | OUT[10]    | ODRV_CNFG[1] | RW   | 0x00    |

| 0x26c   | OUT[11]    | ODRV_EN      | RW   | 0x06    |

| 0x26e   | OUT[11]    | ODRV_CNFG[0] | RW   | 0x3c    |

| 0x26f   | OUT[11]    | ODRV_CNFG[1] | RW   | 0x00    |

## 10.10 BANK Block

Table 27. BANK Block Physical Register Addresses

| Address | Block Name | Register      | Type | Default |

|---------|------------|---------------|------|---------|

| 0x280   | BANK[0]    | OUT_BANK_CNFG | RW   | 0x05    |

| 0x284   | BANK[1]    | OUT_BANK_CNFG | RW   | 0x05    |

| 0x288   | BANK[2]    | OUT_BANK_CNFG | RW   | 0x05    |

| 0x28c   | BANK[3]    | OUT_BANK_CNFG | RW   | 0x05    |

| 0x290   | BANK[4]    | OUT_BANK_CNFG | RW   | 0x05    |

| 0x294   | BANK[5]    | OUT_BANK_CNFG | RW   | 0x05    |

| 0x298   | BANK[6]    | OUT_BANK_CNFG | RW   | 0x05    |

## 10.11 GPI Block

Table 28. GPI Block Physical Register Addresses

| Address | Block Name | Register    | Type | Default |

|---------|------------|-------------|------|---------|

| 0x29c   | GPI[0]     | GPI_CNFG[0] | RW   | 0x7f    |

| 0x29d   | GPI[0]     | GPI_CNFG[1] | RW   | 0x00    |

| 0x29e   | GPI[0]     | GPI_STS     | RO   | 0x00    |

| 0x2a0   | GPI[1]     | GPI_CNFG[0] | RW   | 0x7f    |

| 0x2a1   | GPI[1]     | GPI_CNFG[1] | RW   | 0x00    |

| 0x2a2   | GPI[1]     | GPI_STS     | RO   | 0x00    |

| 0x2a4   | GPI[2]     | GPI_CNFG[0] | RW   | 0x7f    |

| 0x2a5   | GPI[2]     | GPI_CNFG[1] | RW   | 0x00    |

| 0x2a6   | GPI[2]     | GPI_STS     | RO   | 0x00    |

| 0x2a8   | GPI[3]     | GPI_CNFG[0] | RW   | 0x7f    |

| 0x2a9   | GPI[3]     | GPI_CNFG[1] | RW   | 0x00    |

| 0x2aa   | GPI[3]     | GPI_STS     | RO   | 0x00    |

## 10.12 GPIO Block

Table 29. GPIO Block Physical Register Addresses

| Address | Block Name | Register     | Type | Default |

|---------|------------|--------------|------|---------|

| 0x2ac   | GPIO[0]    | GPIO_CNFG[0] | RW   | 0x90    |

| 0x2ad   | GPIO[0]    | GPIO_CNFG[1] | RW   | 0x04    |

| 0x2ae   | GPIO[0]    | GPIO_STS     | RO   | 0x00    |

| 0x2b0   | GPIO[1]    | GPIO_CNFG[0] | RW   | 0x90    |

| 0x2b1   | GPIO[1]    | GPIO_CNFG[1] | RW   | 0x04    |

| 0x2b2   | GPIO[1]    | GPIO_STS     | RO   | 0x00    |

| 0x2b4   | GPIO[2]    | GPIO_CNFG[0] | RW   | 0x90    |

**Table 29. GPIO Block Physical Register Addresses (Cont.)**

| Address | Block Name | Register     | Type | Default |

|---------|------------|--------------|------|---------|

| 0x2b5   | GPIO[2]    | GPIO_CNFG[1] | RW   | 0x04    |

| 0x2b6   | GPIO[2]    | GPIO_STS     | RO   | 0x00    |

| 0x2b8   | GPIO[3]    | GPIO_CNFG[0] | RW   | 0x90    |

| 0x2b9   | GPIO[3]    | GPIO_CNFG[1] | RW   | 0x04    |

| 0x2ba   | GPIO[3]    | GPIO_STS     | RO   | 0x00    |

| 0x2bc   | GPIO[4]    | GPIO_CNFG[0] | RW   | 0x90    |

| 0x2bd   | GPIO[4]    | GPIO_CNFG[1] | RW   | 0x04    |

| 0x2be   | GPIO[4]    | GPIO_STS     | RO   | 0x00    |

## 10.13 SSC Block

**Table 30. SSC Block Physical Register Addresses**

| Address | Block Name | Register    | Type | Default |

|---------|------------|-------------|------|---------|

| 0x300   | SSC[0]     | SSC_CNFG[0] | RW   | 0x8c    |

| 0x301   | SSC[0]     | SSC_CNFG[1] | RW   | 0x2b    |

| 0x302   | SSC[0]     | SSC_CNFG[2] | RW   | 0x51    |

| 0x303   | SSC[0]     | SSC_CNFG[3] | RW   | 0x00    |

| 0x304   | SSC[1]     | SSC_CNFG[0] | RW   | 0x8c    |

| 0x305   | SSC[1]     | SSC_CNFG[1] | RW   | 0x2b    |

| 0x306   | SSC[1]     | SSC_CNFG[2] | RW   | 0x51    |

| 0x307   | SSC[1]     | SSC_CNFG[3] | RW   | 0x00    |

## 10.14 INT Block

**Table 31. INT Block Physical Register Addresses**

| Address | Block Name | Register    | Type | Default |

|---------|------------|-------------|------|---------|

| 0x308   | INT        | SCRATCH0[0] | RW   | 0x00    |

| 0x309   | INT        | SCRATCH0[1] | RW   | 0x00    |

| 0x30a   | INT        | SCRATCH0[2] | RW   | 0x00    |

| 0x30b   | INT        | SCRATCH0[3] | RW   | 0x00    |

| 0x30c   | INT        | INT_EN[0]   | RW   | 0x00    |

| 0x30d   | INT        | INT_EN[1]   | RW   | 0x00    |

| 0x30e   | INT        | INT_EN[2]   | RW   | 0x00    |

| 0x30f   | INT        | INT_EN[3]   | RW   | 0x00    |

| 0x310   | INT        | INT_STS[0]  | RO   | 0x00    |

| 0x311   | INT        | INT_STS[1]  | RO   | 0x00    |

Table 31. INT Block Physical Register Addresses (Cont.)

| Address | Block Name | Register   | Type | Default |

|---------|------------|------------|------|---------|

| 0x312   | INT        | INT_STS[2] | RO   | 0x00    |

| 0x313   | INT        | INT_STS[3] | RO   | 0x00    |

## 11. Register Descriptions

### 11.1 Global Registers

Table 32. VENDOR\_ID - Vendor ID

| Bit Field | Field Name  | Type | Default Value | Description                                                                                                                                                                                       |

|-----------|-------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12     | dev_id_type | RO   | 0x1           | Device ID Block Type.<br>A value of 0x1 indicates that this register is followed by a 16-bit Device ID register and an 16-bit Device Revision register, and a 16-bit Device Programming register. |

| 11        | reserved    | RO   | 0x0           | Reserved.                                                                                                                                                                                         |

| 10:0      | vendor_id   | RO   | 0x33          | Vendor ID.<br>Renesas/IDT JEDEC ID.                                                                                                                                                               |

Table 33. DEVICE\_ID - Device ID

| Bit Field | Field Name | Type | Default Value | Description                                                                                                                |

|-----------|------------|------|---------------|----------------------------------------------------------------------------------------------------------------------------|

| 15:0      | device_id  | RW   | 0x0           | Device ID.<br>For default value refer to Product Identification. This field is writeable so it can be configured from OTP. |

Table 34. DEVICE\_REV - Device Revision

| Bit Field | Field Name      | Type | Default Value | Description                                                                                                                                                                      |

|-----------|-----------------|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0      | device_revision | RO   | 0x0443        | Device Revision.<br>Decode as follows: <ul style="list-style-type: none"><li>▪ 0x0111 = First silicon; not released.</li><li>▪ 0x0333 = Rev A</li><li>▪ 0x0443 = Rev B</li></ul> |

Table 35. DEVICE\_PGM - Device Programming

| Bit Field | Field Name | Type | Default Value | Description                                                                                                                                                                                                                                                                                                                           |

|-----------|------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|