# **Low-Cost 16-Pin Frequency Generator**

## **General Description**

The **9154A** is a 0.8mm version of the industry leading 9154. Like the 9154, the **9154A** is a low-cost frequency generator designed for general purpose PC and disk drive applications. However, because the **9154A** uses 0.8mm technology and the latest phase-locked loop architecture, it offers performance advantages that enable the device to be sold into Pentium<sup>™</sup> systems.

The 9154A guarantees a 45/55 duty cycle over all frequencies. In addition, a worst case jitter of ±250ps is specified at Pentium frequencies.

The CPU clock offers the unique feature of smooth, glitch-free transitions from one frequency to the next, making this the ideal device to use when slowing the CPU speed. The **9154A** makes a gradual transition between frequencies so that it obeys the Intel cycle-to-cycle timing specifications for 486 and Pentium systems.

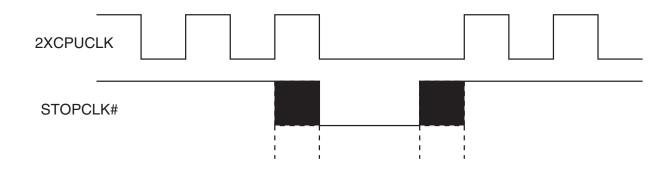

The **9154A**-42 and **9154A**-43 devices offer features specifically for green PCs. The **9154A**-42 and -43 have a single pin that, when pulled low, will smoothly slow the 2XCPU clock to 8 MHz. This is ideal for dynamic DX microprocessors. The **9154A**-43 not only has the slow clock feature, but also offers a glitch-free stop clock for static SX microprocessors. The STOPCLK# pin, when pulled low, enables the 2XCPU clock to go low only after completing its last full cycle. The clock continues to run internally, and will be output again on the first full cycle immediately following stop clock disable. The simultaneous 2X and 1X CPU clocks offer controlled skew to within 500ps of each other (-42 only).

ICS has been shipping motherboard frequency generators since April 1990, and is the leader in the area of multiple output clocks on a single chip. Consult ICS for all your clock generation needs.

### **Features**

- Compatible with 386, 486 and Pentium CPUs

- 45/55 Duty cycle

- Runs up to 66 MHz at 3.3V

- Single pin can slow clock to 8 MHz (on -42 and -43)

- Single pin can stop the CPU clock glitch-free (on -43)

- Very low jitter, ±250ps for Pentium frequencies

- 1X and 2X CPU clocks skew controlled to ±250ps (-42 only)

- Smooth transitions between all CPU frequencies

- Slow frequency ramp at power-on avoids CPU lock-up

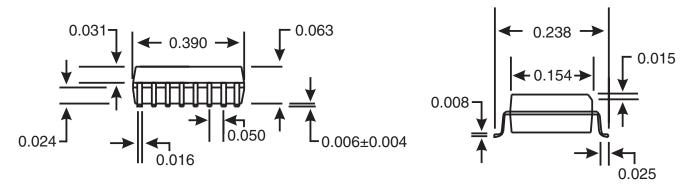

- 16-pin 150-mil skinny SOIC packages

- 0.8μm CMOS technology

## **Applications**

Computer motherboards: The **9154A** replaces crystals and oscillators, saving board space, component cost, part count and inventory costs. It produces a switchable CPU clock and up to four fixed clocks to drive floppy disk, communications, super I/O, Bus, and/or keyboard devices. The small package and 3.3V operation is perfect for handheld computers.

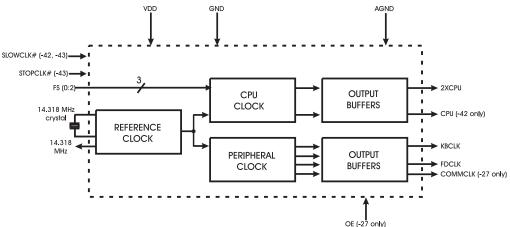

# **Block Diagram**

0174E-03/18/08

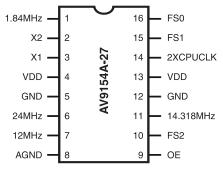

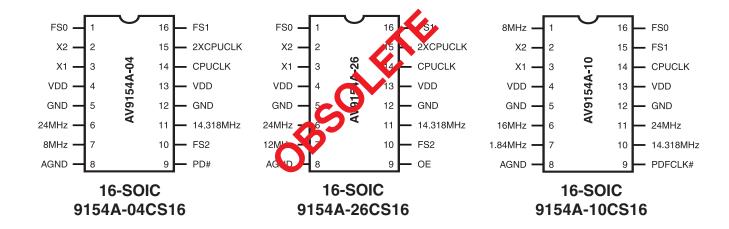

# **Pin Configuration**

16-SOIC 9154A-27CS16

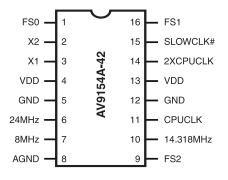

16-SOIC 9154A-42CS16

Description of new pin:

SLOWCLK# forces 2XCPUCLK output to ramp smoothly to 8MHz and CPUCLK output to 4 MHz when pulled low.

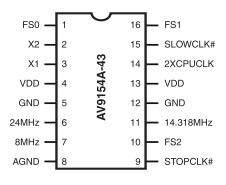

16-SOIC 9154A-43CS16

Description of new pis:

SLOWCLK# forces 2XCPUCLK output to ramp smoothly to 8MHz when pulled low. STOPCLK# provides gilitch-free stop of the 2XCPUCLK output when pulled low. When raised back high, the 2XCPUCLK output clock resumes full speed operation (no clock frequency ramp up since the internal VCO is not stopped).

0174E-03/18/08

Stop Clock Feature

The 9154A-43 incorporates a unique stop clock feature compatible with static logic processors. When the stop clock pin goes low, the 2XCPUCLK will go low after the next occurring falling edge. When STOPCLK again goes high, 2XCPUCLK resumes on the next rising edge of the internal clock. This feature enables fast, glitch-free starts and stops of the 2XCPUCLK and is guaranteed that the CPU does not receive any short period clocks.

**Pin Descriptions**Frequencies based upon 14.318 MHz input)

| PIN NUMBER |     |     | PIN NAME | TYPE | DESCRIPTION |             |   |                                                         |

|------------|-----|-----|----------|------|-------------|-------------|---|---------------------------------------------------------|

| -4         | -10 | -26 | -27      | -42  | -43         |             |   |                                                         |

| 4          | 4   | 4   | 4        | 4    | 4           | VDD         | Р | Digital power (3.3 or 5V).                              |

| 13         | 13  | 13  | 13       | 13   | 13          | VDD         | Р | Digital power (3.3 or 5V).                              |

| 5          | 5   | 5   | 5        | 5    | 5           | GND         | Р | Digital ground.                                         |

| 12         | 12  | 12  | 12       | 12   | 12          | GDD         | Р | Digital ground.                                         |

| 8          | 8   | 8   | 8        | 8    | 8           | AGND        | Р | Analog ground.                                          |

| 1          | 16  | 1   | 16       | 1    | 1           | FS0         | 1 | Frequency select 0 for CPU clock                        |

| _ '        | 10  | '   | 10       | '    |             | 100         | • | (has internal pull-up).*                                |

| 16         | 15  | 16  | 15       | 16   | 16          | FS1         | 1 | Frequency select 1 for CPU clock                        |

| 10         | 10  | 10  | 10       | 10   | 10          | 101         | ' | (has internal pull-up).*                                |

| 10         | _   | 10  | 10       | 9    | 10          | FS2         | 1 | Frequency select 2 for CPU clock                        |

|            |     |     |          | Ü    | 10          |             | • | (has internal pull-up).*                                |

| -          | -   | 9   | 9        | -    | -           | OE          | ı | Tristates outputs when low (has internal pull-up).*     |

| _          | _   | _   | _        | 15   | 15          | SLOWCLK#    | 1 | Slows 2XCPU clock to 8 MHz (active low)                 |

|            |     |     |          | 10   | 10          | OLOW OLIVII |   | (has internal pull-up).                                 |

| _          | _   | _   | _        | _    | 9           | STOPCLK#    | 1 | Stops 2XCPU clock glitch-free (active low)              |

|            |     |     |          |      |             |             | • | (has internal pull-up).                                 |

| 3          | 3   | 3   | 3        | 3    | 3           | X1          | I | Crystal In.                                             |

| 2          | 2   | 2   | 2        | 2    | 2           | X2          | 0 | Crystal Out.                                            |

| 11         | 10  | 11  | 11       | 10   | 11          | 14.318 MHz  | 0 | 14.318 MHz reference clock output.                      |

| -          | 7   |     | 1        | -    | -           | 1.84 MHz    | 0 | 1.84 MHz (comm) clock output.                           |

| 6          | 11  | 6   | 6        | 6    | 6           | 24 MHz      | 0 | 24 MHz (floppy disk) clock output.                      |

| -          | 6   | -   | -        | -    | -           | 16 MHz      | 0 | 16 MHz clock output.                                    |

| -          | -   | 7   | 7        | -    | -           | 12 MHz      | 0 | 12 MHz keyboard clock output.                           |

| 7          | 1   | ı   | ı        | 7    | 7           | 8 MHz       | 0 | 8 MHz keyboard clock output.                            |

| 14         | 14  | 14  | -        | 11   | -           | CPUCLK      | 0 | CPU clock output.                                       |

| 15         | -   | 15  | 14       | 14   | 14          | 2XCPUCLK    | 0 | 2X CPU clock output.                                    |

| 9          | -   | -   | -        | -    | -           | PD#         | I | Power-Down All (active low) (has internal pull-up).     |

| -          | 9   | -   | -        | -    | -           | PDFCLK#     | I | Power-Down Fixed Clock (1.84, 8, 16, 24) (active low).* |

### Note:

Internal Pull-up Resistors.

\* -04 and -10 have no pull-ups or frequency select pins

\*\* -10 has no pull-up or Pin 9 PDFCLK

| Clock Tables<br>(using 14.318 MHz input, all frequencies in MHz) |                                 |   |                 |          |        |       |  |  |

|------------------------------------------------------------------|---------------------------------|---|-----------------|----------|--------|-------|--|--|

| FS2                                                              | FS1 FS0 -27 -42 -42 -42 -42 -42 |   | -43<br>2XCPUCLK |          |        |       |  |  |

|                                                                  |                                 |   | ZAGFUGLK        | 2XCPUCLK | CPUCLK | ٨     |  |  |

| 0                                                                | 0                               | 0 | 75*             | 16       | 8      | 16    |  |  |

| 0                                                                | 0                               | 1 | 32              | 40       | 20     | 40    |  |  |

| 0                                                                | 1                               | 0 | 60              | 33.33    | 16.67  | 33.33 |  |  |

| 0                                                                | 1                               | 1 | 40              | 25       | 12.5   | 25    |  |  |

| 1                                                                | 0                               | 0 | 50              | 60       | 30     | 60    |  |  |

| 1                                                                | 0                               | 1 | 66.66           | 20       | 10     | 20    |  |  |

| 1                                                                | 1                               | 0 | 80*             | 66.66    | 33.33  | 66.66 |  |  |

| 1                                                                | 1                               | 1 | 52              | 50       | 25     | 50    |  |  |

| Actual Frequencies (using 14.318 MHz input, all frequencies in MHz) |     |      |          |          |        |          |  |  |

|---------------------------------------------------------------------|-----|------|----------|----------|--------|----------|--|--|

| FS2                                                                 | FS1 | FS0  | -27      | -42      | 2      | -43      |  |  |

| 1 32                                                                | F31 | 1 30 | 2XCPUCLK | 2XCPUCLK | CPUCLK | 2XCPUCLK |  |  |

| 0                                                                   | 0   | 0    | 75.17*   | 16.00    | 8.00   | 16.00    |  |  |

| 0                                                                   | 0   | 1    | 31.94    | 40.09    | 20.05  | 40.09    |  |  |

| 0                                                                   | 1   | 0    | 60.14    | 33.41    | 16.71  | 33.41    |  |  |

| 0                                                                   | 1   | 1    | 40.09    | 25.06    | 12.55  | 25.06    |  |  |

| 1                                                                   | 0   | 0    | 50.11    | 60.14    | 30.07  | 60.14    |  |  |

| 1                                                                   | 0   | 1    | 66.48    | 20.05    | 10.03  | 20.05    |  |  |

| 1                                                                   | 1   | 0    | 80.18*   | 66.48    | 33.24  | 66.48    |  |  |

| 1                                                                   | 1   | 1    | 51.90    | 50.11    | 25.06  | 50.11    |  |  |

| Fixed Clock Output        |  |  |  |  |  |

|---------------------------|--|--|--|--|--|

| <b>Actual Frequencies</b> |  |  |  |  |  |

| (using 14.318 MHz input,  |  |  |  |  |  |

| all frequencies in MHz)   |  |  |  |  |  |

| 14.318                    |  |  |  |  |  |

| 1.84                      |  |  |  |  |  |

| 24.0                      |  |  |  |  |  |

| 12.0                      |  |  |  |  |  |

| 8.0                       |  |  |  |  |  |

| all frequencies in MHz) |       |      |        |  |  |  |

|-------------------------|-------|------|--------|--|--|--|

| FO(0,0)                 | -     | 04   | -10    |  |  |  |

| FS(3:0)                 | 2XCPU | CPU  | CPUCLK |  |  |  |

| 0                       | 100*  | 50*  | PDCPU  |  |  |  |

| 1                       | 80*   | 40*  | 40     |  |  |  |

| 2                       | 66.6  | 33.3 | 50     |  |  |  |

| 3                       | 50    | 25   | 66.6   |  |  |  |

| 4                       | 40    | 20   | -      |  |  |  |

| 5                       | 32    | 16   | -      |  |  |  |

| 6                       | 24    | 12   | -      |  |  |  |

| 7                       | 16    | 8    | -      |  |  |  |

| -                       |       |      |        |  |  |  |

**Clock Tables in MHz**

**for -04 and -10** (using 14.318 MHz input,

| Clock Table for 9154A-26<br>(using 14.318 MHz input,<br>all frequencies in MHz) |         |        |  |  |  |  |

|---------------------------------------------------------------------------------|---------|--------|--|--|--|--|

| FS(2:0)                                                                         | 2XCPU   | CPUCLK |  |  |  |  |

| 1-3(2.0)                                                                        | (MHz)   | (MHz)  |  |  |  |  |

| 0                                                                               | 100.23* | 50.11  |  |  |  |  |

| 1                                                                               | 80.18*  | 40.09  |  |  |  |  |

| 2                                                                               | 66.48*  | 33.24  |  |  |  |  |

| 3                                                                               | 50.11   | 25.06  |  |  |  |  |

| 4                                                                               | 40.09   | 20.05  |  |  |  |  |

| 5                                                                               | 32.22   | 16.11  |  |  |  |  |

| 6                                                                               | 24.23   | 12.12  |  |  |  |  |

| 7                                                                               | 15.75   | 7.88   |  |  |  |  |

|                                                                                 |         | -      |  |  |  |  |

# **Absolute Maximum Ratings**

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stess specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

## **Electrical Characteristics at 3.3 V**

$V_{DD} = 3.3 \text{ V} \pm 10\%$ ,  $T_A = 0 - 70 \, ^{\circ}\text{C}$  unless otherwise stated

|                              |        | DC Characteristics                |          |          |         |       |

|------------------------------|--------|-----------------------------------|----------|----------|---------|-------|

| PARAMETER                    | SYMBOL | TEST CONDITIONS                   | MIN      | TYP      | MAX     | UNITS |

| Input Low Voltage            | VIL    |                                   | -        | -        | 0.2 VDD | V     |

| Input High Voltage           | VIH    |                                   | 0.7 V    | -        | -       | V     |

| Input Low Current            | IIL    | VIN = 0V (pull-up pin)            | -        | 2.5      | 7       | Α     |

| Input High Current           | IIH    | VIN = VDD                         | -5       | -        | 5       | Α     |

| Output Low Voltage           | VOL    | IOL = 6mA                         | -        | 0.05 VDD | 0.1 VDD | V     |

| Output High Voltage1         | VOH    | IOH = -4mA                        | 0.85 VDD | 0.94 VDD | -       | V     |

| Output Low Current1          | IOL    | VOL = 0.2VDD                      | 15       | 24       | -       | mΑ    |

| Output High Current1         | IOH    | VOH = 0.7VDD                      | -        | -13      | -8      | mΑ    |

| Supply Current               | IDD    | unloaded, 60 MHz                  | -        | 16       | 34      | mΑ    |

| Output Frequency Change over | FD     | With respect to typical frequency | _        | 0.002    | 0.01    | %     |

| Supply and Temperature1      | 10     | With respect to typical frequency | _        | 0.002    | 0.01    | 70    |

| Short circuit current1       | ISC    | each output clock                 | 20       | 30       | -       | mΑ    |

| Input Capacitance1           | CI     | except X1, X2                     | -        | -        | 10      | рF    |

| Load Capacitance1            | CL     | pins X1, X2                       | -        | 20       | -       | рF    |

| Pull-up Resistor1            | Rpu    | at VDD - 0.5V                     | -        | 620      | 900     | k ohm |

### Notes:

1. Parameter is guaranteed by design and characterization.

# Electrical Characteristics at 3.3 V $V_{DD} = 3.3 \text{ V} \pm 10\%$ , $V_{A} = 0.70 \, ^{\circ}\text{C}$ unless otherwise stated

| AC Characteristics                                          |                   |                  |       |        |       |       |  |

|-------------------------------------------------------------|-------------------|------------------|-------|--------|-------|-------|--|

| PARAMETER                                                   | SYMBOL            | TEST CONDITIONS  | MIN   | TYP    | MAX   | UNITS |  |

| Input Clock Rise<br>Time <sup>1</sup>                       | tıCr              |                  | -     | -      | 20    | ns    |  |

| Input Clock Fall<br>Time <sup>1</sup>                       | tıcı              |                  | -     | -      | 20    | ns    |  |

| Rise time, 20% to 80% V <sub>DD</sub> <sup>1</sup>          | tr                | 15pF load        | -     | 2.2    | 3.5   | ns    |  |

| Fall time, 80% to 20% V <sub>DD</sub> 1                     | tf                | 15pF load        | -     | 1.2    | 2.5   | ns    |  |

| Duty cycle at 50% V <sub>DD</sub> <sup>1</sup>              | dt                | 15pF load        | 40/60 | 48/52  | 60/40 | %     |  |

| Duty cycle, reference clocks <sup>1</sup>                   | dŧ                | 15pF load        | 50/65 | 43/57  | 65/50 | %     |  |

| Jitter, one sigma, 20-<br>66 MHz clocks <sup>1</sup>        | t <sub>j</sub> 1s | 10,000 cycles    | -     | 100    | 200   | ps    |  |

| Jitter, one sigma,<br>clocks below 20<br>MHz <sup>1</sup>   | <b>t</b> jls      | 10,000 cycles    | -     | 1.0    | 2.0   | %     |  |

| Jitter, absolute, 20-66<br>MHz clocks <sup>1</sup>          | <b>t</b> jab      | 10,000 cycles    | -350  | -      | 350   | ps    |  |

| Jitter, absolute,<br>clocks below 20<br>MHz <sup>1</sup>    | <b>t</b> jab      | 10,000 cycles    | -     | 1.5    | 4.0   | %     |  |

| Input Frequency <sup>1</sup>                                | fin               |                  | 2     | 14.318 | 32    | MHz   |  |

| Maximum Output<br>Frequency <sup>1</sup>                    | fout              |                  | 70    | -      | -     | MHz   |  |

| Clock skew between<br>CPU and 2XCPU<br>outputs <sup>1</sup> | Tsk               | 9154A-42         | -     | 220    | 500   | ps    |  |

| Power-up Time <sup>1</sup>                                  | <b>t</b> tPO      | off to 50 MHz    | -     | 6      | 12    | ms    |  |

| Frequency Transition<br>Time <sup>1</sup>                   | tft               | from 8 to 50 MHz | -     | 4.5    | 10    | ms    |  |

### Notes:

<sup>1.</sup> Parameter is guaranteed by design and characterization. Not subject to production testing.

# **Electrical Characteristics at 5.0 V**

$V_{DD} = +5 \pm 10\% \text{ V}, T_A = 0 - 70^{\circ}\text{C}$  unless otherwise stated

| DC Characteristics                                                     |        |                                   |     |       |      |       |  |

|------------------------------------------------------------------------|--------|-----------------------------------|-----|-------|------|-------|--|

| PARAMETER                                                              | SYMBOL | TEST CONDITIONS                   | MIN | TYP   | MAX  | UNITS |  |

| Input Low Voltage                                                      | VIL    | VDD=5 V                           | -   | -     | 0.8  | V     |  |

| Input High Voltage                                                     | VIH    | V <sub>DD</sub> =5 V              | 2.0 | -     | -    | V     |  |

| Input Low Current                                                      | lıL    | VIN=0 V (pull-up pin)             | -   | 6     | 15   | Α     |  |

| Input High Current                                                     | Іін    | VIN = VDD                         | -5  | -     | 5    | А     |  |

| Output Low Voltage                                                     | Vol    | IoL = 10 mA                       | -   | 0.15  | 0.4  | V     |  |

| Output High Voltage <sup>1</sup>                                       | Vон    | Iон = -30 mA                      | 2.4 | 3.7   | -    | V     |  |

| Output Low Current <sup>1</sup>                                        | loL    | Vol = 0.8 V                       | 25  | 45    | -    | mA    |  |

| Output High Current <sup>1</sup>                                       | Іон    | Vон = 2.4 V                       | -   | -53   | -35  | mA    |  |

| Supply Current                                                         | IDD    | unloaded, 66 MHz                  | -   | 25    | 50   | mA    |  |

| Output Frequency<br>Change over Supply<br>and Temperature <sup>1</sup> | FD     | with respect to typical frequency | -   | 0.002 | 0.01 | %     |  |

| Short circuit current <sup>1</sup>                                     | Isc    | each output clock                 | 25  | 40    | -    | mA    |  |

| Input Capacitance <sup>1</sup>                                         | Cı     | except X1, X2                     | -   | -     | 10   | pF    |  |

| Load Capacitance <sup>1</sup>                                          | CL     | pins X1, X2                       | -   | 20    | -    | pF    |  |

| Pull-up Resistor <sup>1</sup>                                          | Rpu    | A + V <sub>DD</sub> -1 V          | -   | 400   | 700  | k ohm |  |

### Notes

<sup>1.</sup> Parameter is guaranteed by design and characterization. Not subject to production testing.

# **Electrical Characteristics at 5.0 V**

$V_{DD} = \ +5 \pm 10\% \ V, \, T_{A} = \ 0 - 70^{o} C$  unless otherwise stated

|                                                             | AC Characteristics |                                    |       |        |       |       |  |  |

|-------------------------------------------------------------|--------------------|------------------------------------|-------|--------|-------|-------|--|--|

| PARAMETER                                                   | SYMBOL             | TEST CONDITIONS                    | MIN   | TYP    | MAX   | UNITS |  |  |

| Input Clock Rise<br>Time <sup>1</sup>                       | tıCr               |                                    | -     | -      | 20    | ns    |  |  |

| Input Clock Fall<br>Time <sup>1</sup>                       | ticf               |                                    | -     | -      | 20    | ns    |  |  |

| Output Rise time, 0.8 to 2.0V <sup>1</sup>                  | tr                 | 15pF load                          | -     | 1.5    | 2     | ns    |  |  |

| Rise time, 20% to 80% V <sup>1</sup>                        | tr                 | 15pF load                          | -     | 2.0    | 3     | ns    |  |  |

| Output Fall time, 2.0 to 0.8V <sup>1</sup>                  | tf                 | 15pF load                          | -     | 0.5    | 1.5   | ns    |  |  |

| Fall time, 80% to 20% V <sup>1</sup>                        | tf                 | 15pF load                          | -     | 2.0    | 3.0   | ns    |  |  |

| Duty cycle at 1.4V <sup>1</sup>                             | dt                 | 15pF load, V <sub>DD</sub> = 5V±5% | 45/55 | 48/52  | 55/45 | %     |  |  |

| Duty cycle, reference clocks <sup>1</sup>                   | dŧ                 | 15 pF load                         | 40/65 | 43/57  | 65/40 | %     |  |  |

| Jitter, one sigma, 20<br>MHz- 80 MHz clocks <sup>1</sup>    | t <sub>j1s</sub>   | 10,000 cycles                      | -     | 70     | 140   | ps    |  |  |

| Jitter, one sigma,<br>clocks below 20<br>MHz <sup>1</sup>   | tjis               | 10,000 cycles                      | -     | 0.8    | 2.0   | %     |  |  |

| Jitter, absolute, 20<br>MHz- 80 MHz clocks <sup>1</sup>     | tjab               | 10,000 cycles                      | -250  | -      | 250   | ps    |  |  |

| Jitter, absolute,<br>clocks below 20<br>MHz <sup>1</sup>    | tjab               | 10,000 cycles                      | -     | 1.0    | 3.0   | %     |  |  |

| Input Frequency                                             | fin                |                                    | 2     | 14.318 | 32    | MHz   |  |  |

| Maximum Output<br>Frequency <sup>1</sup>                    | fout               |                                    | 140   | -      | -     | MHz   |  |  |

| Clock skew between<br>CPU and 2XCPU<br>outputs <sup>1</sup> | Tsk                | 9154A-42                           | -     | 140    | 400   | ps    |  |  |

| Power-up Time <sup>1</sup>                                  | ttpo               | to 80 MHz                          | -     | 8      | 15    | ms    |  |  |

| Frequency Transition<br>Time <sup>1</sup>                   | tft                | from 8 to 66.66 MHz                | -     | 6.5    | 12    | ms    |  |  |

Notes:

1. Parameter is guaranteed by design and characterization. Not subject to production testing.

16-Pin SOIC Package

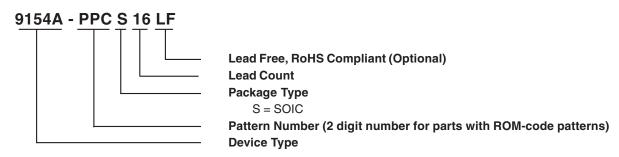

# **Ordering Information**

9154A-04CS16 9154A-27CS16 9154A-43CS16 9154A-10CS16 9154A-42CS16

Example:

0174E-03/18/08

**Revision History**

| Rev. | Issue Date | Description                       | Page # |

|------|------------|-----------------------------------|--------|

| С    | 4/6/2006   | Added LF Ordering Information     | 10     |

| D    | 1/24/2008  | Removed DIP Ordering Information. | -      |

| Е    | 3/18/2008  | Removed reference to "AV".        | -      |

|      |            |                                   |        |

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.