# **RZ/A1LU Group**

Example of Booting from Serial Flash Memory

# Abstract

This application note describes an example of booting from the serial flash memory via the SPI multi-I/O bus controller (hereinafter called "SPIBSC") of by using the boot mode 1 (serial flash boot) function.

#### Products

RZ/A1LU

When using this application note with other Renesas MCUs, careful evaluation is recommended after making modifications to comply with the alternate MCU.

R01AN3093EJ0100

Rev.1.00 Nov. 18, 2016

# Contents

| 1. Specifications                                                                |      |

|----------------------------------------------------------------------------------|------|

| 1.1 Booting from Serial Flash Memory                                             |      |

| 1.2 Peripheral Functions Used                                                    | 5    |

| 2. Operation Confirmation Conditions                                             | 6    |

| 3. Reference Application Notes                                                   | 6    |

| 4. Hardware                                                                      | 7    |

| 4.1 Hardware Configuration                                                       |      |

| 4.2 Pins Used                                                                    |      |

| 5. Software                                                                      |      |

| 5.1 Operation Overview                                                           |      |

| 5.1.1 Terms Related to Serial Flash Boot                                         |      |

| 5.1.2 Operation Overview of Sample Code Overall                                  | . 10 |

| 5.1.3 Operation Overview of SPIBSC Initial setting program                       |      |

| 5.1.4 Application Program (User Program)                                         |      |

| 5.2 Peripheral Functions and Memory Allocation in Sample Code                    | . 17 |

| 5.2.1 Setting for Peripheral Functions                                           | . 17 |

| 5.2.2 Memory Mapping                                                             | . 18 |

| 5.2.3 Section Assignment in Sample Code                                          | . 19 |

| 5.3 Interrupt Used                                                               | . 22 |

| 5.4 Constants Used by the SPIBSC Initial Setting Program                         | . 23 |

| 5.5 List of Structures/Unions Used by the SPIBSC Initial Setting Program         | . 26 |

| 5.6 List of Variables for SPIBSC Initial Setting Program                         |      |

| 5.7 List of Functions Used in the SPIBSC Initial Setting Program                 |      |

| 5.8 SPIBSC Initial Setting Program Functional Specifications                     |      |

| 5.9 SPIBSC Initial Setting Program Flowcharts                                    |      |

| 5.9.1 SPIBSC Initial setting program (Overall)                                   |      |

| 5.9.2 SPIBSC Initial Setting Program 1 (STEP1)                                   |      |

| 5.9.3 SPIBSC Initial Setting Program 2 (STEP2)                                   | . 48 |

| 6. Application Example                                                           | . 50 |

| 6.1 Operation of the Sample Code Used in its Initial State                       |      |

| 6.2 Changing the Sample Code without Changing the Serial Flash Memory            |      |

| 6.2.1 Changing to 2-Serial-Flash-Memory-Device Configuration (8-bit Access Mode) |      |

| 6.2.2 Changing the Access to Serial Flash Memory into DDR Transfer Mode          |      |

| 6.3 Changing the Sample Code When Changing the Serial Flash Memory               |      |

| 6.3.1 Signal Output when a Read Command is Issued                                |      |

| 6.3.2 Setting up the Serial Flash Memory Registers                               |      |

| 6.3.3 Serial Flash Memory Write Enable                                           |      |

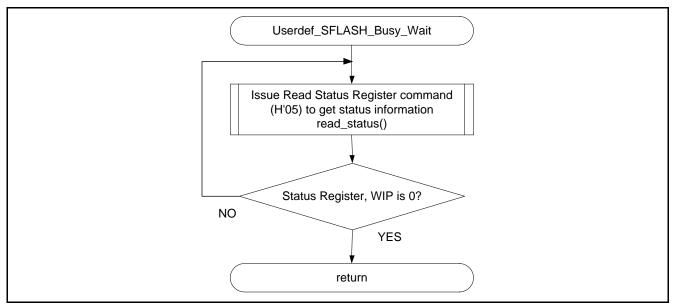

| 6.3.4 Serial Flash Memory Write Completion Wait                                  | . 66 |

| 7. Sample Code                                                                   | . 67 |

| 8. Reference Documents                                                           | . 67 |

# 1. Specifications

# 1.1 Booting from Serial Flash Memory

In boot mode 1, the RZ/A1LU boots from the serial flash memory allocated to the SPI multi-I/O bus space (hereinafter called "serial flash boot"). Figure 1.1 shows the Conceptual Diagram of Serial Flash Boot Operation.

| Boot startup on-chip ROM<br>Boot startup on-chip ROM<br>program<br>(1) Execute boot startup on-chip ROM program.                                                   | e of module standby)<br>SPI multi-I/O bus<br>controller<br>(SPIBSC) | <ul><li>(3) Directly execute serial flash<br/>memory initial setting program.</li><li>(4) Transfer to large-capacity<br/>on-chip RAM.</li></ul>                                            | Serial flash memory<br>SPIBSC initial setting<br>program |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| (1) Execute boot startup on-chip ROM program.<br>(5) Branch to start of SPIBSC<br>initial setting program<br>(6) Change SPIBSC settings.<br>SPIBSC initial setting |                                                                     | <ul> <li>(7) Change serial flash<br/>memory settings (Quad<br/>operation setting and 4-<br/>byte addressing settings).</li> <li>(8) Branch to start of application<br/>program.</li> </ul> | Application program<br>(User program)                    |

Figure 1.1 Conceptual Diagram of Serial Flash Boot Operation

The conceptual diagram of serial flash boot operation is described below.

- (1) When the RZ/A1LU starts up by serial flash boot, the boot startup on-chip ROM program runs after power-on reset is canceled.

- (2) The boot startup on-chip ROM program sets the SPIBSC to external address space read mode to enable to directly run programs allocated to the SPI multi-I/O bus space.

- (3) The serial flash memory initial setting program is executed.

- (4) The SPIBSC initial setting program is transferred from the serial flash memory to the large-capacity on-chip RAM.

- (5) Execution branches to the start address of the SPIBSC initial setting program, which has been transferred to the large-capacity on-chip RAM.

- (6) The SPIBSC initial setting program changes the SPIBSC settings.

- (7) The SPIBSC initial setting program changes the serial flash memory settings.

- (8) Execution branches to the start address of the application program.

The boot startup on-chip ROM program makes settings to allow common access to typical serial flash memory devices, so it is necessary to provide the optimal settings to the serial flash memory used by the customer. For the purpose of this setting, this application note describes how to allocate the SPIBSC initial setting program which provides optimal settings to the serial flash memory used by the customer to the start address (H'1800\_0000) of the SPI multi-I/O bust space branched by the boot startup on-chip ROM program, and then branch to the customer-created application program (user program) after optimal settings are provided by the SPIBSC initial setting program.

This application provides a method for providing optimal settings to the serial flash memory used by the customer using the SPIBSC initial setting program and a method for creating the application program (user program).

# 1.2 Peripheral Functions Used

This sample code not only configures the SPIBSC but also initializes the clock pulse oscillator, interrupt controller, bus state controller, general-purpose input/output ports, memory management unit, primary cache (L1 cache), and secondary cache (L2 cache).

In this application note, the Clock pulse generator is referred to as the CPG, the Interrupt controller as the INTC, the Bus state controller as the BSC, the OS timer as the OSTM, the Serial communication interface with FIFO as the SCIF, the General I/O ports as the PORT, the Power-down modes as the STB, and the Memory management unit as the MMU.

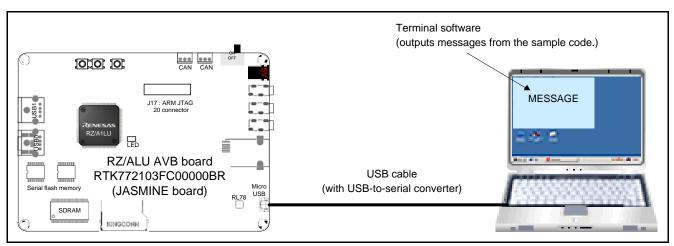

Table 1.1 summarizes Peripheral Functions and Their Applications, and Figure 1.2 shows Operating Environment for the sample code.

| Peripheral Function                                     | Application                                                                                                                                                                |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI multi-I/O bus controller (SPIBSC)                   | When set to external address space read mode, it generates signals that enable the CPU to directly read from serial flash memory connected to the SPI multi-I/O bus space. |

| Clock pulse generator (CPG)                             | Generate the operating frequency of the RZ/A1LU.                                                                                                                           |

| Interrupt controller (INTC)                             | Control OSTM channel 0 interrupt.                                                                                                                                          |

| Bus state controller (BSC)                              | Generate signals for using the SDRAM in the CS3 space (Note).                                                                                                              |

| OS timer (OSTM)                                         | Generate, from the OSTM channel 0 timer, the intervals at which the LED are turned on and off.                                                                             |

| Serial communication interface with FIFO (SCIF)         | Communicate between SCIF channel 0 and the host PC.                                                                                                                        |

| General I/O ports (PORT)                                | Switch multiplexed pin functions for SPIBSC, CS3, and SCIF channel 0.<br>Control pin for LED on/off.                                                                       |

| Power-down modes (STB)                                  | Cancel the module standby state of the RZ/A1LU's peripheral I/O.<br>Enable writing to the on-chip data retention RAM.                                                      |

| Memory management unit (MMU),<br>L1 cache, and L2 cache | Generate conversion tables such as specifying valid area of L1 cache or specifying memory type in the RZ/A1LU external address area. Enable the L1 and L2 caches.          |

#### Table 1.1 Peripheral Functions and Their Applications

Note: RZ/A1LU AVB board (JASMINE board) implements the SDRAM (ISSI IS42S16320F) in the CS3 space. The settings of the BSC and multiplexed pins for using the SDRAM, which lie in the configuration section of the source code, are initially disabled. When using the SDRAM, modify the source code accordingly. When two serial flash memory chips are to be used (in 8-bit access mode), the SDRAM is not available because it uses pins that are shared with the SDRAM control signals.

Figure 1.2 Operating Environment

# 2. Operation Confirmation Conditions

The sample code accompanying this application note has been run and confirmed under the conditions below.

| Table 2.1 | <b>Operation Confirmation Conditions</b> |

|-----------|------------------------------------------|

|-----------|------------------------------------------|

| ltem                           | Contents                                                                     |  |  |

|--------------------------------|------------------------------------------------------------------------------|--|--|

| MCU used                       | RZ/A1LU                                                                      |  |  |

| Operating frequency*           | CPU clock (Iø): 400 MHz                                                      |  |  |

|                                | Internal bus clock (Βφ): 133.33MHz                                           |  |  |

|                                | Peripheral clock 1 (P1φ): 66.67MHz                                           |  |  |

|                                | Peripheral clock 0 (P0φ): 33.33MHz                                           |  |  |

| Operating voltage              | Power supply voltage (I/O): 3.3V                                             |  |  |

|                                | Power supply voltage (internal): 1.18V                                       |  |  |

| Integrated development         | ARM <sup>®</sup> integrated development environment                          |  |  |

| environment                    | ARM Development Studio 5 (DS-5TM) Version 5.24                               |  |  |

| C compiler                     | ARM C/C++ Compiler/Linker/Assembler Ver.5.06 update 2 [Build 183]            |  |  |

|                                | Compiler option                                                              |  |  |

|                                | -O3 -Ospacecpu=Cortex-A9littleendarmapcs=/interwork                          |  |  |

|                                | no_unaligned_accessfpu=vfpv3_fp16 -gasm                                      |  |  |

| Operating mode                 | Boot mode 1 (Serial flash boot)                                              |  |  |

| Board used                     | RZ/A1LU AVB board                                                            |  |  |

|                                | RTK772103FC00000BR (hereinafter called "JASMINE board")                      |  |  |

| Communications settings of the | Baud rate: 115200bps                                                         |  |  |

| terminal software              | Data length: 8 bits                                                          |  |  |

|                                | Parity: None                                                                 |  |  |

|                                | Stop bits: 1 bit                                                             |  |  |

|                                | Flow control: None                                                           |  |  |

| Devices used                   | <ul> <li>Serial flash memory allocated to SPI multi-I/O bus space</li> </ul> |  |  |

| (functions used on the board)  | - Manufacturer: Macronix Inc.                                                |  |  |

|                                | - Product No.: MX25L51245G                                                   |  |  |

|                                | <ul> <li>RL78/G1C (Convert between USB communication and serial</li> </ul>   |  |  |

|                                | communication to communicate with the host PC.)                              |  |  |

|                                | LED1                                                                         |  |  |

Note: \* The operating frequency used in clock mode 0 (Clock input of 13.33MHz from EXTAL pin)

# 3. Reference Application Notes

For additional information associated with this document, refer to the following application notes.

- RZ/A1H Group I/O definition header file <iodefine.h> (R01AN1860EJ)

- RZ/A1H Group: Example of Initialization (R01AN1864EJ)

# 4. Hardware

# 4.1 Hardware Configuration

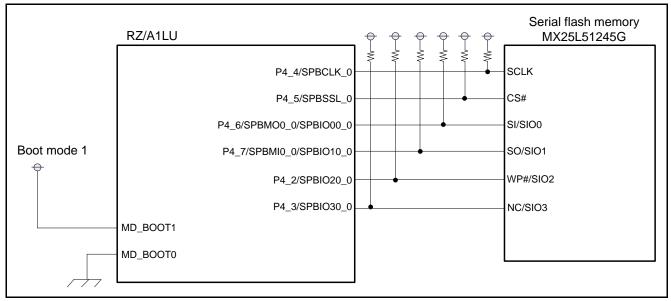

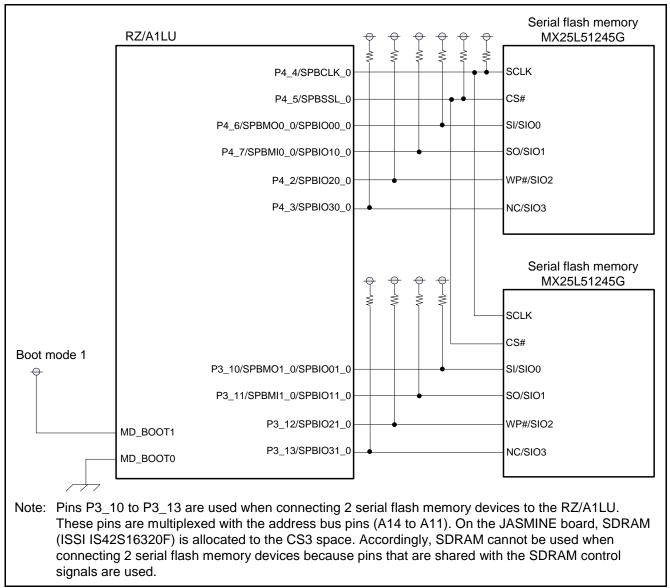

Figure 4.1 shows the Connection Example for Booting from Serial Flash Memory by using boot mode 1.

Figure 4.1 Connection Example for Booting from Serial Flash Memory

# 4.2 Pins Used

Table 4.1 lists the Pins Used and Their Functions.

| Pin Name           | I/O    | Function                                                                                              |

|--------------------|--------|-------------------------------------------------------------------------------------------------------|

| SPBCLK_0           | Output | Clock output                                                                                          |

| SPBSSL_0           | Output | Slave select                                                                                          |

| SPBMO0_0/SPBIO00_0 | I/O    | Master send data: data 0                                                                              |

| SPBMI0_0/SPBIO10_0 | I/O    | Master input data: data 1                                                                             |

| SPBIO20_0          | I/O    | Data 2                                                                                                |

| SPBIO30_0          | I/O    | Data 3                                                                                                |

| MD_BOOT1           | Input  | Select boot mode                                                                                      |

| MD_BOOT0/RxD0      | Input  | MD_BOOT1: "H", MD_BOOT0: "L"                                                                          |

|                    |        | (Set to boot mode 1)                                                                                  |

|                    |        | After boot-up, MD_BOOT0 is switched to the function of the serial receive data signal as RxD0 (Note). |

| P8_12              | Output | Turns on and off LED1.                                                                                |

| TxD0               | Output | Serial transmit data signal                                                                           |

#### Table 4.1 Pins Used and Their Functions

Note: The P0\_0 pin is multiplexed with the MD\_BOOT0 and RxD0 functions. At power-on reset release time, it serves as the MD\_BOOT0 function and is used to select the boot mode. In the sample code, the pin is configured by selecting and controlling the multiplexer/demultiplexer (SN74CB3Q3257) on the JASMINE board so that the boot function select signal is input through a switch on the board at power-on reset time and, after the power-on reset is released, the pin is pulled up and used as the RxD0 function.

#### 5. Software

#### 5.1 **Operation Overview**

This section provides an overview of the sample code operation presented in this application note.

#### 5.1.1 **Terms Related to Serial Flash Boot**

Table 5.1 lists the Terms Related to Serial Flash Boot Operation described in this application note.

| Term                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot startup on-chip ROM program   | This program provides settings to directly execute the programs<br>stored in the serial flash memory connected to the SPI multi-I/O<br>bus space when started up in boot mode 1 (serial flash boot).<br>The RZ/A1LU branches to the address of H'1800_0000 which is<br>the start address of the SPI multi-I/O bus space after the boot<br>startup on-chip ROM program has been executed.<br>Note that the boot startup on-chip ROM program makes settings<br>to enable common access to typical serial flash memory<br>devices. Since this program is stored in the on-chip ROM of the<br>RZ/A1LU, it does not need to be created by the customer.                                                                     |

| SPIBSC initial setting program     | This program is executed after the processing of the boot<br>startup on-chip ROM program has been completed. The<br>SPIBSC initial setting program makes settings to the SPIBSC<br>and to the registers in the serial flash memory corresponding to<br>the serial flash memory used by the customer, and then<br>branches to the start address of the application program.<br>SPIBSC The SPIBSC initial setting program should be created<br>by the customer according to the specifications of the serial<br>flash memory to be used while referring to this application note.<br>In the sample code, the initial settings are optimized for use with<br>the Macronix serial flash memory (product No.: MX25L51245G). |

| Application program (User program) | This program should be created by customers depending on their system to be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 5.1 Terms Related to Serial Flash Boot Operation

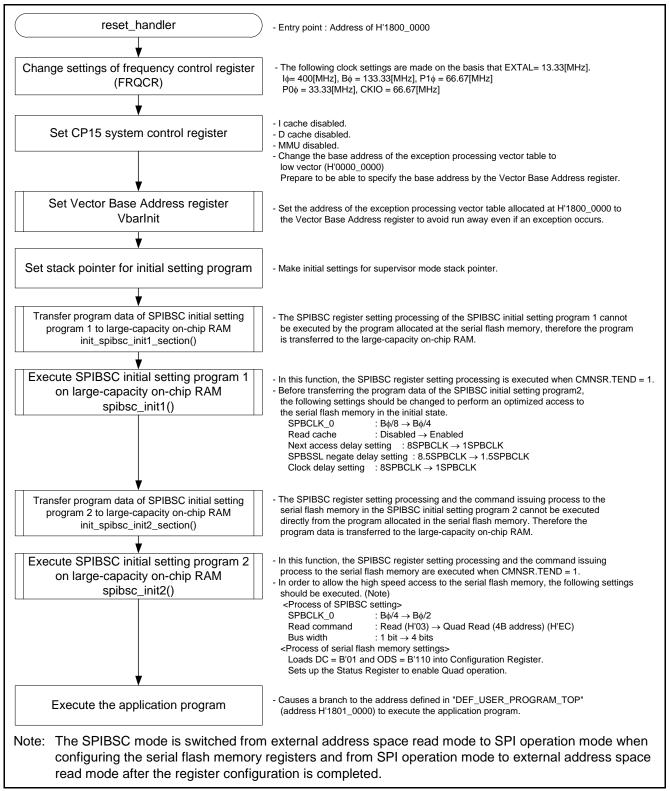

### 5.1.2 Operation Overview of Sample Code Overall

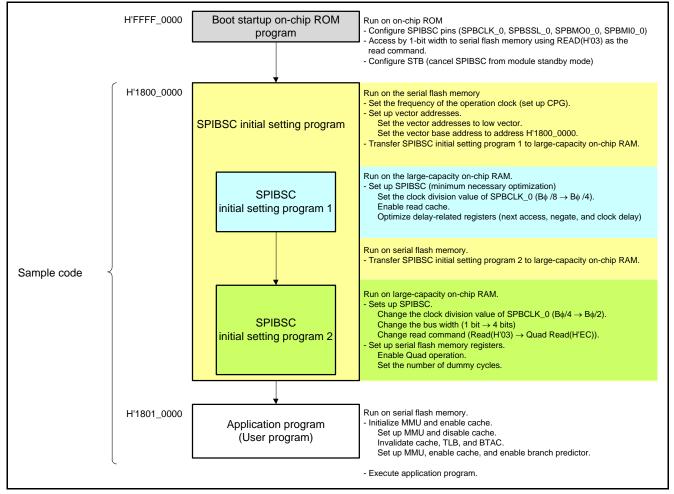

The sample code comprises the SPIBSC initial setting program executed from the boot startup on-chip ROM program and the application program.

(1) SPIBSC initial setting program

The SPIBSC initial setting program provides optimal settings to the serial flash memory used (Macronix serial flash memory (product No.: MX25L51245G)). The SPIBSC initial setting program is located at the start address (H'1800\_0000) of the SPI multi-I/O bus space, which is branched from the boot startup on-chip ROM program. After the SPIBSC initial setting program runs, it branches to the start address of the application program.

(2) Application program (User program)

This is an application program to be executed after optimal settings for the serial flash memory are provided in the SPIBSC initial setting program. In the sample code, the application program is located at address H'1801\_0000.

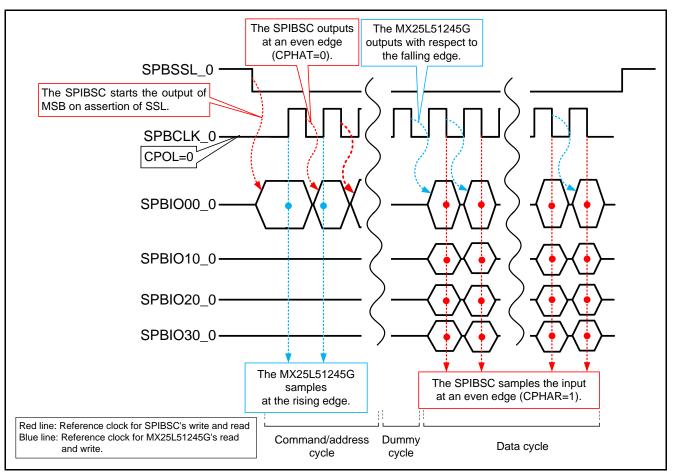

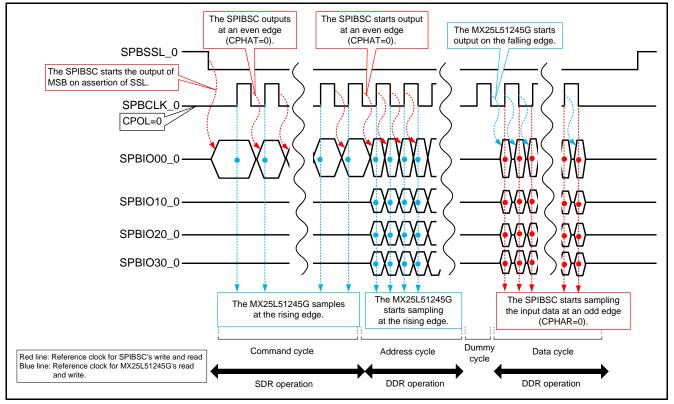

Figure 5.1 shows the Operation Overview of Sample Code presented in this application note.

Figure 5.1 Operation Overview of Sample Code

#### 5.1.3 Operation Overview of SPIBSC Initial setting program

The SPIBSC initial setting program is executed after the boot startup on-chip ROM program. The SPIBSC initial setting program should be located at the start address (H'1800\_0000) of the SPI multi-I/O bus space branched from the boot startup on-chip ROM program.

The boot startup on-chip ROM program makes settings to enable the SPIBSC to operate in external address space read mode. These settings cause the RZ/A1LU to convert read operations targeting the SPI multi-I/O bus space to SPI communication so that the direct read operations are enabled to the connected serial flash memory. This makes it possible for the RZ/A1LU to directly run programs allocated to the SPI multi-I/O bus space. The settings for commands targeting the serial flash memory used in SPI communication conversion allow common access to typical serial flash memory devices, so it is necessary to provide the optimal settings to the serial flash memory used by the customer.

Refer to Table 5.2, Table 5.3, and Table 5.4 for the settings made after the boot startup on-chip ROM program has been executed.

The optimal settings for the serial flash memory are provided in two places: the registers in the SPIBSC module (hereinafter called "SPIBSC settings") and the registers in the serial flash memory (hereinafter called "serial flash memory settings"). In the SPIBSC initial setting program of the sample code, the optimal settings are required when Macronix serial flash memory (product No.: MX25L51245G) is used.

The SPIBSC initial setting program comprises SPIBSC initial setting program 1 and SPIBSC initial setting program 2, as described below. Each is designed to be transferred from the SPI multi-I/O bus space to the large-capacity on-chip RAM and then executed from the large-capacity on-chip RAM.

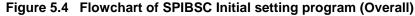

(1) SPIBSC initial setting program 1

The SPIBSC initial setting program 1 sets up the SPIBSC registers so as to shorten the delay times (next access delay, SPBSSL negate delay, and clock delay), specify the transfer bit rate, and enable the read cache. The program size is comparatively compact because the content of processing is small.

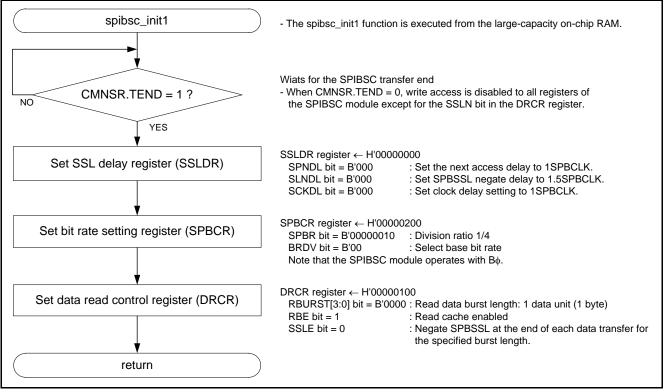

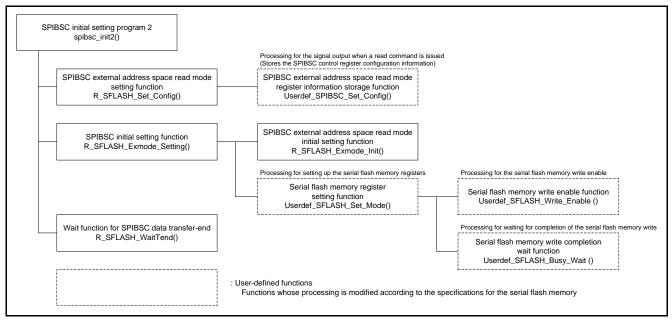

(2) SPIBSC initial setting program 2

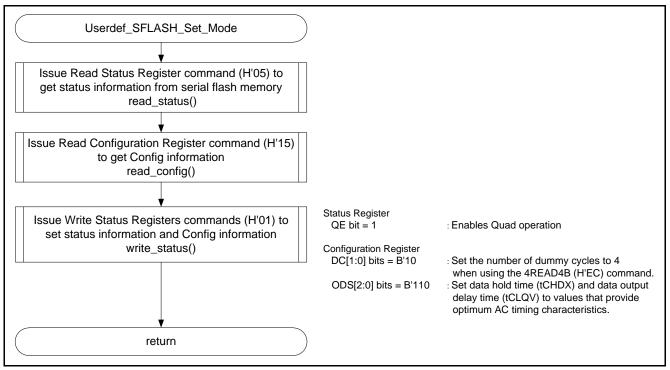

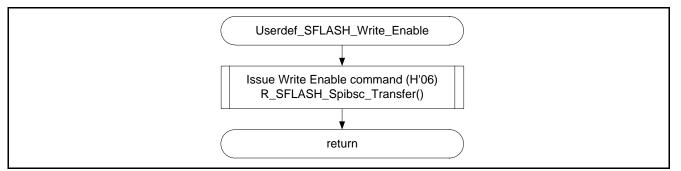

The SPIBSC initial setting program 2 sets up the SPIBSC registers so as to specify a data bus width of 4 bits, optimize the transfer bit rate according to the read command to be used, and output 4-byte addresses. It also sets up the registers in the serial flash memory (MX25L51245G) so as to specify the number of dummy cycles for the serial flash memory, enable quad operation, and make changes for 4-byte addressing. The program size is larger than that of the initial setting program 1 because the volume of its processing is great.

The SPIBSC initial setting program 1 and 2 cannot be set by the program allocated to the SPI multi-I/O bus space, so these programs should be executed from the large-capacity on-chip RAM. In the sample code, the SPIBSC initial setting program 1 is transferred to the large-capacity on-chip RAM to be executed. Then the SPIBSC initial setting program 2 is transferred to the large-capacity on-chip RAM to be executed after the possible optimal settings have been provided to the serial flash memory used. This reduces the overall running time of the SPIBSC initial setting program.

Table 5.2, Table 5.3 and Table 5.4 list the settings made by the SPIBSC initial setting program.

After the settings listed in Table 5.2, Table 5.3 and Table 5.4 are made, the SPIBSC initial setting program branches to the start address of the application program. In the sample code, the application program is allocated to the area starting at H'1801\_0000, which is to be the branch target.

# Table 5.2 Settings for the Boot Startup On-Chip ROM Program and SPIBSC Initial setting Programs (1/3)

|          | Item                                         | Boot Startup On-Chip          | SPIBSC Initial setting          | SPIBSC Initial setting        |

|----------|----------------------------------------------|-------------------------------|---------------------------------|-------------------------------|

|          |                                              | ROM Program                   | program 1                       | program 2                     |

| SPIBSC   | Delay settings                               |                               |                                 |                               |

| settings | Next access delay setting :                  |                               |                                 |                               |

|          | SSLDR.SPNDL[2:0]                             | B'111 (8SPBCLK)               | B'000 (1SPBCLK)                 | B'000 (1SPBCLK)               |

|          | SPBSSL negate delay setting :                |                               |                                 |                               |

|          | SSLDR.SLNDL[2:0]                             | B'111 (8.5SPBCLK)             | B'000 (1.5SPBCLK)               | B'000 (1.5SPBCLK)             |

|          | Clock delay setting :                        |                               |                                 |                               |

|          | SSLDR.SCKDL[2:0]                             | B'111 (8SPBCLK)               | B'000 (1SPBCLK)                 | B'000 (1SPBCLK)               |

|          | Serial clock :                               |                               |                                 |                               |

|          | (@B\$ = 133.33MHz)                           | Bφ/8 = 16.67 [MHz]            | Bφ/4 = 33.33 [MHz]              | Bφ/2 = 66.67 [MHz]            |

|          | SPBCR.SPBR[7:0]                              | 0                             | 2                               | 1                             |

|          | SPBCR.BRDV[1:0]                              | 3                             | 0                               | 0                             |

|          | CPOL : CMNCR.CPOL                            | 0                             | 0                               | 0                             |

|          | CPHAT : CMNCR.CPHAT                          | 0                             | 0                               | 0                             |

|          | CPHAR : CMNCR.CPHAR                          | 0                             | 0                               | 1                             |

|          | SPBSSL output idle value fix :               | Sets output values in         | Sets output values in           | Sets output values in         |

|          |                                              | SPBSSL negation period to     | SPBSSL negation period to       | SPBSSL negation period to     |

|          |                                              | the last bit value of the     | the last bit value of the       | Hi-z                          |

|          |                                              | previous transfer             | previous transfer               |                               |

|          | SPBIO30 and SPBIO31 setting                  | CMNCR.MOIIO3[1:0]=B'10        | CMNCR.MOIIO3[1:0]=B'10          | CMNCR.MOIIO3[1:0]=B'11        |

|          | SPBIO20 and SPBIO21 setting                  | CMNCR.MOIIO2[1:0]=B'10        | CMNCR.MOIIO2[1:0]=B'10          | CMNCR.MOIIO2[1:0]=B'11        |

|          | SPBIO10 and SPBIO11 setting                  | CMNCR.MOIIO1[1:0]=B'10        | CMNCR.MOIIO1[1:0]=B'10          | CMNCR.MOIIO1[1:0]=B'11        |

|          | SPBIO00 and SPBIO01 setting                  | CMNCR.MOIIO0[1:0]=B'10        | CMNCR.MOIIO0[1:0]=B'10          | CMNCR.MOIIO0[1:0]=B'11        |

|          | Fixes the output value of the                | Sets the terminal output      | Sets the terminal output        | Sets the terminal output      |

|          | terminal :                                   | value for 1-bit/2-bit size to | value for 1-bit/2-bit size to   | value for 1-bit/2-bit size to |

|          |                                              | the last bit value of the     | the last bit value of the       | Hi-z                          |

|          | SPRIC20 and SPRIC21 patting                  | previous transfer             | previous transfer               | CMNCR.IO3FV[1:0]=B'11         |

|          | SPBIO30 and SPBIO31 setting                  | CMNCR.IO3FV[1:0]=B'10         | CMNCR.IO3FV[1:0]=B'10           |                               |

|          | SPBIO20 and SPBIO21 setting                  | CMNCR.IO2FV[1:0]=B'10         | CMNCR.IO2FV[1:0]=B'10           | CMNCR.IO2FV[1:0]=B'11         |

|          | SPBIO00 and SPBIO01 setting                  | CMNCR.IO0FV[1:0]=B'10         | CMNCR.IO0FV[1:0]=B'10           | CMNCR.IO0FV[1:0]=B'11         |

|          | Number of serial flash :                     | 1                             | 1                               | 1                             |

|          | CMNCR.BSZ[1:0]                               |                               | B'00                            | B'00                          |

|          | Read cache : DRCR.RBE                        | 0 (Disabled)                  | 1 (Enabled)                     | 1 (Enabled)                   |

|          | Read data burst length :<br>DRCR.RBURST[3:0] | 1 data unit (8 bytes)         | 1 data unit (8 bytes)<br>B'0000 | 4 data unit (32 bytes)        |

|          | DRCR.RBURST[3:0]                             | B'0000                        |                                 | B'0011                        |

|          | DRENR.DRDB[1:0]                              | 1 [bit]<br>B'00               | 1 [bit]<br>B'00                 | 4 [bits]<br>B'10              |

|          | Read command :                               | Read (03H)                    | Read (03H)                      | Quad I/O read (ECH)           |

|          | DRCMR.CMD[7:0]                               | H'03                          | H'03                            | H'EC                          |

|          | Command :                                    | Output enabled                | Output enabled                  | Output enabled                |

|          | DRENR.CDE                                    | 1                             | 1                               | 1                             |

|          |                                              |                               |                                 |                               |

|          |                                              | •                             |                                 |                               |

|          | Optional command :<br>DRENR.OCDE             | Output disabled               | Output disabled                 | Output disabled               |

|          | ltem                        | Boot Startup On-Chip<br>ROM Program | SPIBSC Initial setting<br>program 1 | SPIBSC Initial setting<br>program 2 |

|----------|-----------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| SPIBSC   | Address specification :     | Output address[23:0]                | Output address[23:0]                | Output address[31:0]                |

| settings | DRENR.ADE[3:0]              | B'0111                              | B'0111                              | B'1111                              |

|          | Address bit size :          | 1 [bit]                             | 1 [bit]                             | 4 [bit]                             |

|          | DRENR.ADB[1:0]              | B'00                                | B'00                                | B'10                                |

|          | Option data :               | Output disabled                     | Output disabled                     | Output OPD3 *                       |

|          | DRENR.OPDE[3:0]             | B'0000                              | B'0000                              | B'1000                              |

|          | Option data bit size :      | -                                   | -                                   | 4 [bit]                             |

|          | DRENR.OPDB[1:0]             |                                     |                                     | B'10                                |

|          | Option data :               |                                     |                                     |                                     |

|          | DROPR.OPD3[7:0]             | -                                   | _                                   | H'00                                |

|          | DROPR.OPD2[7:0]             | -                                   | _                                   | _                                   |

|          | DROPR.OPD1[7:0]             | _                                   | _                                   | _                                   |

|          | DROPR.OPD0[7:0]             | _                                   | _                                   | _                                   |

|          | Dummy cycle enable :        | Insertion disabled                  | Insertion disabled                  | Insertion enabled                   |

|          | DRENR.DME                   | 0                                   | 0                                   | 1                                   |

|          | Dummy cycle bit size :      | -                                   | _                                   | 1 [bit]                             |

|          | DRDMCR.DMDB[1:0]            |                                     |                                     | B'00                                |

|          | Number of dummy cycles :    | _                                   | _                                   | 2 cycles                            |

|          | DRDMCR.DMCYC[2:0]           |                                     |                                     | B'001                               |

|          | Extended external Address : | External address bits [24:0]        | External address bits [24:0]        | External address bits [25:0]        |

|          |                             | enabled                             | enabled                             | enabled                             |

|          |                             | (Directly accessible 32MB           | (Directly accessible 32MB           | (Directly accessible 64MB           |

|          |                             | spaces)                             | spaces)                             | spaces)                             |

|          | DREAR.EAC[2:0]              | B'000                               | B'000                               | B'001                               |

|          | DREAR.EAV[7:0]              | H'00                                | H'00                                | H'00                                |

|          | Transfer format :           | Address, option data, and           | Address, option data, and           | Address, option data, and           |

|          |                             | data are transferred in SDR         | data are transferred in SDR         | data are transferred in SDR         |

|          |                             | mode.                               | mode.                               | mode.                               |

|          | DRDRENR.ADDRE               | 0                                   | 0                                   | 0                                   |

|          | DRDRENR.OPDRE               | 0                                   | 0                                   | 0                                   |

|          | DRDRENR.DRDRE               | 0                                   | 0                                   | 0                                   |

|          | AC input characteristics    |                                     |                                     |                                     |

|          | adjustment :                |                                     |                                     | <b></b>                             |

|          | CKDLY.CKDLY[3:0]            | B'0100                              | B'0100                              | B'0100                              |

|          | AC output characteristics   |                                     |                                     |                                     |

|          | adjustment :                | 1.110000                            |                                     |                                     |

|          | SPODLY.SPODLY[15:0]         | H'0000                              | H'0000                              | H'0000                              |

| Table 5.3 | Settings for the Boot Startup On-Chip ROM Program and SPIBSC Initial setting Programs |

|-----------|---------------------------------------------------------------------------------------|

|           | (2/3)                                                                                 |

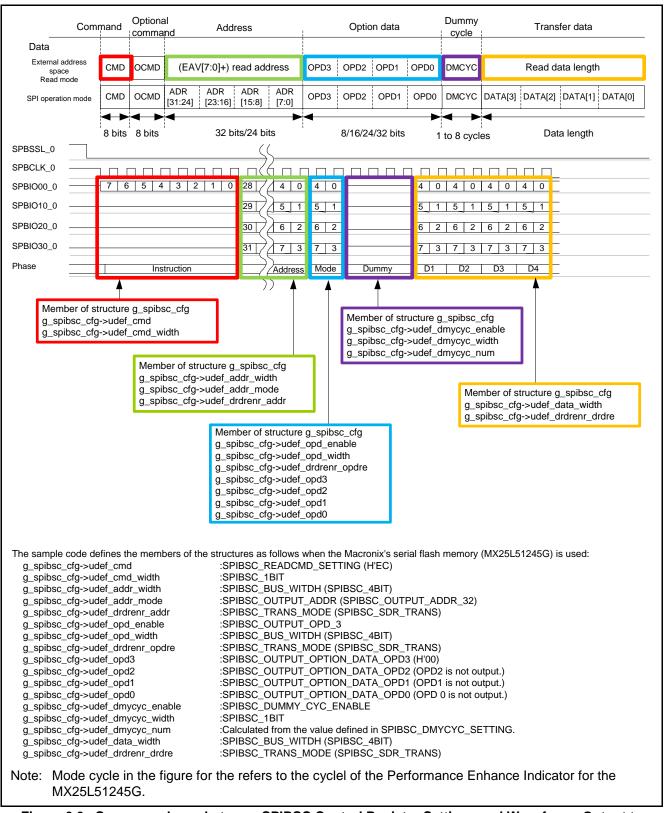

Note: \* The MX25L51245G transits to the Performance Enhance Mode when data (e.g., H'A5, H'5A, H'F0, H'0F, etc.) that toggles between bits 7-4 and bits 3-0 is input during the performance enhance indicator cycle that follows the address cycle. Since the RZ/A1LU's external address space read mode does not support the data transfer in Performance Enhance Mode, the sample code makes configuration so that the MX25L51245G will not switch into the Performance Enhance Mode by making configuration so that H'00 is output from the OPD3 when a QuadIO Read command is issued.

|           | ltem                          | Boot Startup On-Chip<br>ROM Program | SPIBSC Initial setting<br>program 1 | SPIBSC Initial setting<br>program 2 |

|-----------|-------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Multiplex | P4_4                          | SPBCLK_0                            | SPBCLK_0                            | SPBCLK_0                            |

| ed pin    | P4_5                          | SPBSSL_0                            | SPBSSL_0                            | SPBSSL_0                            |

| settings  | P4_6                          | SPBMO0_0 / SPBIO00_0                | SPBMO0_0 / SPBIO00_0                | SPBMO0_0 / SPBIO00_0                |

|           | P4_7                          | SPBMI0_0 / SPBIO10_0                | SPBMI0_0 / SPBIO10_0                | SPBMI0_0 / SPBIO10_0                |

|           | P4_2                          | P4_2                                | P4_2                                | SPBIO20_0                           |

|           | P4_3                          | P4_3                                | P4_3                                | SPBIO30_0                           |

| Serial    | Status Register               | No change *                         | No change *                         | Quad operation enabled.             |

| flash     |                               |                                     |                                     | QE=1                                |

| memory    | Configuration Register        | No change *                         | No change *                         | DC[1:0] = B'01                      |

| settings  |                               |                                     |                                     | ODS[2:0] = B'110                    |

| Other     | Operating clock settings      | Ιφ=133.33[MHz]                      | Ιφ=400[MHz]                         | Ιφ=400[MHz]                         |

|           | Clock input of 13.33MHz from  | Bφ=133.33[MHz]                      | Bφ=133.33[MHz]                      | Bφ=133.33[MHz]                      |

|           | EXTAL pin                     | P1¢=66.67[MHz]                      | P1φ=66.67[MHz]                      | Ρ1φ=66.67[MHz]                      |

|           |                               | P0φ=33.33[MHz]                      | P0\$=33.33[MHz]                     | P0φ=33.33[MHz]                      |

|           | CPU exception vector position | High vector                         | Low vector                          | Low vector                          |

|           |                               | (from H' FFFF_0000)                 | (from H'0000_0000)                  | (from H'0000_0000)                  |

| Table 5.4 | Settings for the Boot Startup On-Chip ROM Program and SPIBSC Initial setting Programs |

|-----------|---------------------------------------------------------------------------------------|

| (         | (3/3)                                                                                 |

Note: \* In serial flash booting (boot mode 1) of RZ/A1LU, the boot program sets the SPIBSC register to issue a read command (opcode: 03H, address: 3 bytes, dummy cycle: none) as the command to the serial flash memory. Therefore if the condition of the serial flash memory can not be received the above read command by the register value in serial flash booting, it is a possibility that can not be normal boot.

### 5.1.4 Application Program (User Program)

(1) Operation of the application program (user program)

After a reset is cancelled, the boot startup on-chip ROM program and SPIBSC initial setting program are executed in that order. Execution then transfers to the application program that is allocated to address H'1801\_0000. The application program executes the settings for the stack pointer and the MMU. It branches to the C standard library function \_\_\_\_main which is provided from the ARM integrated development environment DS-5 compiler toolchain.

The \_\_main function initializes the section area with the scatter-loading function and the library functions. It branches to the \$Sub\$\$main function to initialize the hardware.

In this sample code, the \$Sub\$\$main function initializes the peripheral functions such as STB, BSC, INTC, and PORT, and sets the L1 and L2 caches to enabled, and enables the IRQ and FIQ interrupts. It branches to the main function by calling the \$Super\$\$main function (in the sample code, the configuration for setting up the MMU and enabling the cache is executed by the application program and not by the SPIBSC initial setting program). The main function outputs the character strings to the terminal on the host PC connected with the serial interface and

The main function outputs the character strings to the terminal on the host PC connected with the serial interface and sets the OSTM channel 0 timer to interval timer mode to activate the timer. It generates the OSTM channel 0 interrupt with a cycle of 500ms and repeats turning on/off the LED on the JASMINE board board every 500ms using such interrupt.

For details on the initialization executed by the application program, refer to the application note entitled "RZ/A1H Group Example of Initialization (R01AN1864EJ)".

(2) Notes to be observed when creating an application program (user program)

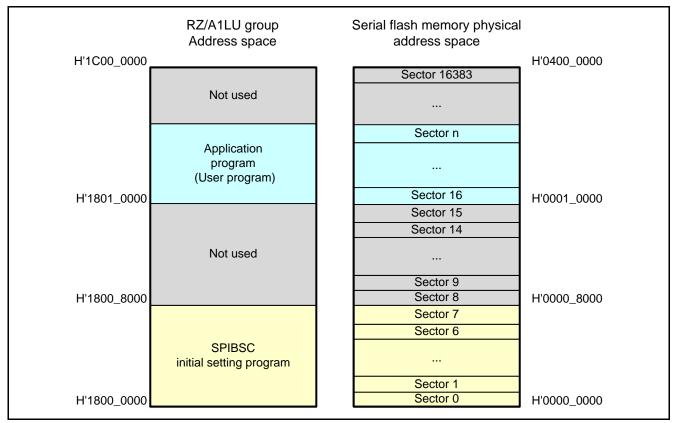

The application program should be allocated to the address branched from the SPIBSC initial setting program. Note that the application program should be allocated to the different sector in the serial flash memory from the one in the SPIBSC initial setting program.

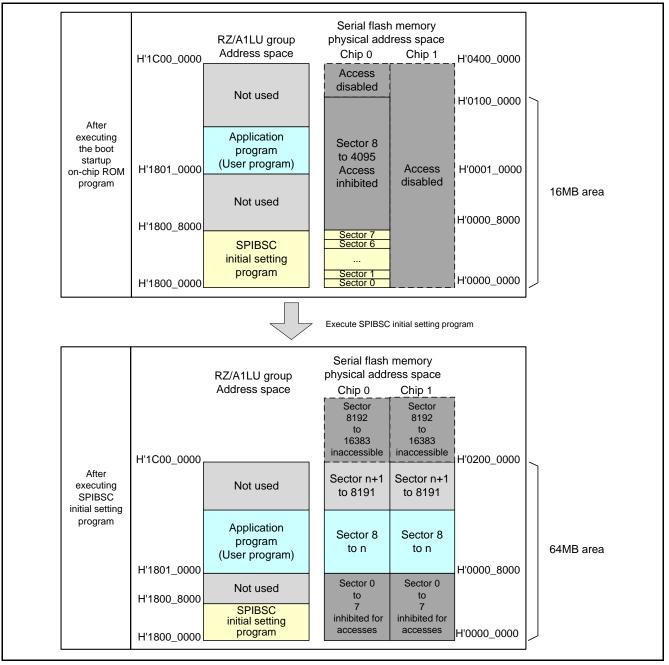

The sector size of the Macronix serial flash memory (MX25L51245G) mounted on the JASMINE board is 4KB. In the sample code, the application program is allocated to the address of H'1801\_0000 (Sector no. 16). Figure 5.2 shows the Sample Code Program Allocation.

Figure 5.2 Sample Code Program Allocation

The start address of the application program can be changed by making the following changes:

• Project for the SPIBSC initial setting program

The branch to the starting address of the application program is executed by the initial setting program 2 (spibsc\_init2.c). Specify the destination of branch with the macro definition "DEF\_USER\_PROGRAM\_TOP" in spibsc\_config.h.

• Project for the application program Change the allocation address so that the VECTOR\_TABLE section of the application program matches the address that is specified in "DEF\_USER\_PROGRAM\_TOP."

# 5.2 Peripheral Functions and Memory Allocation in Sample Code

### 5.2.1 Setting for Peripheral Functions

Table 5.5 lists the Setting for Peripheral Functions during execution of the sample code.

| Table 5.5 Setting for Peripheral Functions | Table 5.5 | Setting for | Peripheral | Functions |

|--------------------------------------------|-----------|-------------|------------|-----------|

|--------------------------------------------|-----------|-------------|------------|-----------|

| Module | Settings                                                                                                                                                                                                                                                                                       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPG    | CPU clock (I                                                                                                                                                                                                                                                                                   |

|        | Internal bus clock (B                                                                                                                                                                                                                                                                          |

|        | Peripheral clock 1 (P1): 66.67 MHz                                                                                                                                                                                                                                                             |

|        | Peripheral clock 0 (P0): 33.33 MHz                                                                                                                                                                                                                                                             |

| SPIBSC | When set to the external address space read mode, it generates the signals which enable the CPU to read directly from the serial flash memory connected to the SPI multi-I/O bus space.<br>See Table 5.2, Table 5.3 and Table 5.4 for details.                                                 |

| PORT   | Multiplexed pin functions are enabled on PORT4, PORT8, PORT6, and<br>PORT0.<br>P4_4:SPBCLK_0<br>P4_5:SPBSSL_0<br>P4_6:SPBMO0_0/SPBIO00_0<br>P4_7:SPBMI0_0/SPBIO10_0<br>P4_2:SPBIO20_0<br>P4_3:SPBIO30_0<br>P4_3:SPBIO30_0<br>P8_12:LED on/off<br>P6_15:TxD0<br>P0_0:RxD0 *                     |

| STB    | Writing to the on-chip RAM used for retention is enabled and clock<br>supply to peripheral functions is enabled.<br>Clock supply is enabled to all peripheral functions for which clock supply<br>and stop control are supported by using STBCR2 to STBCR12.                                   |

| OSTM   | Sets the channel 0 in interval timer mode.<br>Sets the timer counter to have interrupt request generated every 500ms when $P0\phi=33.33$ MHz.                                                                                                                                                  |

| INTC   | Initializes INTC, and registers and executes OSTM channel 0 interrupt (interrupt ID is 134) handler                                                                                                                                                                                            |

| SCIF   | <ul> <li>Sets the channel 0 in asynchronous communication mode.</li> <li>Data length: 8 bits</li> <li>Stop bit length: 1 bit</li> <li>Parity: None</li> <li>Sets the clock source without frequency dividing and the bit rate value at 17. Sets the bit rate to be 115200bps when P1</li></ul> |

Note: \* The P0\_0 pin is multiplexed with the MD\_BOOT0 and RxD0 functions. At power-on reset release time, it serves as the MD\_BOOT0 function and is used to select the boot mode. In the sample code, the pin is configured by selecting and controlling the multiplexer/demultiplexer (SN74CB3Q3257) on the JASMINE board so that the boot function select signal is input through a switch on the board at power-on reset time and, after the power-on reset is released, the pin is pulled up and used as the RxD0 function.

# 5.2.2 Memory Mapping

Figure 5.3 shows the RZ/A1LU Group Address Space and JASMINE board.

| Mirror         RZA1LU group<br>Address space         JASMINE board<br>Memory map           HFFFF FFFF         Others<br>(2557MB)         Others<br>(2557MB)         Others<br>(2557MB)           H6000 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           H5000 0000         H5000 0000         SPI multi-I/O-bus<br>space 1 (64MB)         -           H5000 0000         H5000 0000         CS3 space (64MB)         -           H4000 0000         CS2 space (64MB)         -         -           H4000 0000         CS2 space (64MB)         -         -           H4000 0000         CS2 space (64MB)         -         -           H4000 0000         CS1 space (64MB)         -         -           H4000 0000         H4000 0000         CS1 space (64MB)         -           H4000 0000         Large-capacity on-<br>chip RAM (3MB)         Chiers<br>(509MB)         Others<br>(509MB)         Others<br>(509MB)         Chiers<br>(509MB)         -           Normal<br>space         H11000 0000         SPI multi-I/O-bus<br>space 1 (64MB)         -         -           H1400 0000         CS5 space (64MB)         -         -         -           H1400 0000         H1400 0000         CS5 space (64MB)         -         - <th></th> <th></th> <th></th> <th></th> <th></th> |       |           |                    |          |                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|--------------------|----------|---------------------|

| HIFFFF FFFF         Others<br>(2557MB)         Others<br>(2557MB)           H6030 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           H5000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           H5000 0000         CS5 space (64MB)         -           H5000 0000         CS3 space (64MB)         -           H4000 0000         CS2 space (64MB)         -           H4000 0000         CS2 space (64MB)         -           H4000 0000         CS1 space (64MB)         -           H4000 0000         CS0 space (64MB)         -           H1000 0000         CS0 space (64MB)         -           H1000 0000         CS5 space (64MB)         -           H1000 0000         CS3 space (64MB)         -           H1000 0000         CS2 space (64MB)         -                                                                                                                                                            |       |           |                    |          |                     |

| Others<br>(2557MB)         Others<br>(2557MB)         Others<br>(2557MB)           H6030 0000<br>H6000 0000<br>H6000 0000<br>H500 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           Mirror<br>space 1 (64MB)         -         SPI multi-I/O-bus<br>space 1 (64MB)         -           H5000 0000<br>H4000 0000         CS4 space (64MB)         -         -           H15000 0000<br>H4000 0000         CS3 space (64MB)         -         -           CS1 space (64MB)         -         -         -           H14000 0000         CS1 space (64MB)         -         -           H14000 0000         CS0 space (64MB)         -         -           H14000 0000         CS0 space (64MB)         -         -           H14000 0000         CS1 space (64MB)         -         -           H14000 0000         CS0 space (64MB)         -         -           H14000 0000         CS1 space (64MB)         -         -           H11000 0000         SPI multi-I/O-bus<br>space 1 (64MB)         Serial flash memory<br>(64MB)         -           H11000 0000         CS2 space (64MB)         -         -         -           H1400 0000         CS4 space (64MB)         -         -         - <t< td=""><td></td><td>שיבכב כב</td><td></td><td><b>1</b></td><td></td></t<>                |       | שיבכב כב  |                    | <b>1</b> |                     |

| Mirror         H6030 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM mirror           Mirror         H5000 0000         SPI multi-I/O-bus         -           H5000 0000         H5000 0000         SPI multi-I/O-bus         -           Mirror         SPI multi-I/O-bus         SPI multi-I/O-bus         -           Spi multi-I/O-bus         SPI multi-I/O-bus         SPI multi-I/O-bus         -           Mirror         H5000 0000         CS3 space (64MB)         -         -           H4000 0000         H4000 0000         CS3 space (64MB)         -         -           H4000 0000         H4000 0000         CS1 space (64MB)         -         -           H4000 0000         H4000 0000         CS0 space (64MB)         -         -           H1000 0000         H1000 0000         Large-capacity on-<br>chip RAM (3MB)         Serial flash memory<br>space 1 (64MB)         -           H1100 0000         H1000 0000         CS3 space (64MB)         -         -           H1400 0000         CS3 space (64MB)         -         -         -           H1400 0000         Large-capacity on-<br>chip RAM (3MB)         Serial flash memory<br>space 1 (64MB)         -         -           CS1 space (64MB)         -         -                                                                                                  |       |           |                    |          |                     |

| Mirror<br>space         H6030 0000<br>H6000 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM mirror           Mirror<br>space         H5000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           H5000 0000         H5000 0000         SPI multi-I/O-bus<br>space 1 (64MB)         -           H5000 0000         H5000 0000         CS4 space (64MB)         -           H4000 0000         H4000 0000         CS3 space (64MB)         -           H4000 0000         H4000 0000         CS1 space (64MB)         -           H4000 0000         CS0 space (64MB)         -         -           H4000 0000         CS0 space (64MB)         -         -           H4000 0000         CS1 space (64MB)         -         -           H4000 0000         CS1 space (64MB)         -         -           H2030 0000         Large-capacity on-<br>chip RAM (3MB)         Serial flash memory<br>space 1 (64MB)         -           H1000 0000         H1000 0000         CS3 space (64MB)         -         -           H1400 0000         CS3 space (64MB)         -         -         -           H1400 0000         CS5 space (64MB)         -         -         -           H1400 0000         CS3 space (64MB)         -         -                                                                                                      |       |           |                    |          |                     |

| Mirror         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           Mirror         SPI multi-I/O-bus<br>space 1 (64MB)         -           Mirror         SPI multi-I/O-bus<br>space 1 (64MB)         SPI multi-I/O-bus<br>mirror space 1           Mirror         CS5 space (64MB)         -           H5000 0000         CS4 space (64MB)         -           H4000 0000         CS3 space (64MB)         -           H4000 0000         CS1 space (64MB)         -           H4000 0000         Large-capacity on-<br>chip RAM (3MB)         Chips RAM (3MB)           H2000 0000         Large-capacity on-<br>chip RAM (3MB)         -           H1000 0000         SPI multi-I/O-bus<br>space 1 (64MB)         -           H1400 0000         CS5 space (64MB)         -           H1400 0000         CS4 space (64MB)         -           H1000 0000         CS2 space (64MB)         -                                                                                                               |       |           | (2557MB)           |          | (2557MB)            |

| Mirror         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM mirror           Mirror         SPI multi-I/O-bus         -           H5000 0000         SPI multi-I/O-bus         SPI multi-I/O-bus           H5000 0000         CS5 space (64MB)         -           H5000 0000         CS4 space (64MB)         -           H4000 0000         CS3 space (64MB)         -           H4000 0000         CS2 space (64MB)         -           H4000 0000         CS1 space (64MB)         -           H2000 0000         Large-capacity on-<br>chip RAM (3MB)         Chip RAM (3MB)           H1000 0000         SPI multi-I/O-bus         Serial flash memory<br>(64MB)           Space 1 (64MB)         -         -           H1800 0000         SPI multi-I/O-bus         Serial flash memory<br>(64MB)           Space 1 (64MB)         -         -           H14                                                                                                                                                  |       | H'6030.00 | 000                |          |                     |

| Mirror<br>space         SPI multi-I/O-bus<br>space 2 (64MB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | $\int$    | Large-capacity on- |          |                     |

| Mirror<br>space         H*5C00 0000<br>H*5800 0000         space 2 (64MB)<br>SPI multi-I/O-bus<br>space 1 (64MB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | H'6000 00 |                    |          | chip RAM mirror     |

| Mirror<br>space         SPI multi-I/O-bus<br>space 1 (64MB)         SPI multi-I/O-bus<br>mirror space 1           Mirror<br>space         H'5000 0000<br>H'4000 0000         CS3 space (64MB)         -           H'4000 0000<br>H'4000 0000         CS3 space (64MB)         -           H'4000 0000<br>H'4000 0000         CS2 space (64MB)         -           H'4000 0000<br>H'4000 0000         CS1 space (64MB)         -           H'4000 0000<br>H'4000 0000         CS0 space (64MB)         -           H'2030 0000<br>H'2000 0000         Large-capacity on-<br>chip RAM (3MB)         Others<br>(509MB)         Others<br>(509MB)           H'1000 0000         H'1000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           Normal<br>space         H'1400 0000         CS5 space (64MB)         -           H'1000 0000         CS2 space (64MB)         -           H'1000 0000         CS2 space (64MB)         -           H'1000 0000         CS2 space (64MB)         -           H'0000 0000         CS2 space (64MB)         -           H'0000 0000                                                                        |       | H'5C00 00 |                    |          | -                   |

| Mirror<br>space         CS5 space (64MB)            H*000 0000<br>H*4000 0000<br>H*4600 0000<br>H*4600 0000<br>H*4400 0000         CS3 space (64MB)            Kirror space         CS2 space (64MB)            CS1 space (64MB)             CS1 space (64MB)             CS1 space (64MB)             CS1 space (64MB)             CS0 space (64MB)             CS1 space (64MB)             H*4000 0000         CS0 space (64MB)            H*2030 0000         Large-capacity on-<br>chip RAM (3MB)         Chip RAM (3MB)           H*2000 0000         SPI multi-I/O-bus<br>space 2 (64MB)            H*1000 0000         CS5 space (64MB)            H*1000 0000         CS3 space (64MB)            H*1000 0000         CS3 space (64MB)            H*1000 0000         CS3 space (64MB)            H*1000 0000         CS2 space (64MB)            H*1000 0000         CS2 space (64MB)            H*0000000         CS1 space (64MB)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |           | SPI multi-I/O-bus  |          |                     |

| Mirror<br>space         H 5000 0000<br>H 4200 0000         CS4 space (64MB)         -           H 4C00 0000         CS3 space (64MB)         CS3 mirror space           H 4800 0000         CS1 space (64MB)         -           H 4400 0000         CS0 space (64MB)         -           H 4000 0000         CS0 space (64MB)         -           H 2000 0000         Large-capacity on-<br>chip RAM (3MB)         Chip RAM (3MB)           H 12000 0000         Large-capacity on-<br>chip RAM (3MB)         -           SPI multi-I/O-bus<br>space 2 (64MB)         -         -           H 11000 0000         CS5 space (64MB)         -           H 11000 0000         CS5 space (64MB)         -           H 1000 0000         CS4 space (64MB)         -           H 1000 0000         CS3 space (64MB)         -           H 1000 0000         CS2 space (64MB)         -           H 1000 0000         CS2 space (64MB)         -           H 1000 0000         CS2 space (64MB)         -           H 0400 0000         CS1 space (64MB)         -                                                                                                                                                             |       | H'5800 00 |                    |          | mirror space 1      |

| Mirror         H5000 0000         CS3 space (64MB)         CS3 mirror space           H'4C00 0000         CS2 space (64MB)         -           H'4000 0000         CS1 space (64MB)         -           H'4000 0000         CS1 space (64MB)         -           H'4000 0000         CS0 space (64MB)         -           H'4000 0000         CS0 space (64MB)         -           H'4000 0000         Others         Others           H'2030 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           H'1000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           H'1800 0000         SPI multi-I/O-bus<br>space 1 (64MB)         -           H'1800 0000         CS5 space (64MB)         -           H'1800 0000         CS4 space (64MB)         -           H'1000 0000         CS3 space (64MB)         -           H'000 0000         CS2 space (64MB)         -           H'000 0000         CS1 space (64MB)         -           H'000 0000         CS1 space (64MB)         -                                                                                                                                                                                                                                                                                                                                             |       |           | CS5 space (64MB)   |          | -                   |

| Normal space         H'4C00 0000         CS3 space (64MB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | H'5000 00 | CS4 space (64MB)   |          | _                   |

| Normal<br>space         H'4800 0000<br>H'4400 0000         CS1 space (64MB)         -           Normal<br>space         H'4800 0000         CS0 space (64MB)         -           Normal<br>space         H'12000 0000         CS0 space (64MB)         -           Normal<br>space         H'12000 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           H'1000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           H'1800 0000         SPI multi-I/O-bus<br>space 1 (64MB)         -           H'1400 0000         CS5 space (64MB)         -           H'1000 0000         CS1 space (64MB)         -           H'0000 0000         CS2 space (64MB)         -           H'0000 0000         CS1 space (64MB)         -           H'0400 0000         CS1 space (64MB)         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | space | H'4C00 00 | CS3 space (64MB)   |          | CS3 mirror space    |

| Normal<br>space         H'4400 0000         CS0 space (64MB)         -           H'4000 0000         CS0 space (64MB)         -           H'2030 0000         H'2030 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           H'12000 0000         H'1000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           H'1400 0000         H'1000 0000         SPI multi-I/O-bus<br>space 1 (64MB)         Serial flash memory<br>(64MB)           H'1400 0000         H'1400 0000         CS5 space (64MB)         -           H'1000 0000         CS3 space (64MB)         -           H'1000 0000         CS2 space (64MB)         -           H'0800 0000         CS1 space (64MB)         -           H'0400 0000         CS1 space (64MB)         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | H'4800 00 | CS2 space (64MB)   |          | _                   |

| H'4000 0000         Others<br>(509MB)         Others<br>(509MB)           H'2030 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           H'2000 0000         H'2000 0000         Large-capacity on-<br>chip RAM (3MB)         Large-capacity on-<br>chip RAM (3MB)           Normal<br>space         H'1000 0000         SPI multi-I/O-bus<br>space 2 (64MB)         -           H'1800 0000         CS5 space (64MB)         -           H'1000 0000         CS4 space (64MB)         -           H'1000 0000         CS2 space (64MB)         -           H'000 0000         CS1 space (64MB)         -           H'0400 0000         CS1 space (64MB)         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | H'4400 00 | CS1 space (64MB)   |          | _                   |