# **RX Family**

How to Prevent the On-Chip Flash Memory from Being Accessed by Third Parties or Being Accidentally Programmed by Developers

# Summary

This application note describes methods of prohibiting access by third parties to the on-chip flash memory of Renesas MCUs and methods of protecting the on-chip flash memory during self-programming initiated by developers.

As used in this application note, the terms "developer" and "third party" are defined as follows.

Developer: The program developer. The person enabling protection of the on-chip flash memory.

Third party: A person other than the developer.

# **Target Devices**

RX Family

# RX Family

# Contents

| 1. Prote | ction from Third-Party Access              | 5    |

|----------|--------------------------------------------|------|

| 1.1 Dev  | ice Categories                             | 5    |

| 1.2 Dev  | ice Group A Protection Methods             | 7    |

| 1.2.1    | Specifications                             | 7    |

| 1.2.2    | Selecting Protection Settings              | 8    |

| 1.2.3    | Description of Protection Setting Patterns | . 10 |

| 1.2.3.   | 1 Protection Setting Pattern 1             | . 10 |

| 1.2.3.   | 2 Protection Setting Pattern 2             | . 11 |

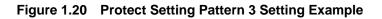

| 1.2.3.   | 3 Protection Setting Pattern 3             | . 12 |

| 1.2.3.   | 4 Protection Setting Pattern 4             | . 13 |

| 1.2.3.   | 5 Protection Setting Pattern 5             | . 14 |

| 1.2.4    | Protection Setting Examples                | . 15 |

| 1.3 Dev  | ice Group B Protection Methods             | . 16 |

|          | Specifications                             |      |

| 1.3.2    | Selecting Protection Settings              | . 17 |

| 1.3.3    | Description of Protection Setting Patterns | . 19 |

| 1.3.3.   | 1 Protection Setting Pattern 1             | . 19 |

| 1.3.3.   |                                            |      |

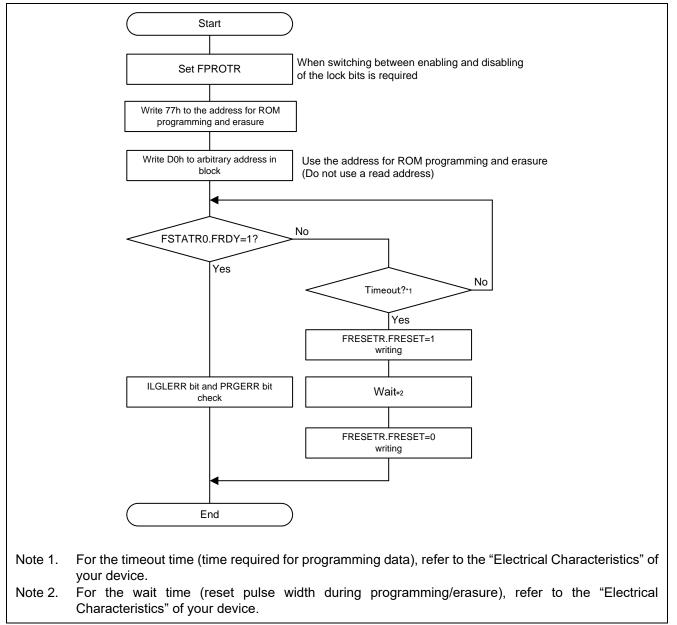

| 1.3.3.   | 3 Protection Setting Pattern 3             | . 21 |

| 1.3.3.   | 4 Protection Setting Pattern 4             | . 22 |

| 1.3.3.   | 5 Protection Setting Pattern 5             | . 23 |

|          | Protection Setting Examples                |      |

| 1.4 Dev  | ice Group C Protection Methods             | . 25 |

| 1.4.1    | Specifications                             | . 25 |

| 1.4.2    | Selecting Protection Settings              | . 26 |

| 1.4.3    | Description of Protection Setting Patterns |      |

| 1.4.3.   | 1 Protection Setting Pattern 1             | . 28 |

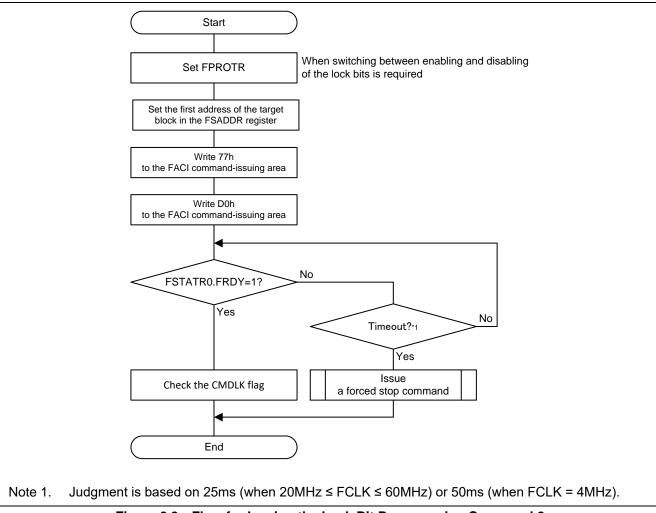

| 1.4.3.   |                                            |      |

| 1.4.3.   | 3 Protection Setting Pattern 3             | . 30 |

| 1.4.3.   | 0                                          |      |

| 1.4.3.   | 5 Protection Setting Pattern 5             | . 32 |

|          | Protection Setting Examples                |      |

|          | ice Group D Protection Methods             |      |

| 1.5.1    | Specifications                             | . 34 |

|          | Selecting Protection Settings              |      |

| 1.5.3    | Description of Protection Setting Patterns |      |

| 1.5.3.   |                                            |      |

| 1.5.3.   | 6                                          |      |

| 1.5.3.   | 5                                          |      |

| 1.5.3.   | 5                                          |      |

|          | Protection Setting Examples                |      |

|          | ice Group E Protection Methods             |      |

|          | Specifications                             |      |

| 1.6.2    | Selecting Protection Settings              | . 43 |

| 1.6.3 De                                                                                                                                                                                             | escription of Protection Setting Patterns                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1.6.3.1                                                                                                                                                                                              | Protection Setting Pattern 1                                                                                                                                                                                                                                                                                                                                                                                                   | 45                                                                                                             |

| 1.6.3.2                                                                                                                                                                                              | Protection Setting Pattern 2                                                                                                                                                                                                                                                                                                                                                                                                   | 46                                                                                                             |

| 1.6.3.3                                                                                                                                                                                              | Protection Setting Pattern 3                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                                                                             |

| 1.6.3.4                                                                                                                                                                                              | Protection Setting Pattern 4                                                                                                                                                                                                                                                                                                                                                                                                   | 48                                                                                                             |

| 1.6.4 Pr                                                                                                                                                                                             | otection Setting Examples                                                                                                                                                                                                                                                                                                                                                                                                      | 49                                                                                                             |

| 1.7 Devic                                                                                                                                                                                            | e Group F Protection Methods                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                                                                             |

| 1.7.1 Sp                                                                                                                                                                                             | pecifications                                                                                                                                                                                                                                                                                                                                                                                                                  | 50                                                                                                             |

| 1.7.2 Se                                                                                                                                                                                             | electing Protection Settings                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                                                             |

| 1.7.3 De                                                                                                                                                                                             | escription of Protection Setting Patterns                                                                                                                                                                                                                                                                                                                                                                                      | 53                                                                                                             |

| 1.7.3.1                                                                                                                                                                                              | Protection Setting Pattern 1                                                                                                                                                                                                                                                                                                                                                                                                   | 53                                                                                                             |

| 1.7.3.2                                                                                                                                                                                              | Protection Setting Pattern 2                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                                                                                             |

| 1.7.3.3                                                                                                                                                                                              | Protection Setting Pattern 3                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                                                             |

| 1.7.3.4                                                                                                                                                                                              | Protection Setting Pattern 4                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| 1.7.3.5                                                                                                                                                                                              | Protection Setting Pattern 5                                                                                                                                                                                                                                                                                                                                                                                                   | 57                                                                                                             |

|                                                                                                                                                                                                      | otection Setting Examples                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 1.8 Devic                                                                                                                                                                                            | e Group G Protection Methods                                                                                                                                                                                                                                                                                                                                                                                                   | 59                                                                                                             |

| •                                                                                                                                                                                                    | pecifications                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

| 1.8.2 Se                                                                                                                                                                                             | electing Protection Settings                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                                                                                             |

| 1.8.3 De                                                                                                                                                                                             | escription of Protection Setting Patterns                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 1.8.3.1                                                                                                                                                                                              | Protection Setting Pattern 1                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| 1.8.3.2                                                                                                                                                                                              | Protection Setting Pattern 2                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| 1.8.3.3                                                                                                                                                                                              | Protection Setting Pattern 3                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| 1.8.3.4                                                                                                                                                                                              | Protection Setting Pattern 4                                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                                                                             |

|                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|                                                                                                                                                                                                      | otection Setting Examples                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 1.8.4 Pr                                                                                                                                                                                             | otection Setting Examples                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                                                                                             |

| 1.8.4 Pr<br>2. Protect                                                                                                                                                                               | otection Setting Examples                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67                                                                                                       |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic                                                                                                                                                                  | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories                                                                                                                                                                                                                                                                                                                               | 66<br>67<br>67                                                                                                 |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic                                                                                                                                                     | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods                                                                                                                                                                                                                                                                                               | 66<br>67<br>67<br>68                                                                                           |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic                                                                                                                                                     | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming                                                                                                                                                                                                                                                           | 66<br>67<br>67<br>68<br>68                                                                                     |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1                                                                                                                              | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods                                                                                                                                                                                                                                                                                               | 66<br>67<br>67<br>68<br>68<br>69                                                                               |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)                                                                                                                       | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits                                                                                                                                                                                                   | 66<br>67<br>67<br>68<br>68<br>69<br>69                                                                         |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)                                                                                                                | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions                                                                                                                                                                                                                | 66<br>67<br>67<br>68<br>68<br>69<br>69<br>71                                                                   |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)                                                                                                         | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register                                                                                                                                                                               | 66<br>67<br>68<br>68<br>69<br>69<br>71<br>74                                                                   |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)                                                                                                  | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register<br>FLWE bit                                                                                                                                                                   | 66<br>67<br>67<br>68<br>68<br>69<br>71<br>74<br>75                                                             |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic                                                                                     | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register<br>FLWE bit<br>DBWE bit<br>e Group B Protection Methods                                                                                                                       | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76                                                             |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic                                                                                     | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register<br>FLWE bit<br>DBWE bit                                                                                                                                                       | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76                                                             |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr                                                                         | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register<br>FLWE bit<br>DBWE bit<br>e Group B Protection Methods                                                                                                                       | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77                                                 |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1                                                              | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register<br>FLWE bit<br>DBWE bit<br>e Group B Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions                                        | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77                                                 |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1<br>(1)                                                       | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods                                                                                                                                                                                                                                                                                               | 66<br>67<br>68<br>68<br>69<br>69<br>71<br>74<br>75<br>76<br>76<br>77<br>77<br>78                               |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic                     | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Lock Bits<br>FENTRYR Register<br>FLWE bit<br>DBWE bit<br>e Group B Protection Methods<br>otection during Self-Programming<br>Description of the Protection Functions<br>Area Protection<br>FENTRYR Register | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77<br>77<br>78<br>80                               |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1<br>(1)<br>(2)<br>(3)<br>(3)                                  | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods                                                                                                                                                                                                                                                                                               | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77<br>77<br>78<br>80<br>81                         |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>(2)<br>(3)<br>(4)<br>(5)      | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods                                                                                                                                                                                                                                                                                               | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77<br>77<br>78<br>80<br>81<br>82                   |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>(2)<br>(3)<br>(4)<br>(5)      | otection Setting Examples<br>ion during Self-Programming Initiated by Developers                                                                                                                                                                                                                                                                                                                                               | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77<br>77<br>78<br>80<br>81<br>82<br>83             |

| 1.8.4 Pr<br>2. Protect<br>2.1 Devic<br>2.2 Devic<br>2.2.1 Pr<br>2.2.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>2.3 Devic<br>2.3.1 Pr<br>2.3.1.1<br>(1)<br>(2)<br>(3)<br>(4)<br>(3)<br>(4)<br>(5)<br>2.3.2 Pr | otection Setting Examples<br>ion during Self-Programming Initiated by Developers<br>e Categories<br>e Group A Protection Methods                                                                                                                                                                                                                                                                                               | 66<br>67<br>68<br>68<br>69<br>71<br>74<br>75<br>76<br>76<br>77<br>77<br>78<br>80<br>81<br>81<br>82<br>83<br>84 |

|           | Information Program Command             |    |

|-----------|-----------------------------------------|----|

| 2.4 Devic | ce Group C Protection Methods           |    |

| 2.4.1 P   | rotection during Self-Programming       |    |

| 2.4.1.1   | Description of the Protection Functions |    |

| (1)       | Area Protection                         |    |

| (2)       | FENTRYR Register                        |    |

| (3)       | FLWE bit                                |    |

| 2.4.2 P   | rotection during Update                 |    |

| 2.4.2.1   | Description of the Protection Functions |    |

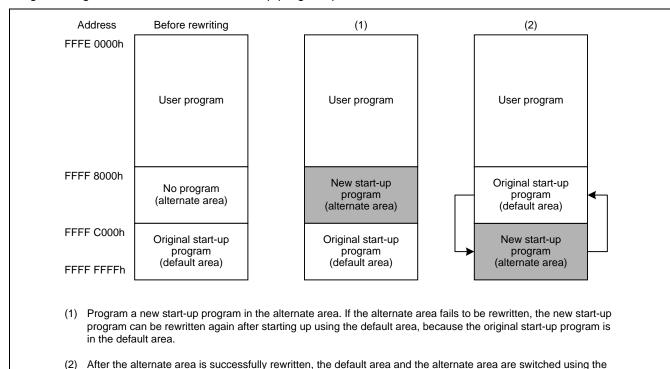

| (1)       | Start-Up Program Protection             |    |

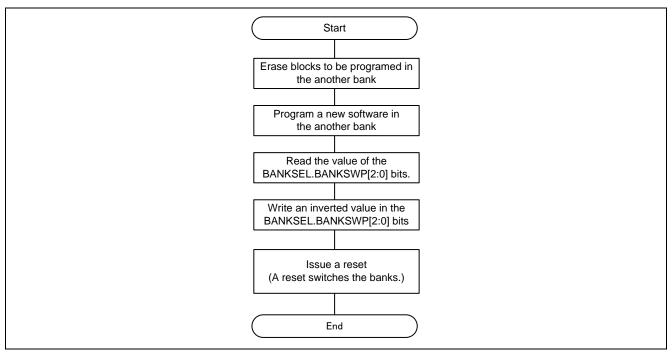

| (2)       | Dual Bank Function                      |    |

| 2.4.2.2   | Option-Setting Memory Setting Example   | 94 |

| 3. Refere | nce Documents                           |    |

# 1. Protection from Third-Party Access

# 1.1 Device Categories

Devices are categorized into seven groups according to their protection functions to prohibit access by third parties.

The device categories are listed in Table 1.1. For details of each protection function, refer to the User's Manual: Hardware of the device.

|         |                           | Protectio    | on Functio   | on (√: Sup   | ported, —    | Not Supp     | orted)       |              |              |              |              |

|---------|---------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|         |                           |              |              |              | Serial       |              | On-Chip      |              |              |              |              |

|         |                           |              | On-Chip      |              | Programmer   | Serial       | Debugger     |              |              |              | Access       |

|         |                           |              | Debugger     |              | Connection   | Programmer   | Connection   |              |              |              | Window       |

|         |                           | ID Code      | ID Code      | ROM Code     | Enable       | Command      | Enable       |              | Access       |              | Protection   |

| Group   | Devices                   | Protection   | Protection   | Protection   | /Disable     | Control      | /Disable     | Memory       | Window       | bit          | Command      |

| Device  | • RX210                   |              |              |              |              |              |              |              |              |              |              |

| group A | • RX610                   |              |              |              |              |              |              |              |              |              |              |

|         | • RX621                   |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX62G</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX62N</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX62T</li> </ul> | $\checkmark$ | $\checkmark$ | $\checkmark$ | <b>√</b> *1  | —            | —            | —            | —            | —            | —            |

|         | <ul> <li>RX630</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | • RX631                   |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX634</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX63N</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX63T</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX230</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | • RX231                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | <b>√</b> *1  | _            | _            |              | ~            | _            |              |

|         | • RX24T                   |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX24U</li> </ul> |              |              |              |              |              |              |              |              |              |              |

| Device  | • RX21A                   | $\checkmark$ | $\checkmark$ | *4           | <b>√</b> *1  |              | _            | _            | _            | _            | _            |

| group B | • RX220                   |              | •            |              | •            |              |              |              |              |              |              |

|         | • RX130                   |              |              |              |              |              |              |              |              |              |              |

|         | • RX13T                   |              |              |              |              |              |              |              |              |              |              |

|         | • RX23E-A                 | $\checkmark$ | $\checkmark$ | *4           | <b>√</b> *1  | —            | —            | —            | $\checkmark$ | —            | —            |

|         | <ul> <li>RX23T</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | • RX23W                   |              |              |              |              |              |              |              |              |              |              |

|         | • RX140                   | $\checkmark$ | $\checkmark$ | *4           | <b>√</b> *1  | —            | —            | _            | $\checkmark$ | —            | $\checkmark$ |

| Device  | • RX110                   |              |              |              |              |              |              |              |              |              |              |

| group C | • RX111                   | $\checkmark$ | $\checkmark$ | *4           | <b>√</b> *1  | —            | —            | _            | $\checkmark$ | —            | _            |

|         | • RX113                   |              |              |              |              |              |              |              |              |              |              |

| Device  | • RX64M                   | <b>√</b> *2  | <b>√</b> *3  | 1            | ✓            | ✓            |              | 1            |              |              |              |

| group D | • RX71M                   | <b>√</b> "∠  | <b>v</b> "5  | V            | v            | v            | —            | v            | _            |              | _            |

| Device  | • RX651                   |              |              |              |              |              |              |              |              |              |              |

| group E | <ul> <li>RX65N</li> </ul> |              |              |              |              |              |              |              |              |              |              |

|         | <ul> <li>RX66N</li> </ul> | $\checkmark$ | <b>√</b> *3  | $\checkmark$ | $\checkmark$ | _            | _            | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            |

|         | • RX72M                   |              |              |              |              |              |              |              |              |              |              |

|         | • RX72N                   |              |              |              |              |              |              |              |              |              |              |

| Device  | • RX66T                   |              |              |              |              |              |              |              |              |              |              |

| group F | <ul> <li>RX72T</li> </ul> | $\checkmark$ | <b>√</b> *3  | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | $\checkmark$ | —            | —            | _            |

| Device  | • RX671                   |              |              |              |              |              |              |              |              |              |              |

| group G |                           | $\checkmark$ | <b>√</b> *3  | $\checkmark$ | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |

#### Table 1.1 Device Categories

Note 1. The ID code protection function is used to make serial programmer connection enable/disable settings.

Note 2. When connected, there is no function for erasing the entire on-chip flash memory area.

Note 3. These do not have a capability to always prohibit connection of an on-chip debugger.

Note 4. The ROM Code Protection is not supported, because those devices cannot use parallel programmer.

# **1.2 Device Group A Protection Methods**

# 1.2.1 Specifications

Three protection functions are provided to prevent access by third parties to the on-chip flash memory: ID code protection, on-chip debugger ID code protection, and ROM code protection.

The access window is not a function to prevent access from third parties.

An overview of each of these protection functions is shown in Table 1.2

| Protection Type                        | Overview of Function                                                                                                                                                                                                                                               |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID Code Protection                     | After the MCU starts up in boot mode, ID authentication is performed when a host such as a PC is connected, prohibiting connection by third parties and preventing reading, programming, or erasing of the on-chip flash memory.                                   |

| On-Chip Debugger ID<br>Code Protection | After the MCU starts up in single-chip mode or user boot mode, ID<br>authentication is performed when an on-chip debugger is connected,<br>prohibiting connection by third parties and preventing reading, programming,<br>or erasing of the on-chip flash memory. |

| ROM Code Protection                    | When a parallel programmer is used, reading, programming, or erasing of the on-chip flash memory by third parties is prevented.                                                                                                                                    |

| Access Window <sup>*1</sup>            | If the access window is set, the area set outside the access window is prevented programming or erasing.<br>The access window is a function to prevent erroneous rewriting in case a program runs out of control during self-programming.                          |

Table 1.2 Overview of Protection Functions

Note 1. The access window is incorporated into RX230, RX231, RX24T and RX24U.

Note that whether or not ID code protection can be used for USB connections in boot mode differs depending on the device. A breakdown by device of the applicability of ID code protection for USB connections is shown in Table 1.3.

For details on the access window, see Chapter 2, Area Protection.

#### Table 1.3 List of Applicability of ID Code Protection for USB Connections

| Devices                                  | Applicability of ID Code Protection |

|------------------------------------------|-------------------------------------|

| RX621, RX62N, RX630, RX631, RX63N, RX63T | Not usable*1                        |

| RX230, RX231                             | Usable                              |

Note 1. When a USB connection is established, no ID authentication takes place but the user area and data area are erased, thereby preventing third parties from reading from the on-chip flash memory.

# 1.2.2 Selecting Protection Settings

The method of access prohibition differs according to the details of the ID code protection, on-chip debugger ID code protection, and ROM code protection settings, as well as how they are combined. It is therefore necessary to make protection settings appropriately to match the desired purpose.

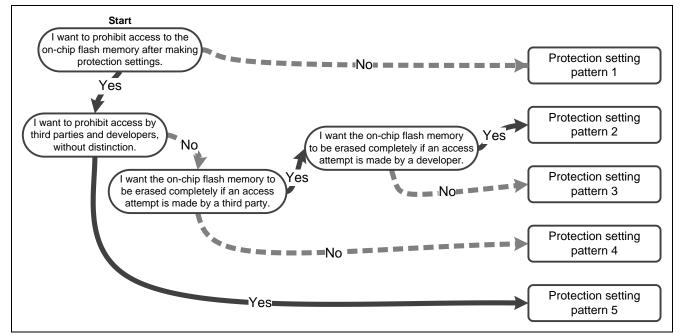

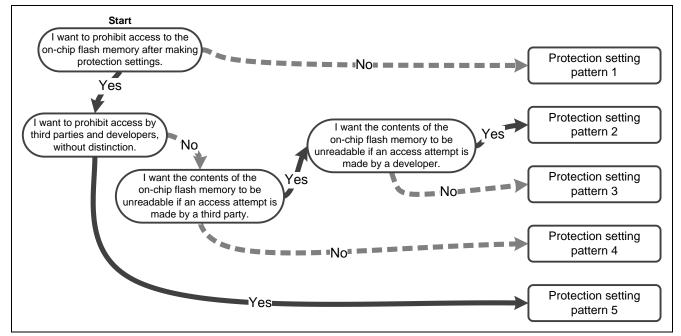

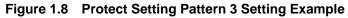

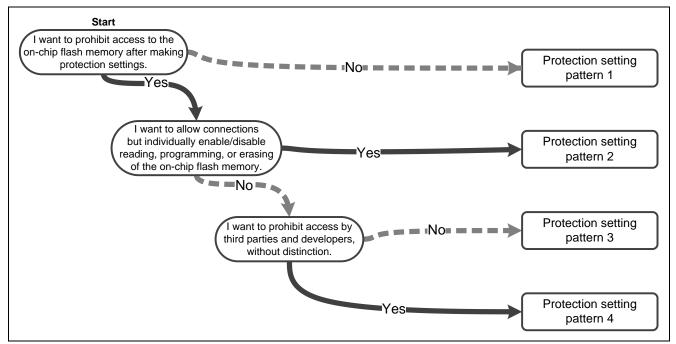

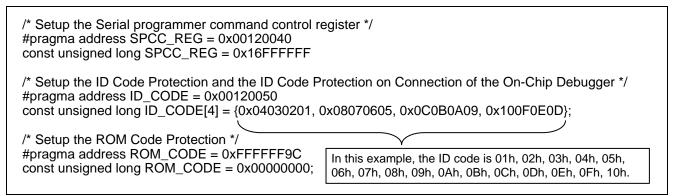

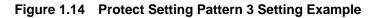

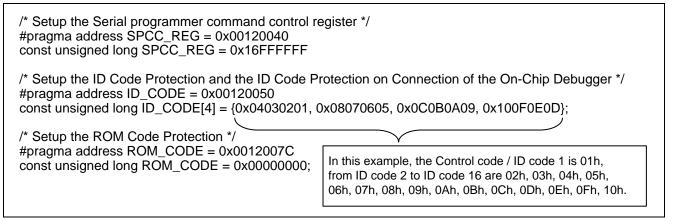

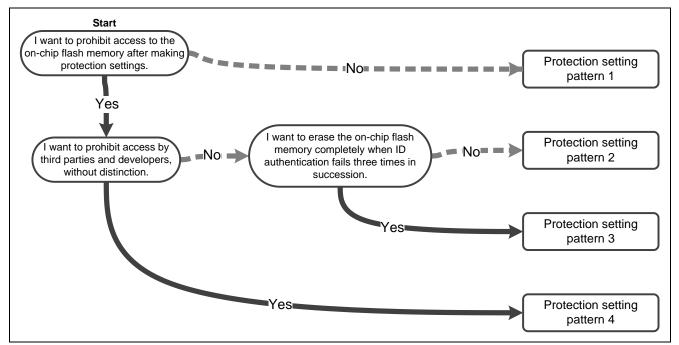

Select an optimal protection setting pattern based on the chart in Figure 1.1, Table 1.4, and Table 1.5. For details on each protection setting pattern, refer to 1.2.3.1 to 1.2.3.5.

Figure 1.1 Protection Setting Pattern Selection Chart

- Protection setting pattern 1 All protection against access by developers and third parties is disabled.

- Protection setting pattern 2

This protection setting pattern prevents reading by third parties. When a connection is made in boot mode, the on-chip flash memory is erased completely, without distinction between third parties and developers.

• Protection setting pattern 3

This protection setting pattern prevents reading by third parties. When a connection is made in boot mode, ID authentication takes place. If ID authentication fails, the on-chip flash memory is erased completely, without distinction between third parties and developers.

- Protection setting pattern 4 This protection setting pattern prevents reading, programming, or erasing by third parties.

- Protection setting pattern 5

This protection setting pattern prohibits connections by both developers and third parties. Once this protection setting pattern is applied, the protection cannot be removed, so caution is necessary.

| Protection | Connection in Boot Mode<br>(ID Code Protection) |              |       |              | Connection of On-Chip<br>Debugger<br>(On-Chip Debugger ID<br>Code Protection) |              |              |              | Connection of parallel<br>programmer<br>(ROM Code Protection) |        |              |              |

|------------|-------------------------------------------------|--------------|-------|--------------|-------------------------------------------------------------------------------|--------------|--------------|--------------|---------------------------------------------------------------|--------|--------------|--------------|

| Setting    | Deve                                            | eloper       | Thirc | d party      | Deve                                                                          | eloper       | Thire        | d party      | Deve                                                          | eloper | Thire        | d party      |

| Pattern    | R                                               | P/E          | R     | P/E          | R                                                                             | P/E          | R            | P/E          | R                                                             | P/E    | R            | P/E          |

| 1          | _                                               | $\checkmark$ | _     | $\checkmark$ | $\checkmark$                                                                  | ✓            | $\checkmark$ | $\checkmark$ | $\checkmark$                                                  | ✓      | $\checkmark$ | $\checkmark$ |

| 2          |                                                 | ✓            |       | ✓            | $\checkmark$                                                                  | ✓            | _            |              |                                                               |        |              |              |

| 3          | ✓                                               | ✓            | *1    | _            | $\checkmark$                                                                  | ✓            | —            |              |                                                               | _      |              |              |

| 4          | ✓                                               | $\checkmark$ |       |              | ✓                                                                             | $\checkmark$ | —            |              |                                                               |        |              | —            |

| 5          |                                                 | _            | _     | _            | _                                                                             | _            | _            |              |                                                               | _      |              | ✓            |

#### Table 1.4 Comparison of Protection Setting Patterns

R: Read, P/E: Program/Erase

✓: Allowed, —: Not allowed

Note 1. The on-chip flash memory is erased completely if repeated ID code mismatches occur. For details of the scope of "complete erasure," refer to the User's Manual: Hardware of the device.

| Protection<br>Setting<br>Pattern | ID Code Protection<br>(Protection for Connection<br>in Boot Mode)                                                                                                                        | On-Chip Debugger ID<br>Code Protection<br>(Protection for Connection<br>of On-Chip Debugger) | ROM Code Protection<br>(Protection for Connection<br>of parallel programmer) |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

| 1                                | Reading is prevented by                                                                                                                                                                  | Disabled                                                                                     | Disabled                                                                     |  |

| 2                                | complete erasure of the on-<br>chip flash memory.*1                                                                                                                                      | · · · · · · · · · · · · · · · · · · ·                                                        |                                                                              |  |

| 3                                | Reading, programming, and<br>erasing are enabled when the<br>ID code matches. The on-chip<br>flash memory is erased<br>completely <sup>*1</sup> if repeated ID<br>code mismatches occur. | the ID code matches.                                                                         | always.                                                                      |  |

| 4                                | Reading, programming, and<br>erasing are enabled when the<br>ID code matches.                                                                                                            | -                                                                                            |                                                                              |  |

| 5                                | Reading, programming, and erasing are prevented always.                                                                                                                                  | Reading, programming, and erasing are prevented always.                                      | -                                                                            |  |

#### Table 1.5 Functions of Protection Setting Patterns

Note 1. For details of the scope of "complete erasure," refer to the User's Manual: Hardware of the device.

# 1.2.3 Description of Protection Setting Patterns

# 1.2.3.1 Protection Setting Pattern 1

This pattern disables all protection. Note, however that the on-chip flash memory is erased completely when a connection is established in boot mode.

The setting details of protection setting pattern 1 are shown in Table 1.6.

#### Table 1.6 Protection Setting Pattern 1 Setting Details

| ID Code Protection an<br>Settings | ROM Code Protection<br>Settings |                          |

|-----------------------------------|---------------------------------|--------------------------|

| Control code (1 byte)             | ROM code (4 bytes)              |                          |

| FFh                               | All FFh                         | Other than               |

|                                   |                                 | (0000 0000h, 0000 0001h) |

For the setting method, refer to 1.2.4, Protection Setting Examples.

The operation of protection setting pattern 1 is outlined in Table 1.7.

| Protection Type                        | Operation                                                                                                                                                                                                                             | Prevented Items                                                                                                                              |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| ID Code Protection                     | When a connection is made in boot mode, no<br>ID authentication occurs and the on-chip<br>flash memory is erased completely. The<br>device then transitions to a state in which<br>reading, programming, and erasing are<br>possible. | Reading the contents of the on-<br>chip flash memory by a third<br>party is prevented by complete<br>erasure of the on-chip flash<br>memory. |

| On-Chip Debugger ID<br>Code Protection | When an on-chip debugger is connected, no ID authentication occurs and the connection with the on-chip debugger is established.                                                                                                       | None                                                                                                                                         |

| ROM Code Protection                    | Reading, programming, and erasing are possible when a parallel programmer is used.                                                                                                                                                    | None                                                                                                                                         |

Table 1.7 Operation of Protection Setting Pattern 1

# 1.2.3.2 Protection Setting Pattern 2

This pattern prevents reading, programming, or erasing of the on-chip flash memory by a parallel programmer. It also provides protection by ID authentication when an on-chip debugger is connected. Note that when a connection is made in boot mode, the on-chip flash memory is erased completely, without distinction between third parties and developers.

The setting details of protection setting pattern 2 are shown in Table 1.8.

| ID Code Protection an<br>Settings | ROM Code Protection<br>Settings |                    |

|-----------------------------------|---------------------------------|--------------------|

| Control code (1 byte)             | ID code (15 bytes)              | ROM code (4 bytes) |

| Other than (45h, 52h)             | Any value                       | 0000 0000h         |

For the setting method, refer to 1.2.4, Protection Setting Examples.

The operation of protection setting pattern 2 is outlined in Table 1.9.

| Protection Type                        | Operation                                                                                                                                                                                                                                            | Prevented Items                                                                                                                                                                                                                                      |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID Code Protection                     | When a connection is made in boot mode, no<br>ID authentication occurs and the on-chip<br>flash memory is erased completely. The<br>device then transitions to a state in which<br>reading, programming, and erasing are<br>possible.                | Reading the contents of the on-<br>chip flash memory by a third<br>party is prevented by complete<br>erasure of the on-chip flash<br>memory.                                                                                                         |

| On-Chip Debugger ID<br>Code Protection | When a connection is made by an on-chip<br>debugger, ID authentication is performed. If<br>the ID code matches, a connection is<br>established with the on-chip debugger. If the<br>ID code does not match, ID authentication is<br>performed again. | Third parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ID<br>authentication.<br>Developers can read, program,<br>or erase the on-chip flash<br>memory by providing the<br>matching ID code. |

| ROM Code Protection                    | Reading, programming, and erasing are prohibited when using a parallel programmer.                                                                                                                                                                   | Both developers and third<br>parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ROM code<br>protection.                                                                                       |

| Table 1.9 | Operation of Protection Setting | Pattern 2 |

|-----------|---------------------------------|-----------|

|-----------|---------------------------------|-----------|

# 1.2.3.3 Protection Setting Pattern 3

This pattern prevents reading, programming, or erasing of the on-chip flash memory by a parallel programmer. It also provides protection by ID authentication when an on-chip debugger is connected. As is the case when an on-chip debugger is connected, protection is provided by ID authentication when a connection is made in boot mode. However, if ID authentication fails three times in succession, the on-chip flash memory is erased completely.

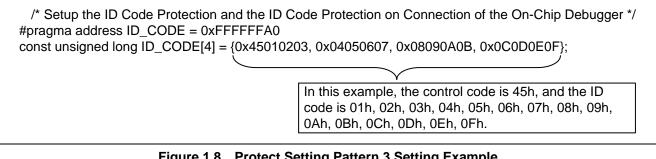

The setting details of protection setting pattern 3 are shown in Table 1.10.

| ID Code Protection and On-Chip Debugger ID Code Protection<br>Settings |                    | ROM Code Protection<br>Settings |

|------------------------------------------------------------------------|--------------------|---------------------------------|

| Control code (1 byte)                                                  | ID code (15 bytes) | ROM code (4 bytes)              |

| 45h                                                                    | Any value          | 0000 0000h                      |

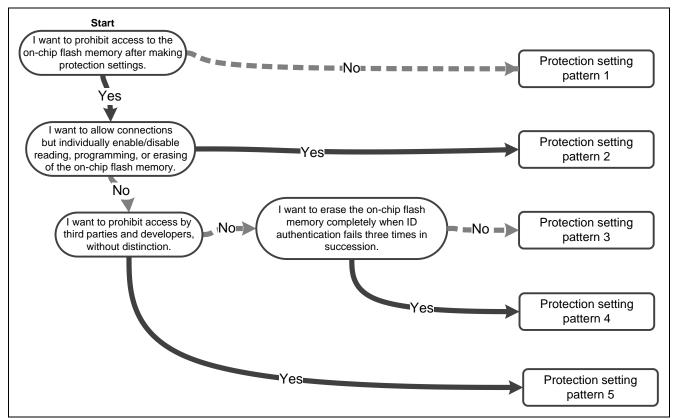

For the setting method, refer to 1.2.4, Protection Setting Examples.

The operation of protection setting pattern 3 is outlined in Table 1.11.

|  | Table 1.11 | <b>Operation of Protection Setting Pattern 3</b> |

|--|------------|--------------------------------------------------|

|--|------------|--------------------------------------------------|

| Protection Type                        | Operation                                                                                                                                                                                                                                                                                                                                                                                                         | Prevented Items                                                                                                                                                                                                                                             |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID Code Protection                     | Protection is provided by ID authentication<br>when a connection is made in boot mode. If<br>the ID code matches, the device transitions to<br>a state in which reading, programming, and<br>erasing are possible. If the ID code does not<br>match, ID authentication is performed again.<br>However, if ID authentication fails three times<br>in succession, the on-chip flash memory is<br>erased completely. | Reading the contents of the on-<br>chip flash memory by a third<br>party is prevented by complete<br>erasure of the on-chip flash<br>memory.<br>Developers can read, program,<br>or erase the on-chip flash<br>memory by providing the<br>matching ID code. |

| On-Chip Debugger ID<br>Code Protection | When a connection is made by an on-chip<br>debugger, ID authentication is performed. If<br>the ID code matches, a connection is<br>established with the on-chip debugger. If the<br>ID code does not match, ID authentication is<br>performed again.                                                                                                                                                              | Third parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ID<br>authentication.<br>Developers can read, program,<br>or erase the on-chip flash<br>memory by providing the<br>matching ID code.        |

| ROM Code Protection                    | Reading, programming, and erasing are prohibited when using a parallel programmer.                                                                                                                                                                                                                                                                                                                                | Both developers and third<br>parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ROM code<br>protection.                                                                                              |

# 1.2.3.4 Protection Setting Pattern 4

This pattern prevents reading, programming, or erasing of the on-chip flash memory by a parallel programmer. It also provides protection by ID authentication when an on-chip debugger is connected. As is the case when an on-chip debugger is connected, protection is provided by ID authentication when a connection is made in boot mode.

The setting details of protection setting pattern 4 are shown in Table 1.12.

| ID Code Protection and On-Chip Debugger ID Code Protection<br>Settings |                                                            | ROM Code Protection<br>Settings |

|------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------|

| Control code (1 byte)                                                  | ID code (15 bytes)                                         | ROM code (4 bytes)              |

| 52h                                                                    | Other than 50h, 72h, 6Fh, 74h, 65h, 63h, 74h,<br>FFh,, FFh | 0000 0000h                      |

For the setting method, refer to 1.2.4, Protection Setting Examples.

The operation of protection setting pattern 4 is outlined in Table 1.13.

| Table 1.13 | <b>Operation of Protection Setting Pattern 4</b> |

|------------|--------------------------------------------------|

|            | operation of i rotection octing i attern 4       |

| Protection Type                        | Operation                                                                                                                                                                                                                                                                                  | Prevented Items                                                                                                                                                                                                                                      |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID Code Protection                     | Protection is provided by ID authentication<br>when a connection is made in boot mode. If<br>the ID code matches, the device transitions to<br>a state in which reading, programming, and<br>erasing are possible. If the ID code does not<br>match, ID authentication is performed again. | Third parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ID<br>authentication.<br>Developers can read, program,<br>or erase the on-chip flash<br>memory by providing the<br>matching ID code. |

| On-Chip Debugger ID<br>Code Protection | When a connection is made by an on-chip<br>debugger, ID authentication is performed. If<br>the ID code matches, a connection is<br>established with the on-chip debugger. If the<br>ID code does not match, ID authentication is<br>performed again.                                       | Third parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ID<br>authentication.<br>Developers can read, program,<br>or erase the on-chip flash<br>memory by providing the<br>matching ID code. |

| ROM Code Protection                    | Reading, programming, and erasing are prohibited when using a parallel programmer.                                                                                                                                                                                                         | Both developers and third<br>parties are prevented from<br>reading, programming, or<br>erasing the on-chip flash<br>memory by means of ROM code<br>protection.                                                                                       |

# 1.2.3.5 Protection Setting Pattern 5

This pattern prevents reading, programming, or erasing of the on-chip flash memory by using a parallel programmer, when an on-chip debugger is connected, and when a connection is made in boot mode.

Note: After this setting is made and the device is reset, the protection cannot be removed by any method, so caution is necessary.

The setting details of protection setting pattern 5 are shown in Table 1.14.

| Table 1.14 | Protection Setting Pattern 5 Setting Details |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| ID Code Protection and On-Chip Debugger ID Code Protection<br>Settings |                                              | ROM Code Protection<br>Settings |

|------------------------------------------------------------------------|----------------------------------------------|---------------------------------|

| Control code (1 byte)                                                  | ID code (15 bytes)                           | ROM code (4 bytes)              |

| 52h                                                                    | 50h, 72h, 6Fh, 74h, 65h, 63h, 74h, FFh,, FFh | 0000 0000h                      |

For the setting method, refer to 1.2.4, Protection Setting Examples.

The operation of protection setting pattern 5 is outlined in Table 1.15.

#### Table 1.15 Operation of Protection Setting Pattern 5

| Protection Type                        | Operation                                                                                                                                                                      | Prevented Items                                                                                                                                                |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ID Code Protection                     | ID authentication is performed when a connection is made in boot mode, but the ID code is always processed as not matching, and ID authentication is performed again.          | Connections are prohibited,<br>preventing both third parties and<br>developers, without distinction,<br>from reading, programming, and<br>erasing.             |  |