# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8 Family, H8S Family, SuperH RISC Engine Family

Flash Memory Programming Routines

### Introduction

All Renesas microcontrollers featuring Flash memory have the ability to self program their Flash memory. This opens up the opportunity to explore new applications and enhance existing ones. For example firmware can be updated in the field via a modem, Internet, wireless etc or motor characterisation data can be changed throughout its lifetime.

At the time of writing Renesas are manufacturing Flash microcontrollers with a  $0.18\mu$ m process complementing the  $0.6\mu$ m and  $0.35\mu$ m based devices. The objective of this apps note is to give an overview of programming and erasing  $0.6\mu$ m,  $0.35\mu$ m and  $0.18\mu$ m based 16-bit and 32-bit microcontrollers and to provide example routines for doing this written in 'C'.

### Contents

| FLASH MEMORY PROGRAMMING MODES |                                                                                                        |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| 0.6μM ALGORITHMS               |                                                                                                        |  |  |

| 0.6μM PROGRAM                  | I/PROGRAM-VERIFY                                                                                       |  |  |

| 0.6μM ERASE/ER                 | ASE-VERIFY                                                                                             |  |  |

| 0.35μM ALGORIT                 | HMS12                                                                                                  |  |  |

| 0.35µM PROGRA                  | M/PROGRAM-VERIFY12                                                                                     |  |  |

| 0.35µM ERASE/E                 | RASE-VERIFY                                                                                            |  |  |

| <sup>*</sup> IMPORTANT NO      | TE RELATING TO 0.35 M DEVICES                                                                          |  |  |

| 0.18μM ALGORIT                 | HMS                                                                                                    |  |  |

| 0.18µM PROGRA                  | MMING                                                                                                  |  |  |

| $0.18 \mu M ERASING$           |                                                                                                        |  |  |

| SUMMARY                        |                                                                                                        |  |  |

| APPENDIX A –                   | RENESAS 0.6µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR H8S/2144F                 |  |  |

| APPENDIX B –                   | RENESAS 0.6µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR SH7045F                   |  |  |

| APPENDIX C –                   | RENESAS 0.35µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR H8S/2612F                |  |  |

| APPENDIX D –                   | RENESAS 0.35µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR SH7047F                  |  |  |

| APPENDIX E -                   | RENESAS 0.35µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR H8/3664F MICROCONTROLLER |  |  |

| APPENDIX F –                   | RENESAS 0.18µM FLASH PROGRAMING & ERASING ROUTINES<br>FOR H8/3069F                                     |  |  |

| APPENDIX G –                   | RENESAS 0.18µM FLASH PROGRAMING & ERASING ROUTINES<br>FOR SH7058F94                                    |  |  |

| WEBSITE AND SUPPORT            |                                                                                                        |  |  |

# Flash Memory Programming Modes

Renesas Flash microcontrollers typically have three programming modes, PROM, boot and user.

PROM mode requires the use of an external 'EPROM' type programmer where the microcontroller is placed into a socket and programmed. This method offers high programming speeds but lacks flexibility and has limited use in the field.

Boot mode is entered by setting values on a combination of the micro's pins and resetting the device. The micro will then execute a 'hidden' program which erases the Flash memory for security purposes, auto-bauds with a host and then allows a programming kernel to be downloaded into the internal RAM of the micro and executed. This mode allows unprogrammed devices to have their Flash memory programmed in-circuit and in the field. This mode is supported by PC hosted applications such as FDT (Flash Development Toolkit) available from <u>http://www.renesas.com</u> It should be noted that in this mode the Flash memory is erased and so must be completely reprogrammed each time it is used and that the SCI port used in the boot process is fixed.

The 0.18µm devices introduce an additional boot mode called 'user boot mode'. In this mode the device boots from an additional area of Flash, typically 8kB in size and starting from address 0, which takes the place of the 'normal' user Flash memory. What differentiates user boot mode from boot mode is that this additional area of Flash can be programmed by the user making the implementation of a bootloader a simpler prospect. It should be noted that the user boot mode area of Flash can only be programmed from 'normal' boot mode. When in user boot mode the 'normal' user Flash area can be erased and programmed. During the erase sequence of 'normal' boot mode both the 'normal' user area of Flash and the user boot mode area of Flash are erased.

User mode offers the most flexible approach to in-field programming. With this mode the micro is able to reprogram itself by copying the required routines from existing memory contents into RAM or external memory and running from there. This method allows partial erasing and reprogramming of the memory and is particularly suited to bootloader type scenarios. Unlike boot mode the way data is supplied to the device is not limited to a particular SCI channel as, by its very nature, it is user defined and so can be via a parallel interface, wireless link or across the Internet etc.

In all cases it is important to note that while the Flash memory of the micro is being erased or programmed the Flash memory must not be accessed. This means that the erasing and programming code must run from internal RAM or external memory and interrupts should be disabled (unless in the case of SH the vector table is located to non-Flash memory and the VBR changed accordingly).

It is the intention of this apps note to present 0.6µm, 0.35µm and 0.18µm programming and erasing routines for H8/300H, H8S and SH-2 Renesas microcontroller families that can be used in user mode applications. This apps note will not be concerned with the mechanics of getting data into the device as this will be application specific. As previously mentioned, user mode typically runs routines from internal RAM that have been copied from Flash memory which means that these routines must be linked for RAM but relocated and stored in Flash. There are various methods of achieving this storage and relocation some of which have been covered in other Renesas application notes. Therefore, the reading of application note REG05B0021-0100 is recommended.

All H8S and H8/300H code examples have been developed using HEW (High\_Performance Embedded Workshop) v1.3 and Renesas C/C++ compiler version v4.0a. The SH-2 examples have been tested using HEW v1.3 and Renesas C/C++ compiler v6.0a.

# 0.6µm Algorithms

The 0.6µm Renesas microcontroller Flash memory has the following characteristics.

The Flash memory must be programmed in units of 32 bytes starting on a 32 byte boundary.

The Flash memory is split into sectors of varying sizes.

Erasing is performed on a sector by sector basis.

The erased state is all 1's.

Programming must be performed in the erased state.

Programming data is written in 16-bit units for H8(S)(300H) and 32-bits for SH-2.

Programming and erase verification data is read in 16-bit units for H8S & H8/300H and 32-bits for SH-2.

Although all 0.6µm Renesas Flash microcontrollers essentially have common programming and erasing algorithms it is important that this apps note is read in conjunction with the hardware manual for the device being programmed as there can be subtle differences.

# 0.6µm Program/Program-Verify

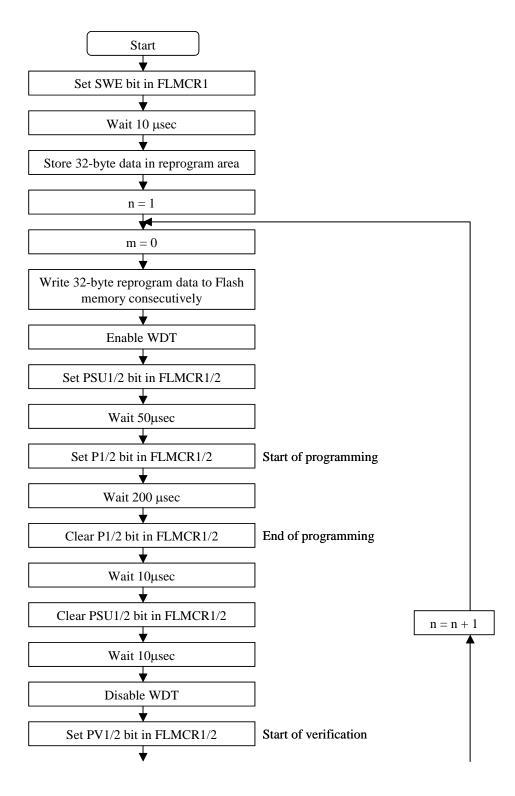

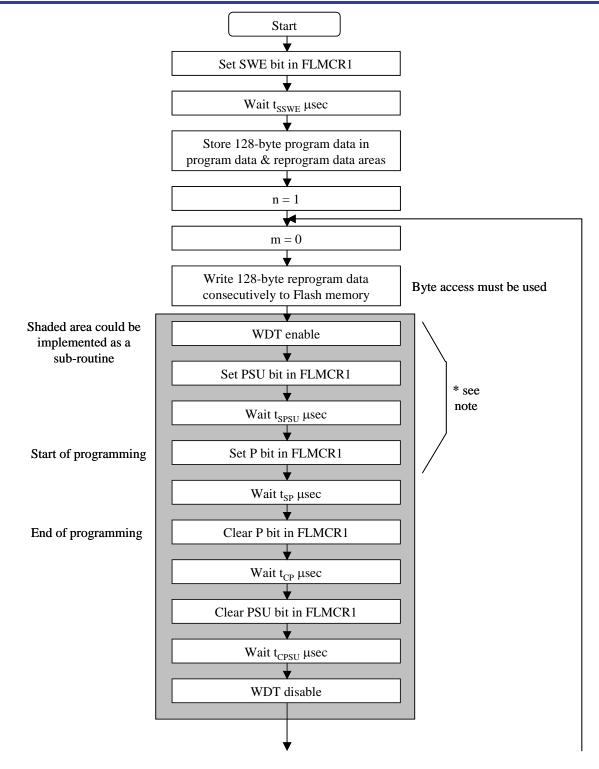

Figure 1 shows the typical program/program verify algorithm for  $0.6 \mu m$  Renesas Flash microcontrollers.

Figure1: 0.6µm Program/Program-Verify Algorithm

Important aspects of the 0.6µm program/program-verify algorithm to note include:

- All delay times are minimum times required to allow the internal signals to settle with one major exception the time the programming signal (P bit in FLMCR) is set. This time is a MAXIMUM and should not be exceeded.

- Loop counts are maximum values and should not be exceeded.

- When performing a dummy write during the verify stage the dummy write should be performed as a byte access.

- During the verify stage the data read back from the Flash should be compared against the actual data to be programmed and not the reprogram data.

- Programming should only be performed with the Flash cells in the erased ('1') state.

The program/program-verify process is a two stage affair. First an attempt to program a Flash line of 32-bytes is made. Then the Flash memory is put into program-verify mode and the programmed data read back using a 'weak' read of the cells. Here if the data is read back correctly with a 'weak' read then the cell's contents can be guaranteed over the data retention lifetime and temperature range specified for the individual device. If any of the bits fail to stick then reprogram data is calculated that only attempts to reprogram the bits that need programming next time and so avoiding the over-programming of cells that stick early in the programming process. This is repeated until either the Flash memory is programmed successfully or the maximum number of programming attempts is reached.

The reprogram data is calculated according to the following truth table.

| Required Data | Verify Data Read | Reprogram Data |

|---------------|------------------|----------------|

| 0             | 0                | 1              |

| 0             | 1                | 0              |

| 1             | 0                | 1              |

| 1             | 1                | 1              |

#### Table 1: Reprogramming Data

Appendix A contains source code for implementing the program/program-verify algorithm described above for the H8S and H8/300H. This code has been tested on an H8S/2144F device. This code should be taken as an example and should be modified where necessary for the particular device being programmed and its xtal frequency. It is worth noting that the delays are implemented using a hardware timer and that for the shorter periods the waiting time will be slightly greater than the desired value. This is acceptable as these shorter delays are provided to allow internal signals to settle and so are, as previously mentioned, minimum values.

Appendix B contains example source code for the 0.6 µm program/program verify algorithm for the SH-2 series of Renesas microcontrollers. This code has been tested on an SH7045F device.

A 32-byte Flash line can be programmed by calling the function 'prog\_flash\_line\_32' which has the following prototype.

unsigned char prog\_flash\_line\_32 (unsigned long t\_address, union char\_rd\_datum\_union \*p\_data)

As can be seen the function is passed two variables. The first, 't\_address' is the address of the first byte to be programmed in the Flash memory and must be on a 32-byte boundary. The second variable, 'p\_data', is a pointer to a 'char\_rd\_datum\_union' which contains the 32 bytes of data to be programmed into the Flash. The function returns a programming success or failure status byte. This function is identical in the two listings with its functionality being modified by the typedef 'read\_datum' which is 16-bits in size for the H8S implementation and 32-bits for the SH-2.

# 0.6µm Erase/Erase-Verify

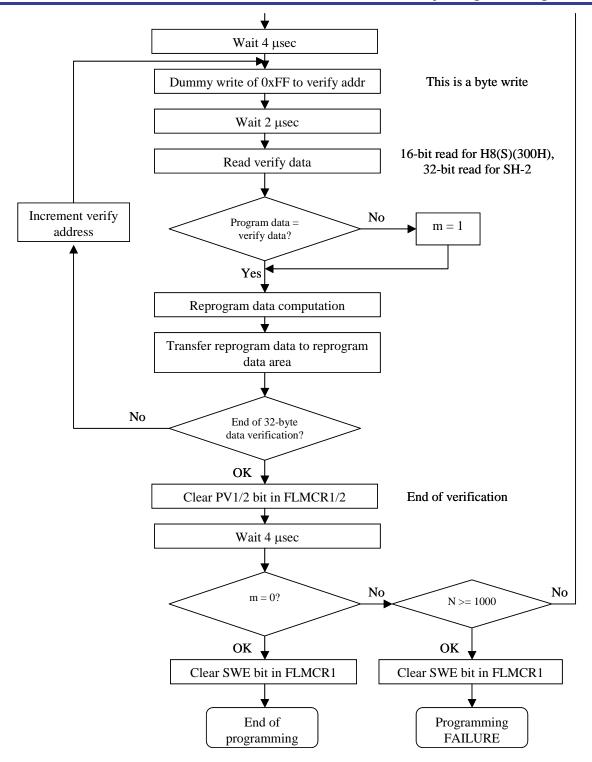

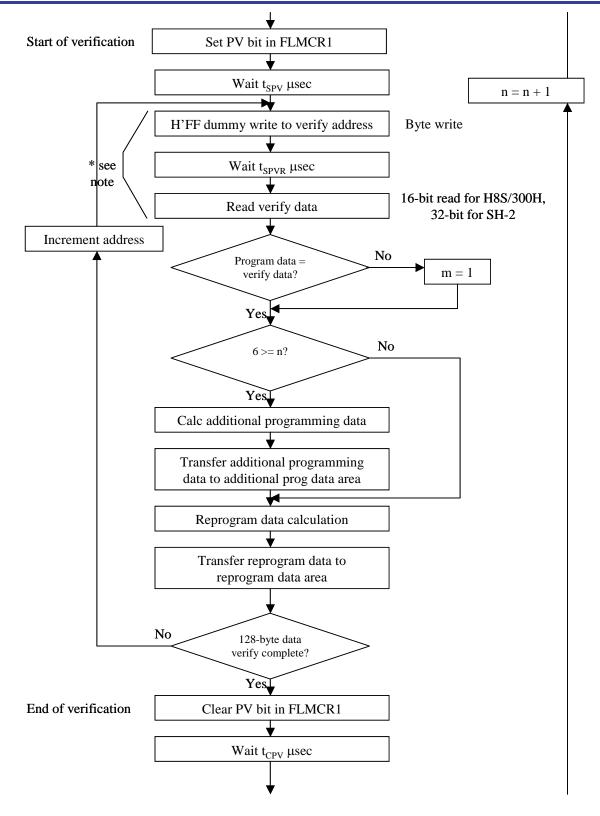

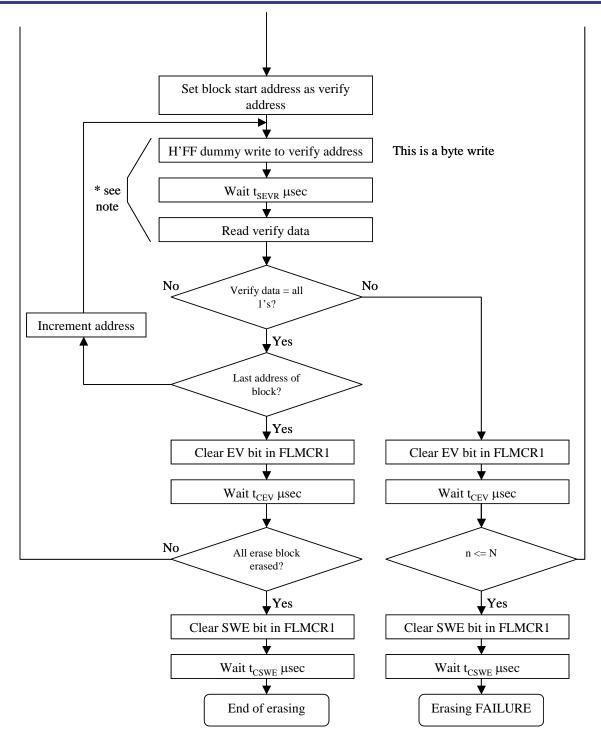

Figure 2 below shows the typical erase/erase verify algorithm for  $0.6\mu m$  Renesas Flash microcontrollers.

Figure 2: 0.6µm Erase/Erase-Verify Algorithm

Important aspects of the 0.6µm erase/erase-verify algorithm to note include:

- All delay times are minimum times required to allow the internal signals to settle with one major exception the time the erase signal (E bit in FLMCR) is set. This time is a MAXIMUM and should not be exceeded.

- The erase pulse time is in units of msec and the settling times in units of µsec.

- Loop counts are maximum values and should not be exceeded.

- The dummy write performed during the erase-verify stage should be a byte wide access.

- During the verify stage the Flash should be accessed as 16-bits for H8S/300H and 32-bits for SH-2.

- The erased state is all 1's.

ENESAS

- Pre-programming the Flash contents to '0' is not necessary.

- Only one bit in the EBR registers should be set at any one time as each Flash block must be erased separately.

As with the programming of the Flash memory the erase/erase-verify is a two stage process. An attempt is made to erase the Flash block then the memory is placed into erase verify mode and a 'weak' read of its contents made. If any bit in the Flash block is not set to '1' when read then another attempt is made to erase the block. This process is repeated until either the Flash block is successfully erased or the maximum number of erase attempts is reached.

The source code listings in Appendices A and B contain a function to erase a specified Flash block. The prototype for this function is shown below.

unsigned char erase\_block\_06\_um (unsigned char block\_num)

The function should be passed the number of the Flash block to be erased with the first block being numbered '0'. A success or failure status byte is returned to the caller. The same function can be used with both H8S and SH-2 based  $0.6\mu m$  Flash memory so long as the typedef 'read\_datum' is declared accordingly.

# 0.35µm Algorithms

The 0.35µm Renesas microcontroller Flash memory has the following characteristics.

- The Flash memory must be programmed in units of 128 bytes starting on a 128 byte boundary.

- The Flash memory is split into sectors of varying sizes.

- Erasing is performed on a sector by sector basis.

- The erased state is all 1's.

- Programming must be performed in the erased state.

- Programming data is written in 16-bit units for H8(S)(300H) and 32-bits for SH-2.

- Programming and erase verification data is read in 16-bit units for H8S & H8/300H and 32bits for SH-2.

- Programming times are reduced when compared to the 0.6µm Flash memory based Renesas microcontrollers.

Although all 0.35µm Renesas Flash microcontrollers essentially have common programming and erasing algorithms it is important that this apps note is read in conjunction with the hardware manual for the device being programmed as there are can subtle differences introduced.

# 0.35µm Program/Program-Verify

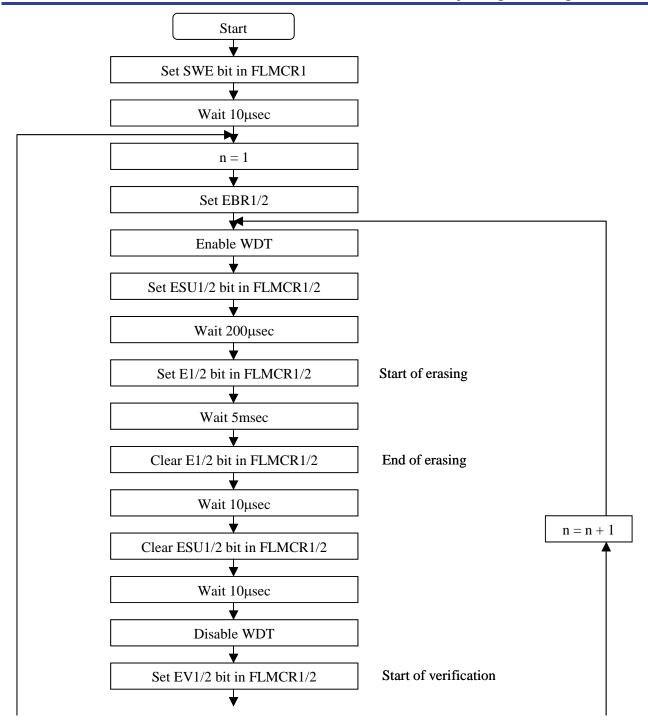

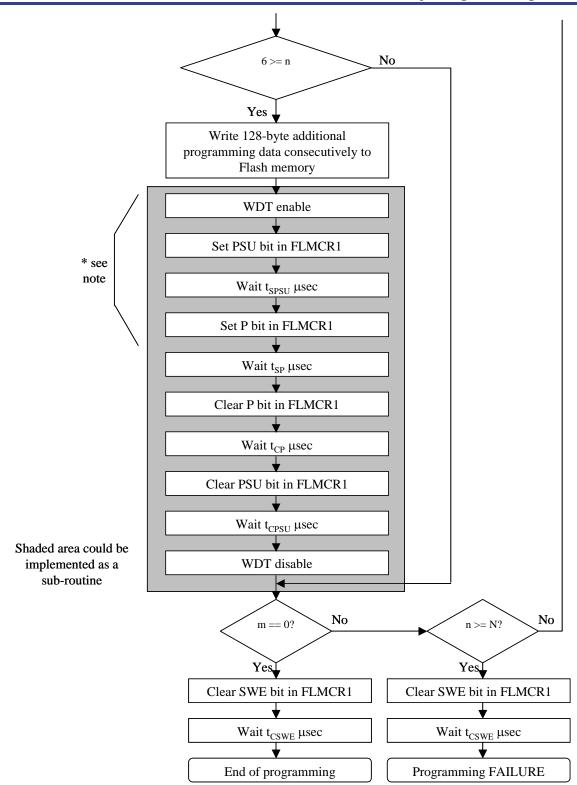

Figure 3 shows the typical program-verify algorithm for  $0.35 \mu m$  Renesas Flash microcontrollers.

Figure 3: 0.35µmProgram/Program-Verify Algorithm

Important aspects of the 0.35µm program/program-verify algorithm worthy of note include:

- The actual values for the delays given in the flowchart should be obtained from the hardware manual for the device being programmed.

- All delay times are minimum times required to allow the internal signals to settle with the exception of the time the 'P' bit is set in the FLMCR1 register. This time is a MAXIMUM value and should not be exceeded.

- Loop counts are maximum values and as such should not be exceeded.

- The verify dummy write should be a byte write of H'FF.

- The verify data read back during the program verify stage must be compared with the actual data to be programmed into the Flash and not the reprogram data or additional program data.

- Programming should only be performed on Flash cells which are in the erased state, '1'.

As can be seen from the algorithm the 0.35µm program/program-verify algorithm is more complex than its 0.6µm counterpart. The program/program-verify process is again a two stage affair with the Flash line being programmed and then verified using the 'weak' read as previously discussed in the 0.6µm section of this apps note. During the programming phase the length of time the 'P' bit in the FLAMCR1 register is set varies depending on how many attempts to program the Flash line have been made. Typically, for the first 6 programming attempts the 'P' bit is set for 30µs and then for the remaining attempts this extends to 200µs. Also, for the first 6 programming attempts after the intial 30µs programming pulse using the reprogramming data there is a extra programming pulse, typically 10µs long, using the additional programming data.

The reprogram data is calculated in the same way as for the 0.6µm algorithm and for completeness is given in table 2 below.

| Required Data | Verify Data Read | Reprogram Data |

|---------------|------------------|----------------|

| 0             | 0                | 1              |

| 0             | 1                | 0              |

| 1             | 0                | 1              |

| 1             | 1                | 1              |

#### Table 2: Reprogramming Data

The additional programming data used during the first 6 programming attempts is calculated according to the truth table shown in table 3 below.

| Reprogram Data | Verify Data Read | Additional Programming Data |

|----------------|------------------|-----------------------------|

|                |                  |                             |

| 0              | 0                | 0                           |

| 0              | 1                | 1                           |

| 1              | 0                | 1                           |

| 1              | 1                | 1                           |

#### Table 3: Additional Programming Data

Appendix C contains C source code for implementing the program/program-verify algorithm described by figure 3 for the H8S series. This code has been tested on an H8S/2612F microcontroller. As with the 0.6µm code this C source should be viewed as example code and modified where necessary to meet the Flash memory programming requirements of a particular Renesas microcontroller. Note should be made that the correct operation of this code is affected by the frequency of the xtal connected to the micro. In this code the xtal frequency is specified as 18.432MHz via the definition 'XTAL' which should be changed to reflect the frequency of the target device. Again the timing delays have been achieved using a hardware timer and so in the case of the shorter delays they can be longer than required but this is not a problem for settling times which have specified minimum values.

Appendix D contains C source code for the SH-2 0.35µm program/program-verify algorithm. This code has been tested on an SH7047F microcontroller.

In both instances a 128-byte Flash line can be programmed by calling the function 'prog\_flash\_line\_128' which has the following definition.

unsigned char prog\_flash\_line\_128 (unsigned long t\_address, union char\_rd\_datum\_union \*p\_data)

The first parameter passed to this function is the start address of the Flash memory to be programmed which must be on a 128-byte boundary. The second passed parameter is a pointer to a 'char\_rd\_datum\_union' union containing the data to be programmed. The function is identical for both H8S and SH-2 with the functionality changing depending on the type specifed by the typedef 'read\_datum'.

# $0.35 \mu m$ Erase/Erase-Verify

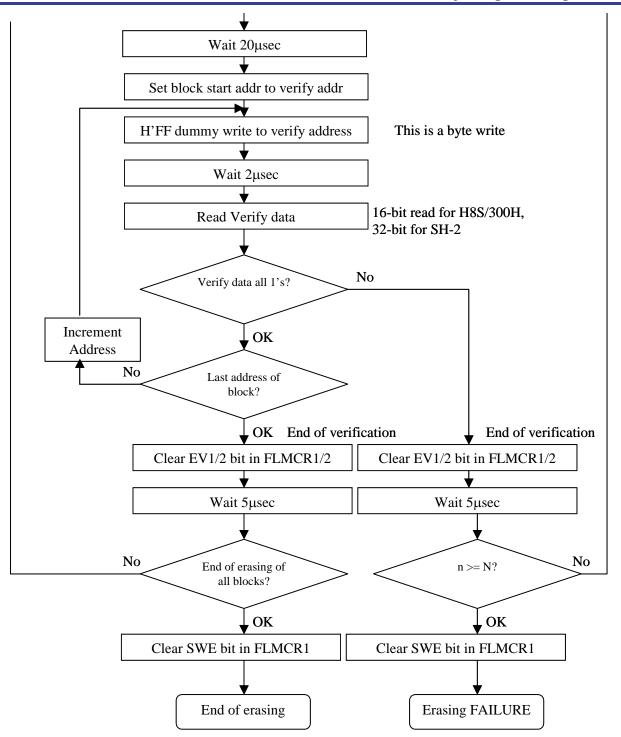

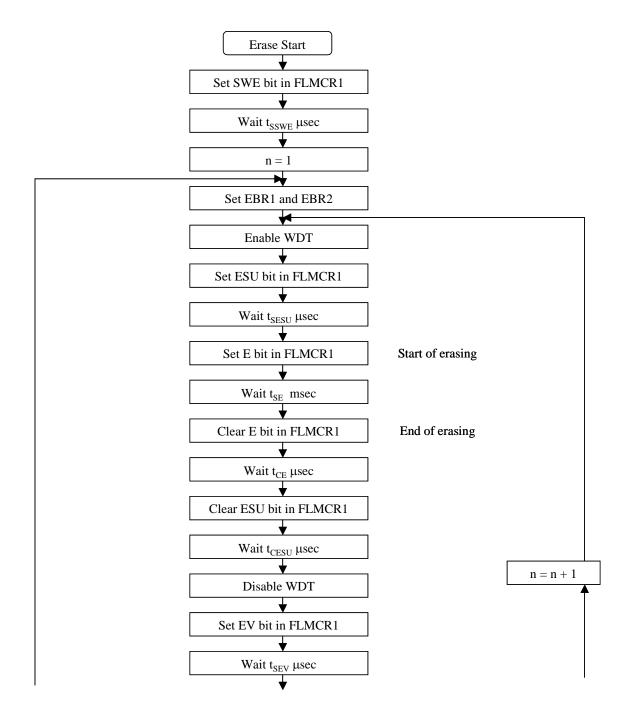

Figure 4 below shows the typical erase/erase-verify algorithm for  $0.35 \mu m$  Renesas Flash microcontrollers.

Figure 4: 0.35 µm Erase/Erase-Verify Algorithm

Important aspects of the 0.35µm erase/erase-verify algorithm worthy of note include:

- All delay times are minimum times required to allow the internal signals to settle with one major exception the time the erase signal (E bit in FLMCR) is set. This time is a MAXIMUM and should not be exceeded.

- The erase pulse time is in units of msec and the settling times in units of µsec.

- Loop counts are maximum values and should not be exceeded.

- When performing a dummy write during the verify stage the dummy write should be performed as a byte access.

- During the verify stage the Flash should be accessed as 16-bits for H8(S)(300H) and 32-bits for SH-2.

- Pre-programming the Flash contents to '0' is not necessary.

- Only one bit in the EBR registers should be set at any one time as each Flash block must be erased separately.

As with 0.6µm Flash erasure the 0.35µm memory is erased in a two stage process. First an attempt is made to erase the Flash block and then the memory is placed into erase-verify mode and its contents read back with a 'weak' read and compared with the erase value of all 1s. If any of the bits in the block are not read back as '1' then another attempt is made to erase the block. This process is repeated until either the Flash memory block is successfully erased or the maximum number of erase attempts specified for the device is reached.

Appendices C and D contain soure code listings with functions to erase a specified  $0.35\mu$ m Flash block for both the H8S/2612F and SH7047F Renesas microcontrollers. The prototype for the erase function is shown below.

unsigned char erase\_block\_035\_um (unsigned char block\_num);

The function should be passed the number of the Flash block to be erased with the first block being numbered '0'. A success or failure status byte is returned to the caller. The same function can be used with both H8(S)(300H) and SH-2 based 0.35µm Flash memory so long as the typedef 'read\_datum' is declared accordingly.

# <sup>\*</sup>Important Note Relating to 0.35µm Devices

The Renesas H8/3664F microcontroller, a member of the H8/300H-Tiny family, has a requiremnt where an 'RTS' instruction is not permitted at certain points in the program/program-verify and erase/erase-verify processes. Figures 3 and 4 indicate the points in the algorithm where this is applicable. This impacts the source code provided in appendices C and D as the affected parts of the algorithm feature delays and the code uses a function call to a 'delay' function to implement the delay. As the function call eventually results in an 'RTS' this will cause problems. A workaround for this problem is to manually inline the 'delay' function code inplace of the function call at the points highlighted in figures 3 and 4.

Although this is a requirement of the H8/3664F it may not be limited to this device. Therefore, it is strongly recommended that the latest hardware manual is obtained for the microcontroller being used and the Flash algorithms are examined carefully. Failure to do so could permanently damage the microcontroller.

Appendix E contains C source code with modified program/program-verify and erase/erase-verify routines specifically for the H8/3664F. In these routines the 'delay' function calls have been replaced by inline code at the critical points mentioned above. In order to reduce the code size for the H8/3664F implementation a separate 'apply\_write\_pulse' function has been used. This enables the programming and erasing functionality to comfortably fit in the internal RAM of this device.

# 0.18µm Algorithms

The 0.18µm Renesas microcontroller Flash memory has the following characteristics.

- The Flash memory is programmed in units of 128 bytes starting on a 128 byte boundary.

- The erasing and programming routines are built into the device and called from a user application.

- The Flash memory is split into sectors of varying sizes.

- Erasing is performed on a sector by sector basis.

- The erased state is all 1's.

- Programming must only be performed in the erased state.

- Programming times are reduced compared to 0.6µm and 0.35µm based Renesas microcontrollers.

Although all 0.18µm Renesas Flash microcontrollers essentially have common programming and erasing algorithms, it is important that this apps note is read in conjunction with the hardware manual for the device being programmed, as there can be subtle differences introduced.

# **0.18µm Programming**

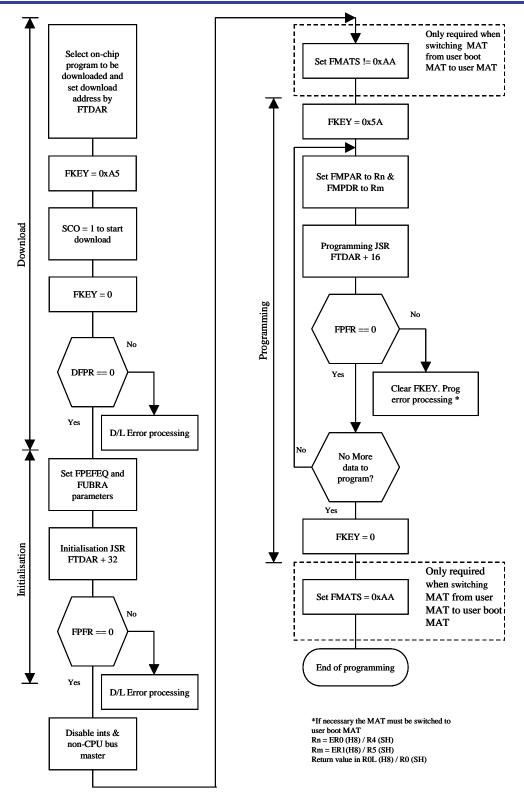

Figure 5 shows the typical programming algorithm for 0.18µm Renesas Flash microcontrollers.

Figure 5: 0.18µm Programming Algorithm

As previously mentioned the actual  $0.18\mu m$  programming routine is built into the device and is called from a user application. Using the built in programming routine consists of 3 steps – loading, initialisation and programming (execution).

### Loading

The loading process copies the built in programming routine into internal RAM for execution. The space used by the programming code is 2000 bytes for H8/300H and 2048 bytes for SH-2. The RAM used by the routine is configurable and set via the FTDAR register. Figure 6 shows the RAM map during the programming process.

| Low Address  | On-Chip RAM                                         | RAMTOP                            |

|--------------|-----------------------------------------------------|-----------------------------------|

|              | RAM emulation area or area that can be used by user |                                   |

|              | DPFR (return value: 1 byte)                         | FTDAR setting                     |

|              | System use area (15 bytes)                          |                                   |

|              |                                                     | FTDAR setting + 16                |

|              | Programming/Erasing entry                           |                                   |

|              | Initialisation process area                         | FTDAR setting + 32                |

|              | Initialisation & programming/erasing program        |                                   |

|              | Area that can be used by user                       | FTDAR setting + 2000(H8)/2048(SH) |

| High Address |                                                     | RAMEND                            |

Figure 6: RAM Map During Programming/Erasing

The first byte of this RAM space is given the label DPFR (download pass/fail result) and is used to indicate the result of the request to download the programming routine to the RAM. The download is executed by setting the routine to be downloaded in the FPCS (flash program code select) and FECS (flash erase code select) registers and then setting SCO (source program copy operation) bit in the FCCS (flash code control and status) register. Four NOPs should be executed after the setting of the SCO bit. When using the Renesas compiler the NOP instruction is inserted in the 'C' code as inline assembly code. With the Renesas compiler, the file containing the inline assembly code must have its output format set as 'assembly code' rather than the default 'machie code'. The DPFR byte should be initialised to H'FF prior to starting the download process.

The 0.18µm Flash memory offers software protection to prevent accidental programming etc. This protection is implemented using the FKEY register. When this register is set to '0' the protection is active. For downloading the FKEY value should be H'A5 and for programming it should be H'5A. FKEY should be left as zero for the initialisation operation.

The results of the loading request is given in the DPFR byte. The loading can fail due to incorrect FKEY value, trying to download the program and erase routines at the same time (multi-session) or an invalid setting in the FPCS and FECS registers.

### Initialisation

Once the correct routine has successfully been loaded into the internal RAM it must be initialised. The initialisation process configures the routines with the current CPU frequency and user branch address. The user branch option, which is supported by SH-2, allows user code to be called during programming and erasing. This is particularly useful for tickling a watchdog timer during erasing and programming. To use the user branch option the address of the routine should be loaded into the FUBRA (flash user branch address) register. The process of erasing a block or programming a flash line consists of many erase or programming pulses respectively; the user branch routine is called for each such pulse. As the erase and programming pulse lengths are not constant the time between two successive calls of the user branch routine will vary. The minimum and maximum values for this period are given in the Flash memory section of the relevant hardware manual. When the user branch feature is either not supported by the hardware or is not being used the FUBRA register should be set to zero.

The CPU frequency (FPEFEQ) and user branch address (FUBRA) parameters are passed to the programming routine via CPU registers. The actual registers used depend on the device family. For H8/300H, FPEFEQ should be in ER0 and for SH-2 it should be in R4. For the FUBRA value, the registers are ER1 for H8/300H and R5 for SH-2. The FPEFEQ value is the CPU frequency in MHz to 2 decimal places multiplied by 100. For example:

CPU frequency = 20.00MHz

$FPEFEQ = 20.00 \times 100 = 2000$

The FUBRA value is the 32-bit address of the user branch routine.

Although passing these parameters via CPU registers may seem initially inconvenient when programming in 'C', the registers used are those used by the Renesas C/C++ compiler for function parameter passing. Appendices F and G contain source code, in C, for implementing programming and erasing of the 0.18 $\mu$ m Flash memory of the H8/3069F (H8/300H) and SH-2e (SH7058F) respectively. This code contains the function 'func' with the prototype below.

void func (unsigned long ul1, unsigned long ul2);

Passing the FPEFEQ and FUBRA values to this function will result in the values being loaded into the correct CPU registers. With the values in the CPU registers the internal initialisation routine must be called. The start address for this routine is the address set by FTDAR + 32 bytes. In the example code this initialisation routine is called via a function pointer 'fp'. This function returns a byte (FPFR) in R0L (H8/300H) or R0 (SH-2e) containing the result of the initialisation request. A non-zero value indicates that the initialisation has failed. Failure can occur due to the CPU frequency or the user branch address being invalid.

The registers used for parameter passing have been chosen for compatibility with the Renesas C/C++ compiler toolchain. When using other compilers provision must be made to ensure that the correct values are loaded into the correct registers. The KPIT GNUH8 and KPIT GNUSH compilers can be configured to use the Renesas calling convention. If the IAR compiler is being used with H8 then some assembler code will be required.

### Programming

With the initialisation completed correctly the 128 byte Flash line can be programmed. If the code is running in user boot mode then, before and after the programming function call, the current MAT must be switched from the user boot MAT to the user MAT and back again. This is achieved by using the FMATS register. Four NOPs should be inserted after changing the FMATS register value.

When programming, the Flash address where programming should start (FMPAR) should be loaded into ER0 for H8/300H and for SH-2 it should be in R4. The address of the data to be programmed (FMPDR), usually in RAM, should be loaded into registers ER1 for H8/300H and R5 for SH-2. The internal programming routine is positioned at address FTDAR + 16. In the example routines programming is executed using the 'fp' function pointer. The return value (FPFR) of this function call contains the result of the programming request. A non-zero value indicates an error such as invalid FWE, invalid FKEY value, incorrect data source address or incorrect data destination address.

If more than one 128 byte Flash line is to be programmed it is not necessary for the programming routine to be downloaded and initialised more than once for each line. This is not implemented in the example source code for reasons of clarity but the download and initialisation functionality can easily be extracted into a subroutine.

The H8/300H 0.18µm makes available an additional feature over the SH-2. This feature is the ability to change the address of the NMI vector for situations where using the NMI interrupt cannot be avoided due to system requirements. The FVACR (Flash vector address control register) enables or disables this feature. When enabled the address of the NMI interrupt service routine should be placed in FVADR (Flash vector address register). This feature is not required by the SH-2 as the whole interrupt and exception vector table can be relocated and then accessed via the VBR (vector base register).

Appendices F and G contain source code, in C, for implementing programming the  $0.18\mu$ m Flash memory of the H8/3069F (H8/300H) and SH-2e (SH7058F) respectively. In both instances a 128 byte Flash line can be programmed by calling the function 'Program018FlashLine' which has the following definition.

unsigned short Program018FlashLine( unsigned long Address, unsigned char \*ProgData );

The first parameter passed is the start address of the Flash to be programmed which must be on a 128-byte boundary. The second parameter is a pointer to the data to be programmed into the Flash line. The return value is zero if the Flash line programming was completed successfully. A non-zero value indicates a failure. The error code format is described in the comments at the start of the function.

The source code is supplied in three files for each processor family – 'erase018.c', 'program018.c' and 'flash.h'. The C source files are the same for both H8/3069F and SH7058F. The header file though is different as it contains the specific addresses of the Flash registers and values specific to each device. If the code is to be executed in user boot mode then the definition 'INUSERBOOTMODE' must be defined in order for the MAT switching to be performed. The header files contain extensive comments so there should be no problem in modifying them for use with other 0.18µm based Renesas Flash microcontrollers.

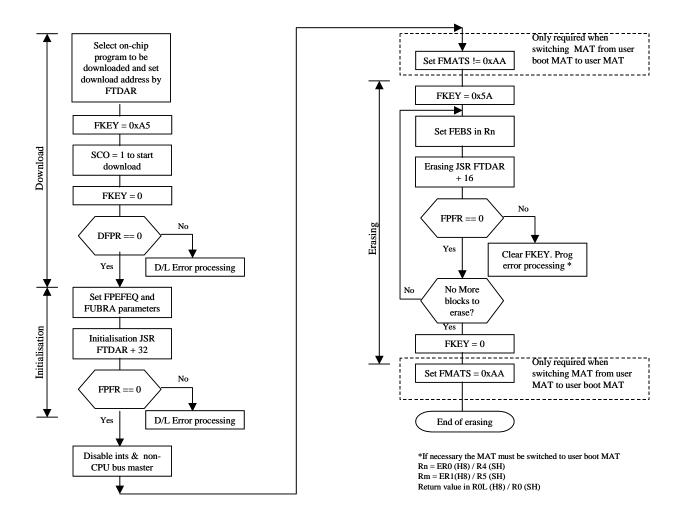

# 0.18µm Erasing

Figure 7 shows the typical erasing algorithm for 0.18µm Renesas Flash microcontrollers.

Figure 7: 0.18µm Erasing Algorithm

As previously mentioned the actual  $0.18\mu m$  erasing routine is built into the device and is called from a user application. Using the built in erasing routine consists of 3 steps – loading, initialisation and erasing (execution).

### Loading

The loading of the built in erasing routine into the internal RAM is the same as for the programming routine. The only change is that the erase program is selected in the FPCS and FECS registers. Figure 6 shows the RAM map during the erasing process.

### Initialisation

Once the correct routine has successfully been loaded into the internal RAM it must be initialised. The initialisation process for erasing is the same as for the programming routine previously described.

### Erasing

With the initialisation completed correctly a Flash block can be erased. If the code is running in user boot mode then, before and after the erasing function call, the current MAT must be switched from the user boot MAT to the user MAT and back again. This is achieved by using the FMATS register. Four NOPs should be inserted after changing the FMATS register value.

The number of the Flash block to be erased (FEBS) should be loaded into ER0 for H8/300H and for SH-2 it should be in R4 using the 'func' function. The internal erasing routine is located at address FTDAR + 16. In the example routines erasing is executed using the 'fp' function pointer. The return value (FPFR) of this function call contains the result of the erasing request. A non-zero value indicates an error such as invalid FWE, invalid FKEY value or invalid erase block.

If more than one erase block is to be erased it is not necessary for the erasing routine to be downloaded and initialised more than once for each block. This is not implemented in the example source code for reasons of clarity but the download and initialisation functionality can easily be extracted into a subroutine.

Again the H8/300H 0.18µm Flash memory NMI vector redirection feature is available during erasing. See the programming section for more details.

Appendices F and G contain source code, in C, for erasing the 0.18µm Flash memory of the H8/3069F (H8/300H) and SH-2e (SH7058F) respectively. In both instances a Flash block can be erased by calling the function 'Erase018FlashBlock' which has the following definition.

unsigned short Erase018FlashBlock( unsigned char FlashBlock )

The 'FlashBlock' parameter passed is Flash block to be erased which must be valid for the device. The return value is zero if the Flash block erase was completed successfully. A non-zero value indicates a failure. The error code format is described in the comments at the start of the function.

The source code is supplied in three files for each processor family – 'erase018.c', 'program018.c' and 'flash.h'. The C source files are the same for both H8/3069F and SH7058F. The header file though is different as it contains the specific addresses of the Flash registers and values specific to each device. If the code is to be executed in user boot mode then the definition 'INUSERBOOTMODE' must be defined in order for the MAT switching to be performed. The header files contains extensive comments so there should be no problem in modifying them for use with other 0.18µm based Renesas Flash microcontrollers.

## Summary

All Renesas micrcontrollers with Flash memory have the ability to easily self program and erase their memory.

It is hoped this application note has helped to demystify the process of programming and erasing the Flash memory of Renesas H8 and SH  $0.6\mu m$ ,  $0.35\mu m$  and  $0.18\mu m$  microcontrollers. The supplied code examples should provided a basis for implementing custom user mode programming routines giving greater flexibility to current and future applications. It is accepted that the code is not the most efficient in its current form but it is hoped that it is easy to follow. This leaves the user to optimise the code for speed and/or size once an understanding of its operation is established.

### APPENDIX A - RENESAS 0.6µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR H8S/2144F

```

// kernel.c

11

11

// Clock speed = 18.432MHz

// H8S2148 uses SCI1 for boot mode

// Kernel start address - 0xffe080

#include "iodefine.h"

// IO header file

// change following define depending on target

//#define SH

#define H8

#ifdef SH

typedef unsigned long read_datum; // unsigned long for SH

#define BLANK_VALUE 0xFFFFFFF

#else

typedef unsigned short read_datum; // unsigned short for H8S

#define BLANK_VALUE 0xFFFF

#endif

// to get round the problem of different 'iodefine.h' files using slightly

// different names for the flash registers and bits the following defines

// are used

FLASH.FLMCR1.BIT.SWE

#define FLASH_SWE

FLASH.FLMCR2.BIT.PSU

#define FLASH_PSU2

#define FLASH_PSU1 FLASH.FLMCR2.BIT.PSU

#define FLASH_P2 FLASH.FLMCR1.BIT.P

#define FLASH_P1

FLASH.FLMCR1.BIT.P

#define FLASH_PV2 FLASH.FLMCR1.BIT.PV

#define FLASH_PV1 FLASH.FLMCR1.BIT.PV

#define FLASH_EBR1 FLASH.EBR1.BYTE

#define FLASH_EBR2

FLASH.EBR2.BYTE

#define FLASH_EB0 FLASH.EBR2.BIT.EB0

#define FLASH_EB1 FLASH.EBR2.BIT.EB1

#define FLASH_EB2 FLASH.EBR2.BIT.EB2

#define FLASH_EB3 FLASH.EBR2.BIT.EB3

#define FLASH_EB4 FLASH.EBR2.BIT.EB4

#define FLASH_EB5 FLASH.EBR2.BIT.EB5

#define FLASH_EB6

FLASH.EBR2.BIT.EB6

#define FLASH_EB7

FLASH.EBR2.BIT.EB7

#define FLASH_EB8 FLASH.EBR1.BIT.EB8

#define FLASH_EB9 FLASH.EBR1.BIT.EB9

#define FLASH_EB10 FLASH.EBR1.BIT.EB9

#define FLASH_EB11 FLASH.EBR1.BIT.EB9

#define FLASH_ESU2 FLASH.FLMCR2.BIT.ESU

#define FLASH_ESU1

FLASH.FLMCR2.BIT.ESU

#define FLASH_E2

FLASH.FLMCR1.BIT.E

#define FLASH_E1

FLASH.FLMCR1.BIT.E

#define FLASH_EV2 FLASH.FLMCR1.BIT.EV

#define FLASH_EV1 FLASH.FLMCR1.BIT.EV

```

// H8S2148 specific #define MAX\_FLASH\_ADDR 0x20000 #define FLASH\_LINE\_SIZE 32 #define NO\_OF\_FLASH\_BLOCKS 10 #define XTAL 18432000L #define MAX\_PROG\_COUNT 1000 #define MAX\_ERASE\_ATTEMPTS 120 #define MAX\_FLMCR1\_ADDRESS 0x1FFFFL // array below should contain the start addresses of the flash memory blocks // final array element should contain the end address of the flash memory (+1) const unsigned long eb\_block\_addr [NO\_OF\_FLASH\_BLOCKS + 1] = { 0x0000000L, 0x00000400L, 0x00000800L, 0x00000C00L, 0x00001000L, 0x00008000L, 0x0000C000L, 0x0000E000L, 0x00010000L, 0x00018000L, 0x00020000L /\* max flash address + 1 \*/ }; #define BLANK 1 #define NOT\_BLANK 2 #define PROG\_PASS 0x01 #define PROG\_FAIL 0x02 #define ERASE\_PASS 0x01 #define ERASE\_FAIL  $0 \times 02$ // delay values // note this is xtal frequency specific #define TWO\_USEC ((2L \* XTAL) / 800000L) #define FOUR\_USEC ((4L \* XTAL) / 800000L) #define FIVE\_USEC ((5L \* XTAL) / 8000000L) #define TEN\_USEC ((1L \* XTAL) / 800000L) ((2L \* XTAL) / 800000L) #define TWENTY\_USEC ((5L \* XTAL) / 800000L) #define FIFTY\_USEC #define TWO\_HUNDRED\_USEC ((2L \* XTAL) / 80000L) #define FIVE\_MSEC ((5L \* XTAL) / 8000L) union char\_rd\_datum\_union { unsigned char c[FLASH\_LINE\_SIZE]; read\_datum u[FLASH\_LINE\_SIZE / sizeof (read\_datum)]; } prog\_data; // function prototypes unsigned char prog\_flash\_line\_32 (unsigned long t\_address, union char\_rd\_datum\_union \*p\_data); void delay (unsigned short); void init\_delay\_timer (void); unsigned char erase\_block\_06\_um (unsigned char block\_num); // variables volatile unsigned long delay\_counter;

# RENESAS

```

// Functions

unsigned char prog_flash_line_32 (unsigned long t_address, union char_rd_datum_union *p_data)

{

unsigned short n_prog_count; // loop counter for programming attempts (0->MAX_PROG_COUNT)

unsigned short d;

// general variable used for various loop counts

unsigned char m;

// flag to indicate if re-programming required 1=yes 0=no

unsigned char *dest_address; // pointer used for writing to the flash

unsigned char *uc_v_write_address;

// pointer used for writing to the addr to be verified

read_datum *ul_v_read_address; // pointer used to read address being verified

unsigned char ax;

// variable used as loop counter for incrementing the

// pointer to the byte being wriiten next

in verify process

union char_rd_datum_union reprog_data; // storage (on stack) for the re-program data

// enable flash writes

FLASH_SWE = 1;

// wait 10us

delay (TEN_USEC);

// copy data from program data area to reprogram data area

for (d=0; d<FLASH_LINE_SIZE; d++)</pre>

{

reprog_data.c[d] = p_data->c[d];

}

// program the data in FLASH_LINE_SIZE byte chunks

for (n_prog_count=0; n_prog_count<MAX_PROG_COUNT; n_prog_count++)</pre>

{

// clear reprogram required flag

m = 0;

// copy data from reprogram data area into the flash

dest_address = (unsigned char *) t_address;

for (d=0; d<FLASH_LINE_SIZE; d++)</pre>

{

*dest_address++ = reprog_data.c[d];

}

// enter program setup

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PSU2 = 1;

}

else

{

// FLMCR1

FLASH_PSU1 = 1;

}

// wait 50us

delay (FIFTY_USEC);

// start programming pulse

if ( t_address > MAX_FLMCR1_ADDRESS )

{

```

```

// FLMCR2

```

```

FLASH_P2 = 1;

}

else

{

// FLMCR1

FLASH_P1 = 1;

}

// wait 200us

delay (TWO_HUNDRED_USEC);

// stop programming pulse

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_P2 = 0;

}

else

{

// FLMCR1

FLASH_P1 = 0;

}

// wait 20us

delay (TEN_USEC);

// leave programming setup

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PSU2 = 0;

}

else

{

// FLMCR1

FLASH_PSU1 = 0;

}

// wait 10us

delay (TEN_USEC);

// enter program verify mode

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PV2 = 1;

}

else

{

// FLMCR1

FLASH_PV1 = 1;

}

// wait 4us

delay (FOUR_USEC);

// verify the data via read_datum size reads

uc_v_write_address = (unsigned char *) t_address;

```

NESAS

```

ul_v_read_address = (read_datum *) t_address;

// verify loop

for (d=0; d<(FLASH_LINE_SIZE / sizeof(read_datum)); d++)</pre>

{

// dummy write of H'FF to verify address

*uc_v_write_address = 0xff;

// increment this address by sizeof(read_datum) to get to next verify address

for(ax=0; ax<sizeof(read_datum); ax++)</pre>

{

uc_v_write_address++;

}

// wait 2us

delay (TWO_USEC);

// read verify data

// check with the original data

if (*ul_v_read_address != p_data->u[d])

{

// 1 or more bits failed to program

11

// set the reprogram required flag

m = 1;

}

// calculate reprog data

reprog_data.u[d] = p_data->u[d] | ~(p_data->u[d] | *ul_v_read_address);

// increment the pointers

ul_v_read_address++;

} // end of verify loop

// exit program verify mode

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PV2 = 0;

}

else

{

// FLMCR1

FLASH_PV1 = 0;

}

// wait 4us

delay (FOUR_USEC);

// check if flash line has successfully been programmed

if (m == 0)

{

// program verified ok

11

// disable flash writes

FLASH_SWE = 0;

// end of successful programming

```

```

return (PROG_PASS);

}

}

// end of MAX_PROG_COUNT attempts to program

// failed to program after MAX_PROG_COUNT attempts

// disable flash writes

FLASH_SWE = 0;

// end of failed programming

return (PROG_FAIL);

}

unsigned char erase_block_06_um (unsigned char block_num)

{

unsigned char erase;

// flag showing erase status - either BLANK or NOT_BLANK

unsigned long attempts;

// counter for erase attempts (0->MAX_ERASE_ATTEMPTS)

read_datum *ul_v_read;

// pointer for reading erase/verify data

unsigned char *uc_v_write; // pointer for writing erase/verify dummy byte

unsigned char inc_uc_v_write_count; // loop counter for incrementing the uc_v_write variable

// check that block is not already erased

erase = BLANK;

for (attempts=eb_block_addr[block_num]; attempts<eb_block_addr[block_num + 1]; attempts++)</pre>

{

if ( *(unsigned char *) attempts != 0xff)

erase = NOT_BLANK;

}

if (erase == BLANK)

return ERASE_PASS;

else

{

// block needs erasing

11

// enable flash writes

FLASH_SWE = 1;

// wait 10us

delay (TEN_USEC);

// set the correct EB bit in correct EBR register

FLASH_EBR1 = 0;

FLASH\_EBR2 = 0;

switch (block_num)

{

case 0:

FLASH_EB0 = 1;

break;

case 1:

FLASH_EB1 = 1;

break;

case 2:

FLASH_EB2 = 1;

break;

```

### H8 Family, H8S Family, SuperH RISC Engine Family Flash Memory Programming Routines

```

case 3:

FLASH\_EB3 = 1;

break;

case 4:

FLASH\_EB4 = 1;

// note the change to EBR2 here!

break;

case 5:

FLASH\_EB5 = 1;

break;

case 6:

FLASH\_EB6 = 1;

break;

case 7:

FLASH\_EB7 = 1;

break;

case 8:

FLASH\_EB8 = 1;

break;

case 9:

FLASH\_EB9 = 1;

break;

case 10:

FLASH\_EB10 = 1;

break;

case 11:

FLASH\_EB11 = 1;

break;

// initialise the attempts counter

// 0 as we check for less than MAX (not <= MAX)</pre>

attempts = 0;

erase = NOT_BLANK;

while ( (attempts < MAX_ERASE_ATTEMPTS) && (erase == NOT_BLANK) )</pre>

// increment the attempts counter

attempts++;

// enter erase setup mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_ESU2 = 1;

}

else

{

// FLMCR1

FLASH_ESU1 = 1;

}

```

}

```

// wait 200us

delay (TWO_HUNDRED_USEC);

// transition to erase mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_E2 = 1;

}

else

{

// FLMCR1

FLASH_E1 = 1;

}

// wait 5ms

delay (FIVE_MSEC);

// exit erase mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_E2 = 0;

}

else

{

// FLMCR1

FLASH_E1 = 0;

}

// wait 10us

delay (TEN_USEC);

// exit erase setup mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH\_ESU2 = 0;

}

else

{

// FLMCR1

FLASH_ESU1 = 0;

}

// wait 10 us

delay (TEN_USEC);

// enter erase/verify mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_EV2 = 1;

}

else

{

// FLMCR1

FLASH_EV1 = 1;

```

```

// wait 20 us

delay (TWENTY_USEC);

// verify flash has been erased

\ensuremath{\prime\prime}\xspace and the addresses in the current erase block and check that they are

// successfully erased

// exit this loop if a non-erased address is detected

ul_v_read = (read_datum *) eb_block_addr [block_num];

uc_v_write = (unsigned char *) eb_block_addr [block_num];

erase = BLANK;

while ( (erase == BLANK) && ( ul_v_read < (read_datum *) eb_block_addr

[block_num + 1] ) )

{

// dummy write

*uc_v_write = 0xff;

// wait 2 us

delay (TWO_USEC);

if (*ul_v_read != BLANK_VALUE)

{

// this address is not erased yet

erase = NOT_BLANK;

}

else

{

// advance to next verify write address

for

(inc_uc_v_write_count=0;

inc_uc_v_write_count<sizeof(read_datum); inc_uc_v_write_count++)</pre>

{

uc_v_write++;

}

// advance to next verify read address

ul_v_read++;

}

}

// exit erase/verify mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_EV2 = 0;

}

else

{

// FLMCR1

FLASH_EV1 = 0;

}

// wait 5 us

delay (FIVE_USEC);

}

// end of outer while loop

// end either of erase attempts or block has been erased ok

11

```

```

// disable flash writes

FLASH_SWE = 0;

// check if block has been erased ok

if (erase == BLANK)

{

// successfully erased

return ERASE_PASS;

}

else

{

// failed to erase this block

return ERASE_FAIL;

}

}

}

void init_delay_timer (void)

{

MSTPCR.BIT.B13 = 0;

// FRT enabled in Module Stop Register

FRT.TOCR.BIT.OCRS = 0;

// Access to OCRA

FRT.OCRA = 0;

FRT.TOCR.BIT.OCRS = 1;

// Access to OCRB

FRT.OCRB = 0;

FRT.TOCR.BIT.ICRS = 0;

// Access to ICRA, ICRB & ICRC enabled

FRT.ICRA = 0;

FRT.ICRB = 0;

FRT.ICRC = 0;

FRT.ICRD = 0;

FRT.TOCR.BIT.ICRS = 1;

// Access to OCRAR, OCRAF & OCRDM enabled

FRT.OCRAR = 0;

FRT.OCRAF = 0;

FRT.OCRDM = 0;

FRT.TIER.BYTE = 0;

// Disable all FRT interrupts

FRT.TCSR.BIT.CCLRA = 1;

// 0 = Timer NOT cleared by compare-match A

// 1 = Timer IS cleared by compare-match A

FRT.TCR.BIT.IEDGA = 0;

// Capture on falling edge

FRT.TCR.BIT.IEDGB = 0;

// Capture on falling edge

FRT.TCR.BIT.IEDGC = 0;

// Capture on falling edge

FRT.TCR.BIT.IEDGD = 0;

// Capture on falling edge

FRT.TCR.BIT.BUFEA = 0;

// ICRC not used as buffer for I/C A \,

FRT.TCR.BIT.BUFEB = 0;

// ICRC not used as buffer for I/C B

// Clock source: CKS1 = 0 CKS0 = 1 ( clk / 8 )

FRT.TCR.BIT.CKS = 1;

FRT.TOCR.BIT.ICRDMS = 0;

FRT.TOCR.BIT.OCRAMS = 0;

FRT.TOCR.BIT.OEA = 0;

FRT.TOCR.BIT.OEB = 0;

FRT.TOCR.BIT.OLVLA = 0;

FRT.TOCR.BIT.OLVLB = 0;

}

```

NESA

void delay (unsigned short d)

```

{

FRT.TOCR.BIT.OCRS = 0; // Access to OCRA

FRT.OCRA = d; // set compare value

FRT.FRC = 0; // clear TCNT to 0

FRT.TCSR.BIT.OCFA = 0; // Clear flag

while(FRT.TCSR.BIT.OCFA == 0); // wait until compare value is met

}

```

```

void main (void)

{

}

```

### APPENDIX B – RENESAS 0.6µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR SH7045F

// kernel.c 11 // Programming kernel for SH7045F 11 // Clock speed = 29.488MHz #include "iodefine.h" // IO header file // change following define depending on target #define SH //#define H8 #ifdef SH typedef unsigned long read\_datum; // unsigned long for SH #define BLANK\_VALUE 0xffffffff #else typedef unsigned short read\_datum; // unsigned short for H8S #define BLANK VALUE 0xFFFF #endif // to get round the problem of different 'iodefine.h' files using slightly // different names for the flash registers and bits the following defines // are used #define FLASH SWE FLASH.FLMCR1.BIT.SWE #defineFLASH\_PSU2 FLASH, FLMCR2, BIT, PSU2 #defineFLASH\_PSU1 FLASH.FLMCR1.BIT.PSU1 #define FLASH\_P2 FLASH.FLMCR2.BIT.P2 #define FLASH\_P1 FLASH.FLMCR1.BIT.P1 #define FLASH\_PV2 FLASH.FLMCR2.BIT.PV2 #define FLASH\_PV1 FLASH.FLMCR1.BIT.PV1 #define FLASH\_EB0 FLASH.EBR1.BIT.EB0 #define FLASH\_EB1 FLASH.EBR1.BIT.EB1 #define FLASH\_EB2 FLASH.EBR1.BIT.EB2 #define FLASH\_EB3 FLASH.EBR1.BIT.EB3 #define FLASH\_EB4 FLASH, EBR2, BTT, EB4 #define FLASH\_EB5 FLASH.EBR2.BIT.EB5 #define FLASH\_EB6 FLASH.EBR2.BIT.EB6 #define FLASH\_EB7 FLASH.EBR2.BIT.EB7 #define FLASH\_EB8 FLASH.EBR2.BIT.EB8 #define FLASH\_EB9 FLASH.EBR2.BIT.EB9 #define FLASH\_EB10 FLASH.EBR2.BIT.EB10 #define FLASH\_EB11 FLASH.EBR2.BIT.EB11 #define FLASH\_ESU2 FLASH.FLMCR2.BIT.ESU2 #define FLASH\_ESU1 FLASH.FLMCR1.BIT.ESU1 #define FLASH\_E2 FLASH.FLMCR2.BIT.E2 #define FLASH\_E1 FLASH FLMCR1 BTT E1 #define FLASH\_EV2 FLASH.FLMCR2.BIT.EV2 #define FLASH\_EV1 FLASH.FLMCR1.BIT.EV1 #define FLASH\_EBR1 FLASH.EBR1.BYTE #define FLASH\_EBR2 FLASH.EBR2.BYTE

// SH704/5F specific

#define MAX\_FLASH\_ADDR 0x40000 #define FLASH\_LINE\_SIZE 32 #define NO\_OF\_FLASH\_BLOCKS 12 #define XTAL 29488000L #define MAX\_PROG\_COUNT 1000 #define MAX\_ERASE\_ATTEMPTS 60 0x1FFFFL #define MAX\_FLMCR1\_ADDRESS // array below should contain the start addresses of the flash memory blocks // final array element should contain the end address of the flash memory (+1) const unsigned long eb\_block\_addr [NO\_OF\_FLASH\_BLOCKS + 1] = { 0x0000000L. 0x00008000L, 0x00010000L, 0x00018000T 0x00020000L, 0x00028000L, 0x00030000L, 0x00038000L, 0x0003F000L, 0x0003F400L, 0x0003F800L, 0x0003FC00L, 0x00040000L /\* max flash address + 1 \*/ }; #define BLANK 1 #define NOT\_BLANK 2 #define PROG\_PASS  $0 \times 01$ #define PROG\_FAIL 0x02 0x01 #define ERASE\_PASS 0x02 #define ERASE\_FAIL // delay values // note this is xtal frequency specific // these values are for the SH7045F CMT with a system clock divider of 8  $\,$ #define TWO\_USEC ((2L \* XTAL) / 800000L) #define FOUR\_USEC ((4L \* XTAL) / 800000L) #define FIVE\_USEC ((5L \* XTAL) / 800000L) #define TEN\_USEC ((1L \* XTAL) / 800000L) #define TWENTY\_USEC ((2L \* XTAL) / 800000L) #define FIFTY\_USEC ((5L \* XTAL) / 800000L) ((2L \* XTAL) / 80000L) #define TWO\_HUNDRED\_USEC #define FIVE\_MSEC ((5L \* XTAL) / 8000L) // function prototypes void main (void); unsigned char prog\_flash\_line\_32 (unsigned long t\_address, union char\_rd\_datum\_union \*p\_data); void delay (unsigned short); void init\_delay\_timer (void); unsigned char erase\_block\_06\_um (unsigned char block\_num); union char\_rd\_datum\_union { unsigned char c[FLASH\_LINE\_SIZE]; read\_datum u[FLASH\_LINE\_SIZE / sizeof (read\_datum)]; } prog\_data;

```

// variables

volatile unsigned long delay_counter;

// Functions

unsigned char prog_flash_line_32 (unsigned long t_address, union char_rd_datum_union *p_data)

{

unsigned short n_prog_count; // loop counter for programming attempts (0->MAX_PROG_COUNT)

unsigned short d;

// general variable used for various loop counts

// flag to indicate if re-programming required 1=yes 0=no

unsigned char m;

unsigned char *dest_address; // pointer used for writing to the flash

unsigned char *uc_v_write_address; // pointer used for writing to the addr to be verified

read_datum *ul_v_read_address; // pointer used to read address being verified

unsigned char ax;

// variable used as loop counter for incrementing the

// pointer to the byte being wriiten next

in verify process

union char_rd_datum_union reprog_data; // storage (on stack) for the re-program data

// enable flash writes

FLASH_SWE = 1;

// wait 10us

delay (TEN_USEC);

// copy data from program data area to reprogram data area

for (d=0; d<FLASH_LINE_SIZE; d++)</pre>

{

reprog_data.c[d] = p_data->c[d];

}

// program the data in FLASH_LINE_SIZE byte chunks

for (n_prog_count=0; n_prog_count<MAX_PROG_COUNT; n_prog_count++)</pre>

{

// clear reprogram required flag

m = 0;

// copy data from reprogram data area into the flash

dest_address = (unsigned char *) t_address;

for (d=0; d<FLASH_LINE_SIZE; d++)</pre>

{

*dest_address++ = reprog_data.c[d];

}

// enter program setup

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PSU2 = 1;

}

else

{

// FLMCR1

FLASH_PSU1 = 1;

}

// wait 50us

delay (FIFTY_USEC);

// start programming pulse

```

```

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_P2 = 1;

}

else

{

// FLMCR1

FLASH_P1 = 1;

}

// wait 200us

delay (TWO_HUNDRED_USEC);

// stop programming pulse

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_P2 = 0;

}

else

{

// FLMCR1

FLASH_P1 = 0;

}

// wait 20us

delay (TEN_USEC);

// leave programming setup

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PSU2 = 0;

}

else

{

// FLMCR1

FLASH_PSU1 = 0;

}

// wait 10us

delay (TEN_USEC);

// enter program verify mode

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PV2 = 1;

}

else

{

// FLMCR1

FLASH_PV1 = 1;

}

// wait 4us

delay (FOUR_USEC);

```

5

ENES

```

// verify the data via read_datum size reads

uc_v_write_address = (unsigned char *) t_address;

ul_v_read_address = (read_datum *) t_address;

// verify loop

for (d=0; d<(FLASH_LINE_SIZE / sizeof(read_datum)); d++)</pre>

{

// dummy write of H'FF to verify address

*uc_v_write_address = 0xff;

// increment this address by sizeof(read_datum) to get to next verify address

for(ax=0; ax<sizeof(read_datum); ax++)</pre>

{

uc_v_write_address++;

}

// wait 2us

delay (TWO_USEC);

// read verify data

// check with the original data

if (*ul_v_read_address != p_data->u[d])

{

// 1 or more bits failed to program

//

// set the reprogram required flag

m = 1;

}

// calculate reprog data

reprog_data.u[d] = p_data->u[d] | ~(p_data->u[d] | *ul_v_read_address);

// increment the pointers

ul_v_read_address++;

} // end of verify loop

// exit program verify mode

if ( t_address > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_PV2 = 0;

}

else

{

// FLMCR1

FLASH_PV1 = 0;

}

// wait 4us

delay (FOUR_USEC);

// check if flash line has successfully been programmed

if (m == 0)

{

// program verified ok

11

// disable flash writes

```

**NESAS**

```

FLASH_SWE = 0;

// end of successful programming

return (PROG_PASS);

}

// end of MAX_PROG_COUNT attempts to program

}

// failed to program after MAX_PROG_COUNT attempts

// disable flash writes

FLASH_SWE = 0;

// end of failed programming

return (PROG_FAIL);

}

unsigned char erase_block_06_um (unsigned char block_num)

{

unsigned char erase;

// flag showing erase status - either BLANK or NOT_BLANK

unsigned long attempts;

// counter for erase attempts (0->MAX_ERASE_ATTEMPTS)

read_datum *ul_v_read;

// pointer for reading erase/verify data

unsigned char *uc_v_write; \ // pointer for writing erase/verify dummy byte

unsigned char inc_uc_v_write_count; // loop counter for incrementing the uc_v_write variable

// check that block is not already erased

erase = BLANK;

for (attempts=eb_block_addr[block_num]; attempts<eb_block_addr[block_num + 1]; attempts++)</pre>

{

if ( *(unsigned char *) attempts != 0xff)

erase = NOT_BLANK;

}

if (erase == BLANK)

return ERASE_PASS;

else

{

// block needs erasing

11

// enable flash writes

FLASH_SWE = 1;

// wait 10us

delay (TEN_USEC);

// set the correct EB bit in correct EBR register

FLASH\_EBR1 = 0;

FLASH\_EBR2 = 0;

switch (block_num)

{

case 0:

FLASH_EB0 = 1;

break;

case 1:

FLASH_EB1 = 1;

break;

case 2:

```

```

FLASH\_EB2 = 1;

break;

case 3:

FLASH\_EB3 = 1;

break;

case 4:

// note the change to EBR2 here!

FLASH\_EB4 = 1;

break;

case 5:

FLASH\_EB5 = 1;

break;

case 6:

FLASH\_EB6 = 1;

break;

case 7:

FLASH\_EB7 = 1;

break;

case 8:

FLASH\_EB8 = 1;

break;

case 9:

FLASH_EB9 = 1;

break;

case 10:

FLASH\_EB10 = 1;

break;

case 11:

FLASH\_EB11 = 1;

break;

// initialise the attempts counter

// 0 as we check for less than MAX (not <= MAX)</pre>

attempts = 0;

erase = NOT_BLANK;

while ( (attempts < MAX_ERASE_ATTEMPTS) && (erase == NOT_BLANK) )

// increment the attempts counter

attempts++;

// enter erase setup mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_ESU2 = 1;

}

else

{

// FLMCR1

```

```

FLASH_ESU1 = 1;

}

// wait 200us

delay (TWO_HUNDRED_USEC);

// transition to erase mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_E2 = 1;

}

else

{

// FLMCR1

FLASH_E1 = 1;

}

// wait 5ms

delay (FIVE_MSEC);

// exit erase mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_E2 = 0;

}

else

{

// FLMCR1

FLASH_E1 = 0;

}

// wait 10us

delay (TEN_USEC);

// exit erase setup mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH\_ESU2 = 0;

}

else

{

// FLMCR1

FLASH_ESU1 = 0;

}

// wait 10 us

delay (TEN_USEC);

// enter erase/verify mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_EV2 = 1;

}

else

```

ENESAS

```

{

// FLMCR1

FLASH_EV1 = 1;

}

// wait 20 us

delay (TWENTY_USEC);

// verify flash has been erased

// read all the addresses in the current erase block and check that they are

// successfully erased

// exit this loop if a non-erased address is detected

ul_v_read = (read_datum *) eb_block_addr [block_num];

uc_v_write = (unsigned char *) eb_block_addr [block_num];

erase = BLANK;

while ( (erase == BLANK) && ( ul_v_read < (read_datum *) eb_block_addr

[block_num + 1] ) )

{

// dummy write

*uc_v_write = 0xff;

// wait 2 us

delay (TWO_USEC);

if (*ul_v_read != BLANK_VALUE)

{

// this address is not erased yet

erase = NOT_BLANK;

}

else

{

// advance to next verify write address

for

(inc_uc_v_write_count=0;

inc_uc_v_write_count<sizeof(read_datum); inc_uc_v_write_count++)</pre>

{

uc_v_write++;

}

// advance to next verify read address

ul_v_read++;

}

}

// exit erase/verify mode

if ( eb_block_addr [block_num] > MAX_FLMCR1_ADDRESS )

{

// FLMCR2

FLASH_EV2 = 0;

}

else

{

// FLMCR1

FLASH_EV1 = 0;

}

// wait 5 us

delay (FIVE_USEC);

}

// end of outer while loop

```

```

// end either of erase attempts or block has been erased ok

11

// disable flash writes

FLASH_SWE = 0;

// check if block has been erased ok

if (erase == BLANK)

{

// successfully erased

return ERASE_PASS;

}

else

{

// failed to erase this block

return ERASE_FAIL;

}

}

}

void init_delay_timer (void)

{

// initialises compare match timer (CMT) channel 0

// enable in module stop register

//MST.MSTCR2.BIT.MSTP12 = 0;

// stop channel 0

CMT.CMSTR.BIT.STR0 = 0;

// channel 0 compare match interrupt disabled

CMT0.CMCSR.BIT.CMIE = 0;

// system clock / 8

CMT0.CMCSR.BIT.CKS = 0;

// start timer

CMT.CMSTR.BIT.STR0 = 1;

}

void delay (unsigned short d)

{

// load compare match value into the constant register

CMT0.CMCOR = di

// clear counter

CMTO.CMCNT = 0;

// clear compare match flag

CMT0.CMCSR.BIT.CMF = 0;

// loop until we have a compare match

while (CMT0.CMCSR.BIT.CMF == 0);

}

void main (void)

{

}

```

NESAS

## APPENDIX C - RENESAS 0.35µM FLASH PROGRAM/PROGRAM VERIFY & ERASE/ERASE VERIFY ROUTINES FOR H8S/2612F

```

// kernel.c

11

//

// Clock speed = 18.432 MHz

// SH7047F WS uses SCI2 for boot mode

// Kernel start address - 0xffe800

#include "iodefine.h"

// IO header file

// change following define depending on target

//#define SH

#define H8

#ifdef SH

typedef unsigned long read_datum; // unsigned long for SH

#define BLANK_VALUE

0xffffffff

#else

typedef unsigned short read_datum; // unsigned short for H8S

#define BLANK_VALUE

0xFFFF

#endif

// H8S2612F WS specific

#define FLASH_SWE FLASH.FLMCR1.BIT.SWE

#define FLASH PSU FLASH.FLMCR1.BIT.PSU

#define FLASH_P

FLASH.FLMCR1.BIT.P

#define FLASH_PV

FLASH.FLMCR1.BIT.PV

#define FLASH_EBR1 FLASH.EBR1.BYTE

#define FLASH_EBR2 FLASH.EBR2.BYTE

#define FLASH_EB0 FLASH.EBR1.BIT.EB0

#define FLASH_EB1 FLASH.EBR1.BIT.EB1

#define FLASH_EB2 FLASH.EBR1.BIT.EB2

#define FLASH_EB3 FLASH.EBR1.BIT.EB3

FLASH.EBR1.BIT.EB4

#define FLASH_EB4

#define FLASH_EB5

FLASH.EBR1.BIT.EB5

#define FLASH_EB6 FLASH.EBR1.BIT.EB6

#define FLASH_EB7 FLASH.EBR1.BIT.EB7

#define FLASH_EB8 FLASH.EBR2.BIT.EB8

#define FLASH_EB9 FLASH.EBR2.BIT.EB9

#define FLASH_EB10 FLASH.EBR2.BIT.EB9

#define FLASH_EB11 FLASH.EBR2.BIT.EB9

#define FLASH_ESU FLASH.FLMCR1.BIT.ESU

#define FLASH_E

FLASH.FLMCR1.BIT.E

#define FLASH_EV FLASH.FLMCR1.BIT.EV

#define MAX_FLASH_ADDR

0 \times 20000

#define FLASH_LINE_SIZE

128

#define NO_OF_FLASH_BLOCKS

10

18432000L

#define XTAL

#define MAX_PROG_COUNT

1000

#define MAX_ERASE_ATTEMPTS

120

// array below should contain the start addresses of the flash memory blocks

// final array element should contain the end address of the flash memory (+1)

```