RENESAS

Digital-DC<sup>™</sup> Control Loop Compensation

## Overview

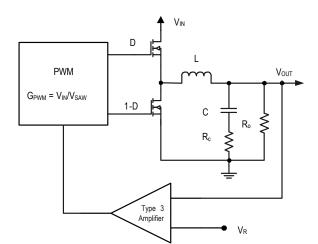

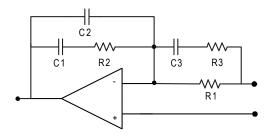

All power supplies require some type of feedback loop to regulate the output voltage. A simplified diagram of a buck controller is shown in Figure 1 with a pulse width modulator (PWM) and an error amplifier / compensator.

For this feedback loop to be stable, negative feedback is used. This means that the output voltage  $(V_{OUT})$  is compared to the reference voltage  $(V_R)$  and the difference  $(V_R - V_{OUT})$  is amplified by the error amplifier. The output of the error amplifier is called the error voltage. The error voltage polarity is inverted with respect to  $V_{OUT}$  and is therefore  $-180^{\circ}$  out of phase with  $V_{OUT}$ . The goal of the feedback loop is to minimize the error between  $V_{OUT}$  and  $V_R$ . The error is small when the overall feedback loop gain is high. Ideally, a feedback loop would have infinite gain for all frequencies, thus providing perfect regulation regardless of the demands of the load.

Figure 1. Simplified Buck Controller

AN2016 Rev. 0.00 May 1, 2009

Practical limitations such as the sampled nature of the switching power supply, finite gain and bandwidth of real components, and time delays in the control loop limit the possible gain and bandwidth of the feedback loop. In practical terms, the goal of power supply loop compensation is to have as high a gain as possible at DC and reduce this gain to less than 1 (0dB) before the phase shift in the control loop reaches  $360^{\circ}$ . Recall that the error amplifier introduces  $-180^{\circ}$  of phase shift. The output stage used in the buck converter is an LC filter. There are several characteristics of this filter that impact its frequency response. Primarily, the LC filter has  $-180^{\circ}$  of phase shift and has an attenuation of 40dB per decade above its natural frequency ( $f_n$ ). The natural frequency of the LC filter is approximated by:

$$f_n = \frac{1}{2\pi\sqrt{LC}}$$

Eq. [1]

Also, the components in the LC filter are not ideal because they contain parasitic impedances. In many capacitors used in output filters, the Equivalent Series Resistance (ESR, shown as  $R_C$  in Figure 1) is large enough to alter the response of the LC filter at frequencies that impact the control loop design. This is called the ESR zero ( $f_{zesr}$ ). It has the effect of changing the LC filter's attenuation slope from -40dB (-2 slope) per decade to -20dB (-1 slope) per decade and adding 90° of phase back into the feedback loop. The ESR zero of the output capacitor is calculated using Eq. [2]:

$$f_{zesr} = \frac{1}{2\pi CR_c} \qquad \qquad \mathbf{Eq. [2]}$$

# **Closing the Control Loop**

Frequency compensation is used to achieve the goal of less than  $360^{\circ}$  of phase shift when the open-loop gain is above 0dB. In the circuit of Figure 1, compensation is provided by the type 3 amplifier. The easiest method of compensating control loops using Digital-DC Technology is by using compensation pin-strap settings listed in the datasheet for each device. Zilker Labs, Inc. also offers user-friendly tools for calculating compensation coefficients using regulator design constraints and filter component parameters.

LC filters exhibit resonant behavior. Near the natural frequency  $(f_n)$ , the LC filter transfer function will effectively amplify the input signal. The extent to which this occurs is determined by the quality factor (Q). In effect, the Q of the circuit is a measure of the gain the LC filter exhibits at  $f_n$  and how abrupt the phase shift from 0 to  $-180^{\circ}$  will be. In power supply applications, it is also indirectly a measure of the circuit's efficiency: the lower the resistances in the circuit, the higher the Q. However, a high Q also corresponds to an abrupt phase shift from 0 to  $-180^{\circ}$ .

For a simplified power stage and output filter consisting of high-side MOSFET on-resistance  $R_{ON-H}$ , low-side MOSFET on-resistance  $R_{ON-L}$ , output inductor L having resistance  $R_L$ , an output capacitance array of n parallel capacitors having capacitance C and equivalent series resistance  $R_C$  and for a load resistance  $R_O$ , the natural frequency and quality factor of the circuit are given by Equations [3] and [4], respectively.

$$f_{n} = \frac{1}{2\pi \sqrt{nC\left(\frac{R_{c}}{n} + R_{o}\right)\left(\frac{L}{R_{e} + R_{o}}\right)}}$$

or

$$f_{n} = \frac{1}{2\pi \sqrt{LC\frac{R_{c} + nR_{o}}{R_{e} + R_{o}}}}$$

Eq. [3]

$$Q = \frac{\sqrt{nC\left(\frac{R_{c}}{n} + R_{o}\right)\left(\frac{L}{R_{e} + R_{o}}\right)}}{\frac{L}{R_{e} + R_{o}} + nC\left(\frac{R_{c}}{n} + \frac{R_{e}R_{o}}{R_{e} + R_{o}}\right)}$$

or Eq. [4]

$$Q = \frac{\sqrt{LC(R_c + nR_o)(R_e + R_o)}}{L + C(R_c(R_e + R_o) + nR_eR_o)}$$

where  $R_e$  is the effective resistance of the MOSFETs averaged over a switching period combined with the inductor resistance. For a given duty cycle, D,  $R_e$  is given by

$$R_e = D \cdot R_{ONH} + (1 - D) \cdot R_{ONL} + R_L \quad \text{Eq. [5]}$$

For Q > 1, which is the case for many low-cost power supplies, the phase can be assumed to shift from 0 to  $-180^{\circ}$  at  $f_n$ .

The PWM has a fixed gain of

$$G_{PWM} = \frac{V_{IN}}{V_{SAW}} \qquad \text{Eq. [6]}$$

where  $V_{SAW}$  is the peak amplitude of the PWM sawtooth waveform used in the PWM controller.  $G_{PWM}$  is a constant and has no phase impact on the feedback loop. The power stage gain,  $g_{PS}$ , (i.e., control-to-output transfer function) consists of a DC gain,  $G_{PS}$ , and a frequency-dependent component which is a function of  $f_{zesr}$ ,  $f_n$  and Q.

$$g_{PS} = G_{PS} \frac{1 + \frac{s}{2\pi f_{zesr}}}{1 + \frac{s}{2\pi f_n Q} + \frac{s^2}{(2\pi f_n)^2}} \quad \text{Eq. [7]}$$

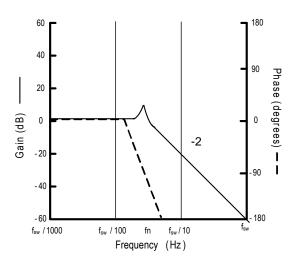

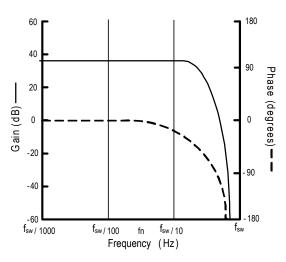

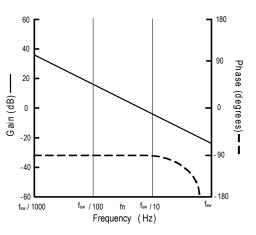

This transfer function is plotted in Figure 2. We define a term,  $G_{FIX}$ , which combines all the DC gains in the loop except that of the compensator.

$$G_{FIX} = G_{PWM}G_{PS} \qquad \qquad \mathbf{Eq. [8]}$$

If  $g_{COMP}$  represents the gain of the compensator, the open-loop transfer function of the simplified buck converter is then

RENESAS

$$g = g_{COMP} G_{FIX} \frac{1 + \frac{s}{2\pi f_{zesr}}}{1 + \frac{s}{2\pi f_n Q} + \frac{s^2}{(2\pi f_n)^2}} \quad \text{Eq. [9]}$$

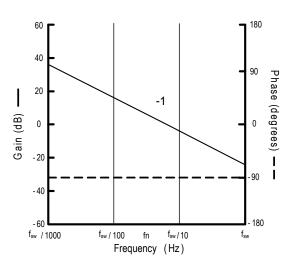

The desired feedback open-loop response is shown in Figure 3.

Figure 2. Buck Converter Power Stage Frequency Response

Figure 3. Desired Open Loop Response

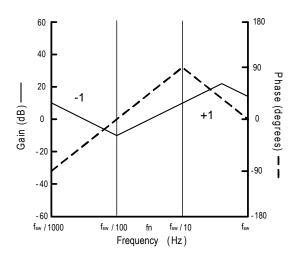

The goal of the compensation circuit is to modify the gain and add phase to the frequency response of the modulator and LC filter sections of the power supply (Figure 2) to achieve the desired feedback gain and

phase (Figure 3). Comparing Figure 2 and Figure 3 reveals what the frequency response of the compensation circuit should be. The compensation circuit frequency response is shown in Figure 4.

### Figure 4. Compensation Circuit Frequency Response

In a voltage mode analog power supply, this compensation is done with resistors and capacitors configured to provide poles, zeroes, and gain in the error amplifier.

To provide the highest possible gain at low frequencies, the compensator is generally chosen to be an integrator. This means that the compensator has a pole at the origin (DC), a -1 gain slope and a phase shift of  $-90^{\circ}$ . Because the phase shift due to the error amplifier is  $-180^{\circ}$ , the phase shift due to the LC filter is  $-180^{\circ}$  and the phase shift of the integrator is  $-90^{\circ}$ , the compensator must provide a positive phase boost. In addition, because the LC filter has a -2 gain slope and the integrator has a -1 slope, the compensator must have a +2 gain slope to yield the desired net gain slope of -1. The compensator accomplishes this with two zeroes placed near the LC filter natural frequency,  $f_n$ . These zeroes provide the +180 phase shift and +2slope needed to counteract the integrator and LC filter characteristics.

Although the loop gain is usually below OdB before the ESR zero, the compensator often provides a pole (-90°, -1 slope) to neutralize the effects of the ESR zero (+90°, +1 slope). Finally, due to limitations of real-world amplifiers, the compensator provides an additional pole to keep the error amplifier from operating beyond its gain-bandwidth product limit and to keep the switching frequency ripple from interfering with the operation of the PWM circuitry.

To complete the compensation circuit design, the amount of gain required by the compensation circuit must be determined. First, select a cross-over frequency ( $f_{xo}$ ), which is a fraction of the switching frequency ( $f_{sw}$ ). Generally, a ratio of 1/20 of the switching frequency is a conservative starting point ( $\sim f_{sw}/2\pi$  is the theoretical max<sup>[11]</sup>). The gain needed from the compensator is determined by assuming the control loop is compensated so the gain plot crosses OdB at a -1 slope as shown in Figure 3. The DC gain needed for this analog compensator ( $G_{ACMP-DC}$ ) is calculated by assuming a -1 slope for the compensated control loop for a given crossover frequency. This can be expressed as

$$G_{ACMP_{-}DC} = \frac{f_{xo}}{f_{sw}G_{FIX}} = \frac{1}{20G_{FIX}}$$

Eq. [10]

As noted above, the compensator has two zeroes at the LC resonant frequency  $(f_n)$ . A pole is added at the ESR zero  $(f_{zesr})$  to keep the gain of the open-loop transfer function at a slope of -1, and an additional pole is added at  $f_{sw}/2$  to reject noise. The amplifier circuit shown in Figure 5 is used to achieve the compensation.<sup>[2]</sup>

Figure 5. Analog Compensation Amplifier

The component values are calculated using the following equations:

$$R_{2} / R_{1} = G_{ACMP-DC} \qquad C_{1} = 1/(2\pi f_{n}R_{2})$$

$$C_{2} = 1/(2\pi f_{zesr}R_{2}) \qquad C_{3} = 1/(2\pi f_{n}R_{1})$$

$$R_{3} = 1/(2\pi (f_{sw}/2)C_{3})$$

The combination of the buck converter and compensation amplifier transfer functions yields the desired open-loop response shown in Figure 3.

Once the compensation values have been determined, the stability of the power supply can be evaluated. Using the equation for the buck converter transfer function and the gain, pole and zero locations from the compensation circuit, the resulting cross-over frequency, phase and gain margin can be evaluated. Although, ideally, the phase margin using this technique would be  $90^{\circ}$  and the gain margin would be 20dB or more, in reality  $60^{\circ}$  and 6dB are considered to be good design goals that strike a balance between performance and stability. Decreasing phase margin to less than  $60^{\circ}$  or gain margin to less than 6dB will increase the output voltage overshoot with transient output loads.

## **Digital PWM**

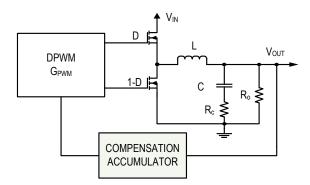

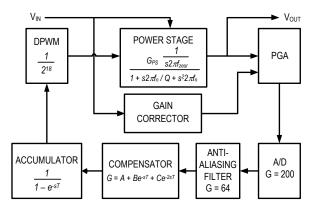

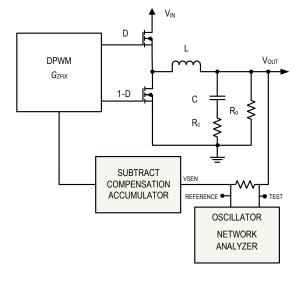

The block diagram for a power supply controlled by a digital PWM is shown in Figure 6. The digitally controlled power supply differs from the analog version only by the values shown in the PWM block and the compensation block. The gain of the digital PWM block is seen in the functional block diagram of Figure 7.

The PWM block is derived from several functions within the device. These functions, although implemented in high speed mixed signal circuitry, can be modeled with constant values because of the relatively high frequency at which these blocks operate compared to the frequencies of interest to the control loop (i.e., >10X the switching frequency).

Figure 6. DPWM-Controlled Power Supply

## Figure 7. Digital-DC Functional Block Diagram

The output voltage is first applied to a programmable gain amplifier (PGA) that has a gain of between 0.2and 2.0. This amplifier is used to enable higher accuracy in the setting of the output voltage. Its gain is cancelled by the gain corrector, which modifies the compensation settings to yield a net gain of 1. The gain correction function also compensates for changes in the input voltage by the same process. The gain corrector normalizes the input voltage to 5V and automatically modifies the gain so that the net result is a loop gain that would exist if the input were at 5V. Following the PGA, the error signal is applied to the A/D converter, which converts this error voltage into a digital value. Its gain is  $1/V_{step}$  (1/5 mV) or 200. Following the A/D converter is the anti-aliasing filter, which is a multi-stage filter that provides signal gain and high frequency noise rejection. It eliminates the need for the second pole used in the analog compensator. As can be seen in Figure 8, it has a fixed

gain of 64 at low frequencies, but a large attenuation at the switching frequency without adding excessive phase loss. This phase loss can be expressed as a function of the switching frequency and is discussed later as part of the compensation.

Figure 8. Anti-Aliasing Filter Response

After passing through the compensator and accumulator, the signal is applied to the digital pulse width modulator (DPWM). The DPWM converts the output of the integrator into the duty cycle that is applied to the power supply MOSFETs. In summary, the DPWM block in Figure 6 is a combination of the PGA, the gain of the A/D, the anti-aliasing filter, and the DPWM. This is also a fixed gain and can be expressed as

$$G_{FIX} = \frac{5 \cdot 200 \cdot 64}{2^{18}} G_{PS}$$

Eq. [11]

The transfer function of the digital voltage mode converter can now be expressed as an equation in the same form as the analog controller:

$$g = g_{COMP} G_{FIX} \frac{1 + \frac{s}{2\pi f_{zesr}}}{1 + \frac{s}{2\pi f_n Q} + \frac{s^2}{(2\pi f_n)^2}} \text{ Eq. [12]}$$

As mentioned earlier, the analog compensator of Figure 5 provides two zeroes to cancel the two poles of Equation [12] (at  $f_n$ ), but it also provides three poles. One of these poles cancels the ESR zero of Equation [12] (at  $f_{zesr}$ ), a high frequency pole (at  $f_{sw}/2$ ) improves noise immunity and the third pole is at the origin – an integrator which provides the desired response of a slope of -1. Finally, the analog compensator provides a DC gain term ( $G_{ACMP-DC}$ ) which ultimately determines the crossover frequency and impacts phase margin and gain margin as well. To obtain the ideal response of Figure 3 and provide noise rejection above  $f_{sw}/2$ , the analog compensator's transfer function must be

$$g_{ACMP} = G_{ACMP_DC} \frac{\left(1 + \frac{s}{2\pi f_n Q} + \frac{s^2}{(2\pi f_n)^2}\right)}{s\left(1 + \frac{s}{2\pi f_{zesr}}\right)\left(1 + \frac{s}{\pi f_{sw}}\right)} \text{ Eq. [13]}$$

Transforming Equation [12] to the digital domain yields an equation of the form

$$g_{Z} = g_{ZCOMP} G_{ZFIX} \frac{(1 - dz^{-1})}{(1 - bz^{-1} + cz^{-2})}$$

Eq. [14]

where  $g_{ZCOMP}$  is the z-domain compensator,  $G_{ZFIX}$  is a transcendental function of  $G_{FIX}$ ,  $f_n$ ,  $f_{zesr}$  and  $f_{sw}$  representing the DC gain in the z-domain, d is a transcendental function of  $f_{zesr}$  and  $f_{sw}$ , and b and c are transcendental functions of  $f_n$  and  $f_{sw}$ . It should be noted that, for Q > 0.5, b becomes complex but may be converted to a real number using Euler's identity.

The digital control loop is compensated in much the same way as the analog control loop. However, because the digital control loop has an anti-aliasing filter that provides noise rejection above  $f_{sw}/10$ , the poles at  $f_{zesr}$  and  $f_{sw}/2$  in Eq. [13] are not required in the digital compensation filter. For this reason, the crossover frequency should occur at least one octave before the ESR zero ( $f_{xo} \leq f_{zesr}/2$ ). The pole at the origin is implemented using an accumulator. Again, a crossover frequency of  $f_{xo} = f_{sw}/20$  is selected and the DC gain of the digital compensator is calculated, using an equation similar to Equation [10] for the analog compensator:

$$G_{ZCMP_{DC}} = \frac{f_{xo}}{f_{sw}G_{ZFIX}} = \frac{1}{20 \cdot G_{ZFIX}}$$

Eq. [15]

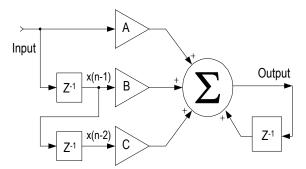

Like the analog compensator, the digital compensator has two zeroes at the LC resonant frequency  $(f_n)$ . Instead of an op-amp circuit, the digital compensator uses a recursive filter, which is simply an adder with four inputs: 1) the output of the A/D converter (the error voltage) multiplied by a constant, 2) the error voltage from the previous switching cycle (shown as  $z^{-1}$ ) multiplied by another constant, 3) the integrator and 4) the error voltage from the switching cycle two cycles previous (shown as an additional  $z^{-1}$ ) multiplied by a third constant. This filter is shown schematically in Figure 9.

### Figure 9. Digital Compensator / Recursive Filter

By substituting  $z^{-1} = e^{-sT}$  for each delay (where *T* is the sampling period), the digital compensator / recursive filter can be represented as follows:

$$g_{ZCOMP} = \frac{A + Bz^{-1} + Cz^{-2}}{(1 - z^{-1})}$$

or

$$g_{COMP} = \frac{A + Be^{-sT} + Ce^{-2sT}}{(1 - e^{-sT})}$$

Eq. [16]

The term  $1/(1-e^{-sT})$  is due to the accumulator and models both the gain and phase response of the integrator. Although in transcendental form, the digital compensator / recursive filter can be configured to have the same response as the analog compensator by selecting appropriate constants for *A*, *B* and *C* in Eq. [16].

To do so, set like terms equal in the numerator of Eq. [16] and the denominator of Eq. [14], being sure to divide by the compensator DC gain,  $G_{ZCMP-DC}$ . This yields Equations [17] for real zeroes (at  $f_{z1}$  and  $f_{z2}$ ) and Equations [18] for complex zeroes (at  $f_n$  for Q > 0.5). To simplify these equations, new terms  $r_1$  and  $r_2$  are defined for Eq. [17] and r and  $\theta$  are defined for Eq. [18].

Compensation Coefficients for Real Zeroes:

Let

$$r_1 \equiv e^{\frac{-2\cdot\pi\cdot f_{z1}}{f_{sw}}}$$

$r_2 \equiv e^{\frac{-2\cdot\pi\cdot f_{z2}}{f_{sw}}}$

$$A = \frac{G_{ZCMP-DC}}{(1-r_1)\cdot(1-r_2)}$$

Eq. [17]

$$B = -A\cdot(r_1+r_2)$$

$$C = A\cdot r_1\cdot r_2$$

Compensation Coefficients for Complex Zeroes:

Let

$$r \equiv e^{\frac{-\pi \cdot f_n}{Q \cdot f_{sw}}}$$

$\theta \equiv \frac{2\pi f_n}{f_{sw}} \cdot \sqrt{1 - \frac{1}{4 \cdot Q^2}}$

$A = \frac{G_{ZCMP-DC}}{1 - 2 \cdot r \cdot \cos \theta + r^2}$  Eq. [18]

$B = -A \cdot 2 \cdot r \cdot \cos \theta$

$C = A \cdot r^2$

As with the analog compensator, select the zero frequencies and the gain desired for the compensator stage. Solve the equations to yield the appropriate A, B, and C coefficients. These coefficients are loaded into the digital compensator using a PMBus command. Additional details on the use of the PMBus for loading compensation coefficients are in Application Note AN2013.<sup>[3]</sup> The power supply response can be simulated and tested in the same manner as an analog controller.

The digital compensator also provides a means of correcting for the Q of the LC filter. Using the calculated coefficients, both the gain and phase of the LC filter are cancelled by the digital compensator, as shown in Figure 10.

Figure 10. Open-Loop Response

As mentioned previously, Zilker Labs, Inc. offers userfriendly tools for calculating compensation coefficients using regulator design constraints and filter component parameters. Contact your regional sales office for details.

## **Performance Verification**

Once the coefficients have been loaded into the device, the circuit can be tested for stability and transient response performance. Transient response is the easiest to test. It is done by applying a rapidly changing output current, or step load, to the output and measuring the response using an oscilloscope. If a programmable electronic load is available,

- Set the step load slew rate to that of the expected end-use application.

- Set the load step to cause a *1-3%* deviation in the output voltage.

- Set the step duty cycle to  $\sim 50\%$

- Select a repetition frequency that allows the power supply to settle after each transition;  $f_{xo}/100$  should be a good starting point.

The power supply output should be 95% settled within three time-constants of the crossover frequency, or

$$t_{95\%} \approx 3 \cdot \tau_{xo} = \frac{3}{2\pi f_{xo}}$$

Eq. [19]

The response to the step load may have some overshoot. However, more than three oscillations indicate marginal stability; an exponential decay is preferred.

The control-loop response should also be verified by injecting a frequency swept signal into the loop and measuring the frequency response with a network analyzer. This is done by placing a small resistor (10 -100 $\Omega$ ) between the output and the VSEN pin and injecting the signal into the feedback loop by applying a floating AC signal across this resistor, as shown in Figure 11. The voltage from VSEN to ground is the input signal (sometimes called reference signal), and the power supply output voltage  $(V_{OUT})$  is the output signal (sometimes called the test signal). The network analyzer will read out the relative phase and gain of the transfer function: output signal/input signal. The goal is to verify a phase margin of  $>60^{\circ}$  and a gain margin of >6dB over a range of operating conditions. The test signal should be monitored with an oscilloscope and adjusted so that the test signal peak amplitude does not exceed 1% of the  $V_{OUT}$ . Excessive test signal amplitude will result in erroneous loop gain measurements. Proper correlation between measurements and simulations depends on the accuracy of the models used, and Zilker Labs, Inc. is constantly working to ensure the accuracy of its models.

References

- [1] Lloyd H. Dixon, Jr., *Control Loop Cookbook*, Unitrode Power Supply Design Seminar Manual SEM-1100, 1996, p. 5-20.

- [2] Venable, Dean and Foster, S. R., *Practical Techniques for Analyzing, Measuring and Stabilizing Feedback Control Loops in Switching Regulators and Converters,* PowerCon7 Proceedings, 1980.

- [3] AN2013 Zilker Labs PMBus<sup>™</sup> Command Set, Zilker Labs, 2006.

| Date       | Rev. #   |                                                                                                                                                                                                                                                                                                                                   |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/27/2006 | 1.0      | Initial Release                                                                                                                                                                                                                                                                                                                   |

| 10/12/2006 | 1.1      | Update Eqs 5, 8 and 14                                                                                                                                                                                                                                                                                                            |

| 06/14/2007 | 1.2      | Corrected Fig 11.                                                                                                                                                                                                                                                                                                                 |

| 09/04/2007 | 1.3      | General updates.                                                                                                                                                                                                                                                                                                                  |

| 09/04/2007 | 1.31     | Minor text revisions.                                                                                                                                                                                                                                                                                                             |

| 12/06/2007 | 1.32     | Corrected loop response descriptions to say<br>"open loop"                                                                                                                                                                                                                                                                        |

| 05/01/2009 | AN2016.0 | Assigned file number AN2016 to app note as<br>this will be the first release with an Intersil<br>file number. Replaced header and footer with<br>Intersil header and footer. Updated<br>disclaimer information to read "Intersil and<br>it's subsidiaries including Zilker Labs, Inc."<br>No changes to application note content. |

# **Revision History**

Figure 11. Loop Gain Measurement

# NOTES

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for velucting the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

(Rev.4.0-1 November 2017)

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information. Renesas Electronics America Inc. Murphy Ranch Road, Milpitas, CA 95035, U.S.A. +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804 **Renesas Electronics Europe GmbH** Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-132 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Si No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338