# **RENESAS** Using VersaClock<sup>®</sup> 6 as Reference Clock for Xilinx<sup>®</sup> 7 Series FPGAs

# Introduction

Xilinx<sup>®</sup> 7 Series FPGAs need a reference clock with relatively stringent requirements. The phase noise requirement is most notable with maximum phase noise levels at 10KHz, 100KHz and 1MHz offsets from the clock carrier frequency. This application note describes how the VersaClock 6 meets all the requirements for the Xilinx 7 Series reference clock.

## Phase Noise

The phase noise specification for the Xilinx 7 Series reference clock is stringent enough that not just any clock generator can meet this spec. In the table below, the phase noise requirements are listed, together with the actual performance of VersaClock 6.

The reference clock is used for the Channel PLL's (CPLL) and Quad PLL's (QPLL) inside the FPGA. The QPLL is an LC based PLL that is used for communication channels with the highest line rates. The CPLL is a ring oscillator based PLL that is used for the lower line rates that don't require "LC" noise performance.

| Ref Clock<br>(MHz) | QPLL Phase Noise (dBc) |         |       | CPLL Phase Noise (dBc) |         |       |

|--------------------|------------------------|---------|-------|------------------------|---------|-------|

|                    | @10kHz                 | @100kHz | @1MHz | @10kHz                 | @100kHz | @1MHz |

| 100                | -126                   | -130    | -134  | -126                   | -132    | -136  |

| 125                | -123                   | -129    | -133  | -123                   | -131    | -135  |

| 156.25             | -122                   | -127    | -132  | -121                   | -129    | -133  |

| 250                | -119                   | -126    | -131  | -119                   | -126    | -132  |

| 312.5              | -115                   | -124    | -130  | -116                   | -124    | -131  |

| 625                | -110                   | -116    | -120  | -110                   | -119    | -127  |

#### Table 1: QPLL and CPLL Requirements

VersaClock 6 can generate all the frequencies above except 625MHz.

Table 2:

VersaClock 6 Performance.

For convenience the QPLL and CPLL requirements are also added to the table.

| Ref Clock | Xtal  | VersaClock 6 Phase Noise (dBc) (QPLL (dBc) / CPLL (dBc) ) |                      |                      |  |

|-----------|-------|-----------------------------------------------------------|----------------------|----------------------|--|

| (MHz)     | (MHz) | @10kHz                                                    | @100kHz              | @1MHz                |  |

| 100       | 25.00 | -128.1 (-126 / -126)                                      | -133.9 (-130 / -132) | -140.5 (-134 / -136) |  |

| 125       | 25.00 | -125.9 (-123 / -123)                                      | -131.8 (-129/-131)   | -138.2 (-133 / -135) |  |

| 156.25    | 25.00 | -123.8 (-122/-121)                                        | -130.0 (-127 / -129) | -136.3 (-132 / -133) |  |

| 250       | 25.00 | -120.3 (-119/-119)                                        | -126.2 (-126 / -126) | -132.2 (-131 / -132) |  |

| 312.5     | 31.25 | -118.2 (-115 / -116)                                      | -124.2 (-124 / -124) | -131.5 (-130/-131)   |  |

VersaClock 6 meets all the phase noise requirements so it can be used with Xilinx 7 Series FPGAs.

For 100MHz to 250MHz output frequencies a 25MHz crystal is good enough to meet the QPLL and CPLL requirements. For 312.5MHz output frequency a 31.25MHz crystal is needed to achieve the required phase noise levels. A crystal frequency higher than 31.25MHz can be used to improve the phase noise margins.

| Ref Clock | Xtal    | VersaClock 6 Phase Noise (dBc) (QPLL (dBc) / CPLL (dBc) ) |                      |                      |  |

|-----------|---------|-----------------------------------------------------------|----------------------|----------------------|--|

| (MHz)     | (MHz)   | @10kHz                                                    | @100kHz              | @1MHz                |  |

| 100       | 39.0625 | -128.5 (-126 / -126)                                      | -135.3 (-130 / -132) | -140.2 (-134 / -136) |  |

| 125       | 39.0625 | -126.8 (-123 / -123)                                      | -133.4 (-129/-131)   | -138.5 (-133 / -135) |  |

| 156.25    | 39.0625 | -124.0 (-122 / -121)                                      | -131.2 (-127 / -129) | -137.3 (-132 / -133) |  |

| 250       | 39.0625 | -120.5 (-119/-119)                                        | -127.3 (-126 / -126) | -134.9 (-131 / -132) |  |

| 312.5     | 39.0625 | -118.6 (-115/-116)                                        | -125.4 (-124 / -124) | -133.0 (-130/-131)   |  |

#### Table 3: Additional Set of Phase Noise Test Results when using a 39.0625MHz Crystal.

The CLKIN differential input on VersaClock 6 can also be used to bring in a reference clock. To meet the phase noise requirements when using the CLKIN differential input, it is advised to use a reference clock frequency of 50MHz or higher.

See "Appendix A: Phase Noise Plots" for example phase noise plots, measured with VersaClock 6.

See "Appendix B: Full VersaClock 6 Configuration, Multiple Outputs" for a study with multiple outputs at different frequencies.

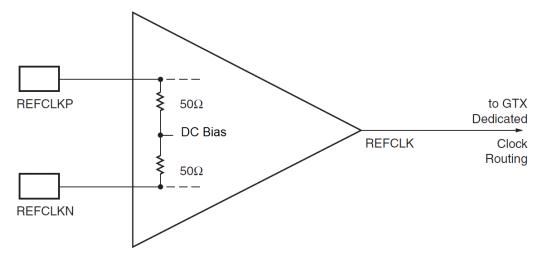

### Xilinx FPGA Reference Clock Input

The reference clock input on the Xilinx FPGA has on-chip  $100\Omega$  ( $50\Omega + 50\Omega$ ) differential termination. The center tab between the two  $50\Omega$  resistors is biased internally and Xilinx recommends to AC couple the differential reference clock with typical 100nF capacitors to the REFCLKP and REFCLKN input pair.

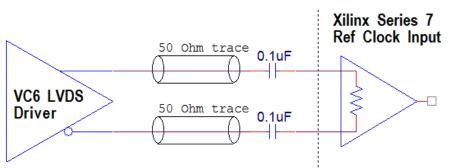

Xilinx specifies minimum 250mV and maximum 2000mV, differential peak-to-peak. The best fit for driving the Xilinx 7 Series input is the LVDS logic. The VersaClock 6 datasheet specifies the LVDS levels per single ended output pin and translated to differential, the spec says minimum 494mV and maximum 908mV peak-to-peak. This fits nicely inside the Xilinx input spec.

Recommended circuit when using a VersaClock 6 LVDS output to drive a Xilinx 7 Series reference clock input:

Only the AC coupling capacitors are needed to connect the VersaClock LVDS output to the Xilinx 7 Series FPGA reference clock input.

### Conclusion

Phase Noise performance of reference clocks generated by VersaClock 6 meet the phase noise mask requirements of Xilinx 7 Series FPGAs.

Waveform requirements can be met easily with the LVDS logic type.

### References

- Xilinx 7 Series FPGAs GTX/GTH Transceivers, User Guide (UG476)

- Xilinx 7 Series FPGAs Overview (DS180)

- Xilinx 7 Series Datasheets for Kintex (DS182) and Virtex (DS183)

- Xilinx 7 Series Phase Noise masks: http://www.xilinx.com/support/answers/44549.html

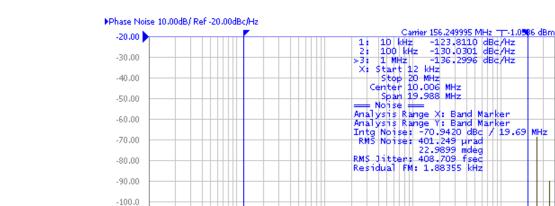

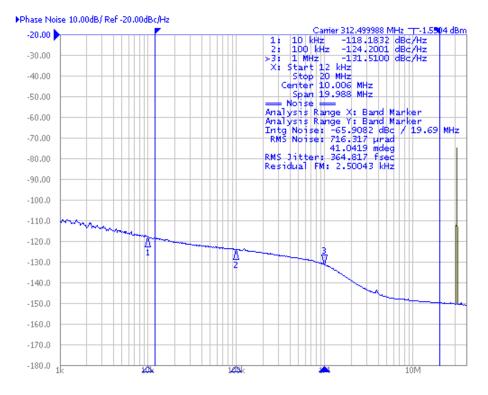

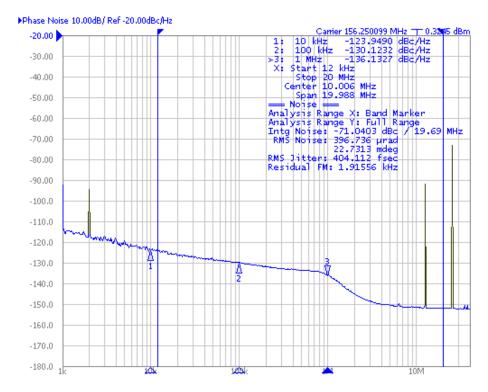

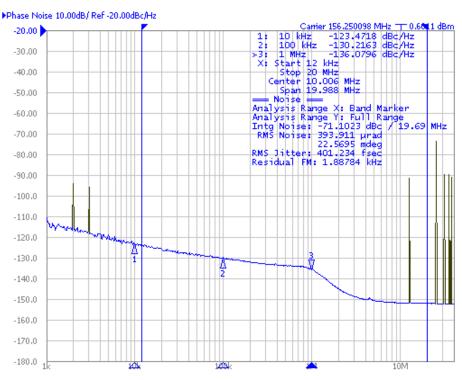

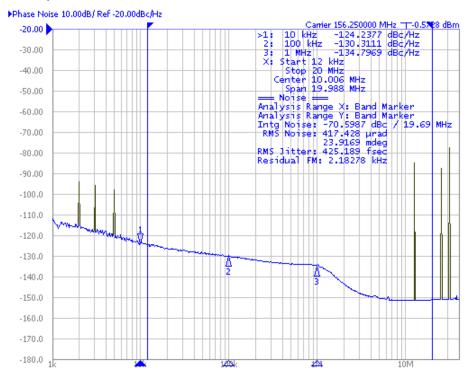

## **Appendix A: Phase Noise Plots**

-110.0

-130.0

-140.0 -150.0 -160.0 -170.0 -180.0

Example A1: 156.25MHz LVDS clock, generated by VersaClock 6 with a 25MHz crystal

Example A2: 312.5MHz LVDS clock, generated by VersaClock 6 with a 31.25MHz crystal

in.

Å

2

1 AN

10M

# Appendix B: Full VersaClock 6 Configuration, Multiple Outputs

Most applications will use one output for driving a Xilinx 7 Series FPGA and other outputs for other purposes. The other outputs will have different frequencies and mixing of the output signals causes spurs in the phase noise plot and jitter. The following phase noise plots show a few example combinations. In all plots we look at a 156.25MHz clock while different frequencies are present on other outputs. For this study a 25MHz crystal was used and all outputs have LVDS logic.

Example B1: 156.25MHz for FPGA and 100MHz for PCI Express®

Adding one output at 100MHz causes a 12.5MHz spur but this spur is below -90dBc and does not contribute significantly to the 12K~20M phase jitter. Phase Noise levels at 10KHz, 100KHz and 1MHz are unaffected. This combination is perfect for the 5P49V6913 with two differential outputs.

Example B2: 156.25MHz for FPGA, 2 X 100MHz for PCI Express and 125MHz for Giga Bit Ethernet

A few spurs appear above 30MHz but still no significant contribution to phase jitter or phase noise levels. This combination is perfect for the 5P49V6901 with four differential outputs.

#### Example B3: 100MHz, 125MHz, 156.25MHz and 250MHz

In this case the 12.5MHz spur is a little bit stronger, causing the phase jitter to increase to 425fs. Phase Noise levels at 10KHz, 100KHz and 1MHz are still unaffected. This combination is perfect for the 5P49V6901 with four differential outputs.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1 October 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

## Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>

## Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.