# Philips Semiconductors

# 32 Bit Logic Families in LFBGA packages: 96 and 114 Balls Low Profile Fine Pitch BGA Packages.

# **Application Note.**

October 26th, 1998 by:

Sylvie Kadivar, Philips Semiconductors

Maria Balian, Texas Instruments

Ed Agis, Texas Instruments

Valentino Liva, Integrated Device Technology

## **Disclaimers**

Philips Semiconductors

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code Date of release: 10-98

#### IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as components in life support or other medical devices or systems (hereinafter life support devices) unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- Life support devices are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. This policy covers any component of a life support device or system whose failure to perform can cause the failure of the life support device or system, or to affect its safety or effectiveness.

Note: Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described hereinother than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication, estoppel, or otherwise under any patent, or other rights, of Integrated Device Technology, Inc.

The IDT logo and Orion are registered trademarks of IDT. AdvantageIDT, BiCameral, BiFIFO, BurstRAM, BUSMUX, CacheRAM, Centaurus, ClockDoubler, CZAR, DECnet, Double-Density, DualSync, FASTX, FlexBus, FLEXI-CACHE, Flexi-PAK, Flow-thruEDC, Four-Port, Fusion Memory, IDT/c, IDTenvY, IDT/sae, IDT/sim, IDT/ux, Libra, MacStation, MicroMonitor, MICROSLICE, NICStAR, Orion, PalatteDAC, Pegasus, QuickStart, RC3041, RC3051, RC3052, RC3071, RC3081, RC36100, RC3715, RC3740, RC4600, RC4650, RC4700, RV3041, RV3081, RV4600, RV4650, RV4700, RC5000, REAL8,RISCard, RISCompiler, RISController, RISCNT, RISC Subsystems, RISC Windows, SARAM, SmartLogic, SolutionPak, SyncFIFO, SyncBiFIFO, SuperSync, TargetSystem, Zero-Bus-Turnaround, Smart Zero-Bus-Turnaround, Smart

MIPS is a registered trademark of MIPS Computer Systems, Inc.

Pentium Processor is a trademark of Intel Corporation.

PowerPC is a trademark of IBM. All other brand names and product names included in this publication are trademarks, registered trademarks or trade names of their respective owners. Use of and IDT product in violation of this policy voids any warranties associated with the product, and is used at the customer's own risk.

# **Table of Contents**

| DISCLAIMERS                                                 | II |

|-------------------------------------------------------------|----|

| TABLE OF CONTENTS                                           |    |

| 1 Introduction                                              | 2  |

| 2 EXAMPLES OF APPLICATIONS WITH LFBGA PACKAGES              | 4  |

| 2.1 Industry expressed requirements for 32 bit Logic        | 4  |

| 2.2 Customer needs and problems targeted                    |    |

| 2.3 Application examples                                    | 5  |

| 2.4 Existing or alternative solutions: a Comparison         | 5  |

| 3 PACKAGE DESCRIPTIONS                                      |    |

| 3.1 LFBGA Package Characteristics                           | 8  |

| 3.1.1 LFBGA-96 package dimensions.                          |    |

| 3.1.2 LFBGA-114 package dimensions.                         |    |

| 3.1.3 LFBGA Power Dissipation                               | 12 |

| 3.2 LFBGA vs. TVSOP, TSSOP, and Millipa $Q^{TM}$ footprint  | 14 |

| 3.3 Benefits to the customer                                | 15 |

| 3.4 Contribution to JEDEC Definition                        | 15 |

| 3.5 Evaluation Units                                        | 15 |

| 4 LFBGA PACKAGE MARKING, SHIPPING MEDIA AND HANDLING.       | 16 |

| 4.1 Marking                                                 | 16 |

| 4.2 Tape & Reel                                             | 17 |

| 4.3 Sockets, and Socket Manufacturer (Ordering Information) | 18 |

| 5 PCB Manufacturing Considerations                          | 19 |

| 5.1 Land Pads                                               | 19 |

| 5.2 Line and Spaces                                         | 19 |

| 5.3 Vias                                                    |    |

| 5.4 Routing                                                 |    |

| 6 CONCLUSION                                                |    |

| Acknowledgements:                                           | 23 |

## 1 Introduction

With increasing systems and circuit complexity and the constant downward pressure on system prices, the requirements for bus interface solutions demand new approaches to system needs. One of the major challenges and goals of the digital processing industry is to continue decreasing the overall system costs as system complexity increases. Consequently, circuit integration and board miniaturization have become key words and key trends in present and future applications. A direct consequence of these trends is the need for wider bus interfacing. Today, as many networking, telecom and computer systems begin using DSP's and MPU's that require 32bit, or even 64 bit wide interfacing, there is an increasing demand for 32bit wide buffer, driver and transceiver functions. These new functions will become the standard in the years to come. To address evolving customer requirements, three suppliers, Integrated Device Technology, Philips Semiconductors and Texas Instruments have come together to define a package for 32bit functions. Collectively Integrated Device Technology, Philips Semiconductors and Texas Instruments evaluated many customer inputs and identified a Low Profile Fine Pitch Ball Grid Array (LFBGA) package solution that would best serve customers' needs. Studies have shown that the LFBGA is an optimal solution for reducing the inductance, improving thermal performance and minimizing board real estate in support of integrated bus functions. Together, our objective is to provide multi-source products in a package that enables significant electrical improvements when compared to existing packages, as well as cost savings to the OEM manufacturing process. From a supplier standpoint, we can now guarantee the multi-sourcing of a package that will become the standard in the very near future.

The purpose of this document is to discuss the two new Fine Pitch BGA solutions, the 96 and 114 ball LFBGA packages. Five 32 bit functions will initially be introduced in LFBGA package. Additional products will be manufactured per market interest and customer demand. A definition and description of the 96 and 114 ball LFBGA packages are discussed in this application note. Content and technical exhibits from the application note should be used to develop PCB layouts using the 96 and/or 114 ball LFBGA packages. Examples of routing, layout and mechanical dimensions are also included in this document. The initial introduction of the 32 bit Logic is noted in the table below:

|                |         | Number of Balls               |   |    |  |  |

|----------------|---------|-------------------------------|---|----|--|--|

| LVCH Functions | Package | Package Gnd Vcc No Connection |   |    |  |  |

| 74LVCH32244    | 96      | 16                            | 8 | NA |  |  |

| 74LVCH32245    | 96      | 16                            | 8 | NA |  |  |

| 74LVCH32373    | 96      | 16                            | 8 | NA |  |  |

| 74LVCH32374    | 96      | 16                            | 8 | NA |  |  |

| ALVCH Function |         |                               |   |    |  |  |

| 74ALVCH32501   | 114     | 16                            | 8 | 2  |  |  |

**Table 1.1 – Initial 32 Bit Functions**

LFBGA packages offer lower inductance and parasitic capacitance than any other TSSOP, TVSOP and MillipaQ<sup>TM</sup> packages. The LFBGA package characteristics supports improvements in Ground bounce, Vcc undershoot, pin-to-pin skew, and signal propagation delay of 20 to 50ps.

The definition of these two packages in terms of standardization, both physical and mechanical, was developed by Integrated Device Technology, Philips Semiconductors and Texas Instruments to provide the industry pinout compatible solutions.

# 2 Examples of Applications with LFBGA Packages

### 2.1 Industry expressed requirements for 32 bit Logic

With the growing trend towards increased bus widths, OEMs are looking to consolidate logic functions in an effort to effectively make use of board real estate. This requirement from customers is prevalent across many end equipments. The requirement to reduce board real estate also necessitates a packaging solution, which integrates logic as well as addresses improved thermal packaging characteristics in addition to minimizing pin-to-pin skew. The selection of the 96 and 114 Ball LFBGA addresses all of these careabouts with improved performance and standardization of pin outs agreed upon by Integrated Device Technology, Philips Semiconductors and Texas Instruments. In the initial 8 month study, consisting of 15 OEMs and several worldwide subcontractors, we found that the preferred pitch for introducing logic in either the LFBGA is a 0.8mm with a 0.5mm ball diameter. Both packages are being offered by Integrated Device Technology, Philips Semiconductors and Texas Instruments to support customer requirements and enable easier PCB design/layout along with a more robust solder joint based on life cycle studies.

While other solutions were looked at such as staggered depopulated balls, with a smaller pitch, as well as, a smaller ball diameter, none were considered suitable to address the current market needs for OEM's and the subcontractors. The LFBGA packages selected by IDT, Philips Semiconductors and Texas Instruments is the optimal solution as it addresses our current customer needs. More details for package comparison are noted within the other subsections of this application note.

## 2.2 Customer needs and problems targeted

#### **Workstations:**

- Workstations busses extend to 128, 256 bits, and wider bus structures;

- Require denser and faster logic products.

#### PCs:

- The trend is to integrate as much logic as possible into fewer packages;

- Due to space constraint, PC Cards require dense integration and small package foot-prints;

- PCI bus structures may require 5V tolerance in addition to integrating logic circuits.

#### **Datacommunication:**

"Intelligent" routers and switches require more logic to support interfaces and build real time lookup tables for routing addresses with statistics.

#### **Telecommunication:**

- Base stations are becoming small and ubiquitous requiring the repackaging of many circuits into dense boards;

- New complex and smaller equipment must interface with legacy equipment.

## 2.3 Application examples

- PC Motherboards

- Data communications

- Telecommunications

- Back Planes

- Base stations

- Cellular and cordless telephone

### 2.4 Existing or alternative solutions: a Comparison

While other packages have been introduced to address integrated logic solutions, these packages have only had limited success, such as the 100 pin TQFPs or the 80/96 pin MillipaQ<sup>TM</sup>. As a comparison, these two solutions have a reduce number of ground and Vcc pins leading one to believe that ground bounce and pin-to-pin skew cannot be optimally designed to address these design issues.

Comparisons of the foot print space show that the 100 pin TQFP and 80/96 pin MillipaQ<sup>TM</sup> packages takes up respectively 245% and 66% more area than the corresponding 96 LFBGA. For further details refer to tables 2.1 and 2.2.

The 96-ball LFBGA package provides an optimal area/bit ratio and improved pin-to-pin skews. Pin-to-pin skew is minimized by the number of pin signals connected to the same ground connection.

| Package                          | Footprint Area    | Area/Bit          | Weight | Total # of    |

|----------------------------------|-------------------|-------------------|--------|---------------|

|                                  | $(\mathbf{mm}^2)$ | $(\mathbf{mm}^2)$ | (g.)   | Balls or pins |

| LFBGA 96                         | 74.25             | 2.32              | 0.132  | 96            |

| MillipaQ <sup>TM</sup> 80/96 pin | 123.0             | 3.84              | 0.332  | 80/96         |

| 2 x TVSOP 48 pin                 | 132.5             | 4.14              | 0.227  | 96            |

| 2 x TSSOP 48 pin                 | 213.0             | 6.66              | 0.383  | 96            |

| 2 x SSOP 48 pin                  | 342.0             | 10.7              | 1.180  | 96            |

| TQFP 100 pin                     | 256.0             | 8.00              | 0.660  | 100           |

Note 1: The Area/bit is computed for 32 bits and assumes a 1.3mm PCB spacing for two-package solution.

Note 2: The MillipaQ<sup>TM</sup> offers 32 bit logic functions with reduced ground and Vccs; such configuration compromises the signal integrity of the logic functions.

Table 2.1 – Comparison of Foot Print Size with 96 LFBGA.

| Package          | Footprint Area    | Area/Bit          | Weight | Total # of    |

|------------------|-------------------|-------------------|--------|---------------|

|                  | $(\mathbf{mm}^2)$ | $(\mathbf{mm}^2)$ | (g.)   | Balls or pins |

| LFBGA 114        | 88.00             | 2.44              | 0.167  | 114           |

| 2 x TVSOP 56 pin | 153.0             | 4.25              | 0.271  | 112           |

| 2 x TSSOP 56 pin | 237.3             | 6.59              | 0.423  | 112           |

| 2 x SSOP 56 pin  | 394.6             | 11.0              | 1.360  | 112           |

| TQFP 120 pin     | 256.0             | 7.11              | 0.660  | 120           |

Note 1: The Area/bit is computed for 36 bits and assumes a 1.3mm PCB spacing for two-package solution.

Table 2.2 - Comparison of Foot Print Size with 114 LFBGA

# **3 Package Descriptions**

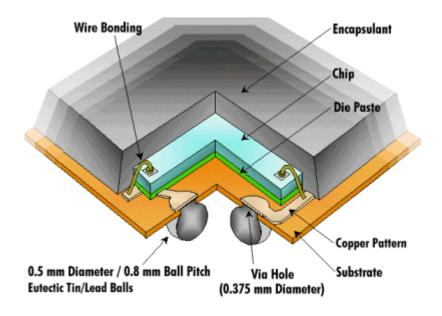

Figure 3.1 shows a cross section of the LFBGA package.

Figure 3.1 - LFBGA Cross Section

Table 3.1 summarizes the package attributes for the LFBGA.

|                                    | LFBGA-96        | LFBGA-114      |

|------------------------------------|-----------------|----------------|

| Ball count                         | 96              | 114            |

| Ball configuration (rows, columns) | 6 x 16          | 6 x 19         |

| Square/Rectangular                 | R               | R              |

| Ball-to-ball pitch (mm)            | 0.8             | 0.8            |

| Ball diameter (mm)                 | 0.5             | 0.5            |

| Package body width (mm)            | 5.5             | 5.5            |

| Package body length (mm)           | 13.5            | 16             |

| Package thickness (mm)             | 1.2min – 1.5max | 1.2min –1.5max |

| Package weight (mg)                | 132             | 167            |

| Shipping media Tape & Reel (units) | 1000            | 1000           |

| Desiccant pack                     | Level 3         | Level 3        |

**Table 3.1 – LFBGA Package Attributes**

## 3.1 LFBGA Package Characteristics

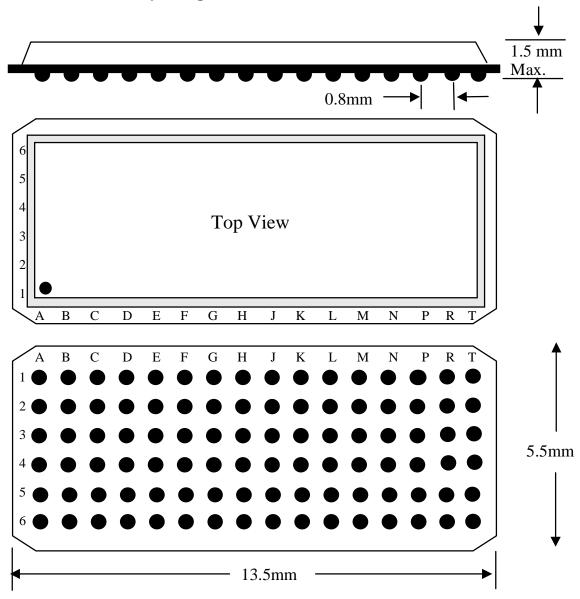

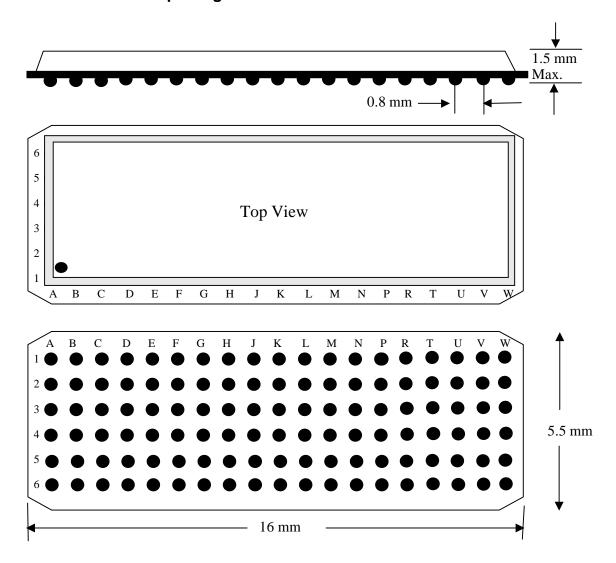

## 3.1.1 LFBGA-96 package dimensions.

Ball organization:  $6 \times 16 = 96$  balls; grid = 0.8mm;

Footprint: 74.25 mm<sup>2</sup>

Figure 3.2 - LFBGA-96 Package Layout

#### **Advantages:**

- Industry accepted 0.8mm pitch industry standard; easy pad-via-to-ball routing;

- Easy customer PCB layout; easy to locate near connectors;

- Robust solderability due to standard .5mm ball size.

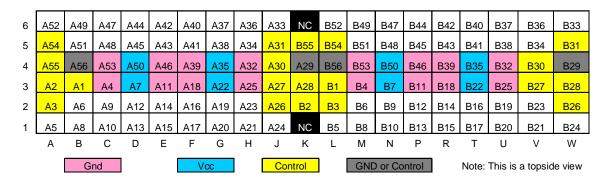

#### **LFBGA-96 Pin Out Configuration:**

Note: The pin out configuration below adopts the same naming convention applied in the industry to logic devices in 48 pin packages (i.e. TSSOP, SSOP, TVSOP).

Figure 3.3 – Top View Pin Assignment

#### **Electrical:**

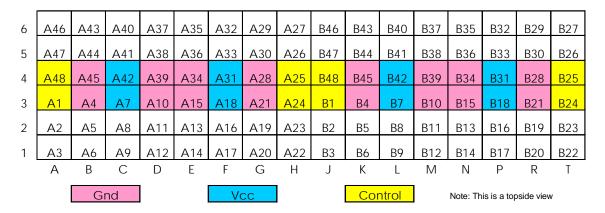

The electrical parameters of a package are dependant upon parasitic elements, which include inductance, capacitance, and electrical or propagation delays throughout the package. The table below summarizes the typical parasitic components of the LFBGA package. One should note that the reported values for the LFBGA package are about 35% better than the TVSOP package and 45% better than the TSSOP package. Overall the LFBGA package is better than any existing industry standard package on the market today.

Figure 3.4 provides an electrical comparison of the LFBGA-96 with other industry standard packages.

Figure 3.4 - Electrical Comparisons.

## 3.1.2 LFBGA-114 package dimensions.

Ball organization:  $6 \times 19 = 114 \text{ balls (112 used)}$ ; grid = 0.8 mm;

Footprint: 88 mm<sup>2</sup>

Figure 3.5 - LFBGA-114 Package Layout

## **Advantages:**

- Industry accepted 0.8mm pitch; easy pad-via-to-ball routing;

- Easy customer PCB layout; easy to locate near connectors;

- Robust solderability due to standard .5mm ball size.

#### **LFBGA-114 Pin Out Configuration:**

Note: The pin out configuration below adopts the same naming convention applied in the industry to logic devices in 56 pin packages (i.e. TSSOP, SSOP, TVSOP).

Figure 3.6 – Top view pin assignment

#### **Electrical:**

The electrical parameters of a package are dependent upon parasitic elements, which include inductance, capacitance and electrical propagation delays throughout the package. The table below summarizes the typical parasitic components of the LFBGA package. One should note that the reported values for the LFBGA package are about 35 % better than the TVSOP package and 42 % better than the TSSOP package. Overall the LFBGA package is better than any existing industry standard package on the market today.

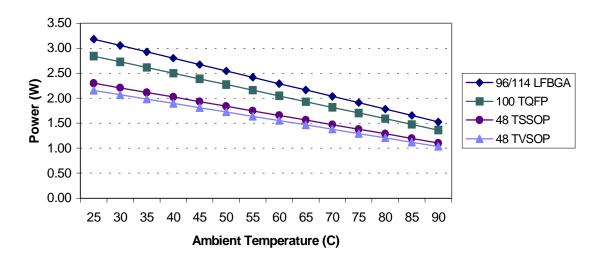

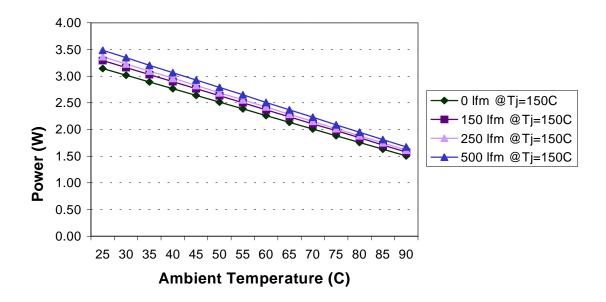

#### 3.1.3 LFBGA Power Dissipation.

The power dissipation of LFBGA is very much dependent upon the thermal conduction paths between the chip and the printed circuit board (PCB). The 96 and 114 ball LFBGA package outline is small, thereby limiting the amount of power dissipation due to convection or radiation, so the PCB becomes the major heat source for the package. The thermal performance of the packages is good when the chip overlaps the solder balls due to the fact that the balls under the chip act as thermal conduction paths to the PCB. The thermal resistance of LFBGA packages is 35 % better than the TVSOP package and 30 % better than the TSSOP package.

A well-designed PCB board further enhances the power dissipation of both LFBGA packages. By adding thermal vias (i.e via from the solder ball to the top buried ground plane), a significant benefit of 15 to 20 % is obtained over existing PCB designs.

Note: The maximum power dissipation is calculated using a junction temperature of 150C.

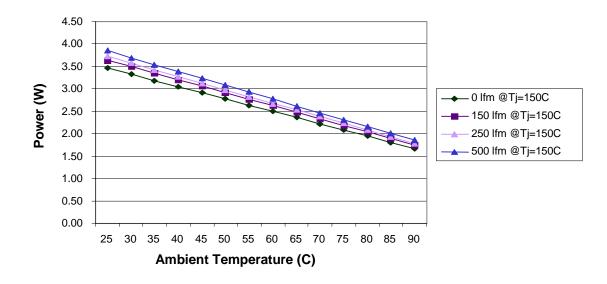

Figure 3.7 - Thermal Comparisons on Multi-layer JEDEC Board.

Note: The maximum power dissipation is calculated using a junction temperature of 150C.

| Air Velocity (ft/min) | 0    | 150  | 250  | 500  |

|-----------------------|------|------|------|------|

| • JA (C/W)            | 39.8 | 38.0 | 37.2 | 35.9 |

Figure 3.8 – LFBGA thermal derating curves without thermal vias using multilayer JEDEC Board.

Note: The maximum power dissipation is calculated using a junction temperature of 150C.

| Air Velocity (ft/min) | 0    | 150  | 250  | 500  |

|-----------------------|------|------|------|------|

| • JA (C/W)            | 36.1 | 34.4 | 33.6 | 32.5 |

Figure 3.9 – LFBGA thermal derating curves with thermal vias using multilayer JEDEC Board.

# 3.2 LFBGA vs. TVSOP, TSSOP, and MillipaQ<sup>™</sup> footprint

Figure 3.10 – Package Comparisons

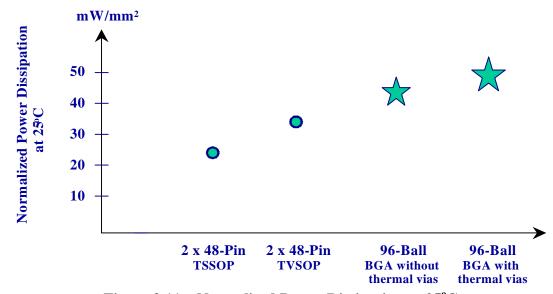

Comparison of the normalized thermal dissipation for the TSSOP, TVSOP, and the LFBGA-96 shows that the LFBGA-96 with thermal vias exceeds by a factor of 2 the capability of 2 x 48 TSSOP packages.

Figure 3.11 – Normalized Power Dissipation at 25°C

Note: Calculations are based on the data from figure 3.7 and figure 3.10.

#### 3.3 Benefits to the customer

The following table summarizes key features and corresponding benefit for logic products assembled in LFBGA packages.

| Feature                                  | Benefit                                               |

|------------------------------------------|-------------------------------------------------------|

|                                          |                                                       |

| Offer the minimum foot print to Industry | Uses the smallest real estate among industry standard |

|                                          | packages; Cost savings for PC boards;                 |

| Minimize the Skew parameter              | Provides the user with a reliable solution in new     |

|                                          | faster busses configurations;                         |

| Minimize package propagation delay       | Provides the user with additional design margin in    |

|                                          | high speed busses;                                    |

| Rise Time and Fall Time is 1ns typical   | Again, Tr and Tf are optimized to meet good duty      |

|                                          | cycle at 100mhz and 133mhz while keeping the          |

|                                          | ground bounce under 500mV                             |

| Lower Ground Bounce                      | Allows more noise margin.                             |

| Selected as a JEDEC standard package     | Meet mechanical and electrical specifications define  |

|                                          | by the IDT/TI/PHILIPS working group                   |

|                                          | Can use 2.5V or other special supply from 2.5 to      |

|                                          | 3.3V                                                  |

| No external components other than bypass | Low cost, low maintenance, better reliability         |

| Capacitors                               |                                                       |

| Supports/enables high speed applications | LFBGA packages has less capacitance pin-to-pin        |

|                                          | inductance and ground inductance. This provides       |

|                                          | better support for high-speed applications.           |

Table 3.2 - Feature/benefits of LFBGA packages

#### 3.4 Contribution to JEDEC Definition

The 96 and 114 LFBGA packages have received JEDEC (Joint Electronics Device Engineering Council) JC-11 under semiconductor package standard MO-205 and EIAJ (Electronic Industry Association Japan) registration. IDT, Texas Instruments and Philips Semiconductors have also submitted to JEDEC a proposed 96 and 114 ball LFBGA pin-out to the JC-40 council and final voting by JEDEC participants is expected by the end of 1998.

#### 3.5 Evaluation Units

For evaluation units, contact authorized distributors or for more information refer to the following URLs:

Integrated Device Technology URL: <a href="http://www.idt.com">http://www.idt.com</a>

Philips Semiconductors URL: <a href="http://www.philipslogic.com">http://www.philipslogic.com</a>

http://www.semiconductors.philips.com/logic

Texas Instruments URL: http://www.ti.com/sc/lfbga

# 4 LFBGA Package Marking, Shipping Media and Handling.

The following section describes the symbolization of these new LFBGA packages.

## 4.1 Marking

Integrated Device Technology, Philips Semiconductors and Texas Instruments use laser marking to identify the vendor, product number, year and month of fabrication, manufacturing site, lot trace code. Each vendor adopted a specific package designator for the LFBGA packages and is reported in table 4.1:

|           | Integrated Device<br>Technology | Philips<br>Semiconductor | Texas<br>Instruments |

|-----------|---------------------------------|--------------------------|----------------------|

|           |                                 | S                        |                      |

| LFBGA 96  | BF                              | GKE                      | GKE                  |

| LFBGA 114 | BF                              | GKF                      | GKF                  |

Table 4.1 – Vendor package designator

Marking examples for the LVCH32244 device:

IDT Marking:

Part #: LVCH322244A

Date Code, Marking Location Lot number, Assembly Location LVCH32244A Logo X9848Y Xmax10xX

Texas Instruments Marking:

Part #: CH244A

Year, Month, Site Lot trace code

CH244A Logo YMS LLLL

Philips Semiconductors Marking:

Part #: LVCH32244A

Lot number, Site Date Code

Logo LVCH32244A Lot Trace O YYWW

| <b>Device Name</b> | Integrated Device Philips |                | <b>Texas Instruments</b> |

|--------------------|---------------------------|----------------|--------------------------|

|                    | Technology                | Semiconductors |                          |

| LVCH32244A         | LVCH32244A                | LVCH32244A     | CH244A                   |

| LVCH32245A         | LVCH32245A                | LVCH32245A     | CH245A                   |

| LVCH32373A         | LVCH32373A                | LVCH32373A     | CH373A                   |

| LVCH32374A         | LVCH32374A                | LVCH32374A     | CH374A                   |

| ALVCH32501         | ALVCH32501                | ALVCH32501     | ACH501                   |

Table 4.2 – Vendor part number marked on top of package

## 4.2 Tape & Reel

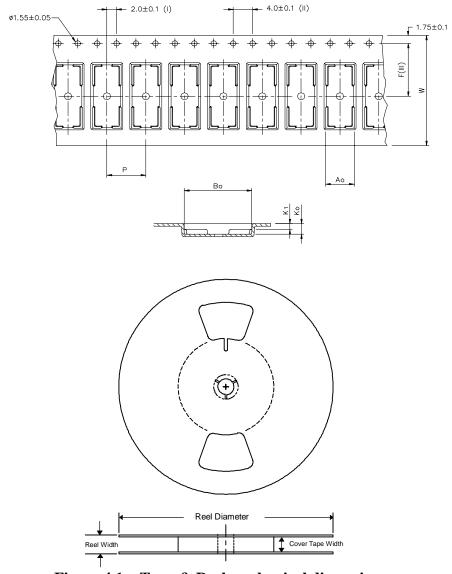

The embossed Tape & Reel method is preferred by automatic pick-and-place machines. Integrated Device Technology, Philips Semiconductors and Texas Instruments offer Tape & Reel packaging for the 96 and 114 ball LFBGA packages. The packaging materials used include Carrier Tape, Cover Tape and a Reel. All material used meets industry guidelines for ESD protection and the design is in full compliance with EIA Standard 481-A, "*Taping of Surface Mount Components for Automatic Placement.*" The dimensions that are of interest to the end-user are tape width (W), pocket pitch (P) and quantity per reel. The figure below illustrates the Tape & Reel design for LFBGA package.

Figure 4.1 – Tape & Reel mechanical dimensions

| Package   | Cover Tape<br>Width (W) | Pocket<br>Pitch (P) | Reel<br>Width | Reel<br>Diamete | Quantity<br>Per Reel |

|-----------|-------------------------|---------------------|---------------|-----------------|----------------------|

|           |                         |                     |               | r               |                      |

| LFBGA 96  | 21.0                    | 8.00                | 24.0          | 330             | 1000                 |

| LFBGA 114 | 21.0                    | 8.00                | 24.0          | 330             | 1000                 |

Table 4.3 – Tape & Reel assembly information

| Package   | Pocket Width (A <sub>0</sub> ) | Pocket<br>Length (B <sub>o</sub> ) | Pocket Depth (K <sub>0</sub> ) | Pedestal<br>Depth (K,) | Hole to<br>Pocket |

|-----------|--------------------------------|------------------------------------|--------------------------------|------------------------|-------------------|

|           | . 0                            |                                    | 1 0                            | <b>1</b>               | Centerline (F)    |

| LFBGA 96  | 5.7                            | 13.7                               | 2.0                            | 1.2                    | 11.5              |

| LFBGA 114 | 5.7                            | 16.2                               | 2.0                            | 1.2                    | 11.5              |

All dimensions are in millimeters

Table 4.4 - Tape & Reel Dimension for LFBGA package.

## 4.3 Sockets, and Socket Manufacturer (Ordering Information)

| Yamaichi Socket numbers: | LFBGA-96   | PN# IC280-096-144 |

|--------------------------|------------|-------------------|

|                          | I FRGA-114 | PN# IC280-114-145 |

Yamaichi Electronics USA, Inc.

2235 Zanker Road

San Jose, CA 95131 Tel: (408) 456-0797

**Loranger Socket numbers**: LFBGA-96 PN# 135055096U6617 LFBGA-114 PN# 169055114U6617

Loranger International Corp.

817 Fourth Avenue

## **5 PCB Manufacturing Considerations**

The following section describes the assembly on PCBs of the LFBGA products.

#### 5.1 Land Pads

The design of the land pads for LFBGA packages on the printed circuit board is critical, if the end-user wants to achieve good manufacturability and optimum reliability. An optimum design is when the diameter of the land pad is equal to the diameter of the package vias; (i.e. the fatigue life of the solder balls is enhanced when the ratio of these dimensions is equal to 1.0).

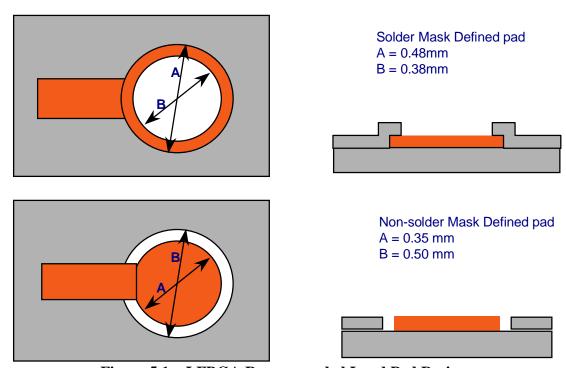

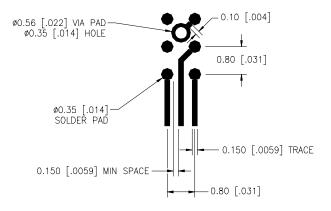

There are two methods of defining land pads on PCB – *solder mask defined* and *non-solder mask defined*. In the *solder mask defined*, the desired land area is defined by the opening of the solder mask. The advantage of this technique is that the land pad size is controlled and the solder mask promotes the adhesion of the copper pad to the PCB. However, the copper pad dimension is larger which makes routing more difficult. In the *non-solder mask defined*, the land area is etched inside the solder mask area. The final land pad dimension is dependent on the accuracy of the copper etching method. The advantage of *non-solder mask defined* over the *solder mask defined* methods is routability (it allows larger trace width/spacing between the solder balls). Figure 5.1 illustrates the land pad dimension for the 96 and 114 ball LFBGA package using the solder mask defined and non-solder mask defined method.

Figure 5.1 – LFBGA Recommended Land Pad Design

## 5.2 Line and Spaces

This section describes the maximum trace width/spacing dimension allowed for 0.8mm ball pitch LFBGA packages with 0.5mm ball diameter. It becomes a challenge to the designers to route this package on a single layer board unless the PCB supplier has fine pitch trace width/spacing capabilities. PCB capabilities are currently in the 4 to 5 mil (100 – 125 • m) trace width/spacing range and using a finer pitch trace width/spacing will increase the overall PCB cost to the end-user. The optimum design is to use current PCB capability, which allows one signal to be routed between the land pads. Using the recommended land pad dimension outlined in section 5.1, the PCB supplier needs to have trace width/spacing capabilities of 4.2 mil (107 • m) and 5.9 mil (150 • m) respectively for the solder mask and non-solder mask defined pads.

Figure 5.2 represents a visual layout as described in section 5.2 and 5.3.

Figure 5.2 – LFBGA Trace Width/Spacing Dimensions (in mm)

#### 5.3 Vias

Via density can be just as challenging to the designers when routing a high-density board. Via density is defined as the number of vias in a particular board area. Using smaller vias increases the via density and the routability of the board by requiring less board space. Holes can be mechanically drilled down to 6 mil (152 • m), however, mechanically drilled holes less than 12 mil (305 • m) begin to add cost to the PCB. To avoid higher PCB costs, other via technology exist (such as laser, punched and plasma-etched) and can be used to form smaller holes. The invention of the microvia has solved many of the problems associated with via density. Micro-vias are often created using a plasma-etched technique, which penetrates layers of dielectric and allows signal routing to the internal layers. Current micro-via technology allows a 2.4 to 4.0 mil (60 - 100 • m) via diameter. Micro-vias can also be designed directly into the land pad thereby obsoleting trace fan-outs.

Table 5.1 summarizes the maximum via diameter that can be used for routing the LFBGA package using recommended land pad dimensions outlined in section 5.1.

|                            | Solder Mask<br>Defined Land Pad | Non-solder Mask<br>Defined Land Pad |

|----------------------------|---------------------------------|-------------------------------------|

| Trace width/spacing        | 0.107mm (4.2 mil)               | 0.150mm (5.9 mil)                   |

| Drill bit diameter         | 0.35 to 0.38 mm                 | 0.23 to 0.25 mm                     |

|                            | (14 to 15 mil)                  | (9 to 10 mil)                       |

| Unplated hole              | 0.35 to 0.38 mm                 | 0.23 to 0.25 mm                     |

|                            | (14 to 15 mil)                  | (9 to 10 mil)                       |

| Finished via size (plated) | 0.30 to 0.33 mm                 | 0.178 to 0.2 mm                     |

|                            | (12 to 13 mil)                  | (7 to 8 mil)                        |

Note: Unplated via diameter assumes a 0.2 mm (8 mil) via land dimension and a 0.1 mm (4 mil) clearance between the via land to the adjacent land pad.

Table 5.1 – Maximum via diameter

## **5.4 Routing**

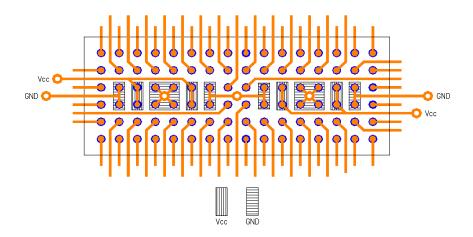

The figures below are examples of a PCB routing with two layers of PCB interconnect:

Note 1: Ground balls are connected together within the PCB.

Figure 5.3 – LFBGA-96 recommended routing

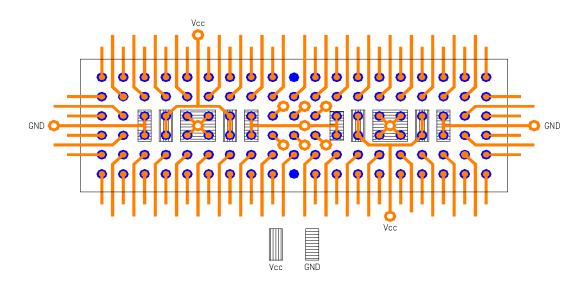

Note 1: Ground balls are connected together within the PCB.

Figure 5.4 – LFBGA-114 recommended routing

## **6 Conclusion**

This joint study by Integrated Device Technology, Philips Semiconductors and Texas Instruments shows the 96 and 114 LBGA packages as the most effective solution for addressing performance issues:

(1) minimal skew due to package layout design; (2) improved thermal power dissipation by taking advantage of the chip overlap over the solder balls; and (3) reduced inductance as functions in these packages take advantage of less capacitance for pin-to-pin inductance, thereby enabling support for high speed applications with close to 2X the bandwidth.

In terms of board integration and miniaturization, these LFBGA packages will reduce board space by up to 65% compared to the corresponding TSSOP package for the same functionality.

Additionally, designers may take advantage of improved reliability and reduced manufacturability costs when the diameter of the PCB land pad is equal to the diameter of package vias as explained in section 5.

With the introduction of the LFBGA by Integrated Device Technology, Philips Semiconductors and Texas Instruments, OEMs are assured of an agreed upon JEDEC standardized package, pin out and availability of the product families and functions to be initially introduced. Integrated Device Technology, Philips Semiconductors and Texas Instruments will continue to work with the market identifying new requirements in terms of product family, and functions.

## **Acknowledgements:**

The Authors would like to thank the following contributors to this Application Note with relevant diagrams and technical information:

Sam Ciani, Ray Purdom, Craig St.Martin from Texas Instruments;

Jeff West, Allen Glaus, Hal Hanson, Joe Schultze, Henk Kloen, Alma Anderson from Philips Semiconductors;

and Tam Vu, Ernie Oregano, Ronnie Tanhueco, from Integrated Device Technology.

AN-Original Revision.