## **White Paper**

# Dual Protocol Transceivers Ease the Design of Industrial Interfaces

#### Introduction

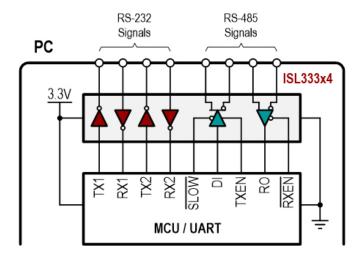

The trend in industrial PC designs towards smaller form factors and more communication versatility is driving the development of modern bus transceivers. New transceivers are favored over legacy designs because of their high level of integration, dual protocol capability supporting the RS-232 and RS-485 standards, and ample configuration features.

This white paper discusses the industry's most commonly used interface standards, RS-232 and RS-485, reviews the functionality and features of a dual protocol transceiver, and discusses multi-protocol application examples, including the industrial PC.

#### The RS-232 Standard

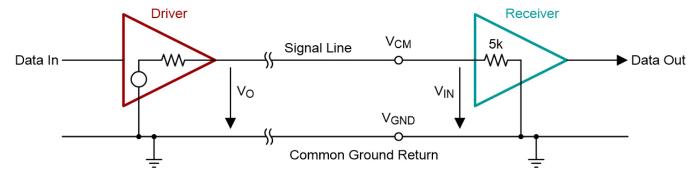

RS-232 is a single-ended full-duplex interface, defined for point-to-point communication only. This means that one driver connects to one receiver, and, vice versa, one receiver connects to one driver. The interface requires a ground wire connection between driver and receiver grounds to provide a common reference for transmit and receive signals (Figure 1).

Figure 1. Single-ended, point-to-point data link

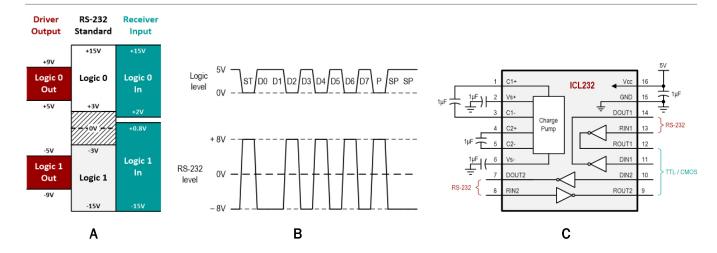

RS-232 tries to gain noise immunity through the use of high signal amplitudes. The standard uses inverse logic and specifies a logic zero, as a bus voltage from +3V to +15V, and a logic one from -3V to -15V (Figure 2). The range from +3V to -3V is undetermined.

Figure 2. RS-232 signal levels (A), their conversion from logic into bus signals (B), and an RS-232 transceiver with integrated charge-pump (C)

Most of today's RS-232 designs use one or two data channels, with each channel consisting of a transmit and receive signal pair. Transceivers providing two channels can utilize one channel for data transmission and the other one for handshake control. Single-channel devices must resort to software flow control.

The RS-232 standard specifies a maximum signal rate of up to 19.8kbps and a maximum slew rate of 30V/µs. However, by reducing the bus voltage amplitudes, modern transceivers can support data rates of up to 1Mbps without violating the slew rate specification. Although not specified, the maximum cable length is limited to around 30m.

#### The RS-485 Standard

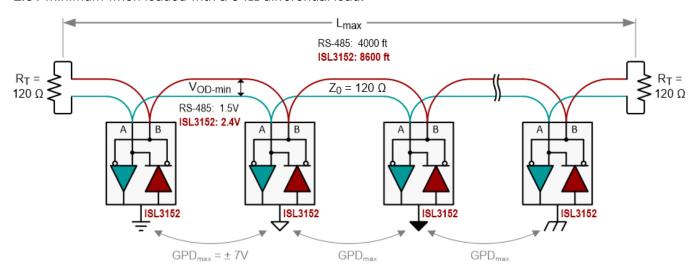

Developed in the early 1980's, RS-485 remains a drastically improved standard for robust data transmission in noisy environments and across long distances. The standard utilizes differential signaling across a signal pair of two conductors, A and B. It specifies a differential bus voltage swing between the two conductors of 1.5V minimum when loaded with a  $54\Omega$  differential load.

Figure 3. Typical RS-485 network with daisy-chained bus nodes and terminated cable ends

RS-485 supports networking of up to 32 unit-loads via a multipoint bus topology. Bus nodes are daisy-chained (Figure 3) to one another through twisted pair cable. The recommended characteristic cable impedance of  $120\Omega$  requires termination resistors at both cable ends, whose values should match the cable impedance.

As the receiver inputs are internally referenced to ground, a separate ground connection between drivers and receivers is not required. This is, as long as the receiver input voltages do not exceed the specified common-mode voltage range of -7V to +12V.

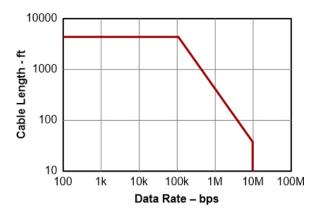

RS-485 supports cable lengths up to 4000ft (1200m) and data rates up to 10Mbps, but not simultaneously. The maximum applicable cable length for a given data rate follows a conservative *cable-length-versus-data-rate* characteristic, as shown in Figure 4.

Figure 4. RS-485 cable length versus data rate characteristic

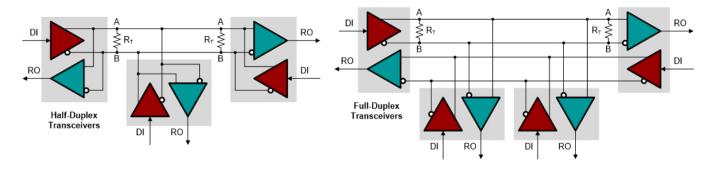

RS-485 supports multipoint topologies where each bus node can either transmit or receive data. Two types of multipoint buses exist: half-duplex and full-duplex (Figure 5). A half-duplex bus uses two wires across, where one node may transmit data while another node receives data. In a full-duplex bus, two signal pairs (four wires) are used. One pair connects the driver of the master node to the receivers of multiple slave nodes, and the other pair connects the drivers of the slave nodes to the receiver of the master node. This topology allows the master to either broadcast data to all slaves or address a specific slave node, while simultaneously receiving data from the slave nodes, one slave at a time. A full-duplex bus increases data throughput but is substantially more expensive than a half-duplex bus due to the higher wiring effort.

Figure 5. Half-duplex and full-duplex multipoint bus topologies in RS-485

### **Dual Protocol Transceivers**

Modern transceivers are capable of supporting the designs of new industrial PCs and the designs of RS-232 to RS-485/RS-422 interface converters. The latter is needed in existing RS-232 equipment, such as legacy PCs, instrumentation equipment, and industrial machinery, where interfaces must either be connected to a single network, or be extended over long distances.

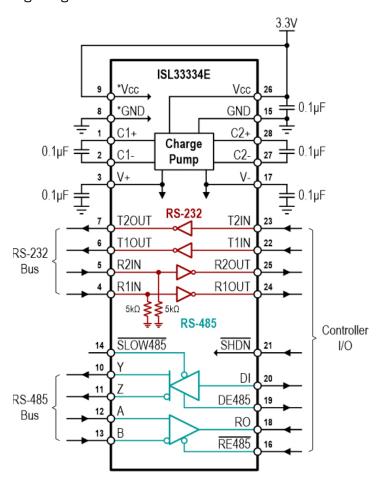

Figure 6 shows the block diagram of a dual protocol transceiver. The device incorporates two RS-232 transmit and receive channels and one full-duplex RS-485 transceiver. Notice the transceiver's flow-through pin-out with bus pins on one side and logic pins on the other. This allows for easy routing of signal traces to the local controller and presents a great advantage over legacy transceivers (as shown in Figure 3), whose pin-outs require the crossing of signal traces from the bus to the controller side and vice versa.

Figure 6. Dual protocol transceiver incorporating one RS-485 and two RS-232 transceivers

When operating the bus systems independently, each RS-232 port can support data rates of up to 400kbps without exceeding the specified slew rate maximum.

The RS-485 section allows for the selection of a 20Mbps high-speed mode and a 115kbps slew rate limited mode via the /SLOW485 pin. In the high-speed mode the driver output is not slew rate limited. This mode should only be applied for distances shorter than 100ft (30m). The high-speed mode also requires the implementation of termination resistors at both cable ends, where the resistor values must match the characteristic cable impedance of either  $120\Omega$  for RS-485 cable or  $100\Omega$  for CAT-5 cable.

Modern transceivers must be able to operate efficiently at low supply voltage. This is accomplished through an optimized charge pump design. The charge pump in Figure 6 creates the bipolar power supplies (V+, V-) for the RS-232 drivers, while only requiring four small  $0.1\mu F$  capacitors. Two capacitors are used for the actual charge pump action converting the initial 3.3V at Vcc into +5V for V+ and -5.3V for V-. The other two capacitors are used for buffering V+ and V- to ensure sufficient supply current for the RS-232 driver during switching action.

While total transceiver supply current is less than 4mA, further power savings can be achieved by driving the entire chip into a shut-down mode. This is accomplished by pulling the /SHDN pin low. In shut-down mode, charge pump operation ceases, and the remaining supply current only consists of the leakage currents flowing into the logic inputs. Thus, total leakage current depends on the device configuration but can be as low as 40µA.

When re-enabling the device by taking /SHDN high, the charge pump takes up to 25µs to stabilize. RS-232 communication is not possible during this time. Since the charge pump does not supply the RS-485 transceiver, RS-485 communication can start 2µs after /SHDN was taken high. This timing is much faster than in legacy transceivers which require the charge pump for all modes of operation.

# **Multi-Protocol Applications**

The integration of one RS-485 and two RS-232 transceivers into one IC makes the interface design of an industrial PC extremely versatile as the local controller can either drive the various bus systems independently, or act as an interface converter, as shown in Figure 7. When operated as an RS-232 to RS-485 converter, the RS-232 signals of either channel 1 or channel 2, or both can be converted into logic levels and then transmitted via the RS-485 bus. Using address coding, the controllers on both sides of the RS-485 link can distinguish between two RS-232 data streams.

Figure 7. Networking multiple RS-232 equipment via RS-232 to RS-485 converters

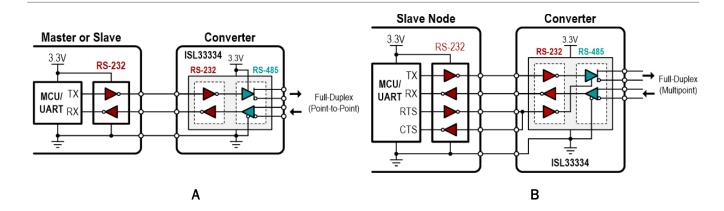

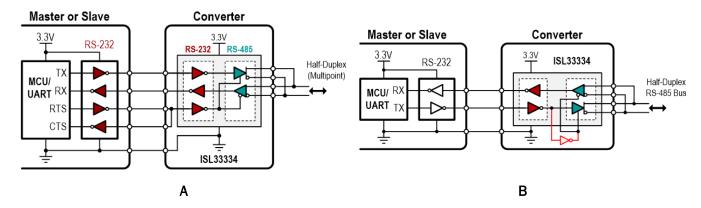

To extend the data link between two RS-232 interfaces via a point-to-point link over long distance, the dual protocol transceiver is configured as a standalone RS-232 to RS-485 converter. Two converters are needed, one at each cable end to convert RS-485 bus signals into RS-232 data and vice versa. The configuration is simple as the enable inputs for driver and receiver can be fixed wired to their respective voltage rails to keep the transceiver constantly active (Figure 8A).

Figure 8. Networking multiple RS-232 equipment via RS-232 to RS-485 converters

Networking multiple RS-232 equipment over a full-duplex RS-485 bus requires a minor configuration change for the converters in slave nodes. The driver and receiver in the master node (PC) can remain active all the time, and so can the receivers in the slave nodes. The drivers in the slave nodes, however, must be closely controlled to prevent two or more slaves from accessing the bus at the same time. For this purpose, the driver of the second RS-232 channel is used to enable and disable the RS-485 driver with the RTS flow control signal (Figure 8B). Note that within the converter the RTS must be looped back to the CTS input of the controller. This is known as a null-modem configuration.

Figure 9. Networking multiple RS-232 equipment via RS-232 to RS-485 converters

Networking multiple RS-232 equipment over a half-duplex RS-485 bus requires the configuration shown in Figure 9A. Here the RTS signal controls the enable functions of both driver and receiver. This configuration is required in all nodes—master and slaves—because a half-duplex bus can only pass data in one direction at a time.

In some equipment the RTS and CTS control signals can be up to 10ms out of sync with the data to be transmitted. In this case it is best to make the enable signals data-driven. This is accomplished by implementing an inverter function between the driver input (DI) and the enable pins (DE485 and /RE485). This puts the transceiver in transmit mode when DI = low, and in receive mode when DI = high. In receive mode the driver outputs are high-impedance, and the low-impedance termination resistors reduce the bus voltage to 0V. Since the RS-485 receiver is a full-failsafe device, all dual protocol transceivers on the bus will indicate a zero bus voltage as a logic high at the receiver output, RO. Thus, toggling a driver output between active low and high-impedance will still generate a low-to-high transition at another receiver's output.

### Conclusion

Modern dual protocol transceivers simplify the design of industrial interfaces due to their high level of integration, combined support of RS-232 and RS-485 protocols, programmable data rates, and power-saving configuration features. To support system engineers in their industrial networking designs, Intersil provides a wide range of fixed and programmable, single and dual channel, multi-protocol transceivers.

# **Next Steps**

- Learn more about the Renesas' dual protocol transceivers

- Download the datasheets

- Order free samples

#### **About Renesas Electronics Corporation**

Renesas Electronics Corporation delivers trusted embedded design innovation with complete semiconductor solutions that enable billions of connected, intelligent devices to enhance the way people work and live—securely and safely. A global leader in microcontrollers, analog, power, and SoC products, Renesas provides the expertise, quality, and comprehensive solutions for a broad range of Automotive, Industrial, Home Electronics, Office Automation and Information Communication Technology applications to help shape a limitless future. Learn more at <a href="mailto:renesas.com">renesas.com</a>

+1 408-432-8888 | © Renesas Electronics America. All rights reserved. Renesas (and design) are trademarks owned by Renesas Electronics Corporation or one of its subsidiaries. All other trademarks mentioned are the property of their respective owners.