Date: May 17, 2024

# RENESAS TECHNICAL UPDATE

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                        | Document<br>No. | TN-RA*-A0112A/E         | Rev.                                                                                                                                                                                                                                                                                                                       | 1.00 |  |

|-----------------------|------------------------------------------------------------------------------------------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Title                 | Remove the description of sub-section [Pin Handling When the Sub-Clock Oscillator Is Not Used] |                 | Information<br>Category | Technical Notification                                                                                                                                                                                                                                                                                                     |      |  |

| Applicable<br>Product | RA2L1 Group<br>RA2E1 Group<br>RA2E3 Group<br>RA2A2 Group<br>RA0E1 Group                        | Lot No.         | Reference<br>Document   | RA2L1 Group User's Manual: Hardware Rev.1.40 (R01UH0853EJ0140) RA2E1 Group User's Manual: Hardware Rev.1.40 (R01UH0852EJ0140) RA2E3 Group User's Manual: Hardware Rev.1.10 (R01UH0992EJ0110) RA2A2 Group User's Manual: Hardware Rev.1.10 (R01UH1005EJ0110) RA0E1 Group User's Manual: Hardware Rev.1.00 (R01UH1005EJ0100) |      |  |

Remove the description of sub-section [Pin Handling When the Sub-Clock Oscillator Is Not Used] and figure of the User's Manual for specific product groups.

# [Before correction of RA2L1, RA2E1 and RA2E3]

# 8.4.2 Pin Handling When the Sub-Clock Oscillator Is Not Used

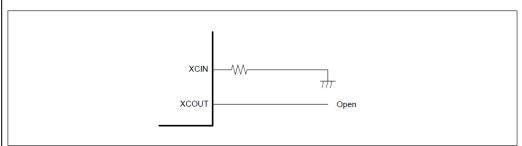

When the sub-clock oscillator is not in use, connect the XCIN pin to VSS through a resistor (to pull VSS down) and leave the XCOUT pin open as shown in Figure 8.10. In addition, if an oscillator is not connected, set the Sub-Clock Oscillator Stop bit (SOSCCR.SOSTP) to 1 to stop the oscillator.

Figure 8.10 Pin handling when the sub-clock oscillator is not used

#### [Before correction of RA2A2]

#### 9.4.2 Pin Handling When the Sub-Clock Oscillator Is Not Used

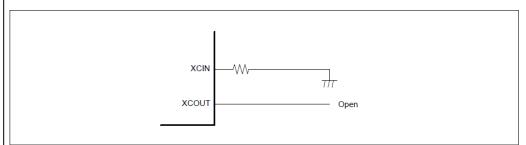

When the sub-clock oscillator is not in use, connect the XCIN pin to VSS through a resistor (to pull VSS down) and leave the XCOUT pin open as shown in Figure 9.10. In addition, if an oscillator is not connected, set the Sub-Clock Oscillator Stop bit (SOSCCR.SOSTP) to 1 to stop the oscillator.

Figure 9.10 Pin handling when the sub-clock oscillator is not used

# [Before correction of RA0E1]

# 8.4.2 Pin Handling When the Sub-clock Oscillator Is Not Used

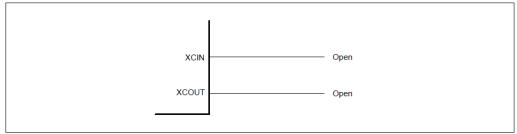

When the sub-clock oscillator is not in use, connect the XCIN pin to VSS through a resistor (to pull VSS down) and leave the XCOUT pin open as shown in Figure 8.9. In addition, if an oscillator is not connected, set Sub Clock Oscillator Switching bit (CMC.SOSEL) is set resonator mode, and the Sub-Clock Oscillator Stop bit (SOSCCR.SOSTP) to 1 to stop the oscillator

Figure 8.9 Pin handling when the sub-clock oscillator is not used

#### [After correction of RA2L1, RA2E1, RA2E3, RA2A2 and RA0E1]

Remove sub-section and figure.

The following table lists the specific sub-sections and figure in the User's Manual that require correction for each product group:

| Product group | Sub-ection & figure number | Section title                                          |

|---------------|----------------------------|--------------------------------------------------------|

| RA2L1         | 8.4.2 and Figure 8.10      | Pin Handling When the Sub-Clock Oscillator Is Not Used |

| RA2E1         | 8.4.2 and Figure 8.10      | Pin Handling When the Sub-Clock Oscillator Is Not Used |

| RA2E3         | 8.4.2 and Figure 8.10      | Pin Handling When the Sub-Clock Oscillator Is Not Used |

| RA2A2         | 9.4.2 and Figure 9.10      | Pin Handling When the Sub-Clock Oscillator Is Not Used |

| RA0E1         | 8.4.2 and Figure 8.9       | Pin Handling When the Sub-Clock Oscillator Is Not Used |

Date: May 17, 2024