# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                    |                    | Docum<br>No.                                            |                                              | TN-RA*-A01324          | √E                  | Rev.                             | 1.00  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------|----------------------------------------------|------------------------|---------------------|----------------------------------|-------|--|--|

| Title                 | RA0E1 Description in the User's Manual: Hard<br>Rev.1.00 Changed.                          | ware               | Informa<br>Categ                                        |                                              | Technical Notification |                     |                                  |       |  |  |

|                       |                                                                                            | Lot No.            |                                                         |                                              |                        |                     |                                  |       |  |  |

| Applicable<br>Product | RA0E1 Group                                                                                | All                | Reference<br>Document RA0E1 Group Us<br>Rev.1.00 (R01U⊢ |                                              |                        |                     |                                  | ware  |  |  |

| This documen          | t describes misstatements found in the RA0E1 L                                             | Jser's Mar         | nual: Hard                                              | ware F                                       | Rev. 1.00 (R01UH10     | 40E                 | J0100).                          |       |  |  |

| Corrections           |                                                                                            |                    |                                                         |                                              |                        |                     |                                  |       |  |  |

|                       | Applicable Item                                                                            |                    | plicable<br>Page                                        |                                              | Contents               | (                   | Pages in<br>documen<br>correctio | t for |  |  |

| Table 5.5 Sta         | ates of LOCO when a reset occurs                                                           | Page               | 60                                                      | Inco<br>revis                                | rrect descriptions     | Р                   | age 2                            |       |  |  |

| Figure 9.1 Lo         | ow power mode transitions                                                                  | Page               | 105                                                     |                                              | rrect descriptions     | P                   | age 3                            |       |  |  |

| Table 11.1 IC         | CU specifications                                                                          | Page               | 124                                                     | Inco<br>revis                                | rrect descriptions     | Page 4,<br>Page 5   |                                  |       |  |  |

| 13.2 Usage I          | Notes                                                                                      | Page               | 152                                                     |                                              | rrect descriptions     | Page 6              |                                  |       |  |  |

| 17.1 Overvie          | 9W                                                                                         | Page               | 207                                                     |                                              | rrect descriptions     | Page 7,<br>Page 8   |                                  |       |  |  |

| 21.3.22 SO1           | : Serial Output Register 1                                                                 | Page               | 361                                                     |                                              | rrect descriptions     | Page 9,<br>Page 10  |                                  |       |  |  |

| 25.2.3 ADM2           | 2: A/D Converter Mode Register 2                                                           | Page               | 574                                                     |                                              | rrect descriptions     | Page 11             |                                  |       |  |  |

| 25.2.6 ADS:           | Analog Input Channel Specification Register                                                | Page               | 578                                                     | Inco<br>revis                                | rrect descriptions     | Page 12             |                                  |       |  |  |

|                       | Example of software trigger wait mode (select mod<br>version mode) operation timing        | <sup>e,</sup> Page | 587                                                     | Inco<br>revis                                | rrect descriptions     | P                   | age 13                           |       |  |  |

|                       | Mode Function                                                                              | Page               | 605                                                     |                                              | rrect descriptions     | P                   | age 14                           |       |  |  |

| 25.7.1 A/D C          | Conversion by Inputting a Software Trigger                                                 | Page<br>Page       |                                                         |                                              | rrect descriptions     |                     | age 15<br>age 16                 |       |  |  |

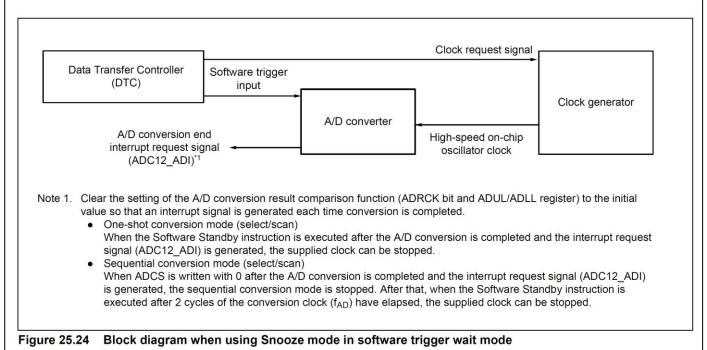

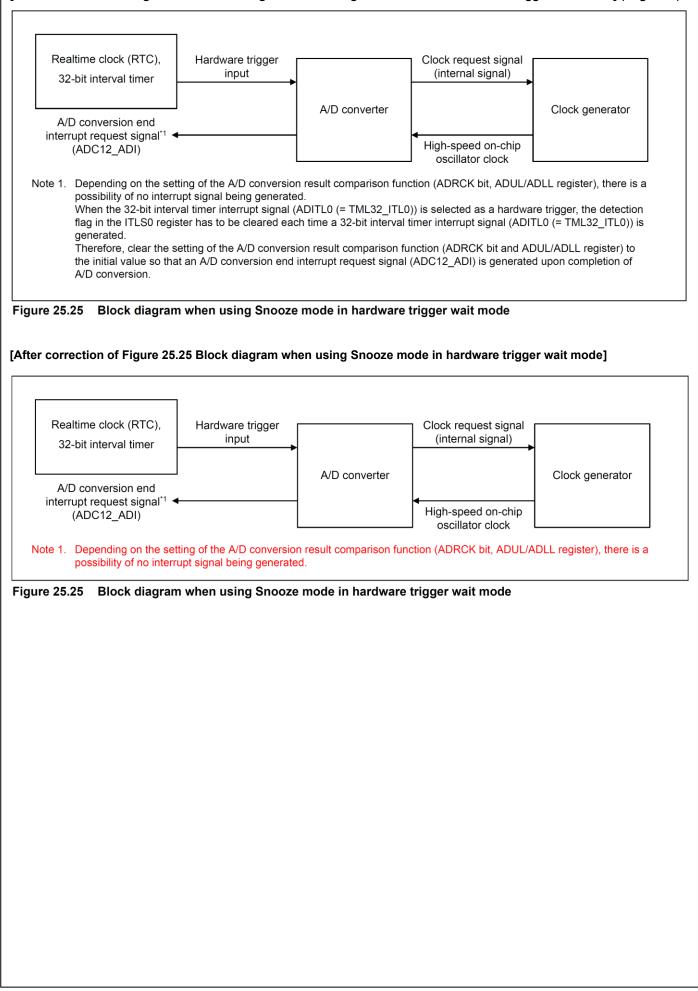

|                       | 5 Block diagram when using Snooze mode gger wait mode                                      |                    |                                                         |                                              | rrect descriptions     |                     | age 17                           |       |  |  |

| Table 28.5 M          | Apping for the extra bit of the startup area selectic setting (address (P/E) :0x0000_0010) | n Page             | 633                                                     |                                              | rrect descriptions     | P                   | age 18                           |       |  |  |

| Table 28.6            | Mapping for the extra bit of the access windo<br>program (address (P/E) :0x0000_0010)      | w Page             | 633                                                     |                                              | rrect descriptions     | P                   | age 19                           |       |  |  |

|                       | Rn : Part Numbering Register n (n = 0 to 3)                                                | Page               | 641                                                     |                                              | rrect descriptions     | Page 20,            |                                  |       |  |  |

| Table 28.15           | Basic functions                                                                            | Page               | 644                                                     |                                              | rrect descriptions     | Page 21<br>Page 22  |                                  |       |  |  |

| 29 True Ran           | dom Number Generator (TRNG)                                                                | Page               | Page 666                                                |                                              | rrect descriptions     | Page 23             |                                  |       |  |  |

| Table 31.1 A          | bsolute maximum ratings                                                                    | Page               | 668                                                     | revised<br>Incorrect descriptions<br>revised |                        |                     | Page 24,<br>Page 25              |       |  |  |

| Table 31.11           | I/O other characteristics                                                                  | Page<br>Page       |                                                         |                                              | rrect descriptions     | Page 26,<br>Page 27 |                                  |       |  |  |

| Table 31.12           | Operating and standby current (1) (2 of 2)                                                 | Page               |                                                         |                                              | rrect descriptions     | Page 28<br>Page 29  |                                  |       |  |  |

| h                     |                                                                                            |                    |                                                         |                                              | rrect descriptions     | 1                   | J = = •                          |       |  |  |

Table 31.16 Reset timing (2 of 2)

Document Improvement

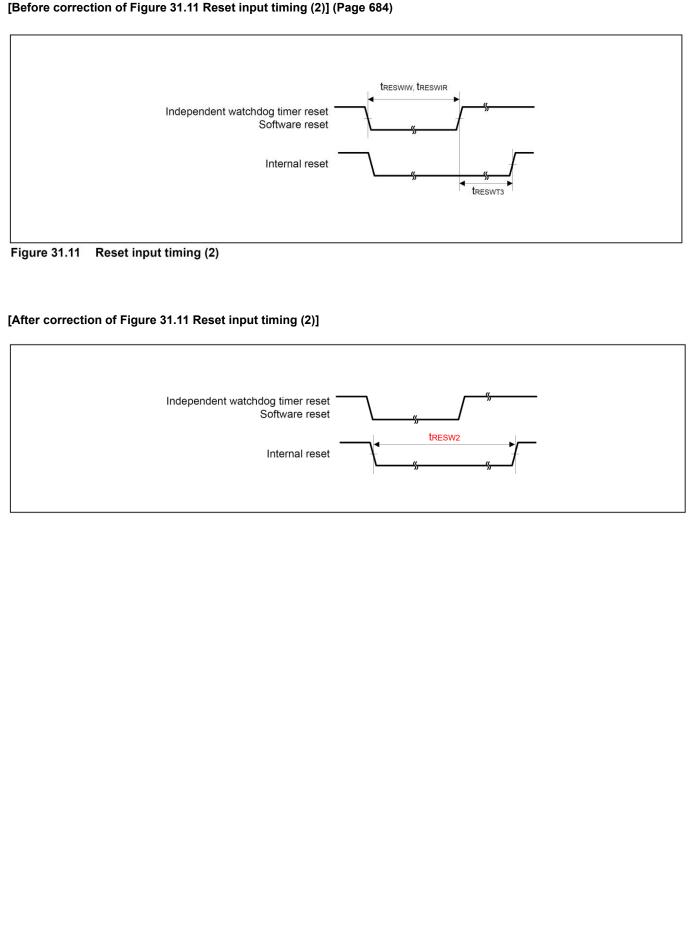

Figure 31.11 Reset input timing (2)

Table 31.46 LVD1 characteristics (2 of 2)

The above corrections will be made for the next revision of the User's Manual: Hardware.

Page 684

Page 684

Page 719

Page 30

Page 31

Page 32

Incorrect descriptions

Incorrect descriptions

Incorrect descriptions

revised

revised

revised

#### [Before correction of Table 5.5 States of LOCO when a reset occurs] (Page 60)

#### Table 5.5 States of LOCO when a reset occurs

|                        |  | Reset source          |       |  |  |  |

|------------------------|--|-----------------------|-------|--|--|--|

|                        |  | POR/LVD0/LVD1         | Other |  |  |  |

| LOCO Enable or disable |  | Initialized to enable |       |  |  |  |

#### [After correction of Table 5.5 States of LOCO when a reset occurs]

#### Table 5.5 States of LOCO when a reset occurs

|      | Reset source                                                |                                              |  |  |  |  |

|------|-------------------------------------------------------------|----------------------------------------------|--|--|--|--|

|      | POR/LVD0/LVD1                                               | Other                                        |  |  |  |  |

| LOCO | Initialized to disable. However, during the value of LCSTP. | WDT operation, LOCO oscillates regardless of |  |  |  |  |

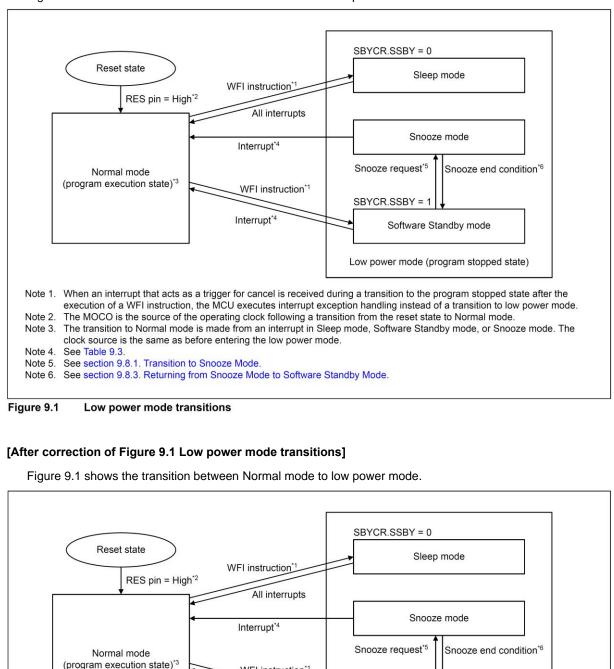

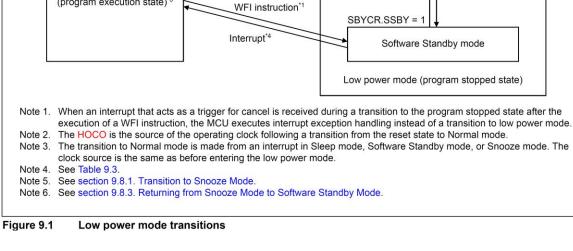

#### [Before correction of Figure 9.1 Low power mode transitions] (Page 105)

Figure 9.1 shows the transition between Normal mode to low power mode.

#### [Before correction of Table 11.1 ICU specifications] (Page 124)

# 11. Interrupt Controller Unit (ICU)

## 11.1 Overview

The Interrupt Controller Unit (ICU) controls which event signals are linked to the Nested Vector Interrupt Controller (NVIC), and the Data Transfer Controller (DTC) modules. The ICU also controls non-maskable interrupts.

Table 11.1 lists the ICU specifications, Figure 11.1 shows a block diagram, and Table 11.2 lists the I/O pins.

#### Table 11.1 ICU specifications

| ltem                   |                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maskable<br>interrupts | Peripheral function interrupts        | Interrupts from peripheral modules     Number of sources: 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | External pin interrupts               | <ul> <li>Interrupt detection on falling edge, rising edge, rising and falling edges. One of these detection methods can be set for each source</li> <li>6 sources, with interrupts from IRQi (i = 0 to 5) pins.</li> </ul>                                                                                                                                                                                                                                                                                                                         |

|                        | Interrupt requests to CPU (NVIC)      | 39 interrupt requests are output to NVIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | DTC control                           | <ul> <li>The DTC can be activated using interrupt sources<sup>*1</sup></li> <li>The method for selecting an interrupt source is the same as that of the interrupt request to NVIC.</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

| Non-<br>maskable       | NMI pin interrupt                     | <ul> <li>Interrupt from the NMI pin</li> <li>Interrupt detection on falling edge or rising edge</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| interrupts*2           | IWDT underflow/refresh error*3        | Interrupt on an underflow of the down-counter or occurrence of a refresh error                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | Low voltage detection 1 <sup>*3</sup> | Voltage monitor 1 interrupt of the voltage monitor 1 circuit (LVD_LVD1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | RPEST                                 | Interrupt on SRAM parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Low power r            | nodes                                 | <ul> <li>Sleep mode: return is initiated by non-maskable interrupts or any other interrupt source</li> <li>Software Standby mode: return is initiated by non-maskable interrupts. Interrupt can be selected in the SBYEDCRn register.</li> <li>Snooze mode: return is initiated by non-maskable interrupts. Interrupt can be selected in the SBYEDCRn register.</li> <li>See section 11.2.14. SBYEDCR0 : Software Standby/Snooze End Control Register 0 and section 11.2.15. SBYEDCR1 : Software Standby/Snooze End Control Register 1.</li> </ul> |

Note 1. For the DTC activation sources, see Table 11.5.

Note 2. Non-maskable interrupts can be enabled only once after a reset release.

Note 3. These non-maskable interrupts can also be used as maskable interrupts. When used as maskable interrupts, do not change the value of the NMIER register from the reset state. To enable voltage monitor 1 interrupts, set the LVD1CR1.IRQSEL bits to 1.

#### [After correction of Table 11.1 ICU specifications]

# 11. Interrupt Controller Unit (ICU)

## 11.1 Overview

The Interrupt Controller Unit (ICU) controls which event signals are linked to the Nested Vector Interrupt Controller (NVIC), and the Data Transfer Controller (DTC) modules. The ICU also controls non-maskable interrupts.

Table 11.1 lists the ICU specifications, Figure 11.1 shows a block diagram, and Table 11.2 lists the I/O pins.

#### Table 11.1 ICU specifications

| ltem                   |                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Maskable<br>interrupts | Peripheral function interrupts        | Interrupts from peripheral modules     Number of sources: 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                        | External pin interrupts               | <ul> <li>Interrupt detection on falling edge, rising edge, rising and falling edges. One of these detection methods can be set for each source</li> <li>6 sources, with interrupts from IRQi (i = 0 to 5) pins.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                        | Interrupt requests to CPU (NVIC)      | 39 interrupt requests are output to NVIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                        | DTC control                           | <ul> <li>The DTC can be activated using interrupt sources<sup>*1</sup></li> <li>The method for selecting an interrupt source is the same as that of the interrupt request to NVIC.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Non-<br>maskable       | NMI pin interrupt                     | <ul> <li>Interrupt from the NMI pin</li> <li>Interrupt detection on falling edge or rising edge</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| interrupts*2           | IWDT underflow/refresh error*3        | Interrupt on an underflow of the down-counter or occurrence of a refresh error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                        | Low voltage detection 1 <sup>*3</sup> | Voltage monitor 1 interrupt of the voltage monitor 1 circuit (LVD_LVD1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                        | RPEST                                 | Interrupt on SRAM parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Low power r            | nodes                                 | <ul> <li>Sleep mode: return is initiated by non-maskable interrupts or any other interrupt source</li> <li>Software Standby mode: return is initiated by non-maskable interrupts or any other interrupt source. Interrupt can be selected in the SBYEDCRn register.</li> <li>Snooze mode: return is initiated by non-maskable interrupts or any other interrupt source. Interrupt can be selected in the SBYEDCRn register.</li> <li>See section 11.2.14. SBYEDCR0 : Software Standby/Snooze End Control Register 0 and section 11.2.15. SBYEDCR1 : Software Standby/Snooze End Control Register 1.</li> </ul> |  |  |  |  |  |  |

Note 1. For the DTC activation sources, see Table 11.5.

Note 2. Non-maskable interrupts can be enabled only once after a reset release.

Note 3. These non-maskable interrupts can also be used as maskable interrupts. When used as maskable interrupts, do not change the value of the NMIER register from the reset state. To enable voltage monitor 1 interrupts, set the LVD1CR1.IRQSEL bits to 1.

#### 13.2 Usage Notes

#### 13.2.1 Notes on the Use of a Debugger

The memory cannot be debugged if the FRP is enabled. Disable the flash read protection when debug a program, OCD debug only valid when OFS1.FRPDIS bit is 1.

#### 13.2.2 **Compiler Settings**

The FRP is a kind of execute-only memory (XOM). Since data in a protected region is not readable, a protected region cannot have constant data such as literal pool. Therefore, appropriate compiler settings are required.

## [After correction of 13.2 Usage Notes]

#### 13.2 Usage Notes

#### 13.2.1 Notes on the Use of a Debugger

The memory cannot be debugged if the FRP is enabled. Disable the flash read protection when debug a program, OCD debug only valid when OFS1.FRPDIS bit is 1.

#### **Compiler Settings** 13.2.2

The FRP is a kind of execute-only memory (XOM). Since data in a protected region is not readable, a protected region cannot have constant data such as literal pool. Therefore, appropriate compiler settings are required.

#### Protection of OFS1 Register 13.2.3

Because overwriting OFS1.FRPS[5:0], OFS1.FRPE[5:0], or OFS1.FRPDIS bits can disable the protection of the FRP, OFS1 register (address =  $0x0000_0404$ ) must be protected by the access window function. However, setting the access window function, which includes setting AWS.FSPR bit to 0, also disables changing AWS.BTFLG and FISR.SAS[1:0] bits used for the startup area select function. Therefore, the startup area select function is not available when using the FRP function. See section 28.5.2. Startup Area Select for the startup area select function and section 28.5.3. Protection by Access Window for

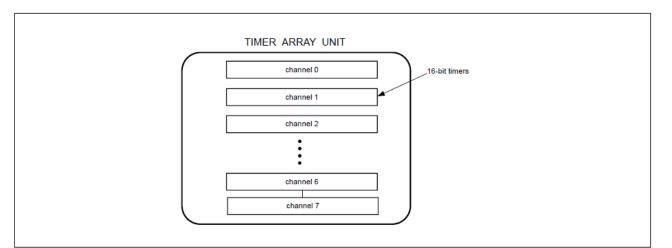

#### [Before correction of 17.1 Overview] (Page 207)

# 17. Timer Array Unit (TAU)

### 17.1 Overview

The timer array unit has eight 16-bit timers.

Each 16-bit timer is called a channel and can be used as an independent timer. In addition, two or more channels can be used to create a high-resolution timer.

Figure 17.1 shows the channel configuration per unit in timer array unit.

#### Figure 17.1 Channel configuration per unit

It is possible to use the 16-bit timer of channels 1 and 3 of unit 0 as two 8-bit timers (higher and lower). The functions that can use channels 1 and 3 as 8-bit timers are as follows:

- Interval timer (upper or lower 8-bit timer) and square wave output (lower 8-bit timer only)

- External event counter (lower 8-bit timer only)

- Delay counter (lower 8-bit timer only)

Channel 7 of unit 0 can be used to realize LIN-bus communication operating in combination with UART2 of the serial array unit.

The peripheral module clock (PCLKB) is equal to the system clock (ICLK) in RA0E1.

Table 17.1 lists the TAU functions and Figure 17.2 to Figure 17.11 show each functional image.

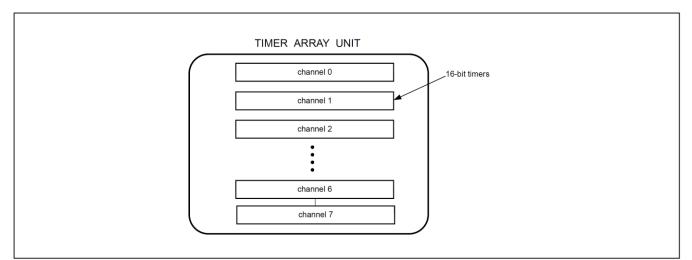

#### [After correction of 17.1 Overview]

# 17. Timer Array Unit (TAU)

# 17.1 Overview

The timer array unit has eight 16-bit timers.

Each 16-bit timer is called a channel and can be used as an independent timer. In addition, two or more channels can be used to create a high-resolution timer.

Figure 17.1 shows the channel configuration per unit in timer array unit.

## Figure 17.1 Channel configuration per unit

It is possible to use the 16-bit timer of channels 1 and 3 of unit 0 as two 8-bit timers (higher and lower). The functions that can use channels 1 and 3 as 8-bit timers are as follows:

- Interval timer (upper and lower 8-bit timer) and square wave output (lower 8-bit timer only)

- External event counter (lower 8-bit timer only)

- Delay counter (lower 8-bit timer only)

Channel 7 of unit 0 can be used to realize LIN-bus communication operating in combination with UART2 of the serial array unit.

The peripheral module clock (PCLKB) is equal to the system clock (ICLK) in RA0E1.

Table 17.1 lists the TAU functions and Figure 17.2 to Figure 17.11 show each functional image.

#### [Before correction of 21.3.22 SO1: Serial Output Register 1] (Page 361)

| 21.3.22 SO1: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Serial O                         | utput F | Registe | r 1 |    |    |   |   |   |   |   |   |   |   |   |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|---------|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| Base address:<br>Offset address:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Base address: SAU1 = 0x400A_2200 |         |         |     |    |    |   |   |   |   |   |   |   |   |   |   |

| Oliset address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0X0120                           |         |         |     |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit position:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                               | 14      | 13      | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Bit field:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit field: CKO[1:0] SO[1:0]      |         |         |     |    |    |   |   |   |   |   |   |   |   |   |   |

| Value after reset:         0         0         0         1         1         1         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th="">         1         <th1< th=""></th1<></th1<> |                                  |         |         |     |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit   | Symbol   | Function                                                                                                   | R/W |

|-------|----------|------------------------------------------------------------------------------------------------------------|-----|

| 1:0   | SO[1:0]  | Serial Data Output of Channel n<br>0: Serial data output value is 0<br>1: Serial data output value is 1    | R/W |

| 7:2   | —        | These bits are read as 0. The write value should be 0.                                                     | R/W |

| 9:8   | CKO[1:0] | Serial Clock Output of Channel n<br>0: Serial clock output value is 0<br>1: Serial clock output value is 1 | R/W |

| 15:10 | —        | These bits are read as 0. The write value should be 0.                                                     | R/W |

The SO1 is a buffer register for serial output of each channel of serial array unit 1.

The value of the SO[n] bit of this register is output from the serial data output pin of channel n.

The value of the CKO[n] bit of this register is output from the serial clock output pin of channel n.

The SO[n] bit of this register can be rewritten by software only when serial output is disabled (SOE1.SOE[n] = 0). When

serial output is enabled (SOE1.SOE[n] = 1), rewriting by software is ignored, and the value of the register can be changed only by a serial communication operation.

The CKO[n] bit of this register can be rewritten by software only when the channel operation is stopped (SE1.SE[n] = 0).

While channel operation is enabled (SE1.SE[n] = 1), rewriting by software is ignored, and the value of the CKO[n] bit can be changed only by a serial communication operation.

To use the pin for serial interface as a port function pin, set the corresponding CKO[n] and SO[n] bits to 1.

#### [After correction of 21.3.22 SO1: Serial Output Register 1]

| 21.3.22 SO1: S     | Serial C                                         | output F | Registe | r 1 |    |    |   |   |   |   |   |   |   |   |   |   |  |

|--------------------|--------------------------------------------------|----------|---------|-----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| Base address:      | Base address: SAU1 = 0x400A_2200                 |          |         |     |    |    |   |   |   |   |   |   |   |   |   |   |  |

| Offset address:    | 0x0128                                           |          |         |     |    |    |   |   |   |   |   |   |   |   |   |   |  |

| Bit position:      | 15                                               | 14       | 13      | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| Bit field:         | Bit field: CKO[1:0] SO[1:0]                      |          |         |     |    |    |   |   |   |   |   |   |   |   |   |   |  |

| Value after reset: | Value after reset: 0 0 0 0 0 0 1 1 0 0 0 0 0 1 1 |          |         |     |    |    |   |   |   |   |   |   |   |   |   |   |  |

| Bit   | Symbol   | Function                                                                                                   | R/W |

|-------|----------|------------------------------------------------------------------------------------------------------------|-----|

| 1:0   | SO[1:0]  | Serial Data Output of Channel n<br>0: Serial data output value is 0<br>1: Serial data output value is 1    | R/W |

| 7:2   | —        | These bits are read as 0. The write value should be 0.                                                     | R/W |

| 9:8   | CKO[1:0] | Serial Clock Output of Channel n<br>0: Serial clock output value is 0<br>1: Serial clock output value is 1 | R/W |

| 15:10 | —        | These bits are read as 0. The write value should be 0.                                                     | R/W |

The SO1 is a buffer register for serial output of each channel of serial array unit 1.

The value of the SO[n] bit of this register is output from the serial data output pin of channel n.

The value of the CKO[n] bit of this register is output from the serial clock output pin of channel n.

The SO[n] bit of this register can be rewritten by software only when serial output is disabled (SOE1.SOE[n] = 0). When

serial output is enabled (SOE1.SOE[n] = 1), rewriting by software is ignored, and the value of the register can be changed only by a serial communication operation.

The CKO[n] bit of this register can be rewritten by software only when the channel operation is stopped (SE1.SE[n] = 0).

While channel operation is enabled (SE1.SE[n] = 1), rewriting by software is ignored, and the value of the CKO[n] bit can be changed only by a serial communication operation.

To use the pin for serial interface as a port function pin, set the corresponding CKO[n] and SO[n] bits to 1.

#### [Before correction of 25.2.3 ADM2: A/D Converter Mode Register 2] (Page 574)

## AWC bit (Specification of the Snooze Mode)

This bit is used for specification of the Snooze mode.

When there is a hardware trigger signal in the Software Standby mode, the Software Standby mode is exited, and A/D conversion is performed without operating the CPU (the Snooze mode).

- When using the Snooze mode function, set AWC to 0 in software trigger wait mode, and set AWC to 1 in hardware trigger wait mode.

- Using the Snooze mode function in the software trigger no-wait mode or hardware trigger no-wait mode is prohibited.

- Using the Snooze mode function in the software trigger no-wait mode, software trigger wait mode, or hardware trigger no-wait mode is prohibited..

- When using the Snooze mode function, specify a hardware trigger interval of at least "shift time to Snooze mode<sup>\*1</sup> + conversion start time + A/D power supply stabilization wait time + A/D conversion time + 2 PCLKB clock cycles + 5 μs".

- Even when using Snooze mode, be sure to set the AWC bit to 0 in normal operation and change it to 1 just before shifting to Software Standby mode.

Also, be sure to change the AWC bit to 0 after returning from Software Standby mode to normal operation. If the AWC bit is left set to 1, A/D conversion will not start normally in spite of the subsequent Snooze mode or normal operation.

Note 1. Refer to Table 31.21 in section 31.4.2. Wakeup Time.

#### [After correction of 25.2.3 ADM2: A/D Converter Mode Register 2]

## AWC bit (Specification of the Snooze Mode)

This bit is used for specification of the Snooze mode.

When there is a hardware trigger signal in the Software Standby mode, the Software Standby mode is exited, and A/D conversion is performed without operating the CPU (the Snooze mode).

- When using the Snooze mode function, set AWC to 1 in hardware trigger wait mode.

- Using the Snooze mode function in the software trigger no-wait mode, software trigger wait mode, or hardware trigger no-wait mode is prohibited.

- Using the Snooze mode function in the sequential conversion mode and hardware trigger wait mode is prohibited.

- When using the Snooze mode function, specify a hardware trigger interval of at least "shift time to Snooze mode<sup>\*1</sup> + conversion start time + A/D power supply stabilization wait time + A/D conversion time + 2 PCLKB clock cycles + 5 µs".

- Even when using Snooze mode, be sure to set the AWC bit to 0 in normal operation and change it to 1 just before shifting to Software Standby mode.

Also, be sure to change the AWC bit to 0 after returning from Software Standby mode to normal operation.

If the AWC bit is left set to 1, A/D conversion will not start normally in spite of the subsequent Snooze mode or normal operation.

Note 1. Refer to Table 31.21 in section 31.4.2. Wakeup Time.

# [Before correction of 25.2.6 ADS: Analog Input Channel Specification Register] (Page 578) (Omitted) Note: Rewrite the value of the ADISS bit while conversion is stopped (ADCS = 0, ADCE = 0). Note. If using VREFH0 as the '+' side reference voltage of the A/D converter, do not select AN000 as an A/D conversion channel. Note: If using VREFL0 as the '-' side reference voltage of the A/D converter, do not select AN001 as an A/D conversion channel. Note: When the setting of the ADISS bit is 1, the internal reference voltage cannot be used for the '+' side reference voltage. After the ADISS bit is set to 1, the initial conversion result cannot be used. For the setting flow, see section 25.6.5. Example of Using the ADC12 when Selecting the Temperature Sensor Output Voltage or Internal Reference Voltage, and Software Trigger No-wait Mode and One-shot Conversion Mode. For details about the internal reference voltage, see section 31, Electrical Characteristics $T_A = -40$ to $+105^{\circ}$ C. Note: Do not set the ADISS bit to 1 when shifting to Software Standby mode, or to Sleep mode while the CPU is operating on the subsystem clock. When the ADISS bit is set to 1, the A/D converter reference voltage current (IADREF) indicated in section 31.3.2. Operating and Standby Current will be added. When the setting of the ADISS bit is 1, the hardware trigger wait mode and one-shot conversion mode cannot be Note: used at the same time. [After correction of 25.2.6 ADS: Analog Input Channel Specification Register] (Omitted) Rewrite the value of the ADISS bit while conversion is stopped (ADCS = 0, ADCE = 0). Note: Note: If using VREFH0 as the '+' side reference voltage of the A/D converter, do not select AN000 as an A/D conversion channel. Note: If using VREFL0 as the '-' side reference voltage of the A/D converter, do not select AN001 as an A/D conversion channel. Note: When the setting of the ADISS bit is 1, the internal reference voltage cannot be used for the '+' side reference voltage. After the ADISS bit is set to 1, the initial conversion result cannot be used. For the setting flow, see section 25.6.5. Example of Using the ADC12 when Selecting the Temperature Sensor Output Voltage or Internal Reference Voltage, and Software Trigger No-wait Mode and One-shot Conversion Mode. For details about the internal reference voltage, see section 31, Electrical Characteristics T<sub>A</sub> = -40 to +105°C. Note: Do not set the ADISS bit to 1 when shifting to Software Standby mode, or to Sleep mode while the CPU is operating on the subsystem clock. When the ADISS bit is set to 1, the A/D converter reference voltage current (IADREF) indicated in section 31.3.2. Operating and Standby Current will be added. Note: When the setting of the ADISS bit is 1, the hardware trigger wait mode and one-shot conversion mode cannot be used at the same time. When the setting of the ADISS bit is 1, the software trigger wait mode and one-shot conversion mode cannot be Note: used at the same time.

[Before correction of Figure 25.13 Example of software trigger wait mode (select mode, one-shot conversion mode) operation timing] (Page 587)

|                                                                                                  | <2                                                         | ADCS is set to 1<br>while in the<br>conversion<br>standby state.                                                                                                                    | <3>ADCS is<br>automatically<br>cleared to 0 after<br>conversion ends                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rl I                                       | > ADCS is overwritte<br>with 1 during A/D<br>conversion operat                                                                              | i i                                           | <2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <8> A hardware trig<br>is generated (ar<br>ignored).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | <2> <                                             | 7> ADCS is cleared to 0<br>during A/D conversion<br>operation.                                                                                       |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCS                                                                                             |                                                            | /                                                                                                                                                                                   | ′ <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                          |                                                                                                                                             | /                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6>ADS is rewritten (from<br>AN000 to AN001) du<br>A/D conversion opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ing/                 | 4                                                 |                                                                                                                                                      |