**Customer Notification**

# **VR4181**<sup>TM</sup>

64-/32-Bit Microprocessor

**Operating Precautions**

$\mu$ PD30181GM-66-8ED

Document No. TPS-HE-B-6004-3 Date Published September 2002

© NEC Electronics (Europe) GmbH

#### DISCLAIMER

The related documents in this customer notification may include preliminary versions. However, preliminary versions may not have been marked as such.

The information in this customer notification is current as of its date of publication. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC PRODUCT(S). Not all PRODUCT(S) and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

No part of this customer notification may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this customer notification. NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC PRODUCT(S) listed in this customer notification or any other liability arising from the use of such PRODUCT(S).

No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others. Descriptions of circuits, software and other related information in this customer notification are provided for illustrative purposes of PRODUCT(S) operation and/or application examples only. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

While wherever feasible, NEC endeavors to enhance the quality, reliability and safe operation of PRODUCT(S) the customer agree and acknowledge that the possibility of defects and/or erroneous thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects and/or errors in PRODUCT(S) the customer must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

The customer agrees to indemnify NEC against and hold NEC harmless from any and all consequences of any and all claims, suits, actions or demands asserted against NEC made by a third party for damages caused by one or more of the items listed in the enclosed table of content of this customer notification for PRODUCT(S) supplied after the date of publication.

#### Applicable Law:

The law of the Federal Republic of Germany applies to all information provided by NEC to the Customer under this Operating Precaution document without the possibility of recourse to the Conflicts Law or the law of 5th July 1989 relating to the UN Convention on Contracts for the International Sale of Goods (the Vienna CISG agreement).

Düsseldorf is the court of jurisdiction for all legal disputes arising directly or indirectly from this information. NEC is also entitled to make a claim against the Customer at his general court of jurisdiction.

If the supplied goods/information are subject to German, European and/or North American export controls, the Customer shall comply with the relevant export control regulations in the event that the goods are exported and/or re-exported. If deliveries are exported without payment of duty at the request of the Customer, the Customer accepts liability for any subsequent customs administration claims with respect to NEC.

**Notes**: (1) **NEC** as used in this statement means NEC Corporation and also includes its direct or indirect owned or controlled subsidiaries.

(2) **PRODUCT(S)** means NEC semiconductor products (*NEC semiconductor products* means any semiconductor product developed or manufactured by or for NEC) and/or TOOLS (*TOOLS* means hardware and/or software development tools for NEC semiconductor products developed, manufactured and supplied by NEC and/or hardware and/or software development tools supplied by NEC but developed and/or manufactured by independent 3<sup>rd</sup> Party vendors worldwide as their own product or on contract from NEC)

| (A) | Table of Operating Precautions    5   | ; |

|-----|---------------------------------------|---|

| (B) | Description of Operating Precautions6 | ; |

| (C) | Valid Specification14                 | ŀ |

| (D) | Revision History                      | ; |

## (A) Table of Operating Precautions

|     |                                                 |                      | μ <b>ΡD7030181</b> | GM-66-8ED |

|-----|-------------------------------------------------|----------------------|--------------------|-----------|

| No. | Outline                                         | Rev.                 | V1.3               |           |

|     |                                                 | Rank <sup>Note</sup> | E                  |           |

| 1   | MAIUINTREG access                               | 1                    | ×                  |           |

| 2   | Execution of hibernate / suspend sequence       |                      | ×                  |           |

| 3   | Mode register setting for 64 Mbits SDRAM        |                      | ×                  |           |

| 4   | MEMWR signal behavior at SDRAM access           |                      | ×                  |           |

| 5   | The behavior after RTCRST                       |                      | ×                  |           |

| 6   | Usage of 64 MBit SDRAM I/F (5)                  |                      | ×                  |           |

| 7   | CBR Refresh interval                            |                      | ×                  |           |

| 8   | Burst CBR Refresh before/after self-refresh     |                      | ×                  |           |

| 9   | Execution of wake-up sequence                   |                      | ×                  |           |

| 10  | USB client function                             |                      | ×                  |           |

| 11  | SDRAM burst refresh before Self-refresh         |                      | ×                  |           |

| 12  | DRAM interface in SUSPEND mode                  |                      | ×                  |           |

| 13  | Internal clock in HIBERNATE mode                |                      | X                  |           |

| 14  | Audio -in DMA transfer                          |                      | ×                  |           |

| 15  | Interrupt for DMA transfer                      |                      | ×                  |           |

| 16  | HAL timer operation                             |                      | ×                  |           |

| 17  | RSTSW# recognition during wake-up sequence      | e                    | ×                  |           |

| 18  | DRAM self-refresh in hibernate mode             |                      | ×                  |           |

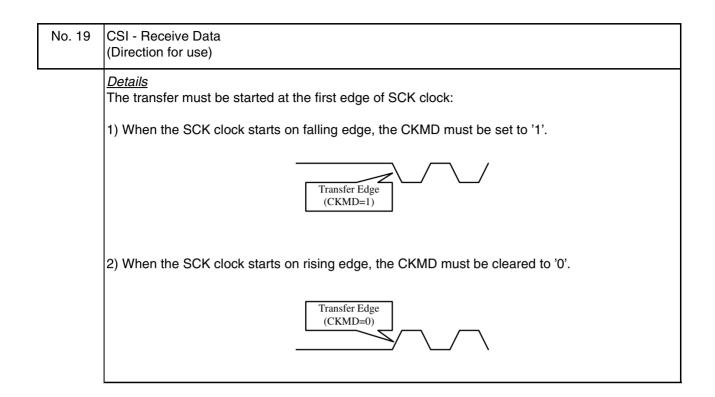

| 19  | CSI - Receive data                              |                      | ×                  |           |

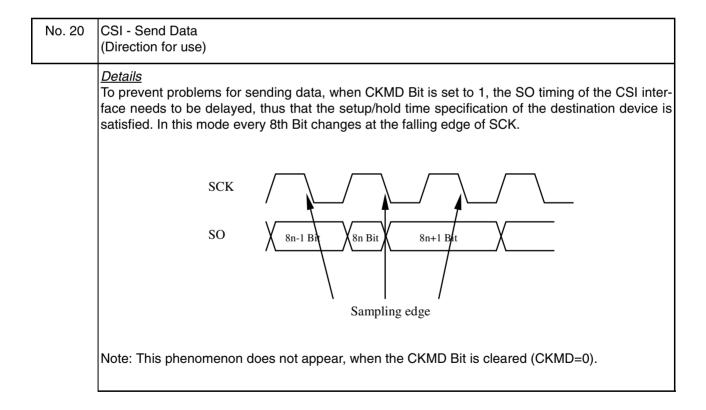

| 20  | CSI - Send data                                 |                      | ×                  |           |

| 21  | Usage of mflo/mfhi instruction within branch de | elay slot            | ×                  |           |

### ✓ : Not applicable

### X : Applicable

**Note:** The rank is indicated by the letter appearing at the 5th position from the left in the lot number, marked on each product.

# (B) Description of Operating Precautions

| No. 1   | MAIUINTREG access<br>(Direction for use)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>Details</u><br>When CPU read the MAIUINTREG (0x0B000090) in case of MISEN bit is set, it reads the con-<br>tents of MIDATREG. This happens only when CPU reads the MAIUINTREG, in other words, CPU<br>writes correct data into the MAIUINTREG.<br>When you write the MAIUINTREG, write same value into work-memory (MISCREG in GIU,<br>DRAM, etc) and refer to work-memory instead of the MAIUINTREG, if the contents of MAIUIN-<br>TREG are needed.                                                                                                                                                                                     |

| <b></b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| No. 2   | Execution of hibernate / suspend sequence<br>(Direction for use)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | DetailsWhen CBR refresh is required, the memory controller unit waits for the external bus idle, and then<br>holds the bus until CBR refresh is done. But when the memory controller unit is in self-refresh<br>state, CBR refresh will not be executed. If CBR refresh is required while the memory controller<br>unit is in self-refresh state, it will continue holding the external bus. Therefore CPU can not get<br>any hibernate / suspend instruction codes from the ROM and VR4181 freeze during hibernate /<br>suspend sequence.Put all hibernate / suspend instruction codes into the cache before executing hibernate / suspend |

|         | sequence. The internal LCD controller and DMA controller must be stopped before executing hibernate / suspend sequence in order to avoid a DRAM access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| No. 3 | Mode register setting for 64 Mbits SDRAM<br>(Specification change notice)                                                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>During the 64 Mbits SDRAM mode register write, A13 of the address bus is forced to logic "1". It<br>should be set logic "0".                                                                                                   |

|       | During the 16 Mbits SDRAM mode register write, A13 had forced to logic "0". Use following sequence to initialize 64 SDRAM:                                                                                                                       |

|       | <ul> <li>(1) Set B0Config and B1Config bits of MEMCFG_REG(0x0A000304) register to "01"</li> <li>(2) Initialize SDRAM by setting Init bit of MEMCFG_REG to "1"</li> <li>(3) Set B0Config and B1Config bits to "10" before using SDRAM.</li> </ul> |

| No. 4 | MEMWR signal behavior at SDRAM access<br>(Direction for use)                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li><u>Details</u></li> <li>The #MEMWR signal is active just before SDCLK is available when using SDRAM. For using a system, which has an external address decoder for an ISA device, apply follows:</li> <li>1) Use VR4181 PCS [1:0] as chip select signal for external device and use LCDCS as chip select signal for external LCD controller.</li> <li>2) Mask #MEMWR signal with #SYSEN signal and enable SYSDIR/#SYSEN function if PCS [1:0] are used as GPIO signal.</li> </ul> |

| No. 5 | The behavior after RTCRST<br>(Direction for use)                                                                                                                                                                                                                                                                                                           |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <i>Details</i><br>The #RTCRST initialization is one of the wake-up events.                                                                                                                                                                                                                                                                                 |

|       | We recommend that hardware initial setting of clock div-mode, bus clock frequency, memory parameter, etc are done in full-speed mode just after RTCRST before going into hibernate-mode. Especially SDRAM initialize should be done just after RTCRST because SDRAM is in unknown state before initialize and its initialize can only be done by software. |

| No. 6 | Usage of 64 MBit SDRAM I/F (5)<br>(Documentation Errata)                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>To prevent a possible deadlock, when the CPU requests cache line fill from 64 MBits SDRAM, do<br>not set the TRP Bits in register SDTIMINGREG (0x0A00030C) to "00" or "01". Set TRP to "10" in<br>register SDTIMINGREG, when 64 Mbits SDRAM is used. |

| No. 7 | CBR Refresh interval<br>(Specification change notice)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Details<br>Interval of CBR refresh after wake-up or resetSW reset is longer as expected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | Refresh timing is generated from detecting match between values of the internal up counter and BCURFCNTREG register. Therefore, when the BCURFCNTREG register value is changed to smaller than current value, and if the internal counter value is bigger than the new BCURFCN-TREG register value, the next CBR refresh timing is at next match after the counter rounds over. After wake-up or resetSW reset, BCURFCNTREG is set to default (0x1FFF) and refresh counter starts counting. If this value will be changed by software, in most cases the counter has already passed this value and the interval is longer as expected. Insert short interval CBR refresh to cancel long CBR refresh interval after exiting self-refresh. |

|       | <ol> <li>(1) Fill into cache (2), (3), (4), (5) and jump to cached routine.</li> <li>(2) Set BCURFCNTREG to short interval (We recommend 250ns interval)</li> <li>(3) Wait for execution of suitable number of CBR refresh by CP0 counter or RTC. In order not to prevent short interval CBR refresh, any external bus cycles should not appear.</li> <li>(4) Set BCURFCNTREG to standard value.</li> <li>(5) Return to main program.</li> </ol>                                                                                                                                                                                                                                                                                         |

| No. 8 | Burst CBR Refresh before/after self-refresh<br>(Direction for use)                                                                                                                                                                                                                                                                                                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>When EDO interface is selected and BstRefr bit of MEMCFG_REG (0x0A000304) is set to 1<br>(enable burst refresh), the CPU applies a burst CBR refresh cycle just before and after self-<br>refresh. When the CPU usually does distributive CBR refresh cycle, mixed use of burst and dis-<br>tributive CBR refresh occurs. This may not fit some DRAM specification. |

|       | Disable burst refreshes by reset BstRefr to 0 if DRAM prohibits mixed use of different refresh type. Moreover, if DRAM needs extra refresh cycle before/after self-refresh, insert short distributive CBR refresh interval.                                                                                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                       |

| No. 9 | Execution of wake-up sequence<br>(Direction for use)                                                                                                                                                                                                                                                                                        |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>When SUSPEND bit of DRAMHIBCTL is set to 1 during wake-up, DRAM controller enters self-<br>refresh state. When DRAM controller is in self-refresh state and CBR refresh request occurs, all<br>next external bus cycles will not appear. Please refer for detail item (2) "Execution of hibernate /<br>suspend sequence". |

|       |                                                                                                                                                                                                                                                                                                                                             |

Exit from self-refresh state before CBR refresh request. Since BCURFCNTREG is reset to default value 0x1FFF, DRAM interface must be exited from self-refresh state within 0x1FFF Tclock (If (7) applies "CBR Refresh interval", 0x1FFF becomes more than 0x3FFF Tclock) Period from cold\_reset.

| USB client function<br>(Specification change notice)             |

|------------------------------------------------------------------|

| Details<br>The VR4181's USB module is removed from specification |

| No. 11 | SDRAM burst refresh before Self-refresh<br>(Direction for use)                                                                                                                                                                                                                                                                                                                                                                               |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <u>Details</u><br>If burst refresh is enabled by the BstRefr bit in MEMCFG_REG and the SUSPEND bit of<br>DRAMHIBCTL register is set to 1, VR4181 applies a self-refresh command to SDRAM before<br>burst CBR refresh. Therefore, SDRAM will exit from self-refresh mode.<br>Disable burst refreshes by reset BstRefr. If SDRAM needs an extra refresh cycle before/after self-<br>refresh, insert a short distributive CBR refresh interval. |

| No. 12                                                                                                                                                                              | DRAM interface in SUSPEND mode<br>(Direction for use)                                                                                                             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                     | <u>Details</u><br>Do not apply SUSPEND instruction, when the DRMEN and STOP_CLK bits in DRAMHIBCTL register are set. To get into suspend mode proceed as follows: |  |

| <ul> <li>clear STOP_CLK bit of the DRAMHIBCTL register</li> <li>wait 1 us</li> <li>clear the SUSPEND bit of the DRAMHIBCTL register</li> <li>execute suspend instruction</li> </ul> |                                                                                                                                                                   |  |

| No. 13 | 13 Internal clock in HIBERNATE mode<br>(Direction for use)                                                                                                                                                                                                                    |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | <u>Details</u><br>Internal clocks (Pclock, Tclock, etc) are running in Hibernate mode as long as Vdd2 power is sup-<br>plied.<br>To avoid an increase in the power consumption of the Hibernate current, cut Vdd2 power supply<br>off in Hibernate mode by the MPOWER signal. |  |

|  |  | To prevent a possible incorrect audio-in DMA transfer, don't use Tclock/8 (reset default) in ISA-<br>BRGCTL (0x0B00 02C0) register. Set PCLK divisor rate to 1/1, 1/2, or 1/4 Tclock when Audio-in |

|--|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. 15 Interrupt for DMA transfer<br>(Documentation Errata) |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             |  | <ul> <li><u>Details</u></li> <li>Following description regarding interrupt during DMA transfer is correct:</li> <li>(1) Interrupt pending bits in DMAITRQREG (0x0A00 0662) can be cleared by writing '1' to the correspond bits.</li> <li>(2) When DMA transfer is set to auto-stop mode, secondary page of DMA buffer is not used in the DMA transfer (only primary page is used).</li> <li>(3) Vr4181 does not use the SSTOPEN bit in SCNTREG (0x0B00 0168).</li> <li>(4) Vr4181 does not use the MSTOPEN bit MCNTREG (0x0B00 0172).</li> </ul> |

| No. 16 | Usage of HAL timer operation<br>(Direction for use)                                                                                                                               |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <u>Details</u><br>For using the HAL timer shutdown make sure that:<br>(a) TIMOUTRST bit in PMUINTREG (0x0B00-00A0) should be cleared as soon as possible after<br>CPU has booted. |

|        | Note: to clear this bit, write "1" to this bit                                                                                                                                    |

|        | (b) DRAM_EN, SUSPEND, STOP_CLK bit in DRAMHIBCTL (0x0B00-00B0) should be cleared before/during DRAM interface initialization.                                                     |

| No. 17 | RSTSW# recognition during wake-up sequence<br>(Direction for use)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | <ul> <li><u>Details</u></li> <li>Vr4181 does not recognize RSTSW# signal until HAL timer is cleared during wake-up sequence<br/>The PMU controls mask of RSTSW# reset for CPU core and internal peripherals. During Vr418'<br/>waking-up sequence, PMU masks this reset until HAL timer is cleared (stopped) by software. I<br/>RSTSW# is activated during resume sequence from hibernate, Vr4181 will run normally until HAI<br/>timer clear although RSTSW# is active. If RSTSW# signal is also used for external peripheral<br/>reset, a conflict may occur in CPU and external system reset. Especially, if boot ROM is reset by<br/>RSTSW#, CPU will go out of order till HAL timer shutdown, because CPU cannot read correct<br/>instruction from ROM.</li> <li>Do not use RSTSW# signal for external peripherals' reset directly. If an external peripherals<br/>reset is needed, RSTSW# signal should be masked by GPIO. This GPIO should be controlled<br/>from wake-up to HAL timer clear.</li> </ul> |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|        | Mask control (use GPIO etc)<br>RSTSW# (modified) to CPU, FROM, other peripherals<br>RSTSW# (original)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| No. 18 | DRAM self-refresh in hibernate mode<br>(Direction for use)                                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Details<br>If RSTSW# is asserted during hibernate mode, DRAM may exit self-refresh and its data may be<br>destroyed. Therefore RSTSW# should be masked by MPOWER or GPIO during hibernate mode. |

| No. 21 | Usage of mflo/mfhi instruction within branch delay slot<br>(Direction for use)                                                                                                                                                                                                                                                                                                     |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | Details<br>To insure proper operation of interruptions, the mflo/mfhi instruction should not be used with<br>branch delay slot, if the preceding instruction before the branch instruction is a div, divu, o<br>dmultu, ddiv, ddivu instruction.<br>Branch delay slots are activated with all Branch/Jump instructions, except beqz, bnez, bteq<br>all MIPS16 branch instructions. |  |

|        | For example, this combination of instructions must be avoided:                                                                                                                                                                                                                                                                                                                     |  |

|        | divu v0,v1<br>bnel zero, v1, label<br>mflo v0<br>nop<br>label: nop<br>nop                                                                                                                                                                                                                                                                                                          |  |

|        | Currently this combination of instructions is generated by applying the 'optimise platform sources option of Microsoft (R) C/C++ Optimizing Compiler Version 12.20.9419 for MIPS R-Series, which is delivered with WinCE V4.0 package,.                                                                                                                                            |  |

|        | Copyright (C) Microsoft Corp 1984-2001.                                                                                                                                                                                                                                                                                                                                            |  |

## (C) Valid Specification

| Item | Date published | Document No.    | Document Title                                               |

|------|----------------|-----------------|--------------------------------------------------------------|

| 1    | Sept 2000      | U14272EJ1V0UMJ1 | VR4181 64-/32-bit Microprocessor Hardware<br>(User's Manual) |

|      |                |                 |                                                              |

|      |                |                 |                                                              |

## (D) Revision History

| Item | Date published | Document No.    | Comment                                                                                                      |

|------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------|

| 1    | January 2001   | TPS-HE-B-6004-1 | First release                                                                                                |

| 2    | April 2002     | TPS-HE-B-6004-2 | Added No19 and 20;<br>Removed descriptions, which effect revisions older than<br>Rev.1.2                     |

| 3    | September 2002 | TPS-HE-B-6004-3 | Addition of Operating Precaution No.21<br>Removed descriptions, which effect revisions older than<br>Rev1.3. |