# RENESAS TECHNICAL UPDATE

〒135-0061 東京都江東区豊洲 3-2-24

豊洲フォレシア

ルネサス エレクトロニクス株式会社

問合せ窓口 <http://japan.renesas.com/contact/>

E-mail: csc@renesas.com

| 製品分類 | MPU & MCU                            | 発行番号   | TN-RL*-A0136A/J | Rev.                                                                                                                                           | 第1版 |

|------|--------------------------------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 題名   | 誤記訂正通知<br>静電容量センサユニットに関する記載変更および制限事項 |        | 情報分類            | 技術情報                                                                                                                                           |     |

| 適用製品 | RL78/G22 グループ、RL78/G23 グループ          | 対象ロット等 | 関連資料            | RL78/G22 ユーザーズマニュアル<br>ハードウェア編 Rev.1.00<br>R01UH0978JJ0100 (Dec.2022)<br>RL78/G23 ユーザーズマニュアル<br>ハードウェア編 Rev.1.30<br>R01UH0896JJ0130 (Jan.2024) |     |

|      |                                      | 全ロット   |                 |                                                                                                                                                |     |

## 1. 誤記訂正について

RL78/G22 ユーザーズマニュアル ハードウェア編 Rev.1.00 (R01UH0978JJ0100) および RL78/G23 ユーザーズマニュアル ハードウェア編 Rev.1.30 (R01UH0896JJ0130) において、下記訂正がございます。

## 今回通知する訂正内容

| 訂正箇所                                                                                      | 該当ページ                             |                                   | 内容   |

|-------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|------|

|                                                                                           | R01UH0978<br>JJ0100<br>(RL78/G22) | R01UH0896<br>JJ0130<br>(RL78/G23) |      |

| センサドライバパルス出力のクロック構成                                                                       | p.1056                            | p.1275                            | 誤記訂正 |

| CTSU 制御レジスタ AL, AH (CTSUCRAL, CTSUCRAH)                                                   | p.1060, p.1062,<br>p.1063         | p.1279, p.1281                    | 誤記訂正 |

| CTSU ステータスレジスタ L (CTSUSRL)                                                                | p.1079                            | p.1296                            | 誤記訂正 |

| CTSU センサオフセットレジスタ 0, 1 (CTSUSO0, CTSUSO1)                                                 | p.1080                            | p.1297                            | 誤記訂正 |

| CTSU センサユニットクロック制御レジスタ AL, AH, BL, BH<br>(CTSUSUCLK0, CTSUSUCLK1, CTSUSUCLK2, CTSUSUCLK3) | p.1087                            | p.1304                            | 誤記訂正 |

| CTSU トリミングレジスタ AL, AH (CTSUTRIM0, CTSUTRIM1)                                              | p.1088                            | p.1305                            | 誤記訂正 |

## ドキュメント改善計画

本訂正内容については、次回ユーザーズマニュアル改版時に修正を行います。

## 2. 誤記による適用製品への影響について

上記適用製品の静電容量センサユニットにおいて、SUCLK に動作可能周波数の範囲外となる周波数が記載されていました。この誤記により、SUCLK を動作可能周波数の範囲外の周波数に設定していた場合は、タッチの測定結果が異常となる可能性があります。

ただし、静電容量式タッチセンサ対応開発支援ツール QE for Capacitive Touch V3.3.0 以前を使用し、デフォルト設定でマルチ周波数計測を実施されている場合は、多数決判定を行っているため、最終的なタッチの測定結果が異常になる可能性は低いと考えられます。詳細は、「2.1 タッチ検出への影響」を参照してください。

ユーザーズマニュアルの訂正一覧

| No  | 訂正内容と該当箇所                                                                               |    |                                   |                                   | 本通知での<br>該当ページ |

|-----|-----------------------------------------------------------------------------------------|----|-----------------------------------|-----------------------------------|----------------|

|     | ドキュメント<br>No.                                                                           | 和文 | R01UH0978<br>JJ0100<br>(RL78/G22) | R01UH0896<br>JJ0130<br>(RL78/G23) |                |

| 1.1 | センサドライブパルス出力のクロック構成                                                                     |    | p.1056                            | p.1275                            | p.3            |

| 1.2 | CTSU制御レジスタAL, AH (CTSUCRAL, CTSUCRAH)                                                   |    | p.1060, p.1062,<br>p.1063         | p.1279,<br>p.1281                 | p.4 ~ p.6      |

| 1.3 | CTSUステータスレジスタL (CTSUSRL)                                                                |    | p.1079                            | p.1296                            | p.7            |

| 1.4 | CTSUセンサオフセットレジスタ0, 1 (CTSUSO0, CTSUSO1)                                                 |    | p.1080                            | p.1297                            | p.8            |

| 1.5 | CTSUセンサユニットクロック制御レジスタAL, AH, BL, BH<br>(CTSUSUCLK0, CTSUSUCLK1, CTSUSUCLK2, CTSUSUCLK3) |    | p.1087                            | p.1304                            | p.9            |

| 1.6 | CTSUトリミングレジスタAL, AH (CTSUTRIM0, CTSUTRIM1)                                              |    | p.1088                            | p.1305                            | p.10           |

誤記訂正の該当箇所は、誤（太字下線）、正（グレー・ハッチング）で記載します

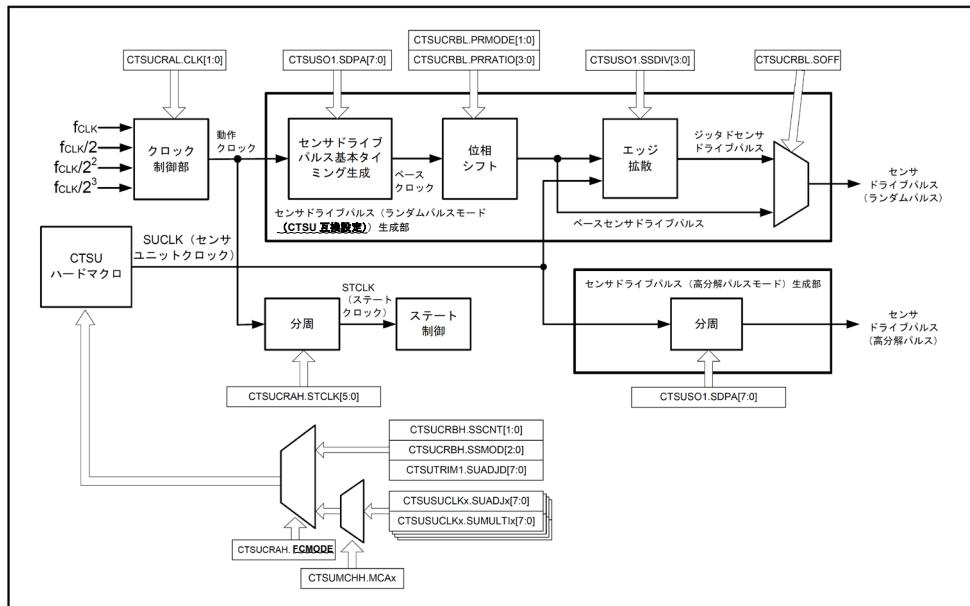

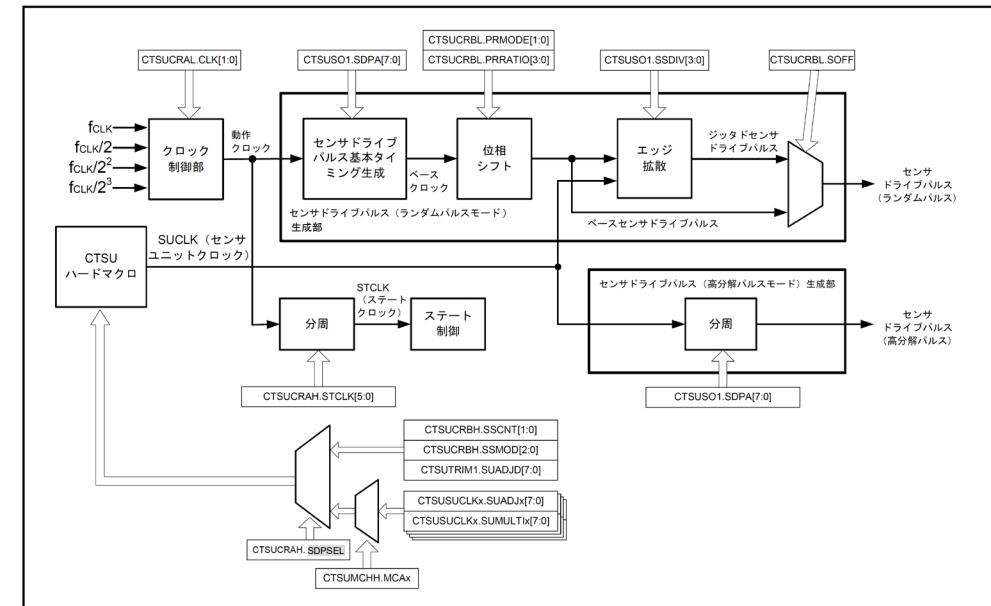

## 1.1 センサドライブパルス出力のクロック構成

誤)

p.1056 (RL78/G22) 、 p.1275 (RL78/G23)

(略)

正)

(略)

(略)

## 1.2 CTSU 制御レジスタ AL, AH (CTSUCRAL, CTSUCRAH)

誤)

p.1060 (RL78/G22) 、p.1279 (RL78/G23)

(略)

アドレス : F0500H, F0501H (CTSUCRAL), F0502H, F0503H (CTSUCRAH)

リセット時: 0000H

R/W属性 : R/W

| 略号       | 15     | 14     | 13 | 12 | 11 | 10 | 9 | 8 |            |

|----------|--------|--------|----|----|----|----|---|---|------------|

| CTSUCRAH | DCBACK | DCMODE |    |    |    |    |   |   | STCLK[5:0] |

|          | 7      | 6      | 5  | 4  | 3  | 2  | 1 | 0 |            |

|        |        |            |       |       |        |   |

|--------|--------|------------|-------|-------|--------|---|

| DCMODE | SDPSEL | POSEL[1:0] | LOAD1 | LOAD0 | ATUNE2 | 0 |

|--------|--------|------------|-------|-------|--------|---|

正)

(略)

アドレス : F0500H, F0501H (CTSUCRAL), F0502H, F0503H (CTSUCRAH)

リセット時: 0000H

R/W属性 : R/W

| 略号       | 15     | 14     | 13 | 12 | 11 | 10 | 9 | 8 |            |

|----------|--------|--------|----|----|----|----|---|---|------------|

| CTSUCRAH | DCBACK | DCMODE |    |    |    |    |   |   | STCLK[5:0] |

|          | 7      | 6      | 5  | 4  | 3  | 2  | 1 | 0 |            |

|       |        |            |       |       |        |   |

|-------|--------|------------|-------|-------|--------|---|

| PCSEL | SDPSEL | POSEL[1:0] | LOAD1 | LOAD0 | ATUNE2 | 0 |

|-------|--------|------------|-------|-------|--------|---|

(略)

| FCMODE | センサユニットクロック (SUCLK) 選択                                                        |

|--------|-------------------------------------------------------------------------------|

| 0      | 周波数拡散クロックとして使用                                                                |

| 1      | マルチクロック計測用リカバリクロックとして使用<br>リカバリクロックとして使用する場合は、CTSUDBGR1.CCOCLK = 1 を設定してください。 |

- FCMODE = 0 のとき (SUCLK を周波数拡散クロックとして使用)

CTSUTRIM1.SUADJD[7:0]、CTSUCRBH.SSCNT[1:0]、CTSUCRBH.SSMODI[2:0] 設定で、デジタル発振器を発振させ、周波数をスペクトラム拡散させた、SUCLK を生成します。

- FCMODE = 1 のとき (SUCLK をマルチクロック計測時のリカバリクロックとして使用)

CTSUSUCLK0 レジスタ FC MODE = 1 を設定する前に、CTSUSUCLK0 レジスタ、CTSUSUCLK1 レジスタ、

CTSUSUCLK2 レジスタまたはCTSUSUCLK3 レジスタの設定を実施してください。

計測中は全選択クロックに対し、非計測期間中 (status0) にリカバリを実施します。リカバリによって

CTSUSUCLK0 レジスタ、CTSUSUCLK1 レジスタ、CTSUSUCLK2 レジスタまたはCTSUSUCLK3 レジスタの SUADJx ビットは更新されます。 (x = 0 ~ 3)

FC MODE = 1 のとき、CTSUSUCLK0 レジスタ、CTSUSUCLK1 レジスタ、CTSUSUCLK2 レジスタまたは

CTSUSUCLK3 レジスタを変更しないでください。

#### <SDPSEL\_FCMODE の関係>

| SDPSEL | FCMODE | 動作                                  |

|--------|--------|-------------------------------------|

| 0      | 0      | ランダムパルスモード (CTSU 互換設定)              |

| 1      | 1      | センサユニットクロック (SUCLK) モードマルチクロック計測時使用 |

| 上記以外   |        | 設定禁止                                |

(略)

| PCSEL | 昇圧クロック選択   |

|-------|------------|

| 0     | センサドライブパルス |

| 1     | STCLK      |

このビットは昇圧回路のクロックを選択します。

| SDPSEL                          | センサドライブパルス選択                                                                                                                                                                                                        |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                               | <p><b>ランダムパルスモード (CTSU 互換設定)</b></p> <p>動作クロックをCTSUSO1.SDPA[7:0]ビットの設定によって分周したベースクロックに、CTSUCRBL.PRMODE[1:0] および CTSUCRBL.PRRATIO[3:0] ビットの設定によって生成される乱数で位相シフトを行ったセンサドライブパルスを選択します。また、周波数拡散クロックによるジッタリング印加が可能です。</p> |

| 1                               | <p><b>センサユニットクロック (SUCLK) モード</b></p> <p>fCLK を基準に周波数リカバリを行ったSUCLKに、CTSUSO1.SDPA[7:0] ビットの設定によって分周を行ったセンサドライブパルスを選択します。</p>                                                                                         |

| <p><b>センサドライブパルスを選択します。</b></p> |                                                                                                                                                                                                                     |

(略)

| SDPSEL                                                                              | センサドライブパルスおよびSUCLK 選択                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                                                   | <p><b>ランダムパルスモード</b></p> <ul style="list-style-type: none"> <li>センサドライブパルス</li> </ul> <p>fCLK を CTSUCRAL.CLK[1:0] ビットおよび CTSUSO1.SDPA[7:0] ビット設定によって分周したベースクロックに、CTSUCRBL.PRMODE[1:0] および CTSUCRBL.PRRATIO[3:0] ビット設定によって生成される乱数で位相シフトを行ったセンサドライブパルスを選択します。また、周波数拡散クロックによるジッタリング印加が可能です。</p> <ul style="list-style-type: none"> <li>SUCLK</li> </ul> <p>CTSUCRBH.SSCNT[1:0], CTSUCRBH.SSMOD[2:0], CTSUTRIM1.SUADJD[7:0]の設定で内蔵発振器を動作させ、周波数拡散したSUCLKを生成します。</p> |

| 1                                                                                   | <p><b>高分解能パルスモード</b></p> <ul style="list-style-type: none"> <li>センサドライブパルス</li> </ul> <p>センサドライブパルスとしてSUCLK をCTSUSO1.SDPA[7:0] ビットで分周したクロック（ペース・クロック）を使用します。</p> <ul style="list-style-type: none"> <li>SUCLK</li> </ul> <p>CTSUSUCLKx レジスタ (x=0-3) を設定することで、クロックリカバリ制御が行われ、SUCLKが生成されます。</p> <p>リカバリにより、CTSUSUCLKx.SUADJx[7:0] ビットが更新されます。</p> <p>このビットを 1 に設定する前に、CTSUSUCLKxレジスタを設定してください。</p> <p>このビットが 1 の間は、CTSUSUCLKxレジスタを変更しないでください。</p>               |

| <p>SDPSELビットは、ランダムパルスモードと高分解能パルスモードを切り替えます。この選択により、センサドライブパルスとSUCLKの生成方法が変わります。</p> |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

(略)

### 1.3 CTSU ステータスレジスタ L (CTSUSRL)

誤)

p.1079 (RL78/G22)、p.1296 (RL78/G23)

(略)

| MFC[1:0]                                                |   | マルチクロックカウンタ |

|---------------------------------------------------------|---|-------------|

| 0                                                       | 0 | マルチクロック0    |

| 0                                                       | 1 | マルチクロック1    |

| 1                                                       | 0 | マルチクロック2    |

| 1                                                       | 1 | マルチクロック3    |

| マルチクロック計測 (CTSUCRAH. <b>FCMODE</b> = 1) での計測中クロックを示します。 |   |             |

正)

(略)

| MFC[1:0]                                                |   | マルチクロックカウンタ |

|---------------------------------------------------------|---|-------------|

| 0                                                       | 0 | マルチクロック0    |

| 0                                                       | 1 | マルチクロック1    |

| 1                                                       | 0 | マルチクロック2    |

| 1                                                       | 1 | マルチクロック3    |

| マルチクロック計測 (CTSUCRAH. <b>SDPSEL</b> = 1) での計測中クロックを示します。 |   |             |

## 1.4 CTSU センサオフセットレジスタ 0, 1 (CTSUSO0, CTSUSO1)

誤)

p.1080 (RL78/G22) 、p.1297 (RL78/G23)

(略)

| SDPA[7:0] | センサドライブパルス分周設定 |

|-----------|----------------|

|-----------|----------------|

- CTSUCRAH.SDPSEL = 0 の場合

動作クロックを分周して、センサドライブパルスの元となるベースクロックを生成します。また本ビットは、CTSU ハードマクロの電圧安定時間の設定としても使用します。

|   |   |   |   |   |   |   |   |                         |

|---|---|---|---|---|---|---|---|-------------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 動作クロックの2分周 <sup>注</sup> |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 動作クロックの4分周              |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 動作クロックの6分周              |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 動作クロックの8分周              |

| : | : | : | : | : | : | : | : | :                       |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 動作クロックの510分周            |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 動作クロックの512分周            |

注 相互容量方式のジッタ印加 OFF 状態 (CTSUCRBL.SOFF = 1) では、SDPA[7:0] = 00000000B は設定禁止です。

- CTSUCRAH.SDPSEL = 1 の場合

SUCLKを分周して、センサドライブパルスを生成します。

|   |   |   |   |   |   |   |   |                 |

|---|---|---|---|---|---|---|---|-----------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SUCLKの1分周       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | SUCLKの2分周       |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | SUCLKの3分周       |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | SUCLKの4分周       |

| : | : | : | : | : | : | : | : | :               |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | SUCLKクロックの255分周 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | SUCLKクロックの256分周 |

正)

(略)

| SDPA[7:0] | ベースクロック (センサドライブパルス分周) 設定 |

|-----------|---------------------------|

|-----------|---------------------------|

- ランダムパルスモード: CTSUCRAH.SDPSEL = 0 の場合

動作クロックを分周して、センサドライブパルスの元となるベースクロックを生成します。また本ビットは、CTSU ハードマクロの電圧安定時間の設定としても使用します。

CTSUSO1.SDPA[7:0]ビットの設定値をnとすると、ベースクロックは動作クロックの2(n+1)分周になります。

|   |   |   |   |   |   |   |   |                         |

|---|---|---|---|---|---|---|---|-------------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 動作クロックの2分周 <sup>注</sup> |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 動作クロックの4分周              |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 動作クロックの6分周              |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 動作クロックの8分周              |

| : | : | : | : | : | : | : | : | :                       |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 動作クロックの510分周            |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 動作クロックの512分周            |

注 相互容量方式のジッタ印加 OFF 状態 (CTSUCRBL.SOFF = 1) では、SDPA[7:0] = 00000000B は設定禁止です。

- 高分解パルスモード: CTSUCRAH.SDPSEL = 1 の場合

SUCLKを分周して、センサドライブパルスを生成します。

SUCLKの周波数は、下記の式にて算出できます。

$$SUCLK = STCLK \times CTSUSUCLKx.SUMULTIx[7:0]ビットでのSUCLK遙倍率設定$$

CTSUSO1.SDPA[7:0]ビットの設定値をnとすると、センサドライブパルスはSUCLKの2(n+1)分周になります。

|   |   |   |   |   |   |   |   |                 |

|---|---|---|---|---|---|---|---|-----------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SUCLKの2分周       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | SUCLKの4分周       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | SUCLKの6分周       |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | SUCLKの8分周       |

| : | : | : | : | : | : | : | : | :               |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | SUCLKクロックの510分周 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | SUCLKクロックの512分周 |

## 1.5 CTSU センサユニットクロック制御レジスタ AL, AH, BL, BH

### (CTSUSUCLK0, CTSUSUCLK1, CTSUSUCLK2, CTSUSUCLK3)

誤)

p.1087 (RL78/G22) 、 p.1304 (RL78/G23)

(略)

| SUMULTIx[7:0]                                          | SUCLK 遅倍率設定 |

|--------------------------------------------------------|-------------|

| SUCLK の STCLK (fCLK の分周 0.5 MHz を想定) に対する遅倍率を設定します。    |             |

| この設定で分周された SUCLK と比較し、比較結果によって、SUADJx[7:0] ビットが更新されます。 |             |

| クロックのターゲットは 32 ~ 80 MHz です。                            |             |

| 0 0 0 0 0 0 0 0                                        | 1 遅倍        |

| :                                                      | :           |

| 0 0 1 1 1 1 1 1                                        | 64 遅倍       |

| :                                                      | :           |

| 0 1 1 1 1 1 1 1                                        | 128 遅倍      |

| :                                                      | :           |

| 1 1 1 1 1 1 1 1                                        | 256 遅倍      |

| SUADJx[7:0]                                                                    | SUCLK 周波数調整 |

|--------------------------------------------------------------------------------|-------------|

| SUCLK 周波数の初期値を設定します。                                                           |             |

| クロックリカバリ機能により、ドリフト調整され、更新されます。                                                 |             |

| 設定値に対して出力周波数は MCU ごとにバラツキがあります。レジスタ設定値を初期値として、クロックリカバリ制御によって調整され、レジスタ値は更新されます。 |             |

正)

(略)

| SUMULTIx[7:0]                                                | STCLK 遅倍率設定 |

|--------------------------------------------------------------|-------------|

| SUCLK を生成するため、STCLK (fCLK から分周した 0.5 MHz を想定) に対する遅倍率を設定します。 |             |

| SUCLK クロックの動作可能周波数は、16 MHz ~ 32 MHz です。                      |             |

| SUCLK クロックが動作可能周波数(16 MHz ~ 32 MHz) の範囲内となる設定でご使用ください。       |             |

| SUCLK = STCLK × CTSUSUCLKx.SUMULTIx[7:0] ビットでの SUCLK 遅倍率設定   |             |

| 0 0 0 0 0 0 0 0                                              | 1 遅倍        |

| :                                                            | :           |

| 0 0 1 1 1 1 1 1                                              | 64 遅倍       |

| :                                                            | :           |

| 0 1 1 1 1 1 1 1                                              | 128 遅倍      |

| :                                                            | :           |

| 1 1 1 1 1 1 1 1                                              | 256 遅倍      |

| SUADJx[7:0]                                 | SUCLK 周波数調整 |

|---------------------------------------------|-------------|

| SUCLK 周波数の初期値が設定されます。                       |             |

| SUCLK はクロックリカバリ機能によりドリフト調整され、本レジスタ値は更新されます。 |             |

| 値を書き換えないでください。                              |             |

## 1.6 CTSU トリミングレジスタ AL, AH (CTSUTRIM0, CTSUTRIM1)

誤)

p.1088 (RL78/G22) 、 p.1305 (RL78/G23)

(略)

| SUADJD[7:0]                                       | SUCLK の周波数調整 |

|---------------------------------------------------|--------------|

| <p><u>出荷時に設定された、約64 MHz となる初期値が書かれています。</u></p>   |              |

| <p><u>FCMODE = 0 のとき、この設定がデジタル発振器に入力されます。</u></p> |              |

| <p><u>出荷時に設定された、初期値が書かれています。書き換えないでください。</u></p>  |              |

(略)

正)

(略)

| SUADJD[7:0]                                                        | SUCLK の周波数調整 |

|--------------------------------------------------------------------|--------------|

| <p>ランダムパルスモード (CTSUCRAH.SDPSEL = 0) のときSUCLK周波数を調整するために使用されます。</p> |              |

| <p>出荷時に設定された初期値が書かれています。値を書き換えないでください。</p>                         |              |

(略)

## 2.1 タッチ検出への影響

### 2.1.1 現象

SUCLK の周波数は 32MHz ~ 80MHz と記載されていますが、動作可能周波数は 16MHz ~ 32MHz になります。SUCLK の周波数が 16MHz ~ 32MHz の範囲外となった状態でタッチの計測を実施すると、SUCLK の 1 クロック目のタッチ検出が不定となり、タッチ計測結果のカウント値に±1 の誤差が発生する可能性があります。タッチ計測結果に対する影響は微小と考えられます。

### 2.1.2 回避方法

SUCLK の周波数は、下記の式によって決まります。SUCLK の周波数が 16MHz ~ 32MHz となるように、CTSUCRAL.CLK[1:0]ビット、CTSUCRAH.STCLK[5:0]ビット、CTSUSUCLK0-1.SUMULTIx[7:0]ビットを設定してください。

$$\text{SUCLK} = (\text{fCLK 周波数} / \text{CLK} / \text{STCLK}) \times \text{SUMULTIx}$$

CLK : CTSUCRAL.CLK[1:0]ビット。fCLK 周波数を分周した動作クロックを設定

STCLK : CTSUCRAH.STCLK[5:0]ビット。動作クロックを分周した STCLK (ステートクロック) を設定

SUMULTIx : CTSUSUCLK0-1.SUMULTIx[7:0]ビット。STCLK を遅倍した SUCLK を設定

### 2.1.3 静電容量式タッチセンサ対応開発支援ツール QE for Capacitive Touch V3.3.0 以前を使用している場合の影響

静電容量式タッチセンサ対応開発支援ツール QE for Capacitive Touch では、SUCLK に動作可能周波数の範囲外の周波数も設定可能になっています。

図 2-1 に QE V3.3.0 以前の 3 周波計測設定(デフォルト設定)を示します。

SIS driver (RL78 タッチドライバ)の CTSU モジュールはマルチ周波数計測が可能であり、デフォルト設定で 3 周波計測を実施しています(3 種類の周波数[nMHz, (n-x)MHz, (n+x)MHz]で計測して多数判定を行っています)。

QE V3.3.0 以前では図 2-1 の赤文字部分に示すように、デフォルト設定で計測 3 の SUCLK 周波数が動作可能周波数の範囲外となる 36.5MHz になっています。

36.5MHz に設定されている場合、タッチ計測結果のカウント値に±1 の誤差が発生する可能性があります。しかし、マルチ周波数計測で多数判定を行っているため、最終的なタッチの測定結果が異常になる可能性は低いと考えられます。この問題に関しては、次回の QE 改版時に修正を行います。また、32MHz より大きい周波数に設定されていてもマイコンが破壊に至る恐れはございません。

図2-1 QE V3.3.0以前の3周波計測設定(デフォルト設定)

自動調整処理中

各メソッドおよびタッチインターフェースの設定値を選択してください。

⚠️ これらの値を誤って設定したり、明確な理解なしに設定したりすると、調整結果が悪くなる可能性があります。

|          |        |        |                |         |             |        |

|----------|--------|--------|----------------|---------|-------------|--------|

| メソッド     | 静電容量方式 | シールド端子 | オフセットチューニング目標値 | 計測電流レンジ | 非計測チャネル出力選択 | 送信端子電源 |

| config01 | 自己容量   | なし     | 自動             | 自動      | 自動          | 自動     |

|      |           |       |       |       |         |  |

|------|-----------|-------|-------|-------|---------|--|

| システム | マルチクロック計測 | 遙倍比 1 | 遙倍比 2 | 遙倍比 3 | タッチ判定方法 |  |

|      | 3周波数      | 64    | 55    | 73    | デフォルト   |  |

SUCLK = STCLK × 遙倍率設定

デフォルト設定では、STCLK は 0.5MHz

|                                |       |       |       |  |

|--------------------------------|-------|-------|-------|--|

| デフォルト設定例：<br>SUCLK周波数が32MHzの場合 |       |       |       |  |

|                                | 計測1   | 計測2   | 計測3   |  |

|                                | 64    | 55    | 73    |  |

| SUCLK周波数[MHz]                  | 32.0  | 27.5  | 36.5  |  |

| CTSUSO1.SDPA[7:0]ビットの設定値       | 3     | 3     | 3     |  |

| ドライバパルス分周比                     | 8     | 8     | 8     |  |

| ドライバパルス周波数[MHz]                | 4.000 | 3.438 | 4.563 |  |