# **CUSTOMER NOTIFICATION**

SUD-DT-03-0314-1-E (SUD-DT-02-0087-1-E revision)

July 31, 2003

Koji Nishibayashi, Senior System Integrator

Microcomputer Group

2nd Solutions Division

Solutions Operations Unit

NEC Electronics Corporation

CP(K), O

IE-V850E-MC (Control Code: A, B, C, D)

IE-V850E-MC-A (Control Code: B, C, D, E, F, G)

# **Operating Precautions**

Be sure to read this document before using the product.

| 1. Product Version                          | 2  |

|---------------------------------------------|----|

| 2. Product History                          | 3  |

| 3. Details of Bugs and Added Specifications | 6  |

| 4. Cautions                                 | 59 |

# Notes on Using IE-V850E-MC-A, IE-V850E-MC

# 1. Product Version

Part number: IE-V850E-MC-A

| Control Code | EVA Chip (for 3.3 V) | Usable Debugger                   |

|--------------|----------------------|-----------------------------------|

| В            | UPD703191AR DS2.0-3V | ID850 E2.00s (for NB85E) or later |

| С            | UPD703191AR DS2.0-3V | ID850 E2.00s (for NB85E) or later |

| D            | UPD703191AR DS3.0-3V | ID850 E2.20f or later             |

| E            | UPD703191AR DS4.1-3V | ID850 E2.20f or later             |

| F            | UPD703191AR ES4.3-3V | ID850 E2.20f or later             |

|              | UPD703191AR DS4.3-3V |                                   |

| G            | UPD703191AR ES4.5-3V | ID850 E2.20f or later             |

Part number: IE-V850E-MC

| Control Code | EVA Chip (for 5 V)  | Usable Debugger                   |

|--------------|---------------------|-----------------------------------|

| А            | UPD703191R DS2.0-5V | ID850 E2.00s (for NB85E) or above |

| В            | UPD703191R DS3.0-5V | ID850 E2.20f or later             |

| С            | UPD703191R DS4.1-5V | ID850 E2.20f or later             |

| D            | UPD703191R DS4.3-5V | ID850 E2.20f or later             |

|              | UPD703191R ES4.3-5V |                                   |

|              | UPD703191R ES4.5-5V |                                   |

The "control code" is the second digit from the left in the 10-digit serial number in the warranty supplied with the product you purchased (if it has not been upgraded). If the product has been upgraded, a label indicating the new version is attached to the product and the x in V-UP LEVEL x on this label indicates the control code.

|                                         |      |                                                                                              |             |              |           | C         | Contro | l Cod | е         |           |              |           |

|-----------------------------------------|------|----------------------------------------------------------------------------------------------|-------------|--------------|-----------|-----------|--------|-------|-----------|-----------|--------------|-----------|

| No.                                     |      | Restrictions                                                                                 | IE-V850E-MC |              |           |           | IE     | -V850 | E-MC      | -A        |              |           |

|                                         |      |                                                                                              | Α           | В            | С         | D         | В      | С     | D         | Е         | F            | G         |

|                                         | a-1  | Interrupt aborts LD instruction immediately before JMP                                       | ×           |              |           |           | ×      | ×     |           |           |              |           |

|                                         | a-2  | Restrictions on IRAM read access after start of interrupt servicing                          | ×           | <b>V</b>     | <b>V</b>  | 1         | ×      | ×     | <b>V</b>  | 1         | <b>√</b>     | <b>V</b>  |

|                                         | a-3  | Fetching is abnormal immediately after writing to SCRn register                              | ×           | √            | 1         | <b>√</b>  | ×      | ×     | √         | <b>V</b>  | <b>√</b>     | <b>√</b>  |

|                                         | a-4  | Single, line, or single-step transfer of 2-cycle DMA                                         | ×           |              |           |           | ×      | ×     |           |           | $\checkmark$ |           |

|                                         | a-5  | Port C is not set in control mode immediately after starting in ROMless mode.                | ×           | V            | √         | V         | ×      | ×     | √         | V         | <b>√</b>     | V         |

|                                         | a-6  | Restrictions on ports DH and DL                                                              | ×           | $\sqrt{}$    |           |           | ×      | ×     |           | √         |              |           |

|                                         | a-7  | HLDAK output illegal due to conflict of self-refresh cycle and HOLDRQ in STOP mode           | ×           | <b>V</b>     | <b>V</b>  | 1         | ×      | ×     | 1         | 1         | <b>√</b>     | <b>V</b>  |

|                                         | a-8  | Fetch/data access fails if hardware STOP is executed after CBR refresh of DRAM/SDRAM         | ×           | √            | 1         | <b>V</b>  | ×      | ×     | √         | <b>V</b>  | <b>√</b>     | <b>V</b>  |

|                                         | a-9  | Restrictions on data cache                                                                   | Perm        | nanen        | t restri  | iction    |        |       |           |           |              |           |

|                                         | a-10 | PFCCM register cannot be read.                                                               | ×           | $\checkmark$ |           |           | ×      | ×     | √         | √         |              |           |

| tions                                   | a-11 | VSB bus and memory controller (NB85E500/501/502) cannot be used together.                    | Perm        | nanen        | t restr   | ction     |        |       |           |           |              |           |

| un                                      | a-12 | Restrictions on VSB bus signal                                                               | ×           |              |           |           | ×      | ×     |           |           |              |           |

| Ď                                       | a-13 | Restrictions on NPB bus signal                                                               | Perm        | anen         | t restr   | ction     |        |       |           |           |              |           |

| S                                       | a-14 | Restrictions on memory controller (NB85E500) signal                                          | ×           |              |           |           | ×      | ×     | $\sqrt{}$ |           |              |           |

| o                                       | a-15 | Restrictions on instruction cache                                                            | ×           |              |           |           | ×      | ×     | $\sqrt{}$ | $\sqrt{}$ |              | $\sqrt{}$ |

| ent                                     | a-16 | Restriction on SDRAM access during bus hold                                                  | ×           | $\sqrt{}$    |           |           | ×      | ×     |           |           |              | $\sqrt{}$ |

| ju de                                   | a-17 | Restriction on self-refresh cycle by SELFREF pin                                             | ×           |              |           |           | ×      | ×     | $\sqrt{}$ |           | <b>√</b>     |           |

| ede                                     | a-18 | Restriction on flyby DMA transfer to EDO DRAM                                                | ×           |              |           |           | ×      | ×     | $\sqrt{}$ |           | <b>√</b>     |           |

| s de                                    | a-19 | Restriction on EDO DRAM with idle state inserted                                             | ×           |              |           |           | ×      | ×     | $\sqrt{}$ |           | <b>√</b>     |           |

| jo                                      | a-20 | Restriction on flyby DMA transfer                                                            | ×           |              |           |           | ×      | ×     |           |           | <b>√</b>     |           |

| Restrictions dependent on CPU functions | a-21 | Restriction on pin status in single-step mode 1 and ROMless modes 0 and 1                    | -           | -            | -         | -         | ×      | ×     | √         | 1         | <b>√</b>     | <b>V</b>  |

| œ                                       | a-22 | Incorrect writeback with LD/SLD instruction when executing CALLT/SWITCH instruction          | ×           | ×            | <b>V</b>  | 1         | ×      | ×     | ×         | 1         | <b>√</b>     | <b>V</b>  |

|                                         | a-23 | Restriction on use of external bus when product is employed as an emulator for the V850E/IA1 | ×           | V            | <b>V</b>  | V         | -      | _     | -         | -         | -            | _         |

|                                         | a-24 | Restriction on output of the _DMAAK signal                                                   | ×           | ×            | $\sqrt{}$ |           | ×      | ×     | ×         |           |              |           |

|                                         | a-25 | Restriction on starting DMA by built-in peripheral I/O interrupt                             | ×           | ×            | V         | V         | ×      | ×     | ×         | V         | $\sqrt{}$    | V         |

|                                         | a-26 | Restriction on EDO DRAM bus collision                                                        | ×           | ×            | $\sqrt{}$ |           | ×      | ×     | ×         |           | $\sqrt{}$    |           |

|                                         | a-27 | Restriction on 2-way associative function of instruction cache                               | ×           | ×            | √         | 1         | ×      | ×     | ×         | 1         | <b>√</b>     | <b>V</b>  |

|                                         | a-28 | Forced stop of external DMA transfer in DMA line transfer mode                               | ×           | ×            | 1         | <b>V</b>  | ×      | ×     | ×         | <b>V</b>  | <b>V</b>     | <b>V</b>  |

|                                         | a-29 | Restriction on reading DCHC register when DMA 2-cycle transfer is complete                   | ×           | ×            | 1         | <b>V</b>  | ×      | ×     | ×         | <b>V</b>  | <b>V</b>     | <b>√</b>  |

|                                         | a-30 | Restriction on conflict between SDRAM initialization and SELFREF input                       | ×           | ×            | √         | V         | ×      | ×     | ×         | V         | <b>V</b>     | √         |

|                                         | a-31 | Restriction on halfword writing to BSC, BCC, DWC0, and DWC1 registers                        | ×           | ×            | √         | <b>V</b>  | ×      | ×     | ×         | √         | <b>V</b>     | √         |

|                                         | a-32 | Restriction on SDRAM write operation                                                         | ×           | ×            |           | $\sqrt{}$ | ×      | ×     | ×         |           |              |           |

$\sqrt{\cdot}$ : Already confirmed and solved

$<sup>\</sup>times$ : Corresponding restriction exists

<sup>-:</sup> Restriction does not apply

|      |                                                                                          | Control Code          |                       |           |           |               |         |        |           |           |          |

|------|------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------|-----------|---------------|---------|--------|-----------|-----------|----------|

| No.  | Restrictions                                                                             | IE-V850E-MC           |                       |           |           | IE-V850E-MC-A |         |        |           |           |          |

|      |                                                                                          | Α                     | В                     | С         | D         | В             | С       | D      | Е         | F         | G        |

| a-33 | Restriction on DRAM fetch immediately after block DMA transfer from DRAM to internal RAM | ×                     |                       | $\sqrt{}$ | $\sqrt{}$ | ×             | ×       | V      | $\sqrt{}$ | $\sqrt{}$ | √        |

| a-34 | Restriction on instruction cache (2)                                                     | Pern                  | nanen                 | t restr   | iction    |               |         |        |           |           |          |

| a-35 | Restriction on SLD instruction                                                           | ×                     | ×                     | ×         | <b>√</b>  | ×             | ×       | ×      | ×         | <b>√</b>  | 1        |

| a-36 | I/O that cannot be used when using a VSB bus                                             | ×                     | ×                     | ×         | V         | ×             | ×       | ×      | ×         | <b>V</b>  | <b>√</b> |

| a-37 | Restriction on instruction cache (3)                                                     | ×                     | ×                     | ×         | V         | ×             | ×       | ×      | ×         | <b>V</b>  | <b>V</b> |

| a-38 | Restriction on DMAAK signal during DMA line transfer                                     |                       |                       |           |           |               |         |        |           |           |          |

| a-39 | Restriction caused by interrupt input during execution of bit manipulation instruction   | ×                     | ×                     | ×         | <b>V</b>  | ×             | ×       | ×      | ×         | <b>V</b>  | √        |

| a-40 | Restriction on hardware stop during bit manipulation instruction execution               | ×                     | ×                     | ×         | <b>V</b>  | ×             | ×       | ×      | ×         | <b>V</b>  | √        |

| a-41 | Restriction related to interruption of DMA transfer by external cause                    | ×                     | ×                     | ×         | <b>V</b>  | ×             | ×       | ×      | ×         | <b>V</b>  | √        |

| a-42 | Restriction on SDCKE signal during bus hold                                              | -                     | _                     | _         | _         | ×             | ×       | ×      | ×         | ×         | √        |

| a-43 | Caution regarding SDRAM controller                                                       | Permanent restriction |                       |           |           |               |         |        |           |           |          |

| a-44 | Restriction on mul/mulu instruction                                                      |                       |                       |           | Pern      | nanen         | t restr | ction  |           |           |          |

| a-45 | Restriction on page ROM access                                                           |                       |                       |           | Pern      | nanen         | t restr | ction  |           |           |          |

| a-46 | Bug related to DMA transfer forcible termination                                         |                       |                       |           | Pern      | nanen         | t restr | iction |           |           |          |

| a-47 | Bug that DMA transfer is forcibly suspended by NMI                                       |                       | Permanent restriction |           |           |               |         |        |           |           |          |

| a-48 | Bug in program execution and DMA transfer in internal RAM                                |                       | Permanent restriction |           |           |               |         |        |           |           |          |

| a-49 | Bug related to DMA transfer whose transfer count is set to two (1)                       |                       | Permanent restriction |           |           |               |         |        |           |           |          |

| a-50 | Bug related to DMA transfer whose transfer count is set to two (2)                       |                       | Permanent restriction |           |           |               |         |        |           |           |          |

| a-51 | Bug that TCn bit of DMA is not cleared automatically                                     |                       |                       | _         | Pern      | nanen         | t restr | iction |           | _         | _        |

$\sqrt{:}$  Already confirmed and solved

$\times$ : Corresponding restriction exists

-: Restriction does not apply

|                                 |                                                                  |                                                                                                 |                                    | Control Code          |    |        |              |         |         |        |          |           |           |

|---------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|----|--------|--------------|---------|---------|--------|----------|-----------|-----------|

| No.                             |                                                                  | Restrictions                                                                                    |                                    | IE-V850E-MC           |    |        |              |         |         |        |          |           |           |

|                                 |                                                                  |                                                                                                 |                                    | Α                     | В  | С      | D            | В       | С       | D      | Е        | F         | G         |

|                                 | b-1                                                              | Restriction on operating frequency                                                              |                                    | ×                     | ×  | ×      | ×            | ×       | ×       | ×      | √        | $\sqrt{}$ | $\sqrt{}$ |

|                                 | b-2                                                              | Restriction on break timing when guarded area is                                                | fetched                            |                       |    |        | Perm         | nanen   | t restr | iction |          |           |           |

|                                 | b-3                                                              | Restriction on trace in case of mis-alignment (duraccess only)                                  | ing read                           | ×                     | √  | √      | √            | ×       | ×       | √      | √        | √         | 1         |

|                                 | b-4                                                              | Restrictions on trace data on execution of HALT instruction                                     | or STOP                            | ×                     | 1  | 1      | $\sqrt{}$    | ×       | ×       | V      | V        | 1         | V         |

|                                 | b-5                                                              | Bit manipulation instruction (set1, clr1, not1, tst1) data is illegally traced by tracer.       | access                             | ×                     | √  | √      | $\sqrt{}$    | ×       | ×       | V      | V        | 1         | V         |

|                                 | b-6                                                              | Events including data conditions by access of bit manipulation instruction cannot be detected.  |                                    | ×                     | √  | √      | V            | ×       | ×       | V      | V        | V         | V         |

|                                 | b-7                                                              | Restriction on HOLD status                                                                      |                                    | ×                     | √  | √      | $\checkmark$ | ×       | ×       | √      | √        | √         | $\sqrt{}$ |

|                                 | b-8                                                              | ROM contents are rewritten if emulation ROM are accessed for write.                             | ea is                              |                       |    |        | Perm         | nanen   | t restr | iction | •        | •         |           |

| ω,                              | b-9                                                              | Restriction on SFR illegal break                                                                |                                    |                       |    |        | Perm         | nanen   | t restr | iction |          |           |           |

| nction                          | h 10                                                             | Doctrictions on programmable I/O cross                                                          | (a)                                |                       |    |        | Suppo        | orted I | by deb  | ugge   | ſ        |           |           |

| ing fui                         | b-10                                                             | -10 Restrictions on programmable I/O space                                                      |                                    | Permanent restriction |    |        |              |         |         |        |          |           |           |

| Restrictions on debug functions | b-11                                                             | Break does not occur even if breakpoint is set.                                                 |                                    | Supported by debugger |    |        |              |         |         |        |          |           |           |

| tions                           | b-12                                                             | Restriction related to access address during DMA trace                                          |                                    | Permanent restriction |    |        |              |         |         |        |          |           |           |

| Restric                         | b-13                                                             | Restriction on DBPC and DBPSW access during                                                     | a break                            | Permanent restriction |    |        |              |         |         |        |          |           |           |

|                                 | b-14                                                             | Restriction on DBTRAP instructions                                                              |                                    |                       |    |        | Perm         | nanen   | t restr | iction |          |           |           |

|                                 | b-15                                                             | Restriction on illegal guard break when IRAM size                                               | e is 28KB                          | ×                     | ×  | ×      | V            | ×       | ×       | ×      | ×        | V         | V         |

|                                 | b-16                                                             | Restriction on illegal trace when big endian is use                                             | ed                                 | ×                     | ×  | ×      | √            | ×       | ×       | ×      | ×        | √         | √         |

|                                 | b-17                                                             | Restriction on access data traced by DMA                                                        |                                    |                       |    |        | Perm         | nanen   | t restr | iction |          |           |           |

|                                 | b-18                                                             | Restriction on SFR read access during break                                                     |                                    |                       | Sı | upport | ed by        | debu    | gger a  | and de | evice f  | ile       |           |

|                                 | b-19                                                             | Restriction that the debugger hangs up dependin software break setting upon PSC register access | g on the                           | Permanent restriction |    |        |              |         |         |        |          |           |           |

|                                 | b-20                                                             | Restriction that the same branch instruction is tra                                             | ced twice                          |                       |    |        | Perm         | nanen   | t restr | iction |          |           |           |

|                                 | b-21                                                             | Restriction on 48-bit length mov instruction trace                                              |                                    | Permanent restriction |    |        |              |         |         |        |          |           |           |

|                                 | b-22 Restriction on illegal trace of consecutive sld instruction |                                                                                                 | Permanent restriction              |                       |    |        |              |         |         |        |          |           |           |

| Other                           | c-1                                                              | Modification through quality improvement                                                        | cation through quality improvement |                       |    | None   |              |         |         | Р      | Provided |           |           |

$\sqrt{:}$  Already confirmed and solved

$\times$ : Corresponding restriction exists

-: Restriction does not apply

# 3. Details of Bugs and Added Specifications

# a-1. Interrupt aborts LD instruction immediately before JMP

# [Description]

If an LD/SLD instruction immediately before a JR/JARL/Bcc instruction is aborted by an interrupt, the instruction may not be executed again after program execution has exited from the interrupt routine.

This phenomenon occurs when all the following conditions are satisfied (the branch destination of JR/JARL/Bcc is saved to EIPC/FEPC):

# 1) An LD/SLD instruction is executed immediately after a JR/JARL/Bcc instruction.

- LD+JR if the instruction is fetched from IROM.

- LD+ LD+ LD+JR if the instruction is fetched from external memory.

- 2) Two or more bus cycles of the preceding LD/SLD remain in the EX stage of the above LD/SLD instruction, and the EX stage of LD/SLD is held.

- 3) An interrupt occurs while the EX stage of the above LD/SLD is held.

#### - Mechanism -

If an interrupt occurs in the ID stage of a JR/JARL/Bcc instruction, the branch destination address is saved to EIPC/FEPC to increase the processing speed after execution has exited from the interrupt routine (because the branch instruction does not have to be executed again).

In the meantime, the LD/SLD/ST/SST instruction is aborted if a bus cycle has not yet been issued, after the EX stage has been started, in order to improve the interrupt response. If these functions conflict, i.e., if an interrupt occurs in the ID stage (= EX stage of LD/SLD) of JR/JARL/Bcc, processing of LD/SLD (saving its own address to EIPC/FEPC) must take precedence over the processing of JR/JARL/Bcc (saving the branch destination to EIPC/FEPC). However, processing of JR/JARL/Bcc takes precedence while the program is waiting for an external bus cycle and, consequently, the branch destination is saved to EIPC/FEPC.

Because the program waits for the ST/SST instruction in the ID stage, the above condition 2) is not satisfied, and therefore, the above phenomenon does not occur.

# [Workaround]

Insert one or more instruction in between the LD/SLD and JR/JARL/Bcc instructions (because the above phenomenon does not occur if the EX stage of LD/SLD and ID stage of JR/JARL/Bcc do not overlap, any instruction (other than JR/JARL/Bcc/LD/SLD) may be inserted).

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

A tool that inserts a NOP instruction between the LD/SLD and JR/JARL/Bcc instruction is available as a patch for the compiler. This patch tool is not supplied with the current release of the compiler (from NEC Electronics and third parties) as standard.

Consult the NEC Electronics Development Tool Support Center for details.

# a-2. Restrictions on IRAM read access after start of interrupt servicing

# [Description]

If the IRAM is read within 10 system CLK after interrupt servicing has been started (after execution has branched to the interrupt handler address), the IRAM cannot be correctly read and "0" is read.

The 10 system CLK is equivalent to the execution time of 20 steps of NOP instructions of assembler.

# [Workaround]

To access IRAM for read after interrupt servicing has been started, insert a dummy read/write (to the external memory) instruction before the instruction that reads the IRAM.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-3. Fetching is abnormal immediately after writing to SCRn register

#### [Description]

An abnormal fetch cycle occurs if the SCR register is written after the VSWC register is set to 11H so that SDRAM is used as the BCTn register.

This is because, if an access to external memory occurs immediately after the SCR register write cycle, the values of A[25:0] and CSZ[7:0] are not normal.

# [Workaround]

Specify two or more wait cycles for VPSTB wait (set VSWL2, VSWL1, and VSWL0 of the VSWC register to 3'b010 or more).

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

# a-4. Single, line, or single-step transfer of 2-cycle DMA

# [Description]

If WAIT is inserted on the VSB bus for 3 clocks or more during single, line, or single-step transfer of 2-cycle DMA, fetch and data access cannot be executed until the DMA cycle is completed (until the TC signal is output).

# [Workaround]

Insert a WAIT of 2 clocks or less. The emulator before correction executes a DMA operation more quickly than the actual chip (including the NB85E core).

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

# a-5. Port C is not set in control mode immediately after starting in ROMless mode.

# [Description]

Port C, which should be in the control mode immediately after the ROMless mode has been started, does not enter the control mode but enters the port mode. (The initial value of PMCCT is 00h.) DRAM cannot be accessed immediately after reset.

# [Workaround]

Write "1" to any bit of PMCCT, even after the ROMless mode has been started, to access DRAM.

Do not execute an application that accesses DRAM immediately after reset.

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

# a-6. Restrictions on ports DH and DL

#### [Description]

Ports DH and DL enter the control mode (D31 to D0) immediately after they have been started (is not started in the port mode).

# [Workaround]

The mode can be changed to the port mode by writing "0" to the PMCDH and PMCDL registers immediately after the emulator has been started.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-7. HLDAK output illegal due to conflict of self-refresh cycle and HOLDRQ in STOP mode

# [Description]

If self-refreshing of DRAM or SDRAM and HOLDRQ conflict in the STOP mode, the HOLDAK signal is illegally output even in the self-refresh cycle.

#### [Workaround]

Do not input HOLDRQ in the STOP mode.

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

#### a-8. Fetch/data access fails if hardware STOP is executed after CBR refresh of DRAM/SDRAM

# [Description]

If hardware STOP is executed while the bus mastership is transferred from the device on the VSB bus to an internal unit of the NB85E after CBR refresh of DRAM or SDRAM, fetch/data access cannot be correctly executed because self refreshing caused by hardware STOP and fetch/data access conflict and the CS signal is disrupted (goes high).

# [Workaround]

Do not use hardware STOP. Use software STOP.

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

#### a-9. Restrictions on data cache

# [Description]

This emulator has no plan to support data cache.

# a-10. PFCCM register cannot be read.

#### [Description]

Although the PFCCM register is an R/W register, it cannot be read.

# [Workaround]

Use the PFCCM register as a write-only register.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-11. VSB bus and memory controller (NB85E500/501/502) cannot be used together.

# [Description]

The VSB bus signal pin is multiplexed with a memory controller pin. Therefore,

- The memory controller cannot be used while the VSB bus is being used.

- The VSB bus cannot be used while the memory controller is being used.

#### [Workaround]

There is no workaround. Please regard this as a permanent restriction.

# a-12. Restrictions on VSB bus signal

#### [Description]

- a) The master device on the VSB bus cannot access the slave source on the NPB bus.

- b) The emulator does not output VBA [27:26].

- c) The emulator does not output VBSEQ [2:0].

#### [Workaround]

- a) There is no workaround.

- b) Temporary workarounds are available for the IE-V850E-MC-EM1-A/B. For details, refer to the document describing the restrictions on the IE-V850E-MC-EM1-A/B.

- c) There is no workaround.

These restrictions have been corrected in the IE-V850E-MC with control code B.

These restrictions have been corrected in the IE-V850E-MC-A with control code D.

# a-13. Restrictions on NPB bus signal

## [Description]

The emulator does not have a VPDACT signal pin and this signal is always fixed to the active level inside the emulator.

# [Workaround]

There is no workaround. Please regard this as a permanent restriction.

# a-14. Restrictions on memory controller (NB85E500) signal

# [Description]

- a) The emulator does not output the ASTBZ, DSTBZ, MPXCZ, RDCYZ, and BUSSTZ signals; therefore, the multiplex bus cannot be used.

- b) The emulator does not output the BENZ3 to BENZ 0 and DC3 to DC0 signals.

- c) The IORDZ and CSZ2, and IOWRZ and CSZ5 signals of the emulator are multiplexed.

- d) The emulator does not have an MCE signal pin and this signal is always fixed to the active level inside the emulator. Therefore, the MEn bit (n = 0 to 7) of the BCTn register (n = 0 or 1) is always "1", enabling operation.

- e) Usually, the IORD and IOWR signals are asserted active in the normal read/write cycle and

during flyby transfer of DMA. But these signals, however, are asserted active only during flyby transfer of DMA in this memory controller.

# [Workaround]

a) Do not use the multiplex bus. Use the separate bus.

Please regard this as a permanent restriction.

b) Design UDL that does not use BENZ3 to BENZ 0 and DC3 to DC0.

Please regard this as a permanent restriction.

c) Do not map external I/O to memory blocks 2 and 5.

The pin assignment of the IE-V850E-MC with control code B and IE-V850E-MC-A with control code D has been changed as follows.

Pin assignment of versions with the old control code:

```

IORDZ and CSZ2 are multiplexed.

```

IOWRZ and CSZ5 are multiplexed.

Pin assignment of the version with the new control code:

```

IORDZ and CSZ5 are multiplexed.

```

\_IOWRZ and \_CSZ2 are multiplexed.

- d) There is no workaround. Please regard this as a permanent restriction.

- e) There is no workaround.

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

# a-15. Restrictions on instruction cache

[Description]

- (a) If control is transferred from a cacheable area to an uncached area and then back to the cacheable area again after auto fill, the first one clock does not hit.

- (b) If the cache clear bit is set while the instruction being cached in the instruction cache is being fetched, a burst transfer is performed immediately due to miss-caching.

- (c) When clearing an instruction cache tag by setting the tag clear bit, the tag is cleared correctly but the LRU is not.

# [Workaround]

There is no workaround.

These restrictions have been corrected in the IE-V850E-MC with control code B.

These restrictions have been corrected in the IE-V850E-MC-A with control code D.

# a-16. Restriction on SDRAM access during bus hold

# [Description]

If the external bus master accesses the SDRAM during bus hold, the bus master cannot correctly access the SDRAM because the page information and bank information immediately before the bus hold status is retained. The SDCLK signal goes into a high-impedance state in the bus hold status. The level of this signal before it goes into a high-impedance state is unstable.

# [Workaround]

Do not access the SDRAM during bus hold.

The specification has been corrected in the IE-V850E-MC with control code B.

The specification has been corrected in the IE-V850E-MC-A with control code D.

The specification has been changed so that the SDCLK signal can be output during bus.

# a-17. Restriction on self-refresh cycle by SELFREF pin

# [Description]

If the self-refresh cycle is started by the SELFREF pin, the REFRQ(–) signal is not asserted.

# [Workaround]

There is no workaround.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-18. Restriction on flyby DMA transfer to EDO DRAM

#### [Description]

When the EDO DRAM is set so that no wait cycle is inserted during on-page access and that the RAS hold mode is enabled, a DMA cycle is stopped in mid-execution, no transfer is executed, and the EDO DRAM cannot be correctly accessed if flyby DMA transfer from the EDO DRAM to an external I/O takes place in the on-page status and during RAS hold.

#### [Workaround]

Insert at least one cycle of CAS precharge wait or data wait.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

#### a-19. Restriction on EDO DRAM with idle state inserted

# [Description]

If an EDO DRAM without a row address hold wait cycle is accessed immediately after an EDO DRAM with an idle state (1 to 3), the former EDO DRAM cannot be correctly read/written.

# [Workaround]

Insert at least one cycle of row address hold wait for the EDO DRAM without a row address hold wait cycle.

This bug has been corrected in the IE-V850E-MC with control code B.

This bug has been corrected in the IE-V850E-MC-A with control code D.

# a-20. Restriction on flyby DMA transfer

# [Description]

If a certain DMA channel is set in a block transfer mode in which flyby DMA transfer is executed from an external memory to an external I/O and if another DMA channel is set in a single, single-step, or line mode in which flyby transfer from an external memory to an external I/O or from an external I/O to external memory is executed, and if these two DMA transfer operations conflict, DMA transfer is not correctly executed.

# [Workaround]

If the external memory that executes DMA transfer in the block transfer mode is SRAM, make sure the total number of data wait states (including inserting of a wait state by using the external WAIT pin), address setup wait states, and idle insertion states does not exceed 1.

(Example: Data wait: 1, address setup wait: 0, idle state: 0, with no wait state inserted by external WAIT pin)

If the external memory of the channel that executes DMA transfer in the block transfer mode is EDO DRAM, use either of the channels for two-cycle transfer.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-21. Restriction on pin status in single-step mode 1 and ROMless modes 0 and 1

[Description]

Some pins do not go into a high-impedance state, but rather output a specific level, when the device is reset in single-chip mode 1 or ROMless mode 0 or 1 (refer to the table below).

| Operating Status                | Current Status                               | After Change                                 |

|---------------------------------|----------------------------------------------|----------------------------------------------|

| Pin                             | Reset (Single-Chip Mode 1, ROMless Mode 0,1) | Reset (Single-Chip Mode 1, ROMless Mode 0,1) |

| A0 to A15 (PAL0 to PAL15)       | L                                            | Hi-Z                                         |

| A16 to A25 (PAH0 to PAH9)       | L                                            | Hi-Z                                         |

| D0 to D15 (PDL0 to PDL15)       | L                                            | Hi-Z                                         |

| CS0 to CS7 (PCS0 to PCS7)       | Н                                            | Hi-Z                                         |

| RAS1, RAS3, RAS4, RAS6          | _                                            | _                                            |

| (PCS1, PCS3, PCS4, PCS6)        |                                              |                                              |

| IOWR (PCS2)                     | _                                            | -                                            |

| IORD (PCS5)                     | _                                            | -                                            |

| LWR, UWR (PCT0, PCT1)           | Н                                            | Hi-Z                                         |

| LCAS, UCAS (PCT0, PCT1)         | _                                            |                                              |

| LDQM, UDQM (PCT0, PCT1)         | _                                            | -                                            |

| RD (PCT4)                       | Н                                            | Hi-Z                                         |

| WE (PCT5)                       | Н                                            | Hi-Z                                         |

| OE (PCT6)                       | Н                                            | Hi-Z                                         |

| BCYST (PCT7)                    | Н                                            | Hi-Z                                         |

| WAIT (PCM0)                     | Н                                            | Hi-Z                                         |

| CLKOUT (PCM1)                   | Operates                                     | Operates                                     |

| BUSCLK (PCM1)                   | _                                            | -                                            |

| HLDAK (PCM2)                    | Н                                            | Hi-Z                                         |

| HLDRQ (PCM3)                    | _                                            | Hi-Z                                         |

| REFRQ (PCM4)                    | Н                                            | Hi-Z                                         |

| SELFREF (PCM5)                  | _                                            | Hi-Z                                         |

| SDCKE (PCD0)                    | L                                            | Hi-Z                                         |

| SDCLK (PCD1)                    | Operates                                     | Hi-Z                                         |

| SDCAS (PCD2)                    | -                                            |                                              |

| LBE (PCD2)                      | Н                                            | Hi-Z                                         |

| SDRAS (PCD3)                    |                                              |                                              |

| UBE (PCD3)                      | Н                                            | Hi-Z                                         |

| DMAAK0 to DMAAK3 (PBD0 to PBD3) | Н                                            | Hi-Z                                         |

Remark Hi-Z: High-impedance

H: High-level outputL: Low-level output-: Input non-sampling

# [Workaround]

There is no workaround. This restriction applies only to the V850E/MA1.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-22. Incorrect writeback with LD/SLD instruction when executing CALLT/SWITCH instruction [Description]

If the bits (bits 15 to 11) corresponding to the halfword WB field immediately after a CALLT/SWITCH instruction match the WB field of an LD/SLD instruction executed immediately before the CALLT/SWITCH instruction, and the CALLT/SWITCH instruction is executed before the bus cycle of the LD/SLD instruction is complete, then the result of LD/SLD is not written back to the register.

The conditions under which the phenomenon occurs are as follows.

- 1) An LD/SLD instruction is executed

- Before the bus cycle of the above instruction is complete, a CALLT/SWITCH instruction is executed.

- 3) Bits 15 to 11 of the halfword after the CALLT/SWITCH instruction in 2) are the same as the writeback register field (bits 15 to 11) of the LD/SLD instruction in 1)

When all the above conditions occur, the results of the LD/SLD instruction in 1) are not written back. One more condition applies in the case of a fetch via VSB, i.e.:

4) There are three or fewer instructions between LD/SLD and CALLT/SWITCH (does not occur with Id-reti-callt/switch.)

# [Workaround]

Either of the following two workarounds can be used:

- 1) Set bits 15 to 11 of the halfword immediately after CALLT/SWITCH to 00000B.

- 2) Insert "mov r31, r0" immediately before CALLT/SWITCH and at the end of interrupt servicing (before RETI.) (It must be inserted before RETI in case an interrupt occurs between the inserted mov and callt.)

It is not necessary to insert mov before RETI if operation is limited only to fetch via VSB.

This bug has been corrected in the IE-V850E-MC with control code C.

This bug has been corrected in the IE-V850E-MC-A with control code E.

A tool that inserts "mov r31, r0" before CALLT/SWITCH and at the end of interrupt servicing (before RETI) is available as a patch for the compiler. This patch tool is not supplied with the current release of the compiler (from NEC Electronics and third parties) as standard.

Consult the NEC Electronics Development Tool Support Center for details.

#### a-23. Restriction on use of external bus when product is employed as an emulator for the V850E/IA1.

# [Description]

The external bus cannot be used when used as emulator of the V850E/IA1.

# [Workaround]

There is no workaround.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction is not applicable to the IE-V850E-MC-A.

# a-24. Restriction on output of the \_DMAAK signal

# [Description]

Although the \_DMAAK signal is intended to remain active during 2-cycle DMA transfer, the \_DMAAK(-) signal becomes inactive for one clock cycle between the read cycle and the write cycle. As a result, this product does not operate normally when the number of DMA transfers are counted externally or when external I/O is started with only the rising edge of the DMAAK(-) signal.

# [Workaround]

There is no workaround.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-25. Restriction on starting DMA by built-in peripheral I/O interrupt

# [Description]

Depending on the timing, it may not be possible to start DMA by interrupt of the built-in peripheral I/O.

# [Workaround]

There is no workaround.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-26. Restriction on EDO DRAM bus collision

# [Description]

There is a possibility of a bus collision in the EDO DRAM when this product is used in RAS hold mode because of an overlap of an EDO DRAM write cycle or the last state (TE state) of a read cycle of an EDO DRAM that does not have an idle state inserted and the first state of the next bus cycle.

# [Workaround]

Do not use in RAS hold mold.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-27. Restriction on the 2-way associative function of the instruction cache

#### [Description]

WAY control information will be incorrect and instructions corrupted as a result if any address A is a miss-hit, the following address B is a cache-hit, and the address A is a hit.

# [Workaround]

There is no workaround.

Use 4K(2K)-Direct mode instead of the 8K(4K)-2way associative function.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-28. Forced stop of external DMA transfer in DMA line transfer mode

# [Description]

The DMA will occupy the VSB when the external DMA transfer stop signal (IDMASTP) is active in DMA line transfer mode. As a result, the CPU will no longer be able to access the VSB and the system may hangs up.

# [Workaround]

Do not use IDMASTP in line transfer mode. In addition, use the IDMASTP signal with single-step transfer mode, not line transfer mode.

This bug has been corrected in the IE-V850E-MC with control code C.

This bug has been corrected in the IE-V850E-MC-A with control code E.

# a-29. Restriction on reading DCHC register when DMA 2-cycle transfer is complete

#### [Description]

The TC bit may be cleared to 0 before it is read as 1 when the DCHC register is read upon completion of DMA transfer in 2-cycle transfer mode from one RAM connected to the VDB bus to another RAM connected to the VDB.

# [Workaround]

Do not use RAM-to-RAM DMA transfer. Moreover, use three or fewer VSWL registers.

\* This applies only when developing a system LSI. This restriction does not apply when using the V850E/MA1, V850E/MA2, V850E/IA1, and V850E/IA2.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-30. Restriction on conflict between SDRAM initialization and SELFREF input

# [Description]

If the system enters standby mode or SELFREF pin input generates a self-refresh cycle before initialization of the SDRAM is set (before writing to the SCR register), the following SDRAM cycle will be incorrect.

# [Workaround]

Do not allow the system to enter standby mode or SELFREF pin input before SDRAM initialization setting is completed.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-31. Restriction on halfword writing to BSC, BCC, DWC0, and DWC1 registers

# [Description]

Data cannot be written correctly to the higher 8 bits (8 to 15) of the BSC, BCC, DWC0, and DWC1 register with halfword (16-bit) write.

The following bugs occur during emulation memory access as a result of this restriction.

(Not applicable to target memory access.)

- The IDLE-state set with the BCC register is not inserted in CS4 to CS7.

- The bus size for CS4 to CS7 does not change to the value set in the BSC register.

- DATA-wait set with the DWC0 register is not inserted in CS2 to CS3.

- DATA-wait set with the DWC1 register is not inserted in CS6 to CS7.

# [Workaround]

Before performing halfword write to set the BSC, BCC, DWC0, and DWC1 registers, byte-write the data which is to be set to the higher 8 bits to the lower 8 bits and then perform halfword write.

**Example:** When writing 0x1234 to BSC (0xffff066)

# Example of access without workaround (The bug occurs in this case.)

| movhi | 0xffff, r0, r10   |

|-------|-------------------|

| ori   | 0xf0000, r10, r10 |

| ori   | 0x1234, r0, r11   |

| st.h  | r11, 0x66[r10]    |

# Example of access with workaround (The bug does not occur in this case.)

| movhi | 0xffff, r0, r10  |                                                   |

|-------|------------------|---------------------------------------------------|

| ori   | 0xf0000, r10, r1 | 0                                                 |

| ori   | 0x12, r0, r11    |                                                   |

| st.b  | r11, 0x66[r10]   | $\leftarrow$ Write higher 8 bits to lower 8 bits. |

| ori   | 0x1234, r0, r11  |                                                   |

| st.b  | r11, 0x66[r10]   | ← Halfword write 0x1234                           |

This bug has been corrected in the IE-V850E-MC with control code C.

This bug has been corrected in the IE-V850E-MC-A with control code E.

# a-32. Restriction on SDRAM write operation

#### [Description]

Data output from the second cycle in a sequence of SDRAM write cycles completes half a clock cycle earlier than originally intended, and, as a result it may not be possible to write to the SDRAM.

# [Workaround]

Do not perform word data access when using the data bus with a 16-bit width. In the case of an 8-bit bus width, do not perform halfword data access or word data access.

This restriction has been corrected in the IE-V850E-MC with control code C.

This restriction has been corrected in the IE-V850E-MC-A with control code E.

# a-33. Restriction on DRAM fetch immediately after block DMA transfer from DRAM to internal RAM [Description]

The OE is not asserted at the first fetch cycle if DRAM fetch is performed immediately after block DMA transfer from DRAM to internal RAM. As a result, illegal data is fetched.

# [Workaround]

There is no workaround.

This restriction has been corrected in the IE-V850E-MC with control code B.

This restriction has been corrected in the IE-V850E-MC-A with control code D.

# a-34. Restriction on instruction cache (2)

[Description]

(1) Be sure to execute the instruction below before setting the cache configuration register (BHC) with the program settings immediately after a reset.

st.h r0, 0x0fffff072[r0]

After executing this instruction, the cache can be enabled by setting the BHC register to "instruction cache enabled."

- (2) The auto-fill function can only be used with WAY0. Be sure to write 0 to bit 5 of the ICC register.

- (3) An instruction that sets the BHC register cannot be used to change the cache settings of the area in which the instruction itself exists. For example, A BHC setting instruction in the CS0 field cannot be used to change the CS0 field from a cache disabled area to a cache enabled area, or from a cache enabled area to a cache disabled area.

However, instructions in a memory area connected to VFB or VDB can be used to change cache settings for all CS fields.

[Workaround]

There is no workaround. Please regard this as a permanent restriction.

# a-35. Restriction on SLD instruction

[Description]

The bug occurs in the following three types of instruction sequences (The asterisks below indicate any parameter).

In a situation where the value loaded by an instruction (this value is stored in register  $rX^{1}$ ) is updated<sup>2)</sup> by another instruction, if an SLD instruction (sld \*,rX) follows immediately after the instruction to update rX (yyy \*,rX), these two instructions are issued at the same time. At this time, if an instruction that follows the SLD instruction uses the rX register, the value that was loaded first (not updated) is used by the instruction<sup>3)</sup> even though the register is correctly updated.

Instruction sequence type 1

<1> xxx \*

<2> sld \* , rX

← 1) The value of rX register is loaded by the first instruction

<3> yyy \* , rX

← 2) rX is updated by another instruction

<4> sld \* , rY

<5> Instruction that uses value of rX

← 3) The old rX value from <2> is used instead of the updated rX value from <3>.

# Instruction sequence type 2

<1> ld/sld \* , rX

← 1) The value of rX register is loaded by the first instruction

<2> xxx (One or more instructions)

<3> yyy \* , rX

← 2) rX is updated by another instruction

<4> sld \* , rY

<5> Instruction that uses value of rX

← 3) The old rX value from <1>is used instead of the updated rX value from <3>.

# Instruction sequence type 3

<1> ld/sld \* , rX

← 1) The value of rX register is loaded by the first instruction

<2> Any instruction sequence that does not perform a memory read.

<3> xxx (One or more instructions)

<4> yyy \* , rX

← 2) rX is updated by another instruction

<5> sld \* , rY

<6> Instruction that uses value of rX

← 3) The old rX value from <1> is used instead of the updated rX value from <4>.

The conditions under which this bug occurs differ depending on the combination of the CPU and emulator used. The conditions of occurrence for each CPU are explained below.

a) Details and conditions of occurrence on system LSI development

(Emulator IE-V850E-MC-A + IE-V850E-MC-EM1-A/B)

The bug occurs if any of the three types of instruction sequence shown below is executed with one of the following fetch conditions.

- 1) Fetch from emulation IROM or IRAM

- 2) Fetch from VSB bus when 32-bit access is 2clk or less

- 2a) 32bit-0/1wait or 16bit-0wait on VSB bus

- 2b) SRAM cycle with 32bit-0wait when using Nx85E500 memory controller

- 3) Fetch from VSB bus under all conditions when iCACHE enabled area is used

#### Instruction sequence type 1

<1> xxx \* (Instruction in **Note 1**)

<2> sld \* , rX (Emulator accesses IRAM)

<3> yyy \* , rX (Instruction in **Note 2**)

<4> sld \* , rY (Emulator accesses IRAM)

<5> Instruction that uses value of rX

# Instruction sequence type 2

<1> Id/sld \* , rX (Emulator accesses IRAM)

<2> xxx (One or more instructions) (Instruction in **Note 3**)

<3> yyy \* , rX (Instruction in **Note 2**)

<4> sld \* , rY (Emulator accesses IRAM)

<5> Instruction that uses value of rX

# Instruction sequence type 3

<1> Id/sld \* , rX (VSB bus access)

<2> Any instruction sequence that does not perform a memory read.

<3> xxx (One or more instructions) (Instruction in **Note 3**)

<4> yyy \* , rX (Instruction in **Note 2**)

<5> sld \* , rY (Emulator accesses IRAM)

<6> Instruction that uses value of rX

# b) Details and conditions of occurrence with V850E/MA1

(Emulator IE-V850E-MC-A + IE-703107-MC-EM1)

The bug occurs if any of the three types of instruction sequence shown below is executed with a fetch from emulator IRAM or IROM.

# Instruction sequence type 1

<1> xxx \* (Instruction in **Note 1**)

<2> sld \* , rX (Emulator accesses IRAM)

<3> yyy \* , rX (Instruction in **Note 2**)

<4> sld \* , rY (Emulator accesses IRAM)

<5> Instruction that uses value of rX

# Instruction sequence type 2

<1> Id/sld \* , rX (Emulator accesses IRAM)

<2> xxx (One or more instructions) (Instruction in **Note 3**)

<3> yyy \* , rX (Instruction in **Note 2**)

<4> sld \* , rY (Emulator accesses IRAM)

<5> Instruction that uses value of rX

# Instruction sequence type 3

<1> Id/sId \* , rX (See ♦1 below)

<2> Any instruction sequence that does not perform a memory read.

<3> xxx (One or more instructions) (Instruction in **Note 3**)

<4> yyy \* , rX (Instruction in **Note 2**)

<5> sld \* , rY (Emulator accesses IRAM)

<6> Instruction that uses value of rX

- ♦1: Only when an Id/sId instruction is fetched from EDO DRAM for which data access wait is 0, or SDRAM. Does not apply in the case of access to page ROM, SRAM or EDO DRAM for which data access wait is 1 or more.

- c) Details and conditions of occurrence with V850E/IA1

(Emulator IE-V850E-MC + IE-703116-MC-EM1)

The bug occurs if any of the two types of instruction sequence shown below is executed with a fetch from emulator IRAM or IROM.

```

Instruction sequence type 1

```

<1> xxx \* (Instruction in **Note 1**)

<2> sld \* , rX (Emulator accesses IRAM)

<3> yyy \* , rX (Instruction in **Note 2**)

<4> sld \* , rY (Emulator accesses IRAM)

<5> Instruction that uses value of rX

Instruction sequence type 2

<1> Id/sld \* , rX (Emulator accesses IRAM)

<2> xxx (One or more instructions) (Instruction in **Note 3**)

<3> yyy \* , rX (Instruction in **Note 2**)

<4> sld \* , rY (Emulator accesses IRAM)

<5> Instruction that uses value of rX

Instruction sequence type 3 is not applicable to the V850E/IA1.

- **Note 1**: One of the following instructions using a register other than r0 or r30.

mov, not, satsubr, satsub, satadd, zxb, zxh, sxb, sxh, or, xor, and, subr, sub, add, shr, sar, shl

- **Note 2**: One of the following instructions, writing to rX (rX is any register other than r0 and r30.) mov, not, satsubr, satsub, satadd, zxb, zxh, sxb, sxh, or, xor, and, subr, sub, add, shr, sar, shl

- **Note 3**: One of the following instructions, writing to any register other than r0 and rX, that does not use rX.

mov, not, satsubr, satsub, satadd, zxb, zxh, sxb, sxh, or, xor, and, subr, sub, add, shr, sar, shl, addi, movea, movhi, satsubi, ori, xori, andi, setf, ldsr, stsr, sasf, cmov, bsw, bsh, hsw

# [Workaround]

NEC Electronics provides a check tool. Use this tool to check for the affected instruction sequence. Refer to the accompanying Readme file for details of how to use the check tool. Use one of the following remedies to avoid the problem if the check tool finds an affected instruction sequence.

a) Replace all SLD instructions with LD instructions.

This is possible using a compiler option with the GHS compiler only.

b) Insert a NOP instruction immediately after the affected SLD instruction.

The NEC Electronics compiler (CA850) provides an option to do this.

c) Change the instruction immediately before the affected SLD instruction. Assembly code can be modified if the SLD instruction is not a branch destination.

Use workaround a) or b) if you are using a C source compiler.

This restriction has been corrected in the IE-V850E-MC with control code D.

This restriction has been corrected in the IE-V850E-MC-A with control code F.

\* Contact the Development Tool Support Center at the address or number below for details of the search tool and compiler updates.

# a-36. I/O that cannot be used when using a VSB bus

[Description]

The following I/O addresses cannot be used when using a VSB bus (including image area).

64 MB mode: 3FFF480H to 3FFF4BEH 256 MB mode: FFFF480H to FFFF4BEH

[Workaround]

There is no workaround.

This restriction has been corrected in the IE-V850E-MC with control code D.

This restriction has been corrected in the IE-V850E-MC-A with control code F.

# a-37. Restriction of instruction cache (3)

- (1) A bug occurs depending on the timing of an interrupt issued to the CPU. If execution returns from an interrupt when the cache is not refilled with data, a hit occurs at an address that is not refilled. As a result, the CPU fetches illegal data and hangs up.

- (2) If TAG is cleared by the ICC register, four lines of TAG (one line of cache data consists of 4 words), lines 0 through 3 (INDEX = 00h through 03h), may not be cleared, depending on the operation status of the cache before TAG is cleared.

- (3) If the halt instruction is executed and then the halt mode is released, icache may return an illegal instruction to the CPU, resulting in a hang-up.

#### Conditions of occurrence

Bug (1) occurs under the following condition.

If a memory area including interrupt handler addresses (0x00000000h to 0x00000800h) is set as a cacheable area by the BHC register.

This bug does not occur under the following conditions.

- 1) If the memory area including interrupt handler addresses is set as an uncached area

- 2) If the memory area including interrupt handler addresses is connected to VFB and if bits 0, 4, 8, and 12 of the chip area select control register 0 (CSC0) are all cleared to 0 (so that VDCSZ does

not become active)

Bug (2) occurs in all the conditions where the instruction cache is used.

Bug (3) occurs under the following conditions.

If the halt instruction is in the icache visible area and if that halt instruction is not at the beginning of a 4-word boundary (If the halt instruction at an address other than address [3:0] = 4'b0000)

# [Workaround]

# **Workaround for restriction (1)**

Implement any of the following workarounds <1> to <3> below in software.

- <1> Set the memory area including interrupt handler addresses (0x00000000h to 0x00000800h) as an uncached area using the BHC register.

- <2> If it is necessary to set a CS (chip select) area including interrupt handler addresses as a cacheable area and if an uncached memory area exists on the other CS area.

Branch to the uncached area once and then branch to the original interrupt service routine after branching to the interrupt handler address. Add the shaded instructions below.

# (Example) .offset 0x80 (Interrupt handler address) jr INT0\_UC .section "uncache" -- Uncached area INT\_UC: ir INT0 .section "cache" -- Cacheable area (original interrupt service routine) INT0: ... ... reti

<3> If it is necessary to set a CS (chip select) area including interrupt handler addresses as a cacheable area and if an uncached memory area does not exist in the other CS area

Immediately after branching to the interrupt handler address, branch to different TAG lines in the cacheable area more than four times, and then branch to the original interrupt service routine. Add the shaded instructions below.

```

(Example)

.offset 0x80 (Interrupt handler address)

INT0_DMY

.section "dmy"

-- Cacheable area

INTO_DMY:

line0

nop; nop; nop; nop; nop; nop; nop;

line0:

line1

nop; nop; nop; nop; nop; nop;

line1:

line2

nop; nop; nop; nop; nop; nop;

line2:

line3

nop; nop; nop; nop; nop; nop;

line3:

INT0

.section "cache"

-- Cacheable area (original interrupt service routine)

INT0:

(It is necessary that an instruction string of 1 line (4

words) or more exist to completely update the

contents of the TAG buffer.)

reti

```

This restriction has been corrected in the IE-V850E-MC with control code D.

This restriction has been corrected in the IE-V850E-MC-A with control code F.

# **Workaround for restriction (2)**

To clear TAG in software, clear TAG two times (write to the ICC register and wait for completion). (Example)

mov 0x3,r2

LOP0:

Id.h ICC[r0],r1cmp r0,r1bnz LOP0st.h r2,ICC[r0]

LOP1: -- TAG cleared first time

ld.h ICC[r0],r1

```

cmp r0,r1

bnz LOP1

st.h r2,ICC[r0]

LOP2: -- TAG cleared second time

Id.h ICC[r0],r1

cmp r0,r1

bnz LOP2

```

Please regard this as a permanent restriction.

# Workaround for restriction (3)

```

Allocate the halt instruction to the beginning of a 4-word boundary by software.

```

```

(Allocate the halt instruction to address [3:0] = 4'b0000.)

```

```

(Example in assembler) ir EXIT

```

```

.section "tmp2", .text >0x0402800

EXIT:

halt

(Example in C)

asm("align 16");

```

asm("halt");

This restriction has been corrected in the IE-V850E-MC with control code D.

This restriction has been corrected in the IE-V850E-MC-A with control code F.

# a-38. Restriction on DMAAK signal during DMA line transfer

[Description]

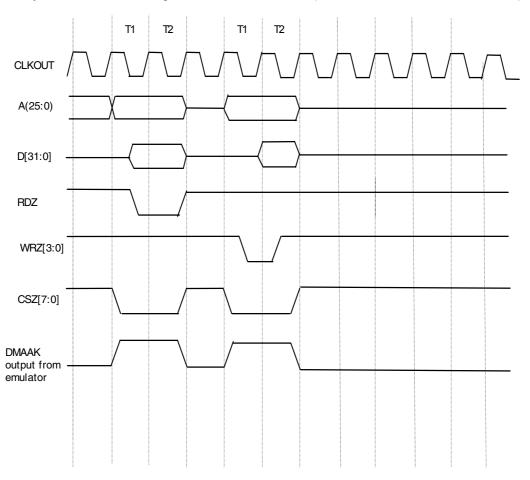

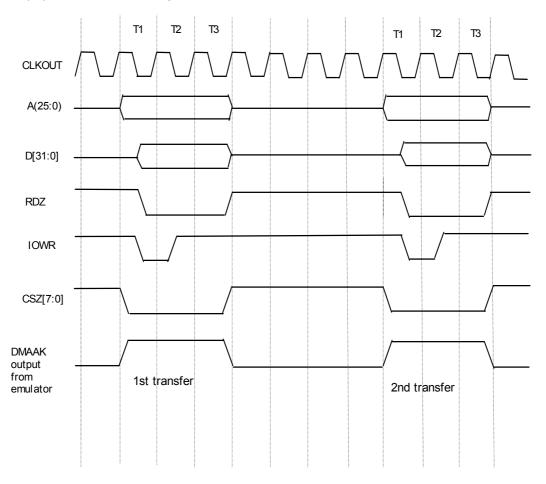

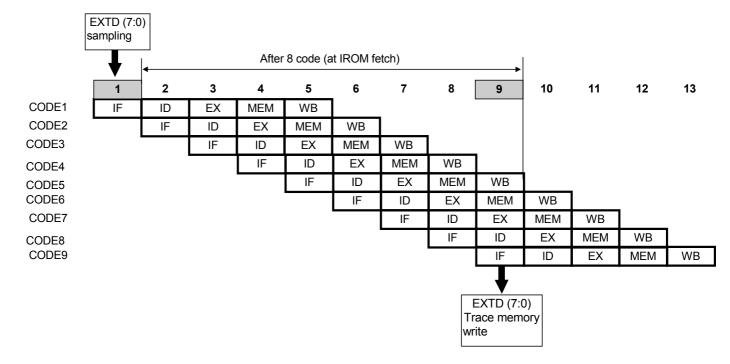

The DMAAK signal is output at the same timing as the NB85E core output signal during DMA line transfer (the output timing from an in-circuit emulator is below).

-- Clear the least significant bit to 0 in the hex mode.

When developing V850E/MA1, MA2:

This restriction does not apply because these products do not support line transfer.

• When developing V850E/IA1, IA2:

This restriction does not apply because these products do not support line transfer.

• When developing a system LSI:

This restriction does not apply and the DMAAK signal is output correctly as a DMACTV signal.

# 2-cycle line transfer timing from in-circuit emulator (external SRAM $\rightarrow$ external SRAM)

# a-39. Restriction caused by interrupt input during execution of bit manipulation instruction

[Description]

If a bit manipulation instruction access (set1, clr1, or not1) and an interrupt request to the following peripheral registers (in the NPB field) contend, two more addresses are illegally written to the interrupt return address saving registers (EIPC and FEPC) as interrupt return addresses, and execution branches to the illegal addresses when it has returned from the interrupt routine. The contending interrupts are all maskable interrupts and the non-maskable interrupt (NMI).

- Peripheral registers -

- When developing V850E/MA1 or IA1

All registers mapped to 0xFFFF100 to 0xFFFF1FF

All registers mapped to 0xFFFF900 to 0xFFFF9FF

- When developing a system LSI (64 MB mode)

All registers mapped to 0x3FFF100 to 0x3FFF1FF

All registers mapped to 0x3FFF900 to 0x3FFF9FF

- When developing a system LSI (256 MB mode)

All registers mapped to 0xFFFF100 to 0xFFFF1FF

All registers mapped to 0xFFFF900 to 0xFFFF9FF

This bug occurs in the in-circuit emulator (IE-V850E-MC-A or IE-V850E-MC) and does not apply to the target device (V850E/MA1, IA1, or NB85E core).

# Caution This bug does not occur if all the following conditions are satisfied:

- Interrupts are always disabled (DI status) when the peripheral registers are accessed.

- If NMI is not used or if NMI is never enabled when a peripheral register is accessed (when NMI is

used to release the standby mode)

# [Workaround]

- (1) The above bug can be prevented in any of the following ways if NMI is not used or if NMI is never enabled when a peripheral register is accessed (when NMI is used to release the standby mode):

- a) Always access the peripheral register (by using a bit manipulation instruction) in the DI status (interrupts are disabled).

#### Save PSW

- $\rightarrow$  di instruction

- → Access register with bit manipulation instruction.

- → Restore PSW

- b) Disable interrupts (pending) by setting the interrupt mask registers (IMR0 to IMR3) when the peripheral register is accessed (by using a bit manipulation instruction).

Save values of IMR0 to IMR3.

- → Write values of IMR0 to IMR3 to 0xffff (disable interrupt servicing).

- → Access peripheral register (by using bit manipulation instruction).

- → Write saved values of IMR0 to IMR3.

- c) Do not use a bit manipulation instruction to access the peripheral register. Use "Id instruction  $\rightarrow$  bit operation with and/or instruction  $\rightarrow$  st instruction" instead to manipulate bits.

- Refer to "NEC Electronics Compiler Coding Example" for coding with the NEC Electronics compiler.

- Refer to "GHS Compiler Coding Example" for coding with the GHS compiler.

- (2) If there is a possibility that NMI is enabled while the peripheral register is accessed, do not use a bit manipulation to access the peripheral register. Use "Id instruction → bit operation with and/or instruction → st instruction" to execute a bit operation and to prevent the above bug.

- Refer to "NEC Electronics Compiler Coding Example" for coding with the NEC Electronics compiler.

- Refer to "GHS Compiler Coding Example" for coding with the GHS compiler.

This restriction has been corrected in the IE-V850E-MC with control code D.

This restriction has been corrected in the IE-V850E-MC-A with control code F.

# [Other]

- (1) If you use the real-time OS (RX850 or RX850 Pro)

- This bug does not apply to task processing because the task processing of the real-time OS does not use bit manipulation instructions.

- (2) The results of investigations into the middleware are as follows. Consult the Development Tool Support Center (toolsupport@lsi.jp.nec.com) for middleware other than shown below.

| AP30100-B03  | Middleware (JPEG)                          | Not applicable                   |

|--------------|--------------------------------------------|----------------------------------|

| AP30100-B12  | Audio codec middleware (True Speech8.5)    | Not applicable                   |

| AP30200-B03  | Middleware (JPEG)                          | Not applicable                   |

| AP703000-B01 | Middleware (MH/MR/MHR)                     | Not applicable                   |

| AP703000-B02 | Middleware (JBIG)                          | Not applicable                   |

| AP703000-B03 | Middleware (JPEG)                          | Not applicable                   |

| AP703000-B04 | Middleware (ADPCM)                         | Not applicable                   |

| AP703000-B07 | Middleware (speech recognition)            | Applied to user-own coding block |

| AP703000-B08 | Middleware (TTS)                           | Not applicable                   |

| AP703000-B09 | Middleware hand-written character recognit | ion Not applicable               |

# [NEC Electronics Compiler Coding Example]

a) To rewrite all the bit manipulation instructions accessing the peripheral register to "ld instruction  $\rightarrow$  bit operation with and/or  $\rightarrow$  st instruction" for coding in the assembler

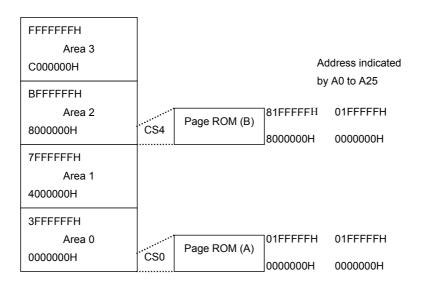

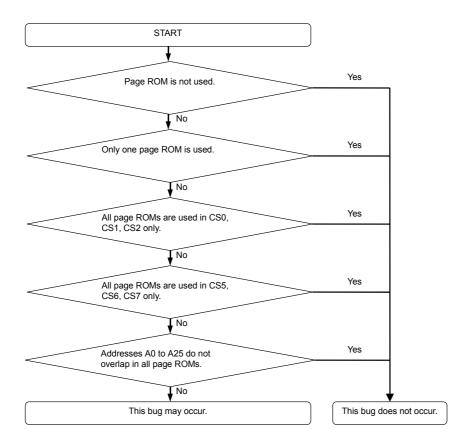

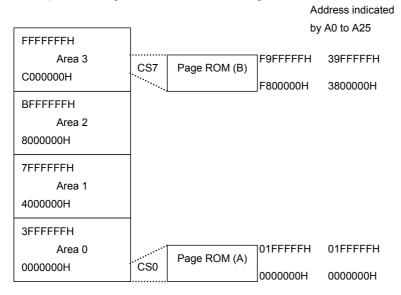

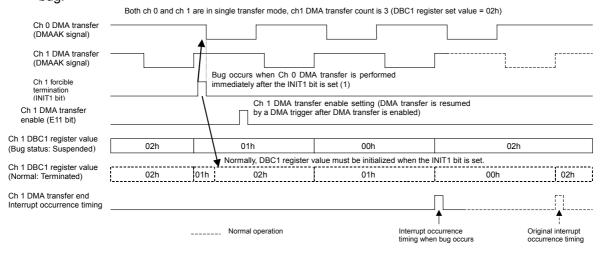

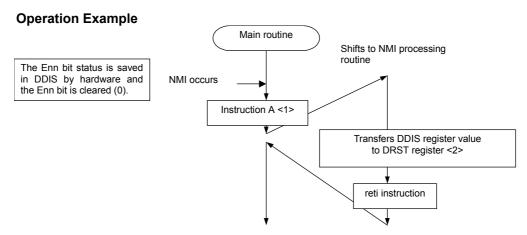

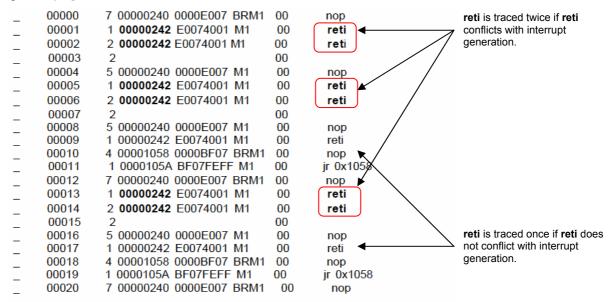

# • Avoiding set1 instruction