# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                 |                      | Document<br>No.         | TN-RL*-A0140A/E                                                              | Rev. | 1.00 |  |

|-----------------------|---------------------------------------------------------------------------------------------------------|----------------------|-------------------------|------------------------------------------------------------------------------|------|------|--|

| Title                 | Correction for Incorrect Description Notice R<br>Descriptions in the User's Manual: Hardware<br>Changed | _78/G24<br>Rev. 1.10 | Information<br>Category | Technical Notification                                                       |      |      |  |

|                       |                                                                                                         | Lot No.              |                         |                                                                              |      |      |  |

| Applicable<br>Product | RL78/G24 Group                                                                                          | All lots             | Reference<br>Document   | RL78/G24 User's Manual: Hardware<br>Rev. 1.10<br>R01UH0961EJ0110 (Nov. 2023) |      |      |  |

This document describes misstatements found in the RL78/G24 User's Manual: Hardware Rev. 1.10 (R01UH0961EJ0110).

## **Corrections**

| Applicable Item                                                                 | Applicable Page                                   | Contents                       |

|---------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|

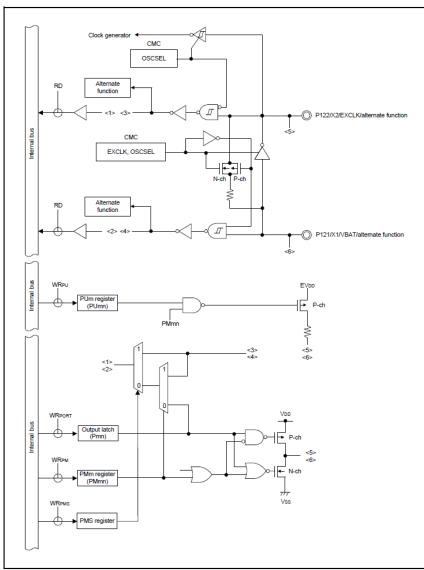

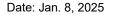

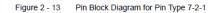

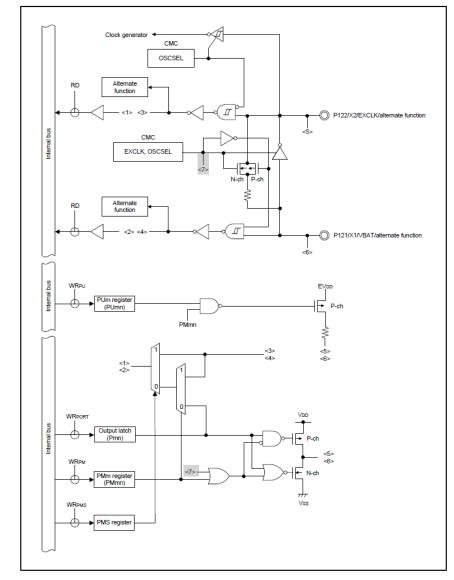

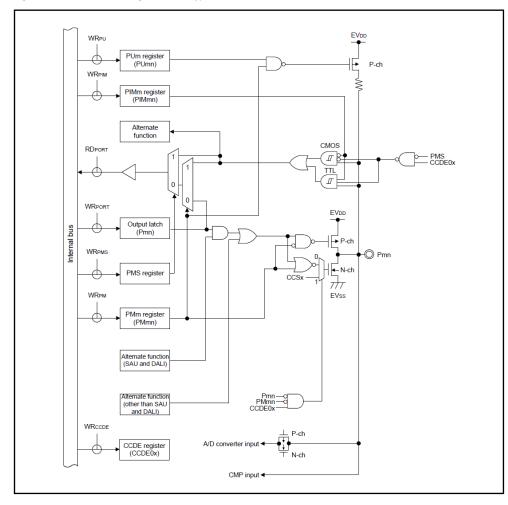

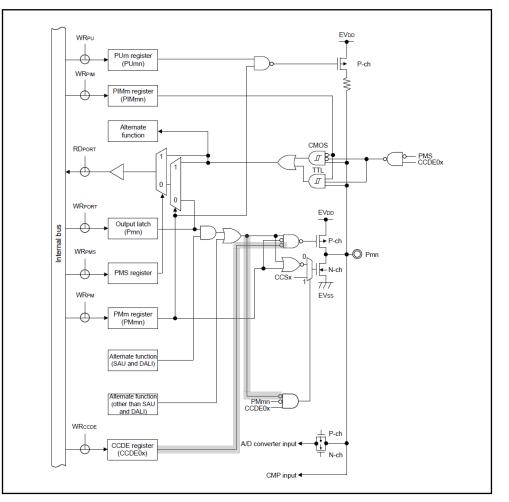

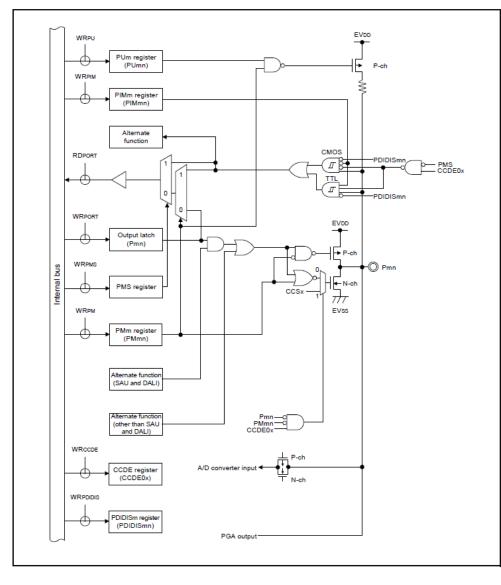

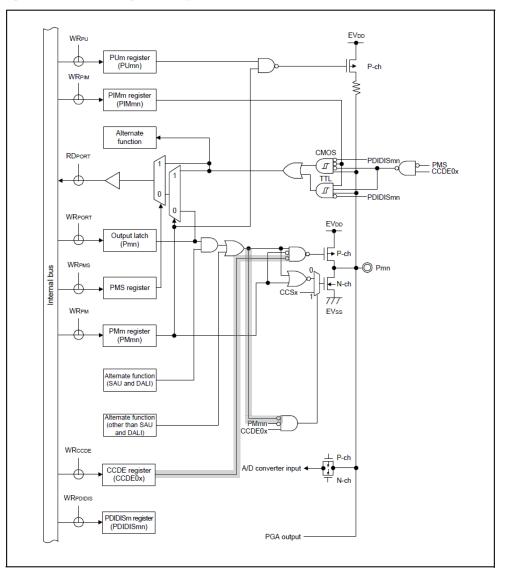

| 2.4 Block Diagrams of Pins                                                      | Page 89, Page 96, Page 102,<br>Page 103, Page 104 | Incorrect descriptions revised |

| 20.3.9 Analog input channel specification register (ADS)                        | Page 1106                                         | Incorrect descriptions revised |

| 20.3.10 Analog input channel specification registers n for advanced mode (ADSn) | Page 1107                                         | Incorrect descriptions revised |

| 20.6.2 Software trigger no-wait mode (select mode, one-shot conversion mode)    | Page 1120                                         | Incorrect descriptions revised |

| 24.3.8 Serial status registers mn (SSRmn) (mn<br>= 00 to 03, 10, 11)            | Page 1244                                         | Incorrect descriptions revised |

| 27.4.3 Repeat mode                                                              | Page 1594                                         | Incorrect descriptions revised |

| 29.4 Interrupt Servicing Operations                                             | Page 1634, Page 1636                              | Incorrect descriptions revised |

| 42.2 Operation List                                                             | Page 1840                                         | Incorrect descriptions revised |

| 43.2 Characteristics of the Oscillators                                         | Page 1845                                         | Incorrect descriptions revised |

| 43.3.2 Supply current characteristics                                           | Page 1856, Page 1859                              | Incorrect descriptions revised |

| 44.2 Characteristics of the Oscillators                                         | Page 1925                                         | Incorrect descriptions revised |

| 44.3.2 Supply current characteristics                                           | Page 1934, Page 1937                              | Incorrect descriptions revised |

| 44.4 AC Characteristics                                                         | Page 1942                                         | Incorrect descriptions revised |

#### Document Improvement

The above corrections will be made for the next revision of the User's Manual: Hardware.

Corrections in the User's Manual: Hardware

| No. |                      | Сс                                              | prrections and App | licable Items                                                                                                                                 | Pages in this document |

|-----|----------------------|-------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| NO. |                      | Document No.                                    | English            | R01UH0961EJ0110                                                                                                                               | for corrections        |

| 1   | 3.1 Men              | nory Space                                      |                    | Page 106, Page 107, Page 112                                                                                                                  | Page 3 to Page 5       |

| 2   | 20.3.3 A             | A/D converter mode re                           | egister 0 (ADM0)   | Page 1071, Page 1075 to Page 1077,<br>Page 1079, Page 1081, Page 1083,<br>Page 1084, Page 1086, Page 1088,<br>Page 1090, Page 1091, Page 1093 | Page 6 to Page 18      |

| 3   | 20.3.4 A             | VD converter mode re                            | egister 1 (ADM1)   | Page 1096                                                                                                                                     | Page 19                |

| 4   | 20.3.5 A             | VD converter mode re                            | egister 2 (ADM2)   | Page 1098, Page1099                                                                                                                           | Page 20, Page21        |

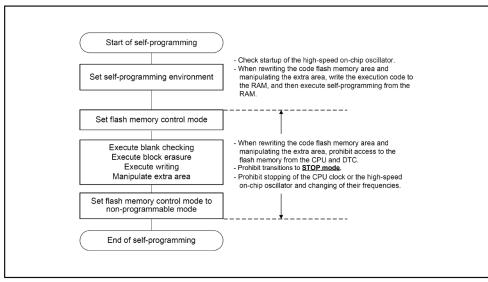

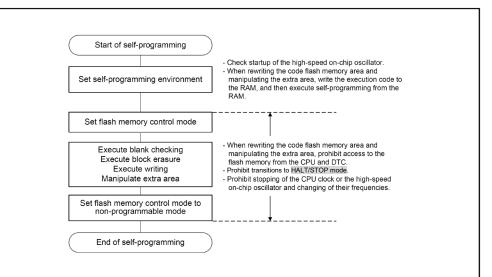

| 5   | 39.6.1 5             | Self-programming pro                            | cedure             | Page 1760                                                                                                                                     | Page 22                |

| 6   | 39.10.1              | Overview of the data                            | flash memory       | Page 1811                                                                                                                                     | Page 23                |

| 7   | 40.3 Se              | curity Settings for On                          | -chip Debugging    | Page 1814                                                                                                                                     | Page 24                |

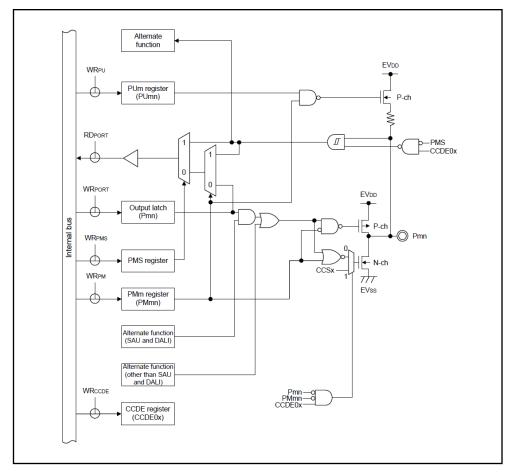

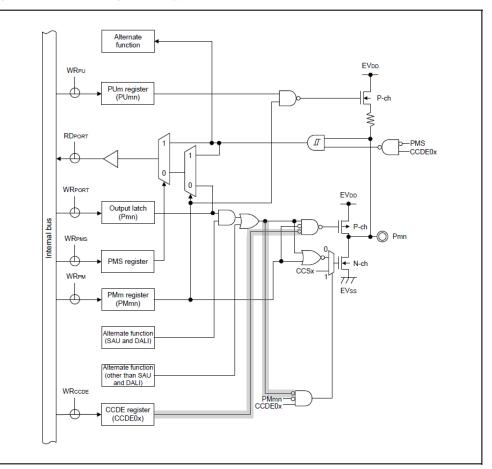

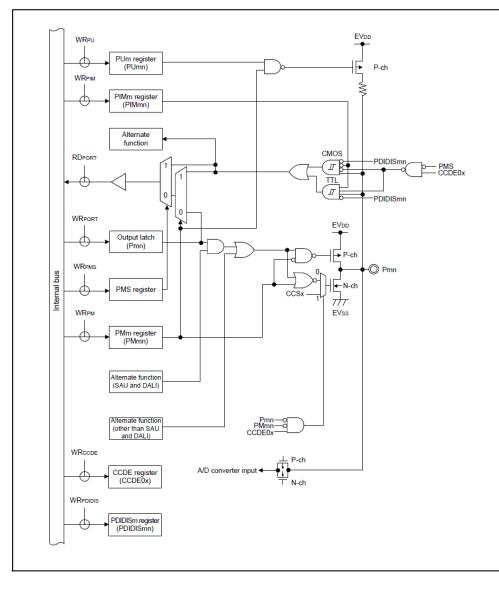

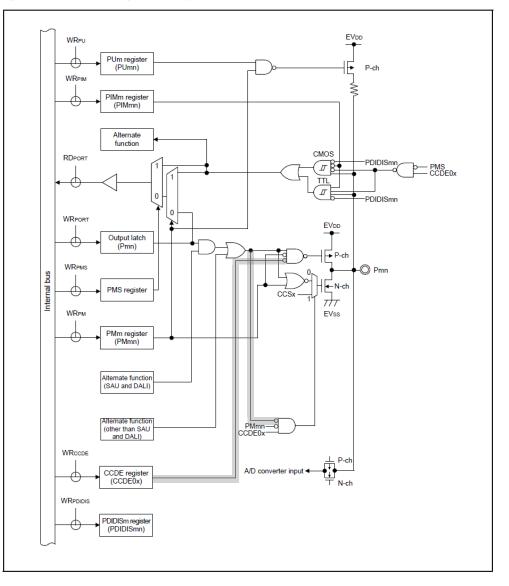

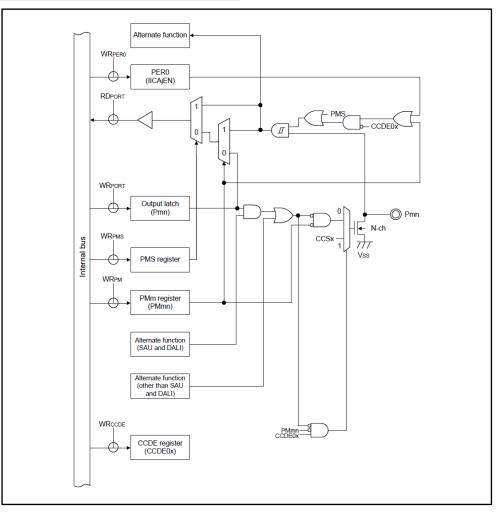

| 8   | 2.4 Bloc             | k Diagrams of Pins                              |                    | Page 89, Page 96, Page 102,<br>Page 103, Page 104                                                                                             | Page 25 to Page 30     |

| 9   | 20.3.9 A<br>register | Analog input channel :<br>(ADS)                 | specification      | Page 1106                                                                                                                                     | Page 31                |

| 10  |                      | Analog input channe<br>s n for advanced mod     |                    | Page 1107                                                                                                                                     | Page 32                |

| 11  |                      | Software trigger no-wa<br>one-shot conversion n |                    | Page 1120                                                                                                                                     | Page 33                |

| 12  |                      | Serial status registers<br>0 to 03, 10, 11)     | mn (SSRmn)         | Page 1244                                                                                                                                     | Page 34                |

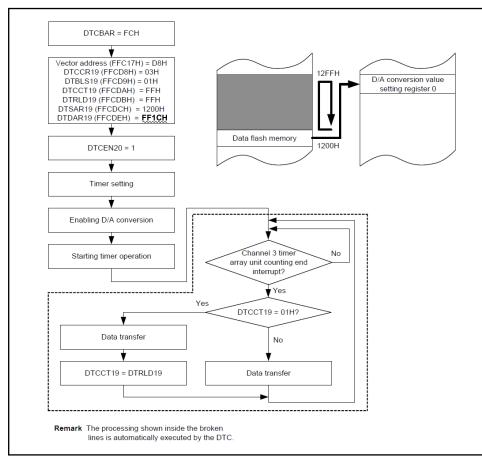

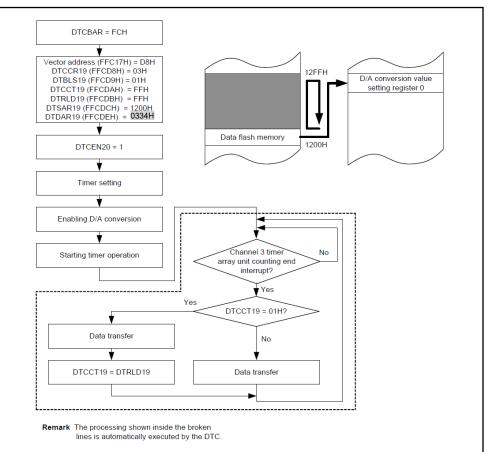

| 13  | 27.4.3 F             | Repeat mode                                     |                    | Page 1594                                                                                                                                     | Page 35                |

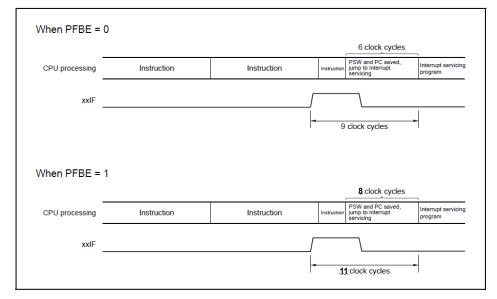

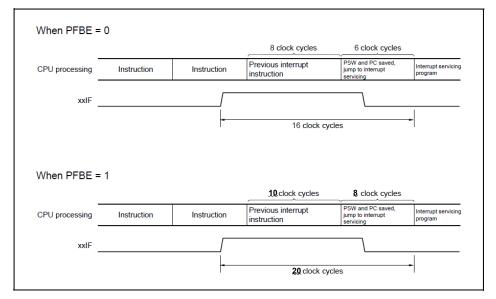

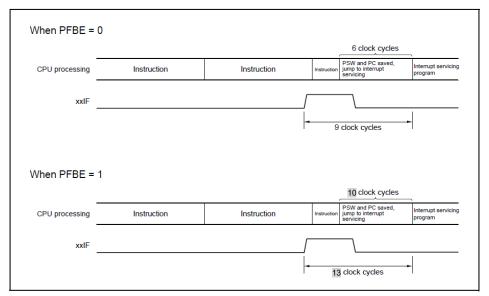

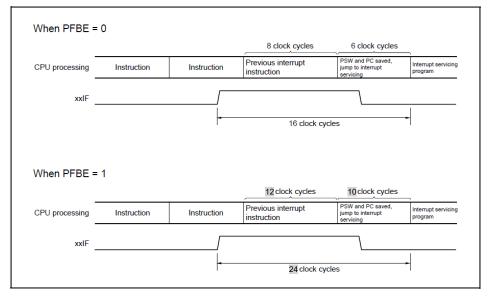

| 14  | 29.4 Inte            | errupt Servicing Oper                           | ations             | Page 1634, Page 1636                                                                                                                          | Page 36, Page 37       |

| 15  | 42.2 Op              | eration List                                    |                    | Page 1840                                                                                                                                     | Page 38                |

| 16  | 43.2 Ch              | aracteristics of the O                          | scillators         | Page 1845                                                                                                                                     | Page 39                |

| 17  | 43.3.2 5             | Supply current charac                           | teristics          | Page 1856, Page 1859                                                                                                                          | Page 40, Page 41       |

| 18  | 44.2 Ch              | aracteristics of the O                          | scillators         | Page 1925                                                                                                                                     | Page 42                |

| 19  | 44.3.2 \$            | Supply current charac                           | teristics          | Page 1934, Page 1937                                                                                                                          | Page 43, Page 44       |

| 20  | 44.4 AC              | Characteristics                                 |                    | Page 1942                                                                                                                                     | Page 45                |

Incorrect: Bold with underline; Correct: Gray hatched

## **Revision History**

RL78/G24 Correction for incorrect description notice

| Document Number | Issue Date    | Description                                       |

|-----------------|---------------|---------------------------------------------------|

| TN-RL*-A0135A/E | Apr. 26, 2024 | First edition issued                              |

|                 |               | Corrections No.1 to No.7 revised                  |

| TN-RL*-A0140A/E | Jan. 8, 2025  | Corrections No.8 to No.XX revised (this document) |

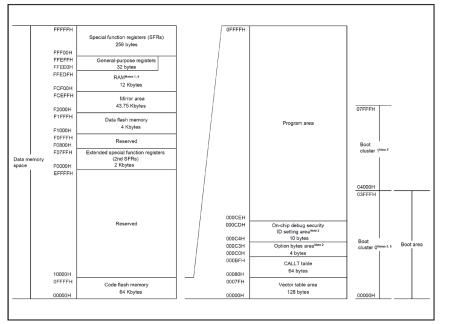

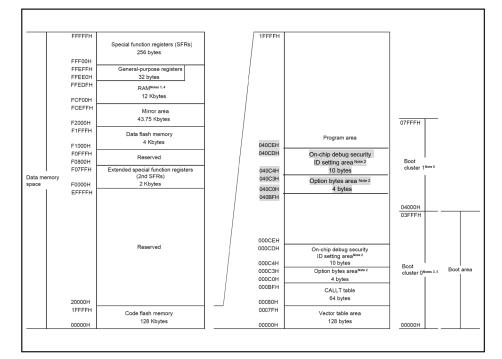

# 1. Memory Space (Page 106, Page107, Page 112)

Incorrect:

(Page 106)

Products in the RL78/G24 can access a 1 MB address space. For details, see Figures 3 - 1 and 3 - 2.

Figure 3 - 1 Memory Map (R7F101GxE (x = 6, 7, 8, A, B, E, F, G, J, L))

- Note 1. Instructions can be executed from the RAM area excluding the general-purpose register area.

- Note 2. When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

When boot swap is used: Set the option bytes to 000C0H to 000C3H and 040C0H to 040C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 040C4H to 040CDH.

(omitted)

Date: Jan. 8, 2025

## Correct:

Products in the RL78/G24 can access a 1 MB address space. For details, see Figures 3 - 1 and 3 - 2.

Figure 3 - 1 Memory Map (R7F101GxE (x = 6, 7, 8, A, B, E, F, G, J, L))

- Note 1. Instructions can be executed from the RAM area excluding the general-purpose register area.

- Note 2. When boot swapping is not to be used, that is, when the value of the BTFLG bit in the FLSEC register is 1, set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

When boot swapping is to be used or the value of the BTFLG bit in the FLSEC register is 0, set the option bytes to 000C0H to 000C3H and 040C0H to 040C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 040C4H to 040CDH.

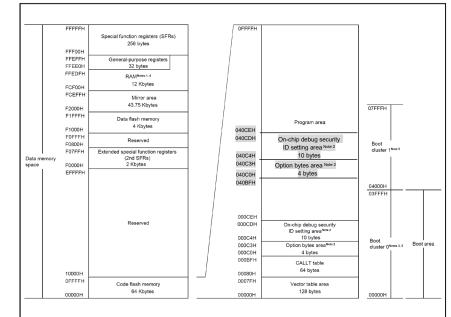

(Page 107)

#### Figure 3 - 2 Memory Map (R7F101GxG (x = 6, 7, 8, A, B, E, F, G, J, L))

- Note 1. Instructions can be executed from the RAM area excluding the general-purpose register area.

- Note 2. When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

When boot swap is used: Set the option bytes to 000C0H to 000C3H and 040C0H to 040C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 040C4H to 040CDH.

(omitted)

#### Figure 3 - 2 Memory Map (R7F101GxG (x = 6, 7, 8, A, B, E, F, G, J, L))

- Note 1. Instructions can be executed from the RAM area excluding the general-purpose register area.

- Note 2. When boot swapping is not to be used, that is, when the value of the BTFLG bit in the FLSEC register is 1, set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

When boot swapping is to be used or the value of the BTFLG bit in the FLSEC register is 0, set the option bytes to 000C0H to 000C3H and 040C0H to 040C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 040C4H to 040CDH.

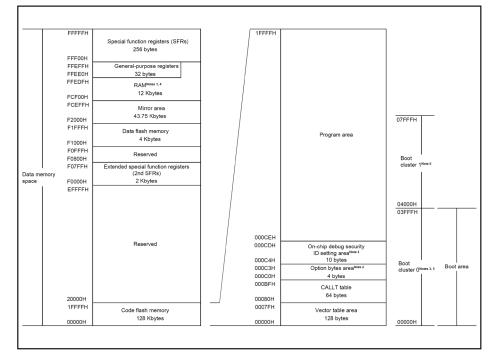

(Page 112)

#### (omitted)

#### 3. Option bytes area

A 4-byte area of 000C0H to 000C3H can be used as an option bytes area. Set the option byte at 040C0H to 040C3H when **the boot swap is used**. For details, see Section 38 Option Bytes.

4. On-chip debug security ID setting area

A 10-byte area of 000C4H to 000CDH and 040C4H to 040CDH can be used as an onchip debug security ID setting area. Set the on-chip debug security ID of 10 bytes at 000C4H to 000CDH when **the boot swap is not used** and at 000C4H to 000CDH and at 040C4H to 040CDH when **the boot swap is used**. For details, see Section 40 On-chip Debugging. Date: Jan. 8, 2025

(omitted)

3. Option bytes area

A 4-byte area of 000C0H to 000C3H can be used as an option bytes area. Set the option byte at 040C0H to 040C3H when boot swapping is to be used or the value of the BTFLG bit in the FLSEC register is 0. For details, see Section 38 Option Bytes.

4. On-chip debug security ID setting area

A 10-byte area of 000C4H to 000CDH and 040C4H to 040CDH can be used as an onchip debug security ID setting area. Set the 10-byte security ID for on-chip debugging at 000C4H to 000CDH when boot swapping is not to be used, that is, the value of the BTFLG bit in the FLSEC register is 1, and at both 000C4H to 000CDH and 040C4H to 040CDH when boot swapping is to be used or the value of the BTFLG bit in the FLSEC register is 0. For details, see Section 40 On-chip Debugging.

2. <u>20.3.3 A/D converter mode register 0 (ADM0) (Page 1071, Page 1075 to Page1077, Page1079, Page 1081, Page 1083, Page 1084, Page 1086, Page 1088, Page 1090, Page 1091, Page 1093 )</u>

Incorrect:

(Page 1071)

Figure 20 - 4 Format of A/D Converter Mode Register 0 (ADM0)

(omitted)

| ADCE | A/D voltage comparator operation control <sup>Note 2</sup> |

|------|------------------------------------------------------------|

| 0    | Stops A/D voltage comparator operation                     |

| 1    | Enables A/D voltage comparator operation                   |

Note 1. For details of the FR[2:0] and LV[1:0] bits and A/D conversion, see Table 20 - 6 Selection of A/D Conversion Time.

- Note 2. While in the software trigger no-wait mode or hardware trigger no-wait mode, the operation of the A/D voltage comparator is controlled by the ADCS and ADCE bits, and it takes 1  $\mu$  s + 2 cycles of the conversion clock (fAD) from the start of operation for the operation to stabilize. Therefore, immediately after the ADCS bit is set to 1 after at least 1  $\mu$  s + 2 cycles of the conversion clock (fAD) have elapsed from the time ADCE bit is set to 1, the conversion result becomes valid. When ADCS is set to 1 while ADCE = 0, A/D conversion starts after the stabilization wait time has passed. If ADCS is set to 1 before at least 1  $\mu$  s + 2 cycles of the conversion clock (fAD) have elapsed, ignore data of the first conversion.

- Caution 1. Change the ADMD, FR[2:0], and LV[1:0] bits while conversion is stopped (ADCS = 0, ADCE = 0).

- Caution 2. Setting change from ADCS = 1 and ADCE = 1 to ADCS = 1 and ADCE = 0 is prohibited.

- Caution 3. Do not change the ADCS and ADCE bits from 0 to 1 at the same time by using an 8-bit manipulation instruction. Be sure to follow the procedure described in 20.7 A/D Converter Setup Flowchart.

Caution 4. Do not set ADMS to 1 when the advanced mode is enabled.

Caution 5. Do not overwrite ADCS with 1 when the setting of ADCS is 1 in the advanced mode. Caution 6. Do not overwrite ADCE with 1 when the setting of ADCE is 1 in the advanced mode. Date: Jan. 8, 2025

#### Correct:

#### Figure 20 - 4 Format of A/D Converter Mode Register 0 (ADM0)

(omitted)

| ADCE | A/D voltage comparator operation control <sup>Note 2</sup> |

|------|------------------------------------------------------------|

| 0    | Stops A/D voltage comparator operation                     |

| 1    | Enables A/D voltage comparator operation                   |

- Note 1. For details of the FR[2:0] and LV[1:0] bits and A/D conversion, see Table 20 6 Selection of A/D Conversion Time.

- Note 2. While in the software trigger no-wait mode or hardware trigger no-wait mode, the operation of the A/D voltage comparator is controlled by the ADCS and ADCE bits, and it takes 1  $\mu$  s + 2 cycles of the conversion clock (fAD) from the start of operation for the operation to stabilize. Therefore, immediately after the ADCS bit is set to 1 after at least 1  $\mu$  s + 2 cycles of the conversion clock (fAD) have elapsed from the time ADCE bit is set to 1, the conversion result becomes valid. When ADCS is set to 1 while ADCE = 0, A/D conversion starts after the stabilization wait time has passed. If ADCS is set to 1 before at least 1  $\mu$  s + 2 cycles of the conversion clock (fAD) have elapsed, ignore data of the first conversion.

- Caution 1. Change the ADMD, FR[2:0], and LV[1:0] bits while conversion is stopped (ADCS = 0, ADCE = 0).

Caution 2. Setting change from ADCS = 1 and ADCE = 1 to ADCS = 1 and ADCE = 0 is prohibited.

Caution 3. Do not change the ADCS and ADCE bits from 0 to 1 at the same time by using an 8-bit manipulation instruction. Be sure to follow the procedure described in 20.7 A/D Converter Setup Flowchart.

Caution 4. Do not set ADMS to 1 when the advanced mode is enabled.

Caution 5. Do not overwrite ADCS with 1 when the setting of ADCS is 1 in the advanced mode.

- Caution 6. Do not overwrite ADCE with 1 when the setting of ADCE is 1 in the advanced mode.

- Caution 7. Following stoppage of conversion by setting the ADCS and ADCE bits to 0 from the

conversion standby or conversion state, wait for at least 5 µs before restoring the values of the bits to 1. Note that, when changing the settings of bits ADMD, FR2 to FR0, LV1, and LV0, start by setting the ADCS and ADCE bits to 0, then wait for at least 0.2 µs before changing the rest of the bits.

#### (Page 1075)

- Caution 1. If using the hardware trigger wait mode, setting the ADCS bit to 1 is prohibited (but the bit is automatically switched to 1 when the hardware trigger signal is detected). However, it is possible to clear the ADCS bit to 0 to specify the A/D conversion standby state.

- Caution 2. While in the one-shot conversion mode of the hardware trigger no-wait mode or advanced mode, the ADCS bit is not automatically cleared to 0 when A/D conversion ends. Instead, 1 is retained.

- Caution 3. Only rewrite the value of the ADCE bit when ADCS = 0 (while in the conversion stopped/conversion standby state).

- Caution 4. In advanced mode, three cycles of the fCLK clock are required from the occurrence of a trigger source until detection of the trigger. Table 20 5 lists the required numbers of clock cycles from the occurrence of a trigger or completion of the most recently executed conversion until A/D conversion starts in advanced mode.

- Caution 5. To complete A/D conversion, specify at least the following time as the hardware trigger interval:

Hardware trigger no-wait mode: 2 cycles of the fCLK clock + conversion start time + A/D conversion time

Hardware trigger wait mode: 2 cycles of the fCLK clock + conversion start time + A/D power supply stabilization wait time + A/D conversion time

Advanced mode: 3 cycles of the fCLK clock + conversion start time + A/D conversion time (omitted)

Caution 1. If using the hardware trigger wait mode, setting the ADCS bit to 1 is prohibited (but the bit is automatically switched to 1 when the hardware trigger signal is detected). However, it is possible to clear the ADCS bit to 0 to specify the A/D conversion standby state.

Caution 2. While in the one-shot conversion mode of the hardware trigger no-wait mode or advanced mode, the ADCS bit is not automatically cleared to 0 when A/D conversion ends. Instead, 1 is retained.

Caution 3. Only rewrite the value of the ADCE bit when ADCS = 0 (while in the conversion stopped/conversion standby state).

- Caution 4. In advanced mode, three cycles of the fCLK clock are required from the occurrence of a trigger source until detection of the trigger. Table 20 5 lists the required numbers of clock cycles from the occurrence of a trigger or completion of the most recently executed conversion until A/D conversion starts in advanced mode.

- Caution 5. To complete A/D conversion, specify at least the following time as the hardware trigger interval:

Hardware trigger no-wait mode: 2 cycles of the fcLK clock + conversion start time + A/D conversion time

Hardware trigger wait mode: 2 fCLK clock cycles + conversion start time + A/D power supply

stabilization wait time + A/D conversion time + 5µs

Advanced mode: 3 cycles of the fCLK clock + conversion start time + A/D conversion time (omitted)

© 2025 Renesas Electronics Corporation. All rights reserved.

Date: Jan. 8, 2025

## (Page 1076)

Table 20 - 6 Selection of A/D Conversion Time (1/11)

#### Normal modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait select mode and hardware trigger no-wait select mode)

|            | Conve<br>Conve |     |     |     |     |             |                           | Number of                           | Number of  | Number of<br>Clock      |           |                       |                       |                       | n Start Delay<br>utput Delay 1 |                  |

|------------|----------------|-----|-----|-----|-----|-------------|---------------------------|-------------------------------------|------------|-------------------------|-----------|-----------------------|-----------------------|-----------------------|--------------------------------|------------------|

| (AD<br>M1) | (ADMU)         |     |     |     |     | Mode        | Conversion<br>Clock (fAD) | Cycles for<br>Conversion Cycles for | Cycles for | Cycles for<br>Interrupt |           |                       | 2.4 ∨ ≤ /             | AVREFP ≤ VD           | o≤5.5 V                        |                  |

| ADL<br>SP  | FR2            | FR1 | FRO | LV1 | LVO |             |                           | Start Delay                         |            | Output<br>Delay         |           | fclk =<br>1 MHz       | fCLK =<br>4 MHz       | fCLK =<br>8 MHz       | fCLK =<br>16 MHz               | fCLK =<br>32 MHz |

| 0          | 0              | 0   | 0   | 0   | 0   | Normal<br>1 | fCLK/32                   | 1 fAD                               | 64 fad     | 1 fAD                   | 2112/fcLK | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited          | 66 µs            |

| 0          | 0              | 0   | 1   |     |     |             | fcLK/16                   | 1 fAD                               | 64 fad     | 1 fAD                   | 1056/fcLK | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 66 µs                          | 33 µs            |

| 1 | 1           | 0            | ( | 0 |  | fcLK/2 | 1 fad | 181 fAD | 1 fad | 366/fclk  | Setting prohibited | 91.5 µs  | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|-------------|--------------|---|---|--|--------|-------|---------|-------|-----------|--------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1           | 0            | 1 | 1 |  | fclk   | 1 fAD | 181 fAD | 1 fAD | 183/fCLK  | 183 µs             | 45.75 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| ¢ | Other<br>al | than<br>bove |   |   |  |        |       |         |       | Setting p | orohibited         |          |                       |                       |                       |

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0).

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use normal mode 2.

- Caution 5. When the internal reference voltage is selected for the + side reference voltage, normal modes 1 and 2 cannot be used. In such cases, use low voltage mode 1 or 2.

Remark fCLK: CPU/peripheral hardware clock frequency

Table 20 - 6 Selection of A/D Conversion Time (1/11)

Normal modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait select mode and hardware trigger no-wait select mode)

|            | Conve<br>Conve |     |     |     |     |             |                           | Number of                         | Number of           | Number of<br>Clock      |           | A/D Conversion Time (Conversion Start Delay Time +<br>Conversion Time + Interrupt Output Delay Time) |                       |                       |                       |                  |  |

|------------|----------------|-----|-----|-----|-----|-------------|---------------------------|-----------------------------------|---------------------|-------------------------|-----------|------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------------------|--|

| (AD<br>M1) |                | (   | ADM | ))  |     | Mode        | Conversion<br>Clock (fAD) | Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for | Cycles for<br>Interrupt |           |                                                                                                      | 2.4 ∨ ≤ /             | AVREFP ≤ Vo           | op ≤ 5.5 V            |                  |  |

| ADL<br>SP  | FR2            | FR1 | FRO | LV1 | LVO |             |                           | Start Delay                       | Conversion          | Output<br>Delay         |           | fclk =<br>1 MHz                                                                                      | fclk =<br>4 MHz       | fclk =<br>8 MHz       | fCLK =<br>16 MHz      | fCLK =<br>32 MHz |  |

| 0          | 0              | 0   | 0   | 0   | 0   | Normal<br>1 | fCLK/32                   | 1 fAD                             | 64 fad              | 1 fAD                   | 2112/fcLK | Setting<br>prohibited                                                                                | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 66 µs            |  |

| 0          | 0              | 0   | 1   |     |     |             | fcLk/16                   | 1 fad                             | 64 fad              | 1 fAD                   | 1056/fcLK | Setting<br>prohibited                                                                                | Setting<br>prohibited | Setting<br>prohibited | 66 µs                 | 33 µs            |  |

| 1                    | 1 | 0 | 0 | 1 |  | fcLK/2 | 1 fad | 181 fad   | 1 fad     | 366/fclk | Setting prohibited | 91.5 µs  | Setting<br>prohibited | Setting<br>prohibited | Setting prohibited    |

|----------------------|---|---|---|---|--|--------|-------|-----------|-----------|----------|--------------------|----------|-----------------------|-----------------------|-----------------------|

| 1                    | 1 | 0 | 1 |   |  | fclk   | 1 fAD | 181 fAD   | 1 fAD     | 183/fclk | 183 µs             | 45.75 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| Other than the above |   |   |   |   |  |        |       | Setting p | rohibited |          |                    |          |                       |                       |                       |

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0). When conversion is to be stopped while the A/D converter is on standby or is operating, wait for at least 0.2 µs before setting the FR[2:0] and LV[1:0] bits.

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use normal mode 2.

- Caution 5. When the internal reference voltage is selected for the + side reference voltage, normal modes 1 and 2 cannot be used. In such cases, use low voltage mode 1 or 2.

Remark fclk: CPU/peripheral hardware clock frequency

(Page 1077)

Table 20 - 6 Selection of A/D Conversion Time (2/11)

#### Low voltage modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait select mode and hardware trigger no-wait select mode)

|            |        | erter N<br>erter N |     |     |                           |                                                               |                                                |                                            |        | Number of                             |                                       |                                       |                                       |                                       | n Start Delay<br>utput Delay |                  |

|------------|--------|--------------------|-----|-----|---------------------------|---------------------------------------------------------------|------------------------------------------------|--------------------------------------------|--------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------------------------|------------------|

| (AD<br>M1) | (ADM0) |                    | Mo  |     | Conversion<br>Clock (fAD) | Number of<br>Clock<br>Cycles for<br>Conversion<br>Start Delay | Number of<br>Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for<br>Interrupt<br>Output |        | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.8 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.4 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.7 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V |                              |                  |

| ADL<br>SP  | FR2    | FR1                | FRO | LV1 | LVO                       |                                                               |                                                |                                            |        | Delay                                 |                                       | fCLK =<br>1 MHz                       | fclk =<br>4 MHz                       | fCLK =<br>8 MHz                       | fCLK =<br>16 MHz             | fCLK =<br>32 MHz |

| 0          | 0      | 0                  | 0   | 1   | 0                         | Low<br>voltage                                                | fCLK/32                                        | 1 fad                                      | 80 fad | 1 fad                                 | 2624/fclk                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited        | 82 µs            |

| 0          | 0      | 0                  | 1   |     |                           | 1                                                             | fCLK/16                                        | 1 fAD                                      | 80 fad | 1 fAD                                 | 1312/fclk                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | 82 µs                        | 41 µs            |

| 1 | 1            | 0            | 0  |  | fCLK/2 | 1 fad | 107 fAD | 1 fad | 218/fclk  | Setting<br>prohibited | 54.5 µs  | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|--------------|--------------|----|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1            | 0            | 1  |  | fclk   | 1 fAD | 107 fAD | 1 fAD | 109/fclk  | 109 µs                | 27.25 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| 0 | ther t<br>ab | han t<br>ove | he |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0).

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use low voltage mode 2 with the conversion clock (fAD) with a frequency of no more than 16 MHz.

Table 20 - 6 Selection of A/D Conversion Time (2/11)

2. Low voltage modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait select mode and hardware trigger no-wait select mode)

|            |     | erter I<br>erter I |     |      | ster 0<br>ster 1          |                                                               |                                                |                                            |         | Number of                             |                                       |                                       |                                       |                                       | on Start Delay<br>Output Delay |                  |

|------------|-----|--------------------|-----|------|---------------------------|---------------------------------------------------------------|------------------------------------------------|--------------------------------------------|---------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|--------------------------------|------------------|

| (AD<br>M1) |     |                    |     | Mode | Conversion<br>Clock (fAD) | Number of<br>Clock<br>Cycles for<br>Conversion<br>Start Delay | Number of<br>Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for<br>Interrupt<br>Output |         | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.8 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.4 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.7 V ≤<br>AVREFP :<br>VDD ≤<br>5.5 V |                                |                  |

| ADL<br>SP  | FR2 | FR1                | FRO | LV1  | LVO                       |                                                               |                                                | ,                                          |         | Delay                                 |                                       | fclk =<br>1 MHz                       | fclk =<br>4 MHz                       | fclk =<br>8 MHz                       | fCLK =<br>16 MHz               | fCLK =<br>32 MHz |

| 0          | 0   | 0                  | 0   | 1    | 0                         | Low<br>voltage                                                | fCLK/32                                        | 1 fad                                      | 80 fad  | 1 fad                                 | 2624/fclk                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited          | 82 µs            |

| 0          | 0   | 0                  | 1   |      |                           | 1                                                             | fcLk/16                                        | 1 fad                                      | 80 fad  | 1 fad                                 | 1312/fcLK                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | 82 µs                          | 41 µs            |

|            |     | _                  | _   |      |                           |                                                               |                                                |                                            |         |                                       |                                       |                                       |                                       |                                       |                                |                  |

| 1          | 1   | 0 0                |     |      |                           |                                                               | fCLK/2                                         | 1 fAD                                      | 107 fAD | 1 fAD                                 | 218/fclk                              | Setting<br>prohibited                 | 54.5 µs                               | Setting<br>prohibited                 | Setting<br>prohibited          | Setting          |

| 1 | 1 | 0             | 0  |  | fCLK/2 | 1 fAD | 107 fad | 1 fad | 218/fclk  | Setting<br>prohibited | 54.5 µs  | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |  |

|---|---|---------------|----|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|--|

| 1 | 1 | 0             | 1  |  | folk   | 1 fad | 107 fad | 1 fad | 109/fclk  | 109 µs                | 27.25 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |  |

| O |   | han th<br>ove | 1e |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |  |

Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0). When conversion is to be stopped while the A/D converter is on standby or is operating, wait for at least 0.2 µs before setting the FR[2:0] and LV[1:0] bits.

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use low voltage mode 2 with the conversion clock (fAD) with a frequency of no more than 16 MHz.

Date: Jan. 8, 2025

## (Page 1079)

Table 20 - 6 Selection of A/D Conversion Time (3/11)

#### 3. Normal modes 1 and 2 with A/D power supply stabilization wait time

(software trigger wait select mode and hardware trigger wait select mode  $^{Note\,1})$

|            |     | erter M<br>erter M            |     |     |      |                           |                                   | Number of<br>Clock    | Number of               | Number of<br>Clock    |           |                       |                       |                       | upply Stabiliz<br>pt Output Del |                  |

|------------|-----|-------------------------------|-----|-----|------|---------------------------|-----------------------------------|-----------------------|-------------------------|-----------------------|-----------|-----------------------|-----------------------|-----------------------|---------------------------------|------------------|

| (AD<br>M1) |     | (ADM0)<br>FR2 FR1 FR0 LV1 LV0 |     |     | Mode | Conversion<br>Clock (fAD) | Cycles for<br>A/D Power<br>Supply | Clock<br>Cycles for   | Cycles for<br>Interrupt |                       |           | 2.4 ∨ ≤ /             | AVREFP ≤ Vo           | o≤5.5 V               |                                 |                  |

| ADL<br>SP  | FR2 | FR1                           | FRO | LV1 | LVO  |                           |                                   | Stabilization<br>Wait | Conversion              | Output<br>DelayNote 2 |           | fcLK =<br>1 MHz       | fclk =<br>4 MHz       | fCLK =<br>8 MHz       | fCLK =<br>16 MHz                | fCLK =<br>32 MHz |

| 0          | 0   | 0                             | 0   | 0   | 0    | Normal<br>1               | fCLK/32                           | 4 fad                 | 64 fad                  | 4 fad                 | 2304/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited           | 72 µs            |

| 0          | 0   |                               |     |     |      |                           | fcLk/16                           | 4 fad                 | 64 fad                  | 4 fad                 | 1152/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 72 µs                           | 36 µs            |

| 1 | 1 | 0          | 0  | 1 |  | fCLK/2 | 4 fad | 181 fad | 4 fad | 378/fclk  | Setting prohibited | 94.5 µs  | Setting prohibited    | Setting<br>prohibited | Setting<br>prohibited |

|---|---|------------|----|---|--|--------|-------|---------|-------|-----------|--------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1 | 0          | 1  | ] |  | fclk   | 6 fad | 181 fAD | 4 fad | 191/fclk  | 191 µs             | 47.75 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| C |   | than toove | he | ] |  |        |       |         |       | Setting p | rohibited          |          |                       |                       |                       |

- Note 1. For the second and subsequent conversion in sequential conversion mode and for conversion of the channels specified for scan 1, 2, and 3 in scan mode, the conversion start time and A/D power supply stabilization wait time do not occur after a hardware trigger is detected. For details, see Table 20 - 6 Selection of A/D Conversion Time (1/11).

- Note 2. This number denotes the number of clock cycles for interrupt output delay in the one-shot conversion mode. When the sequential conversion mode is selected, the number of conversion clock (fAD) cycles becomes shorter by three cycles.

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics. Note that the conversion time (tCONV) does not include A/D power supply stabilization wait time.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0).

#### Table 20 - 6 Selection of A/D Conversion Time (3/11)

3. Normal modes 1 and 2 with A/D power supply stabilization wait time

(software trigger wait select mode and hardware trigger wait select modeNote 1)

| A/D (<br>A/D ( |     |          |     |     |     |             |                           | Number of<br>Clock                | Number of           | Number of<br>Clock      |           |                       |                       |                       | upply Stabiliz<br>pt Output Del |                  |

|----------------|-----|----------|-----|-----|-----|-------------|---------------------------|-----------------------------------|---------------------|-------------------------|-----------|-----------------------|-----------------------|-----------------------|---------------------------------|------------------|

| (AD<br>M1)     |     | (ADM0) M |     |     |     | Mode        | Conversion<br>Clock (fAD) | Cycles for<br>A/D Power<br>Supply | Clock<br>Cycles for | Cycles for<br>Interrupt |           |                       | 2.4 ∨ ≤ /             | AVREFP ≤ Vo           | o≤5.5 V                         |                  |

| ADL<br>SP      | FR2 | FR1      | FRO | LV1 | LVO |             |                           | Stabilization<br>Wait             | Conversion          | Output<br>DelayNote 2   |           | fclk =<br>1 MHz       | fclk =<br>4 MHz       | fclk =<br>8 MHz       | fCLK =<br>16 MHz                | fCLK =<br>32 MHz |

| 0              | 0   | 0        | 0   | 0   | 0   | Normal<br>1 | fCLK/32                   | 4 fad                             | 64 fad              | 4 fad                   | 2304/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited           | 72 µs            |

| 0              | 0   | 0        | 1   |     |     |             | fCLK/16                   | 4 fad                             | 64 fad              | 4 fad                   | 1152/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 72 µs                           | 36 µs            |

| 1 | I  | 1             | 0             | 0  | ] |  | fCLK/2 | 4 fad | 181 fad | 4 fad | 378/fclk  | Setting<br>prohibited | 94.5 µs  | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|----|---------------|---------------|----|---|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | I  | 1             | 0             | 1  |   |  | fclk   | 6 fAD | 181 fAD | 4 fad | 191/fclk  | 191 µs                | 47.75 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|   | Ot | her ti<br>abo | han ti<br>ove | 1e |   |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |

- Note 1. For the second and subsequent conversion in sequential conversion mode and for conversion of the channels specified for scan 1, 2, and 3 in scan mode, the conversion start time and A/D power supply stabilization wait time do not occur after a hardware trigger is detected. For details, see Table 20 - 6 Selection of A/D Conversion Time (1/11).

- Note 2. This number denotes the number of clock cycles for interrupt output delay in the one-shot conversion mode. When the sequential conversion mode is selected, the number of conversion clock (fAD) cycles becomes shorter by three cycles.

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics. Note that the conversion time (tCONV) does not include A/D power supply stabilization wait time.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0). When conversion is to be stopped while the A/D converter is on standby or is operating, wait for at least 0.2 µs before setting the FR[2:0] and LV[1:0] bits.

(Page 1081)

Table 20 - 6 Selection of A/D Conversion Time (4/11)

#### Low voltage modes 1 and 2 with A/D power supply stabilization wait time (software trigger wait select mode and hardware trigger wait select mode<sup>Note 1</sup>)

| A/D (<br>A/D (<br>(AD<br>M1)<br>ADL<br>SP | Conve | erter M | Mode<br>ADM( | Regi | ster 0<br>ster 1 | Mode           | Conversion<br>Clock (fAD) | Number of<br>Clock<br>Cycles for<br>A/D Power<br>Supply<br>Stabilization<br>Wait | Number of<br>Clock<br>Cycles for<br>Conversion | Number of<br>Clock<br>Cycles for<br>Interrupt<br>Output<br>Delay <sup>Note 2</sup> |           |                       |                       |                       | upply Stabiliz<br>pt Output Del<br>2.4 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V<br>fCLK =<br>16 MHz |       |

|-------------------------------------------|-------|---------|--------------|------|------------------|----------------|---------------------------|----------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------|-----------|-----------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------------|-------|

| 0                                         | 0     | 0       | 0            | 1    | 0                | Low<br>voltage | fCLK/32                   | 4 fad                                                                            | 80 fAD                                         | 4 fad                                                                              | 2816/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited                                                                        | 88 µs |

| 0                                         | 0     | 0       | 1            |      |                  | 1              | fcLk/16                   | 4 fad                                                                            | 80 fad                                         | 4 fad                                                                              | 1408/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 88 µs                                                                                        | 44 µs |

| 1 | 1 | 0      | 0  |  | fCLK/2 | 4 fad | 107 fad | 4 fad | 230/fclk  | Setting prohibited | 57.5 µs  | Setting<br>prohibited | Setting prohibited    | Setting<br>prohibited |

|---|---|--------|----|--|--------|-------|---------|-------|-----------|--------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1 | 0      | 1  |  | fclk   | 6 fAD | 107 fad | 4 fAD | 117/fclk  | 117 µs             | 29.25 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| ( |   | than t | he |  |        |       |         |       | Setting p | rohibited          |          |                       |                       |                       |

- Note 1. For the second and subsequent conversion in sequential conversion mode and for conversion of the channels specified for scan 1, 2, and 3 in scan mode, the conversion start time and A/D power supply stabilization wait time do not occur after a hardware trigger is detected. For details, see Table 20 - 6 Selection of A/D Conversion Time (2/11).

- Note 2. This number denotes the number of clock cycles for interrupt output delay in the one-shot conversion mode. When the sequential conversion mode is selected, the number of conversion clock (fAD) cycles becomes shorter by three cycles.

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics. Note that the conversion time (tCONV) does not include A/D power supply stabilization wait time.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0).

Table 20 - 6 Selection of A/D Conversion Time (4/11)

4. Low voltage modes 1 and 2 with A/D power supply stabilization wait time

(software trigger wait select mode and hardware trigger wait select modeNote 1)

|            |     | rerter Mode Register 0<br>rerter Mode Register 1<br>(ADM0) |     |     |      |                           |                                                             | Number of                                      |                                            | Number of               |                                       |                                       |                                       | A/D Power S<br>ime + Interru          |                                       |                  |

|------------|-----|------------------------------------------------------------|-----|-----|------|---------------------------|-------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------------|

| (AD<br>M1) |     | (ADM0)<br>R2 FR1 FR0 LV1 LV0                               |     |     | Mode | Conversion<br>Clock (fAD) | Clock<br>Cycles for<br>A/D Power<br>Supply<br>Stabilization | Number of<br>Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for<br>Interrupt<br>Output |                         | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.8 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.4 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.7 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V |                  |

| ADL<br>SP  | FR2 | FR1                                                        | FRO | LV1 | LVO  |                           |                                                             | Wait                                           |                                            | Delay <sup>Note 2</sup> |                                       | fclk =<br>1 MHz                       | fclk =<br>4 MHz                       | fCLK =<br>8 MHz                       | fCLK =<br>16 MHz                      | fCLK =<br>32 MHz |

| 0          | 0   | 0                                                          | 0   | 1   | 0    | Low<br>voltage            | fCLK/32                                                     | 4 fad                                          | 80 fAD                                     | 4 fad                   | 2816/fclk                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | 88 µs            |

| 0          | 0   |                                                            |     |     |      | 1                         | fCLK/16                                                     | 4 fad                                          | 80 fad                                     | 4 fad                   | 1408/fclk                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | 88 µs                                 | 44 µs            |

| Ī | 1 | 1            | 0 | 0  |  | fCLK/2 | 4 fad | 107 fad | 4 fad | 230/fclk  | Setting<br>prohibited | 57.5 µs  | Setting prohibited    | Setting<br>prohibited | Setting<br>prohibited |

|---|---|--------------|---|----|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|

|   | 1 | 1            | 0 | 1  |  | fclk   | 6 fAD | 107 fAD | 4 fad | 117/fclk  | 117 µs                | 29.25 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| ſ | 0 | ther t<br>ab |   | he |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |

- Note 1. For the second and subsequent conversion in sequential conversion mode and for conversion of the channels specified for scan 1, 2, and 3 in scan mode, the conversion start time and A/D power supply stabilization wait time do not occur after a hardware trigger is detected. For details, see Table 20 - 6 Selection of A/D Conversion Time (2/11).

- Note 2. This number denotes the number of clock cycles for interrupt output delay in the one-shot conversion mode. When the sequential conversion mode is selected, the number of conversion clock (fAD) cycles becomes shorter by three cycles.

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics. Note that the conversion time (tCONV) does not include A/D power supply stabilization wait time.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0). When conversion is to be stopped while the A/D converter is on standby or is operating, wait for at least 0.2 µs before setting the FR[2:0] and LV[1:0] bits.

(Page 1083)

Table 20 - 6 Selection of A/D Conversion Time (5/11)

#### Normal modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait scan mode and hardware trigger no-wait scan mode)

| A/D (<br>A/D ( |     |     |      |     |     |             |                           | Number of   | Number of           | Number of<br>Clock      |           |                       |                       |                       | n Start Delay<br>Output Delay |                  |

|----------------|-----|-----|------|-----|-----|-------------|---------------------------|-------------|---------------------|-------------------------|-----------|-----------------------|-----------------------|-----------------------|-------------------------------|------------------|

| (AD<br>M1)     |     | 6   | ADMO | ))  |     | Mode        | Conversion<br>Clock (fAD) |             | Clock<br>Cycles for | Cycles for<br>Interrupt |           |                       | 2.4 ∨ ≤ /             | AVREFP ≤ Vo           | o≤5.5 V                       |                  |

| ADL<br>SP      | FR2 | FR1 | FRO  | LV1 | LVO |             |                           | Start Delay |                     | Output<br>Delay         |           | fclk =<br>1 MHz       | fclk =<br>4 MHz       | fCLK =<br>8 MHz       | fCLK =<br>16 MHz              | fclk =<br>32 MHz |

| 0              | 0   | 0   | 0    | 0   | 0   | Normal<br>1 | fcLk/32                   | 1 fAD       | 64 fad              | 1 fAD                   | 8256/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited         | 258 µs           |

| 0              | 0   | 0   | 1    |     |     |             | fcLk/16                   | 1 fad       | 64 fad              | 1 fad                   | 4128/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 258 µs                        | 129 µs           |

| 1 | 1          | C              | 0 | ) |  | fCLK/2 | 1 fad | 181 fad | 1 fad | 1452/fclk | Setting<br>prohibited | 363 µs   | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|------------|----------------|---|---|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1          | C              | 1 | 1 |  | fCLK   | 1 fad | 181 fad | 1 fad | 726/fclk  | 726 µs                | 181.5 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|   | Other<br>a | r thar<br>bove |   |   |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0).

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use normal mode 2.

- Caution 5. When the internal reference voltage is selected for the + side reference voltage, normal modes 1 and 2 cannot be used. In such cases, use low voltage mode 1 or 2.

- Remark fcLK: CPU/peripheral hardware clock frequency

Date: Jan. 8, 2025

Table 20 - 6 Selection of A/D Conversion Time (5/11)

Normal modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait scan mode and hardware trigger no-wait scan mode)

|            |     | erter I<br>erter I |     |     |     |             |                           | Number of                         | Number of           | Number of<br>Clock      |           |                       |                       |                       | n Start Delay<br>Output Delay |                  |

|------------|-----|--------------------|-----|-----|-----|-------------|---------------------------|-----------------------------------|---------------------|-------------------------|-----------|-----------------------|-----------------------|-----------------------|-------------------------------|------------------|

| (AD<br>M1) |     | (ADM0) M           |     |     |     | Mode        | Conversion<br>Clock (fAD) | Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for | Cycles for<br>Interrupt |           |                       | 2.4 ∨ ≤ /             | AVREFP ≤ Vo           | op ≤ 5.5 V                    |                  |

| ADL<br>SP  | FR2 | FR1                | FRO | LV1 | LVO |             |                           | Start Delay                       | Conversion          | Output<br>Delay         |           | fclk =<br>1 MHz       | fclk =<br>4 MHz       | fCLK =<br>8 MHz       | fCLK =<br>16 MHz              | fCLK =<br>32 MHz |

| 0          | 0   | 0                  | 0   | 0   | 0   | Normal<br>1 | fCLK/32                   | 1 fAD                             | 64 fad              | 1 fad                   | 8256/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited         | 258 µs           |

| 0          | 0   | 0                  | 1   |     |     |             | fCLK/16                   | 1 fad                             | 64 fad              | 1 fad                   | 4128/fclk | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited | 258 µs                        | 129 µs           |

| T | 1 | 1 | 0            | 0  | 1 |  | fCLK/2 | 1 fad | 181 fAD | 1 fad | 1452/fclk | Setting<br>prohibited | 363 µs   | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|---|---|--------------|----|---|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|

|   | 1 | 1 | 0            | 1  | 1 |  | fCLK   | 1 fad | 181 fAD | 1 fad | 726/fclk  | 726 µs                | 181.5 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|   | 0 |   | han t<br>ove | he | 1 |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |

Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0). When conversion is to be stopped while the A/D converter is on standby or is operating, wait for at least 0.2 us before setting the FR[2:0] and LV[1:0] bits.

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use normal mode 2.

- Caution 5. When the internal reference voltage is selected for the + side reference voltage, normal modes 1 and 2 cannot be used. In such cases, use low voltage mode 1 or 2.

Remark fclk: CPU/peripheral hardware clock frequency

(Page 1084)

Table 20 - 6 Selection of A/D Conversion Time (6/11)

#### Low voltage modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait scan mode and hardware trigger no-wait scan mode)

|            |                               |     |     |     |      |                           |                                                               |                                                |                                            | Number of |                                       |                                       |                                       |                                       | n Start Delay<br>Output Dela          |                  |

|------------|-------------------------------|-----|-----|-----|------|---------------------------|---------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-----------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------------|

| (AD<br>M1) | (ADM0)<br>FR2 FR1 FR0 LV1 LV0 |     |     |     | Mode | Conversion<br>Clock (fAD) | Number of<br>Clock<br>Cycles for<br>Conversion<br>Start Delay | Number of<br>Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for<br>Interrupt<br>Output |           | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 1.8 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.4 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V | 2.7 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V |                  |

| ADL<br>SP  | FR2                           | FR1 | FRO | LV1 | LVO  |                           |                                                               |                                                |                                            | Delay     |                                       | fclk =<br>1 MHz                       | fclk =<br>4 MHz                       | fCLK =<br>8 MHz                       | fCLK =<br>16 MHz                      | fCLK =<br>32 MHz |

| 0          | 0                             | 0   | 0   | 1   | 0    | Low<br>voltage            | fCLK/32                                                       | 1 fAD                                          | 80 fad                                     | 1 fad     | 10304/fcLK                            | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | 322 µs           |

| 0          | 0                             | 0   | 1   |     |      | 1                         | fcLk/16                                                       | 1 fAD                                          | 80 fAD                                     | 1 fad     | 5152/fclk                             | Setting<br>prohibited                 | Setting<br>prohibited                 | Setting<br>prohibited                 | 322 µs                                | 161 µs           |

| 1 | 1 | 0              | 0  |   |  | fCLK/2 | 1 fad | 107 fad | 1 fad | 860/fclk  | Setting<br>prohibited | 215 µs   | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|---|----------------|----|---|--|--------|-------|---------|-------|-----------|-----------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1 | 0              | 1  |   |  | fCLK   | 1 fad | 107 fad | 1 fad | 430/fclk  | 430 µs                | 107.5 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| C |   | than ti<br>ove | he | ] |  |        |       |         |       | Setting p | rohibited             |          |                       |                       |                       |

- Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0).

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use low voltage mode 2 with the conversion clock (fAD) with a frequency of no more than 16 MHz.

Table 20 - 6 Selection of A/D Conversion Time (6/11)

Low voltage modes 1 and 2 with no A/D power supply stabilization wait time (software trigger no-wait scan mode and hardware trigger no-wait scan mode)

|                   |     | erter I<br>erter I |     |     |     |                |                           |                                                               |                                                | Number of                                           |                       |                                                 |                                                 |                                                 | on Start Delay<br>Output Delay                  |                                                 |

|-------------------|-----|--------------------|-----|-----|-----|----------------|---------------------------|---------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------|-----------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| (AD<br>M1)<br>ADL |     |                    |     |     |     | Mode           | Conversion<br>Clock (fAD) | Number of<br>Clock<br>Cycles for<br>Conversion<br>Start Delay | Number of<br>Clock<br>Cycles for<br>Conversion | Clock<br>Cycles for<br>Interrupt<br>Output<br>Delay |                       | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V<br>fcLK = | 1.6 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V<br>fCLK = | 1.8 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V<br>fCLK = | 2.4 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V<br>fCLK = | 2.7 V ≤<br>AVREFP ≤<br>VDD ≤<br>5.5 V<br>fcLK = |

| SP                | FR2 | FR1                | FRU | LV1 | LVU |                |                           |                                                               |                                                |                                                     |                       | 1 MHz                                           | 4 MHz                                           | 8 MHz                                           | 16 MHz                                          | 32 MHz                                          |

| 0                 | 0   | 0                  | 0   | 1   | 0   | Low<br>voltage | fCLK/32                   | 1 fAD                                                         | 80 fAD                                         | 1 fad                                               | 10304/fcLK            | Setting<br>prohibited                           | Setting<br>prohibited                           | Setting<br>prohibited                           | Setting<br>prohibited                           | 322 µs                                          |

| 0                 | 0   | v                  |     |     | 1   | fcLk/16        | 1 fAD                     | 80 fad                                                        | 1 fad                                          | 5152/fclk                                           | Setting<br>prohibited | Setting<br>prohibited                           | Setting<br>prohibited                           | 322 µs                                          | 161 µs                                          |                                                 |

| 1 | 1 | 0      | 0  |  | ĺ | fclk/2 | 1 fad | 107 fad | 1 fad | 860/fclk  | Setting prohibited | 215 µs   | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

|---|---|--------|----|--|---|--------|-------|---------|-------|-----------|--------------------|----------|-----------------------|-----------------------|-----------------------|

| 1 | 1 | 0      | 1  |  |   | fCLK   | 1 fad | 107 fad | 1 fad | 430/fclk  | 430 µs             | 107.5 µs | Setting<br>prohibited | Setting<br>prohibited | Setting<br>prohibited |

| 0 |   | than t | he |  |   |        |       |         |       | Setting p | rohibited          |          |                       |                       |                       |

Caution 1. The A/D conversion time must be within the relevant range of conversion clock (fAD) and conversion times (tCONV) described in 43.6.1 A/D converter characteristics or 44.6.1 A/D converter characteristics.

- Caution 2. Rewrite the FR[2:0] and LV[1:0] bits to different values while conversion is stopped (ADCS = 0, ADCE = 0). When conversion is to be stopped while the A/D converter is on standby or is operating, wait for at least 0.2 µs before setting the FR[2:0] and LV[1:0] bits.

- Caution 3. The above conversion times do not include the conversion start time. Add the conversion start time to obtain the time for the first conversion. Additionally, the conversion times do not include clock frequency errors. Consider clock frequency errors when selecting the conversion time.

- Caution 4. When the internal reference voltage or the temperature sensor output voltage is selected as the conversion target, use low voltage mode 2 with the conversion clock (fAD) with a frequency of no more than 16 MHz.

(Page 1086)

Table 20 - 6 Selection of A/D Conversion Time (7/11)

#### 7. Normal modes 1 and 2 with A/D power supply stabilization wait time

(software trigger wait scan mode and hardware trigger wait scan mode<sup>Note 1</sup>)