# RENESAS TECHNICAL UPDATE

〒135-0061 東京都江東区豊洲 3-2-24

豊洲フォレシア

ルネサス エレクトロニクス株式会社

問合せ窓口 <http://japan.renesas.com/contact/>

E-mail: csc@renesas.com

| 製品分類 | MPU & MCU                                    | 発行番号           | TN-RL*-A0132AJ | Rev.                                                                  | 第1版 |

|------|----------------------------------------------|----------------|----------------|-----------------------------------------------------------------------|-----|

| 題名   | 誤記訂正通知<br>RL78/G23 ユーザーズマニュアル Rev.1.21 の記載変更 |                | 情報分類           | 技術情報                                                                  |     |

| 適用製品 | RL78/G23 グループ                                | 対象ロット等<br>全ロット | 関連資料           | RL78/G23 ユーザーズマニュアル<br>ハードウェア編 Rev.1.21<br>R01UH0896JJ0121 (Nov.2022) |     |

RL78/G23 ユーザーズマニュアル ハードウェア編 Rev.1.21 (R01UH0896JJ0121) において、下記訂正がございます。

## 今回通知する訂正内容

| 訂正箇所                                            | 該当ページ                  | 内容   |

|-------------------------------------------------|------------------------|------|

| 12.3.3 A/Dコンバータ・モード・レジスタ0 (ADM0)                | p.567, p.570 ~ p.578   | 誤記訂正 |

| 12.3.4 A/Dコンバータ・モード・レジスタ1 (ADM1)                | p.580                  | 誤記訂正 |

| 12.3.5 A/Dコンバータ・モード・レジスタ2 (ADM2)                | p.581, p.582           | 誤記訂正 |

| 20.2 ELCLの構成                                    | p.1057, p.1059, p.1061 | 誤記訂正 |

| 20.3.1 入力信号選択レジスタn (ELISELn) (n = 0-11)         | p.1064, p.1068         | 誤記訂正 |

| 20.6 ELCL使用時の注意事項                               | p.1101                 | 誤記訂正 |

| 29.3.3 シーケンサ・インストラクション・レジスタp (SMSIp) (p = 0-31) | p.1235, p.1236         | 誤記訂正 |

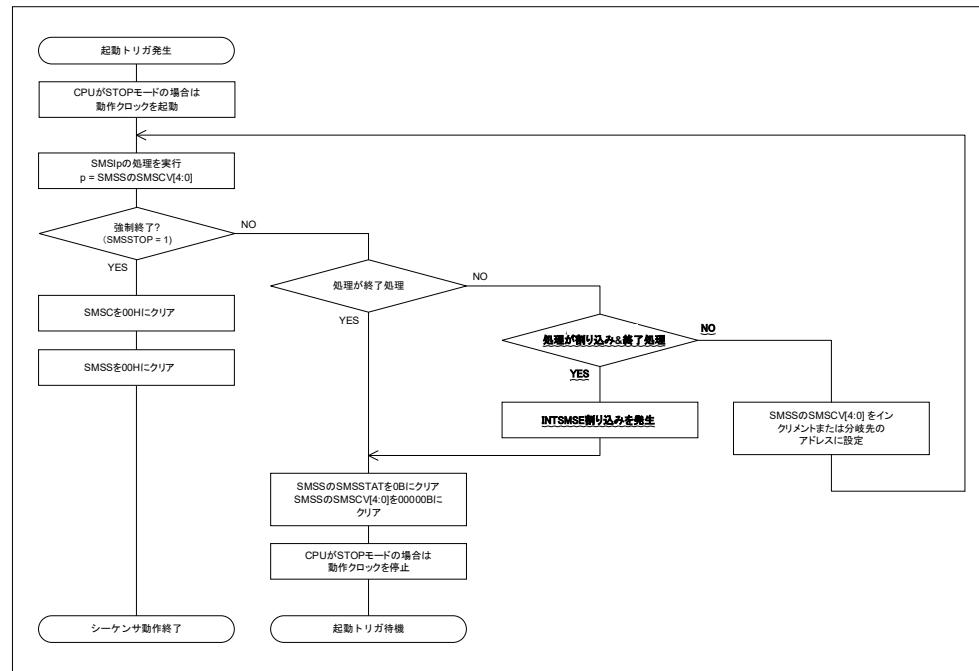

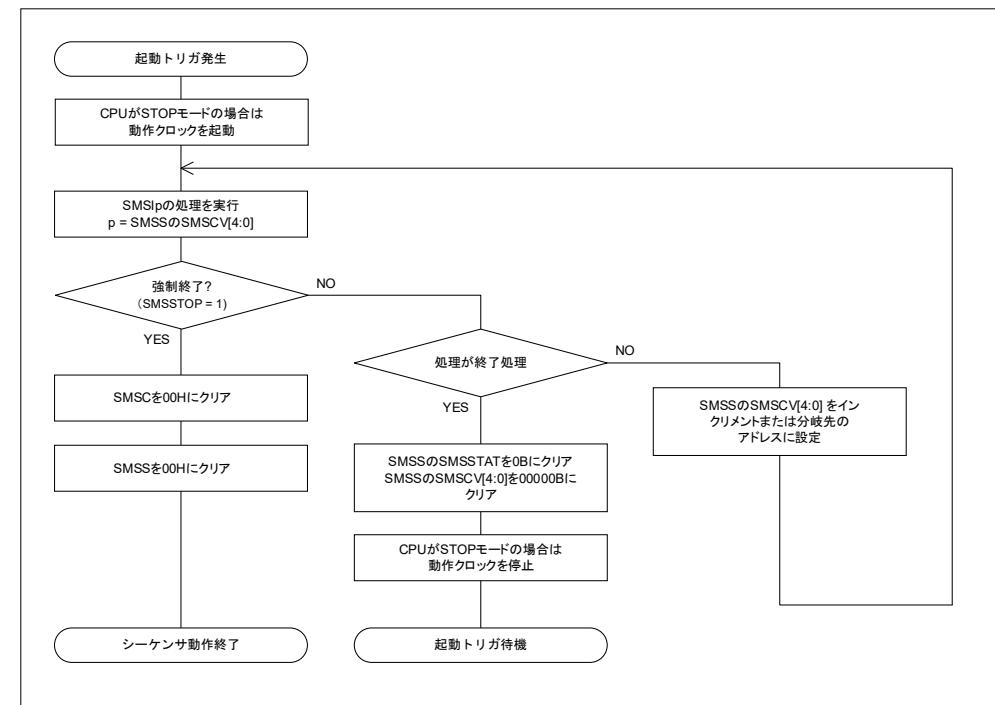

| 29.4 SNOOZEモード・シーケンサの動作                         | p.1245                 | 誤記訂正 |

| 29.4.1 SNOOZEモード・シーケンサの内部の動作                    | p.1242                 | 誤記訂正 |

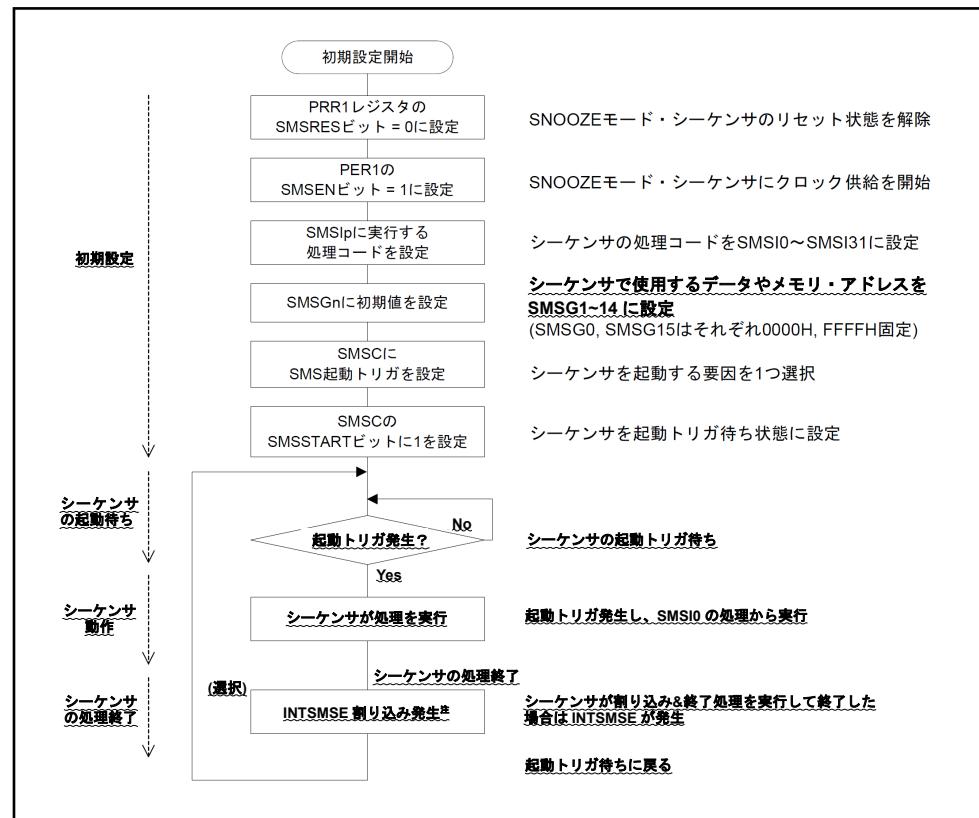

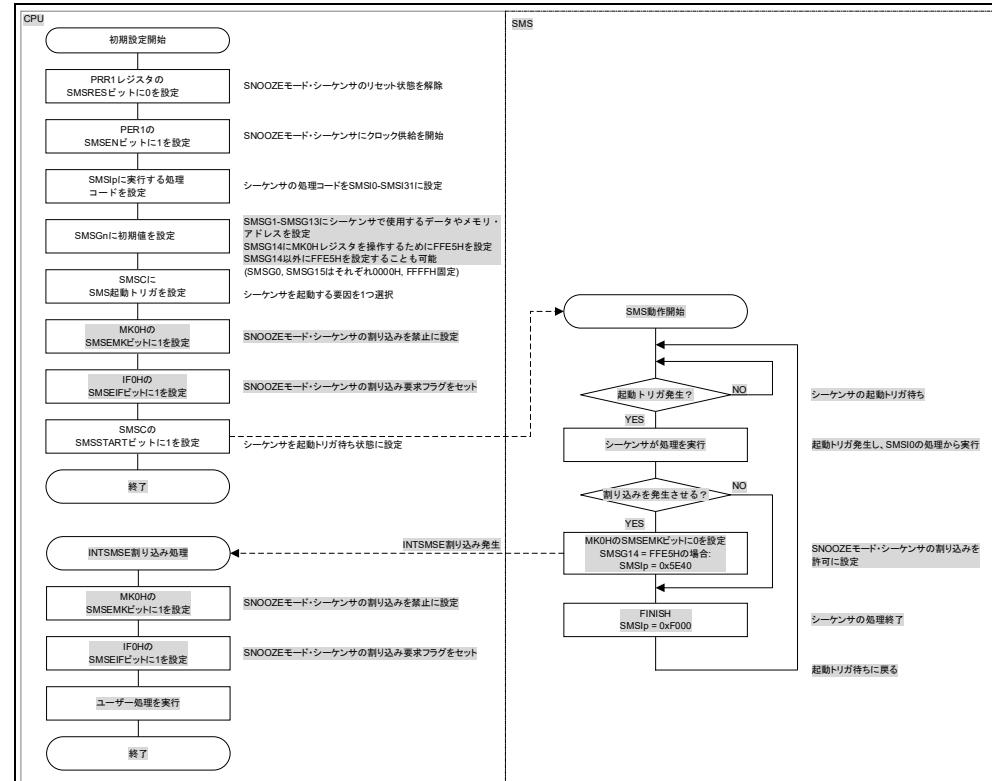

| 29.4.4 SNOOZEモード・シーケンサの操作手順                     | p.1246                 | 誤記訂正 |

| 29.4.5 SNOOZEモード・シーケンサの状態                       | p.1248                 | 誤記訂正 |

| 29.5.20 割り込み&終了処理                               | p.1270                 | 誤記訂正 |

| 29.6 スタンバイ・モード時の動作                              | p.1272                 | 誤記訂正 |

| 37.4 AC特性                                       | p.1451                 | 誤記訂正 |

## ドキュメント改善計画

本訂正内容については、次回ユーザーズマニュアル改版時に修正を行います。

## ユーザーズマニュアルの訂正一覧

| No | 訂正内容と該当箇所                                       |    |                        | 本通知での<br>該当ページ |

|----|-------------------------------------------------|----|------------------------|----------------|

|    | ドキュメント<br>No.                                   | 和文 | R01UH0896JJ0121        |                |

| 1  | 8.3.4 リアルタイム・クロック・コントロール・レジスタ1 (RTCC1)          |    | p.488                  | p.3            |

| 2  | 図8-19 リアルタイム・クロックの読み出し手順                        |    | p.501                  | p.4            |

| 3  | 図8-20 リアルタイム・クロックの書き込み手順                        |    | p.502                  | p.4            |

| 4  | 37.3.2 電源電流特性                                   |    | p.1432 ~ p.1447        | p.5 ~ p.16     |

| 5  | 37.6.4 コンパレータ特性                                 |    | p.1495                 | p.17           |

| 6  | 12.3.3 A/Dコンバータ・モード・レジスタ0 (ADM0)                |    | p.567, p.570 ~ p.578   | p.18 ~ p.27    |

| 7  | 12.3.4 A/Dコンバータ・モード・レジスタ1 (ADM1)                |    | p.580                  | p.28           |

| 8  | 12.3.5 A/Dコンバータ・モード・レジスタ2 (ADM2)                |    | p.581, p.582           | p.29, p.30     |

| 9  | 20.2 ELCLの構成                                    |    | p.1057, p.1059, p.1061 | p.31 ~ p.33    |

| 10 | 20.3.1 入力信号選択レジスタn (ELISELn) (n = 0-11)         |    | p.1064, p.1068         | p.34, p.35     |

| 11 | 20.6 ELCL使用時の注意事項                               |    | p.1101                 | p.36           |

| 12 | 29.3.3 シーケンサ・インストラクション・レジスタp (SMSIp) (p = 0-31) |    | p.1235, p.1236         | p.37, p.38     |

| 13 | 29.4 SNOOZEモード・シーケンサの動作                         |    | p.1245                 | p.39           |

| 14 | 29.4.1 SNOOZEモード・シーケンサの内部の動作                    |    | p.1242                 | p.40           |

| 15 | 29.4.4 SNOOZEモード・シーケンサの操作手順                     |    | p.1246                 | p.41           |

| 16 | 29.4.5 SNOOZEモード・シーケンサの状態                       |    | p.1248                 | p.42           |

| 17 | 29.5.20 割り込み&終了処理                               |    | p.1270                 | p.43           |

| 18 | 29.6 スタンバイ・モード時の動作                              |    | p.1272                 | p.44           |

| 19 | 37.4 AC特性                                       |    | p.1451                 | p.45           |

誤記訂正の該当箇所は、誤) 太字下線、正) グレー・ハッチングで記載します。

## 発行文書履歴

### RL78/G23 ユーザーズマニュアル Rev.1.21 誤記訂正通知 発行文書履歴

| 文書番号            | 発行日        | 記事                               |

|-----------------|------------|----------------------------------|

| TN-RL*-A0103A/J | 2023年1月19日 | 初版発行<br>訂正一覧の No.1 ~ No. 5 の誤記訂正 |

| TN-RL*-A0132A/J | 2024年1月9日  | 訂正一覧の No.6 ~ No.19 の誤記訂正（本通知です。） |

### 1. 8.3.4 リアルタイム・クロック・コントロール・レジスタ1 (RTCC1)

(p.488)

誤)

図8-5 リアルタイム・クロック・コントロール・レジスタ1 (RTCC1) のフォーマット (2/2)

| RWST | リアルタイム・クロックのウェイト状態フラグ <sup>注3</sup> |

|------|-------------------------------------|

| 0    | カウンタ動作中                             |

| 1    | カウンタ値の読み出し、書き込みモード中                 |

RWAIT ビットの設定が有効であるかを示すステータスです。

カウンタ値の読み出し、書き込みは、このフラグの値が1になっていることを確認したあとに行ってください。

| RWAIT | リアルタイム・クロックのウェイト制御                   |

|-------|--------------------------------------|

| 0     | カウンタ動作設定                             |

| 1     | SEC～YEAR カウンタ停止設定。カウンタ値読み出し、書き込みモード。 |

カウンタの動作を制御します。

カウンタ値を読み出し、書き込みを行う際は必ず1 を書き込んでください。

内部カウンタ（16ビット）は動作を継続するので、1秒以内に読み出しや書き込みを終了し、0に戻してください。

RWAIT = 1に設定後、カウンタ値の読み出し、書き込みが可能（RWST = 1）となるまで最大f<sub>RTCC0</sub>の1クロックの時間がかかります。<sup>注1,2</sup>

内部カウンタ（16ビット）のオーバフローがRWAIT = 1のときに起きた場合は、オーバフローが起きたことを保持してRWAIT = 0になったあと、カウント・アップします。

ただし、秒カウント・レジスタへの書き込みを行った場合は、オーバフローが起きたことを保持しません。

正)

図8-5 リアルタイム・クロック・コントロール・レジスタ1 (RTCC1) のフォーマット (2/2)

| RWST | リアルタイム・クロックのウェイト状態フラグ <sup>注3</sup> |

|------|-------------------------------------|

| 0    | カウンタ動作中                             |

| 1    | カウンタ値の読み出し、書き込みモード中                 |

RWAIT ビットの設定が有効であるかを示すステータスです。

カウンタ値の読み出し、書き込みは、このフラグの値が1になっていることを確認したあとに行ってください。

| RWAIT | リアルタイム・クロックのウェイト制御                   |

|-------|--------------------------------------|

| 0     | カウンタ動作設定                             |

| 1     | SEC～YEAR カウンタ停止設定。カウンタ値読み出し、書き込みモード。 |

カウンタの動作を制御します。

カウンタ値を読み出し、書き込みを行う際は必ず1 を書き込んでください。

内部カウンタ（16ビット）は動作を継続するので、1秒以内に読み出しや書き込みを終了し、0に戻してください。

アラーム割り込みを使用するときに、カウンタの読み出し／書き込みを行う場合は、

RTCC0レジスタのCT2～CT0ビットを010B（1秒毎に定期割り込み発生）にして、RWAIT = 1

からRWAIT = 0までの処理を次の定期割り込みが発生するまでに行ってください。

RWAIT = 1に設定後、カウンタ値の読み出し、書き込みが可能（RWST = 1）となるまで最大f<sub>RTCC0</sub>の1

クロックの時間がかかります。<sup>注1,2</sup>

内部カウンタ（16ビット）のオーバフローがRWAIT = 1のときに起きた場合は、オーバフローが起きたことを保持してRWAIT = 0になったあと、カウント・アップします。

ただし、秒カウント・レジスタへの書き込みを行った場合は、オーバフローが起きたことを保持しません。

## 2. 図 8 - 19 リアルタイム・クロックの読み出し手順 (p.501)

誤)

注 STOP モードに移行する前には、必ず RWST = 0 であることを確認してください。

注意 RWAIT = 1 から RWAIT = 0 までの処理を 1 秒以内で行ってください。

備考 秒カウント・レジスタ (SEC) 、分カウント・レジスタ (MIN) 、時カウント・レジスタ (HOUR) 、曜日カウント・レジスタ (WEEK) 、日カウント・レジスタ (DAY) 、月カウント・レジスタ (MONTH) 、年カウント・レジスタ (YEAR) の読み出しの順番に制限はありません。

また、すべてのレジスタを読み出す必要はなく、一部のレジスタのみを読み出しても構いません。

## 3. 図 8 - 20 リアルタイム・クロックの書き込み手順 (p.502)

誤)

注 STOP モードに移行する前には、必ず RWST = 0 であることを確認してください。

注意 1. RWAIT = 1 から RWAIT = 0 とするまでを 1 秒以内で行ってください。

注意 2. カウンタ動作中 (RTCE = 1) に SEC, MIN, HOUR, WEEK, DAY, MONTH, YEAR レジスタを書き換える場合は、INTRTC を割り込みマスク・フラグ・レジスタで割り込み処理禁止にしてから書き換えてください。また、書き換え後に WAFG フラグ、RIFG フラグ、RTCIF フラグをクリアしてください。

備考 秒カウント・レジスタ (SEC) 、分カウント・レジスタ (MIN) 、時カウント・レジスタ (HOUR) 、曜日カウント・レジスタ (WEEK) 、日カウント・レジスタ (DAY) 、月カウント・レジスタ (MONTH) 、年カウント・レジスタ (YEAR) の書き込みの順番に制限はありません。

また、すべてのレジスタを設定する必要はなく、一部のレジスタのみを書き換えて構いません。

正)

注 STOP モードに移行する前には、必ず RWST = 0 であることを確認してください。

注意 RWAIT = 1 から RWAIT = 0 までの処理を 1 秒以内で行ってください。アラーム割り込みを使用するときに、カウンタ読み出しを行う場合は、RTCC0 レジスタの CT2～CT0 ビットを 010B (1 秒毎に定期割り込み発生) にして、RWAIT = 1 から RWAIT = 0 までの処理を次の定期割り込みが発生するまでに行ってください。

備考 秒カウント・レジスタ (SEC) 、分カウント・レジスタ (MIN) 、時カウント・レジスタ (HOUR) 、曜日カウント・レジスタ (WEEK) 、日カウント・レジスタ (DAY) 、月カウント・レジスタ (MONTH) 、年カウント・レジスタ (YEAR) の読み出しの順番に制限はありません。

また、すべてのレジスタを読み出す必要はなく、一部のレジスタのみを読み出しても構いません。

正)

注 STOP モードに移行する前には、必ず RWST = 0 であることを確認してください。

注意 1. RWAIT = 1 から RWAIT = 0 とするまでを 1 秒以内で行ってください。アラーム割り込みを使用するときに、カウンタ書き込みを行う場合は、RTCC0 レジスタの CT2～CT0 ビットを 010B (1 秒毎に定期割り込み発生) にして、RWAIT = 1 から RWAIT = 0 までの処理を次の定期割り込みが発生するまでに行ってください。

注意 2. カウンタ動作中 (RTCE = 1) に SEC, MIN, HOUR, WEEK, DAY, MONTH, YEAR レジスタを書き換える場合は、INTRTC を割り込みマスク・フラグ・レジスタで割り込み処理禁止にしてから書き換えてください。また、書き換え後に WAFG フラグ、RIFG フラグ、RTCIF フラグをクリアしてください。

備考 秒カウント・レジスタ (SEC) 、分カウント・レジスタ (MIN) 、時カウント・レジスタ (HOUR) 、曜日カウント・レジスタ (WEEK) 、日カウント・レジスタ (DAY) 、月カウント・レジスタ (MONTH) 、年カウント・レジスタ (YEAR) の書き込みの順番に制限はありません。

また、すべてのレジスタを設定する必要はなく、一部のレジスタのみを書き換えて構いません。

#### 4. 37. 3. 2 電源電流特性 (p.1432 ~ p.1447)

誤)

##### 37. 3. 2 電源電流特性

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(1/4)

| 項目                 | 略号               | 条件                         |                            |             |     | MIN. | TYP. | MAX. | 単位 |  |  |

|--------------------|------------------|----------------------------|----------------------------|-------------|-----|------|------|------|----|--|--|

|                    |                  | 動作モード<br>HS (高速メイン)<br>モード | fIH = 32 MHz <sup>注2</sup> | 基本動作        |     |      |      |      |    |  |  |

| 電源電流 <sup>注1</sup> | I <sub>DD1</sub> |                            |                            | VDD = 5.0 V | —   | 1.3  | —    | mA   |    |  |  |

|                    |                  |                            |                            | VDD = 1.8 V | —   | 1.3  | —    | mA   |    |  |  |

|                    | 通常動作             |                            | VDD = 5.0 V                | —           | 3.0 | 5.0  | mA   |      |    |  |  |

|                    | 通常動作             |                            | VDD = 1.8 V                | —           | 3.0 | 5.0  | mA   |      |    |  |  |

|  |  |  |  |                                      |      |             |     |     |    |

|--|--|--|--|--------------------------------------|------|-------------|-----|-----|----|

|  |  |  |  | fmX = 8 MHz <sup>注4</sup> ,<br>方形波入力 | 通常動作 | VDD = 5.0 V | 0.8 | 1.3 | mA |

|  |  |  |  |                                      |      | VDD = 1.8 V | 0.7 | 1.3 | mA |

|  |  |  |  |                                      | 通常動作 | VDD = 5.0 V | 0.9 | 1.4 | mA |

|  |  |  |  |                                      |      | VDD = 1.8 V | 0.8 | 1.4 | mA |

注1. VDD, EVDD0に流れるトータル電流です。入力端子をVDD, EVDD0またはVss, EVSS0に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. fIH : 高速オンチップ・オシレータ・クロック周波数

備考2. fm : 中速オンチップ・オシレータ・クロック周波数

備考3. fmX : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

正)

##### 37. 3. 2 電源電流特性

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(1/4)

| 項目                 | 略号               | 条件                         |                            |             |     | MIN. | TYP. | MAX. | 単位 |  |  |

|--------------------|------------------|----------------------------|----------------------------|-------------|-----|------|------|------|----|--|--|

|                    |                  | 動作モード<br>HS (高速メイン)<br>モード | fIH = 32 MHz <sup>注2</sup> | 基本動作        |     |      |      |      |    |  |  |

| 電源電流 <sup>注1</sup> | I <sub>DD1</sub> |                            |                            | VDD = 5.0 V | —   | 1.3  | —    | mA   |    |  |  |

|                    |                  |                            |                            | VDD = 1.8 V | —   | 1.3  | —    | mA   |    |  |  |

|                    | 通常動作             |                            | VDD = 5.0 V                | —           | 3.0 | 5.0  | mA   |      |    |  |  |

|                    | 通常動作             |                            | VDD = 1.8 V                | —           | 3.0 | 5.0  | mA   |      |    |  |  |

|  |  |  |  |                                      |      |             |     |     |    |

|--|--|--|--|--------------------------------------|------|-------------|-----|-----|----|

|  |  |  |  | fmX = 8 MHz <sup>注4</sup> ,<br>方形波入力 | 通常動作 | VDD = 5.0 V | 0.8 | 1.3 | mA |

|  |  |  |  |                                      |      | VDD = 1.8 V | 0.7 | 1.3 | mA |

|  |  |  |  |                                      | 通常動作 | VDD = 5.0 V | 0.9 | 1.4 | mA |

|  |  |  |  |                                      |      | VDD = 1.8 V | 0.8 | 1.4 | mA |

注1. VDD, EVDD0に流れるトータル電流です。入力端子をVDD, EVDD0またはVss, EVSS0に固定した状態での入力リーク電流を含みます。

HS (高速メイン) モード、LS (低速メイン) モード、LP (低電力メイン) モード時、電源電流のTYP.値は周辺動作電流を含みません。MAX.値は周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. fIH : 高速オンチップ・オシレータ・クロック周波数

備考2. fm : 中速オンチップ・オシレータ・クロック周波数

備考3. fmX : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(2/4)

| 項目     | 略号               | 条件         |                  |                      | MIN.        | TYP. | MAX. | 単位 |  |  |  |  |

|--------|------------------|------------|------------------|----------------------|-------------|------|------|----|--|--|--|--|

|        |                  | 動作モード      | サブシステム・クロック動作モード | fSUB = 32.768 kHz注2, |             |      |      |    |  |  |  |  |

| 電源電流注1 | I <sub>DD1</sub> | TA = -40°C | TA = +25°C       | TA = +50°C           | 3.2         | 5.5  | μA   |    |  |  |  |  |

|        |                  |            |                  |                      | 3.5         | 5.8  |      |    |  |  |  |  |

|        |                  |            |                  |                      | 3.8         | 8.5  |      |    |  |  |  |  |

|        |                  |            |                  |                      | TA = +85°C  | 5.2  | 20.9 |    |  |  |  |  |

|        |                  |            |                  |                      | TA = +105°C | 7.7  | 38.5 |    |  |  |  |  |

- 注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注3. 高速オンチップ・オシレータ、高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータは停止時。

低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1クロック発振周波数)

発行日 : 2024年1月9日

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(2/4)

| 項目     | 略号               | 条件         |                  |                      | MIN.        | TYP. | MAX. | 単位 |  |  |  |  |

|--------|------------------|------------|------------------|----------------------|-------------|------|------|----|--|--|--|--|

|        |                  | 動作モード      | サブシステム・クロック動作モード | fSUB = 32.768 kHz注2, |             |      |      |    |  |  |  |  |

| 電源電流注1 | I <sub>DD1</sub> | TA = -40°C | TA = +25°C       | TA = +50°C           | 3.2         | 5.5  | μA   |    |  |  |  |  |

|        |                  |            |                  |                      | 3.5         | 5.8  |      |    |  |  |  |  |

|        |                  |            |                  |                      | 3.8         | 8.5  |      |    |  |  |  |  |

|        |                  |            |                  |                      | TA = +85°C  | 5.2  | 20.9 |    |  |  |  |  |

|        |                  |            |                  |                      | TA = +105°C | 7.7  | 38.5 |    |  |  |  |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

サブシステム・クロック動作モード時、電源電流のTYP.値とMAX.値は周辺動作電流を含みません。

注2. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータは停止時。

低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1クロック発振周波数)

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

( $T_A = -40 \sim +105^\circ C$ ,  $1.6 V \leq EV_{DD0} \leq V_{DD} \leq 5.5 V$ ,  $V_{SS} = EV_{SS0} = 0 V$ )

(3/4)

| 項目                 | 略号             | 条件                |                   |                        | MIN.             | TYP. | MAX. | 単位 |  |  |

|--------------------|----------------|-------------------|-------------------|------------------------|------------------|------|------|----|--|--|

|                    |                | HALT モード          | HS (高速メイン)<br>モード | $f_{IH} = 32 MHz^{注3}$ |                  |      |      |    |  |  |

| 電源電流 <sup>注1</sup> | $I_{DD2}^{注2}$ |                   |                   |                        | $V_{DD} = 5.0 V$ | 0.54 | 1.93 | mA |  |  |

|                    |                |                   |                   |                        | $V_{DD} = 1.8 V$ | 0.53 | 1.92 | mA |  |  |

| 電源電流 <sup>注1</sup> | $I_{DD2}^{注2}$ | LS (低速メイン)<br>モード | HALT モード          | $f_{IH} = 24 MHz^{注3}$ | $V_{DD} = 5.0 V$ | 0.45 | 1.50 | mA |  |  |

|                    |                |                   |                   |                        | $V_{DD} = 1.8 V$ | 0.44 | 1.49 |    |  |  |

|  |  |  |  |                                  |                  |      |      |    |

|--|--|--|--|----------------------------------|------------------|------|------|----|

|  |  |  |  | $f_{MX} = 8 MHz^{注5}$ ,<br>方形波入力 | $V_{DD} = 5.0 V$ | 0.12 | 0.47 | mA |

|  |  |  |  | $V_{DD} = 1.8 V$                 | 0.10             | 0.44 |      |    |

|  |  |  |  | $f_{MX} = 8 MHz^{注5}$ ,<br>発振子接続 | $V_{DD} = 5.0 V$ | 0.21 | 0.58 | mA |

|  |  |  |  |                                  | $V_{DD} = 1.8 V$ | 0.20 | 0.57 |    |

注1.  $V_{DD}$ ,  $EV_{DD0}$ に流れるトータル電流です。入力端子を $V_{DD}$ ,  $EV_{DD0}$ または $V_{SS}$ ,  $EV_{SS0}$ に固定した状態での入力リーコンデンサ電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1.  $f_{IH}$  : 高速オンチップ・オシレータ・クロック周波数

備考2.  $f_{IM}$  : 中速オンチップ・オシレータ・クロック周波数

備考3.  $f_{MX}$  : 高速システム・クロック周波数 ( $X1$ クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、 $T_A = 25^\circ C$ です。

発行日 : 2024年1月9日

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

( $T_A = -40 \sim +105^\circ C$ ,  $1.6 V \leq EV_{DD0} \leq V_{DD} \leq 5.5 V$ ,  $V_{SS} = EV_{SS0} = 0 V$ )

(3/4)

| 項目                 | 略号             | 条件                |                   |                        | MIN.             | TYP. | MAX. | 単位 |  |  |

|--------------------|----------------|-------------------|-------------------|------------------------|------------------|------|------|----|--|--|

|                    |                | HALT モード          | HS (高速メイン)<br>モード | $f_{IH} = 32 MHz^{注3}$ |                  |      |      |    |  |  |

| 電源電流 <sup>注1</sup> | $I_{DD2}^{注2}$ |                   |                   |                        | $V_{DD} = 5.0 V$ | 0.54 | 1.93 | mA |  |  |

|                    |                |                   |                   |                        | $V_{DD} = 1.8 V$ | 0.53 | 1.92 |    |  |  |

| 電源電流 <sup>注1</sup> | $I_{DD2}^{注2}$ | LS (低速メイン)<br>モード | HALT モード          | $f_{IH} = 24 MHz^{注3}$ | $V_{DD} = 5.0 V$ | 0.45 | 1.50 | mA |  |  |

|                    |                |                   |                   |                        | $V_{DD} = 1.8 V$ | 0.44 | 1.49 |    |  |  |

|  |  |  |  |                                  |                  |      |      |      |

|--|--|--|--|----------------------------------|------------------|------|------|------|

|  |  |  |  | $f_{MX} = 8 MHz^{注5}$ ,<br>方形波入力 | $V_{DD} = 5.0 V$ | 0.12 | 0.47 | mA   |

|  |  |  |  | $V_{DD} = 1.8 V$                 | 0.10             | 0.44 | mA   |      |

|  |  |  |  | $f_{MX} = 8 MHz^{注5}$ ,<br>発振子接続 | $V_{DD} = 5.0 V$ | 0.21 |      | 0.58 |

|  |  |  |  |                                  | $V_{DD} = 1.8 V$ | 0.20 |      | 0.57 |

注1.  $V_{DD}$ ,  $EV_{DD0}$ に流れるトータル電流です。入力端子を $V_{DD}$ ,  $EV_{DD0}$ または $V_{SS}$ ,  $EV_{SS0}$ に固定した状態での入力リーコンデンサ電流を含みます。

HS (高速メイン) モード、LS (低速メイン) モード、LP (低電力メイン) モード時、電源電流のTYP.値は周辺動作電流を含みません。MAX.値は周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1.  $f_{IH}$  : 高速オンチップ・オシレータ・クロック周波数

備考2.  $f_{IM}$  : 中速オンチップ・オシレータ・クロック周波数

備考3.  $f_{MX}$  : 高速システム・クロック周波数 ( $X1$ クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、 $T_A = 25^\circ C$ です。

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

( $T_A = -40 \sim +105^\circ C$ ,  $1.6 V \leq EVDD_0 \leq VDD \leq 5.5 V$ ,  $VSS = EVSS_0 = 0 V$ )

(4/4)

| 項目 | 略号 | 条件       |                  |                             | MIN.                 | TYP. | MAX.  | 単位 |  |

|----|----|----------|------------------|-----------------------------|----------------------|------|-------|----|--|

|    |    | HALT モード | サブシステム・クロック動作モード | $f_{SUB} = 32.768 kHz^{注3}$ |                      |      |       |    |  |

|    |    |          |                  | $T_A = -40^\circ C$         |                      | 0.53 | 2.31  |    |  |

|    |    |          |                  | $T_A = +25^\circ C$         |                      | 0.65 | 2.38  |    |  |

|    |    |          |                  |                             | $T_A = +50^\circ C$  | 0.80 | 4.95  |    |  |

|    |    |          |                  |                             | $T_A = +85^\circ C$  | 1.55 | 15.15 |    |  |

|    |    |          |                  |                             | $T_A = +105^\circ C$ | 3.40 | 30.20 |    |  |

- 注1.  $VDD$ ,  $EVDD_0$ に流れるトータル電流です。入力端子を $VDD$ ,  $EVDD_0$ または $VSS$ ,  $EVSS_0$ に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ/ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. フラッシュ・メモリでのHALT命令実行時。

- 注3. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

$RTCLPC = 1$ 、かつ低消費発振3 ( $AMPHS1, AMPHS0 = 1, 1$ ) 設定時。RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注6. 全領域のRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- STOPモード時にサブシステム・クロックを動作させる場合の電流値は、HALTモード時にサブシステム・クロックを動作させる場合の電流値を参照してください。

- 注7. 4 KバイトのRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注8. 4 KバイトのRAMを保持。

低速オンチップ・オシレータは停止時。 $RTCLPC = 1$ 、かつ低消費発振3 ( $AMPHS1, AMPHS0 = 1, 1$ ) 設定時。RTCに流れる電流は含みます。32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

備考1.  $f_{IL}$  : 低速オンチップ・オシレータ・クロック周波数

備考2.  $f_{SUB}$  : サブシステム・クロック周波数 (XT1 クロック発振周波数)

発行日 : 2024年1月9日

(1) 30~64ピン製品のフラッシュROM96~128 KBの製品

( $T_A = -40 \sim +105^\circ C$ ,  $1.6 V \leq EVDD_0 \leq VDD \leq 5.5 V$ ,  $VSS = EVSS_0 = 0 V$ )

(4/4)

| 項目 | 略号 | 条件                 |                                |          | MIN.             | TYP.                        | MAX.                | 単位   |      |

|----|----|--------------------|--------------------------------|----------|------------------|-----------------------------|---------------------|------|------|

|    |    | 電源電流 <sup>注1</sup> | I <sub>DD2</sub> <sup>注2</sup> | HALT モード | サブシステム・クロック動作モード | $f_{SUB} = 32.768 kHz^{注3}$ | $T_A = -40^\circ C$ | 0.53 | 2.31 |

|    |    |                    |                                |          |                  | $T_A = +25^\circ C$         | 0.65                | 2.38 |      |

|    |    |                    |                                |          |                  | $T_A = +50^\circ C$         | 0.80                | 4.95 |      |

|  |  |  |  |  |                      |      |       |  |

|--|--|--|--|--|----------------------|------|-------|--|

|  |  |  |  |  | $T_A = +85^\circ C$  | 1.55 | 15.15 |  |

|  |  |  |  |  | $T_A = +105^\circ C$ | 3.40 | 30.20 |  |

- 注1.  $VDD$ ,  $EVDD_0$ に流れるトータル電流です。入力端子を $VDD$ ,  $EVDD_0$ または $VSS$ ,  $EVSS_0$ に固定した状態での入力リーク電流を含みます。

サブシステム・クロック動作モードおよびSTOPモード時、電源電流のTyp.値とMax.値は周辺動作電流を含みません。

- 注2. フラッシュ・メモリでのHALT命令実行時。

- 注3. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

- 注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

- RTCLPC = 1、かつ低消費発振3 ( $AMPHS1, AMPHS0 = 1, 1$ ) 設定時。

- 注6. 全領域のRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

- STOPモード時にサブシステム・クロックを動作させる場合の電流値は、HALTモード時にサブシステム・クロックを動作させる場合の電流値を参照してください。

- 注7. 4 KバイトのRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

- 注8. 4 KバイトのRAMを保持。

低速オンチップ・オシレータは停止時。 $RTCLPC = 1$ 、かつ低消費発振3 ( $AMPHS1, AMPHS0 = 1, 1$ ) 設定時。RTCに流れる電流は含みます。

備考1.  $f_{IL}$  : 低速オンチップ・オシレータ・クロック周波数

備考2.  $f_{SUB}$  : サブシステム・クロック周波数 (XT1 クロック発振周波数)

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(1/4)

| 項目     | 略号                | 条件                         |                           |             | MIN.        | TYP. | MAX. | 単位 |

|--------|-------------------|----------------------------|---------------------------|-------------|-------------|------|------|----|

| 電源電流注1 | I <sub>DD01</sub> | 動作モード<br>HS (高速メイン)<br>モード | f <sub>H</sub> = 32 MHz注2 | 基本動作        | VDD = 5.0 V | 1.4  | —    | mA |

|        |                   |                            |                           |             | VDD = 1.8 V | 1.4  | —    | mA |

|        |                   |                            |                           | 通常動作        | VDD = 5.0 V | 3.0  | 5.0  | mA |

|        |                   |                            |                           |             | VDD = 1.8 V | 3.0  | 5.0  | mA |

|        |                   | fmX = 8 MHz注4,<br>方形波入力    | 通常動作                      | VDD = 5.0 V | 0.8         | 1.3  | mA   |    |

|        |                   |                            |                           | VDD = 1.8 V | 0.7         | 1.3  | mA   |    |

|        |                   |                            | 発振子接続                     | VDD = 5.0 V | 0.9         | 1.4  | mA   |    |

|        |                   |                            |                           | VDD = 1.8 V | 0.8         | 1.4  | mA   |    |

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. f<sub>H</sub> : 高速オンチップ・オシレータ・クロック周波数

備考2. f<sub>M</sub> : 中速オンチップ・オシレータ・クロック周波数

備考3. fm<sub>X</sub> : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

発行日 : 2024年1月9日

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EV<sub>DD0</sub> ≤ V<sub>DD</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS0</sub> = 0 V)

(1/4)

| 項目     | 略号                | 条件                                  |                           |             | MIN.        | TYP. | MAX. | 単位 |

|--------|-------------------|-------------------------------------|---------------------------|-------------|-------------|------|------|----|

| 電源電流注1 | I <sub>DD01</sub> | 動作モード<br>HS (高速メイン)<br>モード          | f <sub>H</sub> = 32 MHz注2 | 基本動作        | VDD = 5.0 V | 1.4  | —    | mA |

|        |                   |                                     |                           |             | VDD = 1.8 V | 1.4  | —    | mA |

|        |                   |                                     |                           | 通常動作        | VDD = 5.0 V | 3.0  | 5.0  | mA |

|        |                   |                                     |                           |             | VDD = 1.8 V | 3.0  | 5.0  | mA |

|        |                   | fm <sub>X</sub> = 8 MHz注4,<br>方形波入力 | 通常動作                      | VDD = 5.0 V | 0.8         | 1.3  | mA   |    |

|        |                   |                                     |                           | VDD = 1.8 V | 0.7         | 1.3  | mA   |    |

|        |                   |                                     | 発振子接続                     | VDD = 5.0 V | 0.9         | 1.4  | mA   |    |

|        |                   |                                     |                           | VDD = 1.8 V | 0.8         | 1.4  | mA   |    |

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

HS (高速メイン) モード、LS (低速メイン) モード、LP (低電力メイン) モード時、電源電流のTYP.値は周辺動作電流を含みません。MAX.値は周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. f<sub>H</sub> : 高速オンチップ・オシレータ・クロック周波数

備考2. f<sub>M</sub> : 中速オンチップ・オシレータ・クロック周波数

備考3. fm<sub>X</sub> : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(2/4)

| 項目                 | 略号               | 条件         |                  |                                        | MIN. | TYP. | MAX. | 単位 |  |

|--------------------|------------------|------------|------------------|----------------------------------------|------|------|------|----|--|

|                    |                  | 動作モード      | サブシステム・クロック動作モード | fSUB = 32.768 kHz <sup>注2</sup> , 通常動作 |      |      |      |    |  |

| 電源電流 <sup>注1</sup> | I <sub>DD1</sub> | TA = -40°C | TA = +25°C       | TA = +50°C                             | 3.3  | 6.1  | μA   |    |  |

|                    |                  |            |                  |                                        | 3.6  | 6.3  |      |    |  |

|                    |                  |            |                  |                                        | 3.9  | 9.6  |      |    |  |

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>ss</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

注3. 高速オンチップ・オシレータ、高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータは停止時。

低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1クロック発振周波数)

発行日 : 2024年1月9日

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(2/4)

| 項目                 | 略号               | 条件         |                  |                                        | MIN. | TYP. | MAX. | 単位 |  |

|--------------------|------------------|------------|------------------|----------------------------------------|------|------|------|----|--|

|                    |                  | 動作モード      | サブシステム・クロック動作モード | fSUB = 32.768 kHz <sup>注2</sup> , 通常動作 |      |      |      |    |  |

| 電源電流 <sup>注1</sup> | I <sub>DD1</sub> | TA = -40°C | TA = +25°C       | TA = +50°C                             | 3.3  | 6.1  | μA   |    |  |

|                    |                  |            |                  |                                        | 3.6  | 6.3  |      |    |  |

|                    |                  |            |                  |                                        | 3.9  | 9.6  |      |    |  |

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>ss</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

サブシステム・クロック動作モード時、電源電流のTYP.値とMAX.値は周辺動作電流を含みません。

注2. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータは停止時。

低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1クロック発振周波数)

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(3/4)

| 項目                 | 略号                             | 条件                |                                       | MIN.                                  | TYP.                    | MAX. | 単位   |

|--------------------|--------------------------------|-------------------|---------------------------------------|---------------------------------------|-------------------------|------|------|

| 電源電流 <sup>注1</sup> | I <sub>D02</sub> <sup>注2</sup> | HALT モード          | HS (高速メイン)<br>モード                     | f <sub>H</sub> = 32 MHz <sup>注3</sup> | V <sub>DD</sub> = 5.0 V | 0.57 | 1.97 |

|                    |                                |                   |                                       |                                       | V <sub>DD</sub> = 1.8 V | 0.56 | 1.96 |

|                    | I <sub>D02</sub> <sup>注2</sup> | LS (低速メイン)<br>モード | f <sub>H</sub> = 24 MHz <sup>注3</sup> | V <sub>DD</sub> = 5.0 V               | 0.47                    | 1.53 | mA   |

|                    |                                |                   |                                       | V <sub>DD</sub> = 1.8 V               | 0.47                    | 1.52 |      |

|  |  |  |  |                                      |                         |      |      |    |

|--|--|--|--|--------------------------------------|-------------------------|------|------|----|

|  |  |  |  | fmX = 8 MHz <sup>注5</sup> ,<br>方形波入力 | V <sub>DD</sub> = 5.0 V | 0.12 | 0.47 | mA |

|  |  |  |  |                                      | V <sub>DD</sub> = 1.8 V | 0.10 | 0.44 |    |

|  |  |  |  | fmX = 8 MHz <sup>注5</sup> ,<br>発振子接続 | V <sub>DD</sub> = 5.0 V | 0.21 | 0.58 | mA |

|  |  |  |  |                                      | V <sub>DD</sub> = 1.8 V | 0.20 | 0.57 |    |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入カリーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. f<sub>H</sub> : 高速オンチップ・オシレータ・クロック周波数

備考2. f<sub>M</sub> : 中速オンチップ・オシレータ・クロック周波数

備考3. fmX : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

発行日 : 2024年1月9日

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EV<sub>DD0</sub> ≤ V<sub>DD</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS0</sub> = 0 V)

(3/4)

| 項目                 | 略号                             | 条件                |                                       | MIN.                                  | TYP.                    | MAX. | 単位   |

|--------------------|--------------------------------|-------------------|---------------------------------------|---------------------------------------|-------------------------|------|------|

| 電源電流 <sup>注1</sup> | I <sub>D02</sub> <sup>注2</sup> | HALT モード          | HS (高速メイン)<br>モード                     | f <sub>H</sub> = 32 MHz <sup>注3</sup> | V <sub>DD</sub> = 5.0 V | 0.57 | 1.97 |

|                    |                                |                   |                                       |                                       | V <sub>DD</sub> = 1.8 V | 0.56 | 1.96 |

|                    | I <sub>D02</sub> <sup>注2</sup> | LS (低速メイン)<br>モード | f <sub>H</sub> = 24 MHz <sup>注3</sup> | V <sub>DD</sub> = 5.0 V               | 0.47                    | 1.53 | mA   |

|                    |                                |                   |                                       | V <sub>DD</sub> = 1.8 V               | 0.47                    | 1.52 |      |

|  |  |  |  |                                      |                         |      |      |    |

|--|--|--|--|--------------------------------------|-------------------------|------|------|----|

|  |  |  |  | fmX = 8 MHz <sup>注5</sup> ,<br>方形波入力 | V <sub>DD</sub> = 5.0 V | 0.12 | 0.47 | mA |

|  |  |  |  |                                      | V <sub>DD</sub> = 1.8 V | 0.10 | 0.44 |    |

|  |  |  |  | fmX = 8 MHz <sup>注5</sup> ,<br>発振子接続 | V <sub>DD</sub> = 5.0 V | 0.21 | 0.58 | mA |

|  |  |  |  |                                      | V <sub>DD</sub> = 1.8 V | 0.20 | 0.57 |    |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入カリーク電流を含みます。

HS (高速メイン) モード、LS (低速メイン) モード、LP (低電力メイン) モード時、電源電流のTYP.値は周辺動作電流を含みません。MAX.値は周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. f<sub>H</sub> : 高速オンチップ・オシレータ・クロック周波数

備考2. f<sub>M</sub> : 中速オンチップ・オシレータ・クロック周波数

備考3. fmX : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(4/4)

| 項目     | 略号                  | 条件       |                  |                                        | MIN.       | TYP. | MAX. | 単位 |

|--------|---------------------|----------|------------------|----------------------------------------|------------|------|------|----|

| 電源電流注1 | I <sub>DD2</sub> 注2 | HALT モード | サブシステム・クロック動作モード | fsUB = 32.768 kHz注3<br>低速オンチップ・オシレータ動作 | TA = -40°C | 0.62 | 2.94 | μA |

|        |                     |          |                  |                                        | TA = +25°C | 0.74 | 3.00 |    |

|        |                     |          |                  |                                        | TA = +50°C | 0.88 | 6.00 |    |

|  |  |  |  |             |      |       |  |

|--|--|--|--|-------------|------|-------|--|

|  |  |  |  | TA = +85°C  | 2.14 | 19.14 |  |

|  |  |  |  | TA = +105°C | 4.16 | 45.16 |  |

- 注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. フラッシュ・メモリでのHALT命令実行時。

- 注3. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注6. 全領域のRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- STOPモード時にサブシステム・クロックを動作させる場合の電流値は、HALTモード時にサブシステム・クロックを動作させる場合の電流値を参照してください。

- 注7. 4 KバイトのRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注8. 4 KバイトのRAMを保持。

低速オンチップ・オシレータは停止時。RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTCに流れる電流は含みます。32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1 クロック発振周波数)

発行日 : 2024年1月9日

(2) 30~64 ピン製品のフラッシュ ROM192~256 KB の製品および 80 ピン製品のフラッシュ ROM128~256 KB の製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(4/4)

| 項目     | 略号                  | 条件       |                  |                                        | MIN.       | TYP. | MAX. | 単位 |

|--------|---------------------|----------|------------------|----------------------------------------|------------|------|------|----|

| 電源電流注1 | I <sub>DD2</sub> 注2 | HALT モード | サブシステム・クロック動作モード | fsUB = 32.768 kHz注3<br>低速オンチップ・オシレータ動作 | TA = -40°C | 0.62 | 2.94 | μA |

|        |                     |          |                  |                                        | TA = +25°C | 0.74 | 3.00 |    |

|        |                     |          |                  |                                        | TA = +50°C | 0.88 | 6.00 |    |

|  |  |  |  |             |      |       |  |

|--|--|--|--|-------------|------|-------|--|

|  |  |  |  | TA = +85°C  | 2.14 | 19.14 |  |

|  |  |  |  | TA = +105°C | 4.16 | 45.16 |  |

- 注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

サブシステム・クロック動作モードおよびSTOPモード時、電源電流のTyp.値とMax.値は周辺動作電流を含みません。

- 注2. フラッシュ・メモリでのHALT命令実行時。

- 注3. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

- 注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

- RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。

- 注6. 全領域のRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

STOPモード時にサブシステム・クロックを動作させる場合の電流値は、HALTモード時にサブシステム・クロックを動作させる場合の電流値を参照してください。

- 注7. 4 KバイトのRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

- 注8. 4 KバイトのRAMを保持。

低速オンチップ・オシレータは停止時。RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTCに流れる電流は含みます。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1 クロック発振周波数)

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品 ( $T_A = -40 \sim +105^\circ\text{C}$ ,  $1.6 \text{ V} \leq EV_{DD0} \leq V_{DD} \leq 5.5 \text{ V}$ ,  $V_{SS} = EV_{SS0} = 0 \text{ V}$ )

(1/4)

| 項目                 | 略号               | 条件                                               |                                       |                         | MIN.                    | TYP. | MAX. | 単位 |

|--------------------|------------------|--------------------------------------------------|---------------------------------------|-------------------------|-------------------------|------|------|----|

| 電源電流 <sup>注1</sup> | I <sub>DD1</sub> | 動作モード<br>HS (高速メイン)<br>モード                       | f <sub>H</sub> = 32 MHz <sup>注2</sup> | 基本動作                    | V <sub>DD</sub> = 5.0 V | 1.6  | —    | mA |

|                    |                  |                                                  |                                       |                         | V <sub>DD</sub> = 1.8 V | 1.5  | —    | mA |

|                    |                  |                                                  |                                       | 通常動作                    | V <sub>DD</sub> = 5.0 V | 3.5  | 5.6  | mA |

|                    |                  |                                                  |                                       |                         | V <sub>DD</sub> = 1.8 V | 3.5  | 5.6  | mA |

|                    |                  | fm <sub>X</sub> = 8 MHz <sup>注4</sup> ,<br>方形波入力 | 通常動作                                  | V <sub>DD</sub> = 5.0 V | 0.9                     | 1.5  | mA   |    |

|                    |                  |                                                  |                                       | V <sub>DD</sub> = 1.8 V | 0.9                     | 1.5  | mA   |    |

|                    |                  |                                                  | 発振子接続                                 | V <sub>DD</sub> = 5.0 V | 1.0                     | 1.6  | mA   |    |

|                    |                  |                                                  |                                       | V <sub>DD</sub> = 1.8 V | 1.0                     | 1.6  | mA   |    |

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

- 注1.  $V_{DD}$ ,  $EV_{DD0}$ に流れるトータル電流です。入力端子を $V_{DD}$ ,  $EV_{DD0}$ または $V_{SS}$ ,  $EV_{SS0}$ に固定した状態での入力リーク電流を含みます。

**またMAX.値には周辺動作電流を含みます。**ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

- 注3. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. f<sub>H</sub> : 高速オンチップ・オシレータ・クロック周波数

備考2. f<sub>M</sub> : 中速オンチップ・オシレータ・クロック周波数

備考3. fm<sub>X</sub> : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、 $T_A = 25^\circ\text{C}$ です。

発行日 : 2024年1月9日

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品 ( $T_A = -40 \sim +105^\circ\text{C}$ ,  $1.6 \text{ V} \leq EV_{DD0} = EV_{DD1} \leq V_{DD} \leq 5.5 \text{ V}$ ,  $V_{SS} = EV_{SS0} = EV_{SS1} = 0 \text{ V}$ )

(1/4)

| 項目                 | 略号               | 条件                                               |                                       |                         | MIN.                    | TYP. | MAX. | 単位 |

|--------------------|------------------|--------------------------------------------------|---------------------------------------|-------------------------|-------------------------|------|------|----|

| 電源電流 <sup>注1</sup> | I <sub>DD1</sub> | 動作モード<br>HS (高速メイン)<br>モード                       | f <sub>H</sub> = 32 MHz <sup>注2</sup> | 基本動作                    | V <sub>DD</sub> = 5.0 V | 1.6  | —    | mA |

|                    |                  |                                                  |                                       |                         | V <sub>DD</sub> = 1.8 V | 1.5  | —    | mA |

|                    |                  |                                                  |                                       | 通常動作                    | V <sub>DD</sub> = 5.0 V | 3.5  | 5.6  | mA |

|                    |                  |                                                  |                                       |                         | V <sub>DD</sub> = 1.8 V | 3.5  | 5.6  | mA |

|                    |                  | fm <sub>X</sub> = 8 MHz <sup>注4</sup> ,<br>方形波入力 | 通常動作                                  | V <sub>DD</sub> = 5.0 V | 0.9                     | 1.5  | mA   |    |

|                    |                  |                                                  |                                       | V <sub>DD</sub> = 1.8 V | 0.9                     | 1.5  | mA   |    |

|                    |                  |                                                  | 発振子接続                                 | V <sub>DD</sub> = 5.0 V | 1.0                     | 1.6  | mA   |    |

|                    |                  |                                                  |                                       | V <sub>DD</sub> = 1.8 V | 1.0                     | 1.6  | mA   |    |

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |

- 注1.  $V_{DD}$ ,  $EV_{DD0}$ ,  $EV_{DD1}$ に流れるトータル電流です。入力端子を $V_{DD}$ ,  $EV_{DD0}$ ,  $EV_{DD1}$ または $V_{SS}$ ,  $EV_{SS0}$ ,  $EV_{SS1}$ に固定した状態での入力リーク電流を含みます。**HS (高速メイン) モード、LS (低速メイン) モード、LP (低電力メイン) モード時、電源電流のTYP.値は周辺動作電流を含みません。**MAX.値は周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

- 注3. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. f<sub>H</sub> : 高速オンチップ・オシレータ・クロック周波数

備考2. f<sub>M</sub> : 中速オンチップ・オシレータ・クロック周波数

備考3. fm<sub>X</sub> : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、 $T_A = 25^\circ\text{C}$ です。

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品 (TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(2/4)

| 項目     | 略号               | 条件     |                  |       | MIN.             | TYP.                             | MAX. | 単位 |  |  |  |  |

|--------|------------------|--------|------------------|-------|------------------|----------------------------------|------|----|--|--|--|--|

|        |                  | 電源電流注1 | I <sub>DD1</sub> | 動作モード | サブシステム・クロック動作モード | f <sub>SUB</sub> = 32.768 kHz注2, | 通常動作 |    |  |  |  |  |

| 電源電流注1 | I <sub>DD1</sub> |        |                  |       | TA = -40°C       | 3.8                              | 7.7  | μA |  |  |  |  |

|        |                  |        |                  |       | TA = +25°C       | 4.1                              | 8.0  |    |  |  |  |  |

|        |                  |        |                  |       | TA = +50°C       | 4.6                              | 13.5 |    |  |  |  |  |

|        |                  |        |                  |       | TA = +85°C       | 6.8                              | 39.8 |    |  |  |  |  |

|        |                  |        |                  |       | TA = +105°C      | 10.8                             | 87.4 |    |  |  |  |  |

- 注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>ss</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注3. 高速オンチップ・オシレータ、高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータは停止時。

低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1クロック発振周波数)

発行日 : 2024年1月9日

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品 (TA = -40~+105°C, 1.6 V ≤ EVDD0 = EVDD1 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = EVSS1 = 0 V)

(2/4)

| 項目     | 略号               | 条件     |                  |       | MIN.             | TYP.                             | MAX. | 単位 |  |  |  |  |

|--------|------------------|--------|------------------|-------|------------------|----------------------------------|------|----|--|--|--|--|

|        |                  | 電源電流注1 | I <sub>DD1</sub> | 動作モード | サブシステム・クロック動作モード | f <sub>SUB</sub> = 32.768 kHz注2, | 通常動作 |    |  |  |  |  |

| 電源電流注1 | I <sub>DD1</sub> |        |                  |       | TA = -40°C       | 3.8                              | 7.7  | μA |  |  |  |  |

|        |                  |        |                  |       | TA = +25°C       | 4.1                              | 8.0  |    |  |  |  |  |

|        |                  |        |                  |       | TA = +50°C       | 4.6                              | 13.5 |    |  |  |  |  |

|        |                  |        |                  |       | TA = +85°C       | 6.8                              | 39.8 |    |  |  |  |  |

|        |                  |        |                  |       | TA = +105°C      | 10.8                             | 87.4 |    |  |  |  |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>, EV<sub>DD1</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>, EV<sub>DD1</sub>またはV<sub>ss</sub>, EV<sub>SS0</sub>, EV<sub>SS1</sub>に固定した状態での入力リーク電流を含みます。サブシステム・クロック動作モード時、電源電流のTYP.値とMAX.値は周辺動作電流を含みません。

注2. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

注3. 高速オンチップ・オシレータ、高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータは停止時。

低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数

備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1クロック発振周波数)

# RENESAS TECHNICAL UPDATE TN-RL\*-A0132A/J

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品 (TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(3/4)

| 項目                 | 略号                             | HALT モード | 条件                |                            | MIN.        | TYP. | MAX. | 単位 |

|--------------------|--------------------------------|----------|-------------------|----------------------------|-------------|------|------|----|

|                    |                                |          | HS (高速メイン)<br>モード | fIH = 32 MHz <sup>注3</sup> |             |      |      |    |

| 電源電流 <sup>注1</sup> | I <sub>D02</sub> <sup>注2</sup> |          | LS (低速メイン)<br>モード | fIH = 24 MHz <sup>注3</sup> | VDD = 5.0 V | 0.60 | 2.00 | mA |

|                    |                                |          |                   |                            | VDD = 1.8 V | 0.59 | 1.99 |    |

| 電源電流 <sup>注1</sup> | I <sub>D02</sub> <sup>注2</sup> |          | LS (低速メイン)<br>モード | fIH = 24 MHz <sup>注3</sup> | VDD = 5.0 V | 0.49 | 1.56 | mA |

|                    |                                |          |                   |                            | VDD = 1.8 V | 0.48 | 1.55 |    |

|  |  |  |  |                                      |             |      |      |    |

|--|--|--|--|--------------------------------------|-------------|------|------|----|

|  |  |  |  | fMX = 8 MHz <sup>注5</sup> ,<br>方形波入力 | VDD = 5.0 V | 0.13 | 0.48 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.11 | 0.45 |    |

|  |  |  |  |                                      | VDD = 5.0 V | 0.22 | 0.59 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.21 | 0.58 |    |

|  |  |  |  | fMX = 8 MHz <sup>注5</sup> ,<br>発振子接続 | VDD = 5.0 V | 0.13 | 0.48 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.11 | 0.45 |    |

|  |  |  |  |                                      | VDD = 5.0 V | 0.22 | 0.59 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.21 | 0.58 |    |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーケ電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. fIH : 高速オンチップ・オシレータ・クロック周波数

備考2. fIM : 中速オンチップ・オシレータ・クロック周波数

備考3. fMX : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

発行日 : 2024年1月9日

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品

(TA = -40~+105°C, 1.6 V ≤ EV<sub>DD0</sub> = EV<sub>DD1</sub> ≤ V<sub>DD</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS0</sub> = EV<sub>SS1</sub> = 0 V)

(3/4)

| 項目                 | 略号                             | HALT モード | 条件                |                            | MIN.        | TYP. | MAX. | 単位 |

|--------------------|--------------------------------|----------|-------------------|----------------------------|-------------|------|------|----|

|                    |                                |          | HS (高速メイン)<br>モード | fIH = 32 MHz <sup>注3</sup> |             |      |      |    |

| 電源電流 <sup>注1</sup> | I <sub>D02</sub> <sup>注2</sup> |          | LS (低速メイン)<br>モード | fIH = 24 MHz <sup>注3</sup> | VDD = 5.0 V | 0.60 | 2.00 | mA |

|                    |                                |          |                   |                            | VDD = 1.8 V | 0.59 | 1.99 |    |

| 電源電流 <sup>注1</sup> | I <sub>D02</sub> <sup>注2</sup> |          | LS (低速メイン)<br>モード | fIH = 24 MHz <sup>注3</sup> | VDD = 5.0 V | 0.49 | 1.56 | mA |

|                    |                                |          |                   |                            | VDD = 1.8 V | 0.48 | 1.55 |    |

|  |  |  |  |                                      |             |      |      |    |

|--|--|--|--|--------------------------------------|-------------|------|------|----|

|  |  |  |  | fMX = 8 MHz <sup>注5</sup> ,<br>方形波入力 | VDD = 5.0 V | 0.13 | 0.48 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.11 | 0.45 |    |

|  |  |  |  |                                      | VDD = 5.0 V | 0.22 | 0.59 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.21 | 0.58 |    |

|  |  |  |  | fMX = 8 MHz <sup>注5</sup> ,<br>発振子接続 | VDD = 5.0 V | 0.13 | 0.48 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.11 | 0.45 |    |

|  |  |  |  |                                      | VDD = 5.0 V | 0.22 | 0.59 | mA |

|  |  |  |  |                                      | VDD = 1.8 V | 0.21 | 0.58 |    |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>, EV<sub>DD1</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS1</sub>に固定した状態での入力リーケ電流を含みます。HS (高速メイン) モード、LS (低速メイン) モード、LP (低電力メイン) モード時、電源電流のTYP.値は周辺動作電流を含みません。MAX.値は周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵プルアップ／プルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速システム・クロック、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、低速オンチップ・オシレータ、サブシステム・クロックは停止時。

備考1. fIH : 高速オンチップ・オシレータ・クロック周波数

備考2. fIM : 中速オンチップ・オシレータ・クロック周波数

備考3. fMX : 高速システム・クロック周波数 (X1クロック発振周波数または外部メイン・システム・クロック周波数)

備考4. 特に指定がない場合のTYP.値の温度条件は、TA = 25°Cです。

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = 0 V)

(4/4)

| 項目     | 略号                  | 条件       |                  |                     | MIN.       | TYP. | MAX. | 単位 |

|--------|---------------------|----------|------------------|---------------------|------------|------|------|----|

| 電源電流注1 | I <sub>DD2</sub> 注2 | HALT モード | サブシステム・クロック動作モード | fsUB = 32.768 kHz注3 | TA = -40°C | 0.62 | 3.95 | μA |

|        |                     |          |                  |                     | TA = +25°C | 0.78 | 4.00 |    |

|        |                     |          |                  |                     | TA = +50°C | 1.03 | 9.16 |    |

|  |  |  |  |             |      |       |  |

|--|--|--|--|-------------|------|-------|--|

|  |  |  |  | TA = +85°C  | 2.23 | 30.13 |  |

|  |  |  |  | TA = +105°C | 4.64 | 70.14 |  |

- 注1. V<sub>DD</sub>, EV<sub>DD0</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>に固定した状態での入力リーク電流を含みます。

またMAX.値には周辺動作電流を含みます。ただし、A/Dコンバータ、LVD回路、I/Oポート、内蔵ブルアップ／ブルダウン抵抗、データ・フラッシュ書き換え時に流れる電流は含みません。

- 注2. フラッシュ・メモリでのHALT命令実行時。

- 注3. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注6. 全領域のRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- STOPモード時にサブシステム・クロックを動作させる場合の電流値は、HALTモード時にサブシステム・クロックを動作させる場合の電流値を参照してください。

- 注7. 4 KバイトのRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

RTC、32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

- 注8. 4 KバイトのRAMを保持。

低速オンチップ・オシレータは停止時。RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTCに流れる電流は含みます。32ビット・インターバル・タイマ、ウォッチャドッグ・タイマに流れる電流は含みません。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1 クロック発振周波数)

(3) 44~80 ピン製品のフラッシュ ROM384~768 KB の製品および 100~128 ピン製品

(TA = -40~+105°C, 1.6 V ≤ EVDD0 = EVDD1 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = EVSS1 = 0 V)

(4/4)

| 項目     | 略号                  | 条件       |                  |                     | MIN.       | TYP. | MAX. | 単位 |

|--------|---------------------|----------|------------------|---------------------|------------|------|------|----|

| 電源電流注1 | I <sub>DD2</sub> 注2 | HALT モード | サブシステム・クロック動作モード | fsUB = 32.768 kHz注3 | TA = -40°C | 0.62 | 3.95 | μA |

|        |                     |          |                  |                     | TA = +25°C | 0.78 | 4.00 |    |

|        |                     |          |                  |                     | TA = +50°C | 1.03 | 9.16 |    |

|  |  |  |  |             |      |       |  |

|--|--|--|--|-------------|------|-------|--|

|  |  |  |  | TA = +85°C  | 2.23 | 30.13 |  |

|  |  |  |  | TA = +105°C | 4.64 | 70.14 |  |

注1. V<sub>DD</sub>, EV<sub>DD0</sub>, EV<sub>DD1</sub>に流れるトータル電流です。入力端子をV<sub>DD</sub>, EV<sub>DD0</sub>, EV<sub>DD1</sub>またはV<sub>SS</sub>, EV<sub>SS0</sub>, EV<sub>SS1</sub>に固定した状態での入力リーク電流を含みます。サブシステム・クロック動作モードおよびSTOPモード時、電源電流のTyp.値とMax.値は周辺動作電流を含みません。

注2. フラッシュ・メモリでのHALT命令実行時。

注3. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、サブシステム・クロックは停止時。

注4. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

注5. 高速オンチップ・オシレータ、中速オンチップ・オシレータ、高速システム・クロック、低速オンチップ・オシレータは停止時。

RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。

注6. 全領域のRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

STOPモード時にサブシステム・クロックを動作させる場合の電流値は、HALTモード時にサブシステム・クロックを動作させる場合の電流値を参照してください。

注7. 4 KバイトのRAMを保持。

低速オンチップ・オシレータ、サブシステム・クロック発振は停止時。

注8. 4 KバイトのRAMを保持。

低速オンチップ・オシレータは停止時。RTCLPC = 1、かつ低消費発振3 (AMPHS1, AMPHS0 = 1, 1) 設定時。RTCに流れる電流は含みます。

備考1. f<sub>L</sub> : 低速オンチップ・オシレータ・クロック周波数備考2. f<sub>SUB</sub> : サブシステム・クロック周波数 (XT1 クロック発振周波数)

## 5. 37.6.4 コンパレータ特性 (p.1495)

誤)

### 37.6.4 コンパレータ特性

(TA = -40~+105°C, 1.6 V ≤ EVDD0 = EVDD1 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = EVSS1 = 0 V)

| 項目       | 略号    | 条件                                      | MIN.               | TYP.                   | MAX.       | 単位 |

|----------|-------|-----------------------------------------|--------------------|------------------------|------------|----|

| 入力電圧範囲   | IVREF | IVREF0端子、IVREF1端子入力<br>C0LVL, C1LVL = 0 | 0                  | Vdd-1.4<br>かつ<br>EVDD0 | V          |    |

|          |       | IVREF0端子、IVREF1端子入力<br>C0LVL, C1LVL = 1 | 1.4                | EVDD0                  | V          |    |

|          | IVCMP | IVCMPO, IVCMP1端子入力                      | -0.3               | EVDD0 +<br>0.3         | V          |    |

| 出力遅延     | td    | VDD = 3.0 V,<br>入力スルーレート > 1 V/μs       | 高速モード<br><br>低速モード |                        | 1.5<br>3.0 | μs |

| オフセット電圧  | —     | 高速モード<br><br>低速モード                      |                    |                        | 50<br>40   | mV |

| 動作安定待ち時間 | tCMP  |                                         | 30                 |                        |            | μs |

| 内部基準電圧   | VBGR2 |                                         | 1.4                |                        | 1.6        | V  |

正)

### 37.6.4 コンパレータ特性

(TA = -40~+105°C, 1.6 V ≤ EVDD0 = EVDD1 ≤ VDD ≤ 5.5 V, Vss = EVSS0 = EVSS1 = 0 V)

| 項目                   | 略号    | 条件                                      | MIN.               | TYP.                              | MAX.                   | 単位         |

|----------------------|-------|-----------------------------------------|--------------------|-----------------------------------|------------------------|------------|

| 入力電圧範囲               | IVREF | IVREF0端子、IVREF1端子入力<br>C0LVL, C1LVL = 0 | 0                  |                                   | Vdd-1.4<br>かつ<br>EVDD0 | V          |

|                      |       | IVREF0端子、IVREF1端子入力<br>C0LVL, C1LVL = 1 | 1.4                |                                   | EVDD0                  | V          |

|                      | IVCMP | IVCMPO, IVCMP1端子入力                      | -0.3               |                                   | EVDD0 +<br>0.3         | V          |

| 出力遅延                 | td    | VDD = 3.0 V,<br>入力スルーレート > 1 V/μs       | 高速モード<br><br>低速モード | VDD = 3.0 V,<br>入力スルーレート > 1 V/μs | 高速モード<br><br>低速モード     | 1.5<br>3.0 |

|                      |       |                                         |                    |                                   |                        | μs         |

| オフセット電圧              | —     | 高速モード<br><br>低速モード                      | 50<br>40           |                                   | 50                     | mV         |

|                      |       |                                         |                    |                                   | 40                     | mV         |

| 動作安定待ち時間             | tCMP  |                                         |                    |                                   | 30                     | μs         |

| 内部基準電圧 <sup>注1</sup> | VBGR2 |                                         |                    |                                   | 1.4                    | V          |

|                      |       |                                         |                    |                                   | 1.6                    |            |

注 1. コンパレータ基準電圧に内部基準電圧を選択した場合は、1.8V ≤ VDD ≤ 5.5V の範囲内で使用してください。

## 6. 12.3.3 A/D コンバータ・モード・レジスタ 0 (ADM0) (p.567, p.570 ~ p.578)

誤)

(p.567)

| A/D電圧コンパレータの動作制御 <sup>注2</sup> |                   |

|--------------------------------|-------------------|

| 0                              | A/D 電圧コンパレータの動作停止 |

| 1                              | A/D 電圧コンパレータの動作許可 |

注1. FR2-FR0, LV1, LV0ビットおよびA/D変換に関する詳細は、表12 - 3 A/D変換時間の選択（1/8）を参照してください。

注2. ソフトウェア・トリガ・ノーウエイト・モード時およびハードウェア・トリガ・ノーウエイト・モード時、A/D電圧コンパレータはADCSビットとADCEビットで動作制御され、動作開始から安定するまでに、 $1\ \mu s +$  変換クロック (fAD) の2クロックかかります。このため、ADCEビットに1を設定してから $1\ \mu s +$  変換クロック (fAD) の2クロック以上経過したあとに、ADCSビットに1を設定することで、最初の変換データより有効となります。ADCE = 0状態でADCS = 1に設定した場合は、安定待ち後A/D変換を開始します。 $1\ \mu s +$  変換クロック (fAD) の2クロック以上ウエイトしないでADCSビットに1を設定した場合は、最初の変換データを無視してください。

注意1. ADMD, FR2-FR0, LV1, LV0ビットの変更は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

注意2. ADCS = 1, ADCE = 1からADCS = 1, ADCE = 0への設定は禁止です。

注意3. ADCS = 0, ADCE = 0設定状態から8ビット操作命令でADCS = 1, ADCE = 1に設定することは禁止します。必ず12.7 A/Dコンバータの設定フロー・チャートの手順に従ってください。

正)

| A/D電圧コンパレータの動作制御 <sup>注2</sup> |                   |

|--------------------------------|-------------------|

| 0                              | A/D 電圧コンパレータの動作停止 |

| 1                              | A/D 電圧コンパレータの動作許可 |

注1. FR2-FR0, LV1, LV0ビットおよびA/D変換に関する詳細は、表12 - 3 A/D変換時間の選択（1/8）を参照してください。

注2. ソフトウェア・トリガ・ノーウエイト・モード時およびハードウェア・トリガ・ノーウエイト・モード時、A/D電圧コンパレータはADCSビットとADCEビットで動作制御され、動作開始から安定するまでに、 $1\ \mu s +$  変換クロック (fAD) の2クロックかかります。このため、ADCEビットに1を設定してから $1\ \mu s +$  変換クロック (fAD) の2クロック以上経過したあとに、ADCSビットに1を設定することで、最初の変換データより有効となります。ADCE = 0状態でADCS = 1に設定した場合は、安定待ち後A/D変換を開始します。 $1\ \mu s +$  変換クロック (fAD) の2クロック以上ウエイトしないでADCSビットに1を設定した場合は、最初の変換データを無視してください。

注意1. ADMD, FR2-FR0, LV1, LV0ビットの変更は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

注意2. ADCS = 1, ADCE = 1からADCS = 1, ADCE = 0への設定は禁止です。

注意3. ADCS = 0, ADCE = 0設定状態から8ビット操作命令でADCS = 1, ADCE = 1に設定することは禁止します。必ず12.7 A/Dコンバータの設定フロー・チャートの手順に従ってください。

注意4. 変換待機状態／変換動作状態からADCS=0, ADCE=0の変換停止状態にした場合は、次にADCE=1またはADCS=1を設定するまでに $5\ \mu s$ ウエイトしてください。なお、ADMD, FR2-FR0, LV1, LV0ビットを変更する場合は、ADCS=0, ADCE=0に設定した後、 $0.2\ \mu s$ 経過後にADMD, FR2-FR0, LV1, LV0ビットを変更してください。

(p.570)

| ADM1 | ADM0  |     |     | 変換クロック<br>(fAD) | 起動時間 (fCLKクロック数)                            |                                         |

|------|-------|-----|-----|-----------------|---------------------------------------------|-----------------------------------------|

|      | ADLSP | FR2 | FR1 |                 | ソフトウェア・トリガ・ノーウエイト・モード／ハードウェア・トリガ・ノーウエイト・モード | ソフトウェア・トリガ・ウェイト・モード／ハードウェア・トリガ・ウェイト・モード |

| 0    | 0     | 0   | 0   | fCLK/32         | 31                                          | 1                                       |

| 0    | 0     | 0   | 1   | fCLK/16         | 15                                          | 1                                       |

| 0    | 0     | 1   | 0   | fCLK/8          | 7                                           | 1                                       |

| 0    | 0     | 1   | 1   | fCLK/4          | 3                                           | 1                                       |

| 0    | 1     | 0   | 0   | fCLK/2          | 1                                           | 1                                       |

| 0    | 1     | 0   | 1   | fCLK            | 1                                           | 1                                       |

| 1    | 0     | 1   | 1   | fCLK/4          | 3                                           | 1                                       |

| 1    | 1     | 0   | 0   | fCLK/2          | 1                                           | 1                                       |

| 1    | 1     | 0   | 1   | fCLK            | 1                                           | 1                                       |

ただし、連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません。

注意1. ハードウェア・トリガ・ウェイト・モードで使用する場合、ADCSビットに1を設定するのは禁止です（ハードウェア・トリガ信号検出時に、自動的に1に切り替わります）。ただし、A/D変換待機状態にするために、ADCSビットに0を設定することは可能です。

注意2. ハードウェア・トリガ・ノーウエイト・モードでのワンショット変換モード時、A/D変換終了時にADCSビットは、自動的に0にクリアされません。1のまま保持されます。

注意3. ADCEビットの書き換えは、ADCS = 0（変換停止／変換待機状態）のときに行ってください。

注意4. A/D変換を完了させるためには、ハード・トリガ間隔を次の時間以上としてください。

ハードウェア・トリガ・ノーウエイト・モード時 : fCLK の2クロック + 変換起動時間 + A/D変換時間

ハードウェア・トリガ・ウェイト・モード時 : fCLK の2クロック + 変換起動時間 + A/D電源安定待ち時間 + A/D変換時間

| ADM1 | ADM0  |     |     | 変換クロック<br>(fAD) | 起動時間 (fCLKクロック数)                            |                                         |

|------|-------|-----|-----|-----------------|---------------------------------------------|-----------------------------------------|

|      | ADLSP | FR2 | FR1 |                 | ソフトウェア・トリガ・ノーウエイト・モード／ハードウェア・トリガ・ノーウエイト・モード | ソフトウェア・トリガ・ウェイト・モード／ハードウェア・トリガ・ウェイト・モード |

| 0    | 0     | 0   | 0   | fCLK/32         | 31                                          | 1                                       |

| 0    | 0     | 0   | 1   | fCLK/16         | 15                                          | 1                                       |

| 0    | 0     | 1   | 0   | fCLK/8          | 7                                           | 1                                       |

| 0    | 0     | 1   | 1   | fCLK/4          | 3                                           | 1                                       |

| 0    | 1     | 0   | 0   | fCLK/2          | 1                                           | 1                                       |

| 0    | 1     | 0   | 1   | fCLK            | 1                                           | 1                                       |

| 1    | 0     | 1   | 1   | fCLK/4          | 3                                           | 1                                       |

| 1    | 1     | 0   | 0   | fCLK/2          | 1                                           | 1                                       |

| 1    | 1     | 0   | 1   | fCLK            | 1                                           | 1                                       |

ただし、連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません。

注意1. ハードウェア・トリガ・ウェイト・モードで使用する場合、ADCSビットに1を設定するのは禁止です（ハードウェア・トリガ信号検出時に、自動的に1に切り替わります）。ただし、A/D変換待機状態にするために、ADCSビットに0を設定することは可能です。

注意2. ハードウェア・トリガ・ノーウエイト・モードでのワンショット変換モード時、A/D変換終了時にADCSビットは、自動的に0にクリアされません。1のまま保持されます。

注意3. ADCEビットの書き換えは、ADCS = 0（変換停止／変換待機状態）のときに行ってください。

注意4. A/D変換を完了させるためには、ハード・トリガ間隔を次の時間以上としてください。

ハードウェア・トリガ・ノーウエイト・モード時 : fCLK の2クロック + 変換起動時間 + A/D変換時間

ハードウェア・トリガ・ウェイト・モード時 : fCLK の2クロック + 変換起動時間 + A/D電源安定待ち時間 + A/D変換時間 + 5μs

(p.571)

表12 - 3 A/D変換時間の選択 (1/8)

## (1) A/D電源安定待ち時間なし 標準モード1, 2

(ソフトウェア・トリガ・ノーウエイト・セレクト・モード／ハードウェア・トリガ・ノーウエイト・セレクト・モード)

| A/Dコンバータ・モード・レジスタ0<br>A/Dコンバータ・モード・レジスタ1<br>(AD M1)<br>ADL SP |     |     |     |     |     | モード     | 変換クロック(fAD) | 変換開始遅延クロック数 | 変換クロック数 | 割り込み出力遅延クロック数 | A/D変換時間<br>(変換開始遅延時間 + 変換時間 + 割り込み出力遅延時間) |      |      |      |      |  |

|---------------------------------------------------------------|-----|-----|-----|-----|-----|---------|-------------|-------------|---------|---------------|-------------------------------------------|------|------|------|------|--|

| FR2                                                           | FR1 | FR0 | LV1 | LV0 |     |         |             |             |         |               | 2.4 V ≤ AVREFP ≤ VDD ≤ 5.5 V              |      |      |      |      |  |

| 0                                                             | 0   | 0   | 0   | 0   | 標準1 | fCLK/32 | 1 fAD       | 64 fAD      | 1 fAD   | 2112/fCLK     | 設定禁止                                      | 設定禁止 | 設定禁止 | 設定禁止 | 66μs |  |

| 0                                                             | 0   | 0   | 1   |     |     | fCLK/16 | 1 fAD       | 64 fAD      | 1 fAD   | 1056/fCLK     | 設定禁止                                      | 設定禁止 | 設定禁止 | 設定禁止 | 66μs |  |

|                                                               |     |     |     |     |     |         |             |             |         |               |                                           |      |      |      | 33μs |  |

| 1    | 1 | 0 | 0 |  |  |  |  |  |  |  |  |  |  |  |

|------|---|---|---|--|--|--|--|--|--|--|--|--|--|--|

| 1    | 1 | 0 | 1 |  |  |  |  |  |  |  |  |  |  |  |

| 上記以外 |   |   |   |  |  |  |  |  |  |  |  |  |  |  |

| 設定禁止 |   |   |   |  |  |  |  |  |  |  |  |  |  |  |

注意1. A/D変換時間は、37.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。

また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してください。

注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、標準モード2を使用してください。

注意5. +側の基準電圧に内部基準電圧を選択したときは、標準モード1, 2は使用できません。低電圧モード1, 2を使用してください。

表12 - 3 A/D変換時間の選択 (1/8)