# **Packaging Information**

Surface Mount Assembly Guidelines for Optical Dual Flat Pack No Lead (ODFN) Package

#### **Abstract**

Optical Dual-in-line Flat No-lead (ODFN) packages are developed for light sensor applications. The ODFN mechanical structure is similar to that of a conventional DFN, except the molding compound is a transparent material rather than the conventional black compound. Transparent molding compound allows transmission of ambient light through the molding compound to reach the die sensor area. This package is lead-free, with pre-plated Nickel-Palladium-Gold (NiPdAu) finish on the terminals. Figure 1 shows a 6 Ld ODFN. As the image shows, the package finish is transparent to allow light transmission and at the same time, protects the device from the environment.

Figure 1. 6 Ld ODFN Top View (Left) and Bottom View (Right)

This package follows conventional DFN/QFN guidelines for PCB land pattern design and surface mount processing. Some additional recommendations are made to accommodate the special clear mold compound, which has a lower glass transition temperature (Tg) and a higher Coefficient of Thermal Expansion (CTE) compared to conventional molding compounds. This technical brief provides guidelines for assembly and handling during the board mounting process.

#### Contents

| 1.     | Board Mounting Guidelines                                                             | 2 |

|--------|---------------------------------------------------------------------------------------|---|

| 2.     | Product Packing                                                                       | 2 |

| 3.     | Package Construction                                                                  | 2 |

| 3.1    | PCB Land Pattern Design                                                               | 3 |

| 3.2    | Solder Stencil                                                                        | 4 |

| 3.3    | Solder Paste                                                                          | 4 |

| 3.4    | Reflow Profile                                                                        | 4 |

| 3.5    | Visual Inspection                                                                     | 4 |

| 3.6    | ODFN Specific Application Guidelines                                                  | 4 |

| 4.     | Revision History                                                                      | 6 |

| List   | of Figures                                                                            |   |

| Figure | e 1. 6 Ld ODFN Top View (Left) and Bottom View (Right)                                | 1 |

| Figure | e 2. 6 Ld ODFN Package Dimensions                                                     | 2 |

| Figure | e 3. 6 Ld ODFN Footprint (Left) and Corresponding Land Pattern for PCB Design (Right) | 3 |

| Figure | e 4. Schematic Showing ODFN Package Mounted on PCB                                    | 3 |

| Figure |                                                                                       |   |

# 1. Board Mounting Guidelines

The package board mounting process is similar to that of conventional DFN/QFN packages. However, there are some key differences in the materials used; therefore, Renesas recommends that you account for these differences in their application method. Specific guidelines in this document are meant to accommodate for the differences in the materials.

# 2. Product Packing

ODFN products have been qualified under JEDEC MSL test criteria, and are shipped in either a tube or tape and reel format. See the product packing label for further details. In addition to the JEDEC MSL condition, there is an additional optical characteristic (OP) that denotes baking at different conditions, see <u>Table 1</u>. The packing quantity varies depending on the application and purchasing options. The moisture protection seal should not be broken until the board mounting process is ready. If the seal is broken, follow standard instructions for baking conditions per <u>Table 1</u>.

Table 1. Dry Bake Temperature for Clear (OP) Mold Compound

| Package Type           | Example Pkg Types                                                          | Bake Temperature | Bake Time Duration |

|------------------------|----------------------------------------------------------------------------|------------------|--------------------|

| Optical Clear Packages | Optical clear mold compound packages for sensor IC's such as ODFN packages | 110°C ±5°C       | 4 hours +1/-0 hrs  |

| Optical Co-Package     | Optical clear compound packages with LED and sensor.                       | 100°C ±5°C       | 24 hours +1/-0 hrs |

Note: Packages molded with optical (OP) clear mold compounds for photosensor and other optical IC devices turn yellow/brown if baked at higher temperatures or for long time durations. This impedes light transmission to the photosensor IC.

# 3. Package Construction

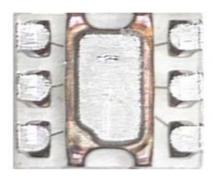

ODFN packages have a nominal package thickness of 0.7mm. <u>Figure 2</u> shows package outline for a 6 Ld ODFN. For specific packages, see <u>plastic packaging</u>. It is important to design PCB land patterns that correspond to the lead dimension as explained in <u>"PCB Land Pattern Design" on page 3</u>.

Figure 2. 6 Ld ODFN Package Dimensions

Similar to DFN and QFN packages, the ODFN has an exposed die paddle/pad as part of the package construction. As shown in <u>Figure 2</u>, the chamfered corner of the exposed thermal pad indicates the Pin 1 location for the product. As with the DFN or QFN, the exposed pad provides robustness to the overall solder joint strength after board mounting.

ODFN packages are assembled on pre-plated copper lead-frames, and individual units are singulated by the sawing process. The occasional presence of a slight oxide layer at the sawn surface of the copper leads is not a concern for solder joint quality. Poor wetting to this exposed side edge does not impact the solder joint quality or reliability.

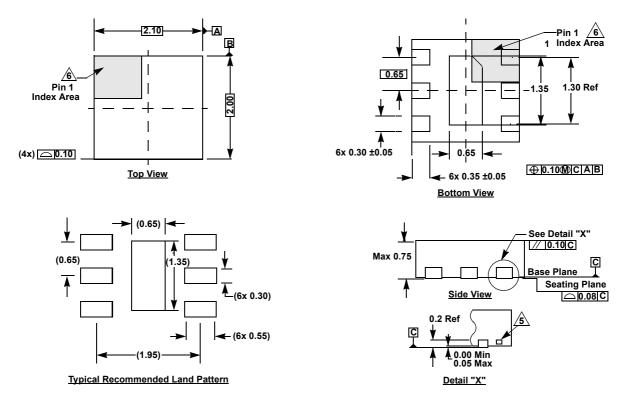

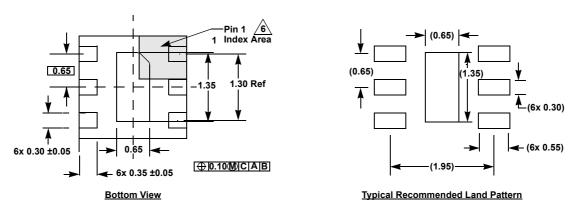

# 3.1 PCB Land Pattern Design

TB389 provides detailed information for PCB design, DFN, QFN packages, and is applicable to ODFN packages. Additionally, package-specific land pattern information is available on package outline drawings, see Renesas support. The package outline drawings are also included in product datasheets. See Figure 3 for an example of land pattern recommendations for the 6 Ld ODFN. The main features are summarized as follows:

- 1:1 match with exposed pad area (for the 6 Ld ODFN, 0.65mmx1.35mm)

- 1:1 match with pin width (for the 6 Ld ODFN, 0.3mm)

- Land length for pin = pin length + 0.2mm (extending out from the package edge)

Figure 3. 6 Ld ODFN Footprint (Left) and Corresponding Land Pattern for PCB Design (Right)

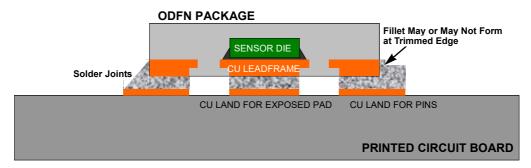

<u>Figure 4</u> shows a reference solder joint shape after ODFN package mounting on the PCB. The solder joint under the exposed pad is intended to provide the package stand-off height and robust assembly.

Renesas recommends that the pad definition on the board is Non Solder Mask Defined (NSMD), though Solder Mask Defined (SMD) pads of the same effective wet able dimension are acceptable. A Nickel/Gold surface finish with 0.2 micron maximum gold thicknesses is recommended for good solder wettability and shelf-life for the SMT process. OSP surface finish is also acceptable, but requires appropriate controls on shelf life and exposure of PCB to environment. HASL or solder plated finishes (pre-plated solder) should not be used for these products.

Figure 4. Schematic Showing ODFN Package Mounted on PCB

#### 3.2 Solder Stencil

- 0.100mm or 0.125mm thick stainless steel stencil is recommended.

- The stencil is laser-cut followed by an electro-polish (chemical finishing not recommended). Alternatively an additive build-up stencil can be used.

- Solder Paste volume is a key contributor to solder joint reliability (higher solder volume leads to greater reliability). However, this must be controlled, as solder bridging can occur when the solder paste is excessive.

- Renesas highly recommends soldering the exposed package pad to the corresponding landing pad on the PCB.

Care should be taken to ensure there is no excessive solder under the exposed area, as this can cause open solder joints due to excess stand-off created by the exposed pad. The optimal value for solder paste in the center pad is 70% to 80% solder paste coverage on the exposed pad area.

## 3.3 Solder Paste

The package itself is Pb-free, and is compatible with both eutectic Tin/Lead or Pb-free Tin/Silver/Copper solders. These packages are qualified at a +235°C maximum temperature reflow profile for eutectic solder, and at a +260°C maximum temperature reflow profile for Pb-free solder. Solder paste with "no-clean" flux and "Type 3" or "Type 4" solder particle size distribution is recommended.

#### 3.4 Reflow Profile

Direct Infrared (IR) heating of these packages must not be done as it can damage the part. Pure convection reflow of these parts is recommended. Typical reflow profiles per JEDEC J-STD-020 criteria are recommended for the eutectic Sn/Pb and PB-free Sn/Ag/Cu solders. Peak temperature for the eutectic Sn/Pb profile is not to exceed +235°C. The Pb-free profile is not to exceed +260°C.

## 3.5 Visual Inspection

Visual inspection of solder joints should be done. Verify that there is no solder bridging between pads, and that the solder joint is "bright-and-shiny" (lead-free appears 'dull' compared to Sn/Pb). The package can not be tilted or off-center with respect to the PCB land pattern. A solder fillet at the edge of the package leads is not a requirement, and in fact may not form at all. Hand solder touch-up is not recommended as excess heat from the air nozzle or soldering iron can damage the transparent mold compound.

## 3.6 ODFN Specific Application Guidelines

The transparency requirement of Ambient Light Sensing products (ALS) does not allow conventional filler loading as a means for controlling mechanical properties of the mold compound (such as Coefficient of Thermal Expansion (CTE), modulus, glass transition temperature (Tg)). As such, the CTE of a clear epoxy is higher than a conventional black epoxy with fillers, has a lower modulus, and a lower Tg. The following sections outline features of the ODFN product for proper application of the product.

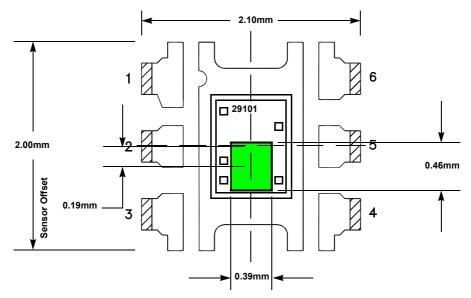

## 3.6.1 Sensor Location and Optics Design

In general, the package body center does not always coincide with the center of the light sensor. The sensor location (green area in top part of IC) is offset from the geometric center of the IC. The location of the sensor itself is specific to the product design in question, and therefore is obtained from the product datasheet. Figure 5 on page 5 shows an example of the sensor location description. In this example, the sensor area is 0.43mmx0.61mm, and it is offset from the center of the IC by 0.25mm. The application set-up should be designed to lead the light to the center of the sensor area and not to the center of the package. On the other hand, the sensor surface height is always located at 0.28 ±0.10mm below the top surface of the package. Solder joint and package height (0.7mm) should also be considered in calculating the sensor surface height from the PCB top surface.

Figure 5. Example of Sensor Location Description

# 3.6.2 Moisture Sensitivity and Bake Conditions

ODFN packages are qualified at JEDEC moisture sensitivity levels for both +235°C and +260°C solder reflow profiles. The properties of clear mold compound are such that moisture saturation occurs rapidly. Therefore, it is important to control the exposure time when the moisture protection seal is broken. Renesas recommends that ODFN components are baked according to the moisture sensitivity level labeling on the reel if the exposure time exceeds the recommended level on the label prior to board mounting.

For recommended baking conditions, see <u>Table 1 on page 2</u>. A bake temperature higher than +110°C can result in discoloration of the clear molding compound.

## 3.6.3 Pick-and-Place with Clear Packages

These optically clear packages are fully compatible with vision-based placement machines. For machines without "auto vision recognition", it may be necessary to manually adjust the machine sensitivity to avoid recognition errors. Renesas does not recommend placing these packages using mechanical centering placement machines or Chip-shooters.

#### 3.6.4 Rework and Associated Risks

ODFN products can be reworked using a reflow profile that closely matches the production reflow profile described earlier. Do not expose ODFN packages to >260°C during rework operation. When rework is involved, do not use the same ODFN unit upon removal from the PCB. Replace with a new ODFN unit.

Maximum reflow that the ODFN unit can see is three times. Excessive heating of the clear mold compound can result in change in color of the mold compound and can also compromise wire bond integrity due to high coefficient of thermal expansion of the mold compound material.

## 3.6.5 Marking and Traceability

ODFN products cannot be marked on the top side of the package due to the need for unobstructed transparency. On the bottom of the package, there is a 4-letter code laser-marking that traces the lot and part details. In addition, the lead frame has a special Pin 1 notch cut-out in the exposed pad next to the Pin 1 lead (top view), which allows verification for correct Pin 1 orientation after mounting on the PCB.

# 4. Revision History

| Rev. | Date      | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.00 | May.31.19 | Updated to new formatting throughout. Updated Figure 1. Changed JEDEC MSL-3 to: JEDEC MSL. Updated Product Packing section and added Table 1. Updated Product Packing section and added Table 1. Updated Package Construction, PCB Land Pattern Design, Moisture Sensitivity and Bake Conditions, Pick-and-Place with Clear Packages, and Rework and Associated Risks sections. Added Revision History section. Updated Disclaimer. |

#### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; willtary equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/