# Understanding Video Timing with Digital Video Encoders

**Technical Brief**

July 1998

TB368

Author: Steven Martin

### Introduction

The timing of the rising edge of active video with respect to the falling edge of the horizontal sync tip is an important parameter in an analog composite video signal. It affects the screen position of the image on the television monitor. If it's too large, then the image is shifted right. If too small, the image goes left.

The use of digital video encoders provides great flexibility in adjusting the timing, and thus the position, of the image. At the same time, it adds some confusion since the standard definitions of digital and analog video do not match. The BT.601 recommendation for digital video defines an active region that's larger than the active region in BT.470 analog video.

This Tech Brief describes the differences between the BT.601 and BT.470 line timing and shows how Intersil digital video encoders (HMP8154, HMP8156A, HMP8170-73, and HMP8190-91) meet the timing requirements. This Tech Brief also describes the timing differences found for the master and slave modes for blanking and sync that the Intersil encoders provide.

## Digital Overscan

Most common definitions of digital video data are based on ITU-R BT.601. The BT.601 recommendation specifies the data sampling rates shown in Table 1. The table shows the active and blanked portions of each line in terms of samples and also microseconds.

| VIDEO    | TOTAL     | ACTIVE    | BLANKED   |  |  |

|----------|-----------|-----------|-----------|--|--|

| STANDARD | SAMPLES   | SAMPLES   | SAMPLES   |  |  |

| NTSC     | 858       | 720       | 138       |  |  |

| 525/60   | (63.56μs) | (53.33μs) | (10.22μs) |  |  |

| PAL      | 864       | 720       | 144       |  |  |

| 625/50   | (64.00μs) | (53.33μs) | (10.67μs) |  |  |

TABLE 1. BT.601 DIGITAL VIDEO LINE TIMING

NOTE: Sampling rate is 13.5MHz for all standards.

The ITU-R BT.470 defines the line timing for analog video signals. The blanking and active regions it recommends are shown in Table 2.

Comparing Tables 1 and 2, we see that the active region of digital video is longer than that of the analog video. The active digital samples overscan the analog active region.

| VIDEO<br>STANDARD | TOTAL LINE<br>TIME    | BLANKED<br>TIME   |                   |  |

|-------------------|-----------------------|-------------------|-------------------|--|

| NTSC<br>525/60    | 63.5μs<br>(15.734kHz) | $52.6\pm0.2\mu s$ | $10.9\pm0.2\mu s$ |  |

| PAL<br>625/50     | 64.0μs<br>(15.625kHz) | $52.0\pm0.3\mu s$ | 12.0 ± 0.3μs      |  |

The overscanned portions of the line in the digital data allow for slight errors in any digital processing without losing any of the sampled active analog video. Typical errors include sampling offsets, filter pre-load, or pipeline delay mismatch.

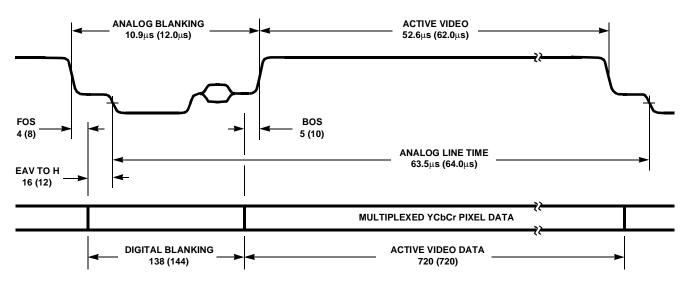

Since the overscanned samples extend into the front and back porch regions of the analog video, they are known as front overscan (FOS) and back overscan (BOS). BT.601 specifies the number of samples from the end of the digital active video (EAV) to the 50% point of the horizontal sync tip. This positions the digital data with respect to the analog line and defines the number of FOS and BOS samples. The values are shown in Table 3.

| VIDEO<br>STANDARD | DIGITAL END<br>TO ANALOG<br>SYNC | FOS<br>SAMPLES | BOS<br>SAMPLES |  |  |

|-------------------|----------------------------------|----------------|----------------|--|--|

| NTSC              | 16                               | 4              | 5              |  |  |

| 525/60            | (1.19µs)                         | (0.30μs)       | (0.37µs)       |  |  |

| PAL               | 12                               | 8              | 10             |  |  |

| 625/50            | (0.89µs)                         | (0.59µs)       | (0.74μs)       |  |  |

NOTE: Sampling rate is 13.5MHz for all standards.

The values shown in the tables above are summarized in Figure 1. The sample counts and times shown in the figure are nominal since some measurements are made from the 50% point of the start or end of the analog video while others are measured from the 4 IRE point.

## H Sync and Blank Timing

The Intersil digital encoders provide a very flexible video control interface. The horizontal and vertical syncs may be input or output, the blanking signal may be input or output, and all may be active low or active high. In addition, the timing of blank with respect to H sync is programmable.

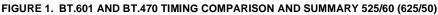

Although the timing of H sync and blank is programmable with respect to each other, the timing relationship between the digital control signals and the output video is fixed when generating standard video waveforms. The four important timing parameters are shown in Figure 2. Note that the figure shows the BT.601 digital blanking and the longer BT.470 analog blanking intervals.

Blank delay is the number of clocks from the edge of blank to the end or start of video. Since the encoder provides edge rate control, the start (end) of video will appear to be slightly after (before) the expected time. The blank delay reflects the data pipeline delay through the part. The pipeline delay is constant throughout the line.

Sync delay is the number of clocks from the active edge of the signal at the HSYNC I/O pin and the 50% point of the falling edge of the analog sync tip.

The end of blank to H sync and H sync to start of blank measurements position the blanking signal around H sync and thus the active video within the line time.

The timing of the video with respect to the control signals depends on their I/O directions. There are four combinations of sync and blank I/O directions: both input, both output, or mixed input and output. The timing of the output video with respect to the control signals is summarized in Table 4.

When the values from Table 4 are combined with Figure 2, the resulting waveforms show the signal timing required to generate standard NTSC video. (This assumes that the overscanned samples in the digital data are input as black pixels.)

FIGURE 2. H SYNC, BLANK, AND VIDEO TIMING

Because of the pipe line delays through the encoder for sync and data, the signals do not line up exactly as shown in Figure 1. However, the difference between the delays is such that the output video timing is correct. For example, the digital blanking interval is given by the sum of the blanking start to H sync and H sync to end times or 276 clocks. The sum is the same as the 138 BT.601 samples. Also, the blanking start to H sync time plus the sync delay less the blank delay is the same as the end of active video to sync time, or 32 clocks (16 samples).

### Summary

This Tech Brief has shown the timing differences between digital video input and analog composite video output per the ITU recommendations BT.601 and BT.470. This Tech Brief

has also shown the H sync and blanking waveforms required by Intersil encoders in order to generate standard video.

| MODE                     |        |        | DELAYS (NOTES 1, 2) |      |                   |      |                             |      |                           |            |

|--------------------------|--------|--------|---------------------|------|-------------------|------|-----------------------------|------|---------------------------|------------|

|                          |        |        | SYNC<br>(NOTE 3)    |      | BLANK<br>(NOTE 4) |      | START TO H SYNC<br>(NOTE 5) |      | H SYNC TO END<br>(NOTE 5) |            |

| NAME                     | SYNC   | BLANK  | т                   | μs   | т                 | μs   | т                           | μs   | т                         | μ <b>s</b> |

| Master                   | Output | Output | 6.2                 | 0.23 | 28                | 1.04 | 55                          | 2.04 | 221                       | 8.19       |

| Mixed Mode A             | Output | Input  | 6.2                 | 0.23 | 26                | 0.96 | 53                          | 1.96 | 223                       | 8.26       |

| Mixed Mode B             | Input  | Output | 15.1                | 0.56 | 28                | 1.04 | 45                          | 1.67 | 231                       | 8.56       |

| HV Slave                 | Input  | Input  | 35.1                | 1.30 | 26                | 0.96 | 23                          | 0.85 | 253                       | 9.37       |

| BT.656 Slave<br>(Note 6) | Output | Output |                     |      |                   |      |                             |      |                           |            |

#### TABLE 4. H SYNC, BLANK, AND VIDEO TIMING DELAY

NOTES:

1. Delay times were measured in microseconds; the number of clocks were calculated. The values are given in pixel clock (CLK2) cycles and in microseconds with an uncertainty of ±0.01μs or about one 27MHz clock cycle.

2. Delay times are given for 8-bit YCbCr mode input. The delays for other input modes are similar but may include extra pixel clock (CLK2) cycles since the inputs are only registered when the input qualifier (CLK) is low.

3. The sync delay time includes fractions of a clock since it is measured with respect to the 50% point of the analog sync tip.

4. The pipe line delays for blank differ by one clock cycle for blank input and output. The second clock cycle shown in the table values occurs since the pixel data must arrive at the part at the same time in all cases. However, when blank is an output, the data follows one clock after the encoder generates blank. When blank is an input, it arrives during the same clock cycle as the data.

5. Delay times for blank w.r.t. H sync are shown for NTSC 525/60 line rates. The net delays for PAL are different but the relative positions of end and start are the same.

6. When BT.656 mode is selected, the video timing is derived from the input. The slaved encoder also outputs the timing signals derived from the input data stream.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

### Sales Office Headquarters

#### NORTH AMERICA

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618 TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 EUROPE Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland TEL: +41 21 6140560 FAX: +41 21 6140579 ASIA Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433

3