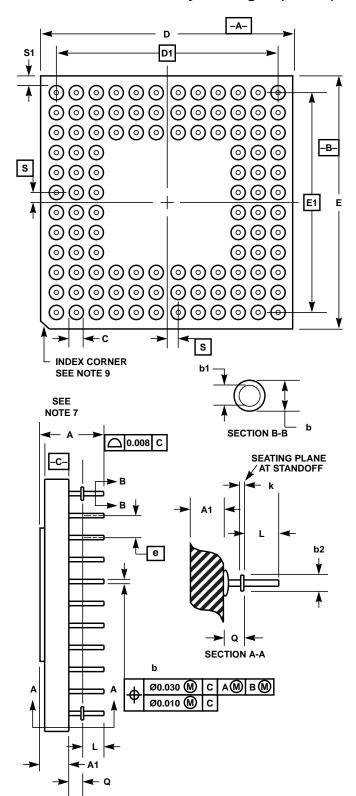

## Ceramic Pin Grid Array Packages (CPGA)

**G68.A** MIL-STD-1835 CMGA3-P68C (P-AC) 68 LEAD CERAMIC PIN GRID ARRAY PACKAGE

|        | INCHES    |        | MILLIMETERS |       |       |

|--------|-----------|--------|-------------|-------|-------|

| SYMBOL | MIN       | MAX    | MIN         | MAX   | NOTES |

| Α      | 0.215     | 0.345  | 5.46        | 8.76  | -     |

| A1     | 0.070     | 0.145  | 1.78        | 3.68  | 3     |

| b      | 0.016     | 0.0215 | 0.41        | 0.55  | 8     |

| b1     | 0.016     | 0.020  | 0.41        | 0.51  | -     |

| b2     | 0.042     | 0.058  | 1.07        | 1.47  | 4     |

| С      | -         | 0.080  | -           | 2.03  | -     |

| D      | 1.140     | 1.180  | 28.96       | 29.97 | -     |

| D1     | 1.000 BSC |        | 25.4 BSC    |       | -     |

| Е      | 1.140     | 1.180  | 28.96       | 29.97 | -     |

| E1     | 1.000 BSC |        | 25.4 BSC    |       | -     |

| е      | 0.100 BSC |        | 2.54 BSC    |       | 6     |

| k      | 0.008 REF |        | 0.20 REF    |       | -     |

| L      | 0.120     | 0.140  | 3.05        | 3.56  | -     |

| Q      | 0.040     | 0.060  | 1.02        | 1.52  | 5     |

| S      | 0.000 BSC |        | 0.00 BSC    |       | 10    |

| S1     | 0.003     | -      | 0.08        | -     | -     |

| М      | 11        |        | 11          |       | 1     |

| N      | -         | 121    | -           | 121   | 2     |

Rev. 1 6/28/95

## NOTES:

- 1. "M" represents the maximum pin matrix size.

- "N" represents the maximum allowable number of pins. Number of pins and location of pins within the matrix is shown on the pinout listing in this data sheet.

- Dimension "A1" includes the package body and Lid for both cavity-up and cavity-down configurations. This package is cavity up.

Dimension "A1" does not include heatsinks or other attached features.

- Standoffs are intrinsic and shall be located on the pin matrix diagonals. The seating plane is defined by the standoffs at dimensions Q.

- 5. Dimension "Q" applies to cavity-up configurations only.

- 6. All pins shall be on the 0.100 inch grid.

- 7. Datum C is the plane of pin to package interface for both cavity up and down configurations.

- 8. Pin diameter includes solder dip or custom finishes. Pin tips shall have a radius or chamfer.

- Corner shape (chamfer, notch, radius, etc.) may vary from that shown on the drawing. The index corner shall be clearly unique.

- 10. Dimension "S" is measured with respect to datums A and B.

- 11. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 12. Controlling dimension: INCH.