# RL78/G22, G23

## 静電容量センサユニット

[QE for Capacitive Touch V3.3.0 以前]

SUCLK動作可能周波数の制限事項

への対応方法

2024年5月28日

ルネサス エレクトロニクス株式会社

# RL78/G22, G23 静電容量センサユニット

## [QE V3.3.0 以前] SUCLK動作可能周波数の制限事項への対応方法

TECHNICAL UPDATE (TU) 発行番号: TN-RL\*-A0136A/J での説明のとおり、SUCLKの動作可能周波数は16 MHz ~ 32 MHzです。

そのため、QE V3.3.0 以前をご使用の場合は、SUCLKの設定に関連する制限事項への対応が必要です。

お客様のご使用方法に応じて以下のページを参照し、ご対応頂きますようお願いします。

### [目次]

- ◆デフォルト設定への対応方法

(SUCLK 32MHzでドライブパルス周波数 0.5MHz, 1MHz, 2MHz, 4MHzを設定している場合) [Page 3](#)

- ◆QEのアドバンスマードへの対応方法(アドバンスマードでドライブパルス周波数を変更している場合) [Page 9](#)

- ◆Appendix [Page 11](#)

# デフォルト設定への対応方法

(SUCLK 32MHzでドライブパルス周波数 0.5MHz, 1MHz, 2MHz, 4MHzを

設定している場合)

# デフォルト設定への対応方法

(SUCLK 32MHzでドライブパルス周波数 0.5MHz, 1MHz, 2MHz, 4MHzを設定している場合)

デフォルト設定をご使用の場合、以下の対応方法①または②を行うようにお願いします。

## 対応方法①

次版タッチツール(QE V3.5.0)を2024/5/31頃にリリース予定です。

お客様製品の開発/アップデート/見直しのタイミングで、

QE V3.5.0以降を使用してQEでの再チューニングおよび再評価を行うようにお願いします。

## 対応方法②

QE V3.3.0以前をデフォルト設定をご使用の場合は、次のページ以降で説明している

「ドライブパルス周波数xxMHzの場合の修正方法(手動)」を参照して、SUCLKの設定を手動修正できます。

お客様製品の開発/アップデート/見直しのタイミングでご対応をお願いします。

# ドライブパルス周波数0.5MHzを設定している場合の修正方法(手動)

## ■修正方法

SUCLKの動作可能周波数は、16 MHz ~ 32 MHzです。そのため、以下のように修正します。

SUCLK = STCLK × 遅倍率設定(遅倍比x)

デフォルト設定では、STCLKは0.5MHz

SUCLK周波数が32MHz(QE V3.3.0以前のデフォルト設定)で

ドライブパルス周波数が0.5MHzを設定している場合

| 一                            | 計測1   | 計測2   | 計測3   |

|------------------------------|-------|-------|-------|

| 遅倍比                          | 64    | 55    | 73    |

| SUCLK周波数[MHz]                | 32.0  | 27.5  | 36.5  |

| CTSUSO1.SDPA[7:0]ビット<br>の設定値 | 31    | 31    | 31    |

| ドライブパルス分周比                   | 64    | 64    | 64    |

| ドライブパルス周波数[MHz]              | 0.500 | 0.430 | 0.570 |

SUCLK周波数を24MHzにして

ドライブパルス周波数を0.5MHzにする設定

| 一                            | 計測1   | 計測2   | 計測3   |

|------------------------------|-------|-------|-------|

| 遅倍比                          | 48    | 41    | 55    |

| SUCLK周波数[MHz]                | 24.0  | 20.5  | 27.5  |

| CTSUSO1.SDPA[7:0]ビット<br>の設定値 | 23    | 23    | 23    |

| ドライブパルス分周比                   | 48    | 48    | 48    |

| ドライブパルス周波数[MHz]              | 0.500 | 0.427 | 0.573 |

計測2および計測3のドライブパルス周波数について、修正前と修正後の値に差分がありますが差分値が微小のため問題ありません。

## ■プログラム修正方法

QEのデフォルト設定でチューニング後のプロジェクトに、以下の修正①および②を行いビルドしてご使用ください。

### 修正①

遅倍比を変更するため、チューニング後に

出力されたqe\_gen/qe\_define.hを以下のように修正してください。

```

#define CTSU_CFG_SUMULTI0 (0x3F) → (0x2F)

#define CTSU_CFG_SUMULTI1 (0x36) → (0x28)

#define CTSU_CFG_SUMULTI2 (0x48) → (0x36)

```

### 修正②

CTSUSO1.SDPA[7:0]ビットの設定値を変更するため、チューニング後に

出力されたqe\_gen/qe\_config.cに記載されているSDPAビットの設定値を以下のように修正してください。

```

const ctsu_element_cfg_t g_qe_ctsu_element_cfg_config01[] = {

{ .so = 0x027, .snum = 0x07, .sdpa = 0x1F }, → .sdpa = 0x17

{ .so = 0x024, .snum = 0x07, .sdpa = 0x1F }, → .sdpa = 0x17

{ .so = 0x029, .snum = 0x07, .sdpa = 0x1F }, → .sdpa = 0x17

};

```

# ドライブパルス周波数1MHzを設定している場合の修正方法(手動)

## ■修正方法

SUCLKの動作可能周波数は、16 MHz ~ 32 MHzです。そのため、以下のように修正します。

SUCLK = STCLK × 遅倍率設定(遅倍比x)

デフォルト設定では、STCLKは0.5MHz

SUCLK周波数が32MHz(QE V3.3.0以前のデフォルト設定)で

ドライブパルス周波数が1MHzを設定している場合

| 一                        | 計測1   | 計測2   | 計測3   |

|--------------------------|-------|-------|-------|

| 遅倍比                      | 64    | 55    | 73    |

| SUCLK周波数[MHz]            | 32.0  | 27.5  | 36.5  |

| CTSUSO1.SDPA[7:0]ビットの設定値 | 15    | 15    | 15    |

| ドライブパルス分周比               | 32    | 32    | 32    |

| ドライブパルス周波数[MHz]          | 1.000 | 0.859 | 1.141 |

SUCLK周波数を24MHzにして

ドライブパルス周波数を1MHzに設定する場合

| 一                        | 計測1   | 計測2   | 計測3   |

|--------------------------|-------|-------|-------|

| 遅倍比                      | 48    | 41    | 55    |

| SUCLK周波数[MHz]            | 24.0  | 20.5  | 27.5  |

| CTSUSO1.SDPA[7:0]ビットの設定値 | 11    | 11    | 11    |

| ドライブパルス分周比               | 24    | 24    | 24    |

| ドライブパルス周波数[MHz]          | 1.000 | 0.854 | 1.146 |

計測2および計測3のドライブパルス周波数について、修正前と修正後の値に差分がありますが差分値が微小のため問題ありません。

## ■プログラム修正方法

QEのデフォルト設定でチューニング後のプロジェクトに、以下の修正①および②を行いビルドしてご使用ください。

### 修正①

遅倍比を変更するため、チューニング後に

出力されたqe\_gen/qe\_define.hを以下のように修正してください。

```

#define CTSU_CFG_SUMULTI0 (0x3F) → (0x2F)

#define CTSU_CFG_SUMULTI1 (0x36) → (0x28)

#define CTSU_CFG_SUMULTI2 (0x48) → (0x36)

```

### 修正②

CTSUSO1.SDPA[7:0]ビットの設定値を変更するため、チューニング後に

出力されたqe\_gen/qe\_config.cに記載されているSDPAビットの設定値を以下のように修正してください。

```

const ctsu_element_cfg_t g_qe_ctsu_element_cfg_config01[] = {

{ .so = 0x027, .snum = 0x07, .sdpa = 0x0F }, → .sdpa = 0x0B

{ .so = 0x024, .snum = 0x07, .sdpa = 0x0F }, → .sdpa = 0x0B

{ .so = 0x029, .snum = 0x07, .sdpa = 0x0F }, → .sdpa = 0x0B

};

```

# ドライブパルス周波数2MHzを設定している場合の修正方法(手動)

## ■修正方法

SUCLKの動作可能周波数は、16 MHz ~ 32 MHzです。そのため、以下のように修正します。

SUCLK = STCLK × 遅倍率設定(遅倍比x)

デフォルト設定では、STCLKは0.5MHz

SUCLK周波数が32MHz(QE V3.3.0以前のデフォルト設定)で

ドライブパルス周波数が2MHzを設定している場合

| 一                        | 計測1   | 計測2   | 計測3   |

|--------------------------|-------|-------|-------|

| 遅倍比                      | 64    | 55    | 73    |

| SUCLK周波数[MHz]            | 32.0  | 27.5  | 36.5  |

| CTSUSO1.SDPA[7:0]ビットの設定値 | 7     | 7     | 7     |

| ドライブパルス分周比               | 16    | 16    | 16    |

| ドライブパルス周波数[MHz]          | 2.000 | 1.719 | 2.281 |

SUCLK周波数を24MHzにして

ドライブパルス周波数を2MHzに設定する場合

| 一                        | 計測1   | 計測2   | 計測3   |

|--------------------------|-------|-------|-------|

| 遅倍比                      | 48    | 41    | 55    |

| SUCLK周波数[MHz]            | 24.0  | 20.5  | 27.5  |

| CTSUSO1.SDPA[7:0]ビットの設定値 | 5     | 5     | 5     |

| ドライブパルス分周比               | 12    | 12    | 12    |

| ドライブパルス周波数[MHz]          | 2.000 | 1.708 | 2.292 |

計測2および計測3のドライブパルス周波数について、修正前と修正後の値に差分がありますが差分値が微小のため問題ありません。

## ■プログラム修正方法

QEのデフォルト設定でチューニング後のプロジェクトに、以下の修正①および②を行いビルドしてご使用ください。

### 修正①

遅倍比を変更するため、チューニング後に

出力されたqe\_gen/qe\_define.hを以下のように修正してください。

```

#define CTSU_CFG_SUMULTI0 (0x3F) → (0x2F)

#define CTSU_CFG_SUMULTI1 (0x36) → (0x28)

#define CTSU_CFG_SUMULTI2 (0x48) → (0x36)

```

### 修正②

CTSUSO1.SDPA[7:0]ビットの設定値を変更するため、チューニング後に

出力されたqe\_gen/qe\_config.cに記載されているSDPAビットの設定値を以下のように修正してください。

```

const ctsu_element_cfg_t g_qe_ctsu_element_cfg_config01[] =

{

{ .so = 0x027, .snum = 0x07, .sdpa = 0x07 }, → .sdpa = 0x05

{ .so = 0x024, .snum = 0x07, .sdpa = 0x07 }, → .sdpa = 0x05

{ .so = 0x029, .snum = 0x07, .sdpa = 0x07 }, → .sdpa = 0x05

};

```

# ドライブパルス周波数4MHzを設定している場合の 修正方法(手動)

## ■修正方法

SUCLKの動作可能周波数は、16 MHz ~ 32 MHzです。そのため、以下のように修正します。

SUCLK = STCLK × 遅倍率設定(遅倍比x)

デフォルト設定では、STCLKは0.5MHz

SUCLK周波数が32MHz(QE V3.3.0以前のデフォルト設定)で

ドライブパルス周波数が4MHzを設定している場合

| 一                            | 計測1   | 計測2   | 計測3   |

|------------------------------|-------|-------|-------|

| 遅倍比                          | 64    | 55    | 73    |

| SUCLK周波数[MHz]                | 32.0  | 27.5  | 36.5  |

| CTSUSO1.SDPA[7:0]ビット<br>の設定値 | 3     | 3     | 3     |

| ドライブパルス分周比                   | 8     | 8     | 8     |

| ドライブパルス周波数[MHz]              | 4.000 | 3.438 | 4.563 |

SUCLK周波数を24MHzにして

ドライブパルス周波数を4MHzに設定する場合

| 一                            | 計測1   | 計測2   | 計測3   |

|------------------------------|-------|-------|-------|

| 遅倍比                          | 48    | 41    | 55    |

| SUCLK周波数[MHz]                | 24.0  | 20.5  | 27.5  |

| CTSUSO1.SDPA[7:0]ビット<br>の設定値 | 2     | 2     | 2     |

| ドライブパルス分周比                   | 6     | 6     | 6     |

| ドライブパルス周波数[MHz]              | 4.000 | 3.417 | 4.583 |

計測2および計測3のドライブパルス周波数について、修正前と修正後の値に差分がありますが差分値が微小のため問題ありません。

## ■プログラム修正方法

QEのデフォルト設定でチューニング後のプロジェクトに、以下の修正①および②を行いビルドしてご使用ください。

### 修正①

遅倍比を変更するため、チューニング後に

出力されたqe\_gen/qe\_define.hを以下のように修正してください。

```

#define CTSU_CFG_SUMULTI0 (0x3F) → (0x2F)

#define CTSU_CFG_SUMULTI1 (0x36) → (0x28)

#define CTSU_CFG_SUMULTI2 (0x48) → (0x36)

```

### 修正②

CTSUSO1.SDPA[7:0]ビットの設定値を変更するため、チューニング後に

出力されたqe\_gen/qe\_config.cに記載されているSDPAビットの設定値を以下のように修正してください。

```

const ctsu_element_cfg_t g_qe_ctsu_element_cfg_config01[] = {

{ .so = 0x027, .snum = 0x07, .sdpa = 0x03 }, → .sdpa = 0x02

{ .so = 0x024, .snum = 0x07, .sdpa = 0x03 }, → .sdpa = 0x02

{ .so = 0x029, .snum = 0x07, .sdpa = 0x03 }, → .sdpa = 0x02

};

```

# QEのアドバンスマードへの対応方法

(アドバンスマードでドライブパルス周波数を変更している場合)

# QEのアドバンスモードへの対応方法

## (アドバンスモードでドライブパルス周波数を変更している場合)

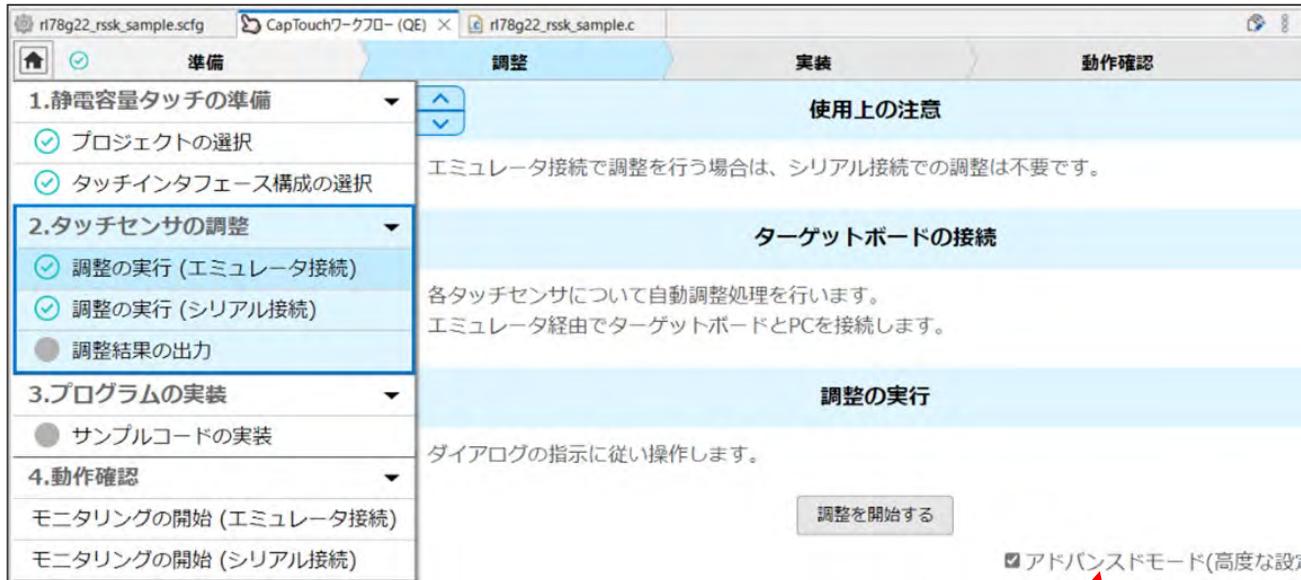

QE V3.3.0以前にてアドバンスモードでドライブパルス周波数を変更している場合、

以下の対応方法を行うようにお願いします。

### 対応方法

次版タッチツール(QE V3.5.0)を2024/5/31頃にリリース予定です。

お客様製品の開発/アップデート/見直しのタイミングで、

QE V3.5.0以降を使用してQEでの再チューニングおよび再評価を行うようにお願いします。

# Appendix

# [Appendix]

## センサドライブパルス周波数について

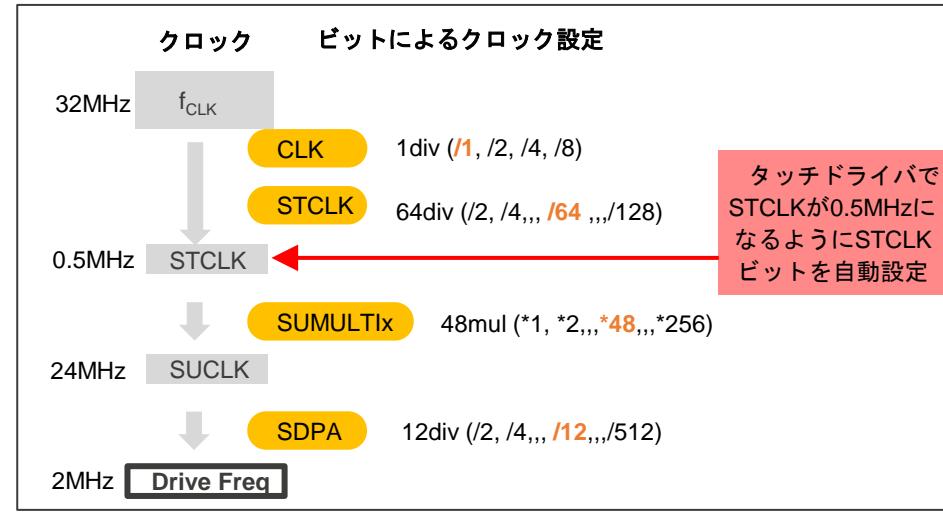

SUCLKやセンサドライブパルス周波数の設定について以下に説明します。

センサドライブパルス周波数は、下記の式によって決まります。

$$\begin{aligned}\text{センサドライブパルス周波数} &= (f_{CLK}\text{周波数} / \text{CLK} / \text{STCLK}) \times \text{SUMULTIx} / \text{SDPA} \\ &= \text{SUCLK} / \text{SDPA}\end{aligned}$$

CLK : CTSUCRAL.CLK[1:0]ビット。 $f_{CLK}$ 周波数を分周した動作クロックを設定

STCLK : CTSUCRAH.STCLK[5:0]ビット。動作クロックを分周したSTCLK（ステートクロック）を設定

SUMULTIx : CTSUSUCLK0-1.SUMULTIx[7:0]ビット。STCLKを遙倍したSUCLKを設定

SDPA : CTSUSO1.SDPA[7:0]ビット。SUCLKを分周したセンサドライブパルス周波数を設定

(CTSUSO1.SDPA[7:0]ビットの設定値をnとすると、

センサドライブパルスはSUCLKの $2(n+1)$ 分周になります。)

# [Appendix] デフォルト設定とは

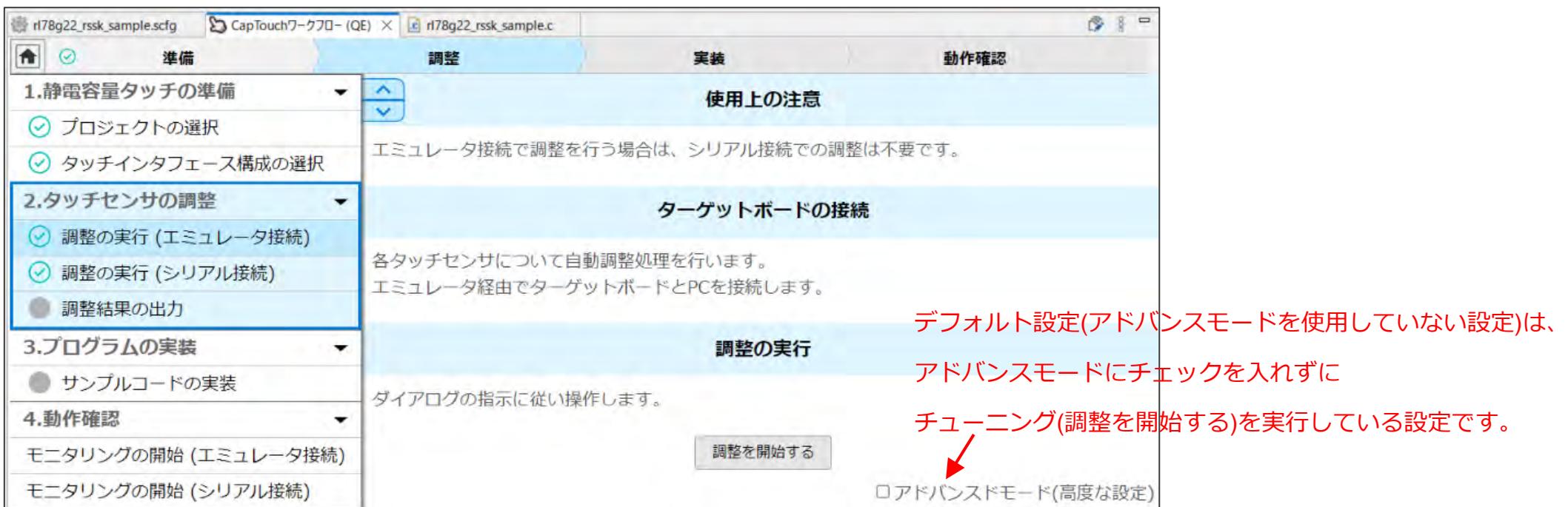

## ■デフォルト設定について

QE V3.3.0以前をデフォルト設定でご使用の場合、チューニングがSUCLK 32MHzで実行されます。

そして、ドライブパルス周波数(計測周波数)が0.5MHz, 1MHz, 2MHz, 4MHzの中から選択します。

本資料で説明しているデフォルト設定とは、以下のQE画面上でアドバンスモードを使用していない設定を意味します。

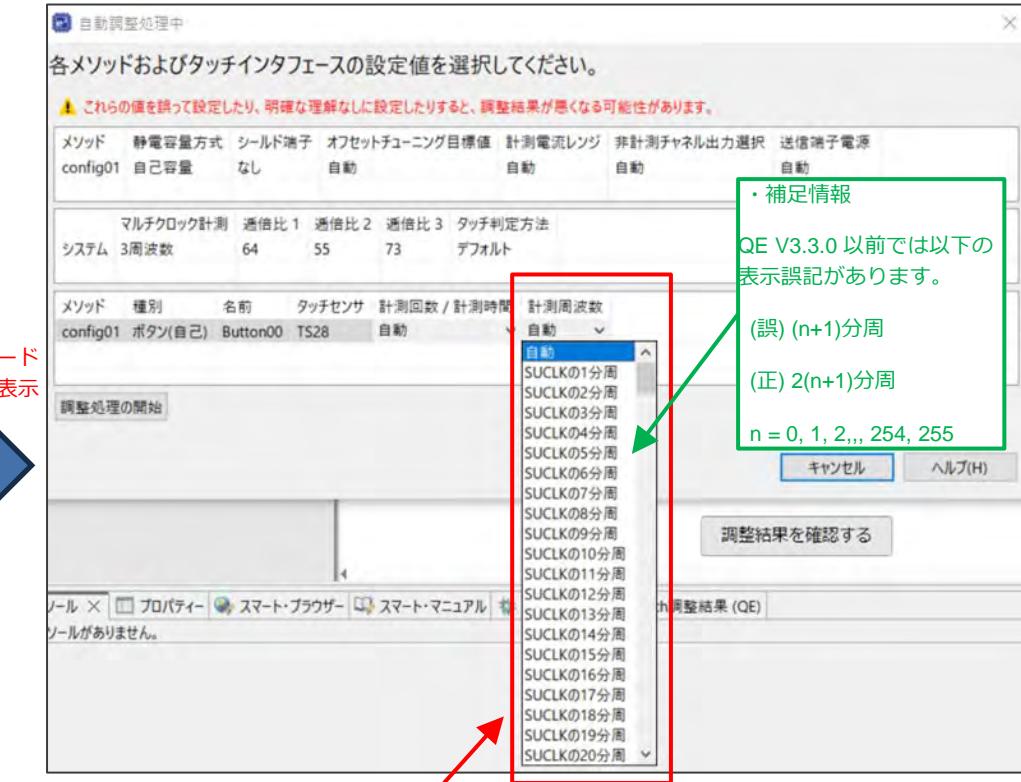

# [Appendix] QEのアドバンスマードとは

## ■アドバンスマードについて

アドバンスマードでドライブパルス周波数を変更している場合とは、

右下のQE画面上でドライブパルス周波数(計測周波数)を変更している場合が該当します。

---

[Renesas.com](https://www.Renesas.com)