# VOICE-RA2L1 Engineering Manual Renesas VUI Reference Solution

Renesas Advanced (RA) Family RA2 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

# Renesas VUI Reference Solution

# **VOICE-RA2L1** Engineering Manual

#### **Contents**

| 1.   | Overview                          | 3   |

|------|-----------------------------------|-----|

| 2.   | Kit Contents                      | 3   |

| 3.   | Kit Ordering Information          | 3   |

| 4.   | Kit Peripheral Features           | 4   |

| 5.   | MCU Feature Support               | 4   |

| 6.   | Kit Architecture                  | 6   |

| 6.1  | System Block Diagram              | 6   |

| 6.2  | Jumper Settings                   | 7   |

| 6.2. | .1 Traditional Pin Header Jumpers | 7   |

| 6.2. | .2 Copper Jumpers                 | 7   |

| 7.   | MCU Port Mapping                  | 8   |

| 8.   | Implementation Details            | 9   |

| 8.1  | Microphones                       | 9   |

| 8.2  | Audio out                         | 10  |

| 8.3  | LEDs                              | 10  |

| 8.4  | Buttons                           | 10  |

| 8.5  | Debug                             | 11  |

| 8.6  | Power                             | 13  |

| 8.7  | USB Type-C                        | 13  |

| 9.   | Certifications                    | 14  |

| Da   | vision History                    | 1.1 |

# **Figures**

| Figure 1. VOICE-RA2L1 Kit Contents                                      | 3  |

|-------------------------------------------------------------------------|----|

| Figure 2. System Block Diagram                                          | 6  |

| Figure 3. Copper Jumpers                                                | 7  |

| Figure 4. PMOD connector                                                | 9  |

| Figure 5. VOICE-RA2L1 Power Block Diagram                               | 13 |

|                                                                         |    |

| Tables                                                                  |    |

| Table 1. Default Jumper Settings                                        | 7  |

| Table 2. Default Copper Jumper Settings                                 | 8  |

| Table 3. MCU Port Assignments                                           | 8  |

| Table 5. PMOD Port Assignments (J15)                                    | 9  |

| Table 6. Analog MEMS Microphone left channel (M2) Port Assignments      | 9  |

| Table 7. Analog MEMS Microphone right channel (M3) Port Assignments     | 10 |

| Table 8. Digital I2S MEMS Microphone left channel (M1) Port Assignments | 10 |

| Table 10. Headphone Jack Pin Assignments                                | 10 |

| Table 11. User LED Port Assignments                                     | 10 |

| Table 12. User Button Port Assignment (S1)                              | 10 |

| Table 13. Jumper Connection Summary for Different Debug                 | 11 |

| Table 14. Debug USB Connector                                           | 11 |

| Table 15. 10-pin JTAG/SWD Connector (J8)                                | 12 |

| Table 16. 20-pin JTAG/SWD Connector (J9)                                | 12 |

| Table 17. Debug Port Signal Assignments                                 | 12 |

| Table 18. USB Type-C Signal Assignments (J1)                            | 13 |

#### 1. Overview

VOICE-RA2L1 is an edge voice recognition evaluation kit designed to be used by Ecosystem Partners, Application Engineers, Field Application Engineers, and for Business Development opportunities. The primary purpose is to evaluate the functionality of projects developed by Ecosystem Partners, and to facilitate the development of additional partner projects. The kit design to use the RA2L1 MCU with LQFP 48pin package as the core logic device, with OPAMP and power devices chosen from the Renesas product portfolio.

#### 2. Kit Contents

The following components are included in the kit:

- 1. VOICE-RĂ2L1 board

- 2. Micro USB device cable (type-A male to micro-B male)

Figure 1. VOICE-RA2L1 Kit Contents

#### 3. Kit Ordering Information

VOICE-RA2L1 kit orderable part number: TW001-VUIA2L1POCZ

#### 4. Kit Peripheral Features

Following is a list of the specific features that have been implemented:

- PMOD: 1 Digilent PMOD connectors, supporting UART, SPI and I2C configurations.

- Microphones: 1 I2S MEMS digital microphones and 2 MEMS analog microphones, distance between each pair of microphones is 50mm which is suitable for beamforming applications.

- Audio out: One stereo audio headphone jack supporting mono output on both channels.

- LEDs: Five LEDs, D2 (Red), D3 (Green) and D4 (Blue) configurable by user, D5 (Blue) as a 3.3V power indicator, D8(Green) as a JLOB (J-LINK on board) indicator.

- Buttons: One RESET button (S2), and one USER button (S1).

- Debug: J-Link On-Board debug interface, supporting JTAG or SWD debug port.

- USB: Micro USB-B (J6) for power input and J-Link On-Board function, USB-C (J1) for power input only.

- Form Factor: 7.5 x 6 cm

#### 5. MCU Feature Support

The RA2L1 MCU supports a full array of peripheral functions. The published features of the MCU are listed below. Features highlighted in **BOLD** text are directly supported by this kit hardware for voice applications.

#### ■ Arm Cortex-M23 Core

- Armv8-M architecture with DSP instruction set

- Maximum operating frequency: 48 MHz

- Support for 4-GB address space

- On-chip debugging system: SWD

- Boundary scan and Arm Memory Protection Unit (Arm MPU) with 8 regions

#### Memory

- Up to 256KB code flash memory

- 8-KB data flash memory (100,000 program/erase cycles minimum)

- 32KB SRAM

- Memory Protection Units (MPU)

- 128-bit unique ID

- Connectivity

- Serial Communications Interface (SCI) x 5

- Serial Peripheral Interface (SPI) x 2

- I2C bus interface (IIC) x 2

- Analog

- 19 channel 12-bit A/D Converter (ADC12) with sample-and-hold circuits

- 12-bit D/A Converter (DAC12) x 1

- Timers

- General PWM Timer 32-bit (GPT32) x 4

- General PWM Timer 16-bit (GPT16) x 6

- Port Output Enable for GPT (POEG)

- Asynchronous General-Purpose Timer (AGT) x 2

- Safety

- ECC in SRAM

- SRAM parity error check

- Flash area protection

- ADC self-diagnosis function

- Clock Frequency Accuracy Measurement Circuit (CAC)

- Cyclic Redundancy Check (CRC) calculator

- Data Operation Circuit (DOC)

- Port Output Enable for GPT (POEG)

- Independent Watchdog Timer (IWDT)

- GPIO readback level detection

- Register write protection

- Main oscillator stop detection

- Security and Encryption

- AES128/256

- True Random Number Generator (TRNG)

- System and Power Management

- Low power modes

- Switching regulator

- Realtime Clock (RTC)

- Event Link Controller (ELC)

- Data Transfer Controller (DTC)

- Key Interrupt Function (KINT)

- Power-on reset

- Low Voltage Detection (LVD) with voltage settings

- Multiple Clock Sources

- Main clock oscillator (MOSC) (1 to 20 MHz)

- Sub-clock oscillator (SOSC) (32.768 kHz)

- High-speed on-chip oscillator (HOCO) (24/32/48/64 MHz)

- Middle-speed on-chip oscillator (MOCO) (8 MHz)

- Low-speed on-chip oscillator (LOCO) (32.768 kHz)

- IWDT-dedicated on-chip oscillator (15 kHz)

- Clock out support

#### **General-Purpose I/O Ports**

• 5V tolerance, open drain, input pull-up, switchable driving ability

#### Operating Voltage

VCC: 1.6 to 5.5 V

#### 6. Kit Architecture

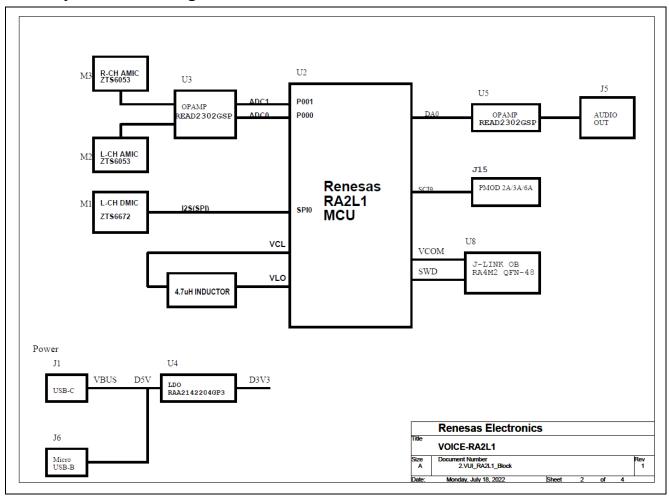

# 6.1 System Block Diagram

Figure 2. System Block Diagram

#### 6.2 Jumper Settings

Two types of jumpers are provided on the VOICE-RA2L1 board.

- 1. Traditional pin header jumpers copper jumpers

- 2. Copper jumpers (trace-cut type and solder bridge type)

#### 6.2.1 Traditional Pin Header Jumpers

These jumpers are traditional small pitch jumpers that require an external shunt to open/close them. The traditional pin jumpers on the VOICE-RA2L1 board are 2.54mm pitch headers and require compatible 2.54mm shunt jumpers.

#### **Default Jumper Configuration**

The following table describes the default settings for each jumper on the VOICE-RA2L1 board. This includes copper jumpers (Ex designation) and traditional pin jumpers (Jx designation.)

Functional details for many of the listed jumpers may be found in sections associated with each functional area of the kits.

**Table 1. Default Jumper Settings**

| Location | Default Open/Closed | Function                                                            |

|----------|---------------------|---------------------------------------------------------------------|

| J2       | Open                | SCI Boot mode : Close to configures the RA2L1 MCU enter SCI boot    |

|          |                     | mode, code can be download through J15 PMOD connector.              |

| J3       | Short               | J3 labeled with "measure current", it is for measure RA2L1 MCU      |

|          |                     | current, remove this jumper wire and serial with a current meter to |

|          |                     | measure RA2L1 MCU current. The RA2L1 current is around 8.33mA.      |

| J7       | Open                | Short with a jumper wire to set the on board debug RA4M2 MCU(U8)    |

|          |                     | in RESET for disable on board debug function.                       |

| J16      | open                | Short with jumper wire to route I2C SDA signal to J15 PMOD          |

|          |                     | connector pin 4.                                                    |

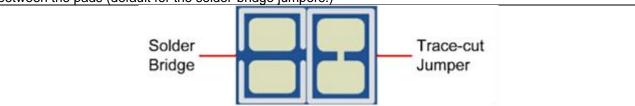

#### 6.2.2 Copper Jumpers

Copper jumpers are of two types, designated trace-cut and solder-bridge.

A trace-cut jumper is provided with a narrow copper trace connecting its pads. The silk screen overlay printing around a trace-cut jumper is a solid box. To isolate the pads, cut the trace between pads adjacent to each pad, then remove the connecting copper foil either mechanically or with the assistance of heat. Once the etched copper trace is removed, the trace-cut jumper is turned into a solder-bridge jumper for any later changes.

A solder-bridge jumper is provided with two isolated pads that may be joined together by one of three methods:

- Solder may be applied to both pads to develop a bulge on each and the bulges joined by touching a soldering iron across the two pads.

- A small wire may be placed across the two pads and soldered in place.

- A SMT resistor, size 0805, 0603, or 0402, may be placed across the two pads and soldered in place. A zero-ohm resistor shorts the pads together.

For any copper jumper, the connection is considered closed if there is an electrical connection between the pads (default for trace-cut jumpers.) The connection is considered open if there is no electrical connection between the pads (default for the solder-bridge jumpers.)

Figure 3. Copper Jumpers

**Table 2. Default Copper Jumper Settings**

| Location | Default Open/Closed | Function                                                         |

|----------|---------------------|------------------------------------------------------------------|

| E1       | Closed              | SCK output to I2S digital microphone                             |

| E3       | Closed              | SCK input to RA2L1 GPT_POEG1                                     |

| E6       | Closed              | ADC0, Analog microphone left channel                             |

| E7       | Closed              | ADC1, Analog microphone right channel                            |

| E8       | Closed              | DAC out to OPAMP, audio out                                      |

| E9       | Closed              | P201/MD signal, cut it then the J8, J9 can be debug out function |

| E10      | Closed              | SCK input for SPI0                                               |

| E11      | Closed              | MOSI for I2S digital microphone left channel                     |

| E12      | Closed              | SSL input for SPI0                                               |

| E13      | Closed              | JLINK VCOM_RXD signal                                            |

| E14      | Closed              | JLINK VCOM_TXD signal                                            |

| E15      | Closed              | JLINK SWCLK signal                                               |

| E16      | Closed              | JLINK SWDIO signal                                               |

# 7. MCU Port Mapping

Here are the port and pin assignments for the kit.

**Table 3. MCU Port Assignments**

| Table 6. Mee 1 of Assignments                                                         |                                                                    |  |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Port                                                                                  | Assigned Function(s)                                               |  |

| P000                                                                                  | Analog microphone, left channel                                    |  |

| P001                                                                                  | Analog microphone, right channel                                   |  |

| P002                                                                                  | Test point 11 (TP11)                                               |  |

| P012                                                                                  | Test point 12 (TP12)                                               |  |

| P013                                                                                  | Test point 13 (TP13)                                               |  |

| P014                                                                                  | Audio out DAC                                                      |  |

| P015                                                                                  | Test point 14 (TP14)                                               |  |

| P100                                                                                  | GPT5 output for SCK to I2S D-MIC left channel                      |  |

| P101                                                                                  | SPI0 MOSIA input form I2S D-MIC left channel                       |  |

| P102                                                                                  | SPI0 RSPCKA input                                                  |  |

| P103                                                                                  | SPI0 SSLA0 input                                                   |  |

| P104                                                                                  | SCK input to RA2L1 GPT_POEG1                                       |  |

| P108                                                                                  | Debug, SWDIO for SWD                                               |  |

| P109                                                                                  | Connect to PMOD(J15), it can be configured as MOSI/TXD/SDA         |  |

| P110                                                                                  | Connect to PMOD(J15), it can be configured as MISO/RXD/SCL         |  |

| P111                                                                                  | Connect to PMOD(J15), it can be configured as SPICLK               |  |

| P112                                                                                  | P112 Delayed SPI SS output signal to P103                          |  |

| P200                                                                                  | · 1 · · ·                                                          |  |

| P201/MD Boot Mode, The RA2L1 enter SCI boot mode if the MD pin is held low on release |                                                                    |  |

| reset signal, it is for download code to RA2L1 flash memory.                          |                                                                    |  |

| P206                                                                                  | PMOD GPIO1                                                         |  |

| P207                                                                                  | PMOD GPIO2                                                         |  |

| P208                                                                                  | PMOD GPIO3                                                         |  |

| P212/EXTAL                                                                            | LED3, user LED, blue color                                         |  |

| P213/XTAL                                                                             | LED2, user LED, green color                                        |  |

| P214/XCOUT                                                                            | No connection, reserve for 32768Hz crystal                         |  |

| P215/XCIN No connection, reserve for 32768Hz crystal                                  |                                                                    |  |

| P300                                                                                  |                                                                    |  |

| P301                                                                                  | Connect to PMOD(J15), it can be configured as SPI SS(Slave Select) |  |

| P302                                                                                  | PMOD, can be GPIO or IRQ5                                          |  |

| P400                                                                                  | User switch(S1), also IRQ0                                         |  |

| P401                                                                                  | GPT6 output for WS to I2S D-MIC left channel                       |  |

| P407                                                                                  | Test point 10 (TP10)                                               |  |

| P408                                                                                  | JLOB VCOM TXD                                                      |  |

| P409                           | JLOB VCOM RXD |

|--------------------------------|---------------|

| P500 LED1, user LED, red color |               |

#### 8. Implementation Details

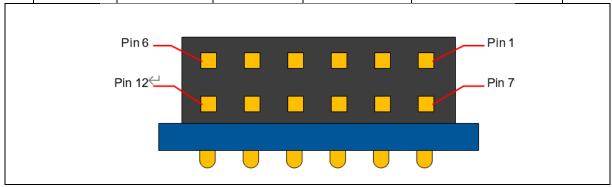

One PMOD type 2A/3A/6A connectors (2x6 pin, dual row, right angle socket) is included. If the RA2L1 SCI9 been configured as Simple I2C, please insert a jumper on header J16 to route SDA signal to PMOD connector pin 4 for meet PMOD 6A pin definition.

**Table 4. PMOD Port Assignments (J15)**

| MCU Port | PMOD Type<br>2A Signal<br>(SPI) | PMOD Type<br>3A Signal<br>(UART) | PMOD Type<br>6A Signal<br>(I2C) | PMOD connector Pin |

|----------|---------------------------------|----------------------------------|---------------------------------|--------------------|

| P301     | SPI_SS                          |                                  |                                 | 1                  |

| P109     | MOSI                            | TXD                              |                                 | 2                  |

| P110     | MISO                            | RXD                              | SCL                             | 3                  |

| P111     | SPI_SLK                         |                                  | SDA(P109)                       | 4                  |

|          | GND                             | GND                              | GND                             | 5                  |

|          | +3.3V                           | +3.3V                            | +3.3V                           | 6                  |

| P302     | INT                             | INT                              | INT                             | 7                  |

| P206     | GPIO                            | GPIO                             | GPIO                            | 8                  |

| P207     | GPIO                            | GPIO                             | GPIO                            | 9                  |

| P208     | GPIO                            | GPIO                             | GPIO                            | 10                 |

|          | GND                             | GND                              | GND                             | 11                 |

|          | +3.3V                           | +3.3V                            | +3.3V                           | 12                 |

Figure 4. PMOD connector

#### 8.1 Microphones

This board includes a pair of analog MEMS microphones (M2 & M3, ZillTek ZTS6053). These 2 analog microphone signals are amplified by Renesas READ2302GSP OPAMP, then fed to RA2L1 ADC channels 0 & 1. One digital I2S MEMS microphone (M1, ZillTek ZTS6672) is also provided, which is connected to RA2L1 SPI0 channels. The physical distance between the 2 analog microphones is 50mm for support beamforming applications.

Table 5. Analog MEMS Microphone left channel (M2) Port Assignments

| MCU Port | MEMS microphone Pin |

|----------|---------------------|

| P000     | 1 – OUT             |

|          | 2 – GND             |

|          | 3 – GND             |

|          | 4 – GND             |

|          | 5 – VDD             |

Table 6. Analog MEMS Microphone right channel (M3) Port Assignments

| MCU Port | MEMS microphone Pin |

|----------|---------------------|

| P001     | 1 – OUT             |

|          | 2 – GND             |

|          | 3 – GND             |

|          | 4 – GND             |

|          | 5 – VDD             |

Table 7. Digital I2S MEMS Microphone left channel (M1) Port Assignments

| MCU Port | SPI0 Signal                      | MEMS microphone Pin   |

|----------|----------------------------------|-----------------------|

| P401     | SSLA0                            | 1 – LRC (Word Select) |

|          | GND – for Select as left channel | 2 – SELECT            |

|          | GND                              | 3 – GND               |

| P102     | RSPCKA                           | 4 – BCLK              |

|          | 3.3V                             | 5 – VDD               |

| P101     | MOSIA                            | 6 – DATA              |

|          |                                  | 7 – CONFIG            |

#### 8.2 Audio out

A stereo headphone jack is connected to the MCU DAC. The DAC signals are connected through an OPAMP for drive earphone, which is Renesas READ2302GSP, in ultra-small 8 pins TSSOP packages.

**Table 8. Headphone Jack Pin Assignments**

| MCU Port   | Audio out Signal | Headphone Jack Pin |

|------------|------------------|--------------------|

| P014 (DA0) | VOUT1            | 1 (Sleeve)         |

|            | VOUT2            | 2 (Mono signal)    |

|            | VOUT2            | 3 (Mono signal)    |

#### 8.3 **LEDs**

3 LED are included on the board and are connected to the MCU I/O. These are Red, Green, and Blue, and can be used for any user defined functions.

Table 9. User LED Port Assignments

| MCU Port | Connected User LED |

|----------|--------------------|

| P500     | Red (D2)           |

| P213     | Green (D3)         |

| P212     | Blue (D4)          |

D5 (blue) is power LED to indicate 3.3V power, and D8 (Green) is debug status LED to indicate the status of the JLOB connection.

#### 8.4 Buttons

There are two mechanical push-button switches on the board. One button is for system/MCU reset (S2). The second button is a user programmable button (S1).

Table 10. User Button Port Assignment (S1)

| MCU Port | User Button Interrupt |

|----------|-----------------------|

| P400     | IRQ0                  |

# 8.5 Debug

The VOICE-RA2L1 board supports following three debug modes.

| Debug Modes    | Debug MCU<br>(one that connects<br>to the IDE on PC) | Target MCU<br>(one that is being<br>debugged) | Debugging<br>Interface/Protocol | Connector Used                                       |

|----------------|------------------------------------------------------|-----------------------------------------------|---------------------------------|------------------------------------------------------|

| Debug on-board | RA4M2 (on-board)                                     | RA2L1 (on-board)                              | SWD                             | Micro USB (J6)                                       |

| Debug in       | External debugging tools                             | RA2L1 (on-board)                              | SWD                             | 20-pin connector (J9)<br>or 10-pin connector<br>(J8) |

| Debug out      | RA4M2 (on-board)                                     | Any external RA<br>MCU                        | SWD, JTAG                       | 20-pin connector (J9)<br>or 10-pin connector<br>(J8) |

#### Notes:

- Please cut E9 for Debug out function

- See Table 14 for the Debug USB connector pin definition.

- See Table 15 for the 10-pin JTAG connector pin definition.

- See Table 16 for the 20-pin JTAG connector pin definition.

**Table 11. Jumper Connection Summary for Different Debug**

| Debug Modes    | J7     |

|----------------|--------|

| Debug on-board | Open   |

| Debug in       | Closed |

| Debug out      | Open   |

The J-Link On-Board (JLOB) debug interface supporting JTAG, SWD debug interface and also supports the VCOM (Virtual COM port) function. The debug MCU is a Renesas RA4M2, programmed with J-Link firmware licensed by Segger. This interface includes one USB micro-B connector (J6) for host debug through the J-Link MCU, one 10-pin and one 20-pin debug header (supporting JTAG and SWD).

**Table 12. Debug USB Connector**

| Debug USB Connector(J6) |                                              | VOICE-RA2L1  |

|-------------------------|----------------------------------------------|--------------|

| Pin                     | Description                                  | Signal / Bus |

| J6-1                    | +5VDC                                        | VBUS2 / TP2  |

| J6-2                    | Data-                                        | D_N          |

| J6-3                    | Data+                                        | D_P          |

| J6-4                    | USB ID, jack internal switch, cable inserted | N.C.         |

| J6-5                    | Ground                                       | GND          |

## Table 13. 10-pin JTAG/SWD Connector (J8)

| Pin   | JTAG Pin Name | SWD Pin Name | RA4M2 Signal/Bus |

|-------|---------------|--------------|------------------|

| J8-1  | Vtref         | Vtref        | +3V3             |

| J8-2  | TMS           | SWDIO        | P108/SWDIO       |

| J8-3  | GND           | GND          | GND              |

| J8-4  | TCK           | SWCLK        | P300/SWCLK       |

| J8-5  | GND           | GND          | GND              |

| J8-6  | TDO           |              | P109             |

| J8-7  | Key           | Key          | N.C.             |

| J8-8  | TDI           |              | P110             |

| J8-9  | GND Detect    | GND Detect   | GND              |

| J8-10 | nSRST         | nSRST        | RESET#           |

# Table 14. 20-pin JTAG/SWD Connector (J9)

| Pin   | JTAG Pin Name | SWD Pin Name | RA4M2 Signal/Bus |

|-------|---------------|--------------|------------------|

| J9-1  | Vtref         | Vtref        | +3V3             |

| J9-2  | TMS           | SWDIO        | P108/SWDIO       |

| J9-3  | GND           | GND          | GND              |

| J9-4  | TCK           | SWCLK        | P300/SWCLK       |

| J9-5  | GND           | GND          | GND              |

| J9-6  | TDO           |              | P109             |

| J9-7  | Key           | Key          | N.C.             |

| J9-8  | TDI           |              | P110             |

| J9-9  | GND Detect    | GND Detect   | GND              |

| J9-10 | nSRST         | nSRST        | RESET#           |

| J9-11 | GND           | GND          | GND              |

| J9-12 | N/A           | N/A          | N.C.             |

| J9-13 | GND           | GND          | GND              |

| J9-14 | N/A           | N/A          | N.C.             |

| J9-15 | GND           | GND          | GND              |

| J9-16 | N/A           | N/A          | N.C.             |

| J9-17 | GND           | GND          | GND              |

| J9-18 | N/A           | N/A          | N.C.             |

| J9-19 | N/A           | N/A          | GND              |

| J9-20 | N/A           | N/A          | N.C.             |

## **Table 15. Debug Port Signal Assignments**

| RA2L1 MCU Port | Debug signal usage |

|----------------|--------------------|

| P108           | SWDIO              |

| P300           | SWCLK              |

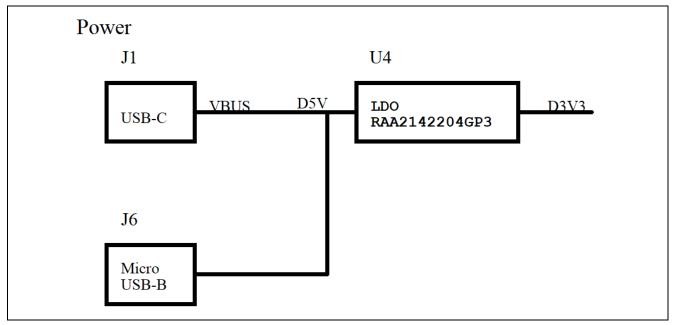

#### 8.6 Power

5V may be supplied from an external USB host to the USB Debug connector (J6) labelled with **J-Link OB** on the board or from USB type-C connector(J1) labelled with **USB-C**.

Figure 5. VOICE-RA2L1 Power Block Diagram

#### 8.7 USB Type-C

The board includes one USB TYPE-C connector (J1) only for supply 5V purpose.

Table 16. USB Type-C Signal Assignments (J1)

| USB FS Signal | USB-C Signal Name | USB-C Connection |

|---------------|-------------------|------------------|

| GND           | GND               | A1               |

| N.C.          | TXp1              | A2               |

| N.C.          | TXn1              | A3               |

| VBUS1         | VBUS              | A4               |

| N.C.          | CC1               | A5               |

| USB1_P        | DP1               | A6               |

| USB1_N        | DN1               | A7               |

| N.C.          | SBU1              | A8               |

| VBUS1         | VBUS              | A9               |

| N.C.          | RXN2              | A10              |

| N.C.          | RXP2              | A11              |

| GND           | GND               | A12              |

| GND           | GND               | B1               |

| N.C.          | TXP2              | B2               |

| N.C.          | TXN2              | B3               |

| VBUS1         | VBUS              | B4               |

| N.C.          | CC2               | B5               |

| USB1_P        | DP2               | B6               |

| USB1_N        | DN2               | B7               |

| N.C.          | SBU2              | B8               |

| VBUS1         | VBUS              | B9               |

| N.C.          | RXN1              | B10              |

| N.C.          | RXP1              | B11              |

| GND           | GND               | B12              |

## 9. Certifications

To support international distribution, the following certification requirements are met, both by design and test.

Americas: FCC Class B Europe: CE Class B

# **Revision History**

|      |                | Description |                 |

|------|----------------|-------------|-----------------|

| Rev. | Date           | Page        | Summary         |

| 1.0  | September 2022 |             | Initial release |

|      |                |             |                 |

Engineering Manual for Project VOICE-RA2L1

Publication Date: September, 18, 2022

Published by: Renesas Electronics Corporation

# Renesas VUI Reference Solution VOICE-RA2L1 Engineering Manual