## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# $\mu$ PD7701x Family

**Digital Signal Processor**

Architecture

μ**PD77015** μ**PD77016** μ**PD77017** μ**PD77018** μ**PD77018A** μ**PD77018**

Document No. U10503EJ4V0UM00 (4th edition) Date Published May 1998 N CP(K)

© NEC Corporation 1993, 1994, 1995, 1998 Printed in Japan [MEMO]

### **()**PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### **③STATUS BEFORE INITIALIZATION OF MOS DEVICES**

### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of IBM Corporation.

InterTools is a trademark of TASKING, Inc.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

License not needed: µPD77016, µPD77019-013

The customer must judge the need for licence: µPD77015, µPD77017, µPD77018, µPD77018A, µPD77019

### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

| NEC Electronics Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782<br>Fax: 408-588-6130<br>800-729-9288 | NEC Electronics (Germany) GmbH<br>Benelux Office<br>Eindhoven, The Netherlands<br>Tel: 040-2445845<br>Fax: 040-2444580 | NEC Electronics Hong Kong Ltd.<br>Hong Kong<br>Tel: 2886-9318<br>Fax: 2886-9022/9044<br>NEC Electronics Hong Kong Ltd.                                            |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NEC Electronics (Germany) GmbH<br>Duesseldorf, Germany<br>Tel: 0211-65 03 02<br>Fax: 0211-65 03 490                              | NEC Electronics (France) S.A.<br>Velizy-Villacoublay, France<br>Tel: 01-30-67 58 00<br>Fax: 01-30-67 58 99             | Seoul Branch<br>Seoul, Korea<br>Tel: 02-528-0303<br>Fax: 02-528-4411                                                                                              |

| <b>NEC Electronics (UK) Ltd.</b><br>Milton Keynes, UK<br>Tel: 01908-691-133<br>Fax: 01908-670-290                                | NEC Electronics (France) S.A.<br>Spain Office<br>Madrid, Spain<br>Tel: 01-504-2787<br>Fax: 01-504-2860                 | NEC Electronics Singapore Pte. Ltd.<br>United Square, Singapore 1130<br>Tel: 65-253-8311<br>Fax: 65-250-3583                                                      |

| <b>NEC Electronics Italiana s.r.1.</b><br>Milano, Italy<br>Tel: 02-66 75 41<br>Fax: 02-66 75 42 99                               | NEC Electronics (Germany) GmbH<br>Scandinavia Office<br>Taeby, Sweden<br>Tel: 08-63 80 820<br>Fax: 08-63 80 388        | NEC Electronics Taiwan Ltd.<br>Taipei, Taiwan<br>Tel: 02-719-2377<br>Fax: 02-719-5951<br>NEC do Brasil S.A.<br>Cumbica-Guarulhos-SP, Brasil<br>Tel: 011-6465-6810 |

Fax: 011-6465-6829

### MAJOR REVISIONS IN THIS EDITION

| Page         | Description                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Throughout   | Addition of descriptions of $\mu$ PD77018A and 77019.                                                                                |

| Throughout   | Deletion of Chapter 5 Assembly Instructions                                                                                          |

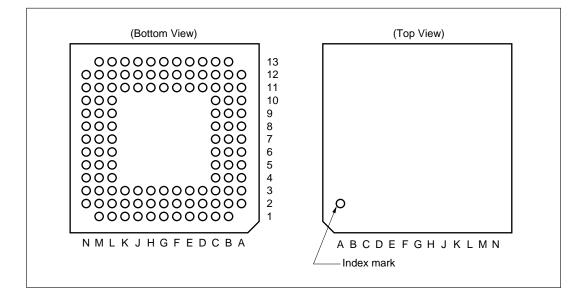

| p.30         | Addition of 2.1.2 (2) 116-pin plastic BGA                                                                                            |

| p.41         | Addition of BGA package numbers to 2.3.2 Pin function of $\mu$ PD77015, 77017, 77018, 77018A, and 77019                              |

| p.62         | Addition of Note 1 to Table 3-7. Initialized Pins and Their Initial Statuses                                                         |

| p.67         | Addition of Table 3-8. Pin Status in HALT Mode                                                                                       |

| p.69         | Addition of Table 3-9. Pin Status in STOP Mode                                                                                       |

| p.96         | Change of Caution in Figure 3-25. External Interrupt Timing                                                                          |

| p.97         | Addition of Caution to Table 3-17. Interrupt Vector Table                                                                            |

| p.116        | Change of status during reset of DA0-DA15 (13) and $\overline{X}/Y$ in <b>Table 3-20. Pin Status</b>                                 |

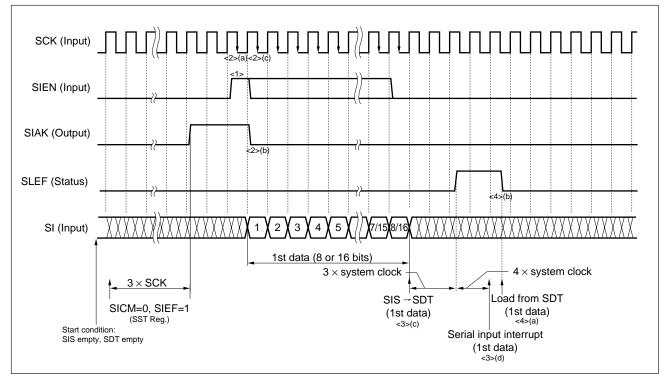

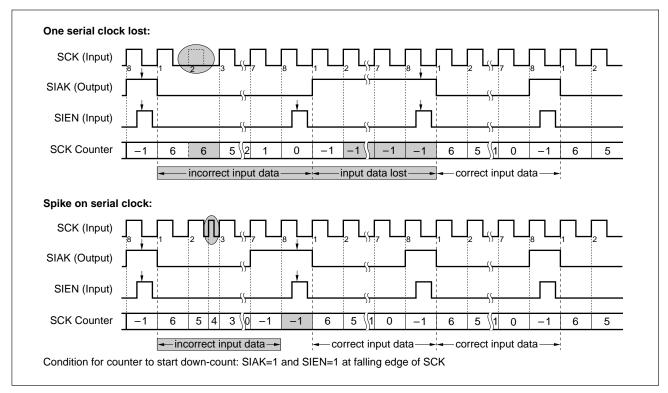

| p.166        | Addition of description to 3.7.3 (3) (C) I/O timing of non-standard serial clock                                                     |

| p.175        | Change of descriptions of HD0-HD7 in Table 3-33. The Pin Status during and after Hardware Reset                                      |

| p.183, 184   | Change of 3.7.4 (5) (c) Interrupts and addition of Caution to this section                                                           |

| p.207        | Addition of 4.3.1 (2) Parameters for self-boot of µPD77019-013                                                                       |

| p.214        | Addition of description of high-speed simulator (SM77016-H) to 5.1.2 Software simulator                                              |

| p.216        | Change of part number of 5.2.2 (3) Adapter for EB-77017 board                                                                        |

| p.230 to 232 | Addition of A.3 CPU Registers to Be Initialized and Initial Values to A.6 Status of Output Pins<br>during Reset to Release STOP mode |

The mark  $\bigstar$  shows major revised points.

### PREFACE

**Readers**: This manual should be read by engineers who wish to understand the functions of the  $\mu$ PD7701x family for designing software or hardware application systems.

**Purpose**: This document describes the hardware and software functions provided in the  $\mu$ PD7701x family products in the order shown below. This manual is designed to be used as a reference manual when developing application system hardware or software using  $\mu$ PD7701x products.

- **Organization**: This manual consists of the following sections:

- Chapter 1 ..... Overview

- Chapter 2 ..... Pin Functions

- Chapter 3 ..... Architecture

- Chapter 4 ...... Boot Function

- Chapter 5 ..... Development Tools

- Appendix A .... Device Summary

- Appendix B .... Ordering Information

- Appendix C .... Index

- How to read: This manual assumes that readers possess basic knowledge on electric/electronic circuits, logic circuits, and microcomputers.

The  $\mu$ PD7701x family consists of the  $\mu$ PD77016, 77015, 77017, 77018, 77018A, and 77019. Unless otherwise specified, " $\mu$ PD7701x" refers to the entire family. If there are some differences in function or operation among family products, they are described under their respective names.

#### • To understand all the µPD7701x functions:

Read this manual from Chapter 1 "Overview" through Chapter 4 "Boot Function" to gain a detailed understanding of the functions of this family.

### • If you are a hardware engineer:

Read this manual from Chapter 1 "Overview" through Chapter 4 "Boot Function". You will learn various useful points for configuring a hardware system as well as gain a detailed understanding of the functions of this family. Chapter 3 "Architecture" describes the related interface levels of the on-chip function blocks.

• If you are a software engineer:

Read this manual from Chapter 1 "Overview" through Chapter 4 "Boot Function". You will learn various useful points for programming a software application as well as gain a detailed understanding of the functions of this family. Chapter 5 "Development Tools" introduces software development tools, additional tools for this family, and evaluation systems. Refer to " $\mu$ PD7701x Family User's Manual Instructions."

### • If you use this document as a reference manual:

Note that an index is provided at the end of this manual. This index can be used to search a word based on a key word. Chapter 3 "Architecture" provides descriptions of internal device architecture on a top-down basis to facilitate searching a specific function.

Appendix A "Device summary" summarizes various key points on the use of this device, such as instruction memory map, data memory map, and peripheral register map.

| Legends: | Data weight          | : Upper digit is left and lower is right.                            |

|----------|----------------------|----------------------------------------------------------------------|

|          | Active low           | : $\overline{XXX}$ (a line is drawn over the name of pin or signal.) |

|          | Memory map address   | : Top-Higher, Bottom-Lower                                           |

|          | Note                 | : Explanation for the Note in the text.                              |

|          | Caution              | : Description that should be read carefully                          |

|          | Remarks              | : Complementary explanation for the text                             |

|          | Bolded text          | : Important items                                                    |

|          | Numerical expression | : Binary 0bXXXX                                                      |

|          |                      | Decimal XXXX                                                         |

|          |                      | Hexadecimal 0xXXXX                                                   |

|          | { }                  | : Either of the items enclosed within $\{ \ \ \}$ can be selected.   |

### Related Documents: Also use the following documents:

### [Documents related to $\mu$ PD7701x family]

• Data sheet

| Part Number     | μPD77016 | μPD77015 | μPD77017 | μPD77018 | μPD77018A | μPD77019 | μPD77019-013 |

|-----------------|----------|----------|----------|----------|-----------|----------|--------------|

| Document Number | U10891E  |          | U10902E  |          | U118      | 349E     | U13053E      |

### • User's manual and brochure

| Document Name    |                | Document Number |

|------------------|----------------|-----------------|

| Brochure         |                | U12395E         |

| User's Manual    | Architecture   | This manual     |

|                  | Instructions   | U13116E         |

| Application Note | Basic software | U11958E         |

### [Documents related to development tools]

| Document Name                         | Document Number |          |

|---------------------------------------|-----------------|----------|

| IE-77016-98/PC User's Manual Hardware |                 | EEU-1541 |

| IE77016-CM-EM6 User's Manual          | EEU-1506        |          |

| EB-77017 User's Manual                |                 | U12660E  |

Some of the above related documents are preliminary versions but are not so specified here.

# Caution The above related documents are subject to change without notice. Be sure to use the latest edition of the document when you design your system.

[MEMO]

### CONTENTS (1/3)

| Chapter | 1 Ov  | erview                                                                         | 19    |

|---------|-------|--------------------------------------------------------------------------------|-------|

| 1.1     | Prod  | ucts of $\mu$ PD7701x Family                                                   | 20    |

| 1.2     | Featu | ires of $\mu$ PD7701x Family                                                   | 21    |

|         | 1.2.1 | Common features                                                                | . 21  |

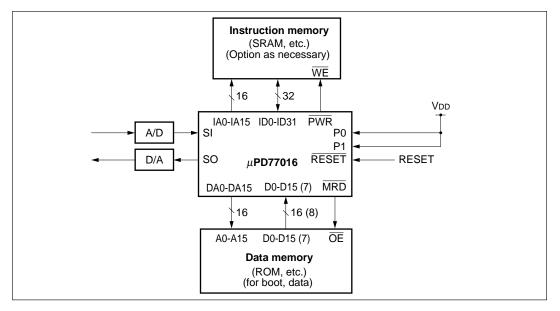

|         | 1.2.2 | Features of $\mu$ PD77016                                                      | . 21  |

|         | 1.2.3 | Features of µPD77015, 77017, 77018, 77018A, and 77019                          | . 21  |

| 1.3     | Main  | Applications of µPD7701x Family                                                | 23    |

|         |       |                                                                                |       |

| •       |       | Functions                                                                      |       |

| 2.1     |       | Configurations                                                                 |       |

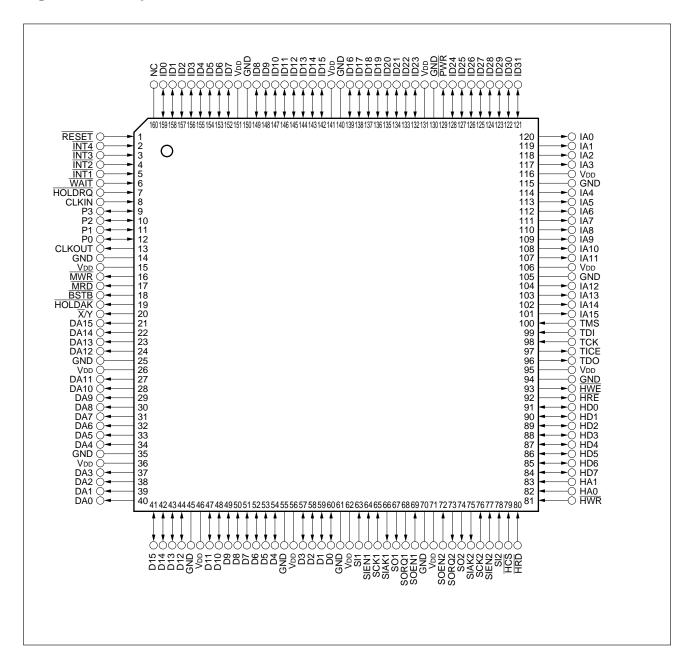

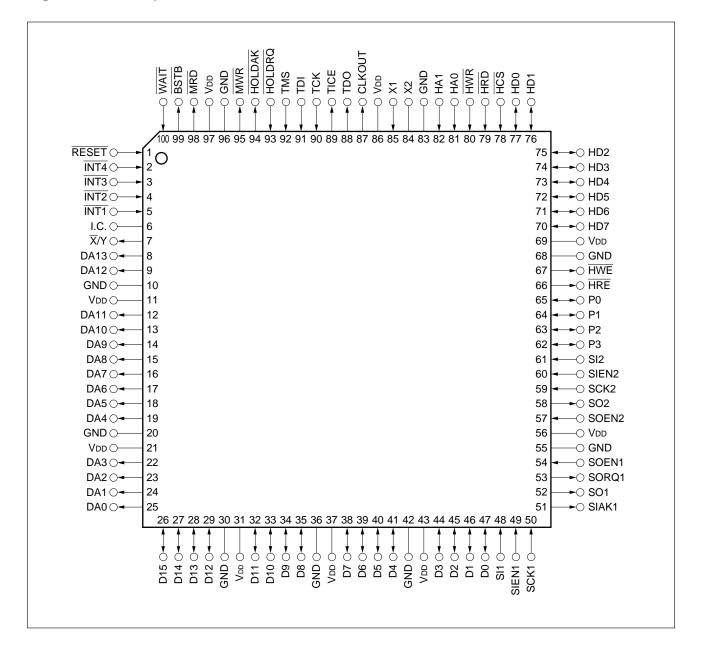

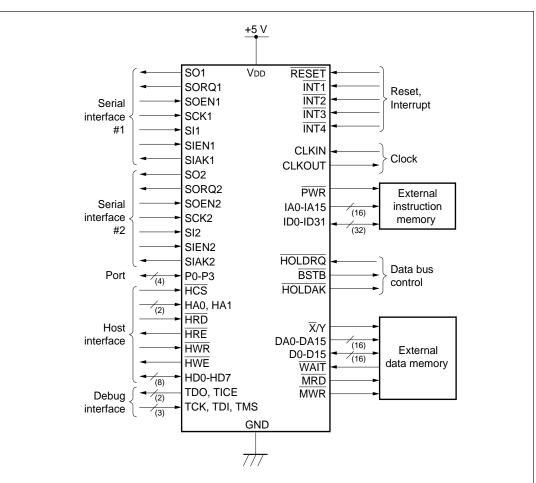

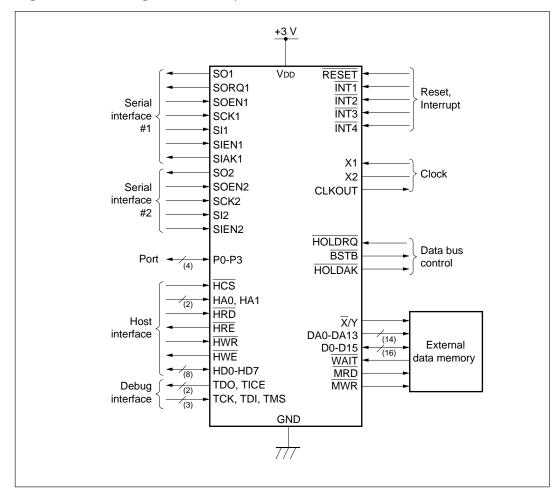

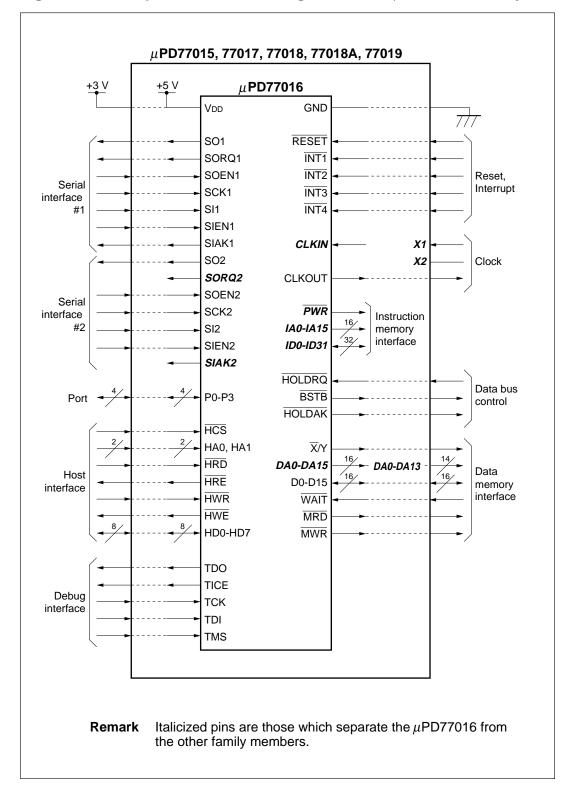

|         | 2.1.1 | Pin configuration of $\mu$ PD77016                                             |       |

|         | 2.1.2 | Pin configuration of $\mu$ PD77015, 77017, 77018, 77018A, and 77019            |       |

| 2.2     | Pin O | Organizations                                                                  |       |

|         | 2.2.1 | Pin organization of $\mu$ PD77016                                              |       |

|         | 2.2.2 | Pin organization of $\mu$ PD77015, 77017, 77018, 77018A, and 77019             | . 33  |

|         | 2.2.3 | Comparison in pin configurations of $\mu$ PD7701x family                       | . 34  |

| 2.3     | Pin F | unctions                                                                       | . 35  |

|         | 2.3.1 | Pin function of $\mu$ PD77016                                                  | . 35  |

|         | 2.3.2 | Pin function of $\mu$ PD77015, 77017, 77018, 77018A, and 77019                 | . 41  |

| 2.4     | Hand  | lling of Unused Pins                                                           | . 47  |

|         |       |                                                                                |       |

| Chapter |       | chitecture                                                                     |       |

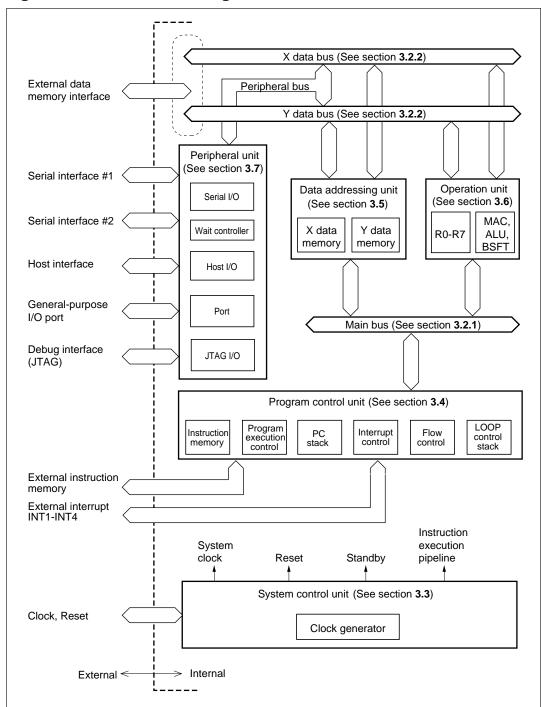

| 3.1     | Overa | all Block Organization                                                         | 49    |

| 3.2     | Buse  | S                                                                              | 51    |

|         | 3.2.1 | Main bus                                                                       | . 51  |

|         | 3.2.2 | Data bus                                                                       | . 53  |

| 3.3     | Syste | em Control Units                                                               | 57    |

|         | 3.3.1 | Clock generator                                                                | . 57  |

|         | 3.3.2 | Reset function                                                                 |       |

|         | 3.3.3 | Pipeline architecture                                                          | . 63  |

|         | 3.3.4 | Standby function                                                               |       |

| 3.4     |       | ram Control Unit                                                               |       |

|         | -     | Block configuration                                                            |       |

|         | 3.4.2 | Program execution control block                                                |       |

|         | 3.4.3 | Flow control block                                                             |       |

|         | 3.4.4 | Interrupt                                                                      |       |

|         | 3.4.5 | Error status register (ESR)                                                    |       |

| 3.5     |       | Addressing Unit                                                                |       |

| 5.5     |       | -                                                                              |       |

|         | 3.5.1 | Block configuration                                                            |       |

|         | 3.5.2 | Data memory space                                                              |       |

| • •     | 3.5.3 | Addressing mode                                                                |       |

| 3.6     | -     | ation Unit                                                                     |       |

|         | 3.6.1 | Block configuration                                                            |       |

|         | 3.6.2 | General-purpose registers and data formats                                     |       |

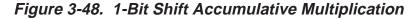

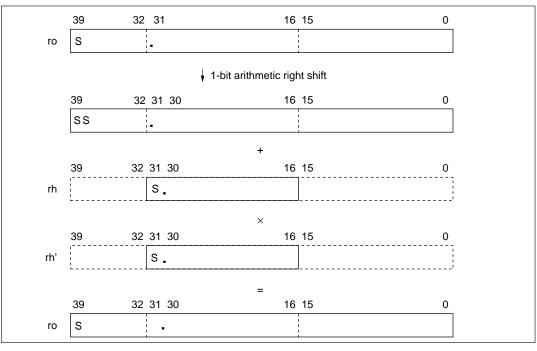

|         | 3.6.3 | Operation functions of multiply accumulator (MAC) and MAC input shifter (MSFT) |       |

|         | 3.6.4 | Operation functions of arithmetic and logic unit (ALU)                         | . 147 |

### CONTENTS (2/3)

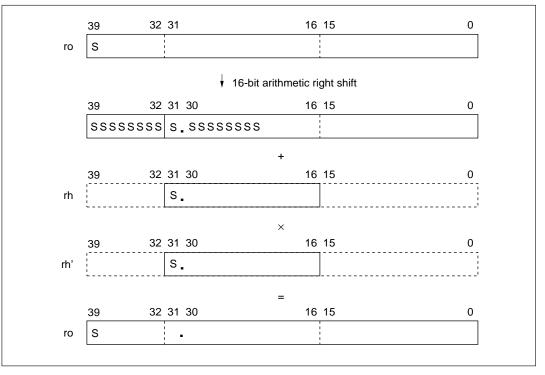

|                                                                | 3.6.5 Operation functions of barrel shifter (BSFT)                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.7                                                            | Peripheral Units                                                                                                                                                                                                                                                                                                                                                                                                                             | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

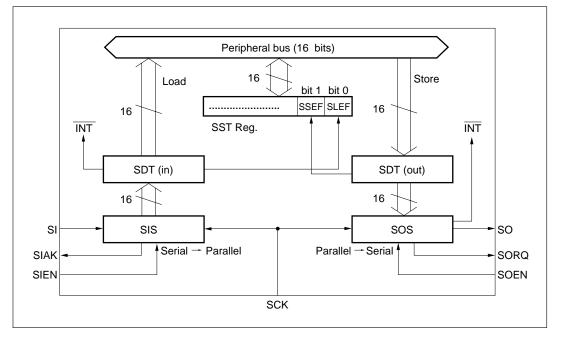

|                                                                | 3.7.1 Block configuration                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 3.7.2 Peripheral registers                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

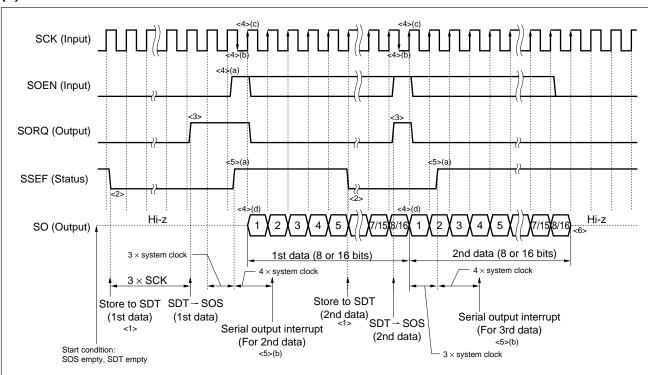

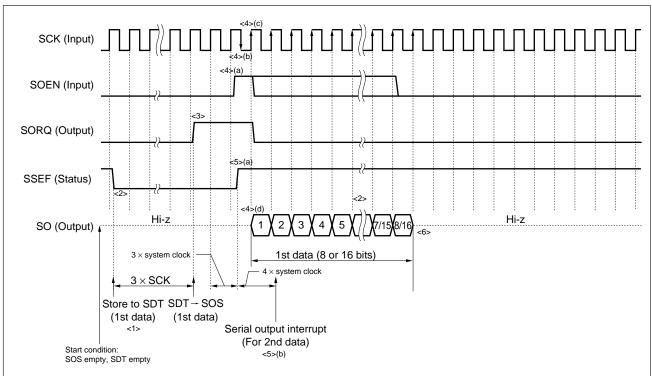

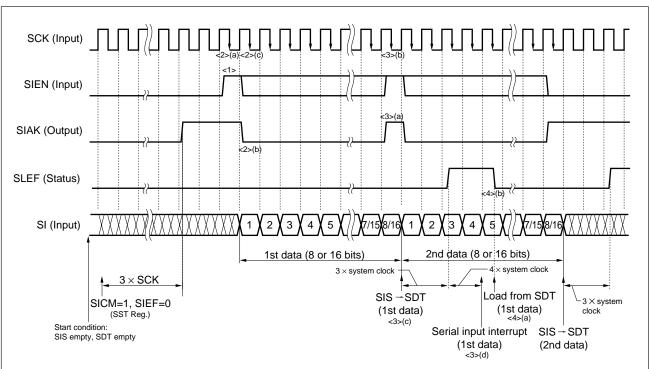

|                                                                | 3.7.3 Serial interface                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

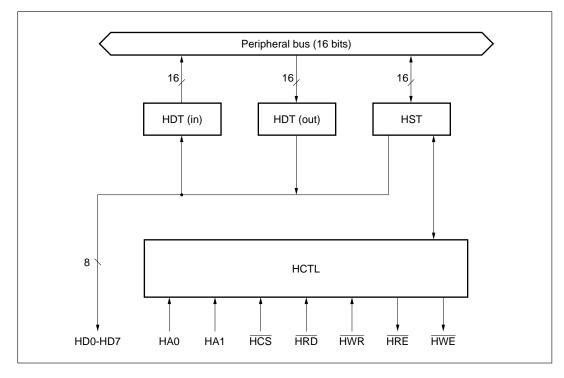

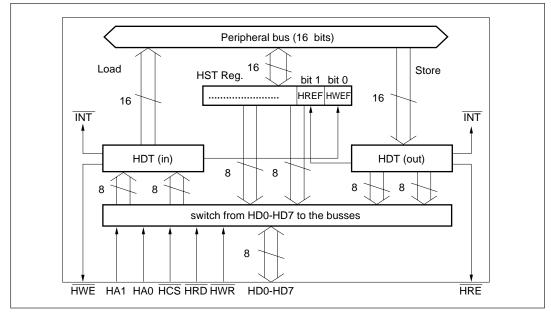

|                                                                | 3.7.4 Host interface                                                                                                                                                                                                                                                                                                                                                                                                                         | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                | 3.7.5 General-purpose input/output port                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 3.7.6 Wait controller                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

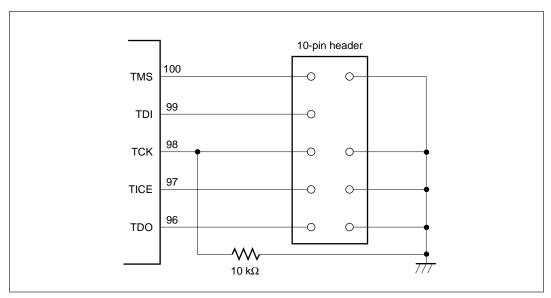

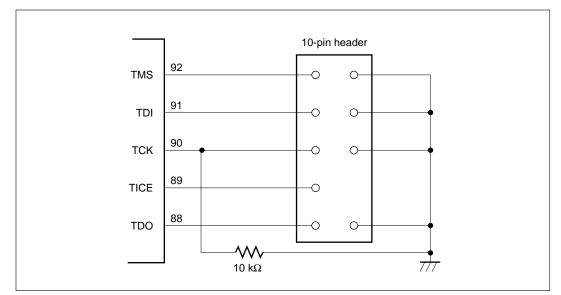

|                                                                | 3.7.7 Debug interface (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Chantor                                                        | r 4 Boot Function                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.1                                                            | General                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.2                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 4.2.1 Classification of boot modes                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -110                                                           | 4.3.1 Self-boot operation                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 4.3.2 Host boot operation                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.4                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 4.4.1 Parameters of X memory word or byte reboot                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 4.4.2 Parameters of Y memory word or byte reboot                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 4.4.3 Parameters for host reboot                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.5                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -                                                              | r 5 Development Tools                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -                                                              | Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                               | 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                                                              | Software Tools         5.1.1       Integrated development environment work bench (WB77016)                                                                                                                                                                                                                                                                                                                                                   | <b>213</b> 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                                                              | Software Tools5.1.1Integrated development environment work bench (WB77016)5.1.2Software simulator (SM77016, SM77016-H)                                                                                                                                                                                                                                                                                                                       | <b>213</b><br>214<br>214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -                                                              | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)                                                                                                                                                                                                                        | <b>213</b><br>214<br>214<br>214<br>214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.1                                                            | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)                                                                                                                                                  | <b>213</b><br>214<br>214<br>214<br>214<br>214<br>214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -                                                              | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                           | 213           214           214           214           214           214           214           214           214           214           214           214           214           214           214           214           214           214           214           214           215                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1                                                            | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools™ 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools         5.2.1       In-circuit emulator                                                                                               | <b>213</b><br>214<br>214<br>214<br>214<br>214<br>214<br>214<br>215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1                                                            | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                           | <b>213</b><br>214<br>214<br>214<br>214<br>214<br>214<br>214<br>215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1                                                            | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools™ 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools         5.2.1       In-circuit emulator                                                                                               | 213         214         214         214         214         214         214         214         214         214         214         214         214         214         214         214         215         215         215                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1<br>5.2<br>Append                                           | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools       5.2.1         5.2.2       Options for in-circuit emulators                                                          | 213<br>214<br>214<br>214<br>214<br>214<br>214<br>214<br>215<br>215<br>215<br>215<br>217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1<br>5.2<br>Append                                           | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools         5.2.1       In-circuit emulator         5.2.2       Options for in-circuit emulators         dix A Device Summary | 213         214         214         214         214         214         214         214         214         214         214         214         215         215         215         215         215         215         215         217         217                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.1<br>5.2<br>Append                                           | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools™ 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                                       | 213         214         214         214         214         214         214         214         214         214         214         214         214         214         214         215         215         215         215         217         217                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.1<br>5.2<br>Append                                           | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools™ 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                                       | 213         214         214         214         214         214         214         214         214         214         214         214         215         215         215         215         217         217         217         217         217         217         217                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1<br>5.2<br>Append<br>A.1                                    | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                           | 213         214         214         214         214         214         214         214         214         214         214         214         215         215         215         215         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         2 |

| 5.1<br>5.2<br>Append<br>A.1<br>A.2                             | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools™ 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                                       | 213         214         214         214         214         214         214         214         214         214         214         215         215         215         215         217         217         217         217         217         217         217         217         217         217         217         217         2130                                                                                                                                                                                                                                                                                                                      |

| 5.1<br>5.2<br>Append<br>A.1<br>A.2<br>A.3                      | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools <sup>™</sup> 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                           | 213         214         214         214         214         214         214         214         214         214         214         214         214         214         215         215         215         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         218         219         210         230         231                                                                                               |

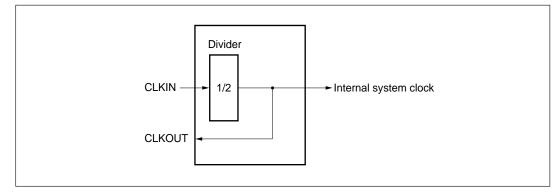

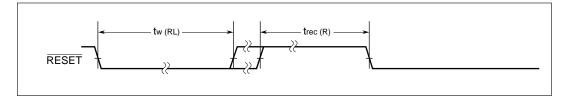

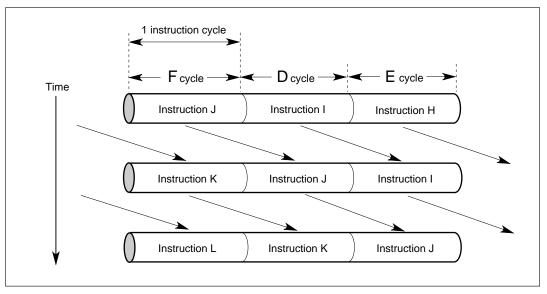

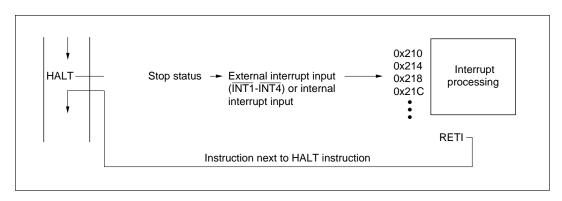

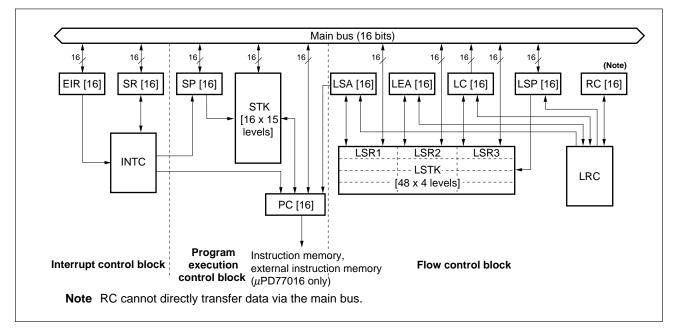

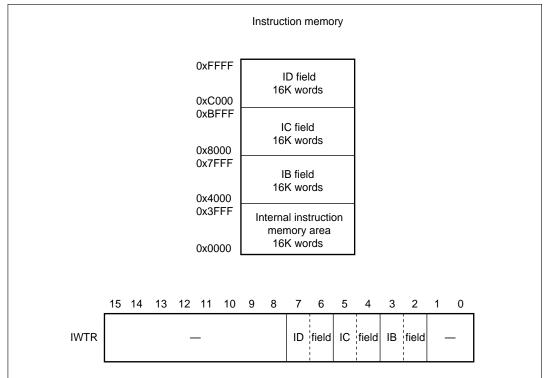

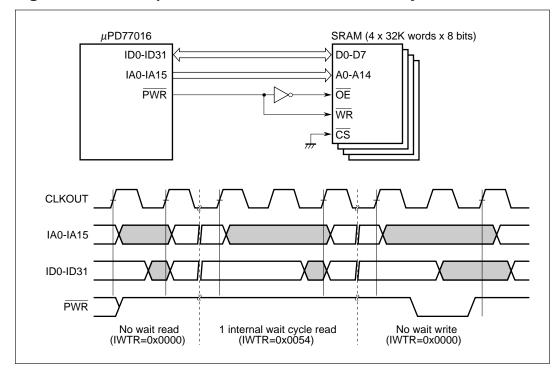

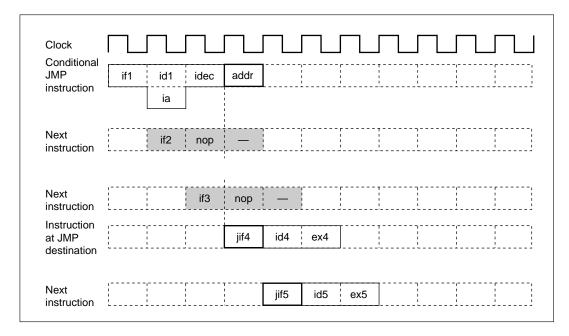

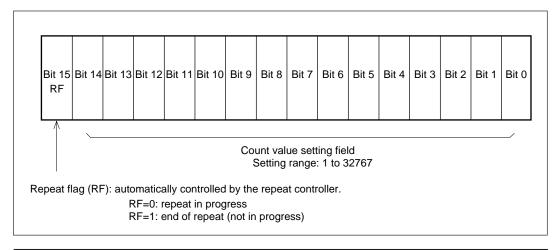

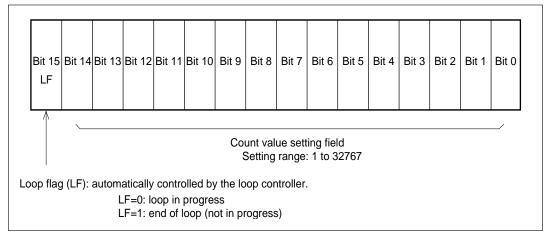

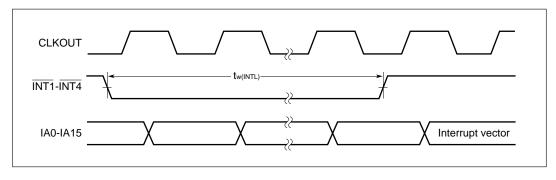

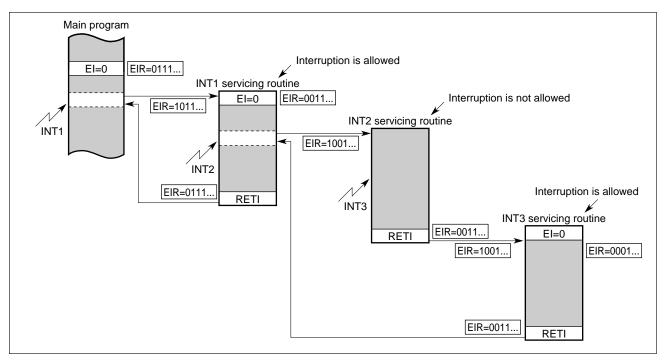

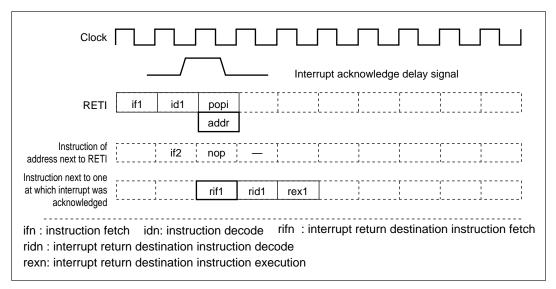

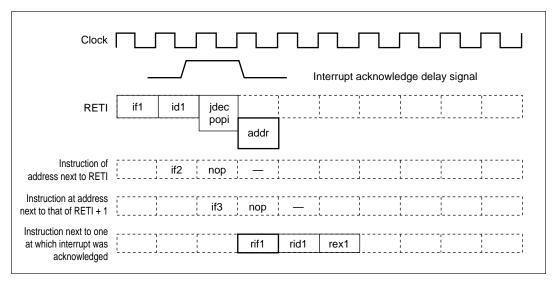

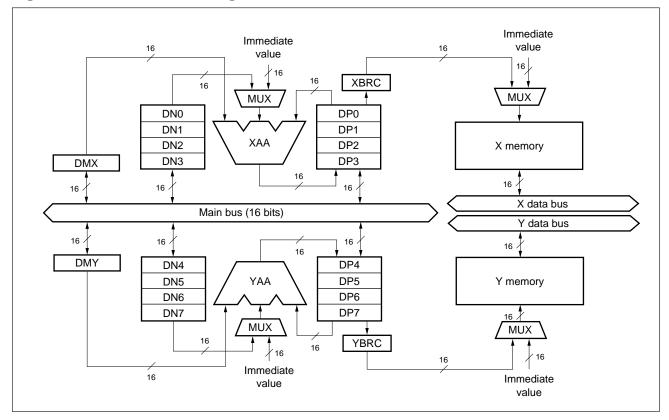

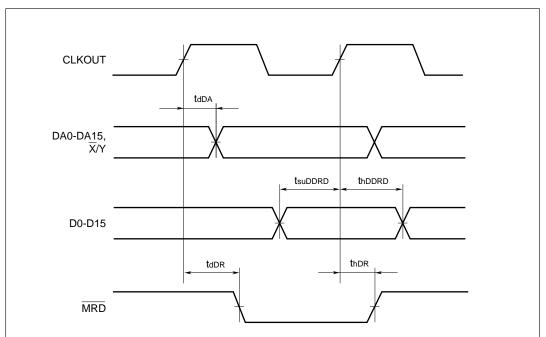

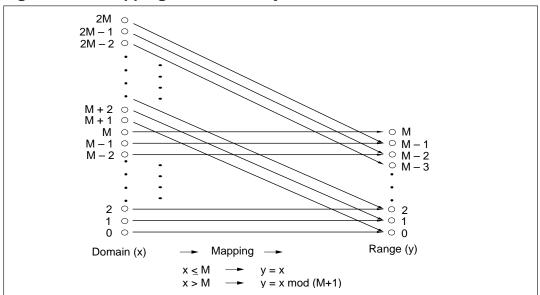

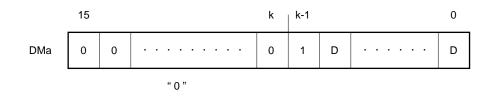

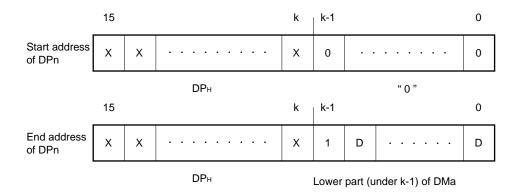

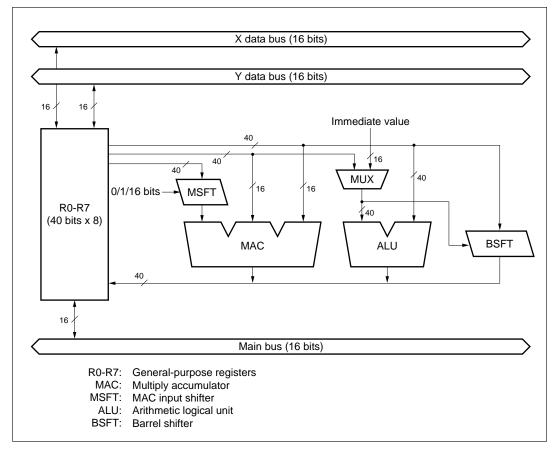

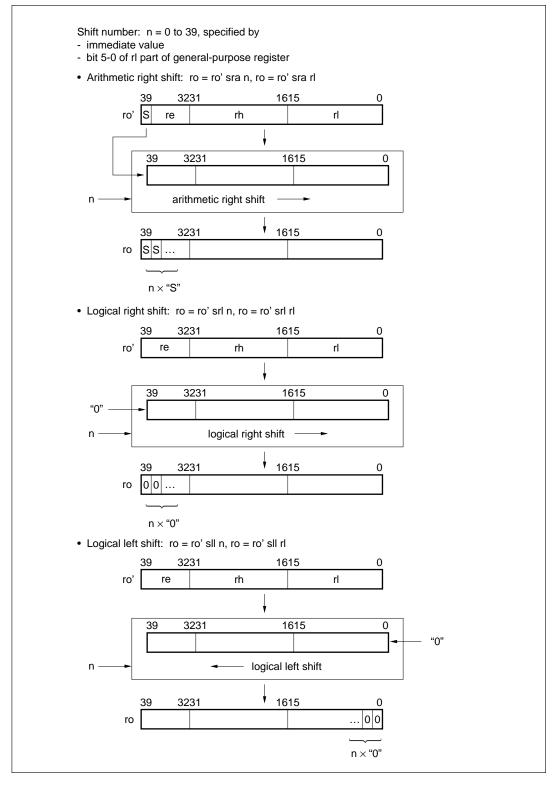

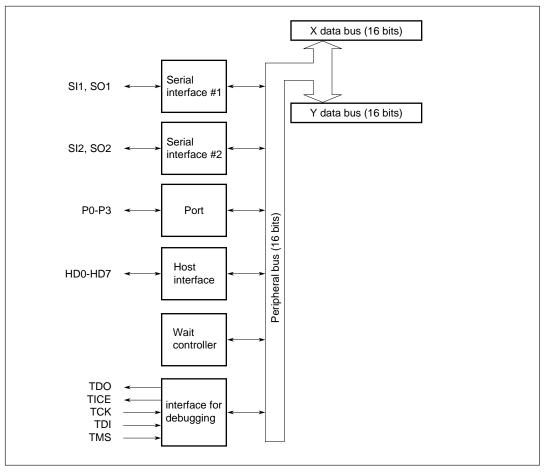

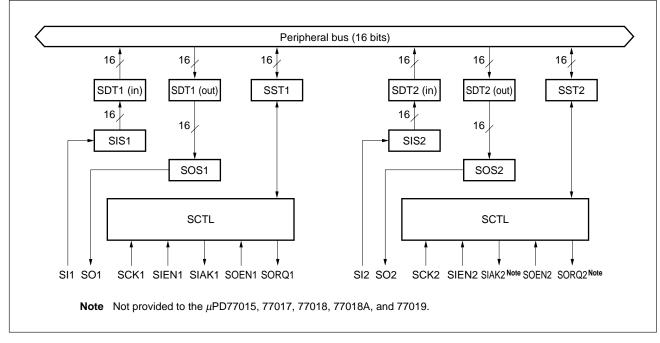

| 5.1<br>5.2<br>Append<br>A.1<br>A.2<br>A.3<br>A.4               | Software Tools         5.1.1       Integrated development environment work bench (WB77016)         5.1.2       Software simulator (SM77016, SM77016-H)         5.1.3       C compiler (InterTools™ 77016)         5.1.4       System software for in-circuit emulator (ID77016)         Hardware Tools                                                                                                                                       | 213         214         214         214         214         214         214         214         214         214         214         214         214         214         215         215         215         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         217         210         230         231                                                           |