# RZ/V2N Evaluation Board Kit (Secure type)

ハードウェアマニュアル

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害(お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許 権、著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うもので はありません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図 しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等 高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等 当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある 機器・システム(大会機能接際 上体に押め込み)使用するよの第) オースけるような飲料書も発生されるような機器・システム(安定機器

機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器 と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの 用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責 任を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。) から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。) によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします。

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的 に支配する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

#### 本社所在地

〒135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア) www.renesas.com

#### 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属し ます。

#### お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/

#### 商標について(つづき)

RZ/V2Nのドキュメントで使用されている商標または登録商標は、以下になります。

Arm® は Arm Limited およびその関連会社の登録商標です。

MIPI® は MIPI Alliance, Inc.の登録商標です。

CSI-2® は MIPI Alliance, Inc.の登録商標です。

DSI® は MIPI Alliance, Inc.の登録商標です。 eMMC™ は MultiMediaCard Association の登録商標です。

PCIe® は PCI-SIG, Inc.の登録商標です。

HDMI® は HDMI Licensing, LLC.の登録商標です。

Pmod™ は Digilent Inc.の登録商標です。

なお、マニュアルの各項目では、®やTMなどの商標表記を省略させていただくことがあります。 すべての商標および登録商標は、それぞれの所有者に帰属します。

# 安全に関する事項

#### 表記の意味

本マニュアルおよび本製品では、本製品を正しくご使用いただくことにより人的危害や物的損害を未然に防止するために、様々なシンボルマークを表記しています。

本章『安全に関する事項』ではそれらのシンボルマークとその意味を説明しています。また、確実に本製品を安全かつ正しくご使用いただくための安全上の注意事項を示しています。

本章の内容を十分にご理解の上本製品をご使用ください。

使用者が死亡または重症を負うことが想定される内容を示します。

人が傷害(注1)を負うことや、物的損害(注2)の発生が想定される内容を示します。

- 注1. 傷害とは、治療に入院や長期の通院を要するものをいいます。

- 注2. 物的損害とは、家屋・家財など周辺への拡大損害を示します。

上記シンボルマークに加え、必要に応じ以下が併記されます。

- [重 要] 本製品を使用する際の設定を誤ると、機器の故障や誤作動を引き起こす可能性がある箇所を示しています。

一般注意

特定しない一般的な注意を示します。

○ その行為を禁止するマークです。

一般禁止 記載されたその行為を禁止します。

指示に基づく行為を強制するマークです。

一般指示

指示に基づく行為を強制するものです。

# <u>♠</u>警告

#### 取り扱いに関して:

電源を接続する前に、必ずジャンパとスイッチの設定を確認してください。ジャンパやスイッチの設定を誤ると、内部の発熱、破裂、発火、または本評価ボード自体や接続されている機器の損傷を引き起こす可能性があります。

本製品の使用中または保管中に、製品自体に異常(異臭、発熱、変色、形状の変化など)が見られた場合は、直ちに電源を抜いてください。

このような異常が発生した場合、破裂、発火、性能劣化の恐れがあります。そのため、このような状態では本製品を使用しないでください。

#### 設置に関して:

湿度の高い場所や水などの液体がかかる場所には設置しないでください。本製品に水などの液体がかかると破損する可能性があります。

#### 周辺温度に関して:

本製品の使用周囲温度範囲は0℃~60℃です。

# 注意

#### 取り扱いに関して:

本製品の取扱いには十分注意してください。落下させるなど強い衝撃を与えないでください。

本製品のコンポーネントピンに素手で触れないでください。静電気が放電し、内部回路を破損する恐れがあります。本製品に触れる前に静電気を除去してください。

本製品とのケーブルの抜き差しの際は、ケーブルの把持部(プラグなど)を持ち、ケーブルに負荷をかけないようにしてください。通信インターフェイスケーブルを接続したまま、本製品などを引っ張らないでください。断線の原因となります。

ケーブルをコネクタに接続する際、プラグを逆向きや上下逆に差し込まないでください。本製品や接 続機器を破損する恐れがあります。

電源を接続する前に、必ずジャンパやスイッチの設定を確認してください。ジャンパやスイッチの設定を誤ると、本製品や接続機器が破損する恐れがあります。

濡れた手で本製品を扱わないでください。故障の原因となります。

#### 輸送方法に関して:

本製品を輸送する際は、製品の梱包箱と緩衝材を使用し、精密機器扱いで輸送してください。 梱包が不十分な場合、輸送中に破損する恐れがあります。

やむを得ず他の方法で輸送する場合は、精密機器として丁寧に梱包してください。

本製品を梱包する際には、必ず本製品に同梱されている静電気防止袋をご使用ください。

他の袋を使用した場合、静電気により製品が損傷する可能性があります。

#### 異常動作に関して:

外部ノイズなどの影響により本製品の動作に異常が発生した場合は、以下の手順に従ってください。

- 1. 電源を切る。

- 2.10秒以上待ってから電源を再投入する。

#### 廃棄に関して:

本製品を廃棄する場合は、必ず産業廃棄物として法令に従って処理してください。

# 目 次

| 1. |      | 概要                     | 9  |

|----|------|------------------------|----|

|    | 1.1  | 特徵                     | 10 |

|    | 1.2  | ブロック構成                 | 11 |

|    | 1.3  | 仕様                     | 13 |

|    |      | 1.3.1 V2NEVK 仕様        | 13 |

|    |      | 1.3.2 V2NEVK 電源仕様      | 14 |

|    |      | 1.3.3  V2NEVK 付属品      | 14 |

|    |      | 1.3.4 外観               |    |

|    |      | 1.3.5  端子機能一覧          |    |

|    | 1.4  |                        |    |

|    |      | 1.4.1 V2NEVK 電源 ON/OFF |    |

|    |      | 1.4.2 イーサネット使用上の注意     | 19 |

| 2. |      | 操作手順                   | 20 |

|    | 2.1  | 組立                     | 20 |

|    | 2.2  | モード設定                  | 22 |

|    | 2.3  | 電源                     | 23 |

| 3. |      | 配置                     | 24 |

|    | 3.1  |                        |    |

|    | 3.2  | 主要部品リスト                | 27 |

| 4. |      | インターフェース仕様             | 28 |

|    | 4.1  | リセット                   |    |

|    | 4.2  | LED                    |    |

|    | 4.3  | スイッチ                   | 28 |

|    | 4.4  | デバッグシリアルインターフェース       |    |

|    | 4.5  | デバッガインターフェース           |    |

|    | 4.6  | MIPI CSI-2 インターフェース    | 30 |

|    | 4.7  | MIPI DSI インターフェース      | 31 |

|    | 4.8  | USB インターフェース           | 31 |

|    | 4.9  | イーサネットインターフェース         | 31 |

|    | 4.10 |                        |    |

|    | 4.11 | 1 SD カードコネクタ           | 32 |

|    | 4.12 |                        |    |

|    | 4.13 |                        |    |

|    | 4.14 |                        |    |

|    | 4.15 |                        |    |

|    | _    |                        |    |

| 4.16 HDMI インターフェース | 35 |

|--------------------|----|

| 4.17 オーディオインターフェース | 35 |

| 4.18 Pmod コネクタ     | 36 |

| 5. 補足事項            | 38 |

| 5.1 V2NEVK の電源 IC  | 38 |

| 5.2 ヒートシンクの組付け     | 38 |

| 付録 A CPU ボード部品配置図  | 39 |

| 改訂記録               | 41 |

# RZ/V2N Evaluation Board Kit (Secure type)

R12UZ0157JJ0110 Rev.1.10 2025.02.28

# 1. 概要

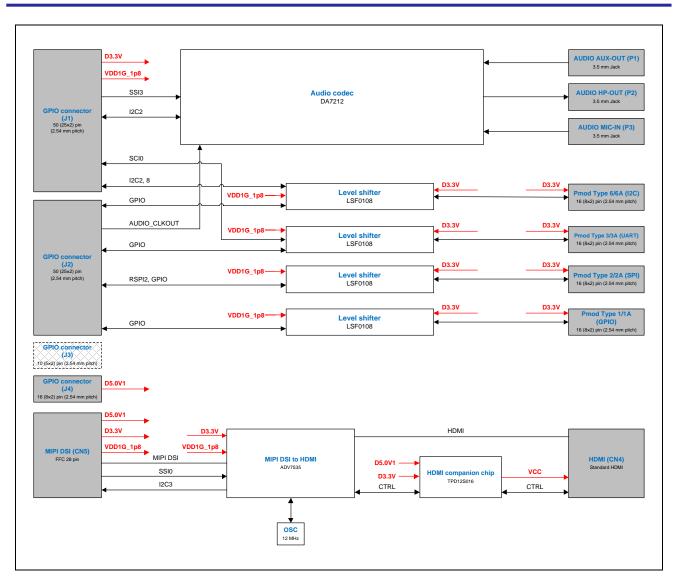

本ボードは、ルネサスエレクトロニクス製 Arm® CPU 搭載ハイエンド MPU RZ/V2N の評価キット(RZ/V2N Evaluation Board Kit (Secure type)、以下 V2NEVK)です。本マニュアルでは、V2NEVK のハードウェア機能について説明します。

V2NEVK は、RZ/V2N Evaluation Board (CPU ボード) および RZ/V2H EVK Expansion Board (EXP ボード)で構成されています。

| ボード名                                    | 概要                                                                                                                 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| RZ/V2N Evaluation Board<br>(CPU ボード)    | <ul><li>■ RZ/V2N 搭載</li><li>■ RZ/V2N の主要な機能部品が搭載</li></ul>                                                         |

| RZ/V2H EVK Expansion Board<br>(EXP ボード) | <ul><li>● RZ/V2N Evaluation Board の J1、J2、J4 に接続されています。</li><li>● HDMI、オーディオ、Pmod インターフェース搭載</li></ul>             |

| eMMC Sub Board<br>(eMMC サブボード)          | <ul> <li>RZ/V2N Evaluation Board の CN15 に接続します。</li> <li>microSD スロット搭載の microSD Sub Board とは排他使用となります。</li> </ul> |

| microSD Sub Board<br>(microSD サブボード)    | ● RZ/V2N Evaluation Board の CN15 に接続します。<br>● eMMC 搭載の eMMC Sub Board とは排他使用となります。                                 |

V2NEVK に関しては、以下の文書があります。必ず最新版を参照してください。ソフトウェアを含む開発環境については、ルネサスエレクトロニクス営業担当まで、お問い合わせください。

| 文書タイプ                 | 文書タイトル                                                          | 文書 No.          | 内容                                                                     |

|-----------------------|-----------------------------------------------------------------|-----------------|------------------------------------------------------------------------|

| ハードウェアマニュアル           | RZ/V2N Evaluation Board<br>Kit (Secure type)<br>Hardware Manual | 本マニュアル          | V2NEVK のハードウェア仕様                                                       |

| ユーザーズマニュアル:<br>ハードウェア | RZ/V2N Group<br>User's Manual:<br>Hardware                      | R01UH1071EJ**** | RZ/V2N のハードウェア仕様<br>(ピンアサイン、メモリマップ、周辺仕<br>様、電気特性、タイミングチャート)お<br>よび機能説明 |

#### 1.1 特徴

V2NEVK には以下の特徴があります。

- LPDDR4X: 64Gb×1

- NOR Flash: 512Mb

- MIPI® CSI-2®コネクタ: 2ch

- ギガビットイーサネットインターフェースコネクタ:2ch

- USB3.2 Gen 2 Type-A: 1ch

- USB2.0 micro-AB: 1ch

- Micro SD カードコネクタ:1ch

- eMMC : 64GB

- PCIe®スロット (×2 レーン) :1ch

- デバッグシリアルインターフェイス USB micro-B:1ch

- デバッガインターフェースコネクタ:1ch

- HDMI® Type-A コネクタ:1ch

- Pmod<sup>TM</sup>インターフェースコネクタ:4ch

- Audio MIC コネクタ: 1ch

- Audio HP コネクタ: 1ch

- Audio AUX コネクタ: 1ch

- USB-PD Type-C(電源):1ch

# 1.2 ブロック構成

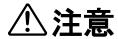

図 1.2-1 RZ/V2N Evaluation Board ブロック図

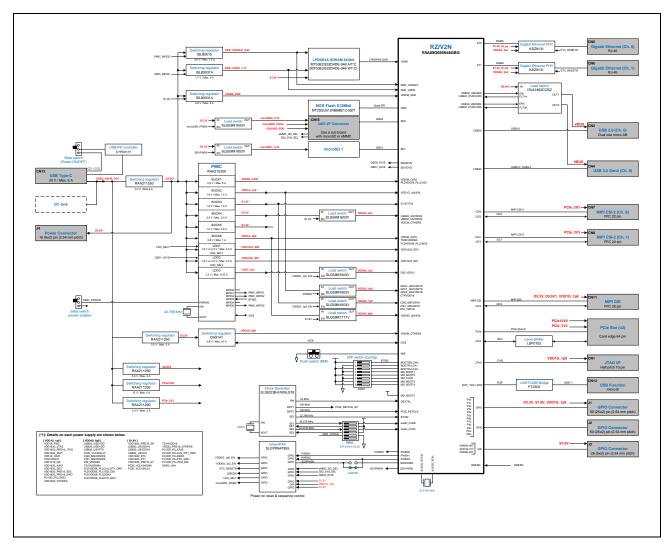

図 1.2-2 RZ/V2H EVK Expansion Board ブロック図

# 1.3 仕様

# 1.3.1 V2NEVK 仕様

#### 表 1.3-1 V2NEVK 仕様

| 項目             | 仕様                                                                                                                                                                                |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MPU            | R9A09G056N48GBG (RZ/V2N [GE3D, Security, ISP])                                                                                                                                    |  |  |

| ボードサイズ         | CPU ボード : 153×100×1.7mm<br>EXP ボード : 153×100×1.7mm<br>eMMC サブボード : 24×18×1.6mm<br>microSD サブボード : 24×18×1.6mm                                                                     |  |  |

| LPDDR4X        | Micron MT53E2G32D4DE-046 AIT:C (MT53E2G32D4DE-046 WT:C) 64 Gb Dual-Rank                                                                                                           |  |  |

| NOR フラッシュ      | Micron MT25QU512ABB8E12                                                                                                                                                           |  |  |

| eMMC           | Micron MTFC64GBCAQTC-IT (MTFC64GAZAQHD)                                                                                                                                           |  |  |

| HDMI I/F       | コネクタ:Type-A (standard)<br>MIPI® DSI®レシーバ HDMI トランスミッタ付:ADV7535                                                                                                                    |  |  |

| USB I/F        | コネクタ: USB3.2 Gen2 Type-A<br>コネクタ: USB2.0 micro-AB                                                                                                                                 |  |  |

| イーサネット I/F     | コネクタ:RJ45×2<br>イーサネット PHY IC:KSZ9131RNXI                                                                                                                                          |  |  |

| オーディオ I/F      | コネクタ: 3.5mm ジャック(MIC)<br>コネクタ: 3.5mm ジャック(HP)<br>コネクタ: 3.5mm ジャック(AUX-IN)                                                                                                         |  |  |

| SD カード I/F     | コネクタ:Micro SD カードスロット                                                                                                                                                             |  |  |

| PCIe I/F       | コネクタ: PCle Slot (×2 レーン)                                                                                                                                                          |  |  |

| MIPI CSI-2 I/F | コネクタ: CF20221V0R0-NH×2ch                                                                                                                                                          |  |  |

| Pmod I/F       | Pmod Type 1A (GPIO) Pmod Type 2A (SPI) Pmod Type 3A (UART) Pmod Type 6A (I2C)                                                                                                     |  |  |

| デバッグ I/F       | コネクタ:USB Micro-B [UART-USB ブリッジ:FT230XS]                                                                                                                                          |  |  |

| デバッガ I/F       | コネクタ:10 ピン、1.27mm ピッチ                                                                                                                                                             |  |  |

| LED            | 電源有効 (PMIC_PWRON) : 緑<br>電源 (D5.0V1) : 緑<br>電源 (VDD1G_1p8) : 緑<br>電源 (S1.8V) : 緑<br>電源 (USBC_VBUS_OUT) : 緑<br>モニター : 黄×2                                                          |  |  |

| スイッチ           | モード設定: 8bit ディップスイッチオーディオクロック選択: 6bit ディップスイッチ電源 ON/OFF: スライドスイッチPMIC ON/OFF: スライドスイッチNMI: プッシュスイッチMIPI CSI-2 カメラインターフェース電圧選択: ディップスイッチMIPI CSI-2 I2C プルアップ ON/OFF: 4bit ディップスイッチ |  |  |

| 電源             | USB-PD Type-C(60W 以上)                                                                                                                                                             |  |  |

#### 1.3.2 V2NEVK 電源仕様

本キットに必要な電力はアプリケーション、周辺機器に依存します。**表 1.3-2** に各インターフェースで想定される電力を示します。

本キットは 60W 以上の USB Power Delivery 規格に準拠した USB 電源から、電力供給されることを想定して設計されています。必ず 60W 以上供給の USB 電源を使用してください。

表 1.3-2 想定消費電力

| 項目         | 電力     | 説明                                             |

|------------|--------|------------------------------------------------|

| RZ/V2N     | 最大 12W | LSI 最大電力(ワースト条件)                               |

| MIPI CSI-2 | 最大 3W  | カメラ2台接続時                                       |

| USB        | 最大 7W  | USB2.0 : 1ch                                   |

|            |        | USB3.2 : 1ch                                   |

| PCle       | 最大 25W | 2 レーン : 1ch                                    |

| その他周辺機器    | 最大 6W  | LPDDR4X:1ch、GbE_PHY:2ch、SD/eMMC:2ch、SPI フラッシュ等 |

#### 1.3.3 V2NEVK 付属品

#### 表 1.3-3 V2NEVK 付属品

| 項目                              | 仕様                                    |  |

|---------------------------------|---------------------------------------|--|

| FFC ケーブル                        | 長さ 64.2mm、幅 14.5mm、28 ピン              |  |

|                                 | 注.CPU ボードの CN11 と EXP ボードの CN5 の接続に使用 |  |

| ヒートシンク                          | 40 × 40 × 20mm                        |  |

| USB ケーブル Type-A – Micro-B 長さ 1m |                                       |  |

| ゴム足                             | D=8mm、t=2.79mm、Qty:4                  |  |

| ネジ                              | M2×4mm サブボード固定用                       |  |

# 1.3.4 外観

図 1.3-1 V2NEVK 外観

# 1.3.5 端子機能一覧

**表 1.3-4** に V2NEVK で使用する端子機能を示します。

表 1.3-4 V2NEVK で使用する端子機能選択一覧(1/3)

| 端子配置 | 端子名 | 機能         | 説明                                                                                                                 |

|------|-----|------------|--------------------------------------------------------------------------------------------------------------------|

| AF5  | P00 | P00/LED    | EXP ボードを介して LD5 のスイッチに接続                                                                                           |

| AE5  | P01 | P01/LED    | EXP ボードを介して LD6 のスイッチに接続                                                                                           |

| AJ4  | P02 | P02        | CPU ボードの J1 コネクタ                                                                                                   |

| AJ5  | P03 | P03        | CPU ボードの J1 コネクタ                                                                                                   |

| AD6  | P04 | SSI3_SDATA | EXP ボードの Audio codec (DA7212)                                                                                      |

| AE6  | P05 | P05        | CPU ボードの J1 コネクタ                                                                                                   |

| AD5  | P06 | SDA8       | CPU ボードの RAA215300 / DA9141 / 5L35023B / J1 コネクタ                                                                   |

| AH4  | P07 | SCL8       | CPU ボードの RAA215300 / DA9141 / 5L35023B / J1 コネクタ                                                                   |

| AF7  | P10 | AUDIO_CLKB | CPU ボードの 5L35023B / J1 コネクタ<br>DSW2 (SW2)<br>ON: Audio CLKB の 5L35023B から供給あり<br>OFF: Audio CLKB の 5L35023B から供給なし |

| AJ6  | P11 | AUDIO_CLKC | CPU ボードの 5L35023B / J1 コネクタ<br>DSW2 (SW4)<br>ON: Audio CLKC の 5L35023B から供給あり<br>OFF: Audio CLKC の 5L35023B から供給なし |

| AD7  | P12 | SSI3_SCK   | EXP ボードの Audio codec (DA7212)                                                                                      |

| AG6  | P13 | SSI3_WS    | EXP ボードの Audio codec (DA7212)                                                                                      |

| AF6  | P14 | P14        | CPU ボードの J1 コネクタ                                                                                                   |

| AH6  | P15 | SSI4_SDATA | EXP ボードの Audio codec (DA7212)                                                                                      |

| AJ21 | P20 | SDA2       | CPU ボードの PCIe slot と<br>EXP ボードの Pmod Type6/6A (I2C) コネクタ / DA7212                                                 |

| AH21 | P21 | SCL2       | CPU ボードの PCIe slot と<br>EXP ボードの Pmod Type6/6A (I2C) コネクタ / DA7212                                                 |

| AH7  | P30 | SDA0       | CPU ボードの MIPI CSI-2 CH0 (CN7) / J1 コネクタ                                                                            |

| AJ7  | P31 | SCL0       | CPU ボードの MIPI CSI-2 CH0 (CN7) / J1 コネクタ                                                                            |

| AH9  | P32 | SDA1       | CPU ボードの MIPI CSI-2 CH1 (CN8) / J1 コネクタ                                                                            |

| AH10 | P33 | SCL1       | CPU ボードの MIPI CSI-2 CH1 (CN8) / J1 コネクタ                                                                            |

| AG8  | P34 | P34        | CPU ボードの J1 コネクタ                                                                                                   |

| AF9  | P35 | P35        | CPU ボードの J1 コネクタ                                                                                                   |

| AG7  | P36 | SDA3       | CPU ボードの MIPI DSI (CN11) / J1 コネクタ                                                                                 |

| AH8  | P37 | SCL3       | CPU ボードの MIPI DSI (CN11) / J1 コネクタ                                                                                 |

| AJ10 | P40 | SSI0_SCK   | CPU ボードの MIPI DSI (CN11) / J1 コネクタ                                                                                 |

| AJ9  | P41 | SSI0_WS    | CPU ボードの MIPI DSI (CN11) / J1 コネクタ                                                                                 |

| AD8  | P42 | SSI0_SDATA | CPU ボードの MIPI DSI (CN11) / J1 コネクタ                                                                                 |

| AE9  | P43 | P43        | CPU ボードの J1 コネクタ                                                                                                   |

| AJ8  | P44 | P44        | CPU ボードの J1 コネクタ                                                                                                   |

| AF8  | P45 | P45        | CPU ボードの J1 コネクタ                                                                                                   |

| AD9  | P46 | P46        | CPU ボードの J1 コネクタ                                                                                                   |

| AE8  | P47 | P47        | CPU ボードの J1 コネクタ                                                                                                   |

| AE10 | P50 | TXD0       | EXP ボードの Pmod Type3/3A (UART) コネクタ                                                                                 |

| AD10 | P51 | RXD0       | EXP ボードの Pmod Type3/3A (UART) コネクタ                                                                                 |

| AC11 | P52 | CTSON      | EXP ボードの Pmod Type3/3A (UART) コネクタ                                                                                 |

表 1.3-4 V2NEVK で使用する端子機能選択一覧(2/3)

| 端子配置 | 端子名 | 機能                 | 説明                                      |

|------|-----|--------------------|-----------------------------------------|

| AD11 | P53 | RTS0N              | EXP ボードの Pmod Type3/3A (UART) コネクタ      |

| AG10 | P54 | P54                | EXP ボードの Pmod Type6/6A (I2C) コネクタ       |

| AG11 | P55 | P55                | EXP ボードの Pmod Type6/6A (I2C) コネクタ       |

| AG12 | P56 | P56                | CPU ボードの J2 コネクタ                        |

| AJ11 | P57 | P57                | EXP ボードの Pmod Type3/3A (UART) コネクタ      |

| AH11 | P60 | P60                | CPU ボードの J2 コネクタ                        |

| AF12 | P61 | P61                | CPU ボードの J2 コネクタ                        |

| AD12 | P62 | P62                | CPU ボードの J2 コネクタ                        |

| AH12 | P63 | P63                | CPU ボードの J2 コネクタ                        |

| AF10 | P64 | P64/CAM0_RST#      | CPU ボードの MIPI CSI-2 CH0 (CN7) / J2 コネクタ |

| AF11 | P65 | P65/CAM1_RST#      | CPU ボードの MIPI CSI-2 CH1 (CN8) / J2 コネクタ |

| AE12 | P66 | P66                | CPU ボードの J2 コネクタ                        |

| AC12 | P67 | P67                | CPU ボードの J2 コネクタ                        |

| AD14 | P70 | P70/IRQ0           | EXP ボードの Pmod Type6/6A (I2C) コネクタ       |

| AC14 | P71 | P71/IRQ1/HDMI_INT# | CPU ボードの MIPI DSI (CN11) / J2 コネクタ      |

| AH13 | P72 | P72/IRQ4           | EXP ボードの Pmod Type6/6A (I2C) コネクタ       |

| AJ14 | P73 | P73                | EXP ボードの Pmod Type3/3A (UART) コネクタ      |

| AE14 | P74 | P74/IRQ8           | EXP ボードの Pmod Type2/2A (SPI) コネクタ       |

| AE13 | P75 | P75                | EXP ボードの Pmod Type2/2A (SPI) コネクタ       |

| AG14 | P76 | P76                | EXP ボードの Pmod Type3/3A (UART) コネクタ      |

| AF14 | P77 | P77                | EXP ボードの Pmod Type3/3A (UART) コネクタ      |

| AD13 | P80 | P80                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AH14 | P81 | P81                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AD15 | P82 | P82                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AJ13 | P83 | P83                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AC15 | P84 | P84                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AF13 | P85 | P85                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AC13 | P86 | P86                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AJ12 | P87 | P87                | EXP ボードの Pmod Type1/1A (GPIO) コネクタ      |

| AH17 | P90 | P90                | EXP ボードの Pmod Type6/6A (I2C) コネクタ       |

| AE17 | P91 | P91                | EXP ボードの Pmod Type6/6A (I2C) コネクタ       |

| AC16 | P92 | P92                | CPU ボードの J2 コネクタ                        |

| AC17 | P93 | P93                | CPU ボードの J2 コネクタ                        |

| AJ15 | P94 | SD1CD              | CPU ボードの SD1 カード検出 / J2 コネクタ            |

| AJ16 | P95 | USB20_VBUSEN       | CPU ボードの USB20 VBUS イネーブル / J2 コネクタ     |

| AF17 | P96 | USB20_OVRCURN      | CPU ボードの USB20 過電流検出 / J2 コネクタ          |

| AG16 | P97 | AUDIO_CLKOUT       | EXP ボードの Audio codec (DA7212)           |

| AE16 | PA0 | SD0IOVS            | CPU ボードの SD0 IO 電圧選択 / J2 コネクタ          |

| AD17 | PA1 | PA1/SD0PWEN        | CPU ボードの SD0 パワーイネーブル(未接続)/ J2 コネクタ     |

| AF16 | PA2 | SD1IOVS            | CPU ボードの SD1 IO 電圧選択 / J2 コネクタ          |

| AD16 | PA3 | SD1PWEN            | CPU ボードの SD1 パワーイネーブル / J2 コネクタ         |

| AH16 | PA4 | PA4/SSLC3          | EXP ボードの Pmod Type2/2A (SPI) コネクタ       |

| AH15 | PA5 | SD0CD              | CPU ボードの SD0 カード検出 / J2 コネクタ            |

| AG15 | PA6 | PA6/SSLC1          | EXP ボードの Pmod Type2/2A (SPI) コネクタ       |

#### 表 1.3-4 V2NEVK で使用する端子機能選択一覧 (3/3)

| 端子配置 | 端子名 | 機能              | 説明                                                                |

|------|-----|-----------------|-------------------------------------------------------------------|

| AF15 | PA7 | PA7/SD1CD/SSLC0 | CPU ボードの SD1 カード検出(未接続)と                                          |

|      |     |                 | EXP ボードの Pmod Type2/2A (SPI) コネクタ                                 |

| AE25 | PB0 | USB30_VBUSEN    | CPU ボードの USB30 VBUS イネーブル / J2 コネクタ                               |

| AG25 | PB1 | USB30_OVRCUR    | CPU ボードの USB30 過電流検出 / J2 コネクタ                                    |

| AG26 | PB2 | PB2/CAM0&1_PWR# | CPU ボードの MIPI CSI-2 CH0 (CN7) / MIPI CSI-2 CH1 (CN8) /<br>J2 コネクタ |

| AG27 | PB3 | MISOC           | EXP ボードの Pmod Type2/2A (SPI) コネクタ                                 |

| AF25 | PB4 | MOSIC           | EXP ボードの Pmod Type2/2A (SPI) コネクタ                                 |

| AF27 | PB5 | RSPCKC          | EXP ボードの Pmod Type2/2A (SPI) コネクタ                                 |

#### 1.4 使用上の注意

#### 1.4.1 V2NEVK 電源 ON/OFF

- V2NEVK のスイッチの設定には十分注意してください。設定を誤ると機器の破損につながる恐れがあります。

- RZ/V2N には電源 ON シーケンスと電源 OFF シーケンスがあります。V2NEVK に関しては以下の注意事項を必ず守ってください。

#### (1) 電源 ON 時

USB Type-C ケーブルを Type-C コネクタ (CN13) に接続する前に、電源スライドスイッチ SW2、SW3 が OFF になっていることを必ず確認してください。

電源スライドスイッチ SW2、SW3 が ON の状態で USB Type-C ケーブルを Type-C コネクタに接続することは禁止されています。

#### (2) 電源 OFF 時

電源スライドスイッチ SW2 と SW3 を OFF にする前に、ソフトウェアによる電源 OFF シーケンスを必ず実行してください。  $^{(\pm 1)}$  ソフトウェアによる電源 OFF シーケンス終了後、これらのスライドスイッチを OFF にし、USB Type-C ケーブルを Type-C コネクタ(CN13)から取り外してください。電源スライドスイッチ SW2、SW3 が ON の状態で Type-C コネクタから USB Type-C ケーブルを取り外すことは禁止されています。そのような行為は機器の損傷につながる可能性があります。

注1. 電源シーケンスについては、『RZ/V2N Group User's Manual: Hardware』を参照してください。

#### 1.4.2 イーサネット使用上の注意

ギガビットイーサネットインターフェースコネクタ (CN5、CN6) は公衆回線に接続しないでください。公衆回線との接続はサポートしていません。本評価キットには MAC アドレスは設定されていませんのでご注意ください。

# 2. 操作手順

# 2.1 組立

CPU ボードと EXP ボードは J1, J2, J4 でスタッキング接続されています。また、MIPI DSI I/F の接続は、専用の FFC ケーブルで接続します。保護のため、EXP ボードの裏面に付属のゴム足を貼り付けてください。

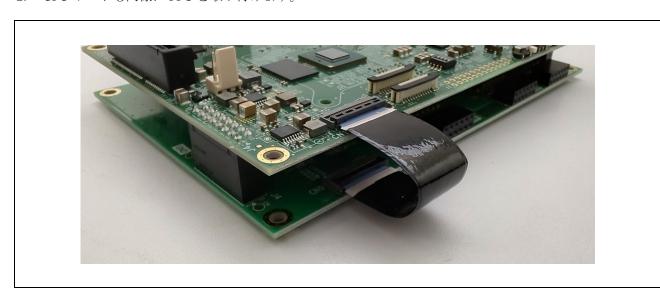

FFC は以下の手順で取付けます。

1. FFC のロック付きカバーを開き、FFC の接点を下向きに合わせてカバーがロックするまで閉じます。 カバーは壊れやすいので、取り扱いには十分注意してください。

図 2.1-1 FFC を RZ/V2H EVK Expansion Board に接続

2. CPU ボードも同様に FFC を取り付けます。

図 2.1-2 FFC を RZ/V2N Evaluation Board に接続

microSD Sub Board および eMMC Sub Board は以下の手順で取付けます。

1. CN15 のスタッキングコネクタに合わせて Sub Board を挿し込みます。方向に注意してください。

図 2.1-3 Sub Board を RZ/V2N Evaluation Board に接続

2. 付属のネジを締めて固定してください。

図 2.1-4 ネジを締めて Sub Board を固定(写真は microSD Sub Board 取付時)

# 2.2 モード設定

以下の表に、ディップスイッチ (RZ/V2N Evaluation Board では DSW1) の設定およびその機能を示します。

表 2.2-1 DSW1 接続先および機能

| スイッチ No. | RZ/V2N ピン   | 機能                                 |

|----------|-------------|------------------------------------|

| 1        | BOOTSELCPU  | コールドブート CPU を選択                    |

|          |             | OFF: CM33、ON: CA55 (初期設定)          |

| 2        | BOOTPLLCA_1 | CA55 コールドブート時に CA55 周波数を入力         |

| 3        | BOOTPLLCA_0 | BOOTPLLCA[1:0] =[OFF:OFF] : 1.6GHz |

|          |             | =[OFF:ON] : 1.7GHz(初期設定)           |

|          |             | =[ON:OFF] : 1.1GHz                 |

|          |             | =[ON:ON] : 1.5GHz                  |

| 4        | MD_BOOT1    | ブートモード選択信号を入力                      |

| 5        | MD_BOOT0    | MD_BOOT[1:0] =[OFF:OFF] : xSPI     |

|          |             | =[OFF:ON] : SCIF                   |

|          |             | =[ON:OFF] : SD (初期設定)              |

|          |             | =[ON:ON] : eMMC                    |

| 6        | MD_CLKS     | OFF: SSCG ON(初期設定)、ON: SSCG OFF    |

| 7        | MD_BOOT3    | OFF:ノーマルモード(初期設定)、ON:デバッグモード       |

| 8        | MD_BOOT4    | OFF 固定                             |

以下の表に、ディップスイッチ (RZ/V2N Evaluation Board では DSW2) の設定およびその機能を示します。

表 2.2-2 DSW2 機能

| スイッチ No. | 信号名           | 機能                                          |

|----------|---------------|---------------------------------------------|

| 1        | Audio_CLKB_OE | OFF : 5L35023B の Audio_CLKB 出力を無効にします(初期設定) |

|          |               | ON : 5L35023B の Audio_CLKB 出力を有効にします        |

| 2        | Audio_CLKB    | OFF : Audio_CLKB は供給されません(初期設定)             |

|          |               | ON : Audio_CLKB にクロック供給します                  |

| 3        | Audio_CLKC_OE | OFF : 5L35023B の Audio_CLKC 出力を無効にします(初期設定) |

|          |               | ON : 5L35023B の Audio_CLKC 出力を有効にします        |

| 4        | Audio_CLKC    | OFF : Audio_CLKC は供給されません(初期設定)             |

|          |               | ON : Audio_CLKC にクロック供給します                  |

| 5        | NEN_VPROG     | OFF : 固定                                    |

|          |               | ON : 設定禁止                                   |

| 6        | _             | _                                           |

以下の表に、ディップスイッチ (RZ/V2N Evaluation Board では JSW1) の設定およびその機能を示します。

表 2.2-3 JSW1 機能

| スイッチ No. | 機能                                  |

|----------|-------------------------------------|

| 1-2      | MIPI CSI-2 カメラインターフェース電圧:1.8V       |

| 2-3      | MIPI CSI-2 カメラインターフェース電圧:3.3V(初期設定) |

注: 接続するカメラモジュールのインターフェース電圧に合わせて、設定してください。

以下の表に、ディップスイッチ (RZ/V2N Evaluation Board では DSW3) の設定およびその機能を示します。

表 2.2-4 DSW3 機能

| スイッチ No. | 信号名      | 機能                                         |

|----------|----------|--------------------------------------------|

| 1        | I2C0_SCL | OFF : MIPI CSI-2 (ch0) SCL 信号プルアップ OFF     |

|          |          | ON : MIPI CSI-2 (ch0) SCL 信号プルアップ ON(初期設定) |

| 2        | I2C0_SDA | OFF : MIPI CSI-2 (ch0) SDA 信号プルアップ OFF     |

|          |          | ON : MIPI CSI-2 (ch0) SDA 信号プルアップ ON(初期設定) |

| 3        | I2C1_SCL | OFF : MIPI CSI-2 (ch1) SCL 信号プルアップ OFF     |

|          |          | ON : MIPI CSI-2 (ch1) SCL 信号プルアップ ON(初期設定) |

| 4        | I2C1_SDA | OFF : MIPI CSI-2 (ch1) SDA 信号プルアップ OFF     |

|          |          | ON : MIPI CSI-2 (ch1) SDA 信号プルアップ ON(初期設定) |

注: これらの信号がカメラモジュール内でプルアップされている場合は、スイッチ設定を OFF にしてください。

#### 2.3 電源

- 1. 電源を供給する前にディップスイッチを設定してください。

- 2. USB Type-C ケーブルを接続する前に、電源スライドスイッチ SW2 と SW3 が OFF になっていることを確認してください。

- 3. USB Type-C ケーブルを RZ/V2N Evaluation Board の CN13 に接続してください。

- 4. SW3 を ON にすると LD2 と LD7 が点灯します。

- 5. SW2 を ON にすると LD1、LD3、LD4 が点灯し、RZ/V2N が起動します。

表 2.3-1 SW2/SW3 設定

| スイッチ No. | 機能                      | 操作                            |

|----------|-------------------------|-------------------------------|

| SW2      | PMIC (RAA215300) ON/OFF | ON : PMIC の出力をイネーブルします。       |

|          |                         | OFF : PMIC の出力のディセーブルを停止します。  |

| SW3      | USB-PD 電源 ON/OFF        | ON : USB-PD 電源の出力をイネーブルします。   |

|          |                         | OFF : USB-PD 電源の出力をディセーブルします。 |

# 3. 配置

# 3.1 部品配置

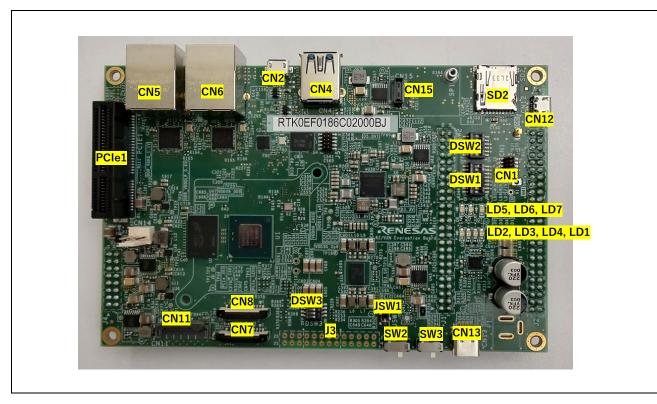

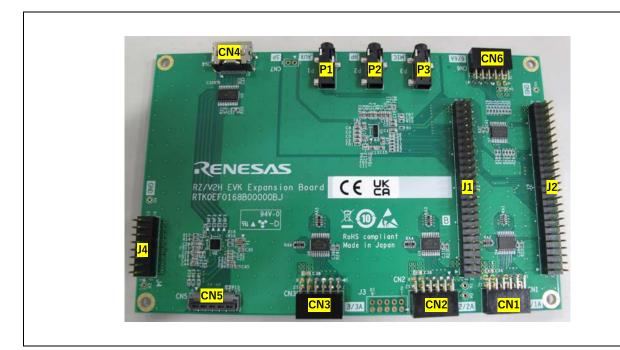

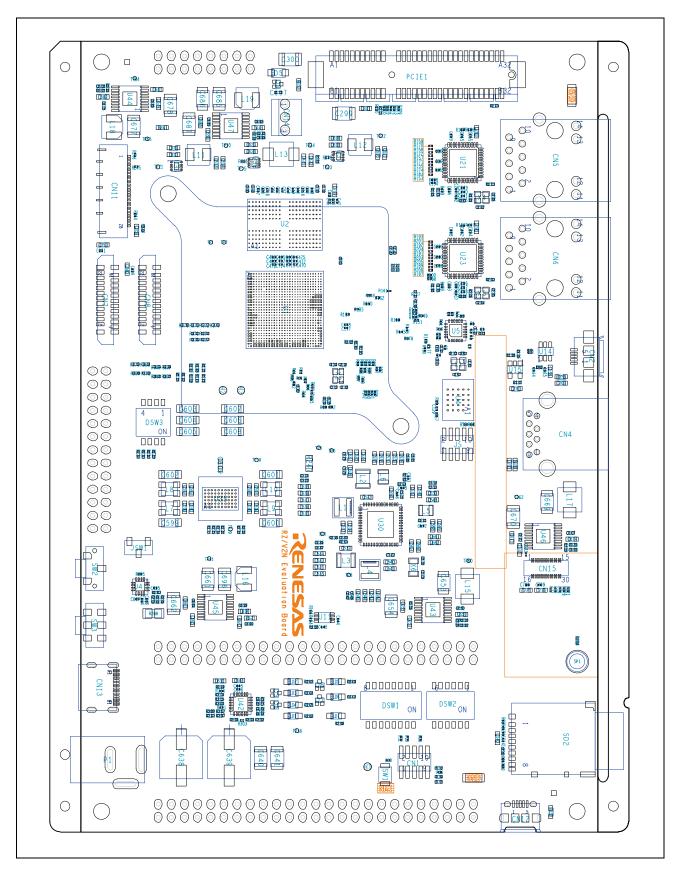

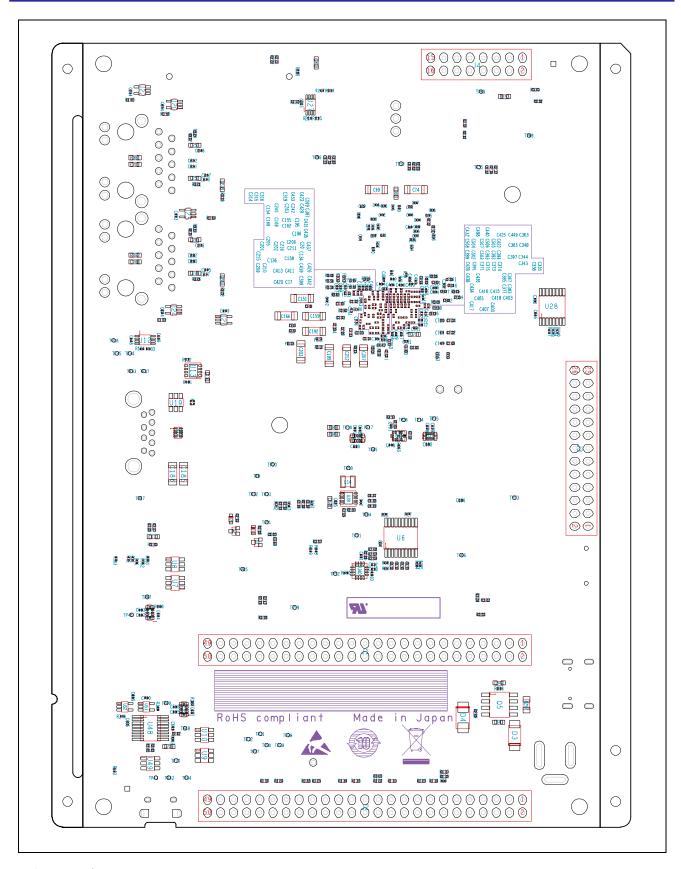

**図 3.1-1** および**図 3.1-2** は RZ/V2N Evaluation Board の部品配置図です。 **図 3.1-3** は RZ/V2H EVK Expansion Board の部品配置図です。

**図 3.1-4** および**図 3.1-5** はそれぞれ Sub Board の図を示します。

図 3.1-1 RZ/V2N Evaluation Board 部品配置図(部品面)

図 3.1-2 RZ/V2N Evaluation Board(半田面)

図 3.1-3 RZ/V2H EVK Expansion Board 部品配置図(部品面)

図 3.1-4 microSD Sub Board

図 3.1-5 eMMC Sub Board

# 3.2 主要部品リスト

**表 3.2-1** および**表 3.2-2** に、RZ/V2N Evaluation Board、RZ/V2H EVK Expansion Board それぞれの主要部品を示します。

表 3.2-1 RZ/V2N Evaluation Board 部品リスト

| No. | 数量 | 部品記号                    | 部品名                        | メーカー                |

|-----|----|-------------------------|----------------------------|---------------------|

| 1   | 1  | U1                      | R9A09G056N48GBG (RZ/V2N)   | Renesas Electronics |

| 2   | 1  | U5                      | 5L35023B-616NLGI8          | Renesas Electronics |

| 3   | 1  | U6                      | SLG7RN47855G               | Renesas Electronics |

| 4   | 1  | U13                     | ISL61852CCRZ               | Renesas Electronics |

| 5   | 1  | U30                     | RAA215300A2GNP#HA2         | Renesas Electronics |

| 6   | 4  | U31, U32, U33, U34      | SLG59M1603V                | Renesas Electronics |

| 7   | 1  | U50                     | SLG59M1717V                | Renesas Electronics |

| 8   | 1  | U35                     | DA9141-08F72 <sup>注1</sup> | Renesas Electronics |

| 9   | 2  | U36, U37                | ISL80031A                  | Renesas Electronics |

| 10  | 1  | U38                     | ISL80015                   | Renesas Electronics |

| 11  | 5  | U43, U44, U45, U46, U47 | RAA211250GSP#HA0           | Renesas Electronics |

注1. 本部品は DA9130-08RT1 に代替可能です。

表 3.2-2 RZ/V2H EVK Expansion Board 部品リスト

| No. | 数量 | 部品記号 | 部品名         | メーカー                |

|-----|----|------|-------------|---------------------|

| 1   | 1  | U1   | DA7212-01UM | Renesas Electronics |

# 4. インターフェース仕様

本章では V2NEVK のインターフェース仕様について説明します。

#### 4.1 リセット

V2NEVK をリセットする場合は、電源制御スイッチ(SW2、SW3)、およびソフトウェアで制御してください。

#### 4.2 LED

V2NEVKのCPUボードには、7つのLEDが搭載されています。表 4.2-1にLEDの色と機能を示します。

表 4.2-1 RZ/V2H Secure Evaluation Board LED

| LED | 色 | 機能                           |

|-----|---|------------------------------|

| LD1 | 緑 | PMIC_PWR ON インジケータ用          |

| LD2 | 緑 | 電源 D5.0V1(5V)インジケータ用         |

| LD3 | 緑 | 電源 VDD1G_1p8(1.8V)インジケータ用    |

| LD4 | 緑 | 電源 S1.8V(1.8V)インジケータ用        |

| LD5 | 黄 | 信号モニタ用                       |

| LD6 | 黄 | 信号モニタ用                       |

| LD7 | 緑 | 電源 USBC_VBUS_OUT(20V)インジケータ用 |

#### 4.3 スイッチ

V2NEVK の CPU ボードには、7 つのスイッチが搭載されています。表 4.3-1 に各スイッチの機能を示します。

表 4.3-1 RZ/V2N Evaluation Board スイッチ

| スイッチ | 形状       | 用途                               |

|------|----------|----------------------------------|

| DSW1 | ディップスイッチ | 「2.2 モー <b>ド設定</b> 」を参照          |

| DSW2 | ディップスイッチ | 「2.2 モー <b>ド設定</b> 」を参照          |

| DSW3 | ディップスイッチ | 「2.2 モー <b>ド設定</b> 」を参照          |

| JSW1 | ディップスイッチ | 「2.2 モー <b>ド設定</b> 」を参照          |

| SW1  | プッシュスイッチ | NMI                              |

| SW2  | スライドスイッチ | 電源スイッチ(PMIC_RAA215300 ON/OFF)    |

| SW3  | スライドスイッチ | 電源スイッチ(USBC VBUS OUT 20V ON/OFF) |

### 4.4 デバッグシリアルインターフェース

デバッグポート(micro USB Type-B コネクタ(CN12))を、USB-UART 変換 IC 経由で RZ/V2N の SCIF インタフェースに接続します。このポートはデバッグ時に使用します。

# 4.5 デバッガインターフェース

ICE を Arm JTAG コネクタ (CN1) に接続します。接続確認済の ICE については、ルネサスエレクトロニクス営業担当までお問い合わせください。

注. エミュレータ接続コネクタは 10 ピンあり、1.27mm ピッチです。

表 4.5-1 Arm JTAG コネクタ(CN1)

| ピン No. | V2NEVK 接続先        |

|--------|-------------------|

| 1      | +1.8V (VDD1G_1p8) |

| 3      | GND               |

| 5      | GND               |

| 7      | NC                |

| 9      | RZ/V2N (TRSTN)    |

| ピン No. | V2NEVK 接続先         |

|--------|--------------------|

| 2      | RZ/V2N (TMS_SWDIO) |

| 4      | RZ/V2N (TCK_SWCLK) |

| 6      | RZ/V2N (TDO)       |

| 8      | RZ/V2N (TDI)       |

| 10     | RZ/V2N (QRESN)     |

# 4.6 MIPI CSI-2 インターフェース

V2NEVK の CPU ボードには、4 つの MIPI CSI-2 インターフェースが搭載されています。

#### 注 意

本インターフェースは Raspberry Pi カメラインターフェースとは異なります。Raspberry Pi カメラモジュールを接続する際は、各信号間の接続をよく確認してください。誤った接続を行うと、ボードやモジュールが壊れる可能性があります。

表 4.6-1 MIPI CSI-2 コネクタ (CN7)

| ピン No. | V2NEVK 接続先           |

|--------|----------------------|

| 1      | GND                  |

| 2      | RZ/V2N (CSI0_DATA0N) |

| 3      | RZ/V2N (CSI0_DATA0P) |

| 4      | GND                  |

| 5      | RZ/V2N (CSI0_DATA1N) |

| 6      | RZ/V2N (CSI0_DATA1P) |

| 7      | GND                  |

| 8      | RZ/V2N (CSI0_CLKN)   |

| 9      | RZ/V2N (CSI0_CLKP)   |

| 10     | GND                  |

| 11     | RZ/V2N (CSI0_DATA2N) |

| ピン No. | V2NEVK 接続先           |

|--------|----------------------|

| 12     | RZ/V2N (CSI0_DATA2P) |

| 13     | GND                  |

| 14     | RZ/V2N (CSI0_DATA3N) |

| 15     | RZ/V2N (CSI0_DATA3P) |

| 16     | GND                  |

| 17     | RZ/V2N (PB2)         |

| 18     | RZ/V2N (P64)         |

| 19     | GND                  |

| 20     | RZ/V2N (I2C0_SCL)    |

| 21     | RZ/V2N (I2C0_SDA)    |

| 22     | +3.3V (PCle_3V3)     |

表 4.6-2 MIPI CSI-2 コネクタ(CN8)

| ピン No. | V2NEVK 接続先           |

|--------|----------------------|

| 1      | GND                  |

| 2      | RZ/V2N (CSI1_DATA0N) |

| 3      | RZ/V2N (CSI1_DATA0P) |

| 4      | GND                  |

| 5      | RZ/V2N (CSI1_DATA1N) |

| 6      | RZ/V2N (CSI1_DATA1P) |

| 7      | GND                  |

| 8      | RZ/V2N (CSI1_CLKN)   |

| 9      | RZ/V2N (CSI1_CLKP)   |

| 10     | GND                  |

| 11     | RZ/V2N (CSI1_DATA2N) |

| ピン No. | V2NEVK 接続先           |

|--------|----------------------|

| 12     | RZ/V2N (CSI1_DATA2P) |

| 13     | GND                  |

| 14     | RZ/V2N (CSI1_DATA3N) |

| 15     | RZ/V2N (CSI1_DATA3P) |

| 16     | GND                  |

| 17     | RZ/V2N (PB2)         |

| 18     | RZ/V2N (P65)         |

| 19     | GND                  |

| 20     | RZ/V2N (I2C1_SCL)    |

| 21     | RZ/V2N (I2C1_SDA)    |

| 22     | +3.3V (PCIe_3V3)     |

#### 4.7 MIPI DSI インターフェース

V2NEVK には、MIPI DSI インターフェースが搭載されています。CPU ボードの RZ/V2N から CN11 に接続されており、専用 FFC で EXP ボードの CN5 に接続します。EXP ボードでは、MIPI DSI を HDMI 信号に変換して、CN4 の HDMI コネクタに出力します。

表 4.7-1 MIPI DSI コネクタ(CN11)

| ピン No. | V2NEVK 接続先           |

|--------|----------------------|

| 1      | RZ/V2N (P37)         |

| 2      | RZ/V2N (P41)         |

| 3      | RZ/V2N (P40)         |

| 4      | RZ/V2N (P42)         |

| 5      | RZ/V2N (P36)         |

| 6      | GND                  |

| 7      | RZ/V2N (DSI_DNDATA3) |

| 8      | RZ/V2N (DSI_DPDATA3) |

| 9      | GND                  |

| 10     | RZ/V2N (DSI_DNDATA2) |

| 11     | RZ/V2N (DSI_DPDATA2) |

| 12     | GND                  |

| 13     | RZ/V2N (DSI_DNDATA1) |

| 14     | RZ/V2N (DSI_DPDATA1) |

| 15     | GND                  |

| ピンNo. | V2NEVK 接続先           |

|-------|----------------------|

| 16    | RZ/V2N (DSI_DNDATA0) |

| 17    | RZ/V2N (DSI_DPDATA0) |

| 18    | GND                  |

| 19    | RZ/V2N (DSI_DNCLK)   |

| 20    | RZ/V2N (DSI_DPCLK)   |

| 21    | GND                  |

| 22    | RZ/V2N (P71)         |

| 23    | GND                  |

| 24    | +1.8V (VDD1G_1p8)    |

| 25    | GND                  |

| 26    | +3.3V (D3.3V)        |

| 27    | GND                  |

| 28    | +5.0V                |

| G1-5  | GND                  |

| F1-2  | GND                  |

#### 4.8 USB インターフェース

V2NEVK の CPU ボードには、以下の USB コネクタが搭載されています。

- USB3.2 Gen2 HOST インターフェース USB Type-A コネクタ (CN4) は RZ/V2N の USB3.2 Gen2 インターフェースに接続されています。

- USB2.0 DRD インターフェース USB micro-AB コネクタ (CN2) は RZ/V2N の USB2.0 (ch0) インターフェースに接続されています。

#### 4.9 イーサネットインターフェース

V2NEVK の CPU ボードには、2 つのイーサネットインターフェースが搭載されています。 RJ45 コネクタ (CN5、CN6) は、イーサネット PHY IC 経由で RZ/V2N のイーサネットインターフェースに接続されています。このインターフェースを公衆回線に接続することは禁止されています。

### 4.10 SD/eMMC サブボードコネクタ

V2NEVK の CPU ボードには、SD/eMMC サブボードコネクタ (CN15) が搭載されています。このコネクタは RZ/V2N の SD インターフェース (SD0) に接続されています。付属の microSD Sub Board または eMMC Sub Board をスタッキングで接続し、Boot デバイスとして使用可能です。

表 4.10-1 SD/eMMC サブボードコネクタ(CN15)

| ピン No. | V2NEVK 接続先            |

|--------|-----------------------|

| 1      | +3.3V (microSD0_3.3V) |

| 2      | +3.3V (microSD0_3.3V) |

| 3      | RZ/V2N (SD0DAT5)      |

| 4      | GND                   |

| 5      | RZ/V2N (SD0DAT7)      |

| 6      | GND                   |

| 7      | RZ/V2N (SD0DAT1)      |

| 8      | GND                   |

| 9      | RZ/V2N (SD0DAT3)      |

| 10     | GND                   |

| 11     | RZ/V2N (SD0DAT2)      |

| 12     | GND                   |

| 13     | eMMC_SD_SEL           |

| 14     | D33_D18_SEL           |

| 15     | RZ/V2N (SD0RSTN)      |

| ピンNo. | V2NEVK 接続先          |

|-------|---------------------|

| 16    | +3.3V (VDD1833_SD0) |

| 17    | GND                 |

| 18    | GND                 |

| 19    | RZ/V2N (SD0DAT0)    |

| 20    | GND                 |

| 21    | RZ/V2N (SD0CLK)     |

| 22    | GND                 |

| 23    | RZ/V2N (SD0CMD)     |

| 24    | GND                 |

| 25    | RZ/V2N (SD0DAT4)    |

| 26    | GND                 |

| 27    | RZ/V2N (SD0DAT6)    |

| 28    | GND                 |

| 29    | RZ/V2N (SD0CD)      |

| 30    | GND                 |

# 4.11 SD カードコネクタ

V2NEVK の CPU ボードには、SD カードコネクタ (SD2) が搭載されています。SD2 は RZ/V2N の SD インターフェース (ch1) にされています。

# 4.12 PCle コネクタ

V2NEVK の CPU ボードには、PCIe コネクタ (PCIe1) が搭載されています。このコネクタは RZ/V2N の PCIe インターフェースに接続されています。

# 4.13 ピンヘッダ

V2NEVKのCPUボードには、5つのピンヘッダが搭載されています。以下の表に接続先を示します。

表 4.13-1 GPIO CN(J1)(EXP ボードへのスタッキング接続)

| ピン No. | V2NEVK 接続先         |

|--------|--------------------|

| 1      | +3.3V (D3.3V)      |

| 3      | +1.8V (VDD_1G_1p8) |

| 5      | +1.8V (S1.8V)      |

| 7      | RZ/V2N (P00)       |

| 9      | RZ/V2N (P01)       |

| 11     | RZ/V2N (P02)       |

| 13     | RZ/V2N (P03)       |

| 15     | RZ/V2N (P04)       |

| 17     | RZ/V2N (P05)       |

| 19     | RZ/V2N (P06)       |

| 21     | RZ/V2N (P07)       |

| 23     | RZ/V2N (P10)       |

| 25     | RZ/V2N (P11)       |

| 27     | RZ/V2N (P12)       |

| 29     | RZ/V2N (P13)       |

| 31     | RZ/V2N (P14)       |

| 33     | RZ/V2N (P15)       |

| 35     | RZ/V2N (P20)       |

| 37     | RZ/V2N (P21)       |

| 39     | RZ/V2N (P30)       |

| 41     | RZ/V2N (P31)       |

| 43     | RZ/V2N (P32)       |

| 45     | RZ/V2N (QRESN)     |

| 47     | PMIC_PWRON         |

| 49     | GND                |

| ピンNo. | V2NEVK 接続先   |

|-------|--------------|

| 2     | GND          |

| 4     | GND          |

| 6     | GND          |

| 8     | P00_LED      |

| 10    | P01_LED      |

| 12    | RZ/V2N (P33) |

| 14    | RZ/V2N (P34) |

| 16    | RZ/V2N (P35) |

| 18    | RZ/V2N (P36) |

| 20    | RZ/V2N (P37) |

| 22    | RZ/V2N (P40) |

| 24    | RZ/V2N (P41) |

| 26    | RZ/V2N (P11) |

| 28    | RZ/V2N (P43) |

| 30    | RZ/V2N (P44) |

| 32    | RZ/V2N (P45) |

| 34    | RZ/V2N (P46) |

| 36    | RZ/V2N (P47) |

| 38    | RZ/V2N (P50) |

| 40    | RZ/V2N (P51) |

| 42    | RZ/V2N (P52) |

| 44    | RZ/V2N (P53) |

| 46    | RZ/V2N (P54) |

| 48    | RZ/V2N (P55) |

| 50    | GND          |

表 4.13-2 GPIO CN (J2) (EXP ボードへのスタッキング接続)

| 105 51 | ) (O) IE) ((/ \dot /\dot /\dot ) |

|--------|----------------------------------|

| ピン No. | V2NEVK 接続先                       |

| 1      | RZ/V2N (P56)                     |

| 3      | RZ/V2N (P57)                     |

| 5      | RZ/V2N (P60)                     |

| 7      | RZ/V2N (P61)                     |

| 9      | RZ/V2N (P62)                     |

| 11     | RZ/V2N (P63)                     |

| 13     | RZ/V2N (P64)                     |

| 15     | RZ/V2N (P65)                     |

| 17     | RZ/V2N (P66)                     |

| 19     | RZ/V2N (P67)                     |

| 21     | RZ/V2N (P70)                     |

| 23     | RZ/V2N (P71)                     |

| 25     | RZ/V2N (P72)                     |

| 27     | RZ/V2N (P73)                     |

| 29     | RZ/V2N (P74)                     |

| 31     | RZ/V2N (P75)                     |

| 33     | RZ/V2N (P76)                     |

| 35     | RZ/V2N (P77)                     |

| 37     | RZ/V2N (P80)                     |

| 39     | RZ/V2N (P81)                     |

| 41     | RZ/V2N (P82)                     |

| 43     | RZ/V2N (P83)                     |

| 45     | RZ/V2N (P84)                     |

| 47     | RZ/V2N (P85)                     |

| 49     | GND                              |

| ピン No. | V2NEVK 接続先   |

|--------|--------------|

| 2      | RZ/V2N (P86) |

| 4      | RZ/V2N (P87) |

| 6      | RZ/V2N (P90) |

| 8      | RZ/V2N (P91) |

| 10     | RZ/V2N (P92) |

| 12     | RZ/V2N (P93) |

| 14     | RZ/V2N (P94) |

| 16     | RZ/V2N (P95) |

| 18     | RZ/V2N (P96) |

| 20     | RZ/V2N (P97) |

| 22     | RZ/V2N (PA0) |

| 24     | RZ/V2N (PA1) |

| 26     | RZ/V2N (P72) |

| 28     | RZ/V2N (PA3) |

| 30     | RZ/V2N (PA4) |

| 32     | RZ/V2N (PA5) |

| 34     | RZ/V2N (PA6) |

| 36     | RZ/V2N (PA7) |

| 38     | RZ/V2N (PB0) |

| 40     | RZ/V2N (PB1) |

| 42     | RZ/V2N (PB2) |

| 44     | RZ/V2N (PB3) |

| 46     | RZ/V2N (PB4) |

| 48     | RZ/V2N (PB5) |

| 50     | GND          |

表 4.13-3 A/D 入力 CN (J3) [未実装]

| ピン No. | V2NEVK 接続先      |

|--------|-----------------|

| 1      | +1.8V (S1.8V)   |

| 3      | RZ/V2N (ANI000) |

| 5      | RZ/V2N (ANI001) |

| 7      | RZ/V2N (ANI002) |

| 9      | RZ/V2N (ANI003) |

| 11     | RZ/V2N (ANI100) |

| 13     | RZ/V2N (ANI101) |

| 15     | RZ/V2N (ANI102) |

| 17     | RZ/V2N (ANI103) |

| 19     | RZ/V2N (ANI200) |

| 21     | RZ/V2N (ANI201) |

| 23     | RZ/V2N (ANI202) |

| 25     | RZ/V2N (ANI203) |

| ピン No. | V2NEVK 接続先      |

|--------|-----------------|

| 2      | GND             |

| 4      | RZ/V2N (ANI004) |

| 6      | RZ/V2N (ANI005) |

| 8      | RZ/V2N (ANI006) |

| 10     | RZ/V2H (ANI007) |

| 12     | RZ/V2N (ANI104) |

| 14     | RZ/V2N (ANI105) |

| 16     | RZ/V2N (ANI106) |

| 18     | RZ/V2N (ANI107) |

| 20     | RZ/V2N (ANI204) |

| 22     | RZ/V2N (ANI205) |

| 24     | RZ/V2N (ANI206) |

| 26     | RZ/V2N (ANI207) |

表 4.13-4 Power CN (J4) (EXP ボードへのスタッキング接続)

| ピン No. | V2NEVK 接続先 |

|--------|------------|

| 1      | +5.0V      |

| 3      | +5.0V      |

| 5      | +5.0V      |

| 7      | +5.0V      |

| 9      | GND        |

| 11     | GND        |

| 13     | GND        |

| 15     | GND        |

| ピンNo. | V2NEVK 接続先 |

|-------|------------|

| 2     | +5.0V      |

| 4     | +5.0V      |

| 6     | +5.0V      |

| 8     | +5.0V      |

| 10    | GND        |

| 12    | GND        |

| 14    | GND        |

| 16    | GND        |

# 4.14 12V コネクタ

CN14 で 12V に接続可能です。

表 4.14-1 12V コネクタ (CN14)

| ピン No. | 接続   |

|--------|------|

| 1      | N.C. |

| 2      | +12V |

| 3      | GND  |

# 4.15 USB-PD コネクタ (電源のみ)

V2NEVK は、USB-PD (CN13) から供給される電源で動作します。

CN13には、USB-PD コントローラが接続されており、USB-PD 電源から 20V/最大 5A を引き出します。

#### 4.16 HDMI インターフェース

V2NEVK の EXP ボードには、HDMI インターフェースが搭載されています。HDMI Type-A コネクタ (CN4) は、DSI-HDMI 変換 IC 経由で RZ/V2N の MIPI DSI インターフェースに接続されています。

#### 4.17 オーディオインターフェース

V2NEVK の EXP ボードには、3 つのオーディオコネクタが搭載されています。3 つのオーディオ 3.5mm ジャック (P1: AUX、P2: HP、P3: MIC) は、オーディオ CODEC IC 経由で RZ/V2N の SSI インターフェースに接続されています。

# 4.18 Pmod コネクタ

V2NEVKのEXPボードには、4つのPmodコネクタが搭載されています。以下の表に仕様を示します。

表 4.18-1 Pmod Type 1A GPIO(CN1)

| ピン No. | Pmod ピン仕様 | V2NEVK 接続先                |

|--------|-----------|---------------------------|

| 1      | IO1       | RZ/V2N (P80) レベルシフタ U4 経由 |

| 2      | IO2       | RZ/V2N (P81) レベルシフタ U4 経由 |

| 3      | IO3       | RZ/V2N (P82) レベルシフタ U4 経由 |

| 4      | IO4       | RZ/V2N (P83) レベルシフタ U4 経由 |

| 5      | GND       | GND                       |

| 6      | VCC       | +3.3V (D3.3V)             |

| 7      | IO5       | RZ/V2N (P84) レベルシフタ U4 経由 |

| 8      | 106       | RZ/V2N (P85) レベルシフタ U4 経由 |

| 9      | 107       | RZ/V2N (P86) レベルシフタ U4 経由 |

| 10     | IO8       | RZ/V2N (P87) レベルシフタ U4 経由 |

| 11     | GND       | GND                       |

| 12     | VCC       | +3.3V (D3.3V)             |

表 4.18-2 Pmod Type 2A SPI (CN2)

| ピン No. | Pmod ピン仕様 | V2NEVK 接続先                |

|--------|-----------|---------------------------|

| 1      | SSLA      | RZ/V2N (PA7) レベルシフタ U5 経由 |

| 2      | MOSI      | RZ/V2N (PB4) レベルシフタ U5 経由 |

| 3      | MISO      | RZ/V2N (PB3) レベルシフタ U5 経由 |

| 4      | SCK       | RZ/V2N (PB5) レベルシフタ U5 経由 |

| 5      | GND       | GND                       |

| 6      | VCC       | +3.3V (D3.3V)             |

| 7      | IO1       | RZ/V2N (P74) レベルシフタ U5 経由 |

| 8      | IO2       | RZ/V2N (P75) レベルシフタ U5 経由 |

| 9      | IO3       | RZ/V2N (PA6) レベルシフタ U5 経由 |

| 10     | IO4       | RZ/V2N (PA4) レベルシフタ U5 経由 |

| 11     | GND       | GND                       |

| 12     | VCC       | +3.3V (D3.3V)             |

表 4.18-3 Pmod Type 3A UART (CN3)

| ピン No. | Pmod ピン仕様 | V2NEVK 接続先                |

|--------|-----------|---------------------------|

| 1      | CTS       | RZ/V2N (P52) レベルシフタ U6 経由 |

| 2      | TXD       | RZ/V2N (P50) レベルシフタ U6 経由 |

| 3      | RXD       | RZ/V2N (P51) レベルシフタ U6 経由 |

| 4      | RTS       | RZ/V2N (P53) レベルシフタ U6 経由 |

| 5      | GND       | GND                       |

| 6      | VCC       | +3.3V (D3.3V)             |

| 7      | IO1       | RZ/V2N (P57) レベルシフタ U6 経由 |

| 8      | IO2       | RZ/V2N (P73) レベルシフタ U6 経由 |

| 9      | IO3       | RZ/V2N (P76) レベルシフタ U6 経由 |

| 10     | IO4       | RZ/V2N (P77) レベルシフタ U6 経由 |

| 11     | GND       | GND                       |

| 12     | VCC       | +3.3V (D3.3V)             |

表 4.18-4 Pmod Type 6A I2C (CN6)

| ピン No. | Pmod ピン仕様 | V2NEVK 接続先                |

|--------|-----------|---------------------------|

| 1      | IO1       | RZ/V2N (P55) レベルシフタ U7 経由 |

| 2      | IO2       | RZ/V2N (P54) レベルシフタ U7 経由 |

| 3      | SCL       | RZ/V2N (P21) レベルシフタ U7 経由 |

| 4      | SDA       | RZ/V2N (P20) レベルシフタ U7 経由 |

| 5      | GND       | GND                       |

| 6      | VCC       | +3.3V (D3.3V)             |

| 7      | IO3       | RZ/V2N (P70) レベルシフタ U7 経由 |

| 8      | IO4       | RZ/V2N (P72) レベルシフタ U7 経由 |

| 9      | IO5       | RZ/V2N (P90) レベルシフタ U7 経由 |

| 10     | IO6       | RZ/V2N (P91) レベルシフタ U7 経由 |

| 11     | GND       | GND                       |

| 12     | VCC       | +3.3V (D3.3V)             |

# 5. 補足事項

#### 5.1 V2NEVK の電源 IC

評価用途を考慮し、V2NEVKの電源 IC は余裕を持って選定しています。電源 IC はユーザ回路に適合したものを推奨します。電源 IC に関しては、ルネサスエレクトロニクス営業担当までお問い合わせください。

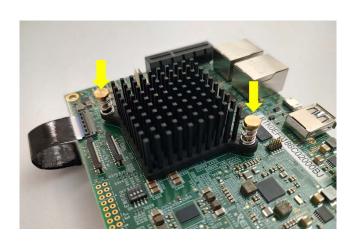

# 5.2 ヒートシンクの組付け

- ヒートシンク裏面の保護シールを剥がしてください。

- ヒートシンクを RZ/V2N Evaluation Board に接続してください。

図 5.2-1 ヒートシンクを RZ/V2N Evaluation Board に接続

# 付録A CPU ボード部品配置図

付録 A.1 部品配置図(Top)

付録 A.2 部品配置図(Bottom)

# 改訂記録 RZ/V2N Evaluation Board Kit (Secure type) ハードウェアマニュアル

|      |            | 改訂内容    |                                                                                                      |

|------|------------|---------|------------------------------------------------------------------------------------------------------|

| Rev. | 発行日        | ページ     | 概要                                                                                                   |

| 1.00 | 2024.11.22 | _       | 初版発行                                                                                                 |

| 1.10 | 2025.02.28 | 1. 概要   |                                                                                                      |

|      |            | 11      | 図 1.2-1 RZ/V2N Evaluation Board ブロック図 修正<br>(ISL97701IRZ, VDD1833_PRE18_SD1 を削除。DDR0_VAA を追加。J3 を修正) |

|      |            | 13      | 表 1.3-1 V2NEVK 仕様<br>項目:eMMC の仕様を修正                                                                  |

|      |            | 16~18   | 1.3.5 端子機能一覧 追加                                                                                      |

|      |            | 2. 操作手順 |                                                                                                      |

|      |            | 22      | 表 2.2-1 DSW1 接続先および機能<br>スイッチ No.2, 3 の RZ/V2N ピンを修正                                                 |

|      |            | 3. 配置   |                                                                                                      |

|      |            | 27      | 表 3.2-1 RZ/V2N Evaluation Board 部品リスト<br>部品記号:U39 を削除                                                |

RZ/V2N Evaluation Board Kit (Secure type) ハードウェアマニュアル

発行年月日 2024年11月22日 Rev.1.00

2025年02月28日 Rev.1.10

発行 ルネサス エレクトロニクス株式会社

〒135-0061 東京都江東区豊洲3-2-24 (豊洲フォレシア)

RZ/V2N Evaluation Board Kit (Secure type)