# System Release Package

User's Manual: Hardware and Software

Renesas Microprocessor RZ G/V/H Series

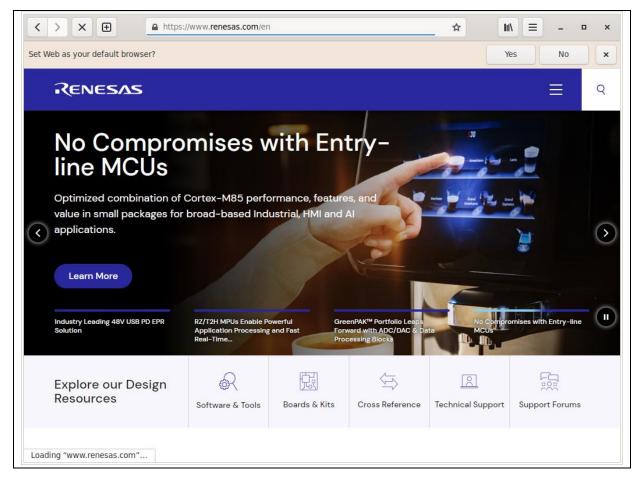

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

### **Trademarks (continued)**

For the "Cortex" notation, it is used as follows;

- Arm® Cortex®-A55

- Arm® Cortex®-M33

Note that after this page, they may be noted as Cortex-A55 and Cortex-M33 respectively.

Examples of trademark or registered trademark used in the RZ/G2L SMARC Module Board RTK9744L23C01000BE User's Manual: Hardware;

CoreSight™: CoreSight is a trademark of Arm Limited.

MIPI®: MIPI is a registered trademark of MIPI Alliance, Inc.

eMMC™: eMMC is a trademark of MultiMediaCard Association.

Note that in each section of the Manual, trademark notation of ® and TM may be omitted.

All other trademarks and registered trademarks are the property of their respective owners.

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

#### 1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

#### 2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

- 3. Input of signal during power-off state

- Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

- 4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

#### Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

# Renesas RZ Family / RZ/G/V/H Series

# Renesas System Release Package

#### Introduction

This user manual describes the unified system release package. The system release package contains supported hardware and software.

The result is a consistent experience across the different platforms. This streamlines the development effort for user applications.

### **Package Contents**

The system release package contains the following:

- Multiple Images that are geared to general baseline use-cases.

- Yocto build scripts.

- Host side tools.

- Environmental files.

- SDKs for all images

- Documentation which includes

- User manual

- · Copyright & License information

### **Features**

The following are the general features of the system release package.

- Architected to support multiple platforms by the same image and tools over time.

- Common frameworks

- Open-source packages using GPLv2 and GPLv3 packages

- Carefully considered base images that allow for a quick starting point to build a product.

- Complete set of features working out of the box.

- Seamless out of box experience.

- Automated Yocto build scripts that can rebuild the entire package with only a few commands.

- Host tools to flash the firmware in multiple processes.

- Tools supporting both Linux and Windows workflows.

- · Docker friendly build scripts.

- Extensive documentation covering the hardware, software and application development and deployment.

### **Contents**

| Introduction                                                  | 5  |

|---------------------------------------------------------------|----|

| Package Contents                                              | 5  |

| Features                                                      | 5  |

| Glossary                                                      | 12 |

| 1. Overview                                                   | 12 |

| 1.1 Supported Distributions                                   | 12 |

| 1.1.1 Yocto Images                                            | 12 |

| 1.1.2 Renesas Custom Images                                   | 13 |

| 1.1.3 Ubuntu Images                                           | 13 |

| 1.2 Supported Platforms                                       | 14 |

| 2. Introduction                                               | 15 |

| 2.1 Package Hierarchy                                         | 16 |

| 2.2 Source Repositories                                       |    |

| 3. Required Resources                                         | 20 |

| 3.1 Development Tools and Software                            |    |

| 3.2 Hardware                                                  |    |

| 3.2.1 Common Hardware Requirements                            |    |

| 3.2.2 Board-Specific Hardware                                 |    |

| 4. Quick Start                                                | 22 |

| 4.1 SD-MMC Card Flashing                                      | 22 |

| 4.2 RZ/G2L-SBC                                                | 23 |

| 4.2.1 Hardware Requirements                                   | 23 |

| 4.2.2 Essential Hardware Setup                                | 23 |

| 4.2.3 Complete Hardware Setup                                 |    |

| 4.2.4 Booting                                                 |    |

| 4.2.5 Known Hardware and Functional Limitations on RZ/G2L-SBC | 25 |

| 4.3 RZ/G2L-EVK and RZ/V2L-EVK                                 | 27 |

| 4.3.1 Hardware Requirements                                   | 27 |

| 4.3.2 Essential Hardware Setup                                |    |

| 4.3.3 Complete Hardware Setup                                 |    |

| 4.3.4 Booting                                                 |    |

| 4.3.5 Known Hardware and Functional Limitation                |    |

| 4.4 RZ/V2H-EVK                                                |    |

|                                                               |    |

| 4.4.1 Hardware Requirements               | 33          |

|-------------------------------------------|-------------|

| 4.4.2 Essential Hardware Setup and Boo    | ting33      |

| 4.4.3 Complete Hardware Setup             | 35          |

| 4.4.4 Booting                             | 36          |

| 4.4.5 Known Hardware and Functional Li    | mitations37 |

| 5. General Operational Flow               | 38          |

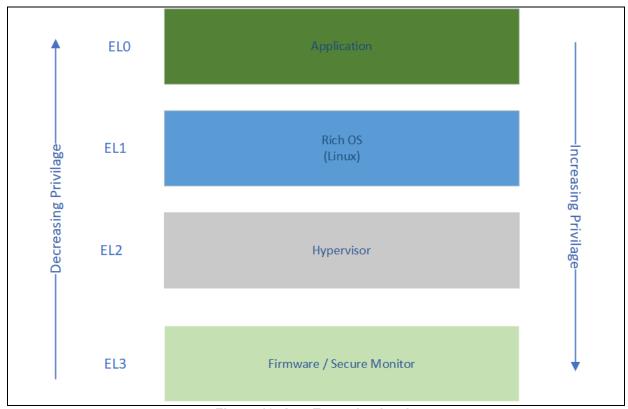

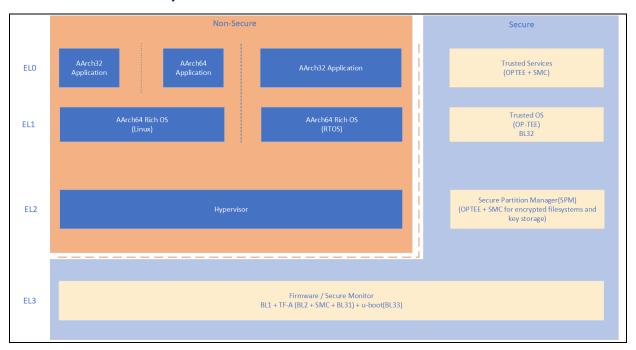

| 5.1 Arm Exception Levels                  | 38          |

| 5.2 Secure and Non-Secure Runtime         | 39          |

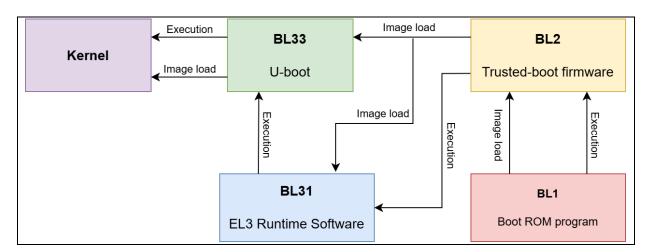

| 5.3 Arm Trusted Firmware-A (TF-A)         | 39          |

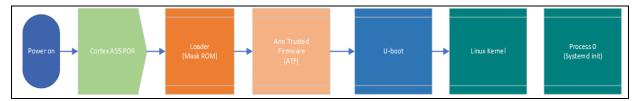

| 5.3.1 Components of Boot                  | 39          |

| 5.3.2 Trusted Boot Flow                   | 42          |

| 6. Build System                           | 43          |

| 6.1 Build Host Environment Setup          | 43          |

| 6.2 Builders                              | 45          |

| 6.2.1 rz_builder.sh                       | 45          |

| 6.2.2 Ubuntu builder                      | 47          |

| 6.3 Yocto OE Build                        | 49          |

| 6.3.1 Initiate Yocto Build                | 49          |

| 6.3.2 Collect the Build Output            | 49          |

| 6.4 Ubuntu OE Build                       | 54          |

| 6.4.1 Ubuntu Build Host Environment Set   | up54        |

| 6.4.2 Initial Ubuntu Build                | 56          |

| 6.4.3 Collect the Build Output            | 57          |

| 7. Programming / Flashing Images          | 62          |

| 7.1 Prerequisites                         | 63          |

| 7.1.1 Linux Setup                         | 63          |

| 7.1.2 Windows Setup                       | 63          |

| 7.2 Hardware Setup                        | 64          |

| 7.2.1 RZ/G2L-SBC                          | 65          |

| 7.2.2 RZ/G2L-EVK and RZ/V2L-EVK           | 65          |

| 7.2.3 RZ/V2H-EVK                          | 66          |

| 7.3 Universal Flashing Script             | 66          |

| 7.3.1 flash_images.json – File Overview a | and Usage67 |

| 7.3.2 Usage and Flashing Operations       | 69          |

| 7.3.3 Flashing the Bootloader             | 73          |

| 7.3.4 Flashing the uLoad-bootloader       | 74          |

| 7.3.5 Flasing the SD Card Image           | 77          |

| Accessing Supported Features                                   | 80  |

|----------------------------------------------------------------|-----|

| 8.1 Supported Features in Yocto Images                         | 80  |

| 8.1.1 Common Yocto Features                                    | 80  |

| 8.1.2 RZ/G2L-SBC Yocto Features                                | 91  |

| 8.2 Supported Features in Ubuntu Images                        | 109 |

| 8.2.1 Accessing Supported Features in Ubuntu LXDE              | 109 |

| 8.2.2 Accessing Supported Features in Ubuntu Core              | 123 |

| 9. Network Boot and TFTP                                       | 126 |

| 9.1 TFTP Server Setup                                          | 126 |

| 9.2 NFS Server Setup                                           | 127 |

| 9.3 U-Boot DHCP IP Configuration                               | 127 |

| 9.4 -TFPT Boot                                                 | 128 |

| 10. Using SSH and SCP for Remote Access and File Transfers     |     |

| 10.1 Differences Between Dropbear and OpenSSH                  | 132 |

| 10.2 Using OpenSSH                                             | 132 |

| 10.3 SSH Access                                                | 133 |

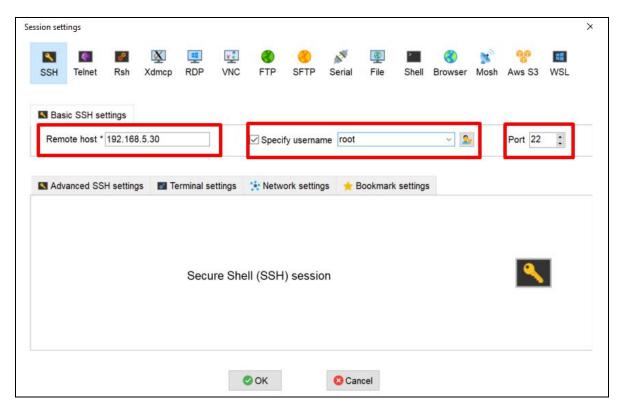

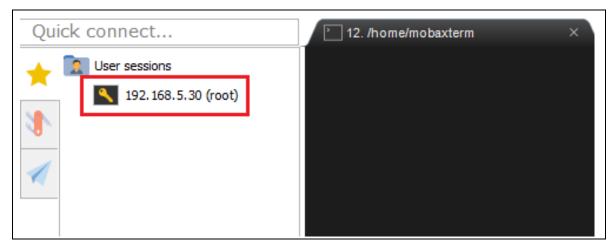

| 10.3.1 SSH from Windows Host                                   | 133 |

| 10.3.2 SSH from Linux Host                                     | 134 |

| 10.4 SCP (Secure copy protocol)                                | 135 |

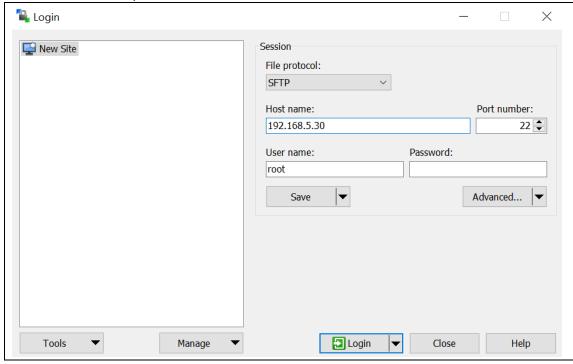

| 10.4.1 SCP from Windows Host                                   | 135 |

| 10.4.2 SCP from Linux Host                                     | 136 |

| 11. Building the eSDK                                          | 137 |

| 12. Application Building, Packaging, and Running               | 139 |

| 12.1 How to extract the eSDK                                   | 139 |

| 12.2 Build a sample application using the eSDK with CMake      | 140 |

| 12.3 Package Programs with Cpack                               | 142 |

| 12.3.1 Package a C Program                                     | 142 |

| 12.3.2 Package a Python Program                                | 145 |

| 12.4 Run Sample Applications                                   | 148 |

| 12.5 Install and Run Debian application packages by using DPKG | 148 |

| 12.6 Using devtool in the Yocto eSDK                           | 150 |

| 12.6.1 Overview                                                | 150 |

| 12.6.2 Prerequisites                                           | 150 |

| 12.6.3 Common Usage Scenarios                                  | 150 |

| 13. Remote Debugging using GDBServer                           |     |

| 13.1 Prepare GDB on the Host Machine                           | 154 |

| 13.2 Install GDBServer on RZ                                   | 154 |

| 13.3 Remote Debugging Example                     | 155 |

|---------------------------------------------------|-----|

| 13.3.1 Remote Debugging on CLI                    | 155 |

| 13.3.2 Remote Debugging on Visual Studio Code     | 158 |

| 13.3.3 Remote Debugging on Eclipse IDE            | 162 |

| 13.4 Postmortem Analysis Example                  | 167 |

| 13.4.1 Postmortem Analysis on CLI                 | 167 |

| 13.4.2 Postmortem Analysis on Visual Studio Code  | 169 |

| 13.4.3 Postmortem Analysis on Eclipse             | 171 |

| 14. Functional Overview                           | 173 |

| 14.1 MPU Architecture                             | 173 |

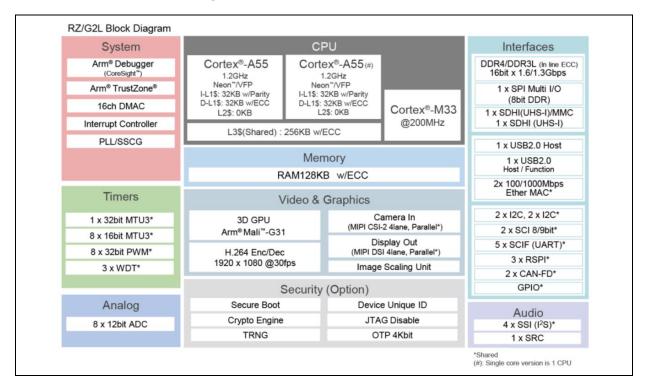

| 14.1.1 RZ/G2L                                     | 173 |

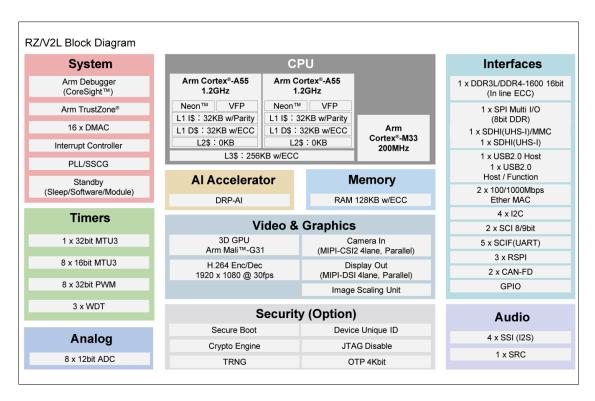

| 14.1.2 RZ/V2L                                     | 173 |

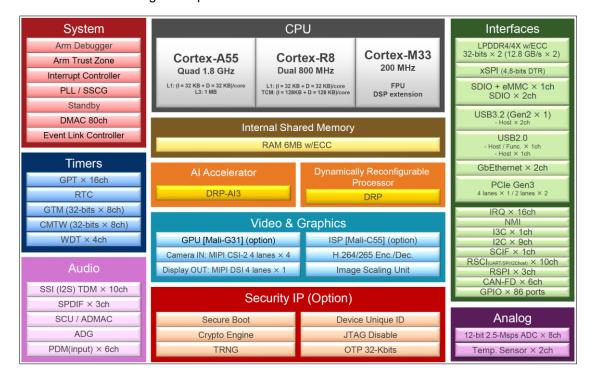

| 14.1.3 RZ/V2H                                     | 174 |

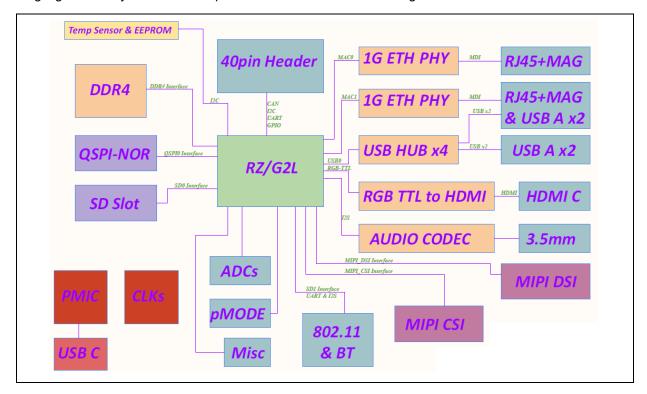

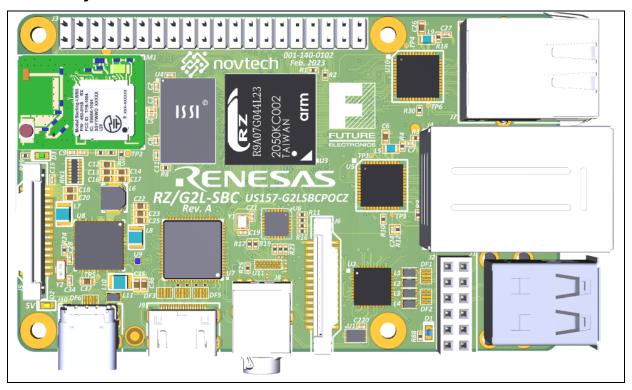

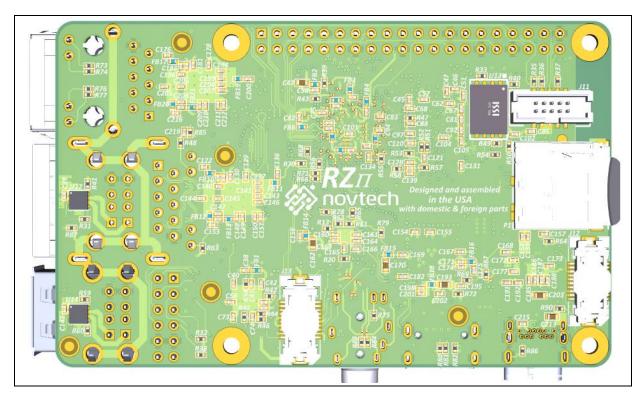

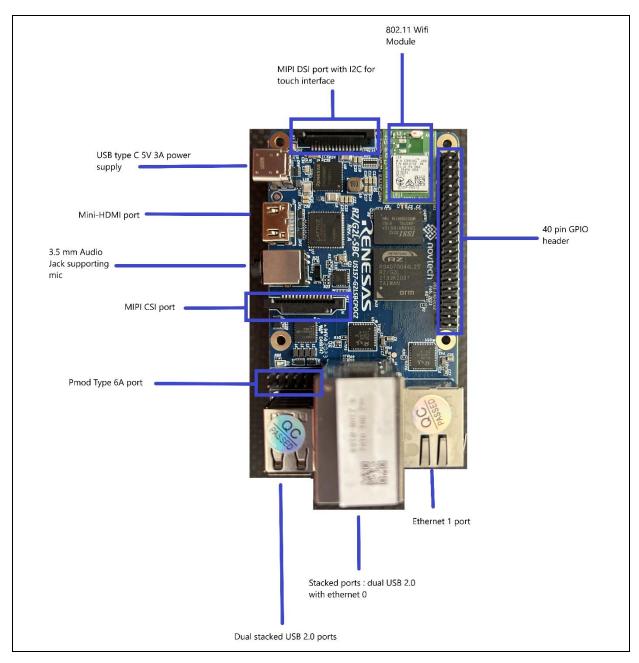

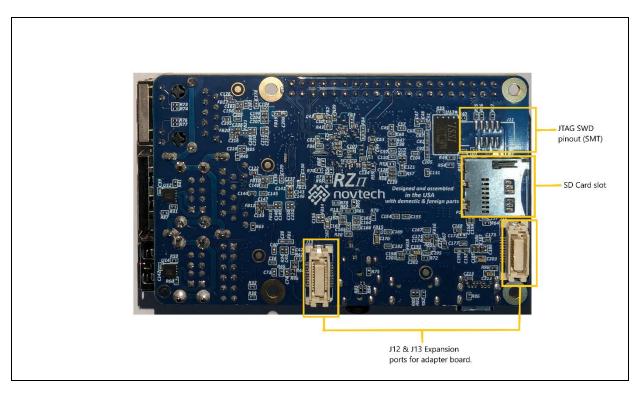

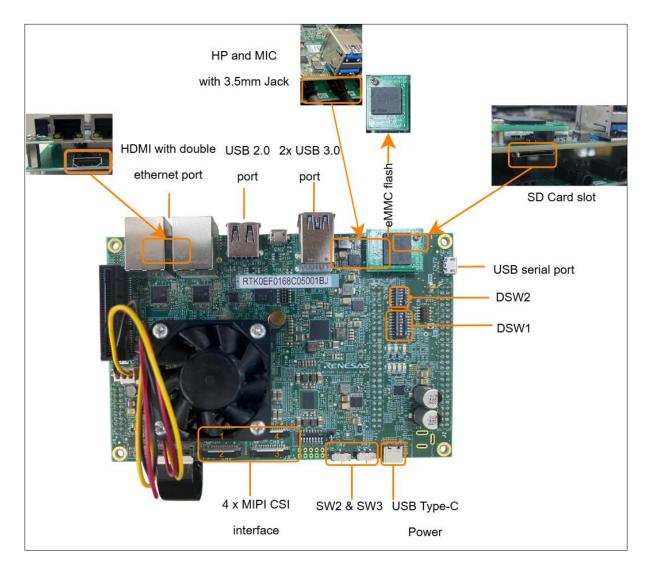

| 14.2 RZ/G2L-SBC Board                             | 175 |

| 14.2.1 Overview                                   | 176 |

| 14.2.2 Physical View                              | 177 |

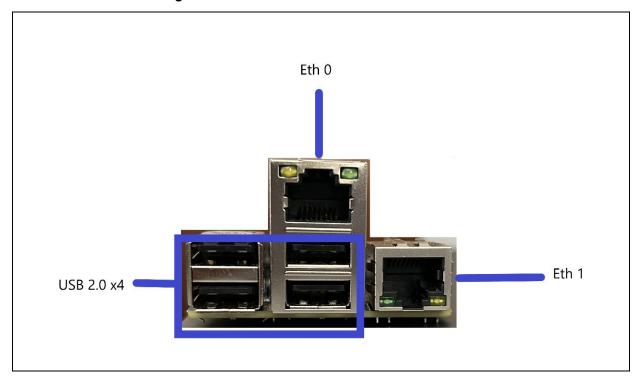

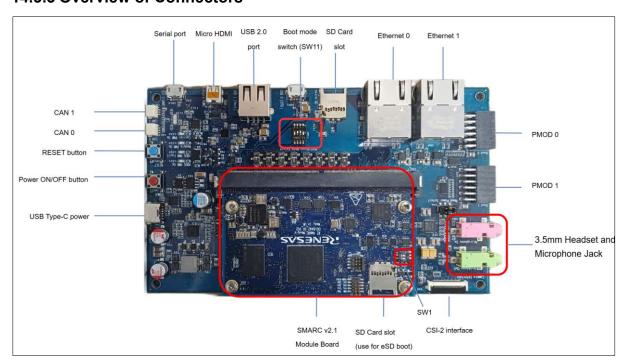

| 14.2.3 Overview of Connectors                     | 178 |

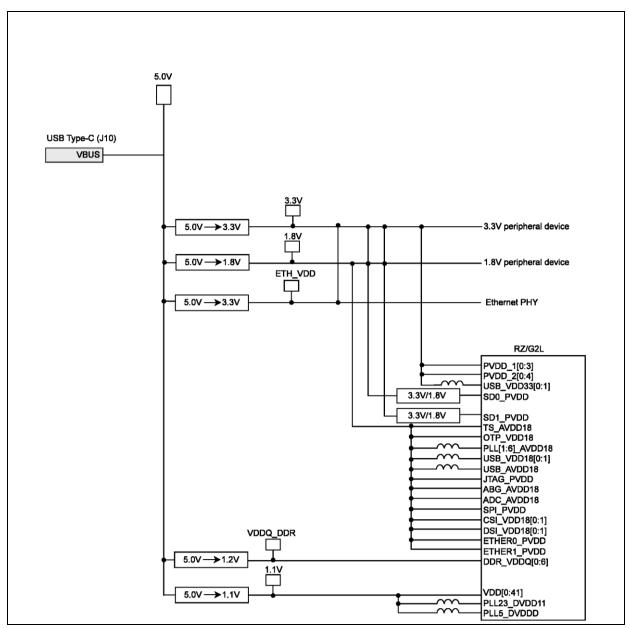

| 14.2.4 Power Supply                               | 181 |

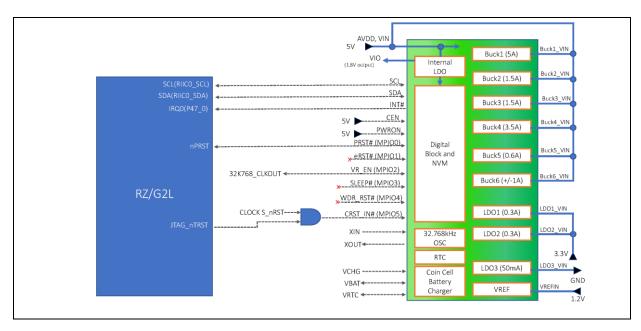

| 14.2.5 Power Management Integrated Circuit- PMIC  | 182 |

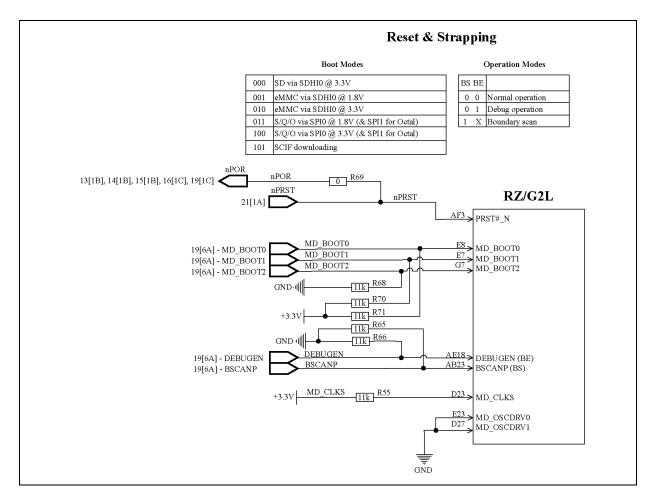

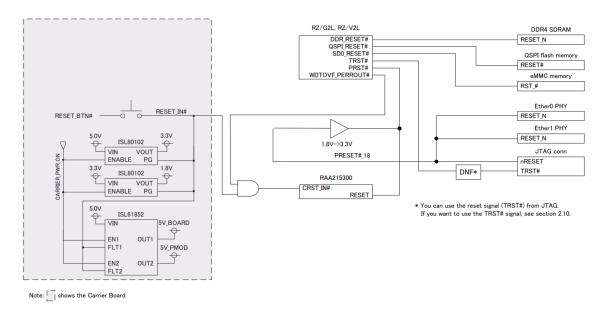

| 14.2.6 RESET Control                              | 183 |

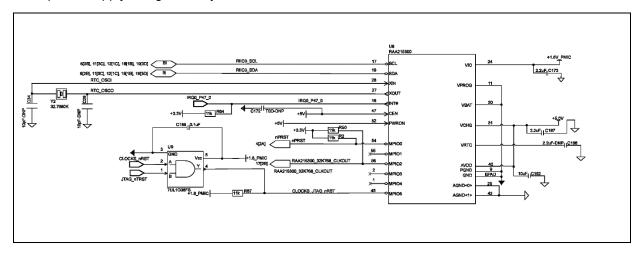

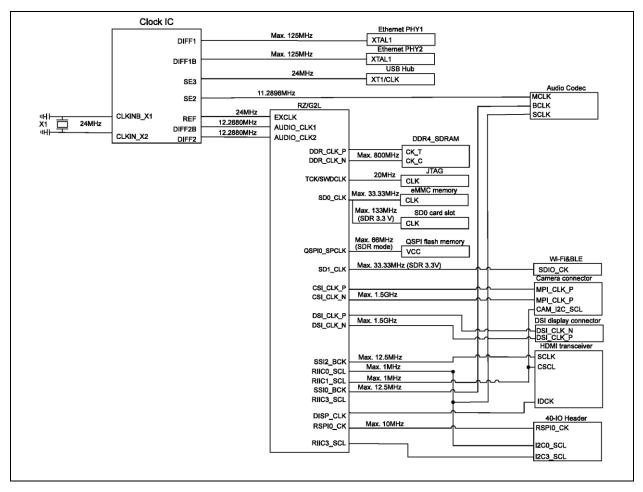

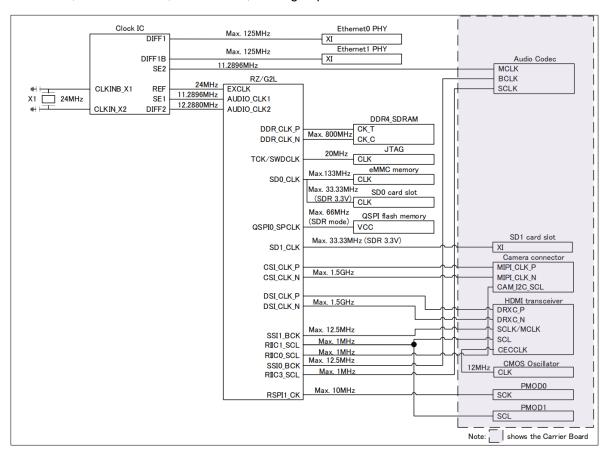

| 14.2.7 Clock Configuration                        | 184 |

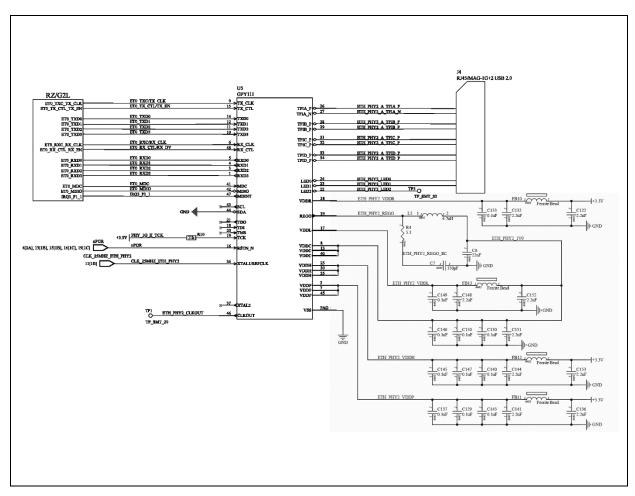

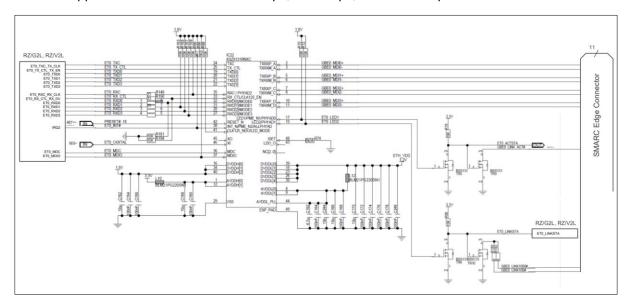

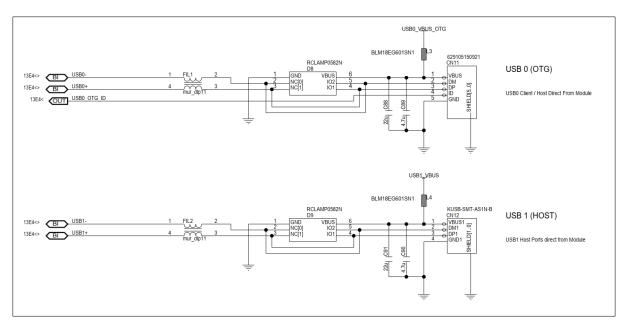

| 14.2.8 Peripheral Interface                       | 185 |

| 14.2.9 Memory                                     | 194 |

| 14.2.10GPIO Internals                             | 196 |

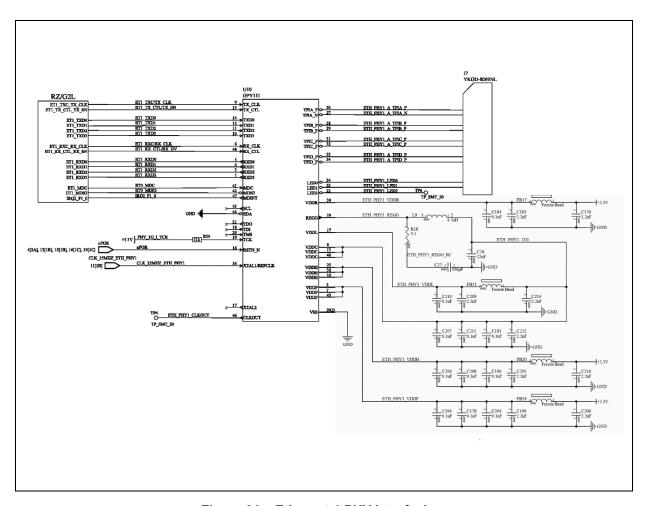

| 14.3 RZ/G2L-EVK & RZ/V2L-EVK Board                | 198 |

| 14.3.1 Overview                                   | 198 |

| 14.3.2 Layout Parts                               | 199 |

| 14.3.3 Overview of Connectors                     | 200 |

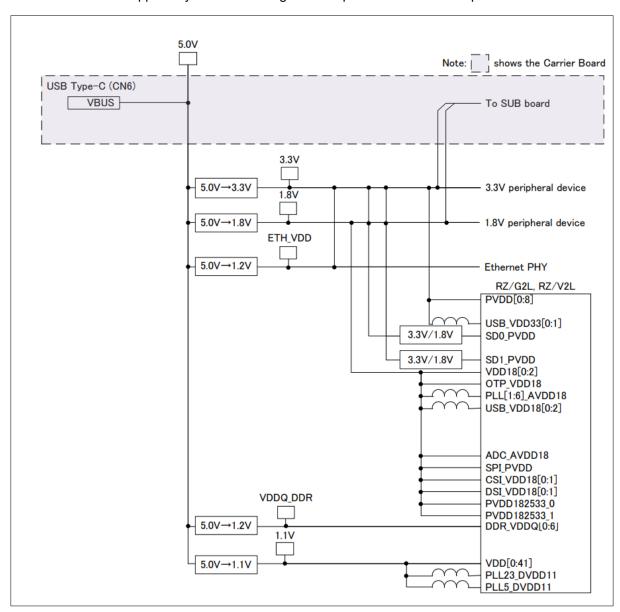

| 14.3.4 Power Supply                               | 200 |

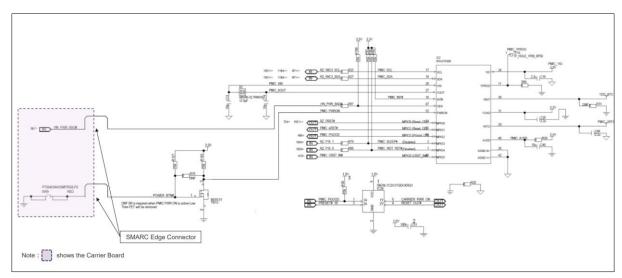

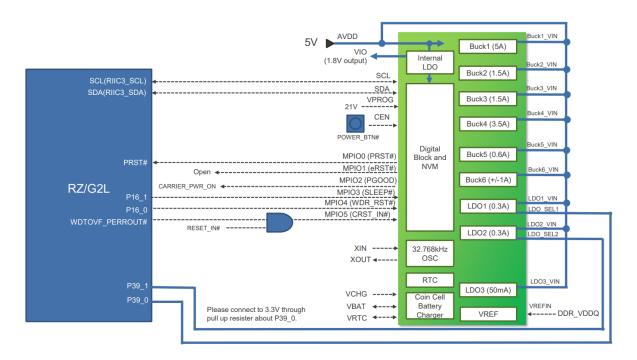

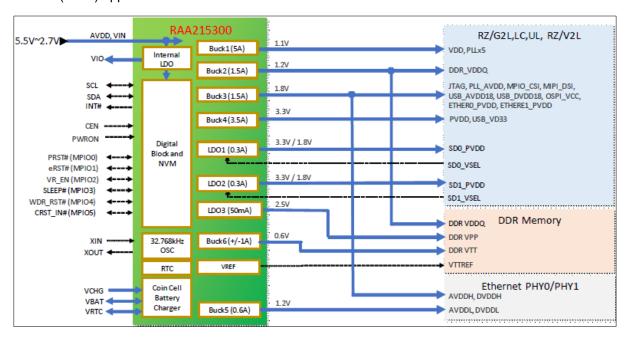

| 14.3.5 Power Management Integrated Circuit (PMIC) | 202 |

| 14.3.6 RESET Control                              | 203 |

| 14.3.7 Clock Configuration                        | 204 |

| 14.3.8 Peripheral Interface                       | 205 |

| 14.3.9 Memory                                     | 211 |

| 14.4 RZ/V2H-EVK Board                             |     |

| 14.4.1 Overview                                   | 213 |

| 14.4.2 Part Layout                                | 216 |

| 14.4.3 Overview of Connectors                     |     |

| 14.4.4 Power Supply                               | 218 |

|                                                   |     |

| 14.4.5 Power Management Integrated Circuit (PMIC)                  | 219 |

|--------------------------------------------------------------------|-----|

| 14.4.6 RESET Control                                               | 219 |

| 14.4.7 Clock Configuration                                         | 220 |

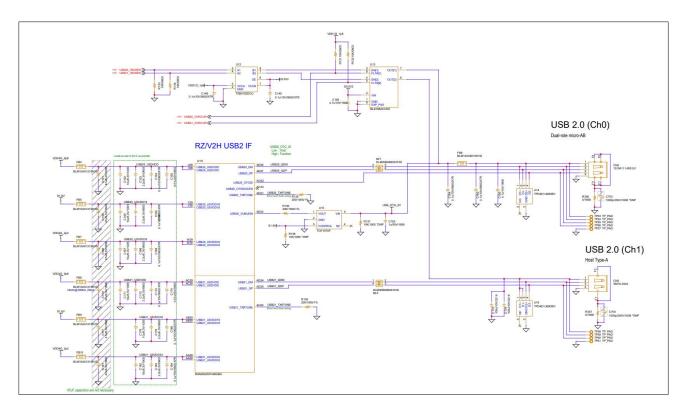

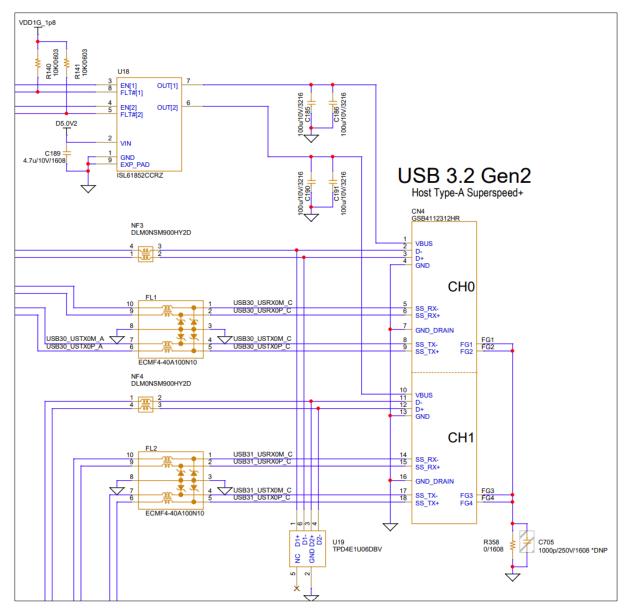

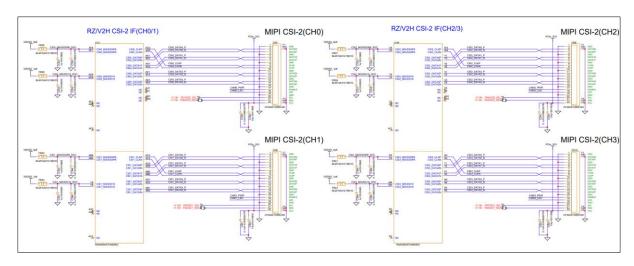

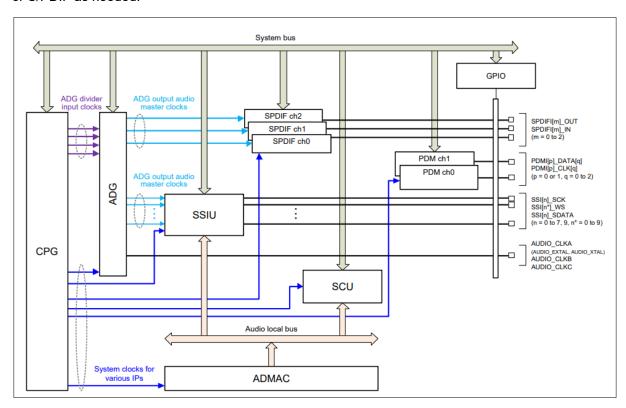

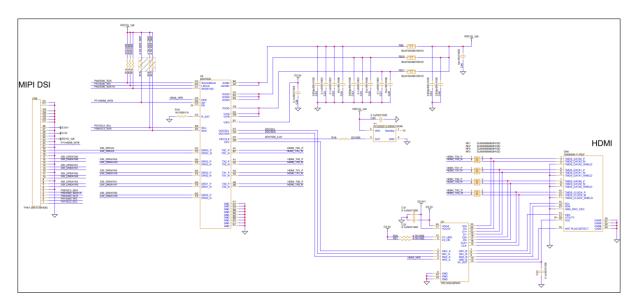

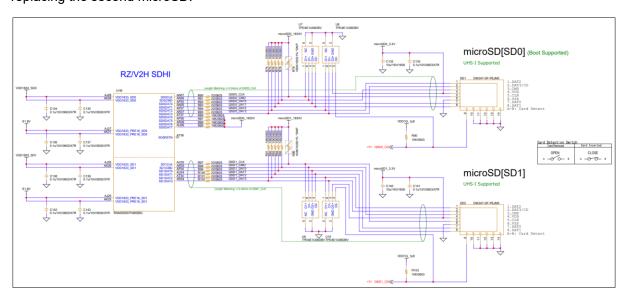

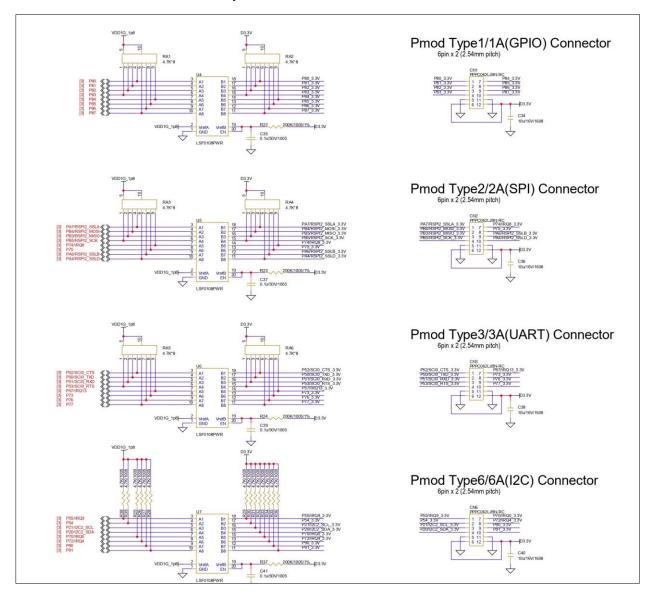

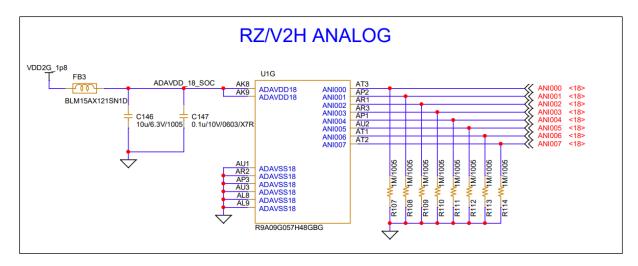

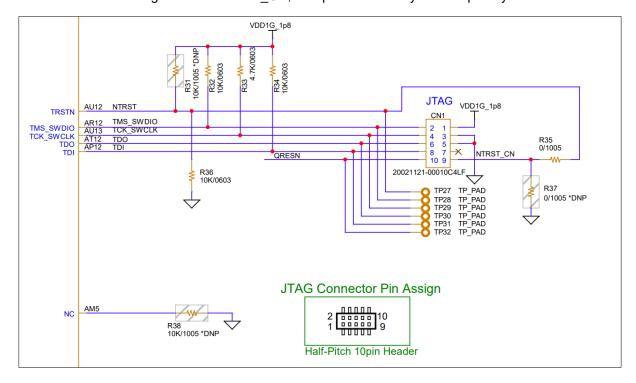

| 14.4.8 Peripheral Interface                                        | 222 |

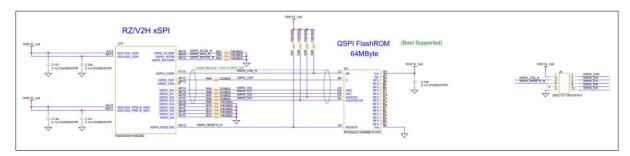

| 14.4.9 Memory                                                      | 229 |

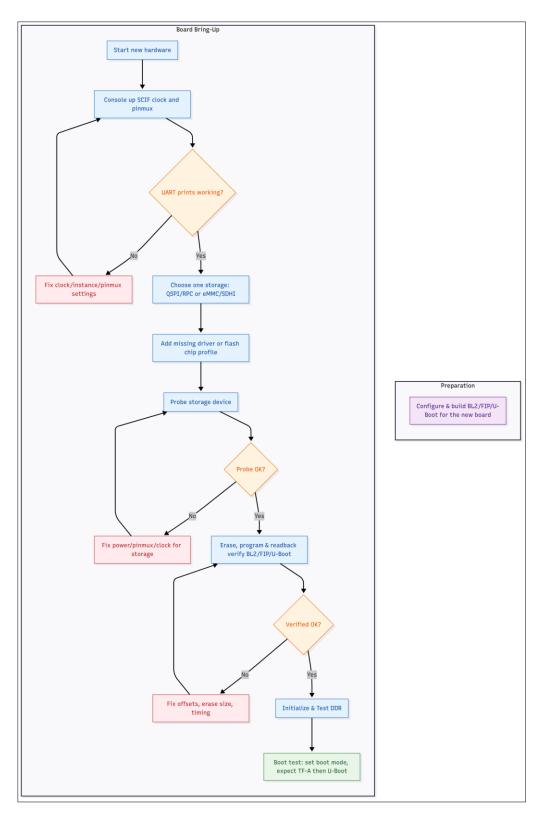

| 15. Adding a New Board (Porting Guide)                             | 231 |

| 15.1 Board Identification JSON Specification                       | 231 |

| 15.1.1 JSON Field Description                                      | 231 |

| 15.1.2 Build and Flash Procedure                                   | 233 |

| 15.2 Flash Writer                                                  | 236 |

| 15.2.1 What must be ported for a new board                         | 236 |

| 15.2.2 DDR bring-up for the Flash Writer                           | 238 |

| 15.2.3 Add a new SPI Flash                                         | 243 |

| 15.3 TF-A (BL2/BL31)                                               | 245 |

| 15.3.1 Firmware Configuration Framework                            | 245 |

| 15.3.2 Tool Location and Layout                                    | 246 |

| 15.3.3 Prerequisites                                               | 246 |

| 15.3.4 Adding a New Board                                          | 247 |

| 15.3.5 Usage                                                       | 248 |

| 15.4 U-Boot (BL33)                                                 | 249 |

| 15.4.1 Initialization model                                        | 249 |

| 15.4.2 How soc_id and board_id are used                            | 250 |

| 15.4.3 Steps to add a board                                        | 250 |

| 15.4.4 Board-specific code hooks                                   | 252 |

| 15.4.5 Adding BSP Drivers                                          | 254 |

| 15.5 Linux kernel                                                  | 254 |

| 15.5.1 Steps to add a board                                        | 254 |

| 15.5.2 Kernel Device Tree Selection                                | 255 |

| 16. Appendix                                                       | 257 |

| 16.1 Factory Firmware Flashing Using Serial Downloader (SCIF) Mode | 257 |

| 16.1.1 RZ/G2L-SBC                                                  | 257 |

| 16.1.2 RZ/G2L-EVK and RZ/V2L-EVK                                   | 257 |

| 16.1.3 RZ/V2H-EVK                                                  | 259 |

| 16.2 Boot Mode Reference (Non-SCIF)                                | 260 |

| 16.2.1 RZ/G2L-EVK & RZ/V2L-EVK                                     | 260 |

| 16.2.2 RZ/V2H-EVK                                                  | 260 |

| 16.3 Prepare the eMMC root filesystem                              | 262 |

| 16.4 How To Get the Console After Bootup                           | 265 |

| 16.5 BSP Interfaces                                                    | 265   |

|------------------------------------------------------------------------|-------|

| 17. Troubleshooting                                                    | 266   |

| 17.1 Unable To Support Scripts for Bootloader/Firmware Flashing on Lin | ux266 |

| 17.2 Flashing Tools Failing Halfway                                    | 266   |

| 17.3 DHCP Failure                                                      | 266   |

| 17.4 'Ifconfig' doesn't list the Wi-Fi interface                       | 266   |

| 17.5 IP Configuration                                                  | 266   |

| 17.6 Stuck in U-boot with error "Bad Linux ARM64 Image magic!"         | 266   |

| 18. References                                                         | 268   |

| 18.1 Git Repositories                                                  | 268   |

| 18.2 RZ/G MPU Series                                                   | 268   |

| 18.3 RZ/V MPU Series                                                   | 268   |

| 18.4 External Resources                                                | 268   |

| 18.4.1 QT Development                                                  | 268   |

| 18.4.2 Yocto Project                                                   | 268   |

| 18.4.3 Linux Kernel Documentation                                      | 268   |

| 18.4.4 Arm Developer Documentation                                     | 268   |

| 18.4.5 JEDEC DDR4                                                      | 269   |

| 18.4.6 PMOD Specification                                              | 269   |

| 18.4.7 Essential Linux Tutorial                                        | 269   |

| 18.4.8 Packaging                                                       | 269   |

| 18.4.9 Using Extensible SDK                                            | 269   |

| 18.4.10Install Eclipse IDE                                             | 269   |

| 18.4.11Linux Kernel Development                                        | 269   |

| 18.4.12Linux Kernel Driver Development                                 | 269   |

| Revision History                                                       | 270   |

# Glossary

| Terms                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 802.11 - Wi-Fi                                                   | The technical name of the standard specification for Wi-Fi is 802.11. This is also the working group that develops and maintains the standards for Wi-Fi that everyone conforms to.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ADC – Analog to digital converter                                | A hardware unit that converts an input analog signal to a digital value by measuring its immediate voltage at a fixed resolution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BSP – Board<br>Support Package                                   | BSP is an essential software package that has bootloaders, Linux kernel, a minimal user space and programming tools, allowing the device to boot. This core software allows the system to boot into an operating system, enables all the features and allows application development.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CAN – Controller<br>area network                                 | This is a standardized communication protocol used widely on automotive and aerospace systems. It connects various ECU's known as nodes and uses two wires / lines as a pair carrying differential signals. This method of signaling allows long length cables to interface different systems on the machine with reliable signals. The CAN protocol has multiple specifications and is an ISO standard. It supports flexible data rates reaching as high as 8Mbps. Most automobiles have CAN networks in them, and it is a part of OBD-2 specification which is mandatory law in most of the world for automotive machines like cars.                                                                                                                                                                                                                                                                        |

| DAC – Digital to analog converter                                | A hardware unit that takes digital value and exerts a corresponding analog voltage on an output line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Firmware                                                         | For the scope of this document, the term 'firmware' refers to the low-level software that runs before an OS takes over. This includes arm trust zone, optee & u-boot at the very least. It also refers to the standalone binaries that run on the embedded real-time core like the CM33.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I2C - Inter<br>Integrated circuit<br>protocol:                   | This is a communication protocol used to implement digital communication between two devices (chips / board) using only two wires. It is a standardized specification and is used widely to implement low to medium data rate data transfers both among devices on the same circuit board as well as external add on peripheral boards. I2C can be implemented across a few meters in distance. I2C is half duplex meaning only one device can communicate at a time. Speeds range from 100 Kbps to 3Mbps while 100 / 400 Kbps are the typical operating mode. The other major advantage of this protocol is that it allows many devices to be on the same two lines reducing the cost of the interfacing. This is ideal when there are many devices like sensors that transfer limited amounts of data periodically. I2C can support up to 127 independent directly addressable devices on the same channel. |

| IEEE- Institute of<br>Electrical and<br>Electronics<br>Engineers | IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. It is a major technical organization covering vast fields of engineering and a major standards organization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCU – Micro<br>controller unit                                   | A micro controller unit is a self-contained unit that has the core processing as well as core memory within the same device. It often contains the core software programmed into the chip itself. This allows the device to start executing with minimal external devices / circuitry. Some microcontrollers can be powered on a mere breadboard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MPU – Micro<br>processing unit                                   | An MPU is a processing unit: a CPU that contains only the processing core and interfaces for external peripherals. A microprocessor is usually a powerful CPU in its class. However, it requires a very large number of external circuitries to achieve its functionality like external memory, disk drives, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PMIC – Power management IC                                       | This is a specific chip on the board that manages multiple power supply lines at various levels. It manages the respective supplies along with sequences which control power on and power off cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SBC – Single<br>board computer          | It is a standard term that means a tiny computer in the form factor of a single circuit board usually just inches in area. This board is self-sufficient in every way and can give you a usable computer with just a power supply, keyboard, mouse, and display.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SiP – System in<br>Package              | SiP is a device where multiple silicon IP's are combined to form a single device. It is one of the densest chips where the external devices like flash memory, DDR RAM and even Wi-Fi module are all packaged into a single chip. These are used in very niche application that require ultra small size and low thermal requirement.                                                                                                                                                                                                                                                                                                                                                                                     |

| SoC- System on<br>Chip                  | A system on chip is a complete hardware platform packaged on to a single chip. It contains the CPU, internal fast memory, interrupt controllers, pin controllers, ROM memory, and a few other peripherals and sensors; all packaged into the same IC. An SoC despite the high level of integration does not necessarily power on and run by itself. Microcontrollers are often independent SoC's that can work on their own. However, SoC's often combine MPU's and MCU's into the same chip. This allows very powerful systems to be built in a compact form factor but requires external supporting peripherals like DDR RAM and flash memory and power management IC's.                                                |

| SMARC                                   | SMARC is a standardized interface to connect a core module to a common platform carrier board. It's basically a connector with specific pin outs. It allows the reuse of the carrier board to support a variety of modules for evaluation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SPI - Serial<br>Peripheral<br>interface | SPI is another standard interface used to interface other devices on the board or attaching peripheral boards. It specifies 3 wires / lines to achieve fast full duplex data transfer. Two devices can send / receive data at the same time in this protocol. The protocol is also a high-speed protocol where typical operating speeds start at 5Mbps and go over 50Mbps. This high speed allows interfacing high speed devices like memory, Wi-Fi, subsystems made of independent microcontrollers, etc. While only 3 lines are needed to interface two devices, a fourth line is used as a device selector allowing multiple devices to share the same interface. However, only two devices may communicate at a time. |

#### 1. Overview

The Renesas System Release Package is a unified software package that aims to provide an easy-to-use yet comprehensive software platform for the Renesas RZ series of MPU-based boards. It aims to provide fully functional base images for supported reference designs, along with easy-to-use development and programming tools that allow the user to quickly get started on their application development. This package aims to provide a standardized and familiar workflow for a similar experience across a variety of Renesas RZ MPU-based product platforms.

This package provides comprehensive documentation, Quick start guides, multiple Linux-based distribution images, automated tools and scripts, and an ongoing expansion of supported products.

### 1.1 Supported Distributions

The System Release package supports a set of both Yocto images and custom images to enable the user to start quickly on their embedded end application. The large collection of images in prebuilt format provides a wide set of capabilities. This release focuses on Yocto images.

### 1.1.1 Yocto Images

This section lists the standard Yocto images, offering a variety of configurations that cater to different embedded use cases. From a minimal bootable environment to fully graphical systems, these images provide the essential building blocks for embedded Linux development.

| Distribution  | Image file         | Version           | Description                                                                                                                                                             |

|---------------|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Yocto minimal | core-image-minimal | styhead-<br>5.1.4 | A basic image that contains the minimal set of components required to boot the device. It focuses on essential system functions without extra tools or features.        |

| Yocto BSP     | core-image-bsp     | styhead-<br>5.1.4 | Extends core-image-minimal with additional utilities and tools, providing a lightweight environment for system validation, hardware diagnostics, and basic development. |

| Yocto weston  | core-image-weston  | styhead-<br>5.1.4 | A standard graphical image with Wayland and Weston support for embedded GUI applications.                                                                               |

Table 1. Yocto images

### 1.1.2 Renesas Custom Images

This section presents Renesas-specific custom images, which are customized and optimized for Renesas products. These images offer specialized features, including fast booting and tailored environments for both graphical and CLI-based applications. Table 2. Renesas custom images

| Distribution                    | Image file                    | Version           | Description                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|-------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Renesas CLI Base                | renesas-core-image-cli        | styhead-<br>5.1.4 | Based on core-image-bsp, this image offers a CLI environment for Renesas hardware development without graphical interfaces. Besides the useful tools inherited from the core-image-bsp, this image also contains new packages for SBC (Single Board Computer) development. For example, package managers (apt, dpgk), network utilities for Bluetooth, Wi-Fi. |

| Renesas<br>Quickboot CLI        | renesas-quickboot-cli         | styhead-<br>5.1.4 | This image has the same system functionality as the renesas-core-image-cli but with Quickboot enabled, allowing for faster boot times and efficient system validation on a CLI environment.                                                                                                                                                                   |

| Renesas Weston<br>(Qt6)         | renesas-core-image-<br>weston | styhead-<br>5.1.4 | Renesas customized core image based on the core-image-weston, with Qt6 framework support (no QT demo apps included). This image offers a full graphical environment for Renesas hardware development and all the useful tools from the renesas-core-image-cli.                                                                                                |

| Renesas<br>Quickboot<br>Wayland | renesas-quickboot-<br>wayland | styhead-<br>5.1.4 | This image has the same system functionality as the renesas-core-image-weston but with Quickboot enabled, allowing for faster boot times and efficient system validation on a graphical environment.                                                                                                                                                          |

Note: Quickboot is a trade term that refers to the specific optimizations that are performed to achieve ultra-low start-up times in specific images. Depending on the board architecture, the startup time can be as low as 2s. While there is no assurance of the startup time in these images for every platform, these images are the most optimized on our platforms.

### 1.1.3 Ubuntu Images

This section presents custom Ubuntu-based images tailored for embedded systems, offering a variety of configurations to suit both headless and graphical environments. These images are optimized for performance and ease of use, providing a solid foundation for deploying embedded applications on Renesas platforms.

Table 3. Renesas Ubuntu images

| Distribution | Image file        | Version               | Description                                                                                                                                                                                                       |

|--------------|-------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ubuntu Core  | ubuntu-core-image | ubuntu-<br>base-24.04 | A minimal, headless Ubuntu image tailored for embedded systems.                                                                                                                                                   |

| Ubuntu LXDE  | ubuntu-lxde-image | ubuntu-<br>base-24.04 | A lightweight Ubuntu image featuring the LXDE desktop environment, providing a graphical interface while maintaining low resource consumption. This image also includes Qt framework support for GUI development. |

# 1.2 Supported Platforms

**Table 4. Supported Platforms**

| Platform   | MPU    | OPN                                        | Description                            |

|------------|--------|--------------------------------------------|----------------------------------------|

| RZ/G2L-SBC | RZ/G2L | US157-G2LSBCPOCZ                           | RZ/G2L-based Pi-compatible SBC.        |

| RZ/G2L-EVK | RZ/G2L | RTK9744L23S01000BE                         | Evaluation Board Kit for RZ/G2L MPU    |

| RZ/V2L-EVK | RZ/V2L | RTK9754L23S01000BE                         | Evaluation Board Kit for RZ/V2L MPU    |

| RZ/V2H-EVK | RZ/V2H | R9A09G057H48GBG#AC0<br>R9A09G057H48GBG#BC0 | Evaluation Board Kit for RZ/V2H<br>MPU |

### 2. Introduction

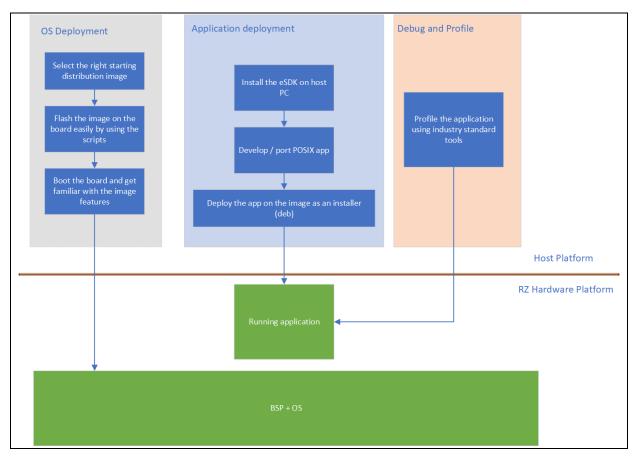

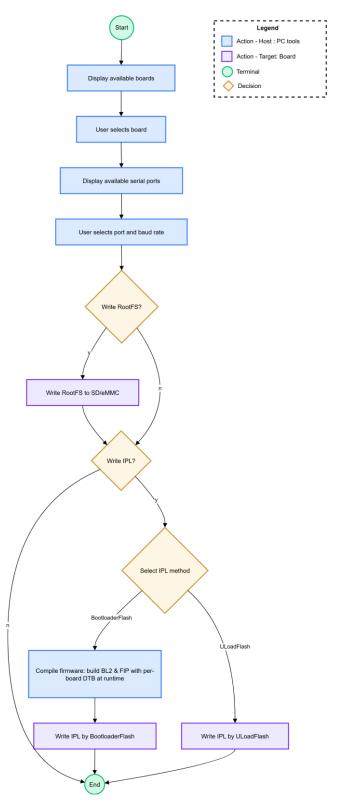

The system release package provides a unified and consistent experience across multiple RZ platforms by providing prebuilt binaries that are as universal as possible, along with all the tools and documentation necessary to work with these platforms. To enable the platforms, the package contains a variety of images that provide the most common starting points for embedded application development. The workflow envisioned is provided below.

Figure 1. Embedded application workflow for RZ System release package

The package also comes with automated scripts that let users rebuild the entire package on the user end as well as modify the existing images as needed. The eSDK's and usage of the wic file formats for the images allow the tweaking and generation of new images without rebuilding the entire package. This lets users focus on the embedded applications instead of the platform's intricacies.

### 2.1 Package Hierarchy

The System Release Package is organized into two archives. The first archive is the primary package itself containing the images, build scripts, documentation, etc. The second archive is the SDK archive. The package is arranged into an intuitive file hierarchy that is easy to follow. There are 'Readme.md' files at every location to help with understanding of the contents. The Readme.md file at the root of the hierarchy is a comprehensive guide that gives an overview of the entire package and how to use it.

Below is an overview of the package hierarchy, followed by a description of the contents and purpose of each directory/file:

```

host

build

env

Readme.md

src

tools

license

- Disclaimer051.pdf

<code>-rz-cmn-srp-um-quick-start-guide.pdf

<code>-rz-cmn-srp-um.pdf

README.md

RZ_System_Release_Package_Evaluation_license.pdf

target

images

Readme.md

9 directories, 9 files

```

**host**/: This directory holds all the tools, scripts, and artifacts needed on the host machine for building and preparing the system images.

- build/: Contains build artifacts (manifests and test data).

Key files:

- Manifest file: Files like core-image-bsp-<timestamp>.rootfs.manifest lists the contents of the generated root file system.

- Test data: Files with the \*.testdata.json extension that contains metadata or test results of the said image.

- **env/:** Provides environment configuration files used during the build or runtime. *Kev files:*

- env Files: Examples include core-image-bsp.env or core-image-minimal.env, which define variables and configuration parameters for different image variants.

- **src/**: Holds build scripts, source code, and patches that are used to build the package. *Key files:*

- o rz-cmn-srp/: The folder that contains artifacts to build Yocto and Ubuntu images.

- Patches: Located in the patches/ subdirectory, these files (For example, 0001-...patch) apply for necessary modifications.

- Build scripts: The master script rz\_builder.sh automates the build process for both Ubuntu and Yocto packages, handling setup, configuration, and image generation based on user-selected build options.

- Configuration files: site.conf, which is used to set up a specific build tag.

- config.json: Contains the available build image options grouped by build type, including Yocto images, Ubuntu images, and static image collections (allyocto-images, all-ubuntu-images, all-supported-images).

- git\_patch.json: Contains json keys and repository configuration such as: url, branch, tag, commit, repo type and patch paths to apply.

- o ubuntu/: Main folder for Ubuntu-based image generation for RZ boards .

- config/: The folder that holds configuration files for different Ubuntu variants.

- docs/: Contains documentation detailing supported features and usage instructions for each Ubuntu image variant.

- Include/: Contains scripts related to Ubuntu (e.g., for creating WIC files, packaging the root filesystem, preparing the environment, etc.)

- script/: The folder that contains all scripts related to Ubuntu image creation.

- config.ini: Configuration file that defines key parameters for the Ubuntu image build process, such as the Ubuntu variant, base image, output filenames, and system settings.

- setup\_ubuntu\_environment.sh: Main entry-point script (acts like a dispatcher/header). It sources and sequences logic from the modular scripts under script/. It does not build anything by itself.

- tools/: Provides utilities to assist with tasks such as bootloader flashing, uLoad bootloader flashing, and SD card image creation. All tools are designed to support both Linux and Windows environments.

#### Key files:

- bin/: This directory contains precompiled tools required for the firmware build and packaging process. They are organized by operating system to support cross-platform usage.

- o firmware\_compile/: Contains a helper script for building Renesas RZ family firmware artifacts, including BL2, Boot Parameter (BP) files, U-Boot binaries, and FIP packages.

- bootloader-flasher/: Contains script and README.md for flashing the main bootloader.

Works on both Linux and Windows.

- sd-creator/: Provides scripts to create SD card images from .wic files. Compatible with both Linux and Windows.

- uload-bootloader: Includes automated host-side scripts to flash the qspi boot firmware (IPL) using the images from the SD card.

- universal\_flash.py: A master Python script that unifies all flashing workflows (bootloader, uLoad, SD card) under a single interface. Cross-platform and recommended for most use cases.

- flash\_images.json: Contains predefined image mappings for supported devices.

User configuration should be defined in this file. All image files referenced for flashing must be located in:

/path/to/your/yocto/package>/target/images>

- config: Contains scripts uses a boards\_flash\_config.toml file to define flash layout and bootloader addresses for supported boards. The configuration is structured per board and boot type (e.g., qspi, emmc), and other information.

**license/:** Contains all the supporting legal documents and licensing agreements related to the release package.

target/: This directory includes all the files needed for deploying the system on target hardware.

env/: Contains environment configuration files that are used during boot-up on the target device.

Key file:

- o uEnv.txt: A file that holds boot configuration parameters.

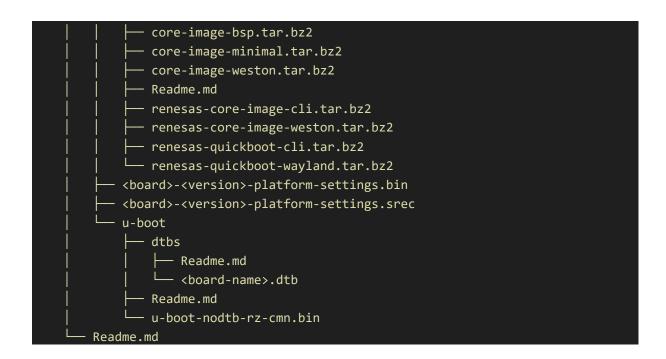

- **images/:** Holds the final system images and associated files required for the target device. *Key files:*

- atf: The RZ Common Arm Trusted-firmware (TF-A) directory contains BL2, BL31 binaries and TF-A configuration DTBs (FDTS).

- u-boot/: The RZ Common U-Boot directory contains the U-Boot binaries and device tree blobs (DTBs) used across all supported boards.

- o linux/: The directory contains linux kernel and device trees for the target images.

- System images: Files with the '.wic' extension corresponding to different build variants (BSP, minimal, Weston, Renesas images).

- o rootfs folder: Compressed archives (For example, core-image-bsp.tar.bz2) contain the root file system for each image.

- README.md (root level): This is the comprehensive guide that provides an overview of the entire release package, including instructions on how to use, build, and deploy the system.

### 2.2 Source Repositories

The system release package is maintained in public repositories that hold all the latest work that has been released. The table below describes the public repositories that are the basis for the system release package.

Table 5. Public repositories for the system release package

| Name                 | Type                      | URL                                                                                                                            | Description                                                                                                                                                                                                 |

|----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rz-build-<br>scripts | Yocto build automation    | Renesas-SST/rz-build-<br>scripts: Build scripts for rz<br>projects                                                             | Custom Yocto build script that downloads the base Yocto package and other downloaded zip files, arranges the layers, applies relevant meta layers, sets up the environment, and initiates a build.          |

| meta-<br>renesas     | Yocto meta layer          | Renesas-SST/meta-<br>renesas: Yocto meta layer<br>for Renesas System<br>Solutions                                              | Yocto meta layer supports RZ-<br>based platforms.                                                                                                                                                           |

| linux-rz             | Linux kernel              | Renesas-SST/linux-rz:<br>Linux kernel for System<br>and Solutions Products                                                     | This repo contains the kernel fork with RZ-based patches.                                                                                                                                                   |

| u-boot               | Boot loader               | Renesas-SST/u-boot: A u-boot suporting System & Solutions Products                                                             | This repository contains the U-Boot bootloader source code customized for Renesas RZ devices. It includes board-specific configurations and patches required to boot Linux on supported RZ-based platforms. |

| rz-atf               | Arm Trusted<br>Firmware-A | Renesas-SST/rz-atf: Arm<br>Trusted Firmware<br>implementation for System<br>& Solutions products                               | Arm trusted the firmware repo with RZ-based patches.                                                                                                                                                        |

| flash-writer         | Firmware flashing tool    | Renesas-SST/flash-writer:<br>Serial flashing utility to load<br>into blank boards<br>supporting System &<br>Solutions Products | This repository contains the code for an essential tool that is used as the base for flashing blank boards in the factory for the first time or recovering bricked boards.                                  |

| rz-utils | Flashing tools | Collection of utilities for                           | Collection of utilities for various workflows related to Renesas |

|----------|----------------|-------------------------------------------------------|------------------------------------------------------------------|

|          |                | various workflows related<br>Renesas RZ based devices | RZ-based devices                                                 |

While the public repositories are mostly open source, the RZ MPUs contain IPs that are licensed differently, and those functionalities require specific packages to be downloaded from the Renesas website through login. These are mostly free-to-download packages and contain their licenses, which are non-standard. The build scripts can identify and point to the missing packages and their download URLs. You can download these scripts manually and copy them to the workspace.

### 3. Required Resources

### 3.1 Development Tools and Software

The following tools are used for development:

- SEGGER JLink software (SEGGER The Embedded Experts Downloads J-Link / J-Trace).

- Tera Term (TeraTerm Project) on Windows PC for accessing UART.

- Minicom on the Ubuntu host machine for accessing the UART on Linux.

- Balena Etcher

#### 3.2 Hardware

The hardware requirements vary slightly depending on the Renesas RZ board in use. Refer to the corresponding subsection below for board-specific details.

### 3.2.1 Common Hardware Requirements

These items are required for all supported Renesas RZ boards:

- Windows PC with Tera Term software and admin privileges.

- Ubuntu 24.04 host environment (native install, VM, or Docker) for working with Yocto distros.

- Ethernet cables for networking.

### 3.2.2 Board-Specific Hardware

### 3.2.2.1 RZ/G2L-SBC

The following hardware would be needed to work with the RZ/G2L-SBC:

- RZ/G2L-SBC RZ/G2L Single Board Computer

- UART TTL cables (Raspberry Pi compatible) featuring FTDI chipset. We do not recommend PL2302-based UART TTL cables, as they have demonstrated issues with Windows drivers.

- Jumper wires/plugs.

- Mini-HDMI to HDMI display interface cable.

- Power supply that can provide 5V at 3 A with USB-C pins. (not included in the package).

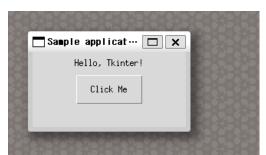

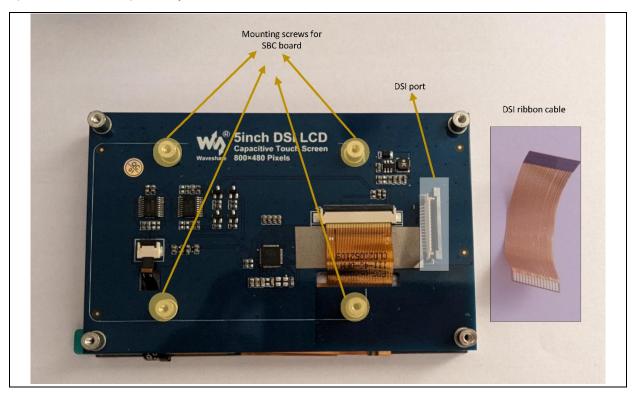

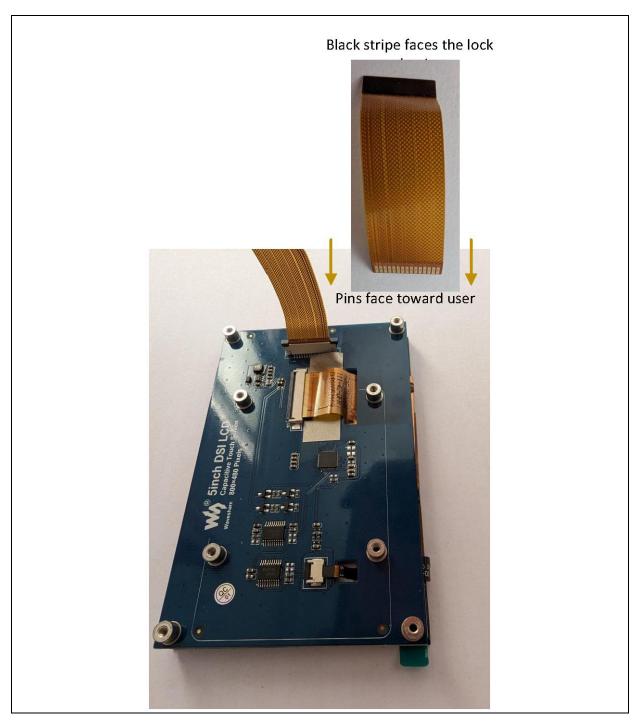

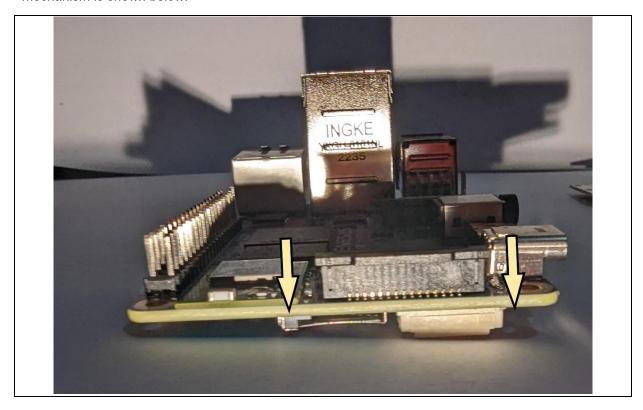

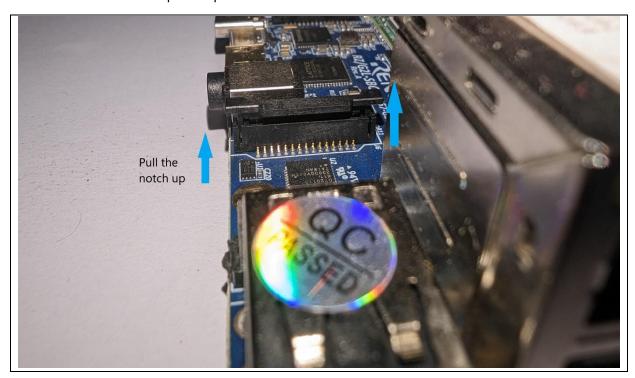

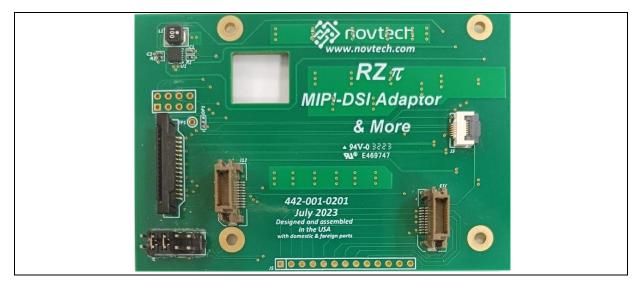

- Waveshare 5" DSI display module with a capacitive touch interface (optional: not included in the hardware package).

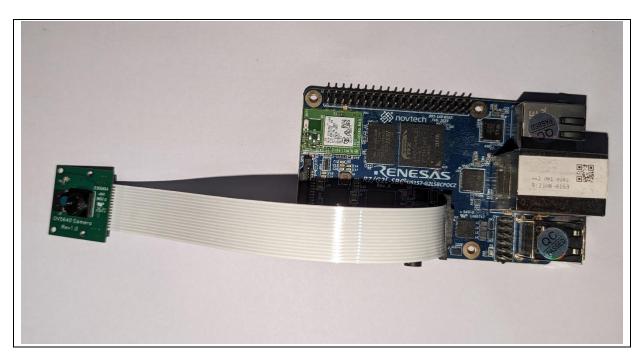

- OV5640 camera module (optional: not included in the hardware package).

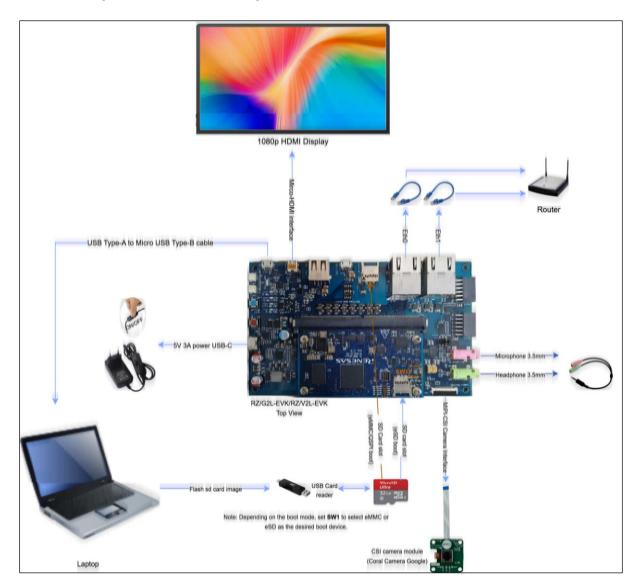

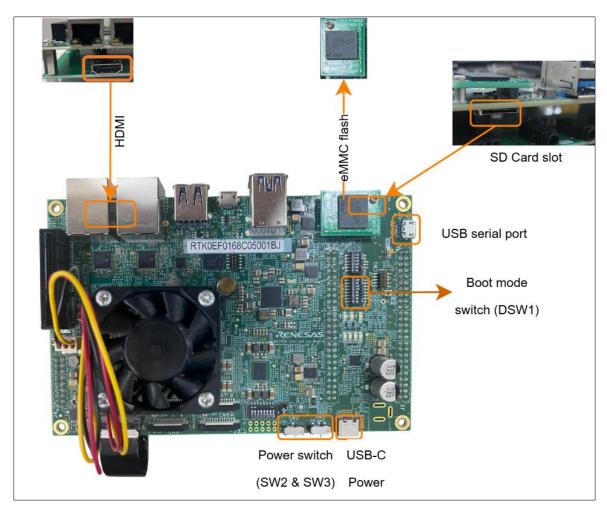

### 3.2.2.2 RZ/G2L-EVK- & RZ/V2L-EVK

The following hardware is required for working with the RZ/G2L-EVK or RZ/V2L-EVK. Most items are identical for both boards:

- RZ/G2L SMARC module board or RZ/V2L SMARC module board and common carrier board.

- USB Type-A to Micro USB Type-B cable

- Micro-HDMI to HDMI display interface cable.

- Power supply that can provide 5V at 3 A with USB-C pins. (not included in the package).

- OV5645 camera module (optional: not included in the hardware package).

- <u>3.5mm Audio Stereo Y Splitter extension cable</u> (optional: not included in the hardware package).

#### 3.2.2.3 RZ/V2H-EVK

The following hardware is needed to work with the RZ/V2H-EVK:

RZ/V2H Quad-core Vision AI MPU Evaluation Kit

- USB Type-A to Micro USB Type-B cable.

- HDMI to HDMI display interface cable.

- Power supply that can provide up to 100W via USB-C PD (not included in the package).

- OV5645 camera module (optional: not included in the hardware package).

- Camera conversion 22-pin to 25-pin FPC adapter (optional: not included in the hardware package).

- 3.5mm Audio Stereo Y Splitter extension cable (optional: not included in the hardware package).

#### 4. Quick Start

This section describes how to quickly get set up and start running the supported platforms with this release. The following are the essential steps for an SD-MMC card-based boot:

- 1. Select an image from the list of available images in Section 1.1. Supported Distributions

- 2. Prepare an SD MMC card that has the image programmed onto it.

- 3. Prepare the hardware with power and debug UART interface. Displaying the connection to one of the HDMI interfaces is highly recommended, but not essential.

- 4. Program the firmware using the appropriate scripts and process in the 'host/tools' directory of the package.

- 5. Boot normally with the SD MMC card.

### 4.1 SD-MMC Card Flashing

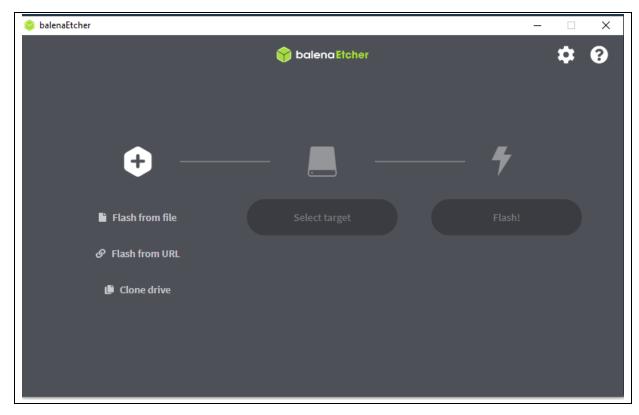

The Linux bootable SD card creation is a very simple process. The idea is to use any filesystem imaging tool (etcher) to burn the required image's '.wic' file (core-image-weston.wic for example) located in the 'target/images' directory of the release to the sd-mmc card. We recommend installing Balena etcher, which is available for Linux, MacOS, and Windows.

Figure 2. Balena etcher UI

### Steps:

- 1. Select "Flash from File".

- 2. In the popup window, navigate to your release and select one of the chosen image files (coreimage-weston.wic).

- 3. Then click on 'Select target,' and it will list all available devices.

- 4. Select your SD MMC card.

Be mindful not to select your primary laptop/desktop hard drive.

- 5. Select 'Flash'.

- 6. When flashing is completed, it will automatically dismount the SD MMC card device.

7. Insert the SD card into the SD-MMC card slot on the RZ board.

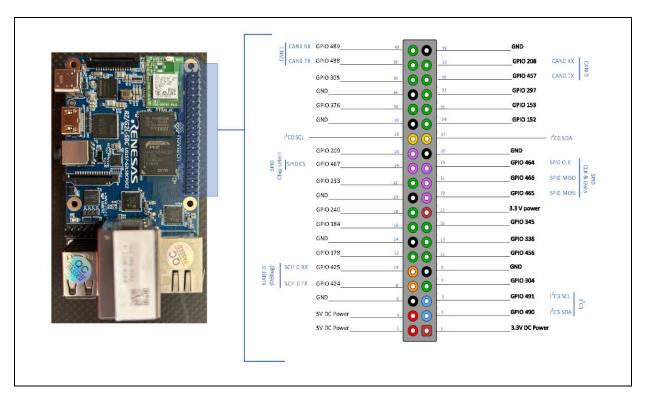

### 4.2 RZ/G2L-SBC

This section describes the hardware-specific processes for the RZ/G2L-SBC (Single-board Computer).

#### Note:

- The release consists of images that have desktop and display support.

- At least one basic display, like a 1080p HDMI monitor, must be available for those images.

- You can also use the DSI touch panel described in the MIPI DSI Display Touch Panel.

- It is recommended to use an FTDI cable for the UART and not any other converter chip.

### 4.2.1 Hardware Requirements

The basic hardware setup consists of the following:

- 1. RZ/G2L-SBC

- 2. FTDI RS232 UART cable

- 3. USB-C 5V 3A+ power supply

- 4. SD-MMC card (minimum 8 GB)

- 5. 1080p HDMI display/Waveshare 5" MIPI DSI display touch panel

- 6. Ethernet cables.

- 7. OV5640 MIPI CSI camera

- 8. USB keyboard and mouse

- 9. 3.5mm Headphone with microphone

### 4.2.2 Essential Hardware Setup

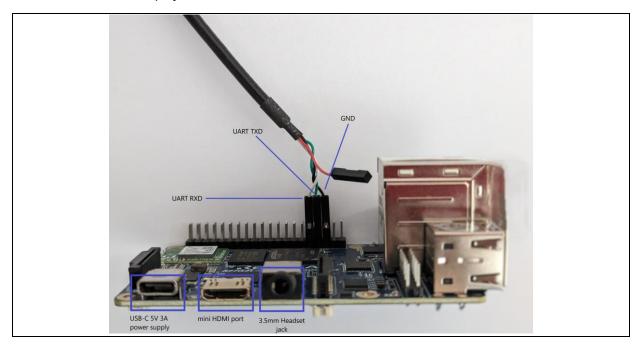

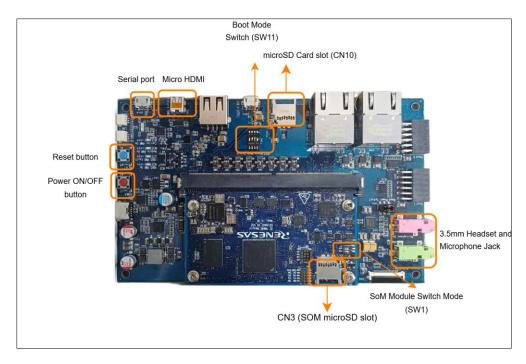

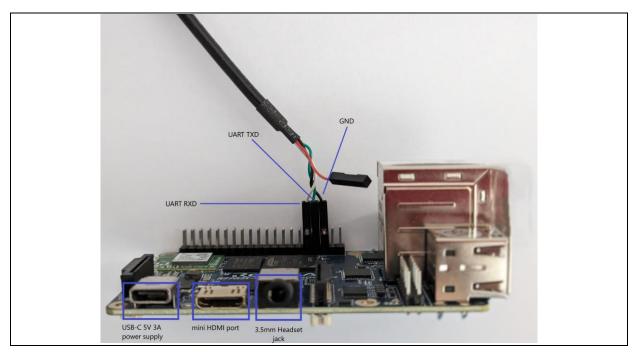

Figure 3. Essential minimum interfaces show the basic essential hardware setup. We expect a UART cable and an HDMI display to be available.

Figure 3. Essential minimum interfaces for RZ/G2L-SBC

## 4.2.3 Complete Hardware Setup

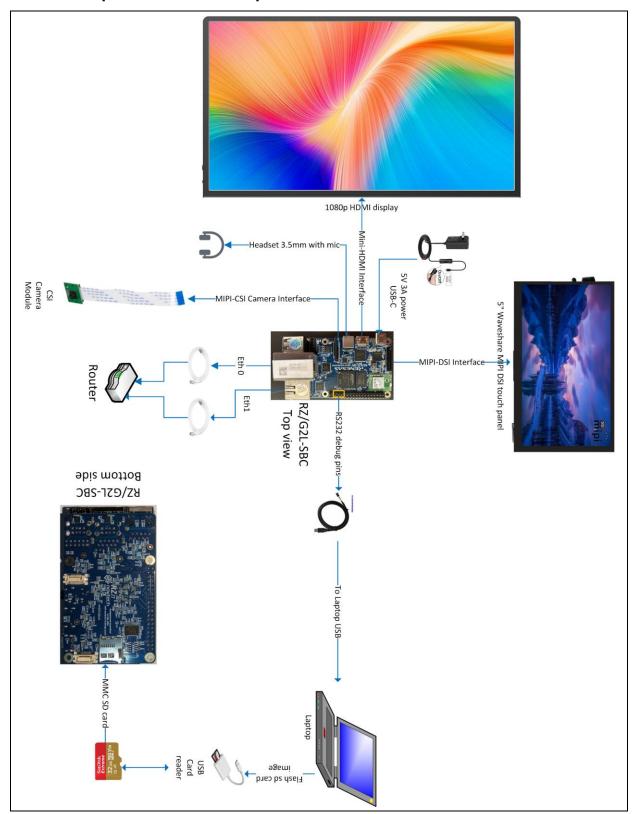

Figure 4. Complete setup for RZ/G2L-SBC board

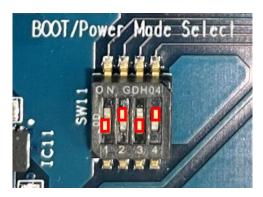

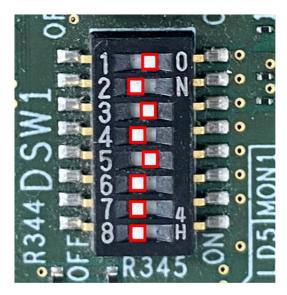

### 4.2.4 Booting

The booting is straightforward.

- 1. Insert the MMC card into the MMC port on the bottom side of the RZ/G2L-SBC.

- 2. Connect the keyboard, mouse, and HDMI display; then insert the USB-C power supply and turn the power on.

- 3. You should see the boot log on the UART console and the Weston desktop on the HDMI screen.

- 4. Click on any of the applications and interact with them.

The image is fully featured and has powerful desktop-grade features. Read further to learn more about the features packed into the Linux image.

Note: The default firmware shipped on the board may not recognize new images. If the board fails to boot, update the firmware using the Serial Download Mode (SCIF) procedure described in Section 16.1.1 RZ/G2L-SBC

### 4.2.5 Known Hardware and Functional Limitations on RZ/G2L-SBC

### 4.2.5.1 Linux (CA55) Side Known Issues

- 1. HDMI audio

- Status: Unverified

- Description: The functionality of the HDMI audio output has not been tested yet, and its behavior remains uncertain. Additional development and testing are required to assess its reliability and performance on the RZ/G2L-SBC.

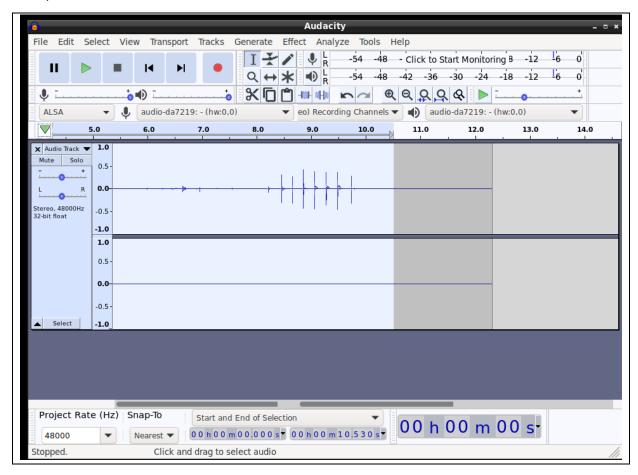

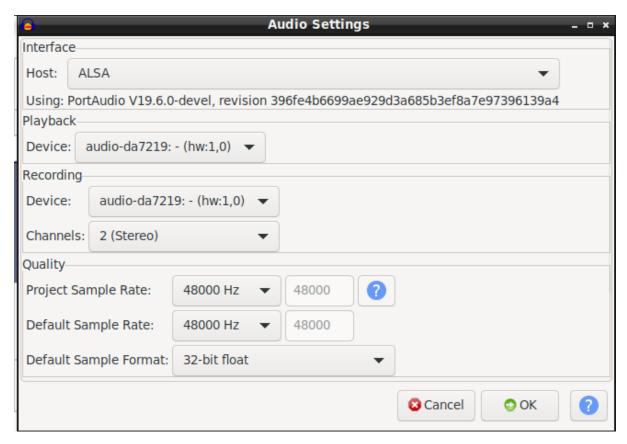

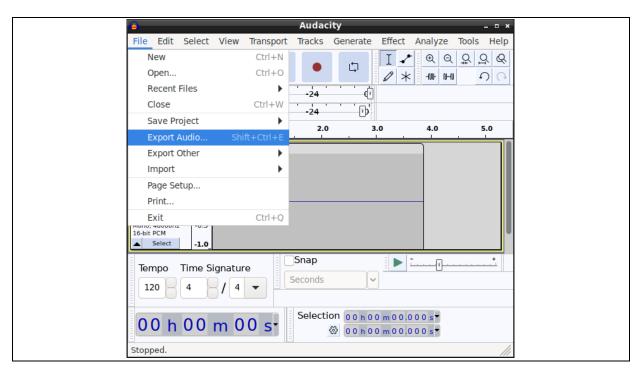

- 2. Audio Sampling Rate Limitation

- Status: Currently limited to 48 kHz (validated)

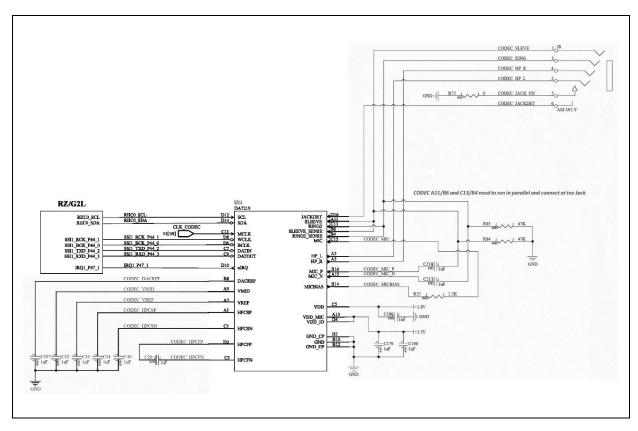

- Description: The board's clock design deviates from the standard RZ reference, which prevents the existing driver frameworks from generating the proper clocks when the SoC operates as I²S/TDM master. As a result, only 48 kHz sampling has been successfully validated so far. This is not a fundamental hardware restriction — codec-master mode has not yet been evaluated, and wider sampling-rate support may be possible but remains unsupported.

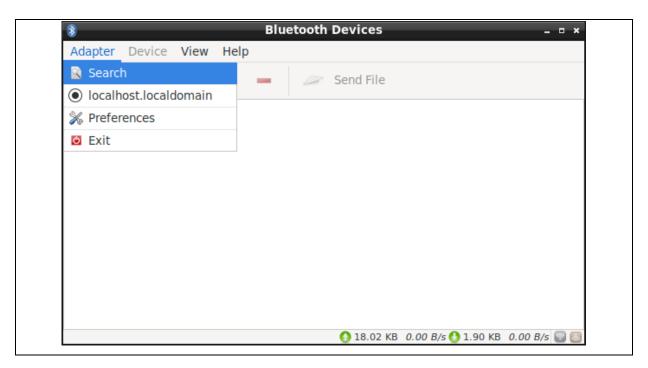

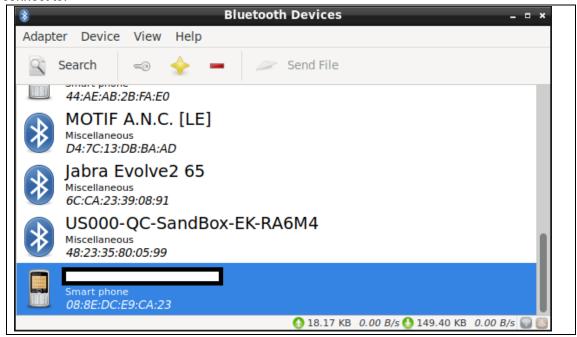

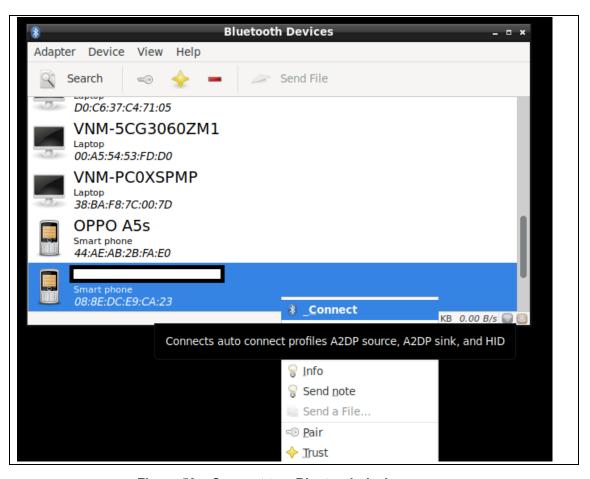

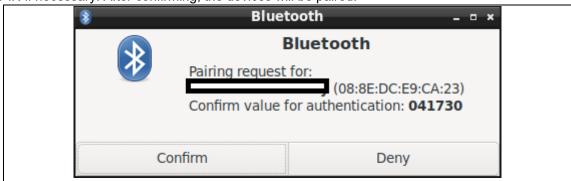

#### 3. Onboard Bluetooth (BT) Functionality

- Status: Non-functional (onboard BT only)

- Description: The onboard Bluetooth functionality is currently non-operational due to a schematic symbol error in the Laird Wi-Fi/BT module. The Bluetooth interface is missing from the module's schematic design, preventing Bluetooth connectivity. However, USB Bluetooth functionality remains operational. This issue requires a hardware revision to enable full Bluetooth functionality on the onboard module.

### 4.2.5.2 FreeRTOS/FSP (CM33) Side Known Issues

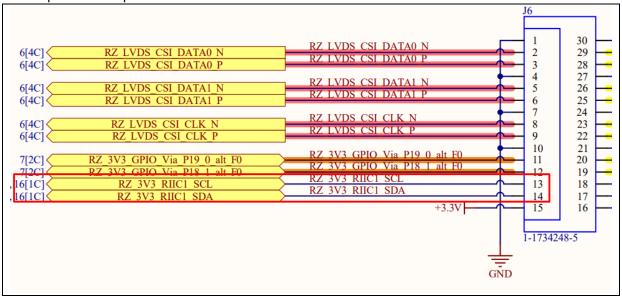

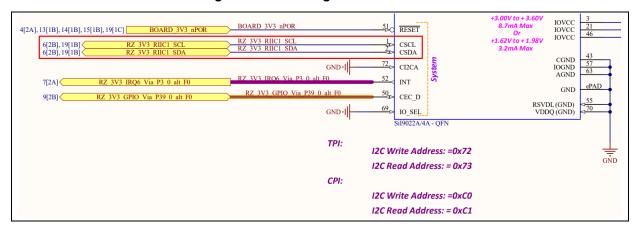

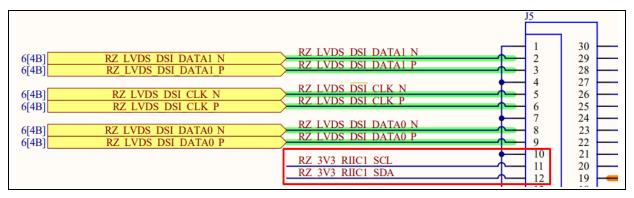

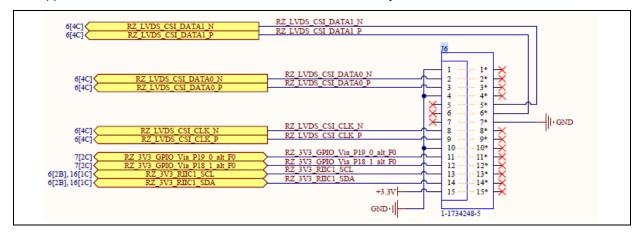

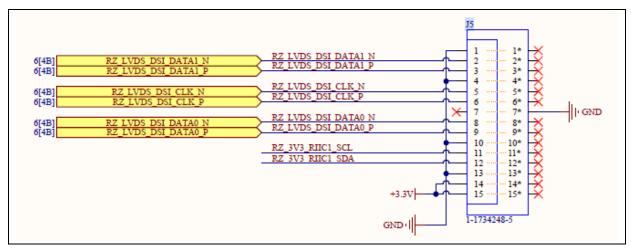

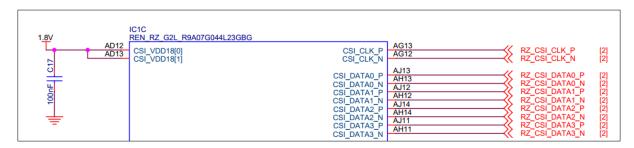

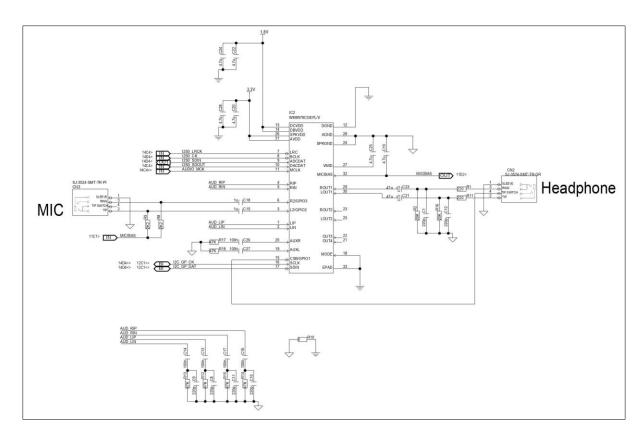

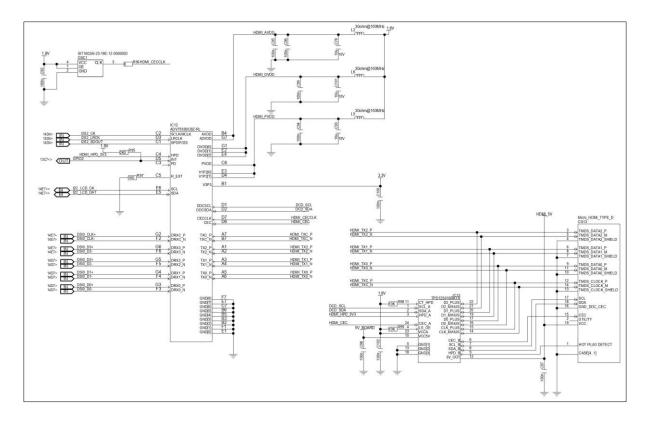

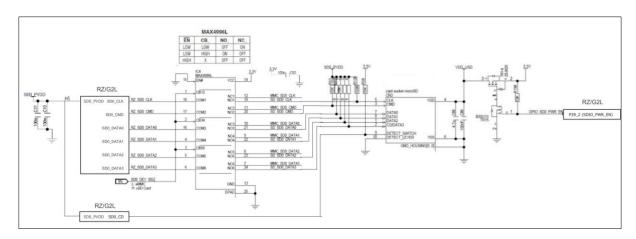

### 1. MIPI-CSI2 Camera and Peripherals Accessing Shared I2C1 Bus

In the RZ/G2L-SBC, the MIPI CSI Camera interface, HDMI Bridge, and MIPI DSI all share the same I2C1 channel. Due to this hardware constraint, controlling one of these devices may impact the functionality of the others.

#### Limitations:

- I2C1 can only be accessed by one core at a time, which can prevent both the camera and display from functioning simultaneously.

- Any device using I2C1 must be managed carefully to avoid conflicts with other peripherals.

- This limitation should be considered when designing the system to ensure both peripherals can operate as required.

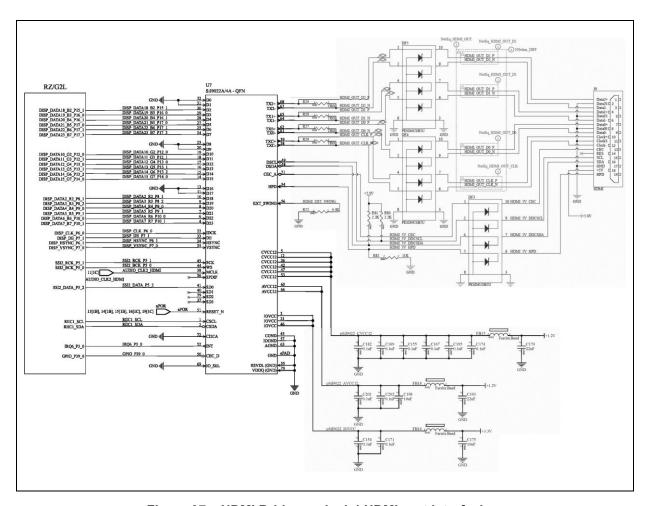

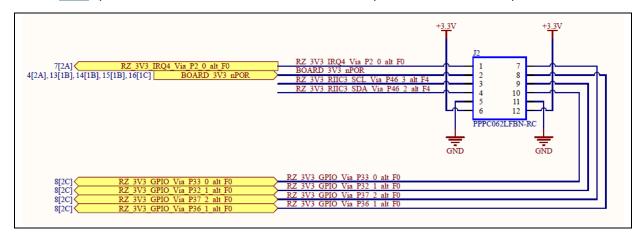

Figure 5. CSI using shared I2C1 bus

Figure 6. HDMI using shared I2C1 bus

Figure 7. DSI using shared I2C1 bus

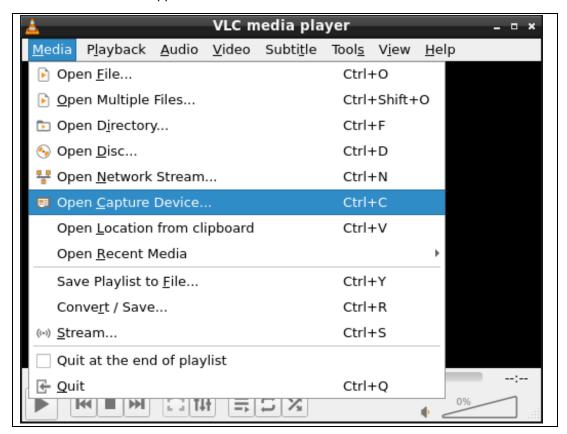

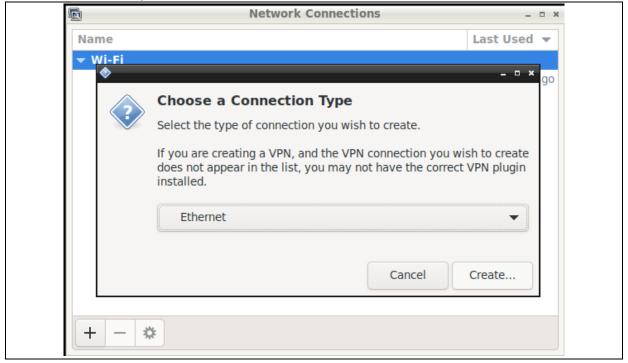

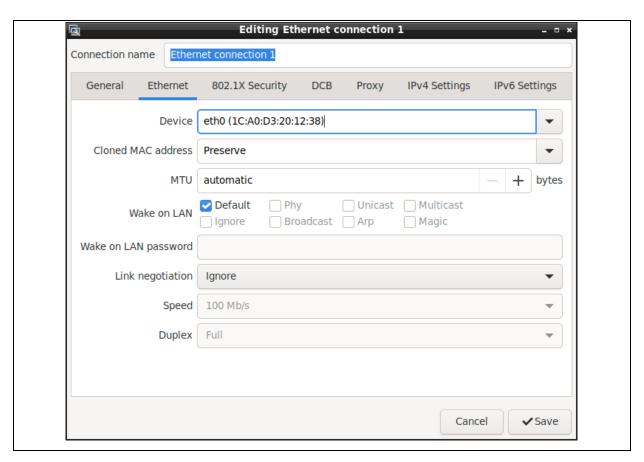

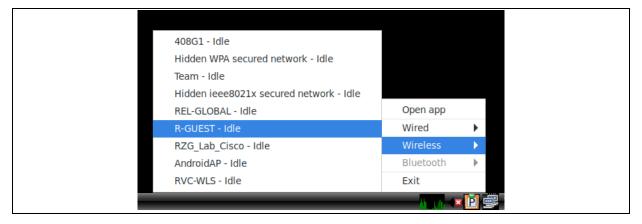

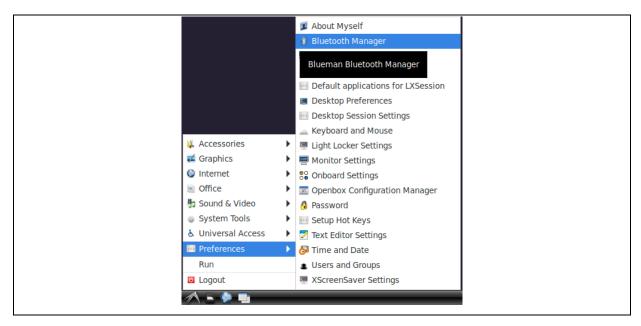

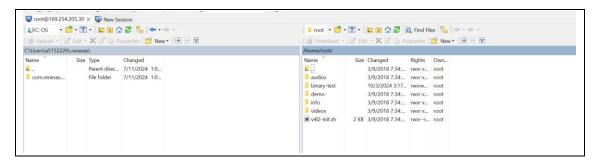

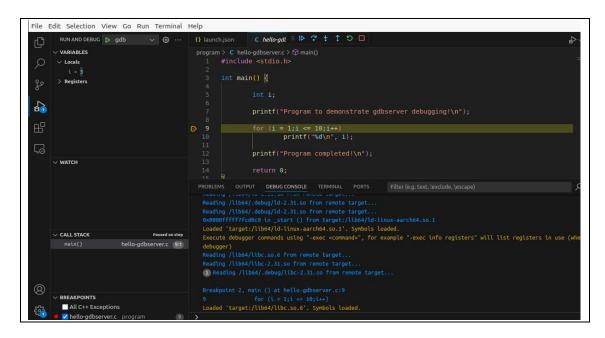

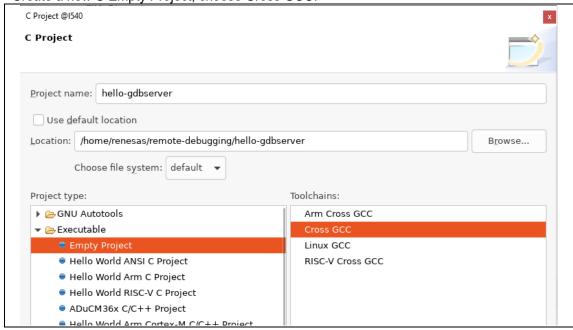

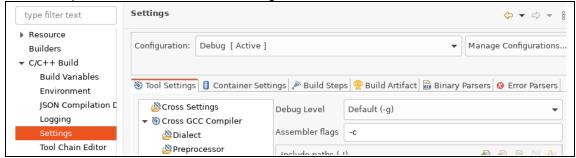

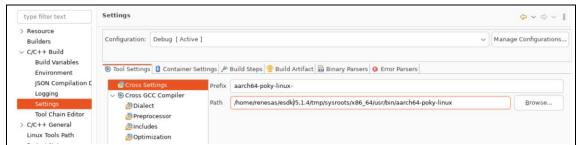

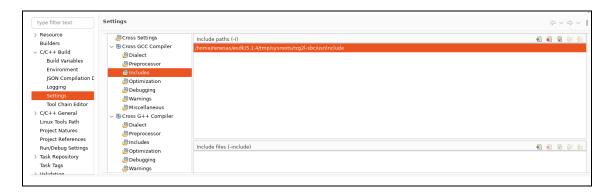

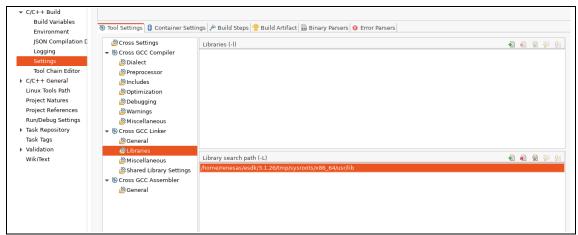

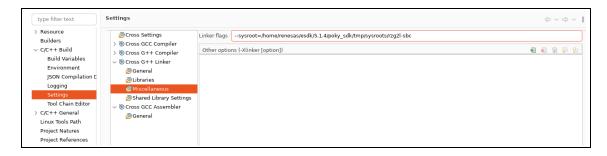

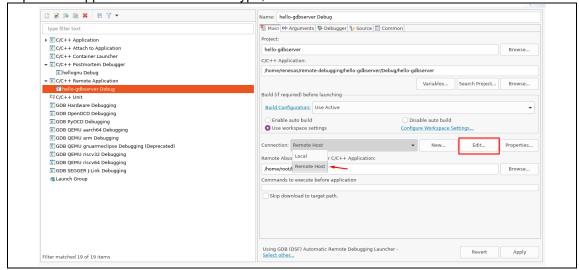

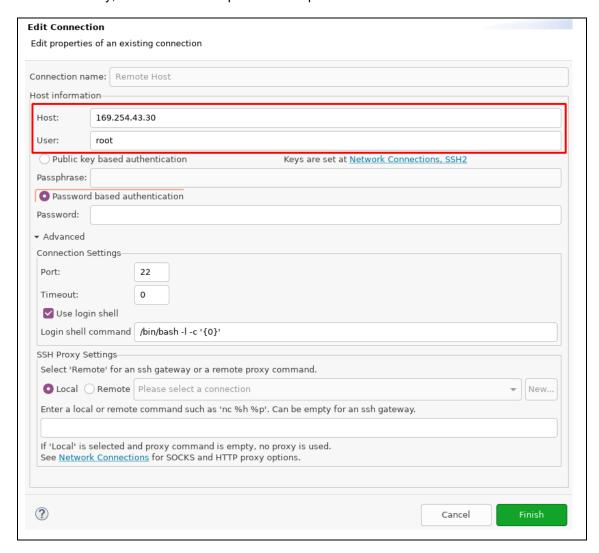

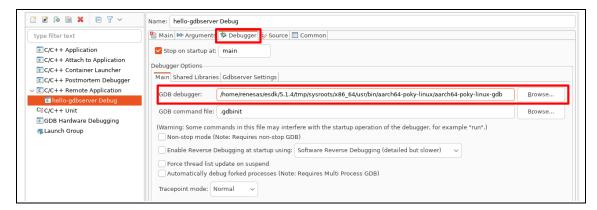

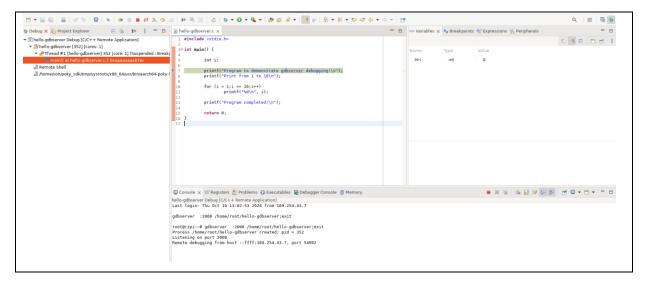

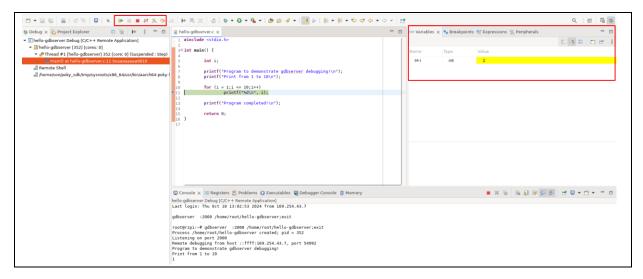

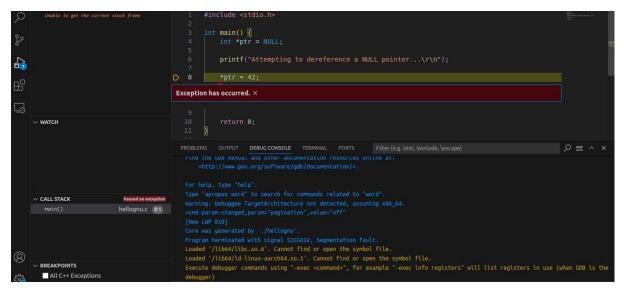

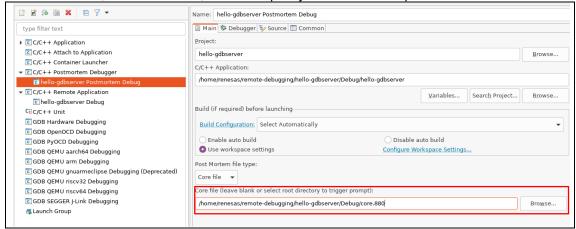

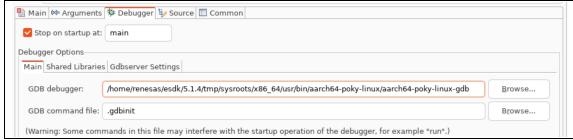

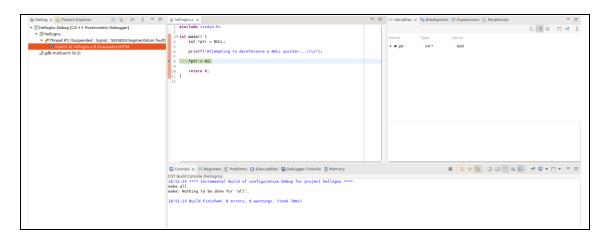

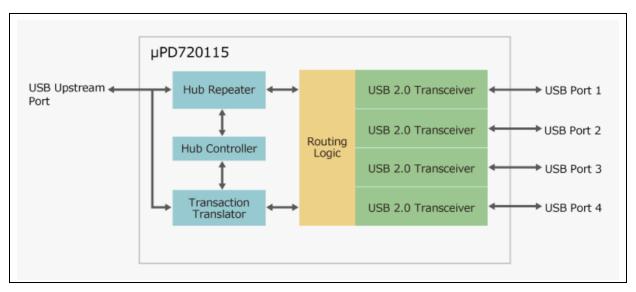

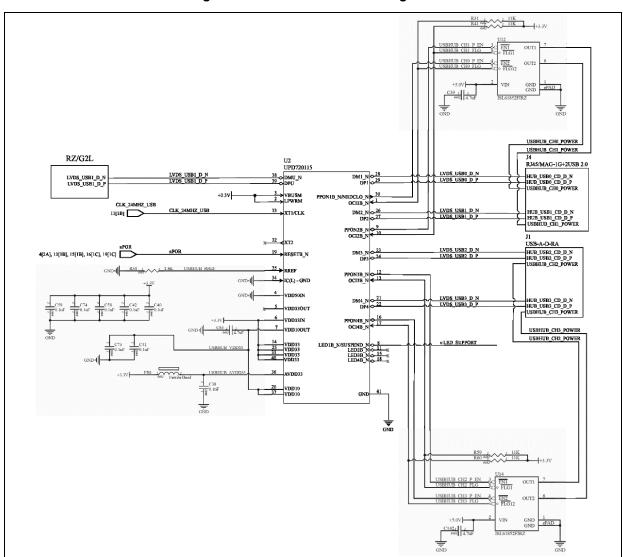

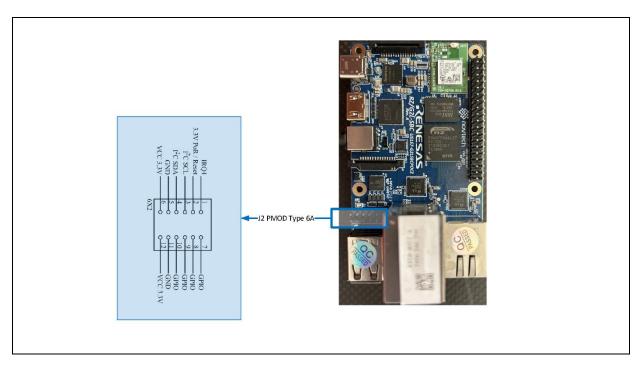

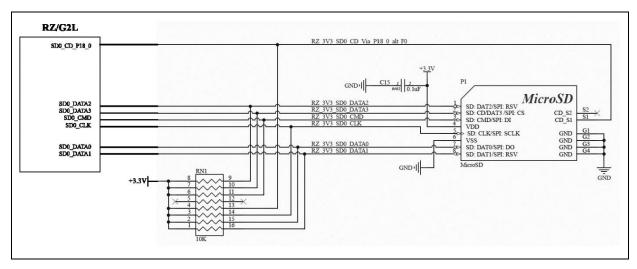

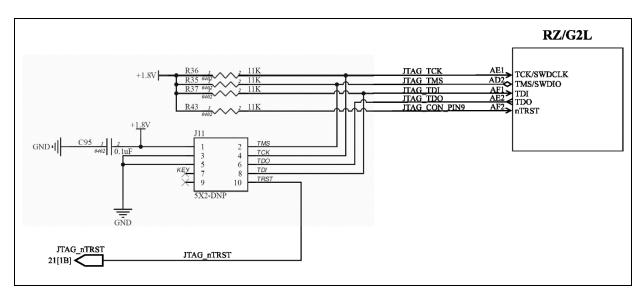

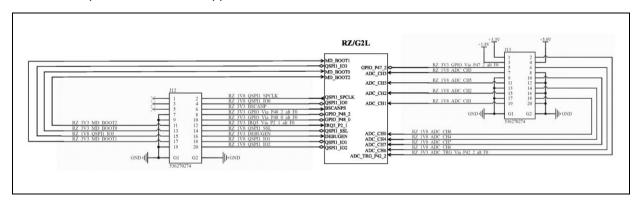

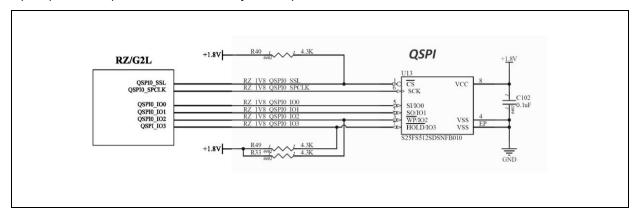

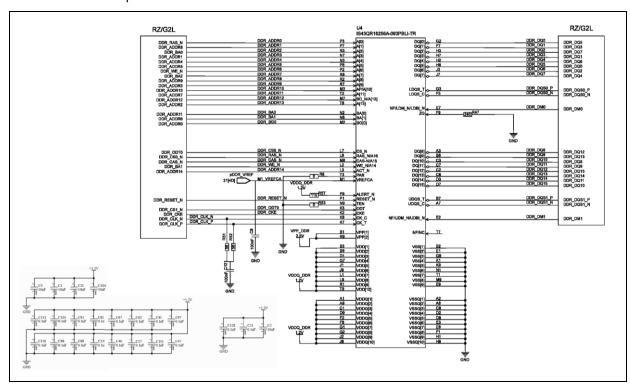

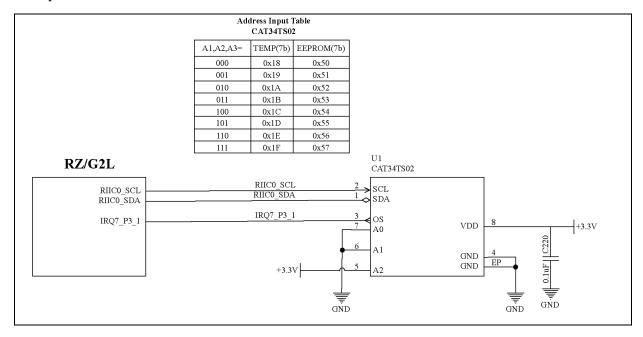

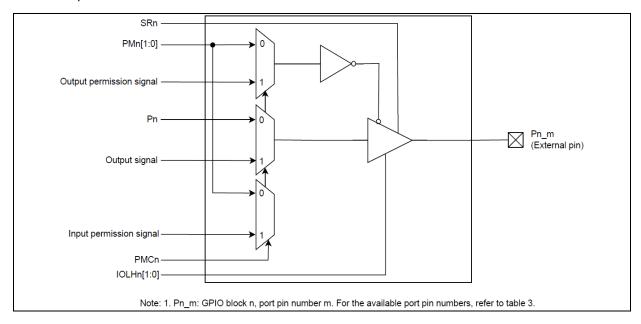

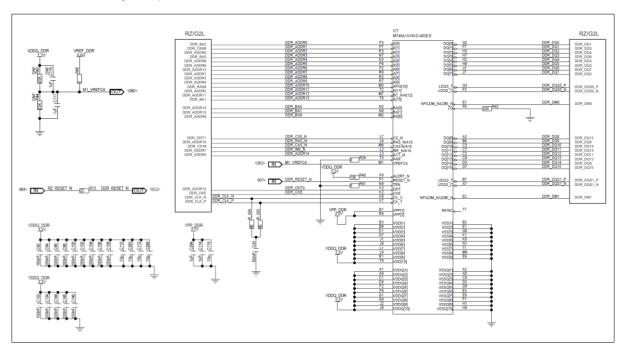

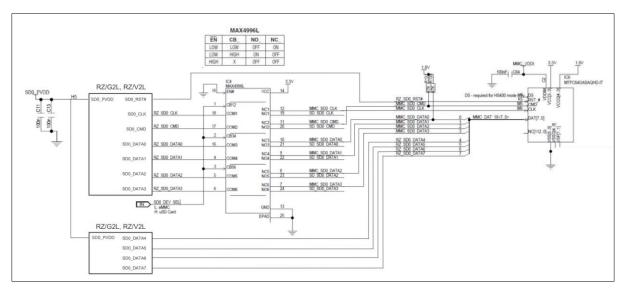

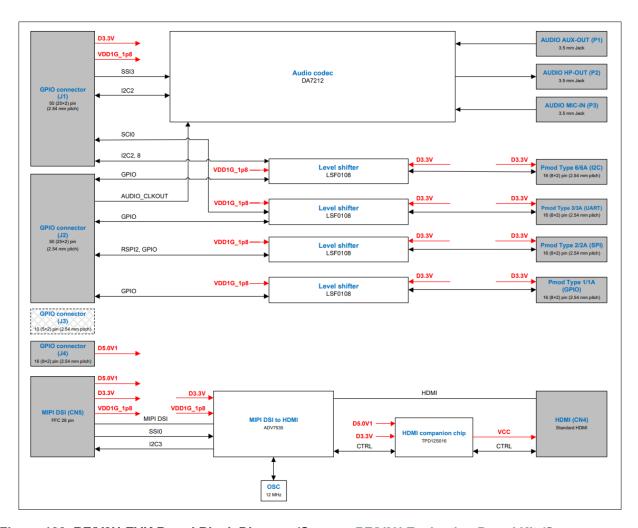

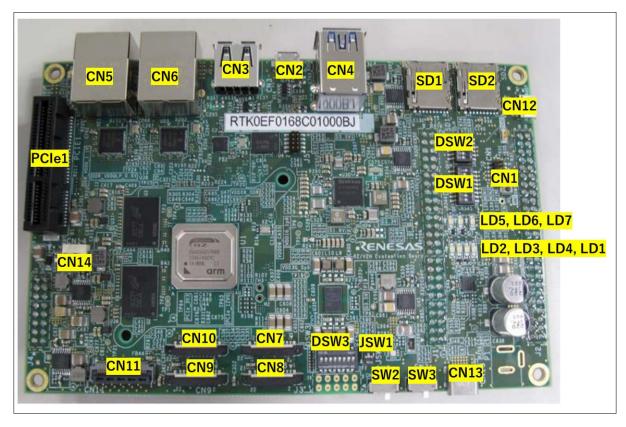

As shown in the three figures above, the shared I2C1 bus is used by multiple peripherals, which may lead to conflicts if both cores are used simultaneously. To avoid issues, users should ensure that only one core accesses I2C1 at a time or consider alternative methods for managing communication between peripherals.