# RL78 Family

Renesas Flash Driver RL78 Type 02

User's Manual

RENESAS Microcontrollers RL78/F24 RL78/F23

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### Contact information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>.

© 2025 Renesas Electronics Corporation. All rights reserved.

## General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

## How to Use This Manual

#### Readers

This manual is intended for engineers who wish to develop application systems using the RL78/F23 and RL78/F24 microcontroller.

#### Purpose

This manual is intended to give users an understanding of the methods for using the Renesas Flash Driver (RFD) RL78 Type 02 to reprogram the flash memory in the RL78/F23 and RL78/F24 microcontroller.

#### Organization

This manual is separated into the following sections.

- 1. Overview

- 2. System Configuration

- 3. API Functions of RFD RL78 Type 02

- 4. Flash Memory Sequencer Operation

- 5. Sample Programs

- 6. Creating a Sample Project for RFD RL78 Type 02

#### How to Read this Manual

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, microcontrollers, C language, and assemblers.

To understand the hardware functions of the RL78/F23 and RL78/F24:

- Refer to the User's Manual of the target RL78/F23 and RL78/F24 device.

#### Conventions

- Data significance: Higher digits on the left and lower digits on the right

- Active low representations: xxx (overscore over pin and signal name)

- Note: Footnote for item marked with Note in the text

- Caution: Information requiring particular attention

- Remark: Supplementary information

- Numeric representation:

Binary: xxxx or xxxxB

Decimal: xxxx

Hexadecimal: xxxxH or 0xxxxx

Prefixes indicating power of 2 (address space and memory capacity):

K (kilo)

$$2^{10} = 1024$$

M (mega)  $2^{20} = 1024^2$

#### Related Documents

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

| ı | No | Document Title                                                                                           | Document Number |

|---|----|----------------------------------------------------------------------------------------------------------|-----------------|

| 1 | 1  | RL78/F23, F24 User's Manual: Hardware                                                                    | R01UH0944EJ     |

| 2 | 2  | E1/E20/E2 Emulator, E2 Emulator Lite Additional Document for User's Manual (Notes on Connection of RL78) | R20UT1994EJ     |

| 3 | 3  | Renesas Flash Driver and EEPROM Emulation Software Target MCU List for RL78                              | R20UT5631EJ     |

## **Table of Contents**

| 1. Ove  | erview                                                                                       | 10      |

|---------|----------------------------------------------------------------------------------------------|---------|

| 1.1 (   | Outline                                                                                      | 10      |

| 1.1.    | 1 Purpose                                                                                    | 10      |

| 1.2 (   | Contents                                                                                     | 10      |

| 1.3 F   | Features                                                                                     | 11      |

| 1.4 (   | Operating Environment                                                                        | 12      |

| 1.5 F   | Points for Caution                                                                           | 13      |

| 1.6     | C Compiler Definitions                                                                       | 15      |

| 2. Sys  | stem Configuration                                                                           | 17      |

| 2.1 F   | File Structure                                                                               | 17      |

| 2.1.    | .1 Folder Structure                                                                          | 17      |

| 2.1.    | .2 List of Files                                                                             | 18      |

| 2.2 F   | Resources of RL78/F23 and RL78/F24                                                           | 20      |

| 2.2.    | .1 Memory Map                                                                                | 20      |

| 2.2.2   | 2 The Allocation of Blocks                                                                   | 21      |

| 2.2.3   | .3 List of Registers Related to Flash Memory Sequencer Control                               | 22      |

| 2.3 F   | Resources Used in RFD RL78 Type 02                                                           | 23      |

| 2.3.    | .1 Sections Used in RFD RL78 Type 02                                                         | 23      |

| 2.3.    | 2 Code Size and Stack Size which API Functions Use                                           | 25      |

| 3. API  | I Functions of RFD RL78 Type 02                                                              | 26      |

|         | List of API Functions of RFD RL78 Type 02                                                    |         |

| 3.1.    | •••                                                                                          |         |

| 3.1.2   | .2 API Functions for Code Flash Memory Control                                               | 27      |

| 3.1.    | •                                                                                            |         |

| 3.1.4   |                                                                                              |         |

| 3.1.    | 5 Hook Functions                                                                             | 28      |

| 3.2     | Data Type Definitions                                                                        | 29      |

| 3.2.    | 1 Data Types                                                                                 | 29      |

| 3.2.2   | 2 Global Variables                                                                           | 29      |

| 3.2.    | .3 Enumerations                                                                              | 30      |

| 3.2.4   | 4 Macro Definitions                                                                          | 31      |

| 3.3     | Specifications of API Functions                                                              |         |

| 3.3.    | .1 Specifications of API Functions Used in Common for Flash Memory Control                   | 41      |

| 3.3.    | 2 Specifications of API Functions for Code Flash Memory Control                              | 59      |

| 3.3.    | .3 Specifications of API Functions for Data Flash Memory Control                             | 63      |

| 3.3.4   | 4 Specifications of API Functions for Extra Area Control                                     | 67      |

| 3.3.    | .5 Specifications of Hook Functions                                                          | 74      |

| 4. Flas | sh Memory Sequencer Operation                                                                | 76      |

| 4.1     | Setting of Flash Memory Control Mode                                                         | 76      |

| 4.1.    |                                                                                              |         |

| 4.1.    | 2 Procedure for Transition from Non-programmable Mode to the Code Flash Memory Prog          | ramming |

| Mod     |                                                                                              |         |

| 4.1.    | .3 Procedure for Transition from Non-programmable Mode to the Data Flash Memory Programmable | amming  |

| Mod     | de 78                                                                                        |         |

| 4.1.4   | 4 Procedure for Transition to the Non-programmable Mode                                      | 79      |

|         | Clearing the Registers for Flash Memory Sequencer Control                                    |         |

| 4.3     | Specifying the Operating Frequency of the Flash Memory Sequencer                             | 81      |

| 4.4        |        | Memory Sequencer Commands                                                           |       |

|------------|--------|-------------------------------------------------------------------------------------|-------|

| 4.4        |        | Overview                                                                            |       |

|            | 1.2    | Code/data Flash Memory Area Sequencer Commands                                      |       |

| 4.4        |        | Extra Area Sequencer Commands                                                       |       |

| 4.4<br>4.4 |        | Procedures for Judging the End of Command Execution in the Flash Memory Sequencer   |       |

| Se         | quenc  | er                                                                                  | 95    |

| 4.5        | Boot   | Swap Function                                                                       | 96    |

| 4.5        | 5.1    | Overview                                                                            | 96    |

| 4.5        | 5.2    | Operation of the Boot Swap Function                                                 | 96    |

| 4.5        | 5.3    | Execution of the Boot Swap Function                                                 | 97    |

| 4.6        | Flash  | Shield Window Function                                                              | 99    |

| 4.6        | 3.1    | Overview                                                                            | 99    |

| 4.6        | 3.2    | Operation of the Flash Shield Window Function                                       | 99    |

| 4.6        | 5.3    | Execution of the Flash Shield Window Function                                       | . 100 |

| 4.7        | Exam   | ples of Command Execution for Reprogramming of Flash Areas                          | . 101 |

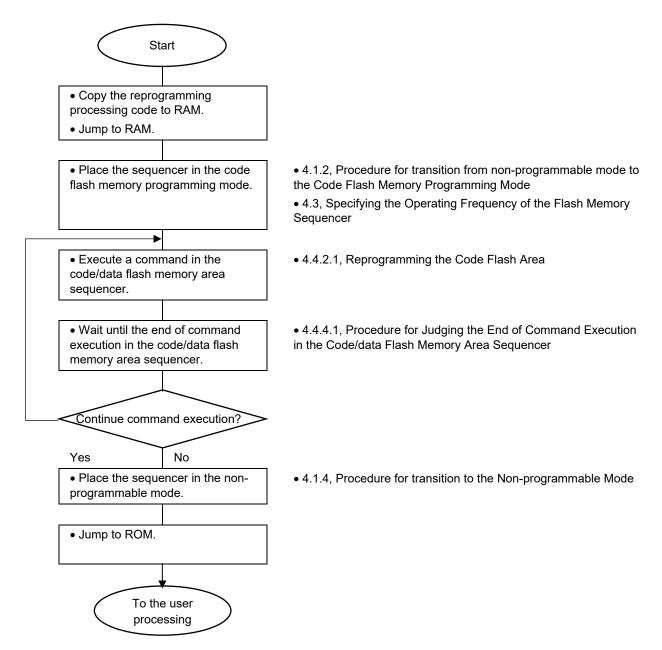

| 4.7        | 7.1    | Example of Command Execution for Reprogramming of the Code Flash Area               |       |

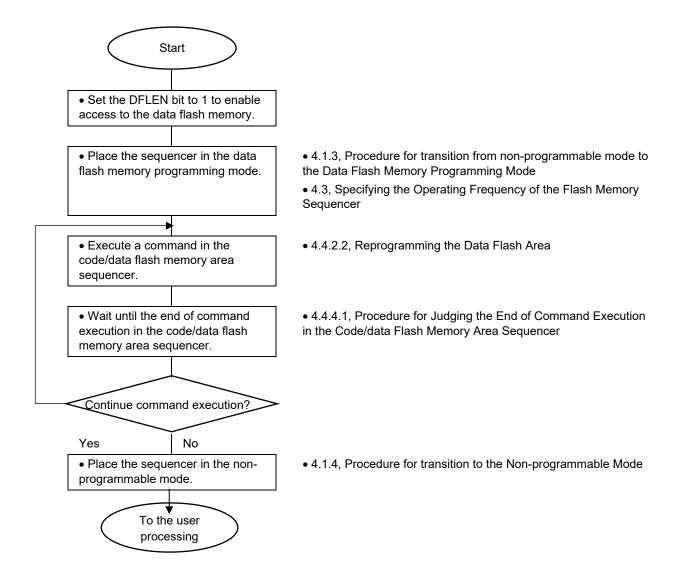

| 4.7        | 7.2    | Example of Command Execution for Reprogramming of the Data Flash Area               |       |

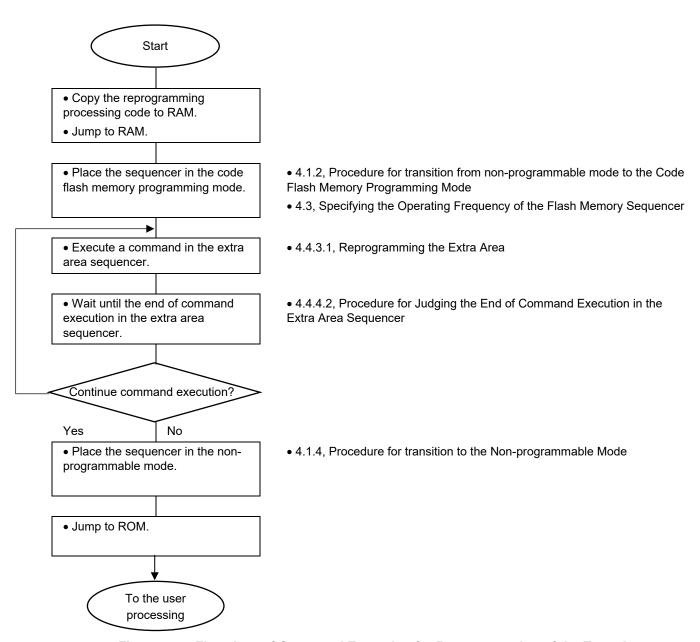

| 4.7        | 7.3    | Example of Command Execution for Reprogramming of the Extra Area                    | . 103 |

|            | •      | Programs                                                                            |       |

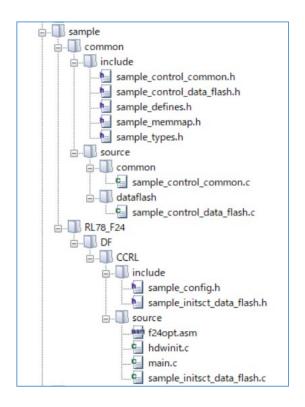

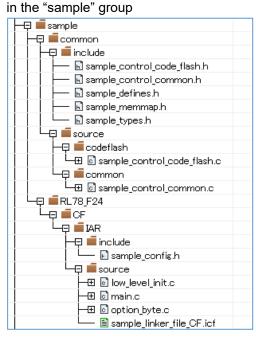

| 5.1        | File S | structure                                                                           |       |

| 5.         |        | Folder Structure                                                                    |       |

| _          | 1.2    | List of Files                                                                       |       |

| 5.2        |        | Type Definitions                                                                    |       |

|            | 2.1    | Enumerations                                                                        |       |

| 5.3        | •      | ble Program Functions                                                               |       |

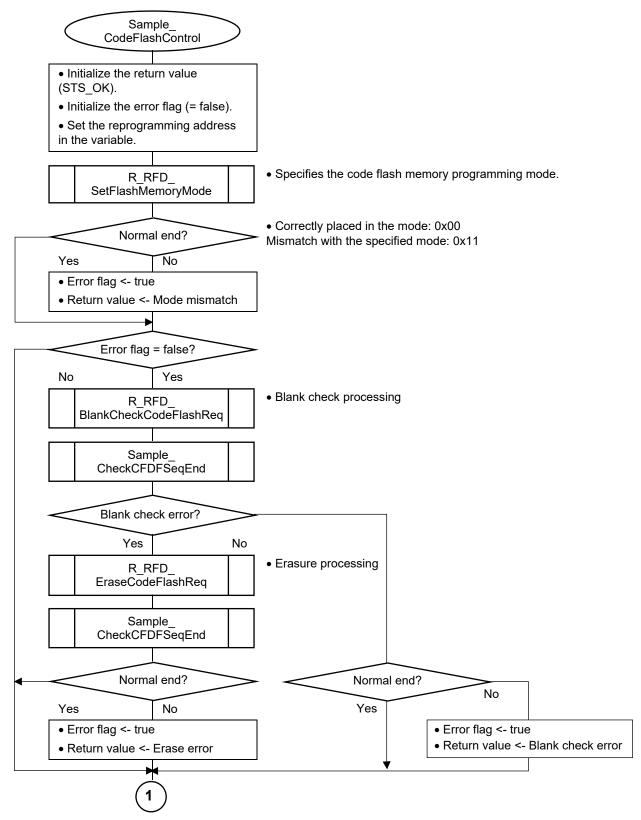

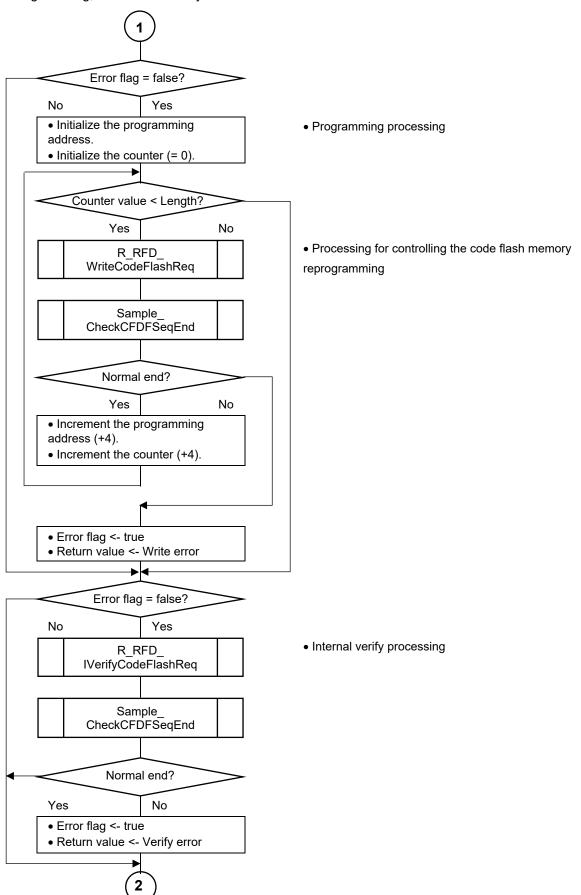

| 5.3        |        | Sample Program for Controlling the Reprogramming of the Code Flash Memory           |       |

|            | 3.2    | Sample Program for Controlling the Reprogramming of the Data Flash Memory           |       |

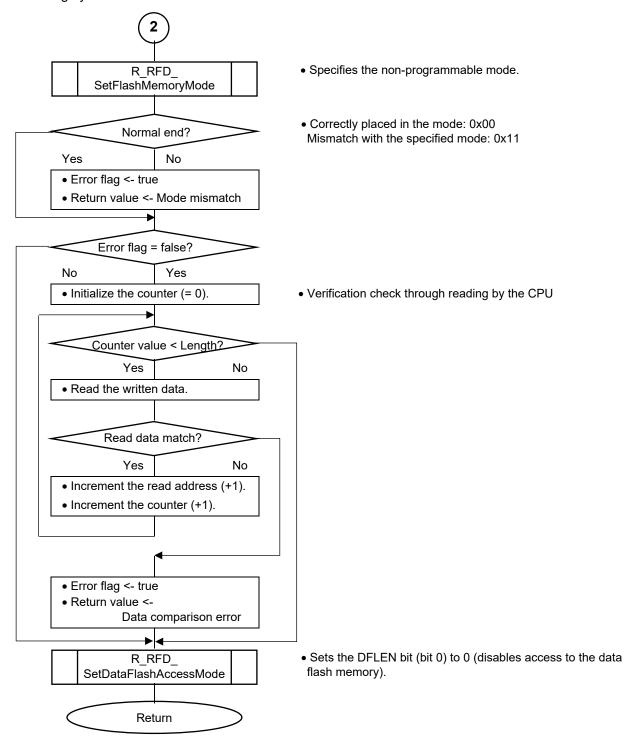

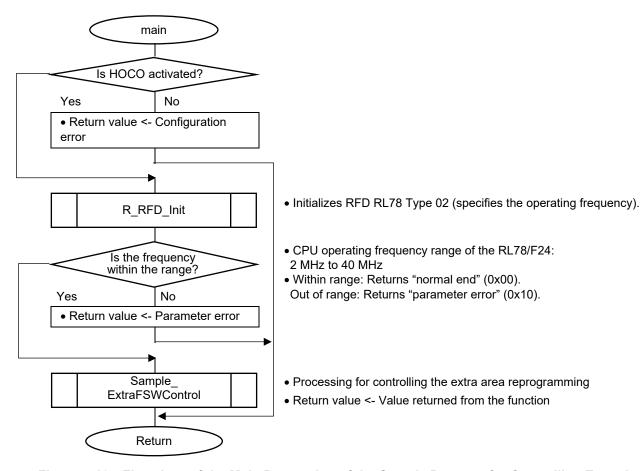

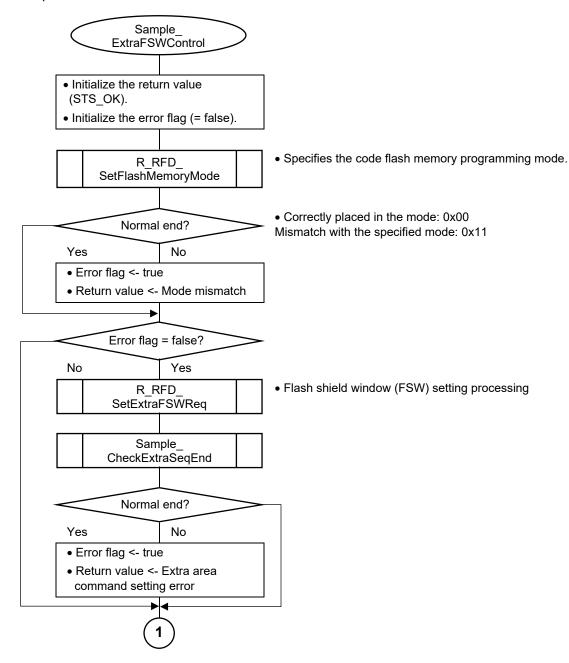

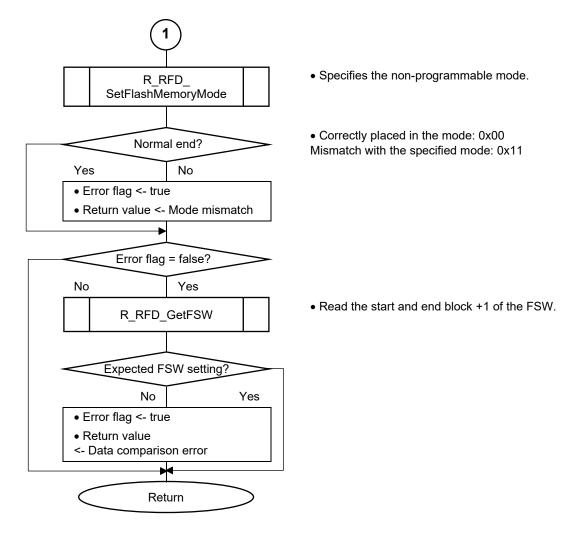

|            | 3.3    | Sample Program for Controlling the Reprogramming of the Extra Area                  |       |

| 5.3        |        | Sample Program Used in Common for Controlling the Flash Memory                      |       |

| 5.4        | •      | ifications of Sample Program Functions                                              |       |

| 5.4        |        | Sample Program Functions for Controlling the Reprogramming of the Code Flash Memory |       |

|            | 1.2    | Sample Program Functions for Controlling the Reprogramming of the Data Flash Memory |       |

| 5.4        |        | Sample Program Functions for Controlling the Reprogramming of the Extra Area        |       |

| 5.4        | +.4    | Sample Program Functions Used in Common                                             | . 128 |

| 6. Cr      | eating | g a Sample Project for RFD RL78 Type 02                                             | 131   |

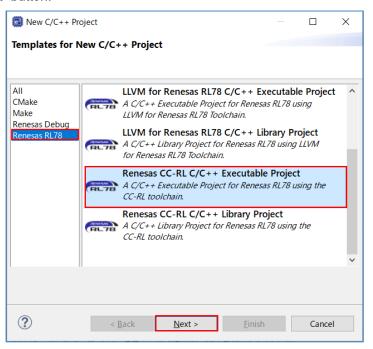

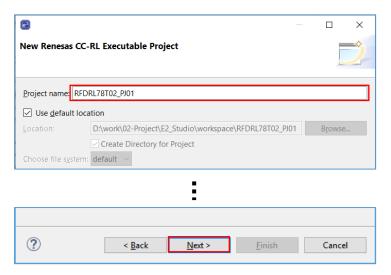

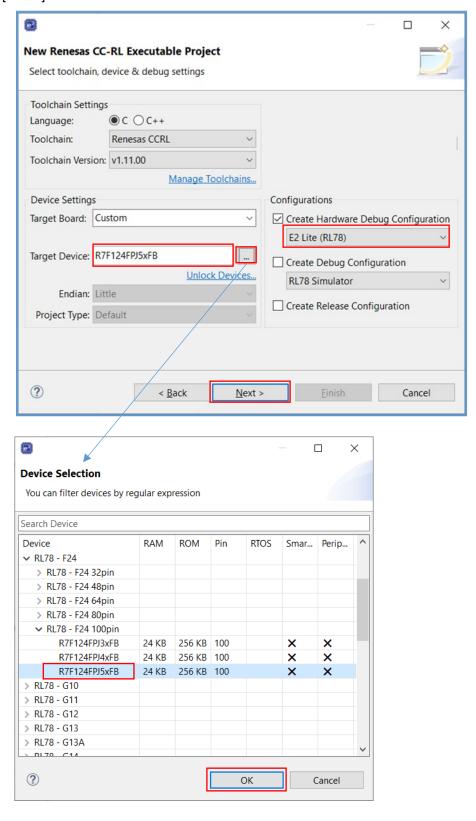

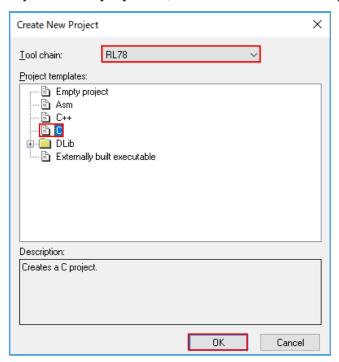

| 6.1        | Creat  | ing a Project in the Case of Using a CC-RL Compiler                                 | . 131 |

| 6.1        | 1.1    | Example of Creating a Sample Project                                                |       |

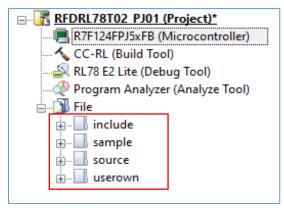

| 6.1        | 1.2    | Example of Registration of Target Folders and Target Files                          | . 135 |

|            | 1.3    | Build Tool Settings                                                                 |       |

| 6.1        |        | Debug Tool Settings                                                                 |       |

| 6.2        |        | ing a Project in the Case of Using IAR Compiler                                     |       |

| 6.2        |        | Example of Creating a Sample Project                                                |       |

|            | 2.2    | Example of Registration of Target Folders and Target Files                          |       |

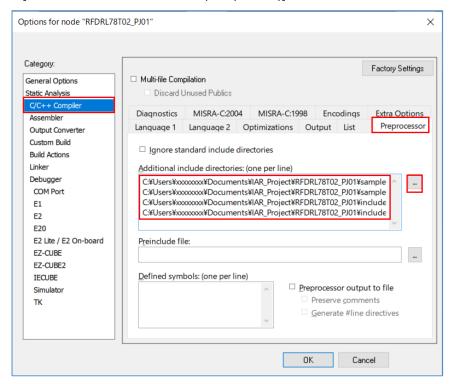

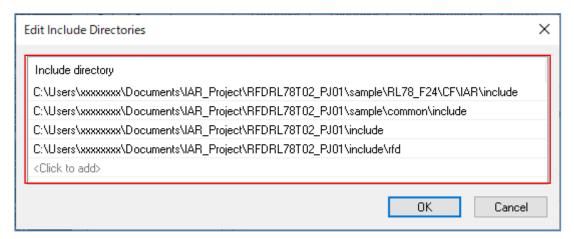

|            | 2.3    | Integrated Development Environment (IDE) Settings                                   |       |

|            | 2.4    | Linker Configuration File(.icf) Settings                                            |       |

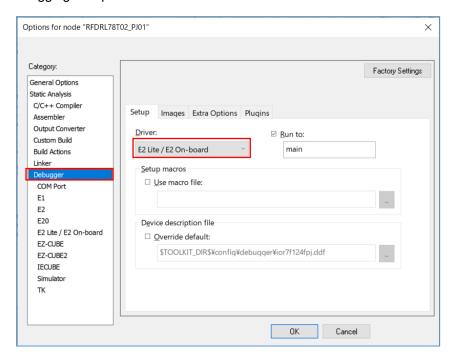

| 6.2        |        | On-chip Debug Settings                                                              |       |

| 6.3        |        | g Related to Changing Devices                                                       |       |

| 6.3        |        | CC-RL Compiler Environment Settings                                                 |       |

| 6.3        |        | IAR Compiler Environment Settings                                                   |       |

| 6.3        | 3.3    | Modifies in the Sample Program (Common to Compilers)                                | . 181 |

## RFD RL78 Type 02

| 7. Re | vision History1                      | 82  |

|-------|--------------------------------------|-----|

| 7.1   | Maior Modifications in this Revision | 182 |

## **Abbreviations**

| Abbreviation                                                                                                                                                                        | Description                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| RFD Renesas flash driver                                                                                                                                                            |                                                                                                                                |  |

| API                                                                                                                                                                                 | Application program interface                                                                                                  |  |

| BGO                                                                                                                                                                                 | Background operation Instructions in the code flash memory can be executed during reprogramming of the data flash memory.      |  |

| Flash shield window  This is a function for disabling programming and erasure of the specified window range flash areas outside the specified window range during self-programming. |                                                                                                                                |  |

| Random access memory  RAM  Randomly accessible volatile memory. It is memory for holding values that are to be chaduring program execution.                                         |                                                                                                                                |  |

| ROM                                                                                                                                                                                 | Read-only memory  Non-volatile memory. It is memory whose contents cannot be changed. The code flash memory may be called ROM. |  |

## **Terminology**

| Terminology                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Code flash memory                                                                                                                                                                                                                                                                                                                                                | Flash memory for storing application code and constant data.                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                  | Note that this memory may be abbreviated as "CF" in this document.                                                                 |

| Data flash memory                                                                                                                                                                                                                                                                                                                                                | Flash memory for storing data.                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                  | Note that this memory may be abbreviated as "DF" in this document.                                                                 |

| Extra area                                                                                                                                                                                                                                                                                                                                                       | Generic name of the configuration setting area, security setting area, block protection area, and boot swap setting area.          |

| Flash memory sequencer  The RL78 microcontroller has a dedicated circuit for controlling the flash This circuit is called the flash memory sequencer in this document. The memory sequencer consists of the code/data flash memory area seque which reprograms the code flash area or data flash area, and the extra sequencer, which reprograms the extra area. |                                                                                                                                    |

| Flash memory control mode                                                                                                                                                                                                                                                                                                                                        | The flash memory sequencer has the following modes, which indicate the programming enabled or disabled state.                      |

|                                                                                                                                                                                                                                                                                                                                                                  | - Code flash memory programming mode                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                  | - Data flash memory programming mode                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                  | - Non-programmable mode                                                                                                            |

| Code flash memory programming mode                                                                                                                                                                                                                                                                                                                               | The code flash memory (and extra area) can be reprogrammed in this mode.                                                           |

| Data flash memory programming mode                                                                                                                                                                                                                                                                                                                               | The data flash memory can be reprogrammed in this mode.                                                                            |

| Non-programmable mode                                                                                                                                                                                                                                                                                                                                            | The flash memory (and extra area) cannot be reprogrammed in this mode.                                                             |

| Self-programming                                                                                                                                                                                                                                                                                                                                                 | A method of reprogramming the flash memory by executing a user program instead of using an external flash memory programming tool. |

| Serial programming                                                                                                                                                                                                                                                                                                                                               | A method of reprogramming the flash memory using an external flash memory programming tool.                                        |

| Boot area                                                                                                                                                                                                                                                                                                                                                        | Logical area from 00000H to 03FFFH (16 Kbytes) including the reset vectors                                                         |

| Boot clusters 0 and 1                                                                                                                                                                                                                                                                                                                                            | A boot cluster is a 16-Kbyte group of blocks and either boot cluster 0 or 1 is allocated to the boot area.                         |

|                                                                                                                                                                                                                                                                                                                                                                  | Physical area name:                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                  | Boot cluster 0: 00000H to 03FFFH (logical addresses at shipment)                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                  | Boot cluster 1: 04000H to 07FFFH (logical addresses at shipment)                                                                   |

| Boot swap                                                                                                                                                                                                                                                                                                                                                        | Boot clusters 0 and 1 are swapped.                                                                                                 |

#### 1. Overview

#### 1.1 Outline

Renesas Flash Driver RL78 Type 02 (hereafter called RFD RL78 Type 02) is software for reprogramming the flash memory in the RL78/F23 and RL78/F24.

#### 1.1.1 Purpose

The purpose of this document is to give the information about RFD RL78 Type 02.

#### 1.2 Contents

The API functions of RFD RL78 Type 02 are called from the user program to reprogram the code flash memory or data flash memory.

The RFD RL78 Type 02 package includes the following.

- This user's manual

- Source code files of RFD RL78 Type 02 for controlling the data flash memory and code flash memory incorporated in the RL78/F23 and RL78/F24

- Sample programs for erasing and reprogramming the data flash memory, code flash memory, and extra area

#### 1.3 Features

RFD RL78 Type 02 reprograms the flash memory according to the specified flow of command processing for the flash memory control circuit. Each API function of RFD RL78 Type 02 consists of a single sub-function or two or more sub-functions, and the necessary processing is implemented by combinations of individual sub-functions and user processing. Such a configuration is adopted so as to flexibly handle processing dependent on the user application, such as, timeout processing in which the timeout value varies with the conditions of user application program execution.

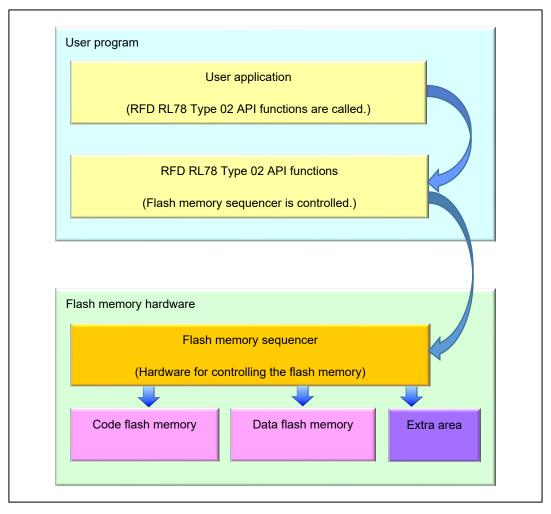

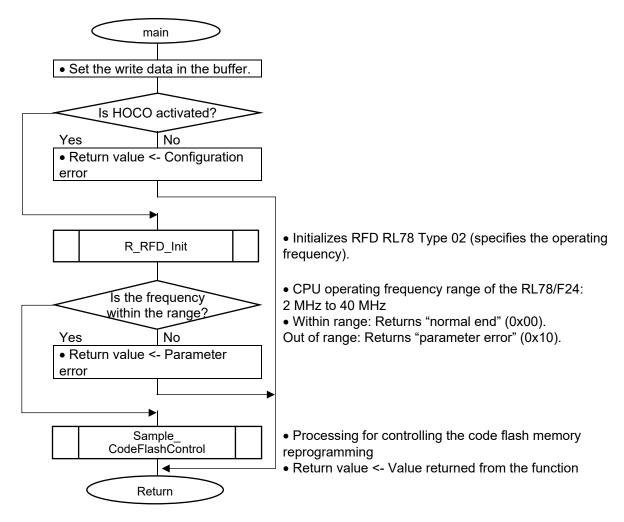

Figure 1-1 shows the flash memory control by the user application using the API functions of RFD RL78 Type 02.

RFD RL78 Type 02 provides sample programs of the processing that is implemented by combinations of two or more API functions and user programs. Refer to the sample programs when embedding the flash memory control processing in the user application.

Figure 1-1 Flash Memory Control Using API Functions of RFD RL78 Type 02

#### 1.4 Operating Environment

#### Host Computer

The operation of RFD RL78 Type 02 does not depend on the host computer but the appropriate environment for the C compiler package, debugger and emulator must be prepared. (RFD RL78 Type 02 was developed and tested on Windows10 Enterprise.)

#### • C Compiler Package

Table 1-1 shows the target C compiler packages for RFD RL78 Type 02.

Table 1-1 The Target C Compiler Packages for RFD RL78 Type 02

| Package                                  | Manufacturer        | Version        |

|------------------------------------------|---------------------|----------------|

| CC-RL (for CS+ or e <sup>2</sup> studio) | Renesas Electronics | V1.11 or later |

| IAR (Embedded Workbench)                 | IAR Systems         | V4.21 or later |

#### Emulator

Table 1-2 shows the emulator on which the operation of RFD RL78 Type 02 was confirmed.

Table 1-2 Emulator on which RFD RL78 Type 02 Operation was Confirmed

| Emulator         | Manufacturer        |

|------------------|---------------------|

| E2 emulator      | Renesas Electronics |

| E2 emulator Lite | Renesas Electronics |

#### Target MCU

RL78/F24

RL78/F23

Renesas Flash Driver(RFD) RL78 Type 02

Table 1-3 shows the Renesas Flash Driver(RFD) RL78 Type 02 supported by this manual.

Table 1-3 The RFD RL78 Type 02 Supported by This Manual

| Package          | Manufacturer        | Package Version |

|------------------|---------------------|-----------------|

| RFD RL78 Type 02 | Renesas Electronics | Ver 1.01        |

#### 1.5 Points for Caution

- (1) Reprogramming of the code flash memory or extra area

Place the reprogramming code in RAM when reprogramming the code flash memory or extra area.

- (2) Precondition for control of the data flash area

Be sure to set the DFLEN bit (bit 0) of the data flash control register (DFLCTL) to 1 (enable access to the data flash area) before controlling the data flash area.

- (3) Program execution during reprogramming of the flash memory

Self-programming in the RL78/F23 and RL78/F24 uses the flash memory sequencer to control the

reprogramming of the flash memory. In the following flash memory control modes in which the flash

memory can be reprogrammed, the CPU cannot read data from the target flash memory.

- In the code flash memory programming mode, the CPU cannot read data from the code flash memory.

The API functions of RFD RL78 Type 02 and the user program to be executed in the code flash memory programming mode should be copied from ROM to RAM in advance and executed and referenced in RAM.

- In the data flash memory programming mode, the CPU cannot read data from the data flash memory.

The data to be read in the data flash memory programming mode should be copied from the data flash memory to RAM in advance and referenced in RAM.

- (4) Points to note when using the Internal verify command

Execute the internal verify command only once for the target area immediately after writing.

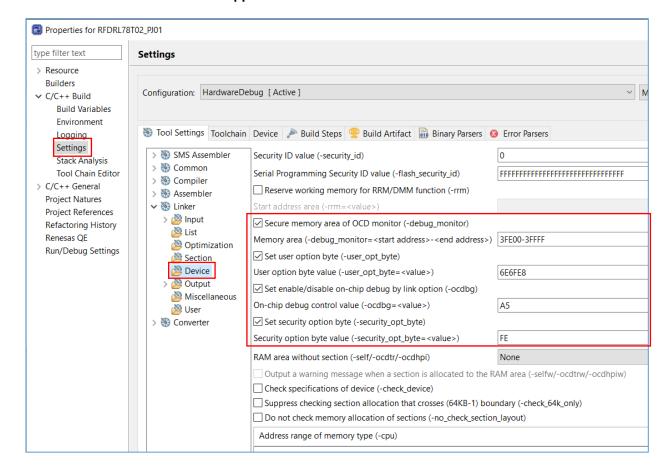

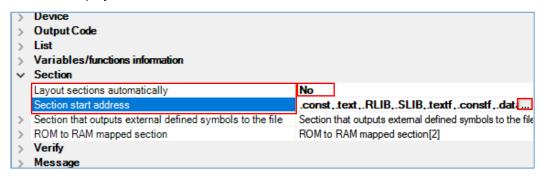

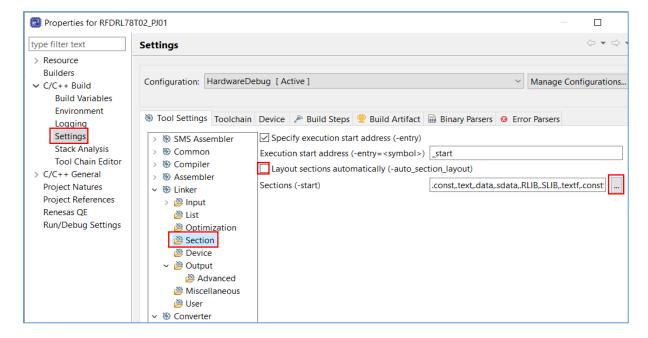

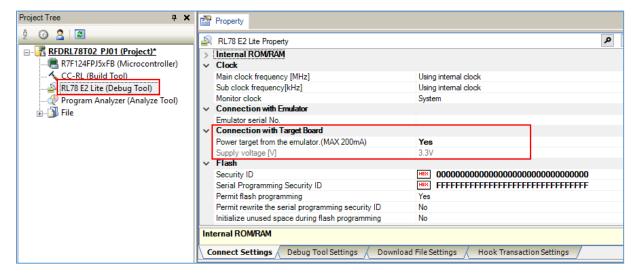

- (5) The precautions in the case of debugging self-programming with an on-chip debugger In the case which debugs self-programming with an on-chip debugger, because 128 bytes of area is used from the top address of RAM when a debugger is executed, it is necessary to vacate this area. Additionally, in case CS+ or e² studio is used as the development environment, the debugger settings need to be configured to use flash self-programming

- Example settings for CS+:

On the project, select "Connect Settings" tab from "RL78 E2 [Lite] (Debug Tool)", and set "Yes" to "Flash" "Using the flash self programming".

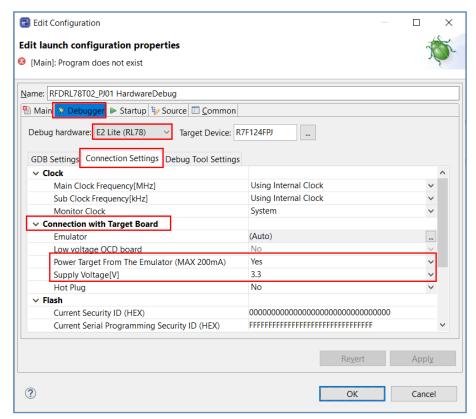

- Example settings for e<sup>2</sup> studio:

On the project, select "Property" "Run/Debug Settings", and edit the target "HardwareDebug" setting.

On the displayed screen, select "Debugger" tab "Connection Settings" tab, and set "Yes" to "Flash" "Program uses flash self programming".

- Example settings for IAR Embedded Workbench:

Put a check mark on "Hardware Setup" of the "Emulator" menu. Select "Download and Debug" from "Project" menu. And if "E2/E2Lite Hardware Setup" screen is displayed, check to "Use flash self programming" of the item of "Flash".

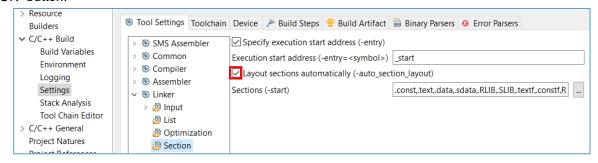

(6) The precautions in the case of executing the data copy from ROM to RAM, when using CC-RL compiler. When using CC-RL compiler, the Sample\_INITSCT\_xxxx function is called from the main function of main.c file (xxxx = CodeFlash, DataFlash or Extra). This function copies the data and the program for RFD RL78 Type 01 to RAM from ROM.

However, the following setting will be necessary if this processing is executed by the start-up routine in the cstart.asm file which is a CC-RL compiler function.

(CC-RL compiler function: "Initialization of RAM area sections by using an initialization table [V1.12 or later]")

- Set "-ram init table section" by linker.

- Set "\_USE\_RAM\_INIT\_TABLE" to the column which defines the macro of assemble options.

- \* For details, please refer to the user's manual of CC-RL compiler

Because "copy processing from ROM to RAM" of a Sample INITSCT xxxx function duplicates in this case, It is necessary to set same [Macro definition] as "Compiler Option", and to cancel processing of a Sample\_INITSCT\_xxxx function.

- Set " USE RAM INIT TABLE" to the column which defines the macro of compiler options.

#### 1.6 C Compiler Definitions

The definitions of the target compiler written in the header file (r\_rfd\_compiler.h) for RFD RL78 Type 02 are shown below.

The definitions differ between compilers. The "r\_rfd\_compiler.h" file is used to identify the current compiler and the definitions for the target compiler are used.

```

Definition of CC-RL compiler:

"__CCRL__" is defined.

#define COMPILER_CC (1)

Definition of IAR compiler:

"__IAR_SYSTEMS_ICC__" is defined

#define COMPILER_IAR (2)

```

<Descriptions in the r\_rfd\_compiler.h file>

```

/* Compiler definition */

#define COMPILER CC

(1)

#define COMPILER IAR (2)

#if defined (__CCRL__)

#define COMPILER COMPILER CC

#elif defined (__IAR_SYSTEMS_ICC__)

#define COMPILER COMPILER IAR

#else

/* Unknown compiler error */

#error "Non-supported compiler."

#endif

/* Compiler dependent definition */

#if (COMPILER CC == COMPILER)

#define R RFD FAR FUNC

far

#define R RFD NO OPERATION()

__nop()

#define R RFD DISABLE INTERRUPT()

DI()

__EI()

#define R RFD ENABLE INTERRUPT()

#define R RFD GET PSW IE STATE()

__get_psw()

#define R_RFD_IS_PSW_IE_ENABLE(u08_psw_ie_state) (0u != (u08_psw_ie_state & 0x80u))

#elif (COMPILER IAR == COMPILER)

__far_func

#define R RFD FAR FUNC

#define R RFD NO OPERATION()

no operation()

#define R_RFD_DISABLE_INTERRUPT() __disable_interrupt()

#define R RFD ENABLE INTERRUPT()

enable interrupt()

__get_interrupt_state()

#define R RFD GET PSW IE STATE()

#define R_RFD_IS_PSW_IE_ENABLE(u08_psw_ie_state) (0u != (u08_psw_ie_state & 0x80u))

#else

/* Unknown compiler error */

#error "Non-supported compiler."

#endif

```

• C Compiler Options

The contents of the C compiler option setup which normal operation can be checking are shown below.

- [CC-RL(CS+)]

Major compile options:

-cpu=S3 -g -g\_line -lang=c99

- [IAR (Embedded Workbench)]

Major compile options:

--core s3 --calling\_convention v2 --code\_model far --data\_model near -e -Ol --no\_cse --no\_unroll --no\_inline --no\_code\_motion --no\_tbaa --no\_cross\_call --no\_scheduling --no\_clustering --debug

## 2. System Configuration

#### 2.1 File Structure

#### 2.1.1 Folder Structure

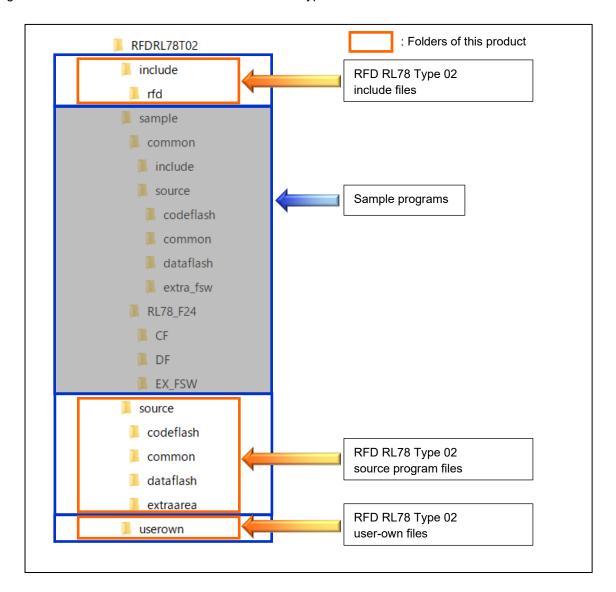

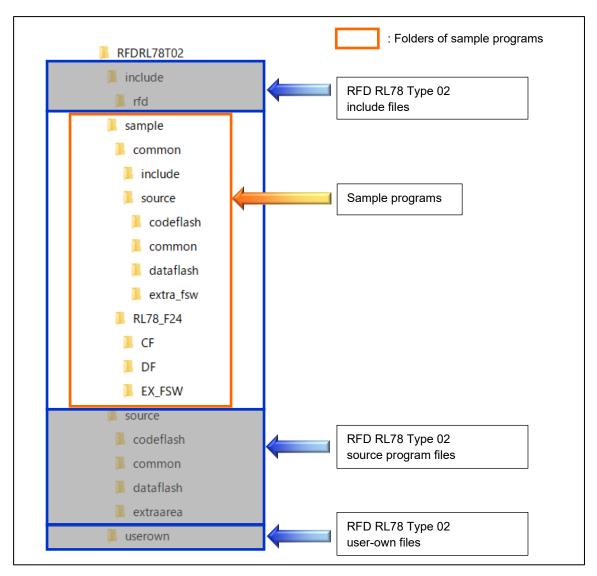

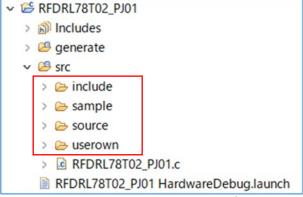

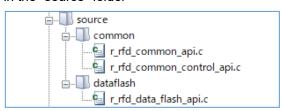

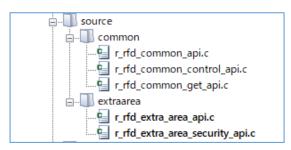

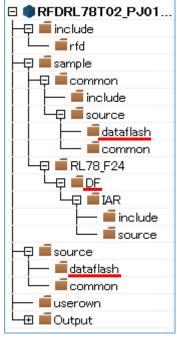

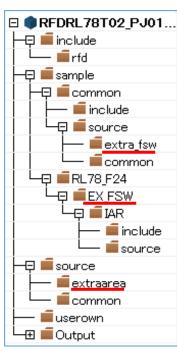

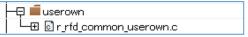

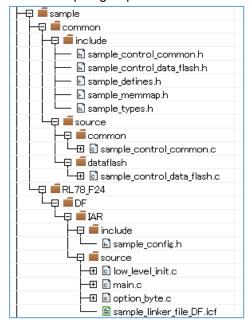

Figure 2-1 shows the folder structure of RFD RL78 Type 02.

Figure 2-1 Folder Structure of RFD RL78 Type 02

Note: Figure 2-1 shows an example of using RL78/F24. Refer to "5.1.1 Folder Structure" for the sample folder.

#### 2.1.2 List of Files

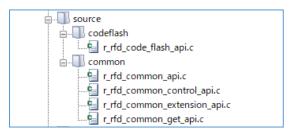

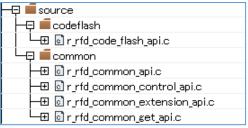

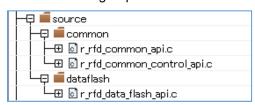

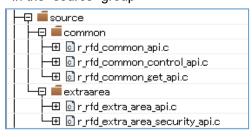

#### 2.1.2.1 List of Source Files

Table 2-1 shows the program source files in the "source\common\" folder.

Table 2-1 Program Source Files in the "source\common\" Folder

| No. | Source File Name             | Description                                                                                               |

|-----|------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1   | r_rfd_common_api.c           | This file contains the API functions for settings used in common for flash memory control.                |

| 2   | r_rfd_common_control_api.c   | This file contains the API functions for command control used in common for flash memory control.         |

| 3   | r_rfd_common_get_api.c       | This file contains the API functions for information acquisition used in common for flash memory control. |

| 4   | r_rfd_common_extension_api.c | This file contains the API functions for extended facilities used in common for flash memory control.     |

Table 2-2 shows the program source file in the "source\codeflash\" folder.

Table 2-2 Program Source File in the "source\codeflash\" Folder

| No. | Source File Name       | Description                                                         |

|-----|------------------------|---------------------------------------------------------------------|

| 1   | r_rfd_code_flash_api.c | This file contains the API functions for code flash memory control. |

Table 2-3 shows the program source file in the "source\dataflash\" folder.

Table 2-3 Program Source File in the "source\dataflash\" Folder

| No. | Source File Name       | Description                                                         |

|-----|------------------------|---------------------------------------------------------------------|

| 1   | r_rfd_data_flash_api.c | This file contains the API functions for data flash memory control. |

Table 2-4 shows the program source files in the "source\extraarea\" folder.

Table 2-4 Program Source File in the "source\extraarea\" Folder

| No. | Source File Name                | Description                                                                          |

|-----|---------------------------------|--------------------------------------------------------------------------------------|

| 1   | r_rfd_extra_area_api.c          | This file contains the API functions for extra area control.                         |

| 2   | r_rfd_extra_area_security_api.c | This file contains the API functions for the security facilities for the extra area. |

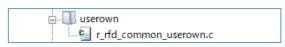

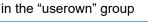

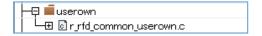

Table 2-5 shows the program source file in the "userown\" folder.

Table 2-5 Program Source File in the "userown\" Folder

| No. | Source File Name       | Description                                                                                    |

|-----|------------------------|------------------------------------------------------------------------------------------------|

| 1   | r_rfd_common_userown.c | This file contains the hook functions for user processing to be performed in RFD RL78 Type 02. |

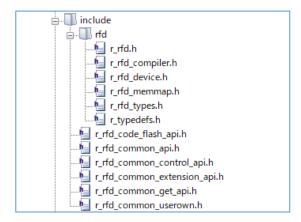

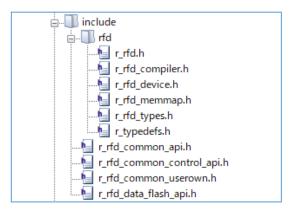

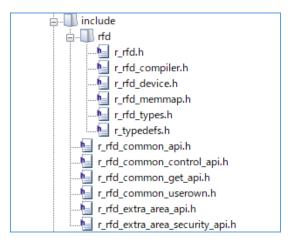

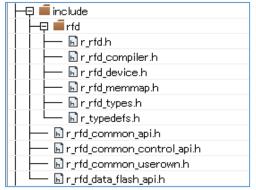

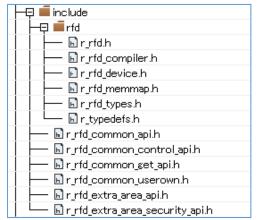

#### 2.1.2.2 Header File List of Header Files

Table 2-6 shows the program header files in the "include\rfd" folder.

Table 2-6 Program Header Files in the "include\rfd" Folder

| No. | Header File Name | Description                                                                                 |

|-----|------------------|---------------------------------------------------------------------------------------------|

| 1   | r_rfd.h          | Common header file.                                                                         |

|     |                  | This file needs to be included when RFD RL78 Type 02 is used.                               |

| 2   | r_rfd_compiler.h | This file describes the definitions that differ between compilers used in RFD RL78 Type 02. |

| 3   | r_rfd_memmap.h   | This file defines macros to describe sections used in RFD RL78 Type 02.                     |

| 4   | r_rfd_device.h   | This file defines the hardware-specific macros used in RFD RL78 Type 02.                    |

| 5   | r_rfd_types.h    | This file defines the types of variables used in RFD RL78 Type 02.                          |

| 6   | r_typedefs.h     | This file defines the types of data used in RFD RL78 Type 02.                               |

Table 2-7 shows the program header files in the "include\" folder.

Table 2-7 Program Header Files in the "include\" Folder

| No. | Header File Name                | Description                                                                                                                            |

|-----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1   | r_rfd_common_api.h              | This file defines the prototype declarations of the API functions for setting used in common for flash memory control.                 |

| 2   | r_rfd_code_flash_api.h          | This file defines the prototype declarations of the API functions for code flash memory control.                                       |

| 3   | r_rfd_common_control_api.h      | This file defines the prototype declarations of the API functions for command control used in common for flash memory control.         |

| 4   | r_rfd_common_get_api.h          | This file defines the prototype declarations of the API functions for information acquisition used in common for flash memory control. |

| 5   | r_rfd_common_extension_api.h    | This file defines the prototype declarations of the API functions for extended facilities used in common for flash memory control.     |

| 6   | r_rfd_common_userown.h          | This file defines the prototype declarations of the hook functions for user processing to be performed in RFD RL78 Type 02.            |

| 7   | r_rfd_data_flash_api.h          | This file defines the prototype declarations of the API functions for data flash memory control.                                       |

| 8   | r_rfd_extra_area_api.h          | This file defines the prototype declarations of the API functions for extra area control.                                              |

| 9   | r_rfd_extra_area_security_api.h | This file defines the prototype declarations of the API functions for the security facilities for the extra area.                      |

#### 2.2 Resources of RL78/F23 and RL78/F24

#### 2.2.1 **Memory Map**

Table 2-8 shows the memory map (code flash memory (CF), data flash memory (DF), and RAM) of the RL78/F23 and RL78/F24.

Table 2-8 Memory Map (ROM, Data Flash, and RAM)

| RL78 | Device                        | Code Flash Memory: CF                             | RAM                       |  |

|------|-------------------------------|---------------------------------------------------|---------------------------|--|

| F23  | R7F123FxG (x = B, G, L, M)    | 128 Kbytes (00000H-1FFFFH)                        | 12 Kbytes (FCF00H-FFEFFH) |  |

|      | Data Flash Memory: DF         | 8 Kbytes (F1000H-F2FFFH) All RL78/F23             |                           |  |

| F24  | R7F124FxJ (x = B, G, L, M, P) | 256 Kbytes (00000H-3FFFFH) 24 Kbytes (F9F00H-FFEF |                           |  |

|      | Data Flash Memory: DF         | 16 Kbytes (F1000H-F4FFFH) All RL78/F24            |                           |  |

#### 2.2.2 The Allocation of Blocks

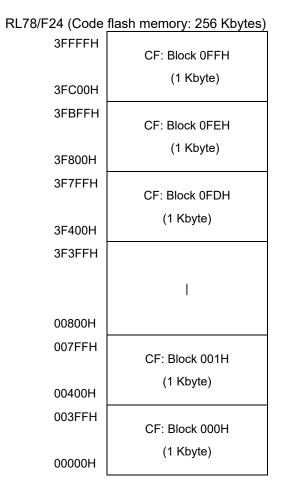

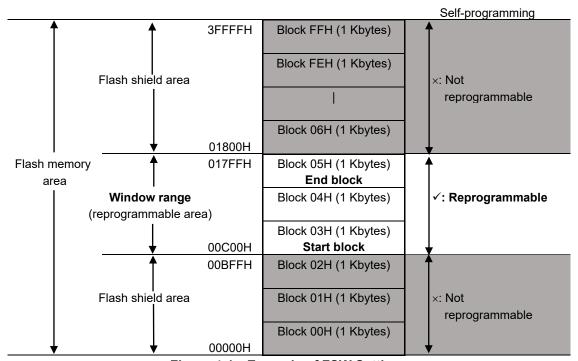

Figure 2-2 and Figure 2-3 shows the allocation of blocks in code flash memory (CF) and data flash memory (DF) for RL78/F24.

Figure 2-2 Blocks in the Code Flash Memory

| RL78/F24 (Data flash memory: 16 Kbytes) |                |  |  |

|-----------------------------------------|----------------|--|--|

| F4FFFH                                  | DF: Block 00FH |  |  |

| F4C00H                                  | (1 Kbyte)      |  |  |

| F4BFFH                                  | DF: Block 00EH |  |  |

| F4800H                                  | (1 Kbyte)      |  |  |

|                                         |                |  |  |

|                                         |                |  |  |

|                                         | l              |  |  |

| F1800H                                  |                |  |  |

| F17FFH                                  | DF: Block 001H |  |  |

| F1400H                                  | (1 Kbyte)      |  |  |

| F13FFH                                  | DF: Block 000H |  |  |

| F1000H                                  | (1 Kbyte)      |  |  |

Figure 2-3 Blocks in the Data Flash Memory

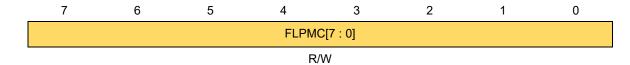

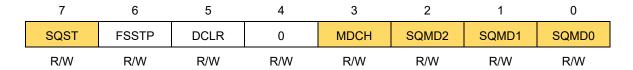

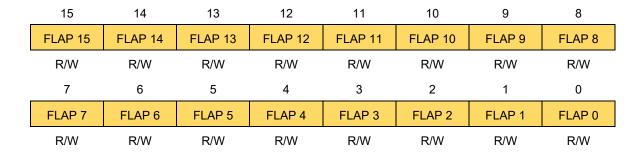

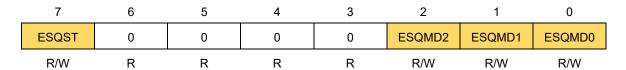

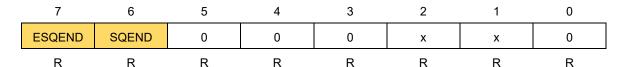

#### 2.2.3 List of Registers Related to Flash Memory Sequencer Control

Table 2-9 shows the registers in the RL78/F23 and RL78/F24 used by RFD RL78 Type 02.

Table 2-9 Registers in the RL78/F23 and RL78/F24 Used by RFD RL78 Type 02

| Base<br>Address | Offset | Register Name | Size    | Function Name and Note                          |

|-----------------|--------|---------------|---------|-------------------------------------------------|

| F0000H          | 90H    | DFLCTL        | 1 byte  | Data flash control register                     |

|                 | C0H    | FLPMC         | 1 byte  | Flash programming mode control register         |

|                 | C1H    | FLARS         | 1 byte  | Flash area select register                      |

|                 | C2H    | FLAPL         | 2 bytes | Flash address pointer register L                |

|                 | C4H    | FLAPH         | 1 byte  | Flash address pointer register H                |

|                 | C5H    | FSSQ          | 1 byte  | Flash memory sequencer control register         |

|                 | C6H    | FLSEDL        | 2 bytes | Flash end address pointer register L            |

|                 | C8H    | FLSEDH        | 1 byte  | Flash end address pointer register H            |

|                 | C9H    | FLRST         | 1 byte  | Flash registers initialization register         |

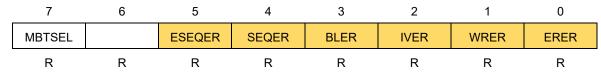

|                 | CAH    | FSASTL        | 1 byte  | Flash memory sequencer status register L        |

|                 | СВН    | FSASTH        | 1 byte  | Flash memory sequencer status register H        |

|                 | CCH    | FLWL          | 2 bytes | Flash write buffer register L                   |

|                 | CEH    | FLWH          | 2 bytes | Flash write buffer register H                   |

| FFF00H          | В0Н    | FLSEC         | 2 bytes | Flash security flag monitor register            |

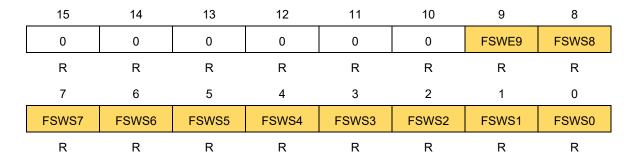

|                 | B2H    | FLFSWS        | 2 bytes | Flash FSW monitoring register S                 |

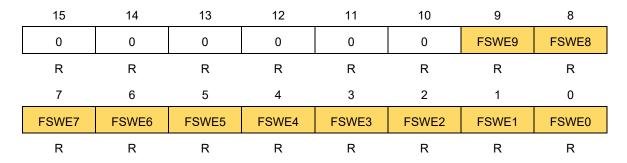

|                 | B4H    | FLFSWE        | 2 bytes | Flash FSW monitoring register E                 |

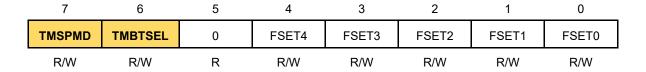

|                 | В6Н    | FSSET         | 1 byte  | Flash memory sequencer initial setting register |

|                 | В7Н    | FSSE          | 1 byte  | Extra area sequencer control register           |

|                 | C0H    | PFCMD         | 1 byte  | Flash protect command register                  |

|                 | C1H    | PFS           | 1 byte  | Flash status register                           |

|                 | C6H    | FLWE          | 1 byte  | Flash ECC write buffer register                 |

#### 2.3 Resources Used in RFD RL78 Type 02

#### 2.3.1 Sections Used in RFD RL78 Type 02

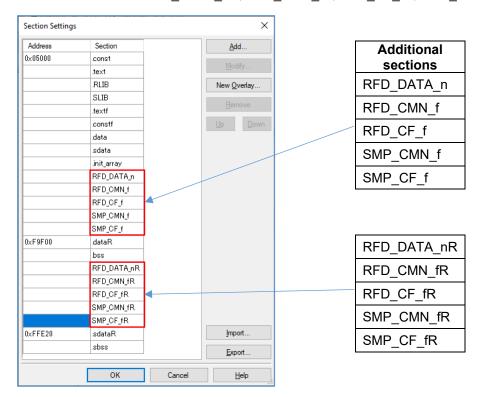

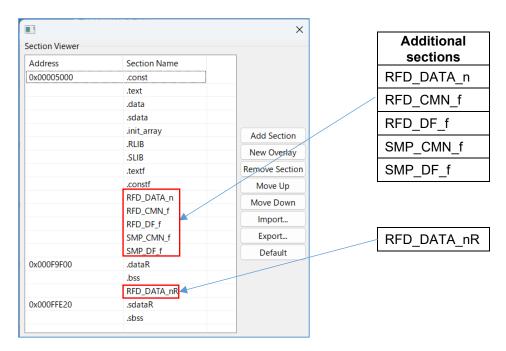

#### 2.3.1.1 Sections Used for Reprogramming of the Code Flash Memory

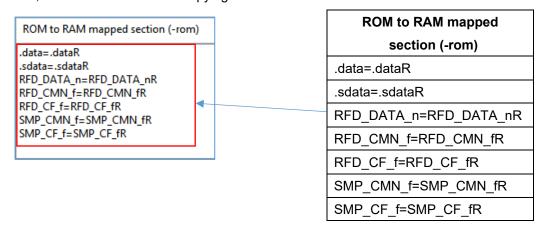

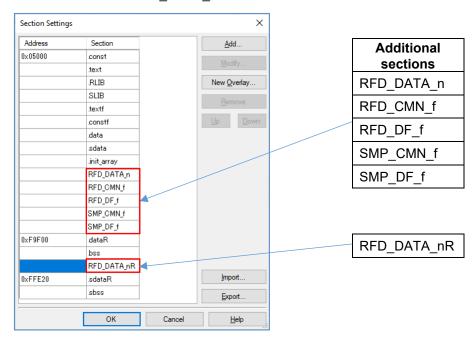

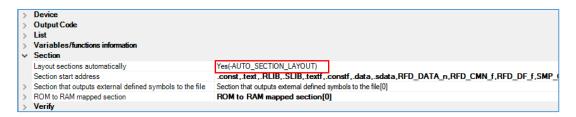

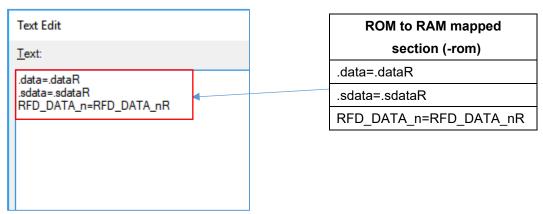

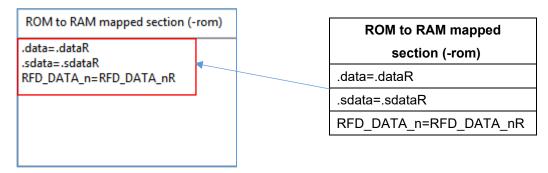

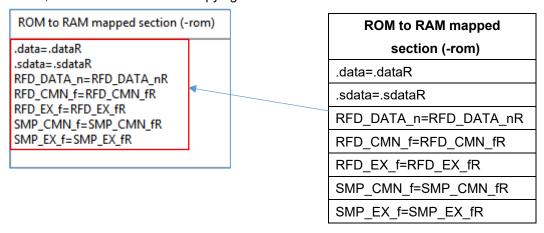

The CPU cannot read from the code flash memory in the "code flash memory programming mode" used for reprogramming of the code flash memory. The sections allocated as program areas should be copied from ROM to RAM in advance and programs should be executed in RAM. The initial values for the initialized global variable section (RFD\_DATA) allocated to RAM should be copied from ROM to RAM in advance according to the directions of the target compiler.

Table 2-10 shows the sections used for reprogramming of the code flash memory and allocations of the sections.

Table 2-10 Sections Used for Reprogramming of the Code Flash Memory

| Section Name                                                                        | Description                                                                     | Allocation |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------|

| RFD_CMN                                                                             | FD_CMN Program section of API functions used in common for flash memory control |            |

| RFD_CF                                                                              | Program section of API functions for code flash memory control                  | RAM        |

| RFD_DATA                                                                            | Data section for initialized global variables                                   | RAM        |

| SMP_CMN Program section of sample functions used in common for flash memory control |                                                                                 | RAM        |

| SMP_CF                                                                              | Program section of sample functions for code flash memory control               | RAM        |

#### 2.3.1.2 Sections Used for Reprogramming of the Data Flash Memory

The initial values for the initialized global variable section (RFD\_DATA) allocated to RAM should be copied from ROM to RAM in advance according to the directions of the target compiler.

Table 2-11 shows the sections used for reprogramming of the data flash memory and allocations of the sections.

Table 2-11 Sections Used for Reprogramming of the Data Flash Memory

| Section Name                                                                        | Description                                                                      | Allocation |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|

| RFD_CMN                                                                             | RFD_CMN Program section of API functions used in common for flash memory control |            |

| RFD_DF                                                                              | Program section of API functions for data flash memory control                   | ROM        |

| RFD_DATA                                                                            | DATA Data section for initialized global variables                               |            |

| SMP_CMN Program section of sample functions used in common for flash memory control |                                                                                  | ROM        |

| SMP_DF                                                                              | Program section of sample functions for data flash memory control                | ROM        |

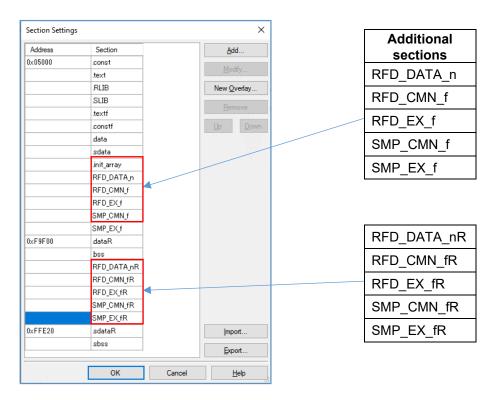

#### 2.3.1.3 Sections Used for Reprogramming of the Extra Area

The CPU cannot read from the code flash memory in the "code flash memory programming mode" used for reprogramming of the extra flash memory. The sections allocated as program areas should be copied from ROM to RAM in advance and programs should be executed in RAM. The initial values for the initialized global variable section (RFD\_DATA) allocated to RAM should be copied from ROM to RAM in advance according to the directions of the target compiler.

Table 2-12 shows the sections used for reprogramming of the extra area and allocations of the sections.

Table 2-12 Sections Used for Reprogramming of the Extra Area

| Section Name | Section Name Description                                                    |     |

|--------------|-----------------------------------------------------------------------------|-----|

| RFD_CMN      | Program section of API functions used in common for flash memory control    | RAM |

| RFD_EX       | Program section of API functions for extra area control                     | RAM |

| RFD_DATA     | Data section for initialized global variables                               | RAM |

| SMP_CMN      | Program section of sample functions used in common for flash memory control | RAM |

| SMP_EX       | Program section of sample functions for extra area control                  | RAM |

#### 2.3.2 Code Size and Stack Size which API Functions Use

Table 2-13 shows code size and stack size which API functions for RFD RL78 Type 02 use.

Table 2-13 Code Size and Stack Size which API Functions for RFD RL78 Type 02 Use

| ADIN                             | Code Size (Bytes) |     | Stack Size (Bytes) |     |

|----------------------------------|-------------------|-----|--------------------|-----|

| API Name                         | CC-RL             | IAR | CC-RL              | IAR |

| R_RFD_Init                       | 37                | 44  | 4                  | 4   |

| R_RFD_SetDataFlashAccessMode     | 36                | 20  | 10                 | 10  |

| R_RFD_SetFlashMemoryMode         | 264               | 284 | 14                 | 16  |

| R_RFD_CheckFlashMemoryMode       | 26                | 36  | 4                  | 4   |

| R_RFD_CheckCFDFSeqEndStep1       | 13                | 24  | 4                  | 6   |

| R_RFD_CheckExtraSeqEndStep1      | 13                | 23  | 4                  | 6   |

| R_RFD_CheckCFDFSeqEndStep2       | 8                 | 19  | 4                  | 6   |

| R_RFD_CheckExtraSeqEndStep2      | 6                 | 19  | 4                  | 6   |

| R_RFD_GetSeqErrorStatus          | 8                 | 8   | 4                  | 4   |

| R_RFD_ClearSeqRegister           | 11                | 10  | 4                  | 4   |

| R_RFD_ForceStopSeq               | 6                 | 5   | 4                  | 4   |

| R_RFD_ForceReset                 | 2                 | 2   | 4                  | 4   |

| R_RFD_SetBootAreaImmediately     | 15                | 19  | 4                  | 4   |

| R_RFD_GetSecurityAndBootFlags    | 5                 | 5   | 4                  | 4   |

| R_RFD_GetFSW                     | 22                | 24  | 8                  | 6   |

| r_rfd_wait_count                 | 19                | 19  | 6                  | 6   |

| R_RFD_EraseCodeFlashReq          | 34                | 43  | 4                  | 4   |

| R_RFD_WriteCodeFlashReq          | 28                | 58  | 4                  | 6   |

| R_RFD_BlankCheckCodeFlashReq     | 34                | 43  | 4                  | 4   |

| R_RFD_IVerifyCodeFlashReq        | 34                | 43  | 4                  | 4   |

| R_RFD_EraseDataFlashReq          | 29                | 41  | 4                  | 4   |

| R_RFD_WriteDataFlashReq          | 20                | 27  | 4                  | 6   |

| R_RFD_BlankCheckDataFlashReq     | 34                | 76  | 6                  | 12  |

| R_RFD_IVerifyDataFlashReq        | 34                | 76  | 6                  | 12  |

| R_RFD_SetExtraEraseProtectReq    | 24                | 29  | 4                  | 4   |

| R_RFD_SetExtraWriteProtectReq    | 24                | 29  | 4                  | 4   |

| R_RFD_SetExtraBootAreaProtectReq | 24                | 29  | 4                  | 4   |

| R_RFD_SetExtraBootAreaReq        | 48                | 77  | 4                  | 6   |

| R_RFD_SetExtraFSWReq             | 21                | 30  | 4                  | 4   |

| R_RFD_HOOK_EnterCriticalSection  | 9                 | 9   | 4                  | 4   |

| R_RFD_HOOK_ExitCriticalSection   | 11                | 10  | 4                  | 4   |

## 3. API Functions of RFD RL78 Type 02

## 3.1 List of API Functions of RFD RL78 Type 02

#### 3.1.1 API Functions Used in Common for Flash Memory Control

Table 3-1 shows the API functions used in common for flash memory control in RFD RL78 Type 02.

Table 3-1 API Functions Used in Common for Flash Memory Control in RFD RL78 Type 02

|    | API Name                      | Overview                                                                                                                                                                         |

|----|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | R_RFD_Init                    | Sets the frequency specified by the parameter in the flash memory sequencer and initializes RFD RL78 Type 02.                                                                    |

| 2  | R_RFD_SetDataFlashAccessMode  | Enables or disables access to the data flash memory according to the parameter setting.                                                                                          |

| 3  | R_RFD_SetFlashMemoryMode      | Places the flash memory sequencer in the flash memory control mode specified by the parameter and then sets the specified CPU operating frequency in the flash memory sequencer. |

| 4  | R_RFD_CheckFlashMemoryMode    | Checks if the flash memory sequencer is in the mode specified by the parameter.                                                                                                  |

| 5  | R_RFD_CheckCFDFSeqEndStep1    | Checks if the operation of the activated code/data flash memory area sequencer has been completed.                                                                               |

| 6  | R_RFD_CheckExtraSeqEndStep1   | Checks if the operation of the activated extra area sequencer has been completed.                                                                                                |

| 7  | R_RFD_CheckCFDFSeqEndStep2    | Checks if the command operation has been completed after the flash memory sequencer control register is cleared.                                                                 |

| 8  | R_RFD_CheckExtraSeqEndStep2   | Checks if the command operation has been completed after the flash memory sequencer control register is cleared.                                                                 |

| 9  | R_RFD_GetSeqErrorStatus       | Acquires the information on errors that occurred during command execution in the code/data flash memory area sequencer or extra area sequencer.                                  |

| 10 | R_RFD_ClearSeqRegister        | Clears the registers for controlling the code/data flash memory area sequencer and extra area sequencer                                                                          |

| 11 | R_RFD_ForceStopSeq            | Forcibly stops the operation of the code/data flash memory area sequencer.                                                                                                       |

| 12 | R_RFD_ForceReset              | Generates an internal reset of the CPU.                                                                                                                                          |

| 13 | R_RFD_SetBootAreaImmediately  | Allocates the boot cluster specified by the parameter to the boot area (00000H to 03FFFH) immediately.                                                                           |

| 14 | R_RFD_GetSecurityAndBootFlags | Acquires the information on the security flags (protection flags) and boot area switching flag.                                                                                  |

| 15 | R_RFD_GetFSW                  | Acquires the range of the flash shield window, the flash shield window mode, and the protection flag value.                                                                      |

| 16 | r_rfd_wait_count              | Executes a software loop to wait for the time specified by the parameter (time count in units of 1 µs).                                                                          |

#### 3.1.2 API Functions for Code Flash Memory Control

Table 3-2 shows the API functions for code flash memory control in RFD RL78 Type 02.

Table 3-2 API Functions for Code Flash Memory Control in RFD RL78 Type 02

|   | API Name                     | Overview                                                                                                                 |

|---|------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1 | R_RFD_EraseCodeFlashReq      | Activates the code/data flash memory area sequencer and begins the erasure of the code flash memory (one block).         |

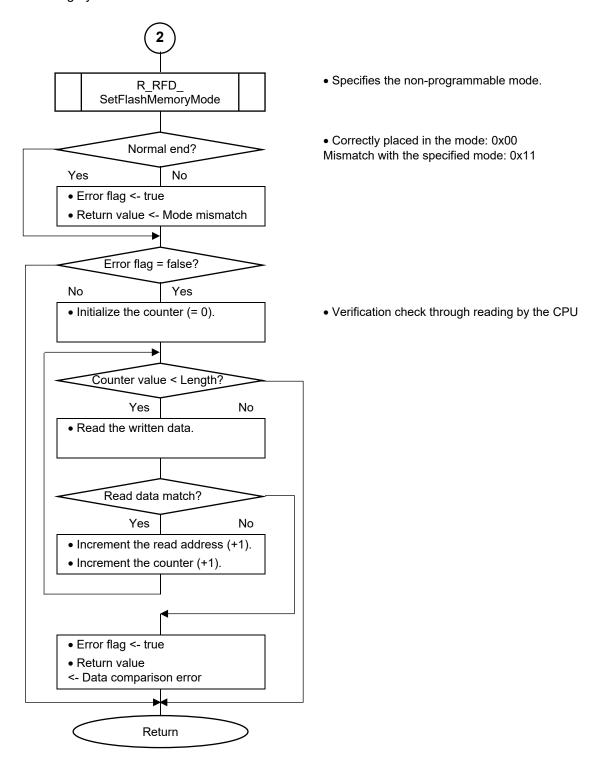

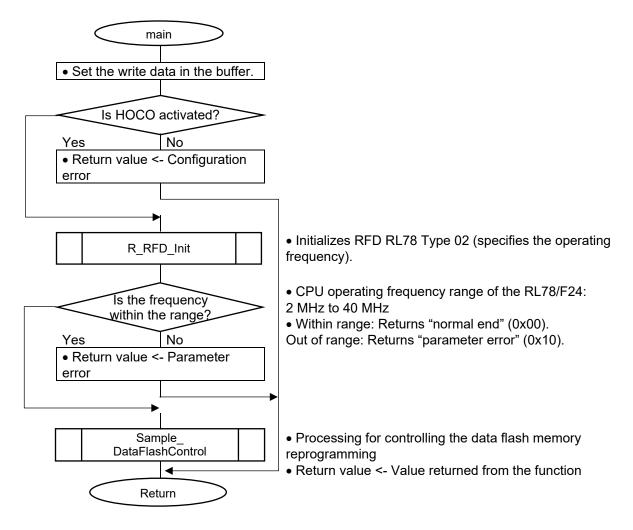

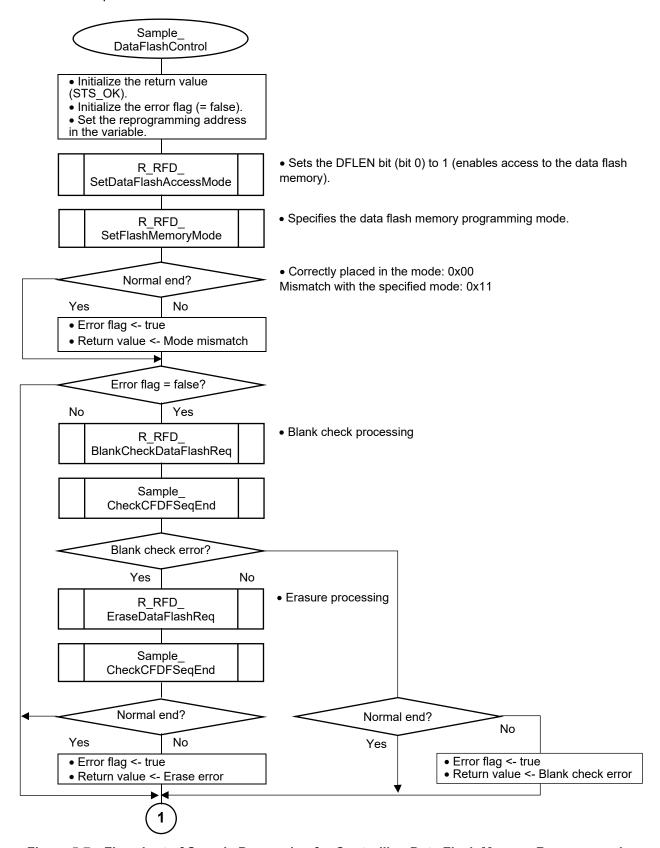

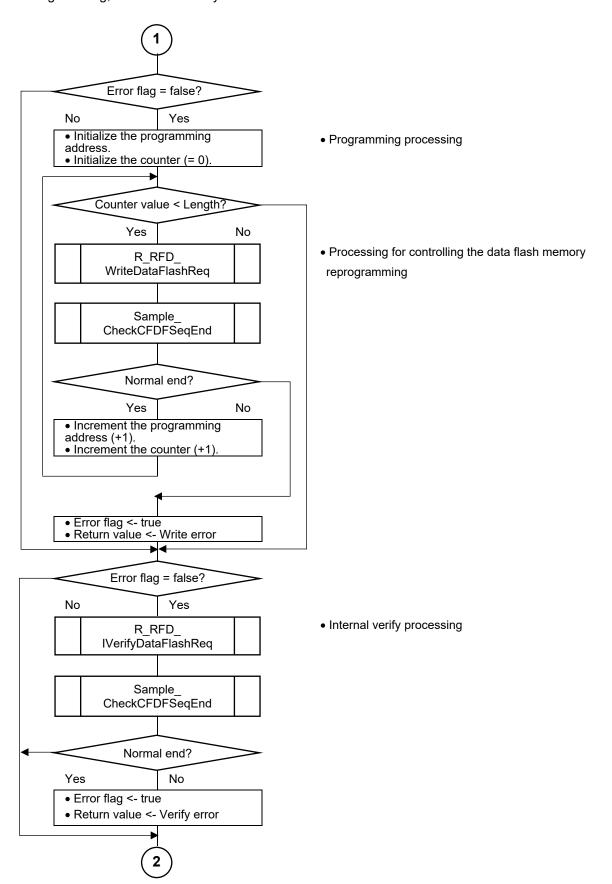

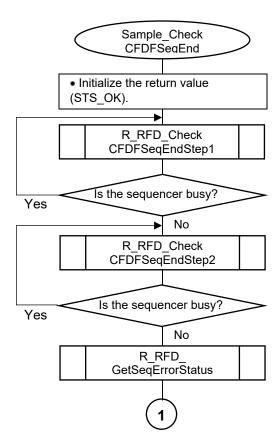

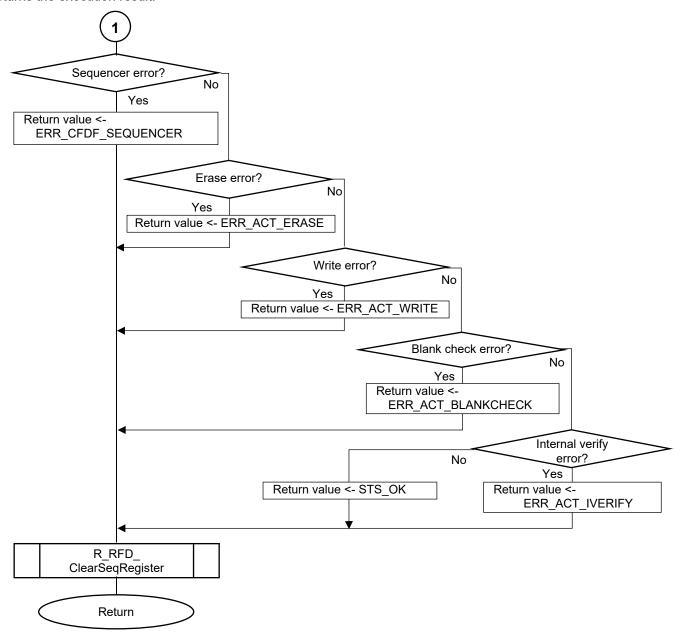

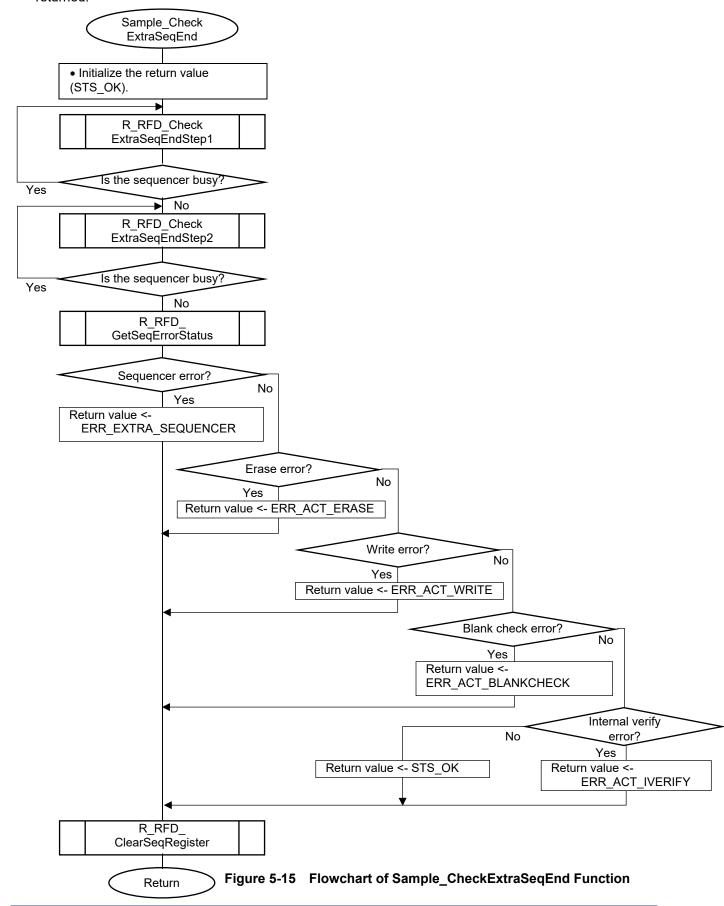

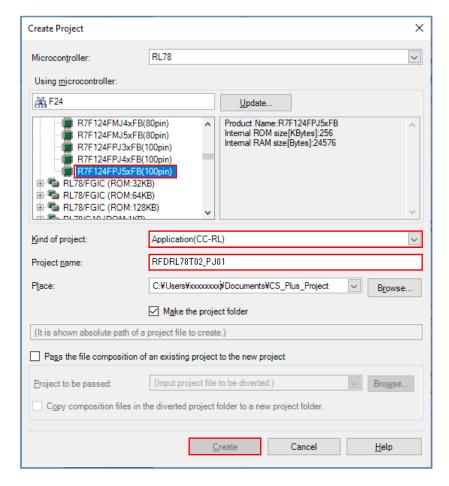

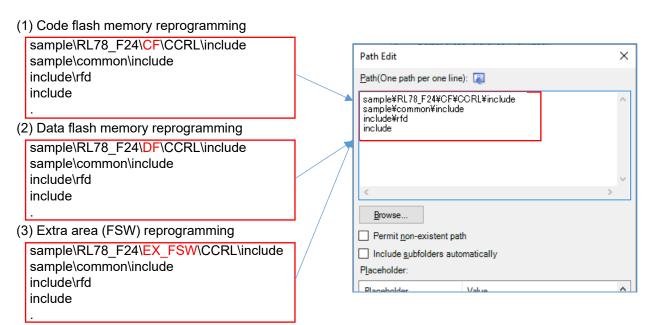

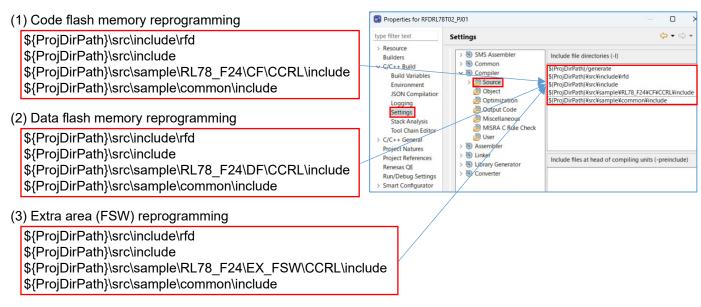

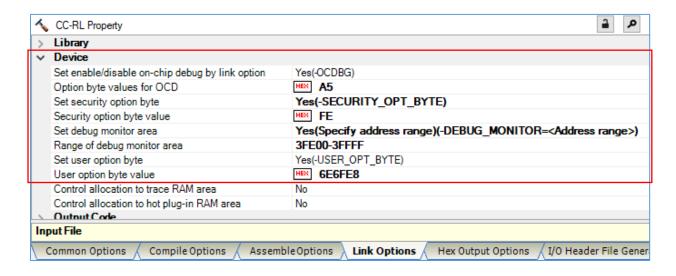

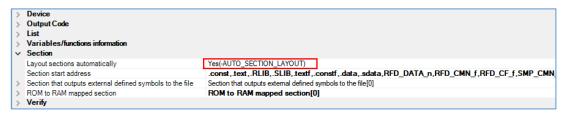

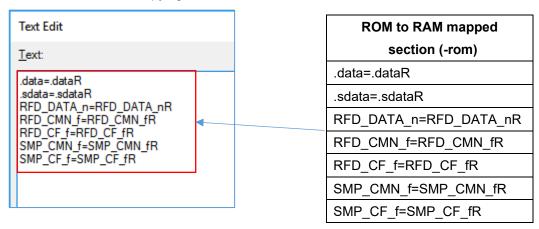

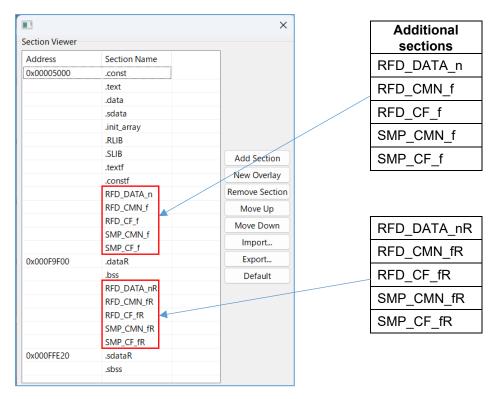

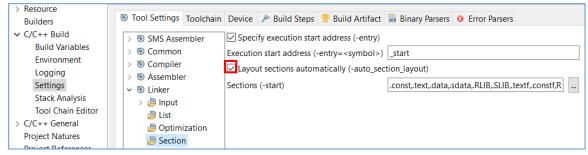

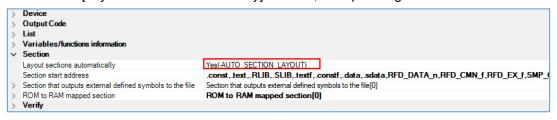

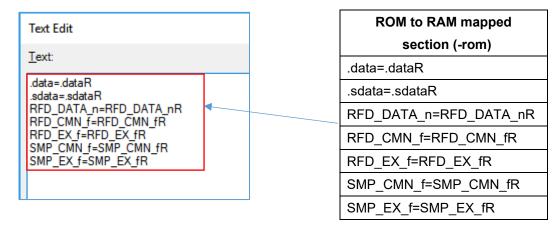

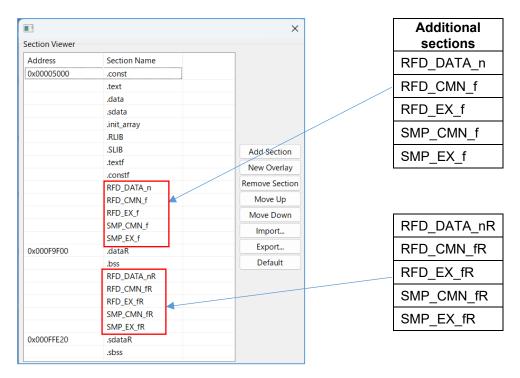

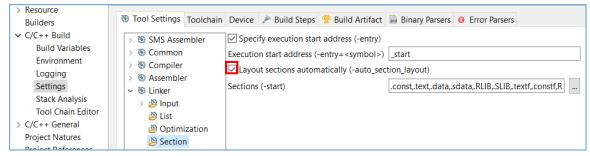

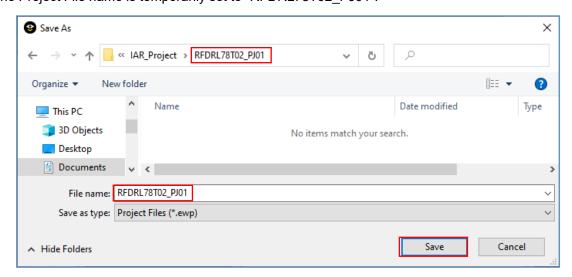

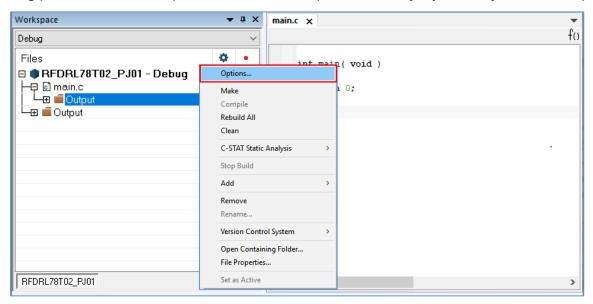

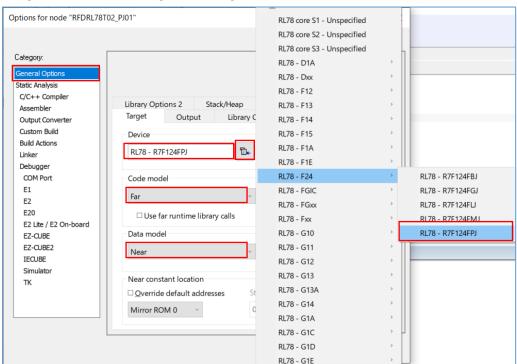

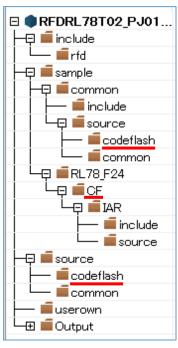

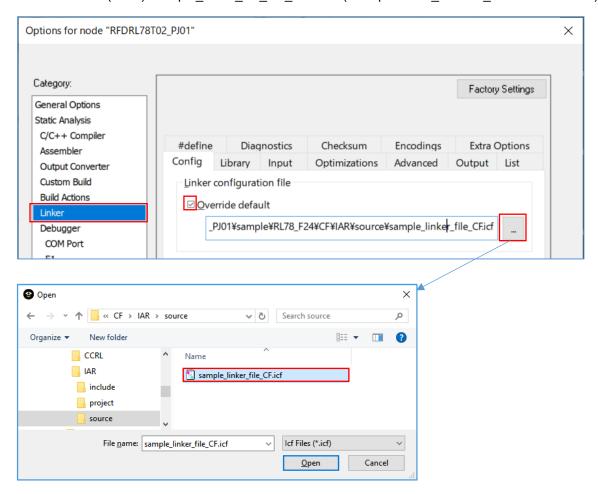

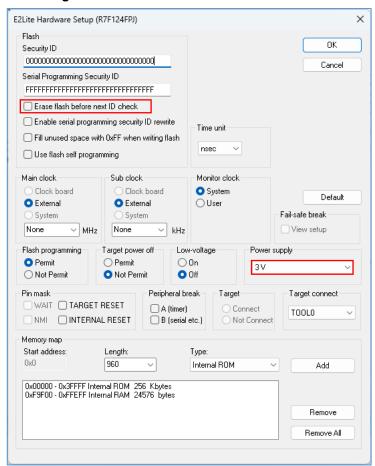

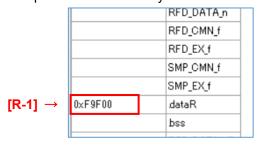

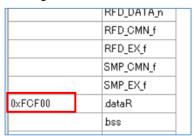

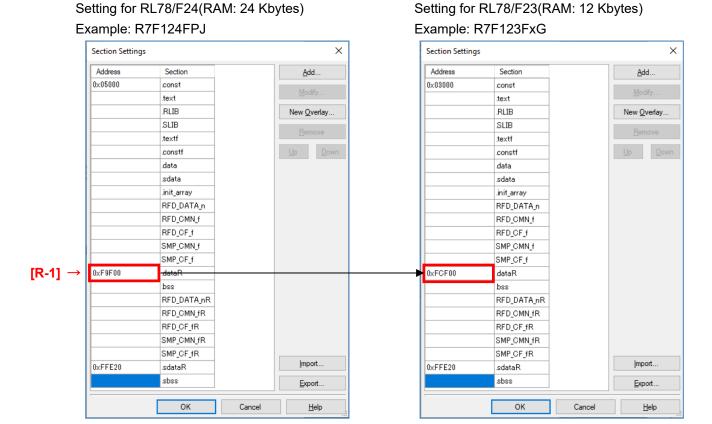

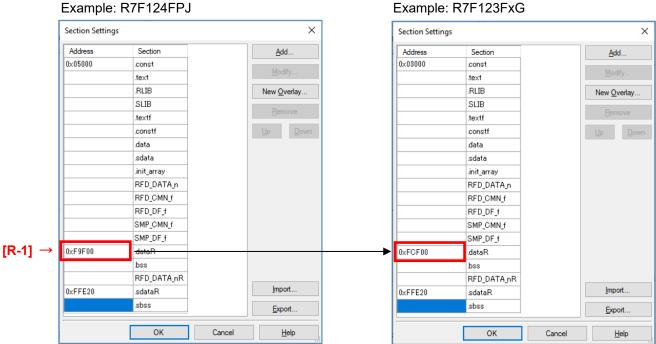

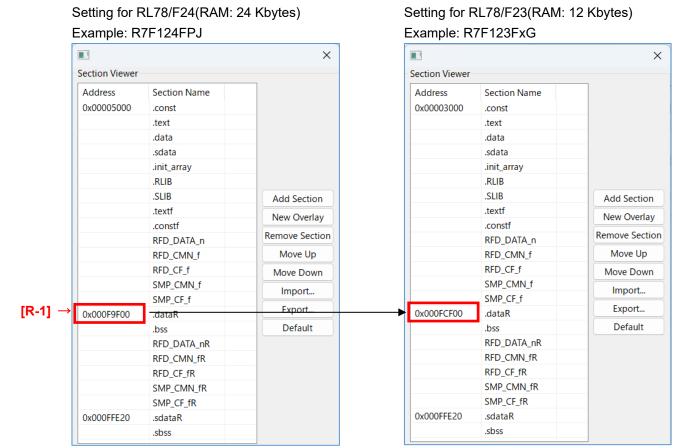

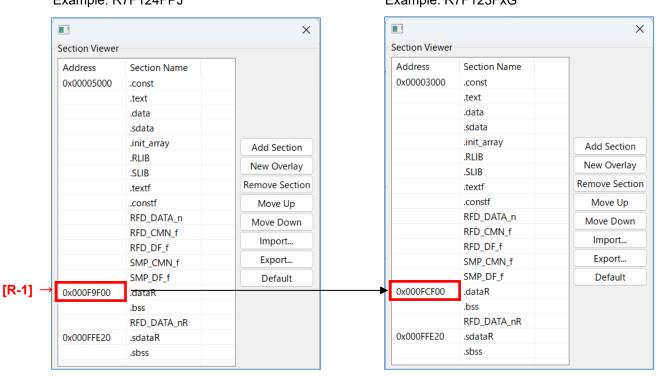

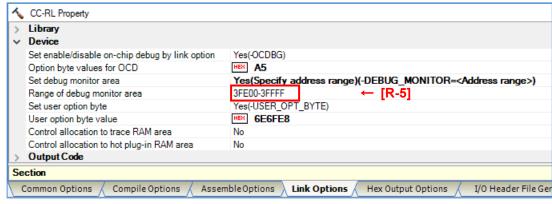

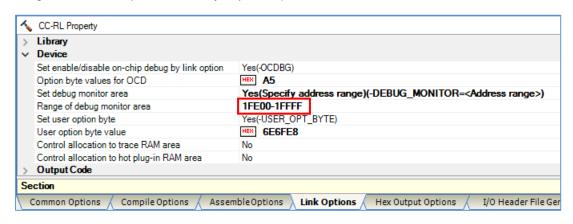

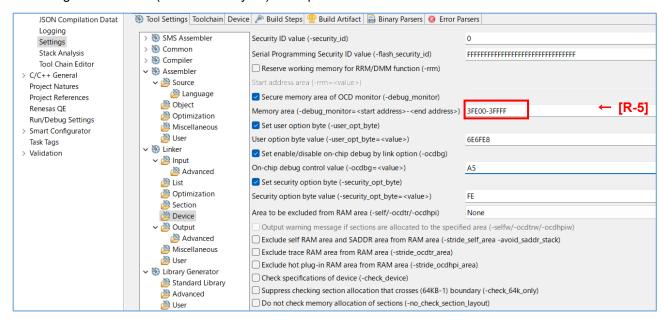

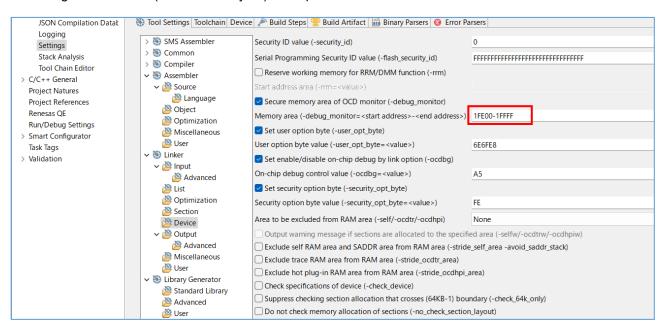

| 2 | R_RFD_WriteCodeFlashReq      | Activates the code/data flash memory area sequencer and begins the programming of the code flash memory (4 bytes).       |