# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# Phase-out/Discontinued

# **RA75X ASSEMBLER PACKAGE**

**VERSION 5.XX**

Language

Document No. U12385EJ7V0UM00 (Previous No. EEU-1363D) Date Published July 1997 N

© NEC Corporation 1990 Printed in Japan

**Phase-out/Discontinued**

[MEMO]

Phase-out/Discontinued

MS-DOS is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries. PC/AT and PC DOS are trademarks of International Business Machines Corporation.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or of others.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

NEC Electronics (Germany) GmbH Duesseldorf, Germany

Tel: 0211-65 03 02 Fax: 0211-65 03 490

**NEC Electronics (UK) Ltd.** Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

NEC Electronics (France) S.A. Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

NEC Electronics (Germany) GmbH Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

Phase-out/Discontinued

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

**NEC do Brasil S.A.** Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

# Major Revisions in This Version

| Section          | Description                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------|

| Whole manual     | RA75X Assembler Package Version 4.5X $\rightarrow$ Version 5.XX                                     |

| Whole manual     | Change of each program of the RA75X Assembler Package                                               |

|                  | • With addition of macro function to assembler program, deletion macro processor                    |

|                  | Addition of library converter program                                                               |

| Whole manual     | Addition of target devices:                                                                         |

|                  | μPD750064, 750066, 750068, 75P0076, 750104, 750106, 750108, 75P0116, 753012A, 753016A,              |

|                  | 753017A, 75P3018A, 753036, 75P3036, 753204, 753206, 753208, 75P3216, 753304Note,                    |

|                  | 754202, 754144, 754244, 754264, 75F4264 <sup>Note</sup> , 754302, 754304, 75P4308                   |

| Whole manual     | Change: Target device under development $\rightarrow$ development completed:                        |

|                  | μPD750004, 750006, 750008, 75P0016, 753012, 753016, 753017, 75P3018, 753104, 753106,                |

|                  | 753108, 75P3116                                                                                     |

| p.25, p.88, p.89 | Change: Symbol length:                                                                              |

|                  | 1 to 8 characters $\rightarrow$ 1 to 31 characters (1 to 8 characters when -NS option is specified) |

| p.35             | Change of a part of Table 3-8. Operator Priority Order                                              |

| p.110            | Addition to Caution in 4.6 BRANCH INSTRUCTION AUTO SELECT PSEUDO-INSTRUCTIONS (1) BR                |

| p.121 to p.140   | Addition of CHAPTER 5 MACRO                                                                         |

| p.151            | Addition of 6.4 CONDITIONAL ASSEMBLE CONTROL INSTRUCTIONS                                           |

| p.174 to p.186   | Addition of control instruction and Note to APPENDIX B LIST OF RESERVED WORDS                       |

| p.190            | Addition of (5) Other to APPENDIX D LIST OF MAXIMUM PERFORMANCE CAPABILITIES                        |

The mark  $\star$  shows major revised points.

Note Under development

**Phase-out/Discontinued**

[MEMO]

# PREFACE

This manual has been prepared so that the basic functions of each program of the RA75X assembler package (subsequently referred to as "assembler package") and the source program describing procedure can be understood correctly.

This manual does not describe the operating procedure for each program. Therefore, after reading this manual, be sure to read the **RA75X Assembler Package User's Manual Operation (U12622E)** when operating each program. (Subsequently referred to as **Operation**)

This manual applies to assembler package products of version 5.XX.

# [Intended Readership]

\*

This manual is intended for use by those who have an understanding of the microcontroller (75X Series/75XL Series) functions and instructions to be developed.

# [Target Devices]

The following microcontroller's software can be developed using this assembler package.

# <75X Series>

| Series                 | Title                                            | Target Device                                                                                                                    |

|------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| _                      | Evachip                                          | μPD75000, 75000A                                                                                                                 |

| General-purpose series | General-purpose                                  | μPD75004, 75006, 75008, 75P008                                                                                                   |

|                        | General-purpose + A/D converter                  | μPD75028, 75036, 75P036, 75064,<br>μPD75066, 75068, 75P068                                                                       |

|                        | General-purpose + A/D converter + EEPROM         | μPD75048, 75P048                                                                                                                 |

| Control series         | For control                                      | μPD75104, 75106, 75108, 75112,<br>μPD75116, 75104A, 75108A,<br>μPD75P108, 75P108B, 75P116                                        |

|                        | For low-voltage high-speed control               | μPD75108F, 75112F, 75116F                                                                                                        |

|                        | F products + low voltage                         | μPD75116H, 75117H, 75P117H                                                                                                       |

| FIP drive series       | For FIP drive                                    | μPD75206, 75208, 75212A,<br>μPD75216A, 75217, 75218,<br>μPD75P216A, 75P218, 75268,<br>μPD75CG208, 75CG216A                       |

|                        | FIP drive + A/D converter                        | μPD75236, 75237, 75238, 75P238                                                                                                   |

| LCD drive series       | For LCD drive                                    | μPD75304, 75306, 75308, 75304B,<br>μPD75306B, 75308B, 75312, 75316,<br>μPD75312B, 75316B, 75P308,<br>μPD75P316, 75P316A, 75P316B |

|                        | LCD drive + A/D converter                        | μPD75328, 75P328                                                                                                                 |

|                        | LCD drive + A/D converter + advanced function    | μPD75336, 75P336                                                                                                                 |

| Slave series           |                                                  | μPD75402A, 75P402                                                                                                                |

| Control (A/D converter | For control (A/D converter on-chip)              | μPD75512, 75516, 75P516                                                                                                          |

| on-chip) series        | For control (A/D converter on-chip) + high speed | μPD75517, 75518, 75P518                                                                                                          |

| Telephone series       | LCD drive + DTMF + D/A converter                 | μPD75352A                                                                                                                        |

|                        | LCD drive + DTMF + D/A converter + A/D converter | μPD75617A                                                                                                                        |

# \* <75XL Series>

| Series                            | Title                                 | Target Device                                                                       |

|-----------------------------------|---------------------------------------|-------------------------------------------------------------------------------------|

| General-purpose series            | General-purpose                       | μPD750004, 750006,<br>μPD750008, 75P0016                                            |

|                                   | General-purpose + RC oscillator       | μPD750104, 750106,<br>μPD750108, 75P0116                                            |

|                                   | General-purpose + A/D converter       | μPD750064, 750066,<br>μPD750068, 75P0076                                            |

| Series for LCD drive              | For LCD drive                         | μPD753012, 753012A, 753016,<br>μPD753016A, 753017, 753017A,<br>μPD75P3018, 75P3018A |

|                                   | For LCD drive + A/D converter         | μPD753036, 75P3036                                                                  |

|                                   | For LCD drive (small)                 | μPD753104, 753106,<br>μPD753108, 75P3116                                            |

|                                   |                                       | μPD753204, 753206,<br>μPD753208, 75P3216                                            |

|                                   | For LCD drive + RC oscillator (small) | μPD753304 <sup>Note</sup>                                                           |

| Key-less entry series             |                                       | μPD754202                                                                           |

|                                   |                                       | μPD754144, 754244,<br>μPD754264, 75F4264 <sup>Note</sup>                            |

| General-purpose small-size series |                                       | μPD754302, 754304, 75P4308                                                          |

# Note Under development

Caution A device file, which must be purchased separately, is required for the development of a 75XL Series device.

# [Format]

This manual consists of the following chapters.

# CHAPTER 1 GENERAL DESCRIPTION CHAPTER 2 75X SERIES/75XL SERIES FEATURES

These two chapters outline the functions of the entire assembler package including the assembler package roles for microcontroller development.

# **CHAPTER 3 SOURCE PROGRAM DESCRIPTION METHOD**

This chapter describes source program description rules including the configuration of the source program, description grammars, and assembler operators.

# CHAPTER 4 PSEUDO-INSTRUCTIONS CHAPTER 5 MACRO CHAPTER 6 CONTROL INSTRUCTIONS

These chapters deal with assembler pseudo-instructions, macros, and control instructions using examples concerning the procedure for writing and using those instructions.

# **CHAPTER 7 ASSEMBLER PACKAGE UTILIZATION**

This chapter introduces know-how concerning source program description.

# **APPENDIX**

The appendixes list assemble objective devices, reserved words, pseudo-instructions, maximum performance capabilities, precautions, and index.

This manual makes no detailed description of instructions. For details of the instructions, refer to the user's manual of each target device to be developed.

# [Reading the Manual]

Those who use the assembler for the first time should start with **CHAPTER 1 GENERAL DESCRIPTION**. Those who have general knowledge of the assembler can skip **CHAPTER 1 GENERAL DESCRIPTION**.

There are several rules relating to the 75X Series/75XL Series source program description procedure. Carefully read **CHAPTER 3 SOURCE PROGRAM DESCRIPTION METHOD**.

Those who want to know the pseudo-instructions, macros, and control instructions of the assembler should read **CHAPTERS 4**, **5**, and **6**. These three chapters describe instruction formats, functions and applications.

# [Legend]

The symbols have the following meanings in this manual.

- ... : The same format is repeated.

- [] : Values inside brackets can be omitted.

- " " : Character(s) or character string(s) marked by " "

- ' ' : Character(s) marked by ' '

- () : Character(s) marked by ()

- < > : Character(s), the title in particular, marked by < >

- " " : Character(s) marked by " "

- \_\_\_\_\_: Input character string(s) or important portion(s)

- \_\_\_\_ : One or more blank space

- $\triangle$  : One blank space

- : Abbreviated program description

- CR : Carriage return

- LF : Line feed

- / : Demarcation symbol

- - ▲ : From to ▲

# [Related Documents]

\*

\*

The following are documents related to this manual.

| Document Name                                                                 | Document No.   |          |  |

|-------------------------------------------------------------------------------|----------------|----------|--|

| bocument Name                                                                 | English        | Japanese |  |

| RA75X Assembler Package Version 5.XX<br>User's Manual <operation></operation> | Under planning | U12622J  |  |

| RA75X Structured Assembler<br>Preprocessor User's Manual                      | Under planning | U12598J  |  |

| 75X Series Structured Assembler<br>Preprocessor Application Note              | EEA-1203       | EEA-603  |  |

**Phase-out/Discontinued**

**Phase-out/Discontinued**

[MEMO]

# CONTENTS

| CHAPTEF | 1 GE    | NERAL DESCRIPTION                             | 1        |

|---------|---------|-----------------------------------------------|----------|

| 1.1     | OUTLI   | NE OF ASSEMBLER                               | 1        |

|         | 1.1.1   | Assembler                                     | 2        |

|         | 1.1.2   | Relocatable Assembler                         | 7        |

|         | 0 0 751 | SERIES/75XL SERIES FEATURES                   | 11       |

| 2.1     | -       | RY FEATURES                                   | 11       |

| 2.1     |         | BY AND SEGMENT DEFINITION PSEUDO-INSTRUCTIONS | 12       |

| 2.2     |         | RAM MEMORY AND CODE SEGMENT                   | 13       |

| 2.5     | 2.3.1   | Reason why Code Segments are Relocatable      | 13       |

|         | -       |                                               | -        |

|         | 2.3.2   | Roles of Linker Relating to Relocation        | 13       |

| • •     | 2.3.3   | Structural Features of Program Memory         | 13       |

| 2.4     | DATA    | MEMORY SPECIAL AREAS                          | 16       |

| CHAPTER | 8.3 50  | URCE PROGRAM DESCRIPTION METHOD               | 17       |

| 3.1     |         | CONFIGURATION OF SOURCE PROGRAM               | 17       |

| 3.2     |         | LE PROGRAM                                    | 18       |

| 3.3     |         | CE PROGRAM DESCRIPTION FORMAT                 | 22       |

| 0.0     | 3.3.1   | Statement Format                              | 22       |

|         | 3.3.2   | Character Set                                 | 22       |

|         | 3.3.2   | Character Set                                 | 23<br>25 |

| 3.4     |         | ULAS AND OPERATORS                            | -        |

| 3.4     | -       |                                               | 35       |

|         | 3.4.1   | Operator Functions                            | 36       |

|         |         | 1) Arithmetic Operators                       | 37       |

|         |         | 2) Logical Operators                          | 40       |

|         | (3      | 3) Compare Operators                          | 42       |

|         | (4      | 4) Shift Operators                            | 48       |

|         | (!      | 5) Bit Location Specification Operator        | 51       |

|         | (6      | 6) Byte Separation Operators                  | 53       |

|         | (7      | 7) Other Operator                             | 54       |

|         | 3.4.2   | Operation Restrictions                        | 55       |

| 3.5     | OPER    | AND CHARACTERISTICS                           | 62       |

|         | 3.5.1   | Symbol Addressing                             | 62       |

|         | 3.5.2   | Operand Value Size and Range                  | 64       |

| CHAPTER | 4 PSEUDO-INSTRUCTIONS                             | 65  |

|---------|---------------------------------------------------|-----|

| 4.1     | OUTLINE OF PSEUDO-INSTRUCTIONS                    | 65  |

| 4.2     | SEGMENT DEFINITION PSEUDO-INSTRUCTIONS            | 66  |

|         | (1) CSEG                                          | 68  |

|         | (2) DSEG                                          | 82  |

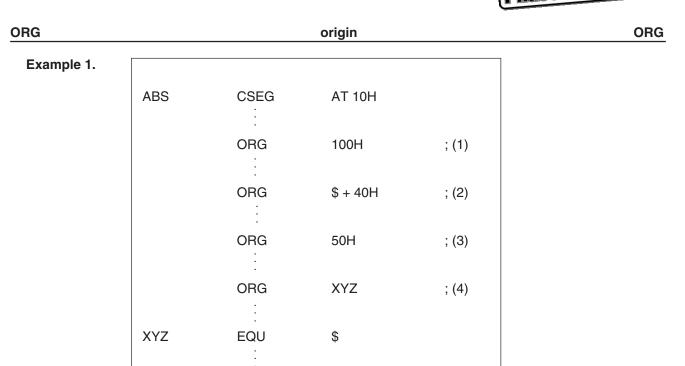

|         | (3) ORG                                           | 84  |

| 4.3     | PROGRAM LINKAGE PSEUDO-INSTRUCTIONS               | 86  |

|         | (1) NAME                                          | 88  |

|         | (2) PUBLIC                                        | 89  |

|         | (3) EXTRN                                         | 91  |

| 4.4     | SYMBOL DEFINITION PSEUDO-INSTRUCTIONS             | 94  |

|         | (1) EQU                                           | 95  |

|         | (2) SET                                           | 97  |

| 4.5     | DATA DEFINITION AND AREA RESERVE                  |     |

|         | PSEUDO-INSTRUCTIONS                               | 98  |

|         | (1) DB                                            | 99  |

|         | (2) DS                                            | 101 |

|         | (3) STKLN                                         | 103 |

| 4.6     | BRANCH INSTRUCTION AUTO SELECT                    |     |

|         | PSEUDO-INSTRUCTIONS                               | 106 |

|         | (1) BR                                            | 107 |

| 4.7     | VECTOR ENTRY TABLE DEFINITION PSEUDO-INSTRUCTIONS | 112 |

|         | (1) VENTn                                         | 113 |

| 4.8     | GETI INSTRUCTION TABLE DEFINITION                 | _   |

|         | PSEUDO-INSTRUCTIONS                               | 115 |

|         | (1) TCALL                                         | 116 |

|         | (2) TBR                                           | 117 |

| 4.9     | ASSEMBLY END PSEUDO-INSTRUCTION                   | 118 |

|         | (1) END                                           | 119 |

|         |                                                   |     |

| CHAPTEF | 3 5 MACRO                                         | 121 |

| 5.1     | OUTLINE OF MACROS                                 | 121 |

| 5.2     | MACRO TYPES                                       | 122 |

| 5.3     | MACRO RULES                                       | 123 |

|         | 5.3.1 Macro Definition Rules                      | 123 |

|         | 5.3.2 Macro Reference Rules                       | 125 |

| 5.4     | OUTLINE OF MACRO INSTRUCTIONS                     | 126 |

$\star$

|    | 5.5    | MACRO DEFINITION INSTRUCTIONS 1                                   | 126 |

|----|--------|-------------------------------------------------------------------|-----|

|    |        | (1) MACRO                                                         | 127 |

|    |        | (2) EXITM                                                         | 128 |

|    |        | (3) ENDM                                                          | 129 |

|    | 5.6    | EXTERNAL MACRO DECLARE INSTRUCTION 1                              | 130 |

|    |        | (1) LODM                                                          | 131 |

|    | 5.7    | MACRO INSTRUCTION 1                                               | 133 |

|    |        | (1) Macro Instruction                                             | 134 |

|    | 5.8    | REPEAT MACRO INSTRUCTIONS 1                                       | 135 |

|    |        | (1) REPT                                                          | 136 |

|    |        | (2) IRP                                                           | 137 |

|    |        | (3) IRPC                                                          | 138 |

|    | 5.9    | GLOBAL SYMBOL DECLARE INSTRUCTION 1                               | 139 |

|    |        | (1) GLOBAL                                                        | 140 |

|    |        |                                                                   |     |

| CF | IAPTEF | R 6 CONTROL INSTRUCTIONS 1                                        | 141 |

|    | 6.1    | GENERAL DESCRIPTION OF CONTROL INSTRUCTIONS 1                     | 141 |

|    | 6.2    | INCLUDE CONTROL INSTRUCTION 1                                     | 141 |

|    |        | (1) INCLUDE                                                       | 142 |

|    | 6.3    | ASSEMBLY LIST CONTROL INSTRUCTIONS 1                              | 143 |

|    |        | (1) TITLE                                                         | 144 |

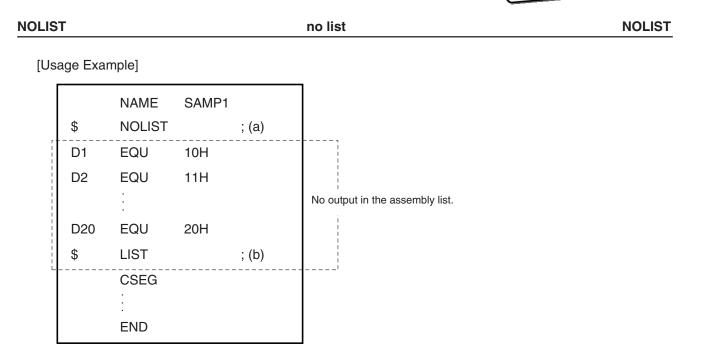

|    |        | (2) NOLIST                                                        | 146 |

|    |        | (3) LIST                                                          | 148 |

|    |        | (4) EJECT                                                         | 149 |

| *  | 6.4    | CONDITIONAL ASSEMBLE CONTROL INSTRUCTIONS 1                       | 151 |

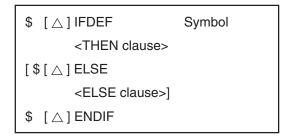

|    |        | (1) IFDEF                                                         | 152 |

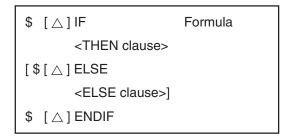

|    |        | (2) IF                                                            | 153 |

|    |        | (3) SWITCH                                                        | 154 |

|    |        |                                                                   |     |

| CF | IAPTEF | R 7 ASSEMBLER PACKAGE UTILIZATION 1                               | 157 |

|    | 7.1    | ASSEMBLER PACKAGE UTILIZATION 1                                   | 157 |

|    | 7.2    | RELOCATION ATTRIBUTES AND INSTRUCTIONS 1                          | 160 |

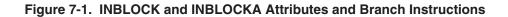

|    |        | 7.2.1 INBLOCK and INBLOCKA Attributes and Branch Instructions     | 160 |

|    |        | 7.2.2 XBLOCK and XBLOCKA Attributes and Branch Instructions       | 162 |

|    |        | 7.2.3 Relocation Attributes and Subroutine Call Instructions      | 162 |

|    |        | 7.2.4 IENT Attribute and GETI Instruction                         | 163 |

|    |        | 7.2.5 PAGE Attributes and MOVT, BR PCDE, and BR PCXA Instructions | 164 |

| APPENDIX A | LIST OF ASSEMBLED RELEVANT UNIT TYPES    | 165 |

|------------|------------------------------------------|-----|

| APPENDIX B | LIST OF RESERVED WORDS                   | 173 |

| APPENDIX C | LIST OF PSEUDO-INSTRUCTIONS              | 187 |

| APPENDIX D | LIST OF MAXIMUM PERFORMANCE CAPABILITIES | 189 |

| APPENDIX E | LIST OF PRECAUTIONS                      | 191 |

| APPENDIX F | INDEX                                    | 193 |

# **CONTENTS OF FIGURES**

| Figure No. | Title                                                   | Page |

|------------|---------------------------------------------------------|------|

| 1-1.       | RA75X Assembler Package                                 | 1    |

| 1-2.       | Assembler Flow                                          | 2    |

| 1-3.       | Development Process of Microcomputer Applied Products   | 3    |

| 1-4.       | Software Development Process                            | 4    |

| 1-5.       | Assembling Process for Assembler Package                | 5    |

| 1-6.       | Renewing Assembly                                       | 8    |

| 1-7.       | Program Creation Using Existing Modules                 | 9    |

| 2-1.       | Memory Addressing                                       | 11   |

| 2-2.       | Source Program Configuration                            | 12   |

| 2-3.       | Program Memory Map                                      | 14   |

| 2-4.       | Data Memory Map                                         | 16   |

| 3-1.       | Source Program Configuration Example                    | 17   |

| 3-2.       | Sample Program Configuration                            | 18   |

| 3-3.       | Statement Component Fields                              | 22   |

| 4-1.       | Segment Definition and Memory Location                  | 67   |

| 4-2.       | Relocation Attributes and Program Memory                | 71   |

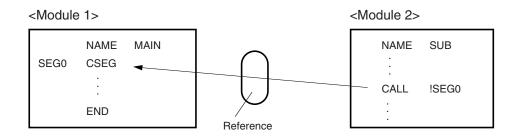

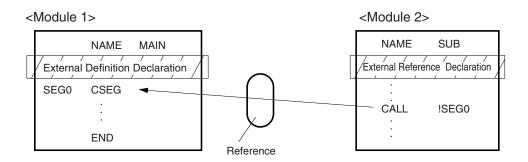

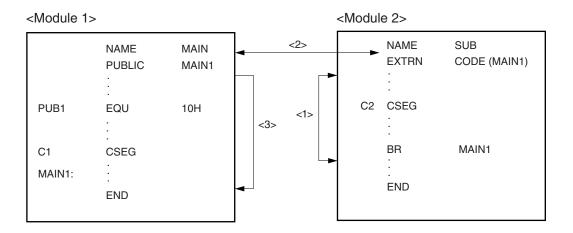

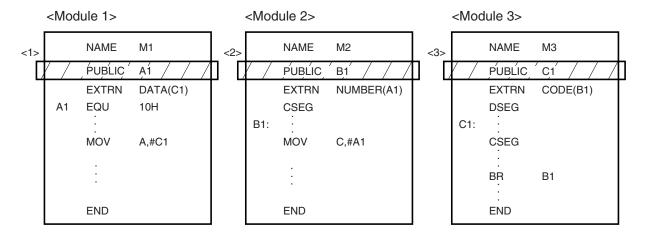

| 4-3.       | Symbol Relations between Two Modules                    | 87   |

| 4-4.       | VENTn Pseudo-Instruction and Program Memory             | 114  |

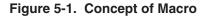

| 5-1.       | Concept of Macro                                        | 122  |

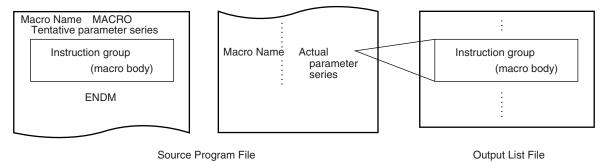

| 5-2.       | Concept of Repeated Macro                               | 122  |

| 7-1.       | INBLOCK and INBLOCKA Attributes and Branch Instructions | 161  |

\*

**Phase-out/Discontinued**

[MEMO]

# CONTENTS OF TABLES

| Table No. | Title                                                                   | Page |

|-----------|-------------------------------------------------------------------------|------|

| 3-1.      | Symbol Types                                                            | 25   |

| 3-2.      | Symbol Attribute Types                                                  | 27   |

| 3-3.      | Symbol Attribute Names                                                  | 28   |

| 3-4.      | Numeric Constant Representation                                         | 31   |

| 3-5.      | Register Types                                                          | 32   |

| 3-6.      | Special Characters Describable in Operand Column                        | 32   |

| 3-7.      | Operator Types                                                          | 35   |

| 3-8.      | Operator Priority Order                                                 | 35   |

| 3-9.      | Relocation Attribute Types                                              | 55   |

| 3-10.     | Combination of Terms and Operators Classified by Relocation Attributes  |      |

|           | (Except External Reference Terms)                                       | 56   |

| 3-11.     | Combinations of Terms and Operators Classified by Relocation Attributes |      |

|           | (External Reference Terms)                                              | 57   |

| 3-12.     | Symbol Attribute Types for Operation                                    | 59   |

| 3-13.     | Combinations of Terms and Operators Classified by Symbol Attributes     | 60   |

| 3-14.     | Symbol Attributes Enabled for Reference (1)                             | 62   |

| 3-15.     | Symbol Attributes Enabled for Reference (2)                             | 63   |

| 3-16.     | Symbol Attributes Enabled for Reference (3)                             | 64   |

| 4-1.      | List of Pseudo-Instruction Types                                        | 65   |

| 4-2.      | Segment Definition Procedure and Memory Address to be Located           | 66   |

| 4-3.      | Relocation Attribute Functions                                          | 69   |

| 4-4.      | Symbol Attribute Specification Procedure                                | 92   |

| 4-5.      | Name and Label Reference Methods                                        | 108  |

| 4-6.      | Optimization Procedure                                                  | 108  |

| 5-1.      | List of Macro Instructions                                              | 126  |

| 6-1.      | Control Instruction Table                                               | 141  |

| 7-1.      | Subroutine Call Instructions and Relocation Attributes                  | 162  |

$\star$

**Phase-out/Discontinued**

[MEMO]

# **CHAPTER 1 GENERAL DESCRIPTION**

In this chapter, the assembler package role in 75X Series/75XL Series development will be described.

# 1.1 OUTLINE OF ASSEMBLER

\*

The RA75X assembler package (subsequently referred to as assembler package) is a general term for a series of programs used to convert the source program described by 75X Series/75XL Series assembler language to machine codes.

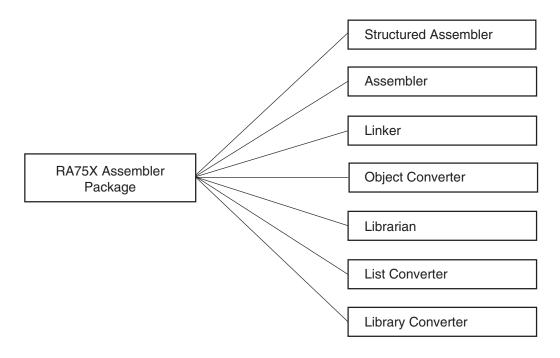

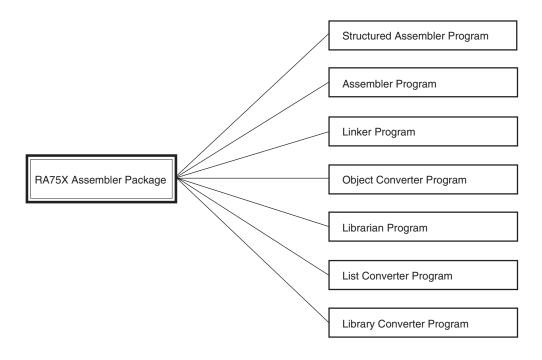

This assembler package consists of seven programs; a structured assembler, an assembler, a linker, an object converter, a librarian, a list converter, and a library converter.

Figure 1-1. RA75X Assembler Package

# 1.1.1 Assembler

### (1) Assembly language and machine code

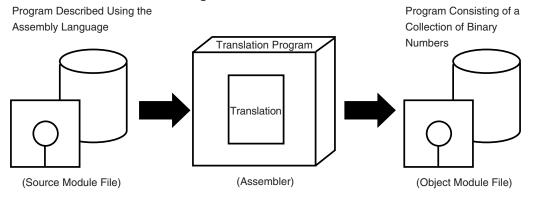

The assembly language is the most basic programming language for microcomputers.

Programs and data are necessary for microcomputer operations. The human operator will carry out programming to store them into the microcomputer memory unit. The programs and data that the microcomputer can handle are a collection of binary numbers called machine codes (the words which the computer can understand).

We may have difficulty or make errors in creatingprograms using the machine codes, that is binary numbers.

Thus, the meaning of the machine codes is represented by easily understood English symbolic codes and the symbolic codes in turn are used for program creation. The program language system based on those codes is called an assembly language.

An assembler is a program to translate the program created using the assembler language into a collection of binary numbers which the microcomputer can understand.

Figure 1-2. Assembler Flow

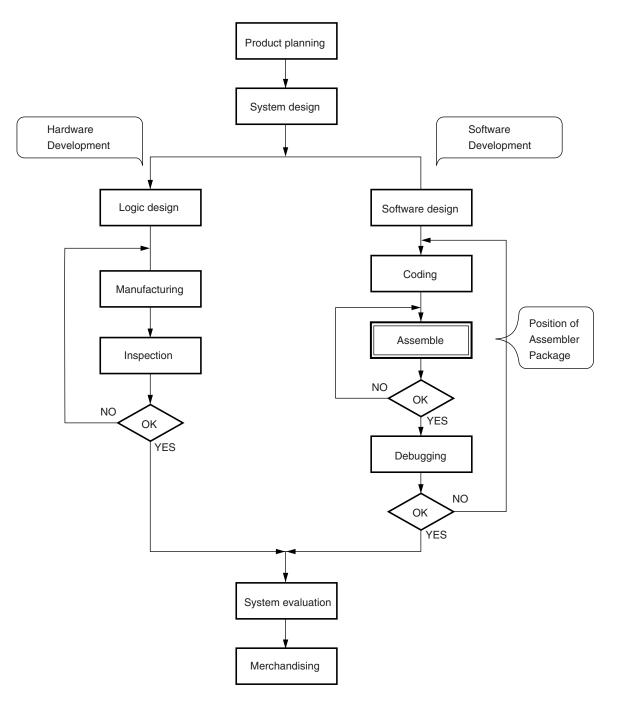

# (2) Development of microcomputer applied products and the roles of assembler package

Figure 1-3. Development Process of Microcomputer Applied Products shows where programming with the assembly language is positioned in product development.

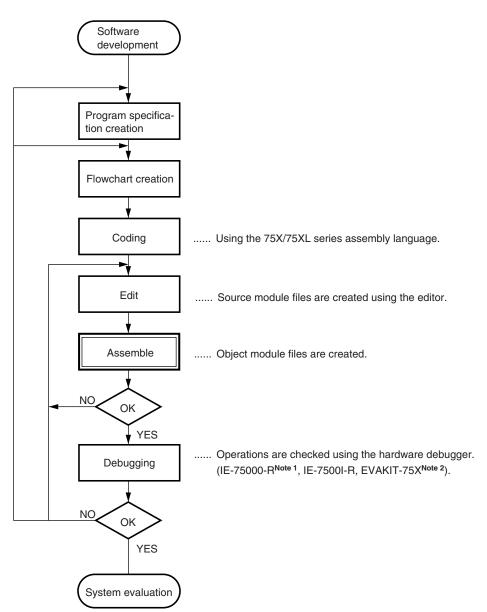

Figure 1-4. Software Development Process shows the software development process in more detail.

Figure 1-4. Software Development Process

- **Notes 1.** Maintenance product (No longer available for purchase)

- 2. Discontinuation product (No longer available for purchase)

The assembler package is now inserted in the assembling process.

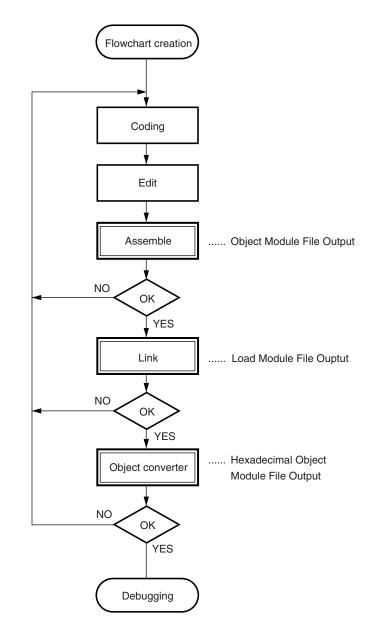

# Figure 1-5. Assembling Process for Assembler Package

## ★ This package has the following features.

## 1. Branch instruction optimization function

A BR pseudo-instruction is provided. This directive automatically selects an appropriate branch instruction code format.

Conventionally, for branch operations, it is required to select either 2-byte or 1-byte branch instructions according to the branch instructions' destination range because it is critical for the efficiently use of memory resources.

However, it is a lot of work for a programmer to take the destination range into account every time a branch instruction is described.

To avoid this, use the BR directive, which makes the assembler generate appropriate branch instruction codes according to the destination range. This feature is called branch instruction optimization function.

### 2. VENTn pseudo-instruction

This pseudo-instruction facilitates writing to the vector table. The 75X Series/75XL Series devices have an interrupt vector table at addresses 0000H to 000FH (The size depends on the part number). This vector table can hold the starting address of interrupt services, the setting of the memory bank enable flag (MBE), and the value of register bank enable flag (RBE) during an interrupt servicing.

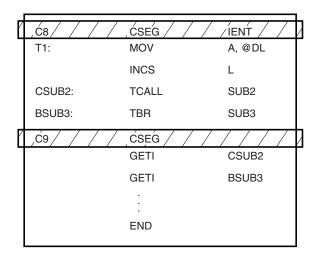

### 3. TCALL, TBR pseudo-instructions

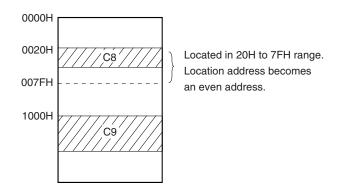

These pseudo-instructions facilitate setting data to the GETI instruction reference table. When 2-byte or 3-byte branch instructions or call instructions need to be executed as 1-byte instructions, special data must be set in the reference table (0020H to 007FH). This setting work can be facilitated by the use of the GETI instruction.

### 4. Librarian (LB75X)

The library function integrates plural object modules into a library file. Integrating general-purpose modules into a single file improves the module use efficiency. It also contributes to improved file management and operation efficiency.

# 5. List converter (LCNV75X)

The list converter improves the debugging work efficiency when a program assembled by a relocatable assembler is debugged with the IE-75000-R<sup>Note 1</sup>, IE-75001-R, or EVAKIT-75X<sup>Note 2</sup>.

Usually, the assemble list values eventually do not match the object codes which reference the addresses and relocatable symbols in the relocatable segments. For this reason, if absolute addresses need to be specified for debugging, it is required to refer to the link map list because the assemble list alone cannot show the absolute addresses.

The list converter is the program that eliminates the reference requirement. This program replaces the relocatable addresses and object codes in the assemble list, which is output from the assembler, with the eventually determined absolute addresses, to generate an absolute assemble list.

**Notes 1.** Maintenance product (No longer available for purchase)

2. Discontinuation product (No longer available for purchase)

# 6. Macro

A macro is a labeled series of instructions. Only the label must be written in the source program in place of the corresponding instructions.

If there are instruction groups that are frequently used, use of macros is effective because it lightens the source program. Also, if a function is composed of specific instruction series, labeling these series instructions as a macro makes the program simple and easy to code or revise.

The machine code converted by the assembler is written into the microcomputer memory for use. Before the writing operation, the location where the converted machine code should be written in the memory must be determined.

Thus, the machine code to be converted with the assembler is provided with the information concerning "At which address in the memory each machine code should be positioned".

Depending on the method of positioning the machine codes at the memory addresses, the assemblers are roughly classified into "absolute assemblers" and "relocatable assemblers".

#### Absolute assembler

The machine codes converted by one assembly are positioned at the absolute addresses.

## • Relocatable assembler

The addresses of the machine codes converted by one assembly are temporary addresses. Absolute addresses are determined using a program called 'linker'.

When creating one program using an absolute assembler, the program must have been created by programming at one time in principle. However, if a large program is created at one time, it may become complex and program analysis for maintenance may become difficult. Thus, one program is divided into several subprograms (modules) for each function unit. This program development process is called 'modular programming'.

The relocatable assembler is suitable for modular programming.

Modular programming using the relocatable assembler makes it possible to obtain the following advantages.

Phase-out/Discontinue

## (1) Improvement of development efficiency

It is difficult to execute programming for a large program at one time. In such cases, dividing the program into function modules enables several people to develop the program concurrently with improved efficiency.

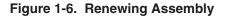

If a bug is found in the program, it is not necessary to assemble the whole program for partial correction. It is possible to reassemble only the modules requiring correction.

By so doing, the debugging time can be decreased.

# (2) Utilization of resources

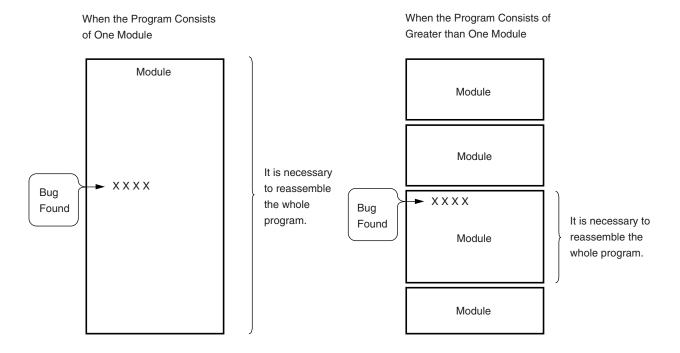

Previously generated highly-reliable, highly-universal modules can be utilized for the development of another program. By accumulating those highly-universal modules, the extent of new program development can be decreased.

**Phase-out/Discontinued**

[MEMO]

# CHAPTER 2 75X SERIES/75XL SERIES FEATURES

In this chapter, features of the memory space of the 75X Series/75XL Series which is the target of the assembler package will be described.

# 2.1 MEMORY FEATURES

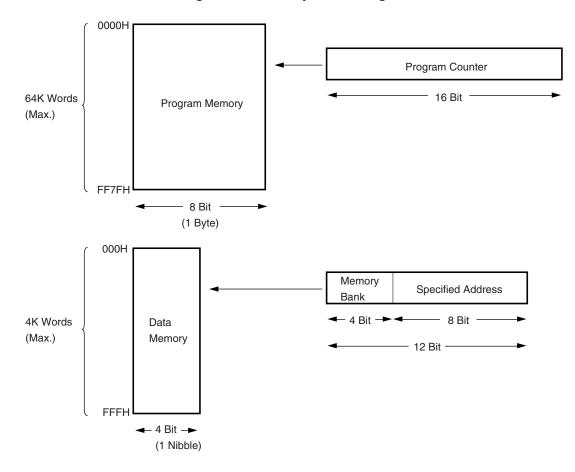

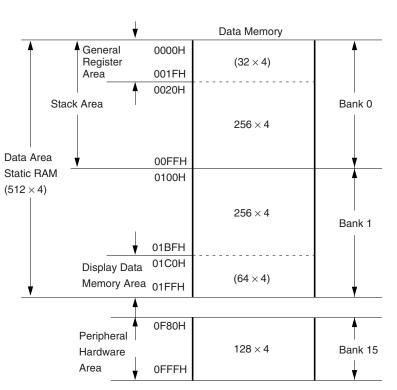

The 75X Series has the following maximum memory spaces:

| Program memory (ROM) | : | 64K words $\times$ 8 bits (64 Kbytes) |

|----------------------|---|---------------------------------------|

| Data memory (RAM)    | : | 4K words $\times$ 4 bits (4K nibbles) |

The program memory and data memory spaces are separate. The program memory has a 1-word, 8-bit configuration and the data memory has a 1-word, 4-bit configuration.

As shown in **Figure 2-1**, the program memory is addressed by a 16-bit program counter and the data memory is addressed by a total of 12 bits consisting of 4 bits of the memory bank (MB) and 8 bits of the address directly or indirectly specified by an instruction.

Figure 2-1. Memory Addressing

# 2.2 MEMORY AND SEGMENT DEFINITION PSEUDO-INSTRUCTIONS

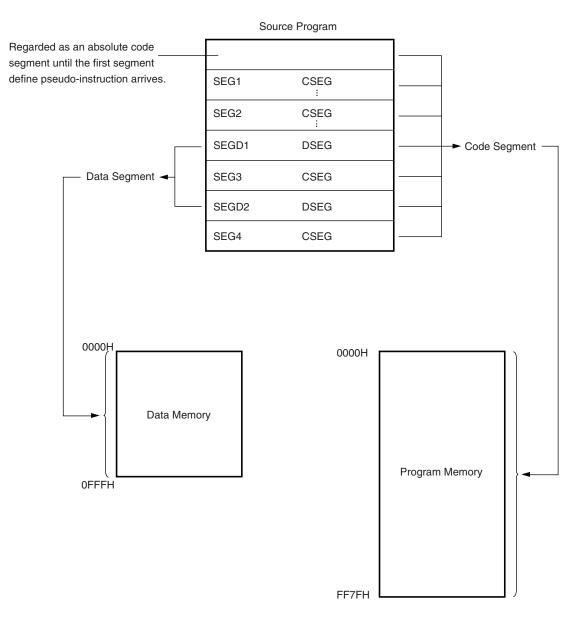

The relocatable assembler is provided with the segment definition pseudo-instructions to define the memory area to cope with the memory configuration described in section **2.1 MEMORY FEATURES**.

CSEG pseudo-instruction and DSEG pseudo-instruction are segment definition pseudo-instructions.

The CSEG pseudo-instruction is used to define the use of program memory area and the DSEG pseudoinstruction is used to define the use of data memory area.

A group of source program statements defined for the use of program memory area by the CSEG pseudoinstruction is called 'code segment' and a group of source program statements defined for the use of data memory area by the DSEG pseudo-instruction is called 'data segment'.

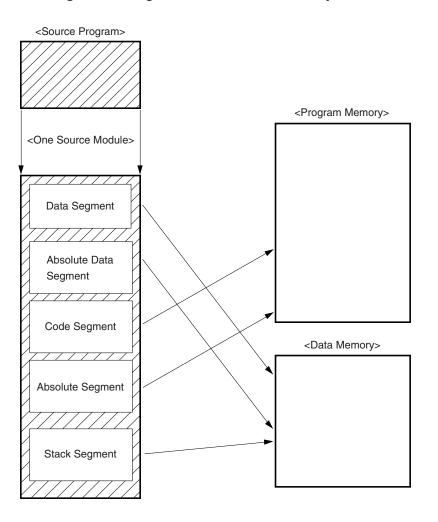

Figure 2-2 shows the Source Program Configuration.

The relocatable assembler regards an area up to where the first segment definition pseudo-instruction appears in the source program (even if the segment definition pseudo-instruction has not been described anywhere) as the code segment starting at address 10H (because program memory addresses 0 to 0FH might be used as the interrupt vector area).

As described above, the relocatable assembler source program consists of segments.

Figure 2-2. Source Program Configuration

# 2.3 PROGRAM MEMORY AND CODE SEGMENT

# 2.3.1 Reason why Code Segments are Relocatable

The 75X Series/75XL Series has a maximum program memory space of 64 Kbytes.

Greater than one programmer may be engaged in the development of such a large program. In view of development efficiency, maintenance and reliability, it may be desirable for greater than one person to be engaged in programming by dividing the program. This is called 'modular programming'.

However, when executing the modular programming, the location in the program memory where each program is positioned cannot be clearly known until the programs of all persons involved are completed. Further, it is difficult to determine at the start of one program generation where the program should be positioned in the program memory space.

For these reasons, the code segments defined for program memory area use by the CSEG pseudo-instruction must be assembled so that they can be located anywhere in the program memory. This is why the code segments are relocatable.

# 2.3.2 Roles of Linker Relating to Relocation

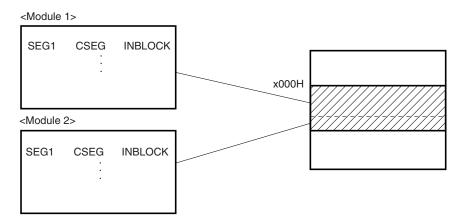

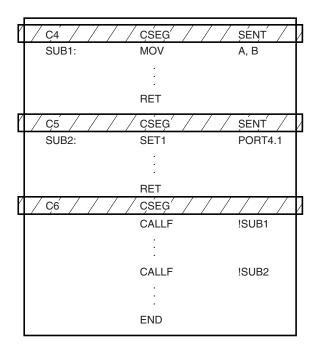

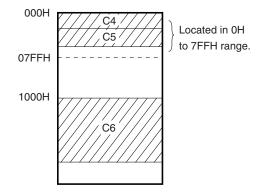

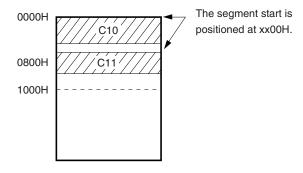

The relocatable assembler assembles the relocatable code segments in relative address format setting the start address of one relocatable code segment at address 0H. By applying one of the assembly results or two or more object modules (object output in one-assembly units) to the linker, the relocatable code segments in each object module are relocated and the absolute addresses are determined.

As such the linker is a program to relocate the relative address object modules and replace them with the absolute address object modules.

However, the 75X series/75XL series program memoryhas special areas used for special purposes and structural boundaries defined by instruction restriction.

Thus, it is necessary for the programmer to understand the structural features of the program memory and to instruct the linker about the relocation positions of the relocatable code segments.

**Remark** The structural boundaries consist of a boundary called 'block' and a boundary called 'page'.

# 2.3.3 Structural Features of Program Memory

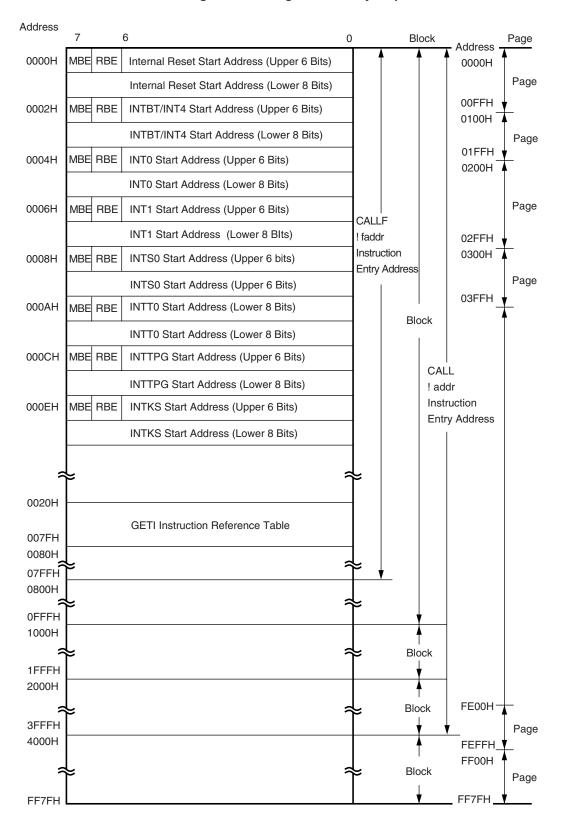

Figure 2-3 shows the special areas used for the specific purposes of the 75X series/75XL series program memory.

| Addresses 0000H to 000FH | : | Vector table area for setting each vectored interrupt start address          |

|--------------------------|---|------------------------------------------------------------------------------|

| Addresses 0020H to 007FH | : | GETI instruction reference table area                                        |

| Addresses 0000H to 07FFH | : | Entry area for subroutines referred to by CALLF instruction                  |

| Addresses 0000H to 3FFFH | : | Area which can be branched by BR! instruction and entry area for subroutines |

|                          |   | referred to by CALL! instruction                                             |

# Caution The vector table area varies depending on the product type.

Caution The vector table area differs from the last address depending on the product type.

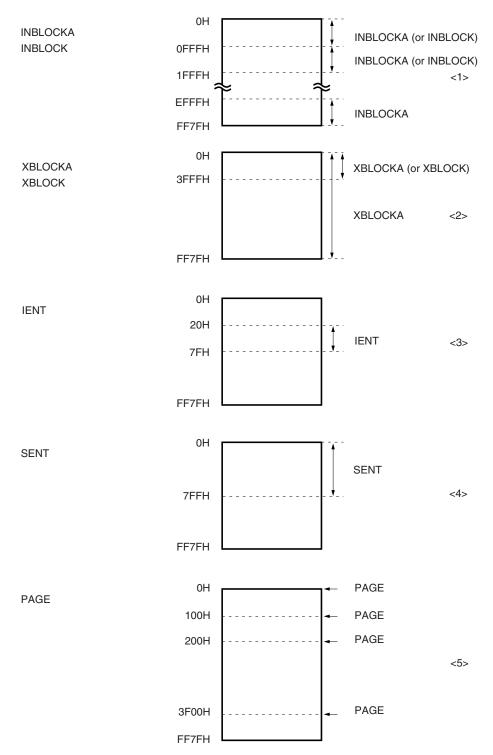

#### (1) Block

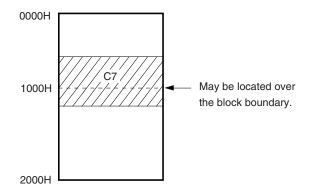

When the 64-Kbyte program memory is divided every 4K (4096) bytes from address 0H as shown in **Figure 2-3**, one 4-Kbyte unit is called 'block' and the boundary of two neighboring blocks is called 'block boundary'.

The 'block' is the concept which derived from the character of the 75X Series/75XL Series branch instruction (BRCB instruction).

The BRCB instruction is a 2-byte branch instruction and is branched with the least significant 12 bits of the address described in the instruction operand replaced with those of the program counter. The most significant 2 bits of the program counter are the same as those of the current location address +2. Thus, the branch range varies depending on where the BRCB instruction is located in the program memory. This is the reason why the concept of 'block' has been introduced to the program memory of the 75X Series/75XL Series.

#### (2) Page

When the 64-Kbyte program memory is divided every 256 bytes from address 0H as shown in **Figure 2-3**, one unit (256 bytes) is called 'page' and the boundary of two neighboring pages is called 'page boundary'.

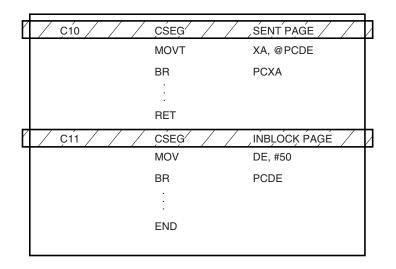

The 'page' is the concept which derived from the characters of the 75X Series/75XL Series table reference instruction MOVT and branch instructions BR PCDE and BR PCXA.

The MOVT instruction is used to refer to the program memory table data. The DE or XA register contents are set to the least significant 8 bits of the program counter and the program memory contents addressed by the input DE or XA register contents are transferred to the XA register.

For example, when the program counter value is 100H and DE = 10H, data at program memory address 110H is transferred to the XA register.

The BR PCDE and BR PCXA branch instructions set the DE and XA register contents to the least significant 8 bits of the program counter. That means that the branch destination varies depending on the data transferred to the DE and XA register.

For example, when the program counter value is 5FFH and DE = 01H, the program counter value is changed to 501H.

In other words, the MOVT instruction reference destination and the BR PCDE and BR PCXA instruction branch destinations are both limited to inside the same page where those instructions are located. This is the reason why the concept of 'page' has been introduced to the program memory.

Phase-out/Discontinue

# 2.4 DATA MEMORY SPECIAL AREAS

The 75X Series/75XL Series data memory is provided with the peripheral hardware including input/output ports and timers at addresses 0F80H to 0FFFH. Thus, the absolute address specification of data segment is not possible for this area.

The assembler has the symbol (name) indicating the address of the hardware loaded at addresses 0F80H to 0FFFH as the reserved word. The reserved word is called 'specific address name code'.

When operating the peripheral hardware, the specific address name code assigned for the address to be manipulated is described for the instruction operand.

Among the specific address name codes, the symbol attribute of the names indicating the bit addresses between 0FB0H.0 and 0FBFH.3 or 0FF0H.0 and 0FFFH.3 is 'PBIT' and the symbol attribute of all other names is 'DATA'. For details of symbol attributes, refer to **3.5 OPERAND CHARACTERISTICS**.

Figure 2-4. Data Memory Map

- Caution The area where hardware is incorporated depends on the product type. Depending on the product type, the stack area of memory banks other than memory bank 0 is also available.

- For how to set a value to the stack pointer, refer to 4.5 (3) STKLN.

# **CHAPTER 3 SOURCE PROGRAM DESCRIPTION METHOD**

In this chapter, the contents necessary for describing the source program (description format, formulas and operators, operand characteristics, etc.) will be described.

# 3.1 BASIC CONFIGURATION OF SOURCE PROGRAM

As described in **CHAPTER 2 75X SERIES/75XL SERIES FEATURES**, the 75X Series/75XL Series source program is configured in units called 'segment'.

The segment is generally configured of functionally similar types of routine or data.

There are code segments and data segments, and they are located in the program memory (ROM) area and the data memory (RAM) area, respectively.

The segment memory space varies depending on the assembled product type.

For details, refer to APPENDIX A LIST OF ASSEMBLED RELEVANT UNIT TYPES.

The segment must be less than each memory space in size.

The code segment can be positioned at any address using the linker. The absolute code segment and the data segment cannot be changed from the address specified by the source program.

To provide instructions to the assembler in the source program, the appropriate object module is generated by placing assembler options or pseudo-instructions.

The source program can be configured by combining any segments.

Figure 3-1 shows a source program configuration example.

|    | NAME TEST1 |   |    | ORG  | 20H  | ] | C1 | CSEG AT 10H  |

|----|------------|---|----|------|------|---|----|--------------|

|    | NAME TESTT |   |    | Und  | 2011 |   | U1 | CSEG AT TUR  |

| C1 | CSEG       |   |    | ÷    |      |   |    | :            |

|    | ÷          |   |    | ORG  | 40H  |   | C2 | CSEG AT 200H |

| D1 | DSEG       |   |    | :    |      |   |    |              |

|    | ÷          | D | )1 | DSEG |      |   | D1 | DSEG         |

|    | :          |   |    | ÷    |      |   |    |              |

|    | END        |   |    | END  |      |   |    | END          |

Figure 3-1. Source Program Configuration Example

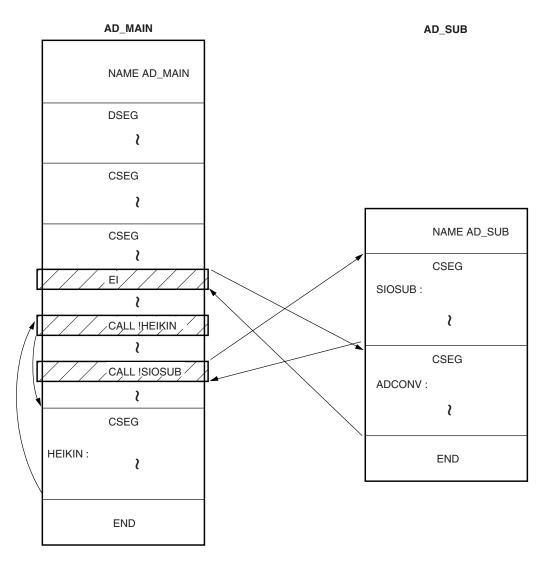

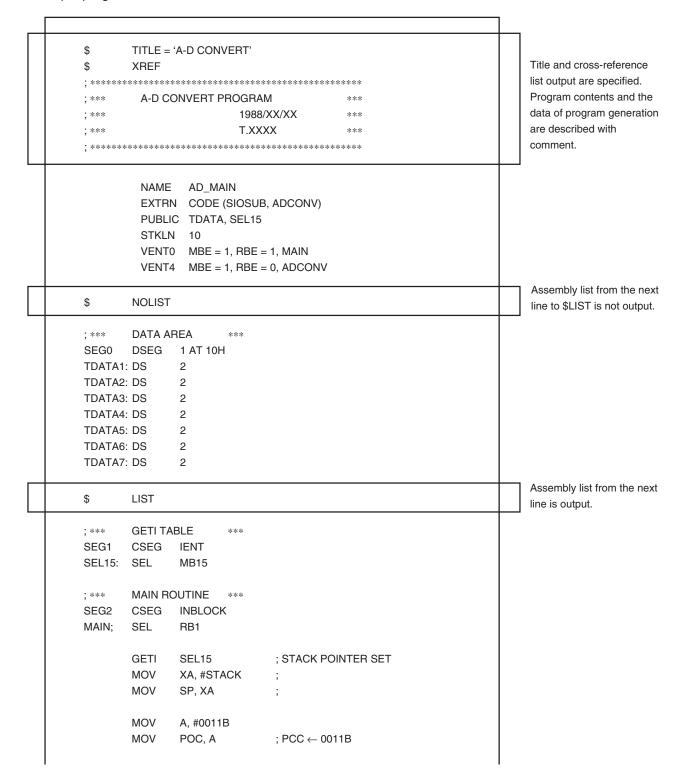

# 3.2 SAMPLE PROGRAM

This section shows a source program (source module) description example (this example is attached to the product as the sample program file).

Source module description procedure should be learned from this example.

This program is designed for the  $\mu$ PD75106.

The sample program contents are briefly explained below.

This sample program is an analog-to-digital conversion program to sample the analog signal (PTH00 pin input signal) eight times using the hardware (programmable threshold port and serial interface) incorporated into the  $\mu$ PD75106 and to generate the average value from the serial output pin.

In this sample program, one program is divided into two modules.

One module is called AD\_MAIN and stored in the source module file "75XTEST1.ASM".

The other module is called AD\_SUB and stored in the source module file "75XTEST2.ASM".

Figure 3-2 shows the sample program configuration.

## Caution

This sample program has been provided to learn the assembler package functions and operations. Thus, it cannot be used as an application program as it is.

#### <Main Routine>

| \$              |          | A-D CONVERT'               | ; (1)                                   |

|-----------------|----------|----------------------------|-----------------------------------------|

| ; *******       |          | ******                     |                                         |

| ;***            |          | VERT PROGRAM               |                                         |

| ; *******       |          | *****************          |                                         |

|                 | NAME     | AD_MAIN                    | ; (2)                                   |

|                 | EXTRN    | (                          | , , , , , , , , , , , , , , , , , , , , |

|                 | PUBLIC   | <i>,</i>                   | ; (4)                                   |

|                 | STKLN    | 10                         | ; (5)                                   |

|                 | VENT0    | MBE = 1, RBE =             |                                         |

| 0500            | VENT4    | MBE = 1, RBE =<br>1 AT 10H |                                         |

| SEG0<br>TDATA : | DSEG     |                            | ; (7)                                   |

| IDATA:          | DS       | 2                          |                                         |

| : ***           | GETI TAE | 81 F ***                   |                                         |

| SEG1            | CSEG     | IENT                       | ; (8)                                   |

| SEL15 :         | SEL      | MB15                       | , (6)                                   |

| OLLIG.          | OLL      | WID 10                     |                                         |

| : ***           | MAIN RO  | UTINE ***                  |                                         |

| ,<br>SEG2       | CSEG     | INBLOCK                    | ; (9)                                   |

| MAIN :          | SEL      | RB1                        | , (0)                                   |

|                 | 011      |                            |                                         |

|                 | GETI     | SEL15                      | ; STACK POINTER SET                     |

|                 | MOV      | XA, #STACK                 | -                                       |

|                 | MOV      | SP, XA                     | -                                       |

|                 |          |                            |                                         |

|                 | MOV      | A, #0011B                  |                                         |

|                 | MOV      | PCC, A                     | ; PCC ← 0011B                           |

|                 |          |                            |                                         |

| ;**             | DATA RA  | M 0H-13FH ZERC             | CLEAR **                                |

|                 |          |                            |                                         |

|                 | SEL      | MB1                        |                                         |

|                 | MOV      | HL, #3FH                   |                                         |

|                 | MOV      | XA, #00                    |                                         |

| LOOP1 :         | MOV      | @HL, A                     | ; 100H-13FH                             |

|                 | DECS     | HL                         |                                         |

|                 | BR       | LOOP1                      |                                         |

|                 | SEL      | MB0                        |                                         |

| LOOP2 :         | MOV      | @HL, A                     | ; 0H-FFH                                |

|                 | DECS     | HL                         |                                         |

|                 | BR       | LOOP2                      |                                         |

- (1) Assembler option

- (2) Module name declaration

- (3) Declaration as an external reference symbol of the symbol defined by another module

Phase-out/Discontinued

- (4) Declaration as an external definition symbol of the symbol to be referred to from another module

- (5) Stack size specification

- (6) Specification of the memory bank and register bank processing start addresses upon interruption

- (7) Data segment start declaration

- (8) Code segment start declaration

- (9) Code segment start declaration

- (10) Code segment start declaration

- (11) Module end declaration

CHAPTER 3 SOURCE PROGRAM DESCRIPTION METHON Phase-out/Discontinued

| ** | TIMER SET (SAMPLING TIME = 30MSEC, FXX = 4. 19MHz) ** | k |

|----|-------------------------------------------------------|---|

| ,  |                                                       |   |

|          | GETI   | SEL15          | ; SEL        | MB15 |        |

|----------|--------|----------------|--------------|------|--------|

|          | MOV    | XA, #79H       |              |      |        |

|          | MOV    | TMOD0, XA      |              |      |        |

|          | MOV    | XA, #01001100B |              |      |        |

|          | MOV    | TM0, XA        |              |      |        |

|          | EI     |                |              |      |        |

|          | EI     | IET0           |              |      |        |

|          | SEL    | MB1            |              |      |        |

| LOOP3 :  | MOV    | XA, #0H        |              |      |        |

|          | MOV    | B, #00H        |              |      |        |

| LOOP4 :  | SKE    | B, #08H        |              |      |        |

|          | BR     | LOOP4          |              |      |        |

|          | CALL   | !HEIKIN        |              |      |        |

|          | MOV    | TDATA, XA      |              |      |        |

|          | CALL   | !SIOSUB        |              |      |        |

|          | BR     | LOOP3          |              |      |        |

| ; ***    | HEIKIN | (SAMPLE NUMBE  | :<br>RS = 8) | ***  |        |

| SEG3     | CSEG   | SENT           | ,            |      | ; (10) |

| HEIKIN : | MOV    | C, #2H         |              |      |        |

| LOOP5 :  | XCH    | Α, Χ           |              |      |        |

|          | CLR1   | CY             |              |      |        |

|          | RORC   | А              |              |      |        |

|          | XCH    | Α, Χ           |              |      |        |

|          | RORC   | A              |              |      |        |

|          | DECS   | С              |              |      |        |

|          | BR     | LOOP5          |              |      |        |

|          | RET    |                |              |      |        |

|          | END    |                |              |      | ; (11) |

|          |        |                |              |      |        |

#### <Subroutine>

| \$               |              | A-D CONVERT'                           | *****                  | ; (12) |

|------------------|--------------|----------------------------------------|------------------------|--------|

| , ***            |              | /ERT PROGRAM                           | ***                    |        |

| ; *******        |              | ************************************** | ****                   | . (10) |

|                  | NAME         | AD_SUB                                 |                        | ; (13) |

|                  | EXTRN        | DATA (TDATA), C                        |                        | ; (14) |

|                  | PUBLIC       | SIOSUB, ADCON                          | V                      | ; (15) |

| • destada        | STKLN        | 2<br>BOUTINE ***                       |                        | ; (16) |

| ; ***            | CSEG         | ROUTINE ***<br>SENT                    |                        | . (17) |

| SEG4<br>SIOSUB : |              | BS                                     |                        | ; (17) |

| 30306.           | SEL          | RB2                                    |                        |        |

|                  | SEL          | MB1                                    |                        |        |

|                  | MOV          | XA, TDATA                              |                        |        |

|                  | GETI         | SEL15                                  | ; SEL MB15             |        |

|                  | MOV          | SIO, XA                                | , SEL MD15             |        |

|                  | MOV          | XA, #11101110B                         |                        |        |

|                  | MOV          | SIOM, XA                               | ; CLOCK = 262KHZ,      | MSB    |

|                  | POP          | BS                                     | , 02001( = 2021(12,    | mob    |

|                  | RET          | 20                                     |                        |        |

| ; ***            | ANALOG       | INPUT (RBE =                           | = 0) ***               |        |

| SEG5             | CSEG         | SENT                                   |                        | ; (18) |

| ADCONV           | PUSH         | BS                                     |                        |        |

|                  | GETI         | SEL15                                  | ; SEL MB15             |        |

|                  | MOV          | HL, #0D3H                              |                        |        |

|                  | MOV          | XA, #0C0H                              |                        |        |

|                  | MOV          | BSB0, A                                | ; $BSB0 \leftarrow 0H$ |        |

| LOOP :           | SET1         | BSB0, @L                               |                        |        |

|                  | MOV          | A, BSB0                                |                        |        |

|                  | MOV          | PTHM, XA                               | ; COMP. START          |        |

|                  | MOV          | A, #0AH                                | ; 18 MACHINE           |        |

| WAIT :           | INCS         | A                                      | ; CIRCLE WAIT          |        |

|                  | BR           | WAIT                                   |                        |        |

|                  | MOV1         | CY, @H+PTH0, 0                         |                        |        |

|                  | MOV1         | BSB0. @L, CY                           |                        |        |

|                  | DECS         | L                                      |                        |        |

|                  | BR           | LOOP                                   |                        |        |

|                  | MOV          | X, #0H                                 |                        |        |

|                  | MOV          | A, BSB0                                |                        |        |

|                  | ADDS         | XA', XA                                | ; ADD DATA             |        |

|                  | SET1         | RBE                                    |                        |        |

|                  | POP          | BS                                     |                        |        |

|                  | INCS<br>RETI | В                                      | ; SAMPLE COUNT IN      | NC.    |

|                  | END          |                                        |                        | ; (19) |

- (12) Assembler option

- (13) Module name declaration

- (14) Declaration as an external reference symbol of the symbol defined by another module

**Phase-out/Discontinued**

- (15) Declaration as an external definition symbol of the symbol referred to from another module

- (16) Stack size specification

- (17) Code segment start declaration

- (18) Code segment start declaration

- (19) Module end declaration

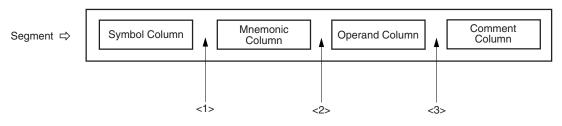

# 3.3 SOURCE PROGRAM DESCRIPTION FORMAT

## 3.3.1 Statement Format

\*

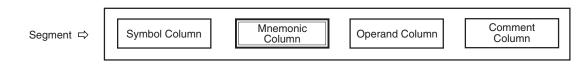

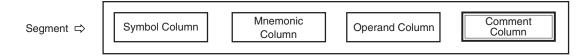

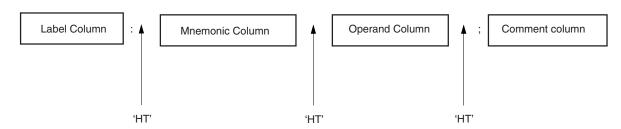

The source program consists of statements. One statement consists of 4 fields indicated in **Figure 3-3. Statement Component Fields**.

# Figure 3-3. Statement Component Fields

<1> The symbol column and the mnemonic column are divided with a colon (:) or more than one blank space (or TAB).

The separator to be used, a colon or space character, depends on the instruction described in the mnemonic column.

- <2> The mnemonic column and the operand column are divided with more than one blank space (or TAB). The operand column may not be necessary depending on the instruction to be described in the mnemonic column.

- <3> When entering in the comment column, describe a semi-colon (;) before the comment column.

One statement is described on one line.

Using description procedure based on a free method, description can be started with any column in the order of the symbol, mnemonic, operand and comment columns.

Description can be done for the following lines:

- Blank line (line having no statement description)

- Line with symbol column only

- · Line with comment column only

#### 3.3.2 Character Set

For statement description, standard-size alphanumeric characters and standard-size special characters are used (editors etc. available on the market may be used).

#### (1) Alphabetic letters (Figures in parentheses represents the JIS code.)

F Ρ В С D Е G Н J Κ L Ο Q А I Μ Ν (41H) (42H) (43H) (44H) (45H) (46H) (47H) (48H) (49H) (4AH) (4BH) (4CH) (4DH) (4EH) (4FH) (50H) (51H) R S Т U V W Х Υ Ζ (52H) (53H) (54H) (55H) (56H) (57H) (58H) (59H) (5AH) d а b С е f g h i i k m n 0 p α (61H) (62H) (63H) (64H) (65H) (66H) (67H) (68H) (69H) (6AH) (6BH) (6CH) (6DH) (6EH) (6FH) (70H) (71H) t s z r u V w Х y (72H) (73H) (74H) (75H) (76H) (77H) (78H) (79H) (7AH)

#### - Caution –

When a reserved word is described using small alphabetic letters, they are interpreted as capital letters.

#### (2) Numerals (Figures in parentheses represents the JIS code.)

| 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     |  |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| (30H) | (31H) | (32H) | (33H) | (34H) | (35H) | (36H) | (37H) | (38H) | (39H) |  |

### (3) Special characters

| Characters               | JIS Code                                      | Name                                                                               |                                                                                                                                                                                                                                         | Main Applications                                                                                                                                                                                                    |  |  |  |  |  |

|--------------------------|-----------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ?<br>@<br>               | 3FH<br>40H<br>6FH                             | Question mark<br>Unit price symbol<br>Underline                                    | Character corresponding<br>Indirect addressing start s<br>Character corresponding                                                                                                                                                       | symbol                                                                                                                                                                                                               |  |  |  |  |  |

| HT<br>,<br>;<br>CR<br>LF | 20H<br>09H<br>2CH<br>3AH<br>3BH<br>0DH<br>0AH | Blank<br>Tab code<br>Comma<br>Colon<br>Semi-colon<br>Return code<br>Line feed code | Division symbol                                                                                                                                                                                                                         | Division symbol foreach column<br>Character corresponding to blank space<br>Operand division symbol<br>Label division symbol<br>Comment column start symbol<br>Last symbol of one line<br>(ignored by the assembler) |  |  |  |  |  |

| +<br>-<br>*<br>/<br>()   | 2BH<br>2DH<br>2AH<br>2FH<br>2EH<br>28H        | Plus<br>Minus<br>Asterisk<br>Slash<br>Period<br>Left and right parentheses         | Assembler operator                                                                                                                                                                                                                      | Add operator or plus sign<br>Subtraction operator or minus sign<br>Multiplication operator<br>Division operator<br>Bit operator<br>Operation order change                                                            |  |  |  |  |  |

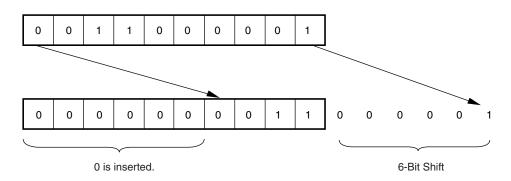

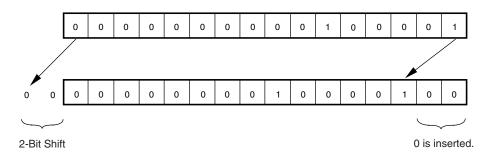

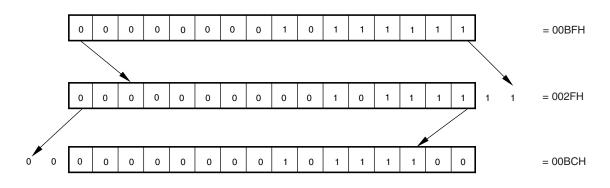

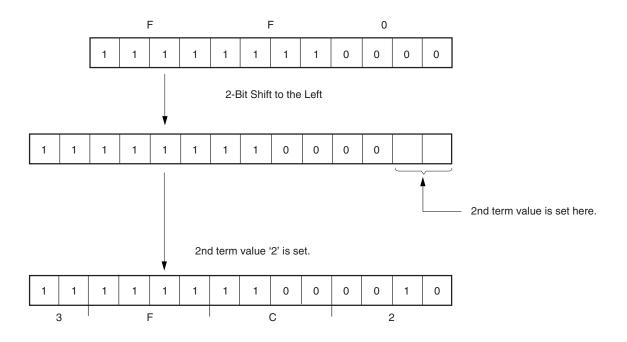

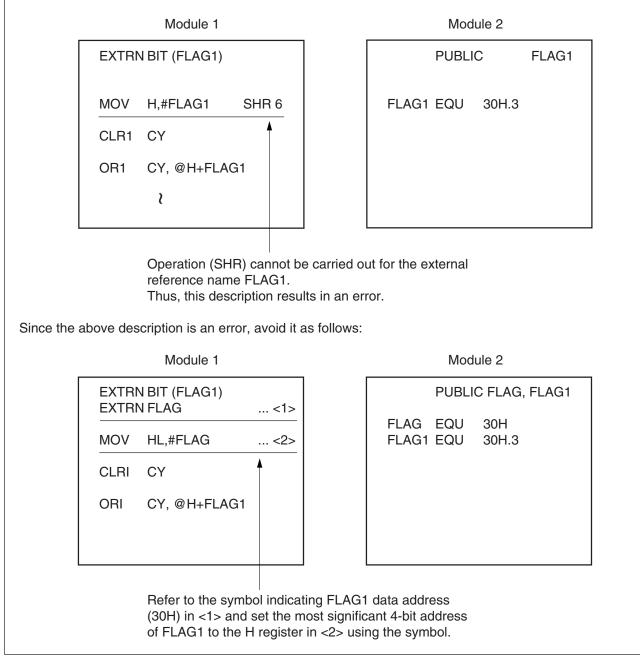

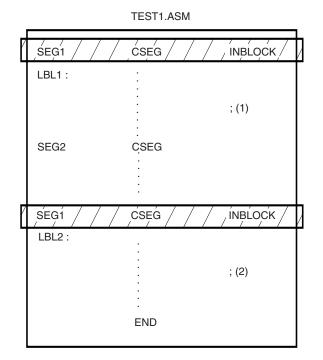

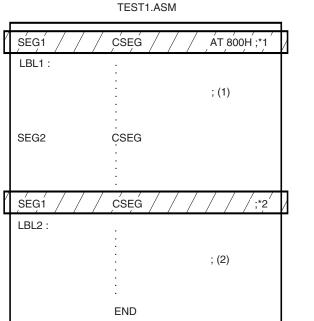

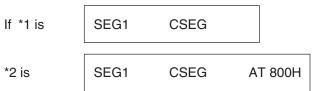

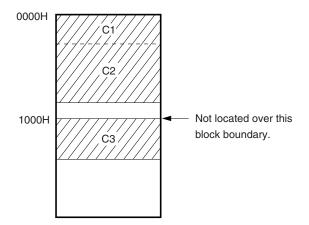

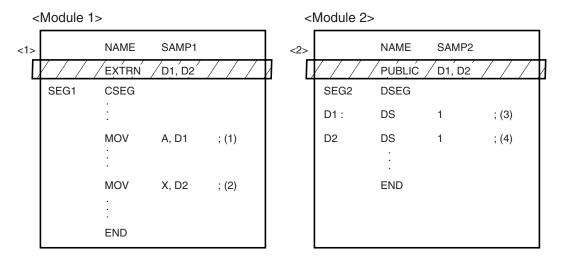

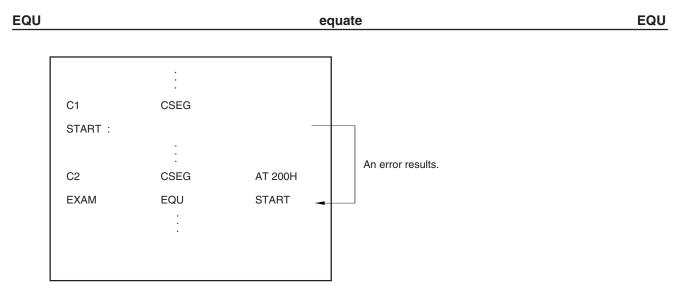

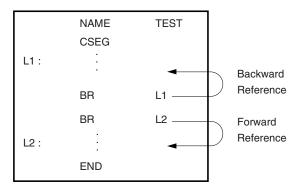

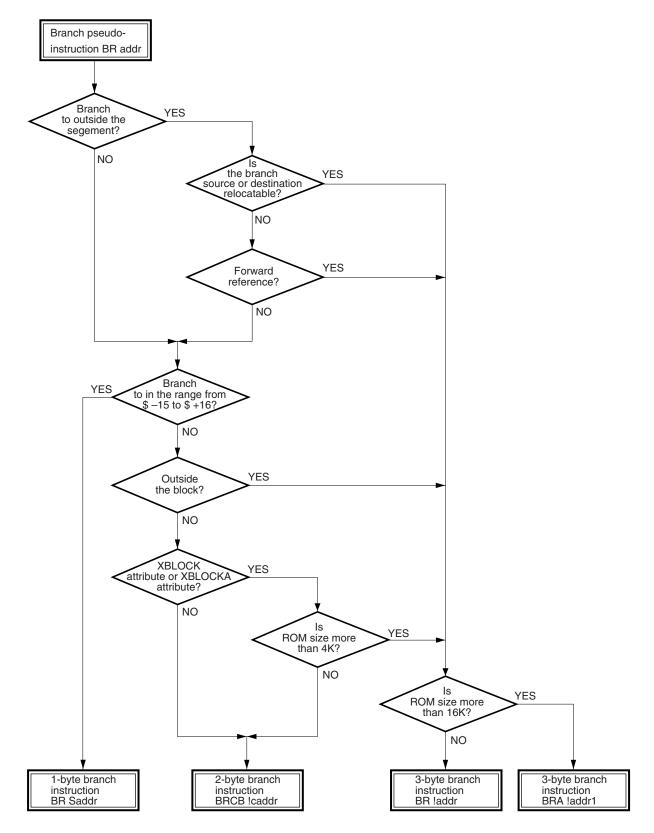

| ,<br><<br>><br>=         | 27H<br>3CH<br>3EH<br>3DH                      | Quotation mark<br>Inequality<br>sign<br>Equality sign                              | Character constant start a                                                                                                                                                                                                              | and end symbols                                                                                                                                                                                                      |  |  |  |  |  |