## IPS2550

## Contents

| 1. | Intro | duction  |                                                     | 4  |

|----|-------|----------|-----------------------------------------------------|----|

|    | 1.1   | Quick-S  | Start / Default Configuration                       | 4  |

|    | 1.2   | Prograr  | mming Procedure                                     | 4  |

|    | 1.3   | IPS255   | 50 Block Diagram                                    | 5  |

|    | 1.4   | Prograr  | mming Modes                                         | 5  |

|    |       | 1.4.1.   | Programming Over I2C Pins                           | 5  |

|    |       | 1.4.2.   | Programming Over Output Pins                        | 6  |

|    |       | 1.4.3.   | Programming Over Output Pins Using the IPS-Comboard | 7  |

|    | 1.5   | Automa   | atic Gain Control (AGC)                             |    |

| 2. | I2C I | nterface |                                                     | 9  |

|    | 2.1   | Suppor   | ted Features                                        | 9  |

|    | 2.2   | Not Su   | pported Optional Features                           | 9  |

|    | 2.3   | Slave A  | Address                                             | 10 |

|    | 2.4   | Operati  | ion and Frame Format                                | 11 |

|    | 2.5   | Memor    | y Address                                           | 11 |

|    | 2.6   | Conten   | ıt Data Bytes                                       | 12 |

|    | 2.7   | SINGLE   | E WRITE Operation                                   | 12 |

|    | 2.8   | SINGLE   | E READ Operation                                    | 13 |

|    | 2.9   | Protoco  | ol Integrity Check                                  | 13 |

|    |       | 2.9.1.   | Slave Address Parity Check                          | 13 |

|    |       | 2.9.2.   | Content Data CRC check                              | 13 |

| 3. | Mem   | ory Arch | hitecture                                           | 14 |

|    | 3.1   | Memor    | y Map and Default FTP Values                        | 14 |

|    | 3.2   | Registe  | er Descriptions                                     | 16 |

|    |       | 3.2.1.   | FTP (Non-Volatile) and SRB (Volatile)               | 16 |

|    |       | 3.2.2.   | SFR (Special Functions Register)                    | 30 |

| 4. | Glos  | sary     |                                                     | 38 |

| 5  | Rovi  | eion Hie | tory                                                | 38 |

# **Figures**

| Figure 1. Block Diagram                                                                                             | 5  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Programming the IPS2550 Over the I2C Interface                                                            | 6  |

| Figure 3. Programming the IPS2550 Over the Output Pins                                                              | 6  |

| Figure 4. Enter Programming Mode Over Output Pins                                                                   | 7  |

| Figure 5. Enter Programming Commands                                                                                | 7  |

| Figure 6. AGC Effect on Change in Magnitude                                                                         | 8  |

| Figure 7. I2C Bit Transfer Signal State                                                                             | 9  |

| Figure 8. I2C START and STOP Conditions                                                                             | 10 |

| Figure 9. I2C Acknowledge Signal State                                                                              | 10 |

| Figure 10. I2C Device Address                                                                                       | 10 |

| Figure 11. Memory Address Byte                                                                                      | 11 |

| Figure 12. Content Data Bytes                                                                                       | 12 |

| Figure 13. Single Write Frame                                                                                       | 12 |

| Figure 14. Single Read Frame                                                                                        | 13 |

| Figure 15. Memory Architecture                                                                                      | 14 |

| Figure 16. Compensated and Uncompensated Amplitude Mismatch                                                         | 20 |

| Figure 17. Compensated and Uncompensated Signal Offset                                                              | 21 |

| Figure 18. Transmitter current configuration for LC Tank                                                            | 23 |

| Tables         Table 1. Programmable I2C Slave Addresses with ADR_IRQN PIN 1 configured for Interrupt Output (0x00) |    |

| system_protocol='0')system_protocol='0')                                                                            |    |

| Table 2. Programmable I2C Slave Addresses with ADR_IRQN Pin 1 configured for Adress Input (0x00,                    |    |

| system_protocol='1')                                                                                                | 11 |

| Table 3. I2C Slave Address Byte and Memory Address Field Integrity Check                                            |    |

| Table 4. I2C <contentdata> Integrity Check</contentdata>                                                            |    |

| Table 5. FTP (Non-Volatile)                                                                                         | 14 |

| Table 6. SRB/SFR (Volatile)                                                                                         | 15 |

| Table 7. System Configuration 1: Address 0x00 FTP; 0x40 SRB                                                         | 16 |

| Table 8. System Configuration 2: Address 0x01 FTP; 0x41 SRB                                                         | 16 |

| Table 9. R1/R2 gain: Address 0x02 FTP; 0x42 SRB                                                                     | 18 |

| Table 10. R1 Fine Gain Compensation: Address 0x03 FTP; 0x43 SRB                                                     | 20 |

| Table 11. R1 Offset Compensation: Address 0x04 FTP; 0x44 SRB                                                        | 21 |

| Table 12. R2 Fine Gain Compensation: Address 0x05 FTP; 0x45 SRB                                                     | 22 |

| Table 13. R2 Offset Compensation: Address 0x06 FTP; 0x46 SRB                                                        | 22 |

| Table 14. Transmitter Current Configuration: Address 0x07 FTP; 0x47 SRB                                             | 23 |

| Table 15. Transmitter Bias Current in μA                                                                            | 24 |

| Table 16. Transmitter Frequency Time-Base: Address 0x08 FTP; 0x48 SRB                                               | 25 |

| Table 17. Transmitter Frequency Lower Limit: Address 0x09 FTP; 0x49 SRB                                             | 25 |

| Table 18. Transmitter Frequency Upper Limit: Address 0x0A FTP; 0x4A SRB                                             | 25 |

| Table 19. Interrupt Enable 1: Address 0x0B FTP; 0x4B SRB                                                            | 26 |

| T                                                                                                                   |    |

| Table 20. Interrupt Enable 2: Address 0x0C FTP; 0x4C SRB                                                            |    |

| Table 22. IRQN Watchdog: Address 0x0E FTP; 0x4E SRB                  | 28 |

|----------------------------------------------------------------------|----|

| Table 23. AGC Plausibility Configuration: Address 0x0F FTP; 0x4F SRB | 29 |

| Table 24. Customer Identification: Address Register 0x18 FTP         | 29 |

| Table 25. Product Identifier: Address 0x19 FTP                       | 29 |

| Table 26. Interrupt Clear 1: Address 0x68 SFR                        | 30 |

| Table 27. Interrupt Clear 2: Address 0x69 SFR                        | 31 |

| Table 28. Interrupt Clear 3: Address 0x6A SFR                        | 32 |

| Table 29. Interrupt State 1: Address 0x6B SFR                        | 33 |

| Table 30. Interrupt State 2: Address 0x6C SFR                        | 34 |

| Table 31. Interrupt State 3: Address 0x6D SFR                        |    |

| Table 32. Transmitter Counter State: Address 0x6E SFR                | 35 |

| Table 33. FTP ECC State: Address 0x70 SFR                            | 36 |

| Table 34. Product Identifier Version: Address 0x73 SFR               | 36 |

| Table 35. AGC_OBSERVATION: Address 0x78 SFR                          | 36 |

| Table 36. DBIST_STS: Address 0x79 SFR                                | 37 |

| Table 37 External SM for Checking CRC: Address 0x7E SER              | 37 |

#### 1. Introduction

The IPS2550 is a high-speed inductive position sensor with analog sine and cosine voltage output, which can be differential or single-ended. The analog high-speed sensor is optimized for lowest propagation delay.

The IPS2550 high-speed inductive position sensor is used in automotive, industrial, medical, and consumer applications. The sensor configuration can be changed to address a wide range of applications. This document describes digital communication with the IPS2550 and the available configuration options.

The digital communication interface of the IPS2550 uses I2C Standard-mode to program, configure and to read the diagnostic status. In addition to using the dedicated SDA and SCL pins, it is also possible to communicate via I2C protocol over the analog output pins to reduce the number of wires to a sensor module. The Slave Address is programmable in the register and can be modified by applying the correct voltage at ADR IRQN pin1, for details see section 2.3.

**Note**: It is highly recommended to read the *IPS2550 Datasheet* for electrical characteristics, product details, such as features, pin descriptions, functionality, and circuit descriptions before reading this manual.

### 1.1 Quick-Start / Default Configuration

The IPS2550 comes with a default configuration for the transmitter bias current, automatic gain control and output pins in differential sine and cosine voltage mode. Diagnostic alarm at the output pins is not active. The sensor outputs sine and cosine voltages relative to the target position after power-up without the need for programming in case the sensor coils are designed appropriately to work with the default configuration.

**Default Configuration:** (refer to section 3.1 for details)

Supply Mode: 5V

Output Mode: SIN/COS differential AGC Mode: ON (gain booster off)

Interrupt Signaling: Off

I2C ADR/IRQN Pin: I2C address pin

I2C Address: 24dec (ADR pin high), 17dec (ADR pin low)

I2C Integrity check: ON

RX configuration: INTERLEAVED - IPS2550

TX bias current: 496uA

#### 1.2 Programming Procedure

The programming parameters depend on the application requirements. Most parameters do not change for production parts. Some parameters can be programmed individually to compensate production tolerances. A programming procedure usually includes following steps:

- 1. **General Configuration** (Select the correct supply voltage, Interface mode, etc. mainly in system configuration registers Adr 0x00, 0x01, ...)

- 2. Transmitter Configuration (TX Bias Current Setting, Adr 0x07)

- 3. Receiver Configuration (can be programmed individually if needed)

- a. Static Gain Adjustment if AGC is switched off (Adr 0x02)

- b. Signal Offset Compensation (Adr 0x04, 0x06)

- c. Amplitude Mismatch Compensation (Adr 0x03, 0x05)

Dec.15.25

4. **Diagnostics Configuration** (Diagnostic Mask, Alarm Levels, Adr 0x0B, 0x0C, 0x0D, 0x0F, 0x08, 0x09, 0x0A)

#### Notes:

- To avoid possible error signalling during a configuration procedure, it is recommended to enable the backend interrupt signalling (by System Configuration 1: Address 0x00 FTP; 0x40 SRB, back\_end\_irqn\_ena) and the interrupt mask (in Interrupt Enable 1: Address 0x0B FTP; 0x4B SRB, Interrupt Enable 2: Address 0x0C FTP; 0x4C SRB and Interrupt Enable 3: Address 0x0D FTP; 0x4D SRB) at the end of the programming procedure.

- It is recommended to disable the AGC and configure a fixed gain during configuration of offset compensation and gain mismatch registers to avoid distortion of measurements during a compensation procedure (R1 Fine Gain Compensation: Address 0x03 FTP; 0x43 SRB, R1 Offset Compensation: Address 0x04 FTP; 0x44 SRB, R2 Fine Gain Compensation: Address 0x05 FTP; 0x45 SRB, R2 Offset Compensation: Address 0x06 FTP; 0x46 SRB).

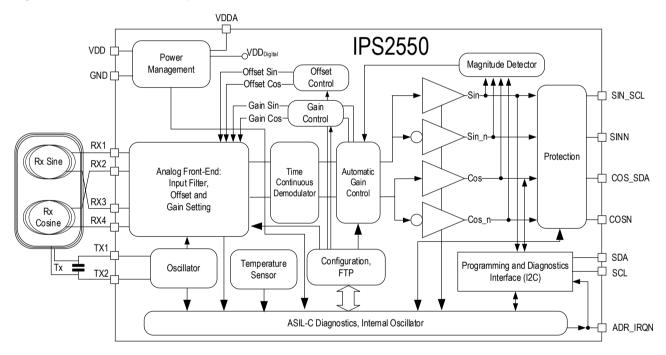

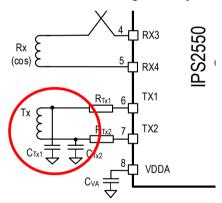

## 1.3 IPS2550 Block Diagram

Figure 1 shows the main components of the IPS2550.

Figure 1. Block Diagram

## 1.4 Programming Modes

There are two different programming modes available:

- Programming over I2C pins: used for embedded applications with I2C pins permanently connected to the sensor IC.

- Programming over output pins (slower): used for remote applications like a sensor module where only supply and output pins are available.

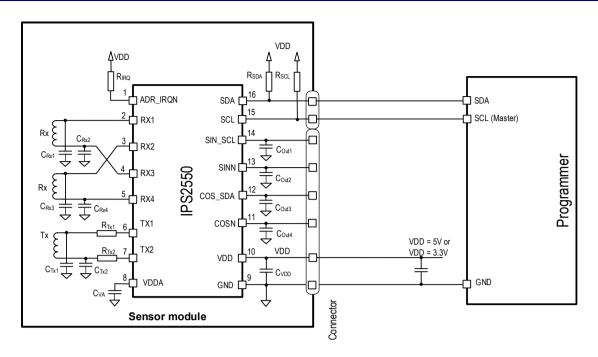

#### 1.4.1. Programming Over I2C Pins

The IPS2550 can be programmed with a clock frequency of up to 100kHz over the I2C interface pins SDA (pin16) and SCL (pin15). The I2C pins must be tied to VDD using two pull-ups as shown below. Communication over the I2C pins is available during operation and allows reading the diagnostic status while the differential sine cosine output is active.

Figure 2. Programming the IPS2550 Over the I2C Interface

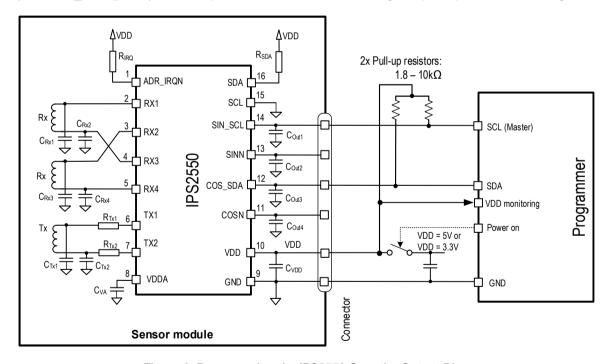

## 1.4.2. Programming Over Output Pins

The IPS2550 can be programmed with a clock frequency of up to 25kHz over the output pins COS\_SDA (pin12) and SIN\_SCL (pin14). The I2C pins must be tied to VDD using two pull-ups as shown in Figure 3.

Figure 3. Programming the IPS2550 Over the Output Pins

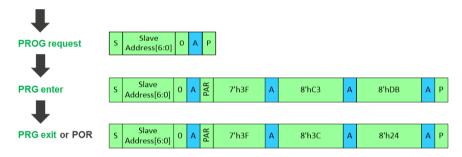

Programming over the output pins can be enabled only by sending an unlock command within a defined timeframe during the start-up procedure. In operation mode SinP/CosP are solely analog outputs used for either mission mode data, or diagnostics. The procedure to enter and exit the Programming mode is shown below.

Figure 4. Enter Programming Mode Over Output Pins

To enter the Programming mode, the programming request must be sent: the master must send the Slave Address byte with R/W bit set to '0' in the 1ms to 3ms time frame after the power-on-reset. If NACK is received, first step of the programming entry is not successful.

Once the programming request is received, the IPS2550 does not start in Normal Operation mode, but a programming window is enabled for 75ms.

During the programming window, a password command must be sent consisting of Slave Address, Memory Address and password code as shown in Figure 5. If the valid password command is received, the programming window counter is stopped and the IPS2550 enters the Programming mode. If no valid password command is received, the IPS2550 enters the Normal Operation mode after the programming window counter is finished after 75ms.

**Figure 5. Enter Programming Commands**

After successful configuration and programming, exit the Programming mode by sending the exit command.

#### Notes:

- During programming mode via the analog output pins, the analog output voltage can be read from SIN\_N

and COS N pins only for sensor configuration.

- When entering the programming mode via the analog output pins, the i2c\_protocol\_fail flag in register Interrupt State 1: Address 0x6B SFR is set. Reset the error flag during the programming procedure if needed.

If IPS2550 is programmed via the analog output pins, the outbuf\_vcm\_fail flag in register Interrupt State 2: Address 0x6C SFR is set.

#### 1.4.3. Programming Over Output Pins Using the IPS-Comboard

When using the IPS-comboard to program an IPS2550 over the analog output pins, consider the following:

- Select 4kHz I2C clock (automatically selected by GUI)

- Filtering capacitors must be max 47nF or lower

- For further details please refer to the User Manual of the IPS2550 Starter Kit

X0116354 Page 7

Dec.15.25

#### 1.5 Automatic Gain Control (AGC)

As default, the automatic gain control is active. The AGC uses the signal of an internal magnitude detector to control the signal amplitudes into a control window as defined in the IPS2550 Datasheet document.

The AGC uses all available gain steps per default. If agc plause chk en is activated (0x02, bit10), the AGC uses only gain steps inside the plausibility range defined in the AGC Plausibility register (Address 0x0F FTP; 0x4F SRB). If the AGC plausibility check is enabled, the agc err bit is set when the plausibility boundary code configured in the AGC Plausibility Configuration register (agc plause uthresh, agc plause Ithresh) is reached.

Note: The upper plausibility threshold must be higher than the lower plausibility threshold.

It is possible to double the overall gain by using d2a afe boost sel (0x02, bit07).

Some applications may require a static gain setting. In this case, the AGC must be disabled (0x00, bit9 afe agc dis) and the R1/R2 gain register must be configured for the desired gain.

To see if the AGC is in range, check the agc err bit (0x6C, bit 1).

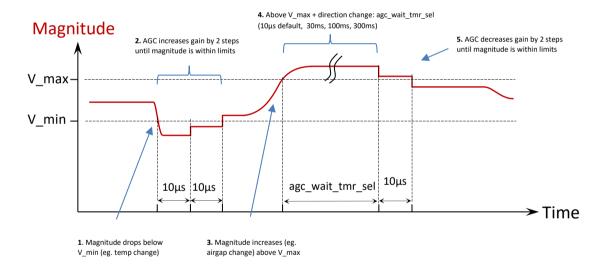

By using bits agc wait tmr sel (0x02, bits [9:8]), the wait time after a direction change of the magnitude can be configured as shown in Figure 6. The default is 10µs.

After power-up, the AGC starts to work from the gain value that is configured for R1/R2.

Note: The agc\_err bit is set during start-up if an AGC start value is programmed and the magnitude exceeds the AGC target range until the correct gain value is reached. To avoid such situation during start-up, set the R1/R2 gain to a low value or '0' when using the AGC.

Figure 6. AGC Effect on Change in Magnitude

For lab evaluation purpose the actual AGC value can be read from the agc\_gain\_stage (0x78, bits[6:0]) register.

The target amplitude is  $0.9V \pm 0.2V$  (default).

Note: The default typical peak amplitude on an output pin is 0.9V, and 1.8V peak-peak if the sensor is operated within AGC range. The differential typical output voltage between positive and negative output pin is 3.6V.

X0116354 RENESAS Page 8

#### 2. I2C Interface

To communicate with a microcontroller, the IPS2550 uses a two-wire Inter-Integrated Circuit (I2C) interface based on the specification rev. 6. The Slave Address is programmable and pin 1 can be configured as an address or interrupt pin.

## 2.1 Supported Features

- · Standard-mode (Sm) up to 100 kbit/s

- Start condition

- Stop condition

- Acknowledge

- o 7-bit Slave Address

- · Single Write Operation

- · Single Read Operation

## 2.2 Not Supported Optional Features

The following features are not supported:

- Clock stretching

- · 10-bit Slave Address

- · General Call Address

- Software Reset

- Device ID

Two wires connected to the serial data pin (SIO\_SDA, pin 16) and serial clock pin (SCK\_SCL, pin 15) carry information between the devices connected to the bus. Both SDA and SCL pins are connected to VDD via external pull-up resistors. When the bus is free, both lines are high. An external master (host controller) initiates a transfer, generates clock signals, and terminates a transfer.

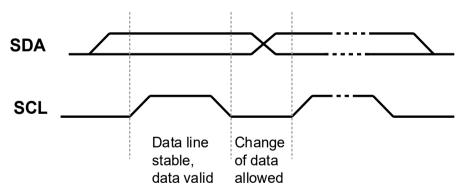

The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change when the clock signal on the SCL line is low.

Figure 7. I2C Bit Transfer Signal State

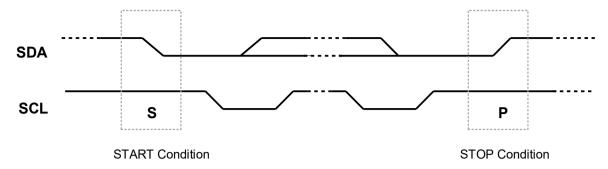

A data transfer is initiated by a START condition (S) and is defined as a high to low transition on the SDA line while SCL is high. A STOP condition (P) is defined as a low to high transition on the SDA line while SCL is high as shown in Figure 8.

The master always generates START and STOP conditions. The bus is considered busy after the START condition. The bus is considered to be free again after the STOP condition.

Figure 8. I2C START and STOP Conditions

If a repeated START (Sr) is generated instead of a STOP condition, the bus stays busy. In this respect, the START and repeated START conditions are functionally identical.

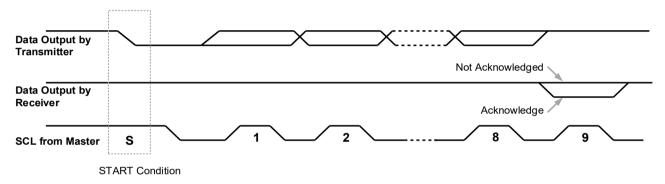

Every transfer block on the SDA line must have a length of 1 byte (8 bits). The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an acknowledge bit from the I2C master (see Figure 9). Data is transferred with the most significant bit (MSB) first. Data transfer with acknowledgement is mandatory.

Figure 9. I2C Acknowledge Signal State

#### 2.3 Slave Address

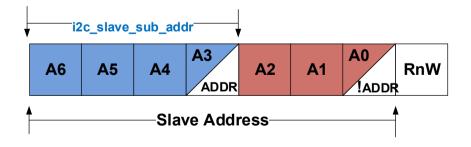

The IPS2550 supports a 7-bit I2C Slave Address. The Slave Address format is shown in Figure 10.

The Slave Address can be configured by four programmable bits (A6, A5, A4, A3). These bits can be modified in System Configuration 1 register (0x00, bits [7:4] i2c\_slave\_sub\_addr). Slave address bits A2, A1, A0 are reserved bits and are set to '0' if pin1 is configured as interrupt pin.

If pin1 is configured as address pin (default, System Configuration 1 (0x00, bit [0]=0b1 system\_protocol)), A3 has the state of the address pin and A0 has the inverse state of the address pin.

Figure 10. I2C Device Address

Up to 21 devices can be connected to the same bus when using the address pin, and up 14 devices when using different address pins. Two groups of reserved addresses (0000XXX and 1111XXX) are excluded. A list of configurable slave addresses is shown in Table 1.

Table 1. Programmable I2C Slave Addresses with ADR\_IRQN PIN 1 configured for Interrupt Output (0x00, system\_protocol='0')

| i2c_slave_sub_addr dec | 1       | 2       | 3       | 4       | 5       | 6       | 7       |

|------------------------|---------|---------|---------|---------|---------|---------|---------|

| [A6:A0] bin            | 0001000 | 0010000 | 0011000 | 0100000 | 0101000 | 0110000 | 0111000 |

| slave adr dec          | 8       | 16      | 24      | 32      | 40      | 48      | 56      |

| slave adr hex          | 8       | 10      | 18      | 20      | 28      | 30      | 38      |

| i2c_slave_sub_addr dec | 8       | 9       | 10      | 11      | 12      | 13      | 14      |

| [A6:A0] bin            | 1000000 | 1001000 | 1010000 | 1011000 | 1100000 | 1101000 | 1110000 |

| slave adr dec          | 64      | 72      | 80      | 88      | 96      | 104     | 112     |

| slave adr hex          | 40      | 48      | 50      | 58      | 60      | 68      | 70      |

Table 2. Programmable I2C Slave Addresses with ADR\_IRQN Pin 1 configured for Adress Input (0x00, system\_protocol='1')

|                        |                  | Default                 | Default                  |                        |                  |                       |                       |

|------------------------|------------------|-------------------------|--------------------------|------------------------|------------------|-----------------------|-----------------------|

| i2c_slave_sub_addr dec | 0, 1             | 2, 3                    | 2, 3                     | 4, 5                   | 4, 5             | 6, 7                  | 6, 7                  |

| [A6:A0] bin            | 000 <u>1</u> 000 | 001 <u>0</u> 001        | 001 <u>1</u> 000         | <b>010<u>0</u></b> 001 | 010 <u>1</u> 000 | <b>011<u>0</u>001</b> | <b>011<u>1</u>000</b> |

| slave adr dec          | 8                | 17                      | 24                       | 33                     | 40               | 49                    | 56                    |

| slave adr hex          | 8                | 11                      | 18                       | 21                     | 28               | 31                    | 38                    |

| ADR Pin                | <u>High</u>      | ADR =<br>" <u>LOW</u> " | ADR =<br>" <u>HIGH</u> " | Low                    | <u>High</u>      | <u>Low</u>            | <u>High</u>           |

| i2c_slave_sub_addr dec | 8, 9             | 8, 9                    | 10, 11                   | 10, 11                 | 12, 13           | 12, 13                | 14, 15                |

| [A6:A0] bin            | 100 <u>0</u> 001 | 100 <u>1</u> 000        | <b>101<u>0</u>001</b>    | <b>101<u>1</u>000</b>  | 110 <u>0</u> 001 | 110 <u>1</u> 000      | 111 <u>0</u> 001      |

| slave adr dec          | 65               | 72                      | 81                       | 88                     | 97               | 104                   | 113                   |

| slave adr hex          | 41               | 48                      | 51                       | 58                     | 61               | 68                    | 71                    |

| ADR Pin                | Low              | <u>High</u>             | Low                      | <u>High</u>            | Low              | <u>High</u>           | Low                   |

## 2.4 Operation and Frame Format

The IPS2550 supports both read and write operation. By default, the protocol integrity check is enabled for all I2C frames and can be deactivated in System Configuration 2 register (0x01, bit [2] prot\_integ\_check\_dis).

#### 2.5 Memory Address

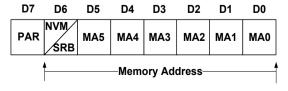

The first data byte after the Slave Address is defined as memory address <MemAddr> and consists of:

- D7 Slave Address Parity Bit

- D6....D0 6-bit memory address

Figure 11. Memory Address Byte

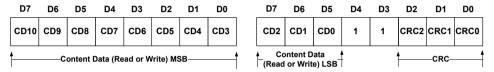

### 2.6 Content Data Bytes

The following consecutive pairs of data bytes (<CmdData> field) contain the 11-bit information for the memory. The remaining 5-bits are reserved and fixed to '1'. The sequence is MSB first.

#### Data Byte N:

D7 ....D0 < ContentData[10:3]>

#### Data Byte N+1:

- D7 ....D5 < ContentData[2:0]>

- D4 ....D3 <Reserved, always 2'b11>

- D2 ....D0 <Reserved>:

- 。 Integrity check 'On': CRC[2:0] over Memory Address and Content Data

- Integrity check 'Off': <Reserved> (Always all 1's)

The <Reserved> field is checked for all 1's and if the check fails the <ContentData> field is not written to the addressed memory space (no write action) and the slave receiver does not produce an acknowledge.

Figure 12. Content Data Bytes

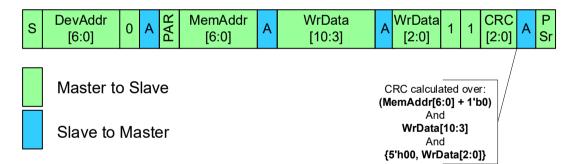

## 2.7 SINGLE WRITE Operation

For a single write operation, the Slave Address byte has the R/W bit set to '0' and is followed by the memory address byte and two content data bytes as shown below in Figure 13. The master sends the address bytes and content data, which are acknowledged by the slave.

Figure 13. Single Write Frame

#### Notes:

- If I2C master continue to provide clocks and data after the second write data byte, the IC will NACK the next byte.

- · Consider the programming time when writing to a FTP register. Refer to Table 5 for details.

Dec.15.25

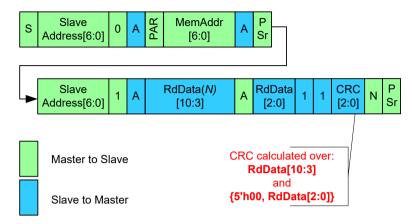

### 2.8 SINGLE READ Operation

For a single read operation, the Slave Address byte has the R/W bit set to '0', followed by the memory address byte. After a stop (P) or repeated start (Sr) condition, the Slave Address byte follows with the R/W bit set to '1' and two content data bytes. The master sends the address bytes, which are acknowledged by the slave. The slave sends the content data, which are acknowledged by the master.

Figure 14. Single Read Frame

**Note:** If the I2C master continues to provide clocks after the second read data byte, the IC continues to provide the same read data.

### 2.9 Protocol Integrity Check

The Data Integrity Check is an extension of the I2C protocol for fail safe communication between I2C master and slave devices. This check is activated by default, and can be disabled in System Configuration 2 register (0x01, bit [2] prot\_integ\_check\_dis).

#### 2.9.1. Slave Address Parity Check

The IPS2550 supports an even parity check of I2C device address. If the check fails, the subsequent command is discarded and the diagnostic status "protocol integrity fail" is asserted.

PAR: Even parity calculated and checked for preceding received SlaveAddress address byte:

PAR = XOR ({SlaveAddr, RnW})

Table 3 shows the Slave Address field handling for verified "read/write action".

Table 3. I2C Slave Address Byte and Memory Address Field Integrity Check

| Protocol Integrity Check Disable | D7                  | D6D0       | Diagnostic | Description                                         |

|----------------------------------|---------------------|------------|------------|-----------------------------------------------------|

| 0b1                              | 0b1                 | 0bxxxxxxxx | Asserted   | No action, no slave acknowledge                     |

| 0b1                              | 0b0                 | 0bxxxxxxx  | Idle       | Read/write action                                   |

| 0b0                              | $PAR_{fail}$        | 0bxxxxxxxx | Asserted   | Parity check fails, no action, no slave acknowledge |

| 0b0                              | PAR <sub>pass</sub> | 0bxxxxxxx  | Idle       | Parity check passes, read/write action              |

#### 2.9.2. Content Data CRC check

A 16-bit word is defined and transported by two consecutive data bytes (data byte n, data byte n+1).

A 3-bit CRC field is defined to detect the presence of errors in the transmission of each 16-bit data word. If the data transferred does not pass CRC verification, no write action is taken, the slave receiver does not produce an acknowledge, and the diagnostic status "protocol\_integrity\_fail" is asserted.

The polynomial used to calculate the 3-bit CRC is:

$$CRC(x) = x^3 + x^1 + x^0$$

Table 4 shows the data word handling for verified "write action".

| Table 4   | 12C | <contentd< th=""><th>ata&gt; Inted</th><th>rity Check</th></contentd<> | ata> Inted  | rity Check  |

|-----------|-----|------------------------------------------------------------------------|-------------|-------------|

| I able T. | 120 | ~OULLELLED                                                             | ala- IIILEI | ALIEV OHECK |

| Protocol Integrity<br>Check Disable | <contentdata></contentdata> | <reserved></reserved>    |             | Diagnostic | Description                                |

|-------------------------------------|-----------------------------|--------------------------|-------------|------------|--------------------------------------------|

| 0b1                                 | 0bxxx_xxxx_xxxx             | 0b1_11                   | 11          | Idle       | Write action executed                      |

| 0b1                                 | 0bxxx_xxxx_xxxx             | 0b0_0000<br><br>0b1 1110 |             | Asserted   | Write action suspend, no slave acknowledge |

| Protocol Integrity<br>Check Enable  | < ContentData >             | <reserved></reserved>    | <crc></crc> | Diagnostic | Description                                |

| 0b0                                 | 0bxxx_xxxx_xxxx             | 0b11                     | Pass        | Idle       | Write action executed                      |

| 0b0                                 | 0bxxx_xxxx_xxxx             | 0b11                     | Fail        | Asserted   | Write action suspend, no slave acknowledge |

| 0b0                                 | 0bxxx_xxxx_xxxx             | 0b00<br><br>0b10         | Fail        | Asserted   | Write action suspend, no slave acknowledge |

| 0b0                                 | 0bxxx_xxxx_xxxx             | 0b00<br><br>0b10         | Pass        | Asserted   | Write action suspend, no slave acknowledge |

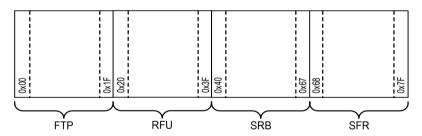

## 3. Memory Architecture

The memory architecture of the IPS2550 consists of three different storage blocks with a total address range of 7 bits as follows:

Few Times Programmable (FTP) 00HEX through 1FHEX

Internal Configuration (RFU) 20HEX through 3FHEX

Shadow Register Bank (SRB) 40HEX through 67HEX

Special Function Register (SFR) 68HEX through 7FHEX

Figure 15. Memory Architecture

#### Notes:

- Some registers are be modified by internal processes.

- After power-on-reset (POR), most of the FTP content is mirrored into the corresponding SRB address range within the start-up time window.

- Do not change registers and bits that are marked as "Internal Configuration (RFU)" with note "Read as X".

#### 3.1 Memory Map and Default FTP Values

After writing to a FTP register, a programming time of minimum 3ms is required before a new command can be sent.

Table 5. FTP (Non-Volatile)

| Address (hex) | Description            |      | Default<br>Value         |      |      |        |

|---------------|------------------------|------|--------------------------|------|------|--------|

|               | -                      | 1512 | 118                      | 74   | 30   | hex    |

| 0x00          | System configuration 1 | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0121 |

| 0x01          | System configuration 2 | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0001 |

| 0x02          | R1/R2 gain             | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0300 |

| 0x03          | R1 gain compensation   | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| Address (hex) | Description                       |      | Default<br>Value         |      |      |        |

|---------------|-----------------------------------|------|--------------------------|------|------|--------|

| ,             |                                   | 1512 | 118                      | 74   | 30   | hex    |

| 0x04          | R1 offset compensation            | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x05          | R2 gain compensation              | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x06          | R2 offset compensation            | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x07          | Transmitter current configuration | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x00BE |

| 0x08          | Transmitter frequency time-base   | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x00AF |

| 0x09          | Transmitter frequency lower limit | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x0A          | Transmitter frequency upper limit | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x07FF |

| 0x0B          | Interrupt enable 1                | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x0C          | Interrupt enable 2                | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x0D          | Interrupt enable 3                | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x0E          | IRQN watchdog                     | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x0F          | AGC Plausibility configuration    | ECC  | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 | 0x0000 |

| 0x100x17      | Internal Configuration            |      |                          |      |      |        |

| 0x18          | Customer Identifier               | ECC  | PDED, n10n8              | n7n4 | n3n0 | 0x0000 |

| 0x19          | Product Identifier                | ECC  | PDED, n10n8              | n7n4 | n3n0 | 0x0019 |

| 0x1A0x3E      | Internal Configuration            |      |                          |      |      |        |

| 0x3F          | Entry / Exit analog programming   |      | Read as '                | Κ'   |      |        |

## Table 6. SRB/SFR (Volatile)

| Address (hex) | Description                       |          | Bit position             |      |      |  |  |

|---------------|-----------------------------------|----------|--------------------------|------|------|--|--|

|               |                                   | 1512     | 118                      | 74   | 30   |  |  |

| 0x40          | System configuration 1            | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x41          | System configuration 2            | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x42          | R1/R2 gain                        | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x43          | R1 gain compensation              | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x44          | R1 offset compensation            | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x45          | R2 gain compensation              | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x46          | R2 offset compensation            | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x47          | Transmitter current configuration | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x48          | Transmitter frequency time-base   | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x49          | Transmitter frequency lower limit | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x4A          | Transmitter frequency upper limit | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x4B          | Interrupt enable 1                | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x4C          | Interrupt enable 2                | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x4D          | Interrupt enable 3                | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x4E          | IRQN watchdog                     | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x4F          | AGC Plausibility configuration    | ECC      | P <sub>DED</sub> , n10n8 | n7n4 | n3n0 |  |  |

| 0x500x67      | Internal Configuration            |          | Read as 'X'              | 1    |      |  |  |

| 0x68          | Interrupt clear 1                 | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x69          | Interrupt clear 2                 | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x6A          | Interrupt clear 3                 | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x6B          | Interrupt state 1                 | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x6C          | Interrupt state 2                 | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x6D          | Interrupt state 3                 | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x6E          | Transmitter counter state         | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x6F          | Internal Configuration            |          | Read as 'X'              | '    |      |  |  |

| 0x70          | FTP ECC state                     | Not used | 'x', n10n8               | n7n4 | n3n0 |  |  |

| 0x710x72      | Internal Configuration            |          | Read as 'X'              |      |      |  |  |

| Address (hex) | Description                  | Bit position |            |      |      |  |

|---------------|------------------------------|--------------|------------|------|------|--|

|               |                              | 1512         | 118        | 74   | 30   |  |

| 0x73          | Product Identifier Version   | Not used     | 'x', n10n8 | n7n4 | n3n0 |  |

| 0x740x77      | Internal Configuration       | Read as 'X'  |            |      |      |  |

| 0x78          | AGC_OBS                      | Not used     | 'x', n10n8 | n7n4 | n3n0 |  |

| 0x79          | DBIST_STS                    | Not used     | 'x', n10n8 | n7n4 | n3n0 |  |

| 0x7A0x7E      | Internal Configuration       | Read as 'X'  |            |      |      |  |

| 0x7F          | External SM for checking CRC | Not used     | 'x', n10n8 | n7n4 | n3n0 |  |

## 3.2 Register Descriptions

## 3.2.1. FTP (Non-Volatile) and SRB (Volatile)

Table 7. System Configuration 1: Address 0x00 FTP; 0x40 SRB

|       | ss FTP<br>RB | Bits    | Function                                                                                                                                                                                                                                                                                                                                                                          | Acc<br>FTP |    | Reset<br>SRB | Default<br>FTP |

|-------|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--------------|----------------|

| 0x00  | 0x40         | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                                                                                                                             | NA         | NA | NA           | NA             |

|       |              | [11]    | ded_par: Parity bit for double bit error detection                                                                                                                                                                                                                                                                                                                                | NA         | NA | NA           | NA             |

|       |              | [10]    | <ul> <li>ana_prgm_dis: Disables programming over output pins and enables faster start-up.</li> <li>0b0: programming through analog enabled; start-up time 5ms</li> <li>0b1: programming through analog disabled; start-up time 3ms</li> </ul>                                                                                                                                     | RW         | RO | 0            | 0              |

|       |              | [9]     | <ul> <li>afe_agc_dis: Disables the automatic gain control.</li> <li>0b0: AGC enabled</li> <li>0b1: AGC disabled</li> <li>Note: If the AGC is enabled, afe_gain_code [6:0] in Table 9 is used as start value for the AGC during power-up.</li> </ul>                                                                                                                               |            |    | 0            | 0              |

|       |              |         | <ul> <li>intr_volatile_mode: Enables dynamic interrupt signaling. If this mode is enabled, an interrupt is cleared automatically if the error disappears after a debounce time of up to 5ms.</li> <li>0b0: disable, IRQN cleared by uC host</li> <li>0b1: enable, IRQN event type</li> </ul>                                                                                      |            |    | 1            | 1              |

|       |              | [7:4]   | i2c_slave_sub_addr: Programmable most significant nibble (MSN) of the I2C Slave Address. Refer to section 2.3 for details.                                                                                                                                                                                                                                                        |            |    | 0x2          | 0x2            |

|       |              | [3:2]   | back_end_irqn_ena: Enable Interrupt signaling at back-end interface.  2'b00: interrupt signaling @ SinP/CosP/SinN/CosN OFF  2'b01: interrupt signaling @ SinP/CosP ON; SinN/CosN OFF  2'b10: interrupt signaling @ SinP/CosP OFF; SinN/CosN ON  2'b11: interrupt signaling @ SinP/CosP / SinN/CosN ON  Note: Critical alarm flags will always put the outputs in diagnostic mode. |            |    | 0x3          | 0x0            |

|       |              | [1]     | <ul> <li>back_end_protocol: Configuration option to switch from Differential Ouptut into Single Ended mode.</li> <li>0b0: analog differntial: SINP, SINN, COSP; COSN</li> <li>0b1: analog single ended: SINP, REF, COSP, REF</li> </ul>                                                                                                                                           |            |    | 0            | 0              |

| Table | S. Carata    | [0]     | system_protocol: Configures Pin1 as Interrupt or address pin.  0b0: Interrupt: I2C Slave Address: MSN & 3'b000  0b1: Address Pin: I2C Slave Address: MSN[3:1] and PIN1 and 3'b000 Consider reserved address groups (0000XXX and 1111XXX)                                                                                                                                          |            |    | 1            | 1              |

Table 8. System Configuration 2: Address 0x01 FTP; 0x41 SRB

| Addres<br>SR |      | Bits    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Acc<br>FTP | ess<br>SRB | Reset<br>SRB | Default<br>FTP |

|--------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|----------------|

| 0x01         | 0x41 | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NA         | NA         | NA           | NA             |

|              |      | [11]    | ded_par: Parity bit for double bit error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NA         | NA         | NA           | NA             |

|              |      | [10]    | thermal_shutdown_en: Enable automatic shutdown of the transmitter (Stop excitation emitter current = 8'h00) in case the temperature exceeds the TovT_ERR (over-temperature error) threshold defined in the IP2550 Datasheet document  Note: The output buffers are switched off automatically to reduce the power consumption after exceeding the TovT_WARN (temperature warning) threshold defined in the IP2550 Datasheet document.  Ob0: disable automatic shutdown  Ob1: enable shutdown                                                                                                                                                                                                                                                                                                                      | RW         | RO         | 0            | 0              |

|              |      | [9:8]   | rc_amp_swap_time: Configures the RX amplifier swapping time if RX swapping is enabled in sysconf2[7:6]:  • 0b11: (For FuSa)  • 0b00: 10μs  • 0b10: 100μs  • 0b10: 100μs  • 0b11: 200μs  Consider system sampling time and noise requirements when selecting swap time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |            | 0x0          | 0              |

|              |      | [7:6]   | rc_swap: Configuration bits to activate static or dynamic swapping of the RX amplifier (for FuSa)  • 0b00: off  • 0b01: R1/2 swap static  • 0b10: R1/2 swap static  • 0b11: R1/2 swap toggle  If swapped, amplifier 2 is swapped into channel 1 and vice versa. Amplifier 2 errors are identified on channel1 output. For swap toggle, the setting is exchanged periodically, and error on one amplifier is visible as a ripple on the output signals.  If "swap toggle" is activated: higher noise must be expected. The internal offset compensation can be used to minimize the output ripple caused by residual offsets. In this situation, the internal offset compensation for R1 and R2 cannot be used to compensate for coil offsets any more and must be compensated by the application microcontroller. |            |            | 0x0          | 0x0            |

|              |      | [5]     | rc_switch: Switch between interleaved or straight receiver pin configurations.  obo: interleaved connections, IPS2550 default (FuSa)  obo1: straight connection, IPS2200 compliant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |            | 0            | 0              |

|              |      | [4:3]   | cyber_security: Configures the I2C access mode.  • 0b00: I2C read/write access  • 0b01: I2C read only access  • 0b10: no read/write access  • 0b11: I2C read / write access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |            | 0x0          | 0x0            |

|              |      | [2]     | <ul> <li>prot_integ_check_dis: Deactivates the I2C integrity check.</li> <li>0b0: integrity check 'On'</li> <li>0b1: integrity check 'Off'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |            | 0            | 0              |

|              |      | [1]     | <ul> <li>agc_mode: Configures the output voltage target for the AGC in 5V mode. In 3V3 supply mode it is 0.9V.</li> <li>0b0 – Programming option1: 1.8Vpp mode (for 5V and 3V3 supply)</li> <li>0b1 – Programming option2: 3.0Vpp mode (for 5V mode only)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |            | 0            | 0              |

| Address FTP<br>SRB |  | Bits | Function                                                                                                                        | Acc<br>FTP | Reset<br>SRB | Default<br>FTP |

|--------------------|--|------|---------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------|

|                    |  | [0]  | <ul> <li>vdda_3v_5v: Configuration bit for the supply voltage range.</li> <li>0b0: 3.3V mode</li> <li>0b1: 5.0V mode</li> </ul> |            | 1            | 1              |

## Table 9. R1/R2 gain: Address 0x02 FTP; 0x42 SRB

| Add<br>FTP | ress<br>SRB | Bits    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                    | Acc<br>FTP |    | Reset<br>SRB | Default<br>FTP |

|------------|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--------------|----------------|

| 0x02       | 0x42        | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                                                                                                                                                                                       | NA         | NA | NA           | NA             |

|            |             | [11]    | ded_par: Parity bit for double bit error detection                                                                                                                                                                                                                                                                                                                                                                                          | NA         | NA | NA           | NA             |

|            |             | [10]    | agc_plause_chk_en: Enable AGC plausibility check. Behaviour defined by register agc_plause_cfg. If enabled, AGC stops gain code update when out of plausibility range. If the plausibility check is enabled, the threshold limits in register "AGC Plausibility Configuration: Address 0x0F FTP; 0x4F SRB" must be configured correctly. The upper threshold must be configured obove the lower threshold.  • 0b1: enabled  • 0b0: disabled | RW         | RW | 0            | 0              |

|            |             | [9:8]   | agc_wait_tmr_sel: AGC timer selection when changing the gain in opposite direction: Used for selecting the wait time after the AGC direction changes.  • 2'b00: 30ms  • 2'b10: 300ms  • 2'b11: 10μs                                                                                                                                                                                                                                         |            |    | 0            | 0x3            |

|            |             | [7]     | d2a_afe_boost_sel: Overall gain multiplication by factor of 2  • 0b1: enabled , Gain factor 2x  • 0b0: disabled , Gain factor 1x                                                                                                                                                                                                                                                                                                            |            |    | 0            | 0              |

| Address<br>FTP SRB | Bits  |             |                |             | Fund           | ction       |                |             |                | Acc<br>FTP | Reset<br>SRB | Default<br>FTP |

|--------------------|-------|-------------|----------------|-------------|----------------|-------------|----------------|-------------|----------------|------------|--------------|----------------|

|                    | [6:0] | afe_gain_   | code: Ov       | eral gain o | configurati    | on for rec  | eiver 1 an     | d 2.        |                |            | 0x0          | 0x0            |

|                    |       | Code in hex | Gain<br>Factor |            |              |                |

|                    |       | 0x0         | 2.00           | 0x18        | 5.66           | 0x30        | 16.00          | 0x48        | 45.25          |            |              |                |

|                    |       | 0x1         | 2.10           | 0x19        | 5.94           | 0x31        | 16.80          | 0x49        | 47.51          |            |              |                |

|                    |       | 0x2         | 2.18           | 0x1A        | 6.17           | 0x32        | 17.45          | 0x4A        | 49.36          |            |              |                |

|                    |       | 0x3         | 2.29           | 0x1B        | 6.48           | 0x33        | 18.32          | 0x4B        | 51.83          |            |              |                |

|                    |       | 0x4         | 2.38           | 0x1C        | 6.73           | 0x34        | 19.02          | 0x4C        | 53.82          |            |              |                |

|                    |       | 0x5         | 2.50           | 0x1D        | 7.06           | 0x35        | 19.98          | 0x4D        | 56.52          |            |              |                |

|                    |       | 0x6         | 2.59           | 0x1E        | 7.34           | 0x36        | 20.75          | 0x4E        | 58.69          |            |              |                |

|                    |       | 0x7         | 2.72           | 0x1F        | 7.70           | 0x37        | 21.79          | 0x4F        | 61.62          |            |              |                |

|                    |       | 0x8         | 2.83           | 0x20        | 8.00           | 0x38        | 22.62          | 0x50        | 64.00          |            |              |                |

|                    |       | 0x9         | 2.97           | 0x21        | 8.40           | 0x39        | 23.76          | 0x51        | 67.20          |            |              |                |

|                    |       | 0xA         | 3.09           | 0x22        | 8.72           | 0x3A        | 24.68          | 0x52        | 69.79          |            |              |                |

|                    |       | 0xB         | 3.24           | 0x23        | 9.16           | 0x3B        | 25.91          | 0x53        | 73.28          |            |              |                |

|                    |       | 0xC         | 3.36           | 0x24        | 9.51           | 0x3C        | 26.91          | 0x54        | 76.10          |            |              |                |

|                    |       | 0xD         | 3.53           | 0x25        | 9.99           | 0x3D        | 28.26          | 0x55        | 79.90          |            |              |                |

|                    |       | 0xE         | 3.67           | 0x26        | 10.38          | 0x3E        | 29.34          | 0x56        | 83.01          |            |              |                |

|                    |       | 0xF         | 3.85           | 0x27        | 10.89          | 0x3F        | 30.81          | 0x57        | 87.16          |            |              |                |

|                    |       | 0x10        | 4.00           | 0x28        | 11.31          | 0x40        | 32.00          | 0x58        | 90.50          |            |              |                |

|                    |       | 0x11        | 4.20           | 0x29        | 11.88          | 0x41        | 33.60          | 0x59        | 95.02          |            |              |                |

|                    |       | 0x12        | 4.36           | 0x2A        | 12.34          | 0x42        | 34.90          | 0x5A        | 98.72          |            |              |                |

|                    |       | 0x13        | 4.58           | 0x2B        | 12.96          | 0x43        | 36.64          | 0x5B        | 103.66         |            |              |                |

|                    |       | 0x14        | 4.76           | 0x2C        | 13.46          | 0x44        | 38.05          | 0x5C        | 107.65         |            |              |                |

|                    |       | 0x15        | 4.99           | 0x2D        | 14.13          | 0x45        | 39.95          | 0x5D        | 113.03         |            |              |                |

|                    |       | 0x16        | 5.19           | 0x2E        | 14.67          | 0x46        | 41.50          | 0x5E        | 117.38         |            |              |                |

|                    |       | 0x17        | 5.45           | 0x2F        | 15.41          | 0x47        | 43.58          | 0x5F        | 123.24         |            |              |                |

|                    |       |             |                |             |                |             |                |             |                |            |              |                |

Table 10. R1 Fine Gain Compensation: Address 0x03 FTP; 0x43 SRB

|      | ss FTP<br>RB | Bits    | Function                                                                                                                                                                                                                                                                         | Access<br>FTP SRB |    | Reset<br>SRB | Default<br>FTP |

|------|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|--------------|----------------|

| 0x03 | 0x43         | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                            | NA                | NA | NA           | NA             |

|      |              | [11]    | ded_par: Parity bit for double bit error detection                                                                                                                                                                                                                               | NA                | NA | NA           | NA             |

|      |              | [10:7]  | RFU: Read as X                                                                                                                                                                                                                                                                   | RW                | RO | 0x0          | 0x0            |

|      |              | [6:0]   | afe_r1_gain_cal: Used for increasing the amplitude of receiver 1 to compensate amplitude mismatch caused by not ideal coils. Overall range is 16% with 0.125% step size.  • 0x00: no correction  • 0x01: 0.125%  • 0x02: 0.250%  • 0x03: 0.375%  •  • 0x7E: 15.875%  • 0x7F: 16% |                   | RW | 0x00         | 0x00           |

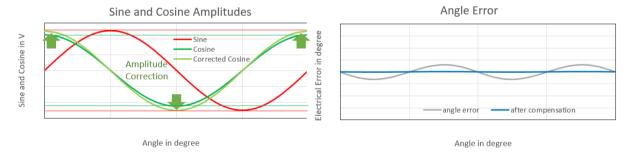

The output signals can have amplitude mismatch resulting from production tolerances or a non-ideal coil structure. Such amplitude mismatch leads to increased angle non-linearity that is calculated from sine and cosine signals. Therefore, the application microcontroller usually calculates and eliminate the amplitude mismatch before angle calculation. IPS2550 is able to eliminate such amplitude mismatch already within the sensor IC as shown in Figure 16. The left picture shows amplitude mismatch on the cosine channel causing angle error, the right picture shows the error and the improved signal after compensation.

Figure 16. Compensated and Uncompensated Amplitude Mismatch

Table 11. R1 Offset Compensation: Address 0x04 FTP; 0x44 SRB

|      | ss FTP<br>RB                                                                                                                                                                                         | Bits    | Function                                                                                                                                                                                                                                                                                                                                                 | Acc<br>FTP |    | Reset<br>SRB | Default<br>FTP |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--------------|----------------|

| 0x04 | 0x44                                                                                                                                                                                                 | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                                                                                                    | NA         | NA | NA           | NA             |

|      |                                                                                                                                                                                                      | [11]    | ded_par: Parity bit for double bit error detection                                                                                                                                                                                                                                                                                                       | NA         | NA | NA           | NA             |

|      |                                                                                                                                                                                                      | [10]    | dis_fsm_output_err: Use for disabling the FSM output error interrupt signalizing.  • 0b0: signalizing enabled  • 0b1: signalizing disabled                                                                                                                                                                                                               | RW         | RW | 0            | 0              |

|      |                                                                                                                                                                                                      | [9]     |                                                                                                                                                                                                                                                                                                                                                          |            | 0  | 0            |                |

|      | [8] dis_r12_short_fail: Disable diagnostic alarm at R1/2 short fail.  • 1'b0: enabled, R1/2 short fail triggers diagnostic state  • 1'b1: disabled, R1/2 short fail doesn't trigger diagnostic state |         | 1'b0: enabled, R1/2 short fail triggers diagnostic state                                                                                                                                                                                                                                                                                                 |            |    | 0            | 0              |

|      |                                                                                                                                                                                                      | [7]     | <ul> <li>afe_r1_offset_cal: Define the offset compensation polarity.</li> <li>0b0: addition</li> <li>0b1: subtraction</li> </ul>                                                                                                                                                                                                                         |            |    | 0            | 0              |

|      |                                                                                                                                                                                                      | [6:0]   | afe_r1_offset_cal: R1 Offset compensation relative to the LC oscillator amplitude. Used for reducing the signal offset caused by non-ideal coils. Overall range is 0.2% relative to the LC oscillator amplitude, the step size is 0.0015%.  • 0x00: no correction  • 0x01: 0.0015%  • 0x02: 0.0030%  • 0x03: 0.0045%  •  • 0x7E: 0.189%  • 0x7F: 0.1905% |            |    | 0x00         | 0x00           |

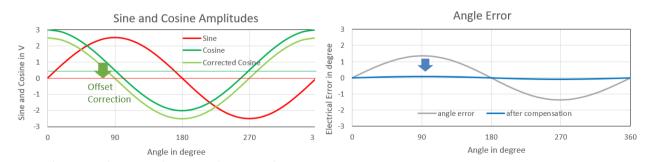

The output signals can have offset resulting from production tolerances or a non-ideal coil structure. Such offset leads to increased angle non-linearity that is calculated from the sine and cosine signals. Therefore, the application microcontroller usually calculates and eliminate signal offset before angle calculation. IPS2550 is able to eliminate such offset already within the sensor IC as shown in Figure 17. The left picture shows signal offset on the cosine channel causing angle error, the right picture shows the error and the improved signal after compensation.

Figure 17. Compensated and Uncompensated Signal Offset

Table 12. R2 Fine Gain Compensation: Address 0x05 FTP; 0x45 SRB

|      | ss FTP<br>RB | Bits    | Function                                                                                                                                                                                                                                                                      | Acc<br>FTP |    | Reset<br>SRB | Default<br>FTP |

|------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--------------|----------------|

| 0x05 | 0x45         | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                         | NA         | NA | NA           | NA             |

|      |              | [11]    | ded_par: Parity bit for double bit error detection                                                                                                                                                                                                                            | NA         | NA | NA           | NA             |

|      |              | [10:7]  | RFU: Read as X                                                                                                                                                                                                                                                                | RW         | RO | 0x0          | 0x0            |

|      |              | [6:0]   | afe_r2_gain_cal: Used for increasing the amplitude of receiver 1 to compensate amplitude mismatch caused by non-ideal coils. Overall range is 16%, one step is 0.125%  • 0x00: no correction  • 0x01: 0.125%  • 0x02: 0.250%  • 0x03: 0.375%  •  • 0x7E: 15.875%  • 0x7F: 16% |            | RW | 0x00         | 0x0            |

Table 13. R2 Offset Compensation: Address 0x06 FTP; 0x46 SRB

|      | ss FTP<br>RB                                                                                                                  | Bits    | Function                                                                                                                                                                                                                                                                                                     |    | ess<br>SRB | Reset<br>SRB | Default<br>FTP |

|------|-------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|--------------|----------------|

| 0x06 | 0x46                                                                                                                          | [15:12] | Ecc: Parity word for error correction                                                                                                                                                                                                                                                                        | NA | NA         | NA           | NA             |