# Operation of the HC5503EVAL Evaluation Board

Application Note July 1997 AN9736.1

## Features

- · Includes the Ringing Relay

- Toggle Switch Programming for Logic States

- Monitoring of Switch Hook Detect (SHD) via On Board LED's

- Includes On-Board Op Amp for Evaluation of Transhybrid Balance

- Logic Terminal Port for Easy Evaluation in Existing Systems

## Functional Description

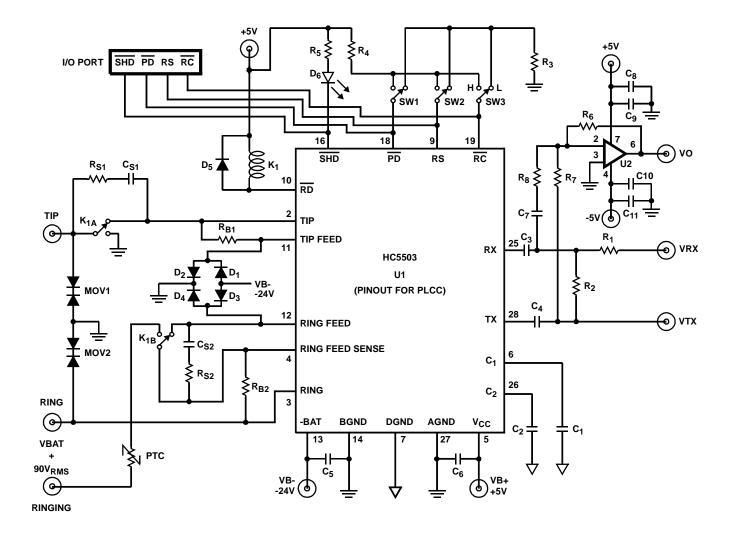

The HC5503 **S**ubscriber Line Interface **C**ircuit (SLIC) evaluation board has provisions for: Full evaluation of the voice and DC feeding characteristics, ring injected single ended ringing, and transhybrid balance. Functional control of the SLIC is provided using the toggle switches RS,  $\overline{RC}$  and  $\overline{PD}$ . See Table 7 for the logic states.

The HC5503 evaluation board is configured to match a  $600\Omega$  line impedance. Resistors  $R_{B1}$  and  $R_{B2}$  account for  $300\Omega$  and the remaining  $300\Omega$  is synthesized via feedback through resistor  $R_2$ . Reference the HC5503 data sheet for more details about impedance matching.

## Power Requirements for the HC5503

#### **Power Supply Connections**

The HC5503 requires three external power supplies for a complete evaluation of the application. The SLIC is powered by two supplies  $V_{BAT} = -24V$  and  $V_{CC} = +5V$  and the third supply ( $V_{EE} = -5V$ ) powers an external op-amp (U2) for the transhybrid balance circuit. This op-amp is usually contained in the CODEC.

## **Ground Connections**

The HC5503 board has tied the analog, digital and battery grounds to a common ground plane designated GND. It is recommended that the analog, digital and battery grounds of the SLIC be tied together as close to the device pins as possible. The three external power supplies should each be grounded to the evaluation board.

## **HC5503 Board SLIC Controls**

The design of the HC5503 board incorporates three SPDT center off switches. The three SPDT switches (RS,  $\overline{RC}$ ,  $\overline{PD}$ ) control the functional state of the SLIC. If off-board mode control of the SLIC is desired, the three SPDT switches can be set to center open position and driven by logic at the logic terminal port. The logic terminal port is located in the upper left hand corner of the board.

#### **Mode Control Switches**

Toggling RS, RC or PD towards the top of the board (Intersil logo to bottom left) results in a logic "1" state on the pin; and toggling them towards the bottom results in a logic "0" state on the pin.

A common ground must exist between the HC5503 evaluation board and the off board logic. A differential ground voltage may result in erroneous logic states at the SLIC inputs.

## **Getting Started**

Verify that the sample HC5503 included with the evaluation board is oriented in its socket correctly. Correct orientation is with pin 1 pointing towards the onboard pin 1 designator located to the left of the socket (reference the data sheet for location of device pin 1).

## Verifying the HC5503 Operation

The operation of the HC5503 and the sample part can be verified by performing six tests:

- 1. Power Supply Current Verification.

- 2. Normal Loop Feed Mode Verification.

- 3. Tip and Ring Voltage Verification.

- 4. Gain Verification (4-wire to 2-wire).

- Ring Trip Detector Verification.

- 6. Transhybrid Balance Verification.

The above 6 tests require the following equipment: a  $600\Omega$  load, an AC volt meter, three external supplies (one each for  $V_{CC}$ ,  $V_{EE}$ , and  $V_{BAT}$ ), an oscilloscope, a telephone and a battery backed AC source.

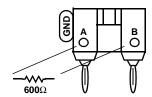

Application Tip: When terminating tip and ring, it is handy to assemble terminators using a Pomona MDP dual banana plug connector as the terminating resistor receptacle. Refer to Figure 1 for details.

FIGURE 1. TERMINATION ADAPTER

Using the termination shown in Figure 1 provides an unobtrusive technique for terminating tip and ring while still providing access to both signals using the banana jack feature of the MDP connector. Posts are also available that fit into holes A and B, providing a solderable connection for the terminating resistor.

## **Test #1 Power Supply Current Verification**

A quick check of evaluation board and the HC5503 sample is to measure the supply currents. The readings should be similar to the values listed in Table 1. The measurements can be made using a series ammeter on each supply, or power supplies with current displays.

#### **Normal Loop Feed**

#### Discussion:

The currents measured include those of the SLIC and supporting circuitry. For SLIC supply currents consult the HC5503 data sheet.

## Setup:

- 1. Connect the power supplies to the HC5503.

- 2. Set the mode switches for "Normal Loop Feed" mode: RS = 1,  $\overline{RC} = 1$ ,  $\overline{PD} = 1$ .

- 3. Terminate HC5503 SLIC with a  $600\Omega$  load.

- Measure the supply currents and compare to those in Table 1.

### **Power Denial**

#### Discussion:

Power denial limits power to the subscriber loop: it does not power down the SLIC, i.e., the SLIC will still consume its normal on-hook quiescent power during a power denial period. This function is intended to "isolate" from the battery, under processor control, selected subscriber loops during an overload or similar fault status.

If power denial is selected, the logic circuitry switches in a current source to charge up the external capacitor  $C_3$ . As  $C_3$  charges up, the ring voltage approaches the tip voltage. Since tip is always biased at -4V, the battery feed across the loop is essentially zero, and minimum loop power will be dissipated if the circuit goes off-hook. No signalling functions are available during this mode.

#### Setup:

- Set the mode switches for "Power Denial" mode: RS = 1, RC = 0/1. PD = 0.

- 2. Terminate HC5503 SLIC with a  $600\Omega$  load.

- Measure the supply currents and compare to those in Table 1.

TABLE 1.

| SUPPLY                  | R <sub>L</sub><br>(Ω) | MODE             | HC5503<br>TYP (mA) |

|-------------------------|-----------------------|------------------|--------------------|

| V <sub>CC</sub> = +5V   | 600                   | Normal Loop Feed | 7.2                |

| V <sub>EE</sub> = -5V   | 600                   | Normal Loop Feed | 0.74               |

| V <sub>BAT</sub> = -24V | 600                   | Normal Loop Feed | 20.7               |

| V <sub>BAT</sub> = -24V | 600                   | Power Denial     | 1.0                |

#### Test # 2 Normal Loop Feed Mode Verification

This test verifies loop current operation and loop current detection in the Normal Loop feed mode via the on-board LED.

#### Discussion:

When power is applied to the SLIC a loop current will flow from tip to ring through the  $600\Omega$  load. Loop current detection occurs when this loop current triggers an internal detector that pulls the output of  $\overline{\text{SHD}}$  low, illuminating the LED through the +5V supply. Once the LED illuminates, remove the  $600\Omega$  termination and verify that the LED turns off.

#### Setup

- 1. Connect the power supplies to the HC5503.

- 2. Set V<sub>BAT</sub> to -24V.

- 3. Terminate the HC5503 with  $600\Omega$  load across Tip and Ring.

- 4. Set the mode switches for "Normal Loop Feed" mode: RS = 1.  $\overline{RC}$  = 1.  $\overline{PD}$  = 1.

#### Verification:

- 1. The  $\overline{\text{SHD}}$  LED is on when tip and ring are terminated with  $600\Omega$ .

- 2. The SHD LED is off when tip and ring are open circuit.

#### Test # 3 Tip and Ring Voltage Verification

This test verifies the tip and ring voltages for both the Normal Feed and Power Denial Modes.

#### Setup:

- 1. Connect the power supplies to the HC5503.

- 2. Set V<sub>BAT</sub> to -24V.

- 3. Disconnect the  $600\Omega$  load across Tip and Ring.

- 4. Set the mode switches for "Normal Loop Feed" mode: RS = 1,  $\overline{RC} = 1$ ,  $\overline{PD} = 1$ .

- Measure tip and ring voltages with respect to ground and compare to those in Table 2.

- Repeat the above test with the SLIC in the Power Denial Mode: RS = 1, RC = 0/1, PD = 0 and compare to those in Table 2.

TABLE 2.

| MODE             | PART                      | TIP<br>TYP (V) | RING<br>TYP (V) |

|------------------|---------------------------|----------------|-----------------|

| Normal Loop Feed | $(V_{BAT} = -24V)$        | -3.2           | -21.0           |

| Power Denial     | (V <sub>BAT</sub> = -24V) | -3.2           | -3.0            |

## Test #4 Gain Verification (4-Wire to 2-Wire)

This test will verify that HC5503 SLIC is operating properly and that the 4-wire to 2-wire gain is about 0.615 or -4.0dB.

#### Discussion:

When terminated with  $600\Omega$  load, the SLIC will exhibit about a -4.0dB gain from the  $V_{RX}$  input pin to across tip and ring (V\_TR). When an open circuit exists, a mismatch occurs and the gain of the SLIC goes to about 0.869 or +2.0dB. Reference the HC5503 data sheet for more information concerning the feedback network for impedance matching. The dB gain is calculated in Equation 1.

$$dB = 20 \times log \frac{V_{TR}}{V_{RX}}$$

(EQ. 1)

## Setup:

- 1. Connect the power supplies to the HC5503.

- 2. Set the mode switches for "Normal Loop Feed" mode: RS = 1,  $\overline{RC} = 1$ ,  $\overline{PD} = 1$ .

- 3. Terminate HC5503 SLIC with a  $600\Omega$  load.

- 4. Connect a sine wave generator to the V<sub>RX</sub> input.

- Set the generator for 1V<sub>RMS</sub> and 1kHz.

- 6. Connect an AC voltmeter across tip and ring.

#### Verification:

- 1. Tip to ring AC voltage of 0.64V<sub>RMS</sub> when terminated.

- 2. Tip to ring AC voltage of 1.27V<sub>RMS</sub> when not terminated.

## **Test #5 Ring Trip Detector Verification**

This test will verify the ringing function of the SLIC. A telephone and an AC signal source are the only additional hardware required to complete the test.

#### Discussion:

The  $600\Omega$  termination is not necessary for this test since the phone provides this nominal impedance when off-hook. Setting the mode switches as shown below will cause the relay driver pin  $(\overline{RD})$  of the SLIC to energize the relay that is on the evaluation board.

#### Setup:

- 1. Connect the power supplies to the HC5503.

- 2. Set the mode switches for "RD active (Ringing)" mode: RS = 1, RC = 0, PD = 1.

- 3. Connect the telephone across tip and ring.

- Connect battery backed AC (20Hz oscillator) to GENHI (V<sub>BAT</sub> + 90V<sub>RMS</sub>) banana jack.

#### Verification:

- 1. Phone starts ringing when power applied to test setup.

- 2. While ringing and on-hook, SHD LED is not illuminated.

- While ringing, going off-hook will illuminate the SHD LED.

CAUTION: Short time durations of off-hook should be maintained to protect the feed resistors. In systems, the ring relay is software controlled to turn off milliseconds after off-hook is detected, hence limiting power dissipated

- 4. When phone is returned to on-hook, SHD LED will turn off.

- 5. Configure SLIC in Normal Loop Feed mode to stop phone from ringing. Set mode switches to RS = 1, RC = 1, PD = 1.

### **Test #6 Transhybrid Balance Verification**

in the feed resistors.

This test will verify the transhybrid balance circuitry. A low distortion AC signal source and a volt meter are the only additional hardware required to complete this test.

#### Discussion:

Transhybrid balance is a measure of how well the input signal is canceled (that being received by the SLIC) from the transmit signal (that being transmitted from the SLIC). Without this function, voice communication would be difficult because of the echo.

#### Setup:

- 1. Connect the power supplies to the HC5503.

- 2. Set the mode switches for "Normal Loop Feed" mode: RS = 1, RC = 1, PD = 1.

- 3. Terminate HC5503 SLIC with a  $600\Omega$  load.

- 4. Set the AC source to  $1V_{RMS}$ , 1kHz and apply to the VRX input.

- 5. Connect an AC voltmeter between the VO and GND.

#### Verification:

- 1. Measure the AC voltage at VO output.

- 2. Calculate the Transhybrid balance using Equation 2

Transhybrid =

$$20 \times log \frac{VO}{1V_{RMS}}$$

(EQ. 2)

3. The value should be around -37.8dB.

## **Functional Circuit COMPONENT Descriptions**

A brief description of each component is provided below. The components will be grouped by function to provide further insight into the operation of the HC5503 board.

#### TABLE 3. TWO WIRE SIDE, TIP AND RING

| R <sub>B1</sub> , R <sub>B2</sub>                                                    | Feed resistors that limit the current into the tip and ring inputs and are used for loop current detection.                                                                                                         |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| К <sub>1</sub>                                                                       | Relay used to switch between normal loop feed operation and battery backed ring injected ringing.                                                                                                                   |

| RD                                                                                   | Relay Driver output. The $\overline{\text{RD}}$ pin is an open collector output that is used to control the ring relay (K <sub>1</sub> ).                                                                           |

| R <sub>S1</sub> , C <sub>S1</sub> ,<br>R <sub>S2</sub> , C <sub>S2</sub>             | RC snubber network placed across the ring relay contacts to minimize inductive kickback effects from the telephone ringer.                                                                                          |

| D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> ,<br>D <sub>4</sub> , MOV1,<br>MOV2 | Secondary surge protection.                                                                                                                                                                                         |

| PTC                                                                                  | Provisions for a positive temperature coefficient (PTC) resistor. The PTC provides short circuit protection during ringing. The value of the PTC is application specific and therefore not provided with the board. |

#### **TABLE 4. TRANSHYBRID CIRCUIT**

| C <sub>7</sub> , U <sub>2</sub> | Transhybrid balance circuit cancels the input signal (that being received by the SLIC) from the transmit signal (that being transmitted from the SLIC). $C_7$ couples the output of the SLIC to the transhybrid op-amp. It also provides the proper phase shift to account for $C_4$ 's phase shift. |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### **TABLE 5. FILTER CAPACITORS**

| C <sub>1</sub> , C <sub>2</sub> | $C_1$ is required for proper operation of the loop                                           |

|---------------------------------|----------------------------------------------------------------------------------------------|

|                                 | current limit function.                                                                      |

|                                 | C <sub>2</sub> Filters out the AC to avoid false ring trip detection when ringing the phone. |

|                                 | detection when ringing the phone.                                                            |

|                                 |                                                                                              |

#### **TABLE 6. AC DECOUPLING CAPACITORS**

| C <sub>3</sub> , C <sub>4</sub> | AC decoupling capacitors |

|---------------------------------|--------------------------|

|---------------------------------|--------------------------|

#### TABLE 7. LOGIC CURRENT LIMITING RESISTORS

| R <sub>3</sub> , R <sub>4</sub> | $\ensuremath{R}_3$ is the logic low current limiting resistor. $\ensuremath{R}_4$ is the logic high current limiting resistor. |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

#### **TABLE 8. SUPPLY DECOUPLING CAPACITORS**

| C <sub>5</sub> , C <sub>6</sub> , C <sub>8-11</sub> | Supply decoupling capacitors. |

|-----------------------------------------------------|-------------------------------|

|-----------------------------------------------------|-------------------------------|

#### TABLE 9. FEEDBACK RESISTORS

| 11. 4 | Feedback resistors for synthesizing the AC 2-wire impedance. |

|-------|--------------------------------------------------------------|

|       |                                                              |

## TABLE 10. SHD LED

| R <sub>5</sub> , D <sub>6</sub> | $R_5$ is the Current limiting resistors for the $\overline{SHD}$ , LED |

|---------------------------------|------------------------------------------------------------------------|

|                                 | (D <sub>6</sub> ).                                                     |

## **TABLE 11. SPDT TOGGLE SWITCH**

| SW1, SW2, | SPDT center open switches. Controls logic input |

|-----------|-------------------------------------------------|

|           | RS, RC, PD.                                     |

## **TABLE 12. LOGIC TERMINAL PORT**

|  | This port allows external processor control of the 3 logic inputs (RS, $\overline{RC}$ , PD) and the logic output (SHD). SW1, SW2, SW3 need to be in the center open position for proper operation. |

|--|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# **Application Note 9736**

# **HC5503 SLIC Operating Modes**

TABLE 13.

|    |    |    |                     | DETECTOR<br>(VALID) |  |

|----|----|----|---------------------|---------------------|--|

| RS | RC | PD | MODE                | SHD                 |  |

| 1  | 0  | 0  | Power Denial        |                     |  |

| 1  | 0  | 1  | RD Active (Ringing) | ✓                   |  |

| 1  | 1  | 0  | Power Denial        |                     |  |

| 1  | 1  | 1  | Normal Loop Feed    | ✓                   |  |

RS is the ring synchronization input. RS is used to activate and deactivate the ring relay  $(K_1)$  when the instantaneous ring voltage is near zero. If synchronization is not required the pin should be tied to +5V.

## **HC5503 Evaluation Board Parts List**

| COMPONENT                                                        | VALUE  | TOLERANCE | RATING | COMPONENT                                                                          | VALUE                   | TOLERANCE | RATING   |

|------------------------------------------------------------------|--------|-----------|--------|------------------------------------------------------------------------------------|-------------------------|-----------|----------|

| SLIC                                                             | U1     | HC5503    |        | C <sub>5,</sub> C <sub>6</sub>                                                     | 0.01μF                  | 20%       | 100V     |

| R <sub>1,</sub> R <sub>4</sub>                                   | 10.0kΩ | 1%        | 1/4W   | C <sub>8,</sub> C <sub>11</sub>                                                    | 0.1μF                   | 20%       | 50V      |

| R <sub>2</sub>                                                   | 24.9kΩ | 1%        | 1/4W   | C <sub>9</sub> , C <sub>10</sub>                                                   | 0.01μF                  | 20%       | 50V      |

| R <sub>3</sub>                                                   | 1.0kΩ  | 5%        | 1/4W   | C <sub>S1</sub> , C <sub>S2</sub>                                                  | 0.1μF                   | 20%       | 100V     |

| R <sub>5</sub>                                                   | 510Ω   | 5%        | 1/4W   | D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> , D <sub>4</sub> , D <sub>5</sub> | 1N40007                 | n/a       | 100V, 1A |

| R <sub>7</sub>                                                   | 200kΩ  | 1%        | 1/4W   | D <sub>6</sub>                                                                     | LED, RED                | n/a       | n/a      |

| R <sub>6</sub> , R <sub>8</sub>                                  | 150kΩ  | 1%        | 1/4W   | PTC                                                                                | Shorted                 | n/a       | n/a      |

| R <sub>B1</sub> , R <sub>B2</sub>                                | 150Ω   | 1%        | 2W     | MOV1, MOV2                                                                         | Open                    | n/a       | n/a      |

| R <sub>S1</sub> , R <sub>S2</sub>                                | 1.0kΩ  | 1%        | 1/4W   | U2                                                                                 | CA741C Op-Amp           |           |          |

| C <sub>1</sub>                                                   | 0.33μF | 20%       | 50V    | RELAY (K1 <sub>A,B</sub> )                                                         | DS2E-M-<br>DC5V         | n/a       | n/a      |

| C <sub>2,</sub> C <sub>3</sub> , C <sub>4</sub> , C <sub>7</sub> | 0.47μF | 20%       | 50V    | SW1, SW2, SW3                                                                      | SPDT CO PC Mount Switch |           |          |

6

intersil

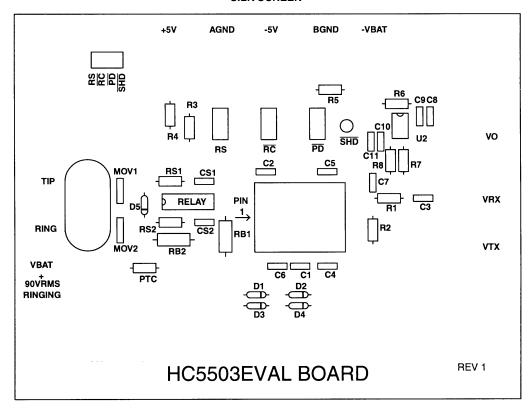

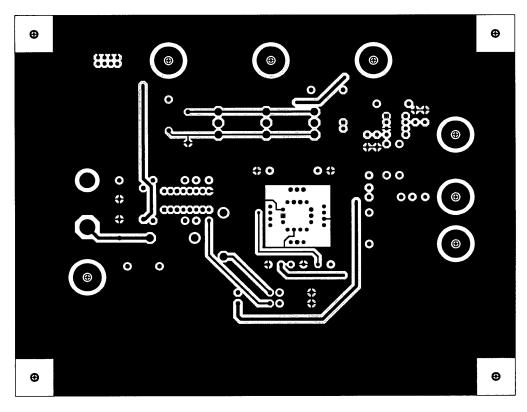

# HC5503 Evaluation Board Layout

**SILK SCREEN**

**TOP SIDE**

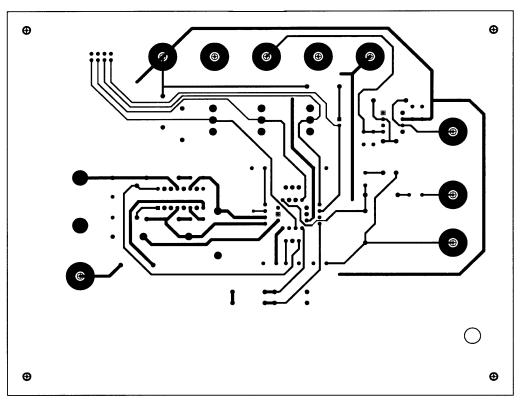

## HC5503 Evaluation Board Layout (Continued)

#### **BOTTOM SIDE**

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com