## E1/E20 Emulator, E2 Emulator

Additional Document for User's Manual (Notes on Connection of RH850/C1M-A)

Supported Devices:

RH850 Family

RH850/C1x Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

## **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

(Rev.5.0-1 October 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/.

## **Important**

Before using the emulator, be sure to read the emulator user's manual carefully.

Keep the user's manual, and refer to it when you have questions about the emulator.

## When using the emulator:

- (1) Renesas Electronics Corporation cannot predict all possible situations and possible cases of misuse that carry a potential for danger. Therefore, the warnings in this user's manual and the warning labels attached to the emulator do not necessarily cover all such possible situations and cases. The customer is responsible for correctly and safely using the emulator.

- (2) Renesas Electronics Corporation will not assume responsibility of direct or indirect damage caused by an accidental failure or malfunction in the emulator.

## About rights:

- (1) We assume no responsibility for any damage or infringement on patent rights or any other rights arising from the use of any information, products or circuits presented in this user's manual.

- (2) The information or data in this user's manual does not implicitly or otherwise grant a license to patent rights or any other rights belonging to Renesas or to a third party.

- (3) This user's manual and the emulator are copyrighted, with all rights reserved by Renesas. This user's manual may not be copied, duplicated or reproduced, in whole or part, without prior written consent from Renesas.

#### About diagrams:

Some diagrams in this user's manual may differ from the objects they represent.

## **Precautions for Safety**

This chapter, by showing the relevant diagrammatic symbols and their meanings, describes the precautions which should be taken in order to use this product safely and properly. Be sure to read and understand this chapter before using this product.

Contact us if you have any questions about the precautions described here.

**WARNING**

WARNING indicates a potentially dangerous situation that will cause death or heavy wound unless it is avoided.

**CAUTION**

CAUTION indicates a potentially dangerous situation that will cause a slight injury or a medium-degree injury or property damage unless it is avoided.

To avoid a possible danger, the following diagrammatic symbols are used to call your attention.

$\triangle$  means WARNING or CAUTION.

Example:

CAUTION AGAINST AN ELECTRIC SHOCK

Example:

DISASSEMBLY PROHIBITED

means A FORCIBLE ACTION.

Example:

UNPLUG THE POWER CABLE FROM THE RECEPTACLE.

## Warnings for AC Power Supply:

Do not repair or remodel the emulator product by yourself in order to prevent danger such as an electric shock or fire and for the sake of quality assurance. For after-sale services in case of a mechanical or electrical fault, please contact your local distributor.

Always switch off the Host machine and user system before connecting or disconnecting any cables or parts. Neglect of this precaution will result in getting an electric shock or will result in the emulator product or user system emitting smoke or catching fire. Also, the user program under debug will be destroyed.

Make sure that the connectors on both ends of the user interface cable are facing the right way relative to the user-side connector on the emulator and the connector on the user system, respectively.

Neglect of this precaution will result in getting an electric shock or will result in the emulator product or user system emitting smoke or catching fire.

## Warning for Modification:

Do not modify the emulator. Personal injury due to electric shock may occur if the emulator is modified. Modifying the product will void your warranty.

#### Warning for Installation:

Do not set the emulator in water or areas of high humidity. Make sure that the product does not get wet. Spilling water or some other liquid into the product may cause un-repairable damage.

## Warning for Use Temperature:

The emulator is to be used in an environment with a maximum ambient temperature of 35°C. Care should be taken that this temperature is not exceeded.

#### Caution to Be Taken for Handling the Emulator:

Exercise caution when handling the emulator. Be careful not to apply a mechanical shock.

Do not touch the connector pins of the emulator and the target MCU connector pins directly. Static electricity may damage the internal circuits.

When attaching and removing the cable, hold the plug of the cable and do not touch the cable. When installing the emulator, do not flex the cable excessively or pull the emulator or the board by the cable connected to it. The cable may cause a break.

Do not tape the flexible cable or apply adhesives to secure the cable. The shielding material on the surface of the cable may come off.

#### Caution to Be Taken for System Malfunctions:

If the emulator malfunctions because of interference like external noise, do the following to remedy the trouble.

- (1) Exit the emulator debugger, and shut OFF the emulator and the user system.

- (2) After a lapse of 10 seconds, turn ON the power of the emulator and the user system again, then launch the emulator debugger.

#### Caution to Be Taken for Disposal:

Penalties may be applicable for incorrect disposal of this waste, in accordance with your national legislation.

## European Union Regulatory Notices:

The WEEE (Waste Electrical and Electronic Equipment) regulations put responsibilities on producers for the collection and recycling or disposal of electrical and electronic waste. Return of WEEE under these regulations is applicable in the European Union only. This equipment (including all accessories) is not intended for household use. After use the equipment cannot be disposed of as household waste, and the WEEE must be treated, recycled and disposed of in an environmentally sound manner.

Renesas Electronics Europe GmbH can take back end of life equipment, register for this service at "http://www.renesas.eu/weee"

## **Table of Contents**

| 1.    | Outil   | ne                                                                                           | 1   |

|-------|---------|----------------------------------------------------------------------------------------------|-----|

| 1.1   | Featu   | ıres of an E1, E20, or E2 emulator                                                           | 1   |

| 1.2   | Cauti   | on on using the E20 emulator                                                                 | 1   |

| 1.3   | Confi   | guration of manuals                                                                          | 1   |

| 2. Co | nnec    | ting the Emulator and User System                                                            | 2   |

| 2.1   |         | ector mounted on the user system                                                             |     |

|       |         | ssignments of the connector                                                                  |     |

| 2.3   | Conn    | ection interface and modes                                                                   | 5   |

| 2.4   | Exam    | ples of recommended connections between the connector and MCU                                | 6   |

| 2.4   | .1      | Example of recommended connections for debugging (4-pin LPD or JTAG) and                     |     |

| pro   | gramr   | ming (2-wire UART or CSI)                                                                    |     |

| 2.4   | .2      | Example of recommended connections for only programming (2-wire UART)                        |     |

| 2.4   | .3      | Example of recommended connections for only programming (CSI)                                |     |

| 2.4   |         | Connecting the RESET pin                                                                     |     |

| 2.4   | .5      | Connecting the TVDD pin                                                                      |     |

| 2.4   |         | Hot plug-in connection                                                                       |     |

| 2.4   |         | Isolator for the E1 emulator                                                                 |     |

| 2.4   | .8      | Small connector conversion adapter for the E1 emulator                                       | .13 |

| 3. Sp | ecific  | ations                                                                                       | 14  |

| •     |         | view of specifications specific to the E2 emulator                                           |     |

| 3.1   | .1      | Software tracing (LPD output)                                                                | .19 |

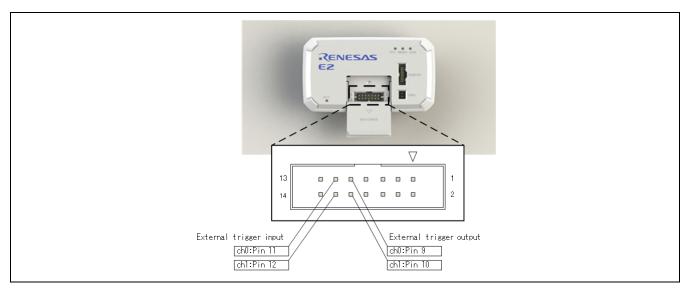

| 3.1   | .2      | External trigger input and output                                                            | .20 |

| 4 No  | tes o   | n Usage                                                                                      | 21  |

|       |         | on differences in operation between the actual device and the E1, E20, or E2 emulator        |     |

| 4.1   |         | DBTRAP instruction                                                                           |     |

| 4.1   |         | AUDR function                                                                                |     |

| 4.1   |         | Serial programming function                                                                  |     |

| 4.1   | .4      | HALT mode (skipped number)                                                                   |     |

| 4.1   | .5      | Current drawn                                                                                | .21 |

| 4.1   | .6      | Initialization of RAM areas                                                                  | .21 |

| 4.1   | .7      | OTP flag                                                                                     | .22 |

| 4.1   | .8      | Operation in response to resets and interrupts when an emulator is in use (skipped number) . | .22 |

| 4.1   | .9      | Option byte register                                                                         | .22 |

| 4.1   | .10     | Initially stopped state of CPU2 and the sub-CPU (when a debugger is connected or             |     |

| app   | olies a | reset)                                                                                       | .22 |

| 4.2   | Cauti   | onary notes on debugging                                                                     |     |

| 4.2   |         | Handling of devices which were used for debugging                                            |     |

| 4.2   |         | Power to the target system while debugging                                                   |     |

| 4.2   |         | Hardware break (access) function (the timing of a break occurring)                           |     |

| 4.2   |         | Hardware break (access) function (64-bit data comparison)                                    |     |

| 4.2   |         | Hardware break (access) function (EIINT table)                                               |     |

| 4.2   | -       | Debugging interface                                                                          |     |

| 4.2   |         | Initialization of RAM areas                                                                  |     |

| 4.2   |         | Reset of pins (skipped number)                                                               |     |

| 4.2   |         | Trace function                                                                               |     |

| 4.2   |         | Quality of flash programming                                                                 |     |

| 4.2   |         | Turning the power on/off                                                                     |     |

| 4.2   |         | STMSEL (option byte 0 register)                                                              |     |

| 4.2   | . 13    | GRG and PBG                                                                                  | .26 |

| 4.2.14 Resets while the emulator is in use                                            | 26          |

|---------------------------------------------------------------------------------------|-------------|

| 4.2.15 Interrupts while the emulator is in use                                        | 27          |

| 4.2.16 HALT mode and stepped execution of the HALT instruction                        | 27          |

| 4.2.17 Cautionary point regarding connecting an emulator (pin reset)                  |             |

| 4.2.18 Cautionary point regarding connecting an emulator (time required for preparin  | g to        |

| communicate)                                                                          | 28          |

| 4.2.19 Cautionary point regarding connecting an emulator (internal reset)             | 28          |

| 4.2.20 Access to I/O resources in the MCU                                             | 28          |

| 4.2.21 Cautionary points regarding hot plug-in connection                             | 29          |

| 4.2.22 Cases where hot plug-in connection is not possible                             | 29          |

| 4.2.23 Cautionary point regarding asynchronous debugging mode (peripheral break       | function)29 |

| 4.2.24 Cautionary point regarding asynchronous debugging mode (reset)                 | 29          |

| 4.2.25 Cautionary point regarding asynchronous debugging mode (watchdog timer).       | 29          |

| 4.2.26 Cautionary point regarding asynchronous debugging mode (ECC error)             | 29          |

| 4.2.27 Cautionary point regarding asynchronous debugging mode (specific sequence      | e)30        |

| 4.2.28 Performance measurement                                                        | 30          |

| 4.2.29 Rewriting of on-chip flash memory (working RAM)                                | 30          |

| 4.2.30 Rewriting of on-chip flash memory (clock monitor)                              | 30          |

| 4.2.31 Breaks during execution of code for making clock settings                      | 31          |

| 4.2.32 Initially stopped states of CPU2 and the sub-CPU (forced break)                | 31          |

| 4.2.33 Initially stopped states of CPU2 and the sub-CPU (synchronous break)           | 31          |

| 4.2.34 Event functions (64-bit access)                                                | 31          |

| 4.2.35 Event functions (in the order of event detection)                              | 31          |

| 4.2.36 Event functions (bit-manipulation instructions)                                | 32          |

| 4.2.37 Event functions (memory-access detection not possible)                         | 32          |

| 4.2.38 Satisfaction of two break conditions before a single break                     | 32          |

| 4.2.39 Software break functions (RAM areas)                                           | 32          |

| 4.2.40 Emulator detection by user programs                                            | 32          |

| 4.2.41 Cautionary point regarding trace data acquired by software tracing (LPD outpot |             |

| (only for the E2 emulator)                                                            |             |

| 4.2.42 Breakpoints in the code flash P/E mode or data flash P/E mode                  | 33          |

| 5. Internal Circuits of the Emulator                                                  | 34          |

| 6. Troubleshooting                                                                    | 37          |

| 6.1 Problems when the emulator is connected                                           |             |

| 6.2 Problems after the emulator is connected                                          |             |

E1/E20/E2 Emulator 1. Outline

## 1. Outline

## 1.1 Features of an E1, E20, or E2 emulator

An E1, E20, or E2 emulator is an on-chip debugging emulator that includes a flash programming function, which is used for debugging and programming programs to be embedded in microcontrollers that have on-chip flash memory. That is, either product can debug a program while the target microcontroller is connected to the user system, and can write programs to the on-chip flash memory of microcontrollers.

## 1.2 Caution on using the E20 emulator

The functions used for debugging of the RH850 family by using the E20 emulator are the same as in the E1 emulator. Large trace function, a characteristic function of the E20 emulator, cannot be used.

## 1.3 Configuration of manuals

When using the E1, E20, or E2 emulator in debugging with an RH850 family product, be sure to read the manuals (1) and (2) below. Also read the application note (3) if required.

- (1) E1 or E20 emulator user's manual and E2 emulator user's manual

- The E1/E20 Emulator User's Manual and E2 Emulator User's Manual describe hardware specifications including the following items:

- · Components of the emulators

- Emulator hardware specifications

- Connecting the emulator to a host computer and user system

- (2) E1 or E20 emulator, E2 emulator additional document for user's manual

- The E1/E20 Emulator, E2 Emulator Additional Document for User's Manual describes functions of a debugger, and its contents depend on the given set of MCUs. In general, an additional document has notes on items including the following:

- For use in hardware design, an example of connection and the interface circuits required to connect the emulator.

- Notes on using the emulator

- (3) E2 emulator application note

The E2 Emulator Application Note includes an explanation, descriptions of usage, and notes on the extended functions of the E2 emulator.

## 2. Connecting the Emulator and User System

To connect the E1, E20, or E2 emulator, a connector for the user system interface cable must be mounted on the user system. When designing the user system, read this chapter of this manual and the hardware manual for the MCUs to be used.

## 2.1 Connector mounted on the user system

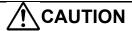

Table 2-1 shows the recommended 14-pin connector for connection of the E1, E20, or E2 emulator. When other components are mounted around the connector, do not mount components with heights exceeding 10 mm within 5 mm of the connector on the user system as shown in Figure 2-1.

**Table 2-1 Recommended Connector**

|           | Type<br>Number | Manufacturer     | Specification                          |

|-----------|----------------|------------------|----------------------------------------|

| 14-pin    | 7614-6002      | 3M Japan Limited | 14-pin straight type (Japan)           |

| connector | 2514-6002      | 3M Limited       | 14-pin straight type (other countries) |

Figure 2-1 Area where Restriction Applies to Mounted Components

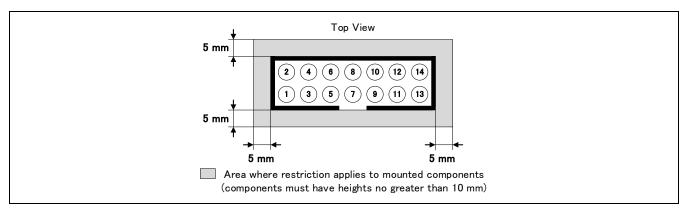

For the connection of an E1 emulator

Figure 2-2 shows an example of the connection of the user system interface cable of an E1 emulator to a 14-pin connector.

Figure 2-2 Connecting the User System Interface Cable to the 14-pin Connector in the E1 Emulator

For the connection of an E20 emulator

To use an E20 emulator with a 14-pin connector, use the 38-pin/14-pin connector conversion adapter [R0E000200CKA00] that comes with the E20.

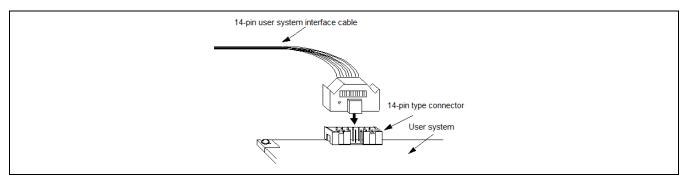

For the connection of an E2 emulator

To use an E2 emulator with a 14-pin connector, use the connector conversion adapter that comes with the E2. Figure 2-3 shows an example of the connection.

The connector conversion adapter is provided with a switch. Setting for the switch must be on the "1" side for the RH850. Operation is not guaranteed if the switch is on the "3" side. For setting the switch, refer to Table 2-2.

Figure 2-3 Connecting the User System Interface Cable to the 14-pin Connector in the E2 Emulator

Table 2-2 Setting of Switches (SW1)

| Setting | Description                                                      |  |

|---------|------------------------------------------------------------------|--|

| 1       | The target device is an RH850 microcontroller (default setting). |  |

| 3       | The target device is an RL78 microcontroller.                    |  |

Note on connector insertion and removal (1):

When connecting or disconnecting the user-system interface cable and the user system, grasp the connector cover at the end of the cable or both sides of the board of the connector conversion adapter. Pulling the cable itself will damage the wiring.

If a 20-pin (1.27-mm pitch) user-system interface cable of the E2 emulator becomes disconnected, purchase the following discontinued product: RTE0T00020KCAC0000J.

Note on connector insertion and removal (2):

Be aware that the user-system interface cable or the connector conversion adapter must be inserted with the correct orientation. Connecting the user-system interface cable or the connector conversion adapter with the wrong orientation may cause damage.

## 2.2 Pin assignments of the connector

Table 2-3 shows the pin assignments of the 14-pin connector.

Table 2-3

Pin Assignments of the 14-pin Connector

|         |            |        | I/O (*4)    |                   |        |

|---------|------------|--------|-------------|-------------------|--------|

| Pin No. | Debugging  |        |             | Programming (RFP) |        |

|         | 4-pin LPD  | JTAG   | 2-wire UART | CSI               |        |

| 1       | LPDCLK     | TCK    | _           | FPCK              | Input  |

| 2 (*1)  | GND        | GND    | GND         | GND               | _      |

| 3       | LPDRST#    | TRST#  | _           | _                 | Input  |

| 4       | FPMD0      | FPMD0  | FPMD0       | FPMD0             | Input  |

| 5       | LPDO       | TDO    | FPDT        | FPDT              | Output |

| 6       | _          | _      | FPMD1       | FPMD1             | Input  |

| 7       | LPDI/LPDIO | TDI    | FPDR        | FPDR              | I/O    |

| 8       | TVDD       | TVDD   | TVDD        | TVDD              | _      |

| 9       | _          | TMS    | _           | _                 | Input  |

| 10 (*3) | EVTO       | EVTO   | _           | _                 | Output |

| 11      | LPDCLKO    | RDY#   | _           | _                 | Output |

| 12 (*1) | GND        | GND    | GND         | GND               | _      |

| 13 (*2) | RESET#     | RESET# | RESET#      | RESET#            | Input  |

| 14 (*1) | GND        | GND    | GND         | GND               | _      |

Notes: 1. Securely connect pins 2, 12, and 14 of the connector to GND of the user system. These pins are used for electrical GND and to monitor connection with the user system by the E1, E20, or E2 emulator.

- 2. Be particularly sure to connect pin 13 before using the emulator.

- 3. The EVTO pin provides for the output of event signals from the device to the E2 emulator. Although connecting the EVTO pin is not essential, we recommend connecting this pin in advance.

In some devices, the EVTO pin is not present or is only available as a pin function multiplexed with other functions. When the EVTO pin is a multiplexed pin function and the event output function is to be used, set the EVTO pin so that it will function as the EVTO pin by making the required register settings described in the user's manual for the device.

- 4. Input and output are defined from the perspective of the target device.

Unused pins:

Do not apply signals from the user system to unused pins. Doing so may damage the pins.

#### 2.3 Connection interface and modes

The operating mode and the connection interface of an E1, E20, or E2 emulator is switched in the ways shown in Table 2-4 according to whether it is in use for debugging (when a debugger is in use) or programming (when the Flash Programmer is in use). The serial programming mode may still be used even if the debugger is in use. When flash memory is programmed by the downloading function of the debugger, the flash self-programming function is used.

Table 2-4 Modes and Connection Interfaces

| Usage       | Tool                           |                                                | Device Mode             | Connection Interface |

|-------------|--------------------------------|------------------------------------------------|-------------------------|----------------------|

| Programming | Renesas Flash Programmer (RFP) |                                                | Serial programming mode | 2-wire UART or CSI   |

| Debugging   | CS+,<br>MULTI*1,               | When OPJTAG is automatically set (connected)*2 | Serial programming mode | 2-wire UART          |

|             | or During debugging            | Normal operation mode or user boot mode        | 4-pin LPD or JTAG       |                      |

Notes: 1. This refers to the MULTI integrated development environment from Green Hills Software. It is simply referred to as MULTI in the remainder of this document.

2. OPJTAG automatic setting function: When a device is debugged, the OPJTAG bit in the option byte register determines the type of connection interface. Debugging will not start if the interface selected by the OPJTAG bit does not match that selected by the debugger. If the OPJTAG automatic setting function is enabled, the emulator makes a transition to the serial programming mode without fail and reads the OPJTAG bit. If the interface differs from that selected by the debugger, the OPJTAG bit is rewritten, the mode is switched to the normal operating mode, and debugging will start. This function only works when the 4-pin LPD is selected as the connection interface.

When this function is enabled to start debugging, since the mode is switched to the serial programming mode, some emulation may be impossible since the initial values in memory and of ECC errors after a reset are undefined. Therefore, only use the OPJTAG automatic setting function when the OPJTAG bit in the option byte register is to be modified. For details on setting this function, refer to the user's manual for the debugger you are using.

With CS+, select "Yes" as the [Set OPJTAG in LPD connection before connecting] property on the [Connect Settings] tabbed page to enable the OPJTAG automatic setting function.

## 2.4 Examples of recommended connections between the connector and MCU

This section describes examples of recommended connections between the connector for the E1, E20, or E2 emulator and the target device. Since there are various examples of recommended connections according to the purpose of the emulator, select the appropriate circuit with reference to Table 2-5. Be sure to take the specifications of the target device as well as measures to prevent noise into consideration when designing your circuit.

Table 2-5 Purpose of the E1, E20, or E2 Emulator and the Corresponding Example of Recommended Connections

| Purpose                                                            | Figure     |

|--------------------------------------------------------------------|------------|

| Debugging (4-pin LPD or JTAG) and programming (2-wire UART or CSI) | Figure 2-4 |

| Only programming (2-wire UART)                                     | Figure 2-5 |

| Only programming (CSI)                                             | Figure 2-6 |

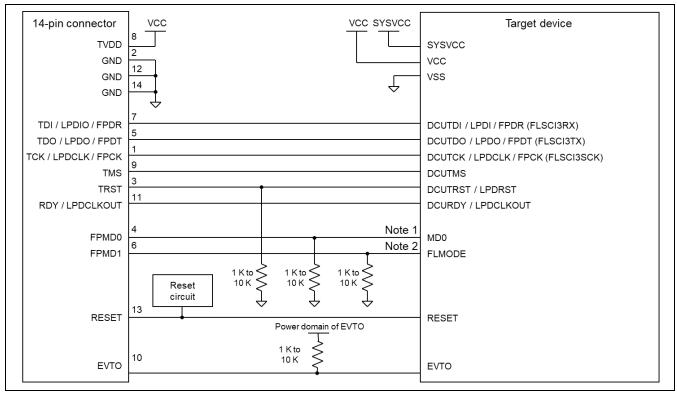

# 2.4.1 Example of recommended connections for debugging (4-pin LPD or JTAG) and programming (2-wire UART or CSI)

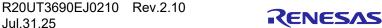

Figure 2-4 Example of Connection

- Note 1: The FLMD0 pin and the debugging interface are in different power domains to those in the target device. However, the interface voltage of the E2 emulator is based on the power supply that is connected to TVDD of the 14-pin connector. Refer to chapter 5, Internal Circuits of the Emulator. Therefore, when the RFP is in use, the E2 emulator drives the FLMD0 pin by TVDD (power domain of the debugging interface). After confirming the specification of the FLMD0 pin of the target device, insert level shifters as required.

- Note 2: The target device must be transferred to serial programming mode when the RFP is in use.

Therefore, the E2 emulator outputs the high level on FPMD0 and the low level on FPMD1. Connect FLMD1 and FPMD1 as required after having confirmed the specifications for operation modes of the target device.

- During debugging, the E2 emulator does not output signals to FPMD0 or FPMD1 (they are in the high-impedance state).

- Refer to section 2.4.4, Connecting the RESET pin, for more information on the reset circuit.

- For details on TVDD, refer to section 2.4.5, Connecting the TVDD pin.

- Make wiring runs between the 14-pin connector and target device as short as possible (within 50 mm is recommended). Do not connect the signal lines between the connector and target device to other signal lines.

- Use GND to apply a guard ring for the wiring which runs between the 14-pin connector and target device. Do not route high-speed signal lines parallel to each other or allow them to cross each other.

- Pin names may vary among target devices. Refer to the user's manual for the target device you are using for the actual pin names.

- Proceed with appropriate processing for pins of target devices which do not require connection to the emulator in accord with the descriptions in "Handling of Unused Pins" in the user's manual for the target device.

## **CAUTION**

Connection of emulators from other manufacturers:

If you use an emulator from another manufacturer for debugging, be sure to read its manual beforehand.

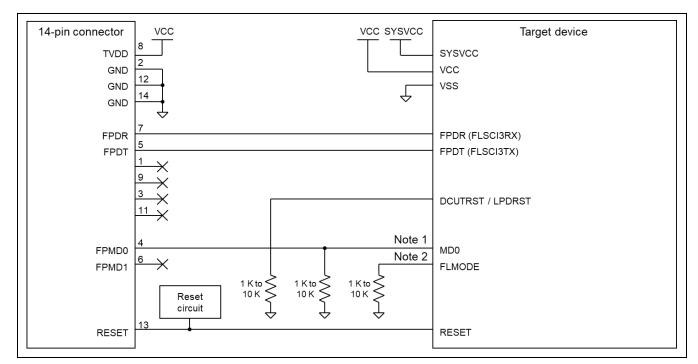

## 2.4.2 Example of recommended connections for only programming (2-wire UART)

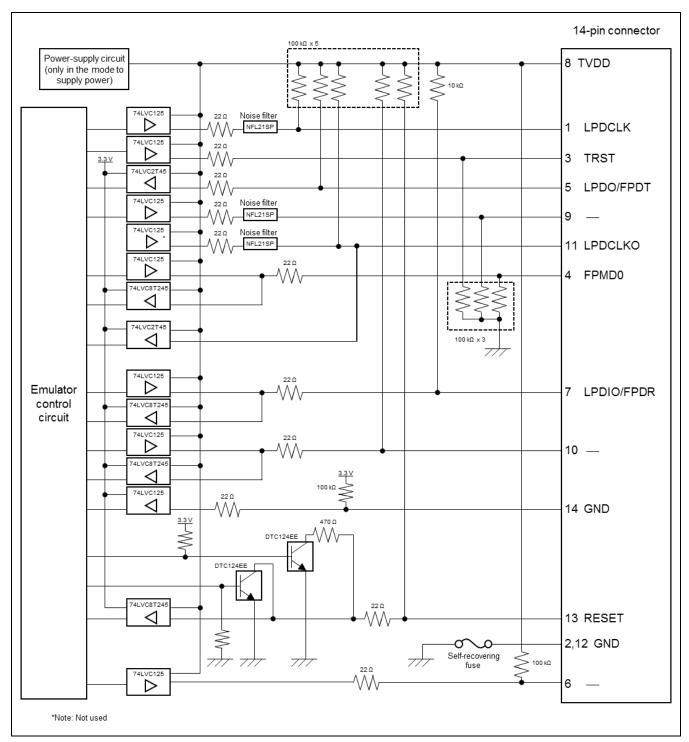

Figure 2-5 Example of Connection

- Note 1: The FLMD0 pin and the debugging interface are in different power domains to those in the target device. However, the interface voltage of the E2 emulator is based on the power supply that is connected to TVDD of the 14-pin connector. Refer to chapter 5, Internal Circuits of the Emulator. Therefore, when the RFP is in use, the E2 emulator drives the FLMD0 pin by TVDD (power domain of the debugging interface). After confirming the specification of the FLMD0 pin of the target device, insert level shifters as required.

- Note 2: The target device must be transferred to serial programming mode when the RFP is in use.

Therefore, the E2 emulator outputs the high level on FPMD0 and the low level on FPMD1. Connect FLMD1 and FPMD1 as required after having confirmed the specifications for operation modes of the target device.

- During debugging, the E2 emulator does not output signals to FPMD0 or FPMD1 (they are in the high-impedance state).

- Refer to section 2.4.4, Connecting the RESET pin, for more information on the reset circuit.

- For details on TVDD, refer to section 2.4.5, Connecting the TVDD pin.

- Make wiring runs between the 14-pin connector and target device as short as possible (within 50 mm is recommended). Do not connect the signal lines between the connector and target device to other signal lines.

- Use GND to apply a guard ring for the wiring which runs between the 14-pin connector and target device. Do not route high-speed signal lines parallel to each other or allow them to cross each other.

- Pin names may vary among target devices. Refer to the user's manual for the target device you are using for the actual pin names.

- Proceed with appropriate processing for pins of target devices which do not require connection to the emulator in accord with the descriptions in "Handling of Unused Pins" in the user's manual for the target device.

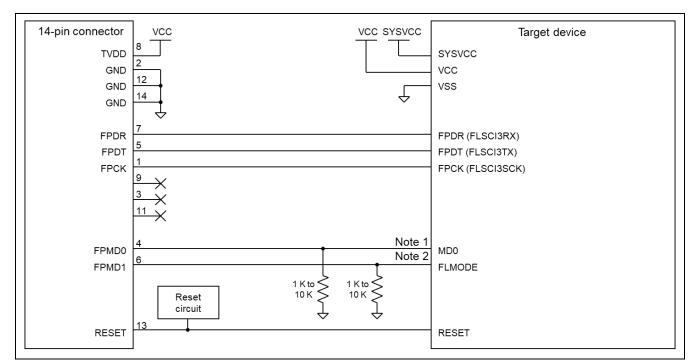

## 2.4.3 Example of recommended connections for only programming (CSI)

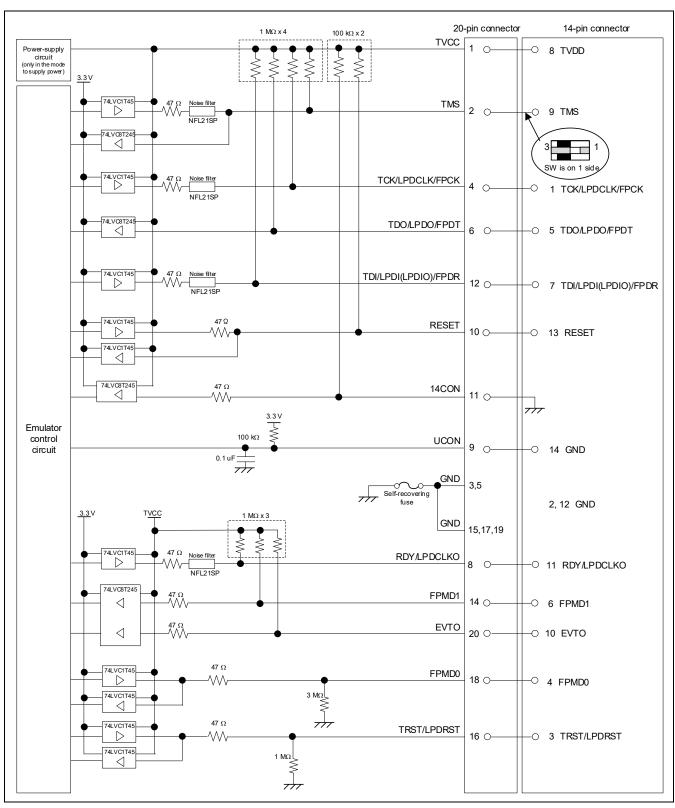

Figure 2-6 Example of Connection

- Note 1: The FLMD0 pin and the debugging interface are in different power domains to those in the target device. However, the interface voltage of the E2 emulator is based on the power supply that is connected to TVDD of the 14-pin connector. Refer to chapter 5, Internal Circuits of the Emulator. Therefore, when the RFP is in use, the E2 emulator drives the FLMD0 pin by TVDD (power domain of the debugging interface). After confirming the specification of the FLMD0 pin of the target device, insert level shifters as required.

- Note 2: The target device must be transferred to serial programming mode when the RFP is in use.

Therefore, the E2 emulator outputs the high level on FPMD0 and the low level on FPMD1. Connect FLMD1 and FPMD1 as required after having confirmed the specifications for operation modes of the target device.

- During debugging, the E2 emulator does not output signals to FPMD0 or FPMD1 (they are in the high-impedance state).

- Refer to section 2.4.4, Connecting the RESET pin, for more information on the reset circuit.

- For details on TVDD, refer to section 2.4.5, Connecting the TVDD pin.

- Make wiring runs between the 14-pin connector and target device as short as possible (within 50 mm is recommended). Do not connect the signal lines between the connector and target device to other signal lines.

- Use GND to apply a guard ring for the wiring which runs between the 14-pin connector and target device. Do not route high-speed signal lines parallel to each other or allow them to cross each other.

- Pin names may vary among target devices. Refer to the user's manual for the target device you are using for the actual pin names.

- Proceed with appropriate processing for pins of target devices which do not require connection to the

emulator in accord with the descriptions in "Handling of Unused Pins" in the user's manual for the target

device.

## 2.4.4 Connecting the RESET pin

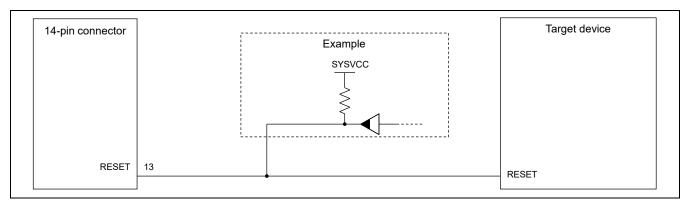

While you are using the E1, E20, or E2 emulator, pin 13 (RESET pin) of the 14-pin connector must be connected to the reset pin of the target device. Figure 2-7 shows an example.

Figure 2-7 Example of Connecting a Reset Circuit

The E1, E20, or E2 emulator fixes the RESET pin to the low level before the debugger is activated. After the debugger is activated, the emulator either keeps the pin at the low level or places it in the high-impedance state in accord with the operation of the debugger.

- Output of the reset circuit should be either n-channel open drain or be a signal generated solely by a resistor and capacitor (and possible other components).

- For the target device in this user's manual, pull the RESET signal up to the SYSVCC voltage.

- Pin 13 (RESET) of the E1, E20, or E2 emulator is pulled up (by a 100-k $\Omega$  resistor) within the emulator (refer to chapter 5, Internal Circuits of the Emulator).

- The RESET pin of the target device may be pulled up or down within the device. On this point, refer to the user's manual for the target device.

- The maximum sink current accepted by the RESET pin of the E1, E20, or E2 emulator is 2 mA. Select an appropriate pull-up resistance which does not surpass this value.

- Adjust the time constant of the reset circuit so that the time elapsing before the signal reaches 80% of the high level from the low level is within 900 μs.

- When you use hot plug-in, consider installation of a capacitor between the reset signal and GND in order to suppress a noise. In this case, however, the specifications of the time described above must be satisfied.

## 2.4.5 Connecting the TVDD pin

### (1) Power source monitoring function

Connect the power source on the user system to pin 8 (TVDD pin) of the 14-pin connector. For the target device in this user's manual, this will be the source of the VCC voltage.

The power source connected to the TVDD pin provides power to the final stage output buffer and first stage input buffer on the E1/E20/E2 emulator circuit. When the E1, E20, or E2 emulator is connected, it will draw current as described below in addition to the current drawn by the user system.

- E1/E2 emulator: Approx. 20 mA when TVDD is 3.3 V, and approx. 40 mA when TVDD is 5.0 V

- E20 emulator: Approx. 40 mA when TVDD is 3.3 V, and approx. 100 mA when TVDD is 5.0 V

#### (2) Power supply function (applies only to the E1 or E2 emulator)

The E1 or E2 emulator can also supply power at 3.3 V or 5.0 V from the TVDD pin to the user system (at a current of up to 200 mA). When using this function, take care of the following points.

- Do not use this function if power is being separately supplied to the user system. Attempting to do so might break the E1 or E2 emulator.

- Do not use this function for a user system which draws a current of 200 mA or more. The E1 or E2 emulator or USB interface of the host machine might be broken.

- Make sure that the supplied voltage is within the voltage range required by the user system.

- E1 emulator: The 5.0-V supply depending on the environment of the host machine in use, the voltage might be lower than 5.0 V by 0.5 V or more.

- E2 emulator: The 5.0-V supply depending on the environment of the host machine in use, the voltage might be lower than 5.0 V by 0.3 V or more.

Power supply from the E1 or E2 emulator depends on the quality of the USB power supply of the host machine, and as such, precision is not guaranteed. When writing a program that requires reliability, do not use the power supply function of the E1 or E2 emulator. Use a stable, separate power supply for the user system. When writing a program for mass production processes, use the Renesas Flash Programmer.

## CAUTION

## Turning the Power On/Off:

When supplying power, ensure that there are no shorts between the user system and power circuit. Only connect the E1, E20, or E2 after confirming that there are no mismatches of alignment on the user system port connector. Incorrect connection will result in the host machine, the emulator, and the user system emitting smoke or catching fire.

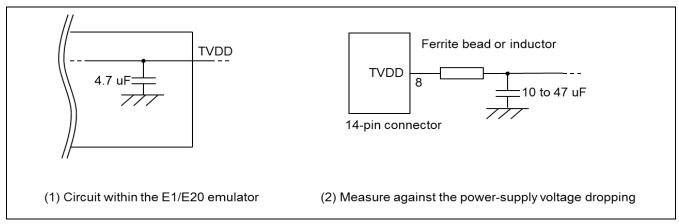

### 2.4.6 Hot plug-in connection

If there is a possibility you will be using hot plug-in connection, you will need to configure the circuit as shown below. Pin 8 of the E1 emulator is connected to a 4.7-uF capacitor as shown in (1) in Figure 2-8, so hot plug-in connection of the emulator may lead to a momentary drop in the power-supply voltage on the user system. This might cause the MCU to be reset.

As shown in (2) in Figure 2-8, this effect can be reduced by placing a ferrite bead (or inductor) and relatively large capacitor with low equivalent series resistance near the TVDD line of the connector for connection of the emulator. However, this measure will not completely eliminate the voltage drop. Note that hot plug-in connection is only for use during debugging, and a separately sold hot plug-in adapter is necessary to use this function otherwise.

Figure 2-8 Circuit Configuration for Hot Plug-in

Hot plug-in adapter for the E1 emulator

For hot plug-in connection to the E1 emulator, use the hot plug-in adapter for the E1 emulator (R0E000010ACB00) that is separately available from Renesas.

Hot plug-in connection can be used with the E2 emulator without the need for a hot plug-in adapter. For details, refer to the E2 Emulator User's Manual.

The E1, E20, or E2 emulator does not support the hot plug-out function. Do not disconnect the user-system interface cable during debugging.

Note on the hot plug-out function:

While the power of the user system is on, do not unplug the user-system interface cable. The emulator and the user system may be damaged.

### 2.4.7 Isolator for the E1 emulator

For a debugging environment where there is a difference in potential between the GND of the user system and that of the host PC, use the isolator for the E1 emulator (R0E000010ACB20) which is separately available from Renesas.

## 2.4.8 Small connector conversion adapter for the E1 emulator

A small connector conversion adapter for the E1 emulator (R0E000010CKZ11) is separately available from Renesas for user system boards which are too small to mount the 14-pin connector that is the standard connector for the E1 emulator. By using the adapter, you can reduce the area taken up by the connector mounted on your system.

However, when you use the small connector conversion adapter for the E1 emulator, be aware that the pin assignments of the connector differ from those of the standard interface connector for the E1 emulator.

## 3. Specifications

Table 3-1 shows specifications common to the E1, E20, and E2 emulators.

Table 3-2 shows specifications specific to the E2 emulator.

Support for some debugging-related functions also depends on the debugger. Refer to the user's manual, etc. for the debugger you are using.

Table 3-1 Specifications Common to the E1, E20, and E2 Emulators

| Broad Category          | Medium<br>Category                         | Narrow Category                  | Specification                                                                                                                                                                |

|-------------------------|--------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware in general     | Corresponding host                         | machine                          | Computer equipped with a USB port,                                                                                                                                           |

|                         |                                            |                                  | OS depends on the debugger                                                                                                                                                   |

|                         | User system interfac                       | e                                | 14-pin connector                                                                                                                                                             |

|                         | Host machine interfa                       | ace                              | USB 2.0 (full speed or high speed)                                                                                                                                           |

|                         | Connection to the us                       | ser system                       | Connection by the provided user system interface cable                                                                                                                       |

|                         | Power supply function emulator is an E1 or |                                  | 3.3 V or 5.0 V (with current up to 200 mA) can be supplied from TVDD to the user system (make settings with the debugger)                                                    |

|                         | Power supply for the                       | e emulator                       | No need (the host computer supplies power through the USB)                                                                                                                   |

| Debugging-related items | Break                                      | Software break                   | In ROM and RAM areas combined: 2000 points                                                                                                                                   |

|                         |                                            | Hardware break                   | 12 points including those used for both execution and CPU access conditions (8 points only for execution conditions, and 4 points for either execution or access conditions) |

|                         |                                            | Event break                      | Available                                                                                                                                                                    |

|                         |                                            | Forced break                     | Available                                                                                                                                                                    |

|                         |                                            | Trace-full break                 | Available (internal trace memory and E2 storage)                                                                                                                             |

|                         |                                            | External trigger input break     | Available (E2 emulator only)                                                                                                                                                 |

|                         | Event                                      | Number of events that can be set | 8 points for execution, 8 points for CPU access, 4 points for DMA access, and 4 points for GRAM access                                                                       |

|                         |                                            | Available function               | Break, trace, performance measurement                                                                                                                                        |

|                         |                                            | Combination of events            | OR, sequential                                                                                                                                                               |

| Broad Category                  |                         | lium<br>gory             | Narrow Category                                      | Specification                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|-------------------------|--------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Debugging-related items (cont.) | Tracing (only for       |                          | Destination for storage                              | Internal trace memory                                                                                                                                                                                                                                                                                                                                                                   |

| ,                               | including               | an                       | Size                                                 | Branch only: 1,000 branches                                                                                                                                                                                                                                                                                                                                                             |

|                                 | RAM)                    |                          |                                                      | Data trace only: 1,000 cycles of access Software trace only: 1,000 to 2,000 instructions                                                                                                                                                                                                                                                                                                |

|                                 |                         |                          | Traced data                                          | Branches, cycles of data access, cycles of DMA access, cycles of GRAM access, and software trace                                                                                                                                                                                                                                                                                        |

|                                 |                         |                          | Conditions to start<br>and stop recording of<br>data | Stopping of program execution, event condition settings                                                                                                                                                                                                                                                                                                                                 |

|                                 |                         |                          | Data-trace conditions                                | Event conditions                                                                                                                                                                                                                                                                                                                                                                        |

|                                 |                         |                          | Priority of trace acquisition                        | Real-time trace mode (priority given to speed)                                                                                                                                                                                                                                                                                                                                          |

|                                 |                         |                          |                                                      | Non-real-time trace mode (priority given to data)                                                                                                                                                                                                                                                                                                                                       |

|                                 |                         |                          | Recording of trace                                   | Ring mode (overwriting mode)                                                                                                                                                                                                                                                                                                                                                            |

|                                 |                         |                          | memory                                               | Trace-full stop mode                                                                                                                                                                                                                                                                                                                                                                    |

|                                 |                         |                          |                                                      | Trace-full break mode                                                                                                                                                                                                                                                                                                                                                                   |

|                                 |                         |                          |                                                      | Halting tracing due to the input of an external trigger (E2 emulator only)                                                                                                                                                                                                                                                                                                              |

|                                 | Performance measurement | Time<br>(1)              | Measurement section                                  | From run to break                                                                                                                                                                                                                                                                                                                                                                       |

|                                 |                         |                          | Item measured                                        | Execution time*4                                                                                                                                                                                                                                                                                                                                                                        |

|                                 |                         |                          | Performance                                          | 32-bit counters                                                                                                                                                                                                                                                                                                                                                                         |

|                                 |                         | Other than time          | Measurement section                                  | From run to break, or between two event points                                                                                                                                                                                                                                                                                                                                          |

|                                 |                         |                          | Items measured                                       | Execution time, total execution time, pass count, maximum execution time, minimum execution time*4                                                                                                                                                                                                                                                                                      |

|                                 |                         |                          | Performance                                          | 32-bit counters (for three sections)                                                                                                                                                                                                                                                                                                                                                    |

|                                 |                         |                          | Items measured                                       | Number of instructions executed (all or branches only), number of interrupts accepted (El level or FE level), number of exceptions accepted (instruction asynchronous or instruction synchronous), clock cycles (all, while interrupts are inhibited, or other than for the processing of interrupts), number of instruction fetches requested, number of hits on the instruction cache |

|                                 |                         |                          | Measurement section                                  | From run to break, or between two event points                                                                                                                                                                                                                                                                                                                                          |

|                                 |                         |                          | Items measured                                       | Latest value, total value, pass count, maximum value, minimum value                                                                                                                                                                                                                                                                                                                     |

|                                 |                         |                          | Performance                                          | 32-bit counters (for four sections)                                                                                                                                                                                                                                                                                                                                                     |

|                                 | Pseudo r                | real-time RAM monitoring |                                                      | Available (occupies a bus (steals cycles))*1                                                                                                                                                                                                                                                                                                                                            |

|                                 | Direct me               | emory modi               | ification                                            | Available (occupies a bus (steals cycles))*1                                                                                                                                                                                                                                                                                                                                            |

| Broad Category    | Medium<br>Category                                                                                        | Narrow Category | Specification                                                                          |

|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------|

| Debugging-related | Debugging console                                                                                         |                 | Not available                                                                          |

| items (cont.)     | Downloading of the external flash memory                                                                  |                 | Not possible                                                                           |

|                   | Hot plug-in                                                                                               |                 | Possible (To use with the E1 emulator, requires a separately sold hot plug-in adapter) |

|                   | Peripheral breaks                                                                                         |                 | Available*2                                                                            |

|                   | Emulator detection b                                                                                      | y user programs | Available*3                                                                            |

|                   |                                                                                                           |                 | Debugging startup register                                                             |

|                   |                                                                                                           |                 | Initial value: 0000 0000 <sub>H</sub>                                                  |

|                   |                                                                                                           |                 | Address: FA00 2078 <sub>H</sub> (CPU1)                                                 |

|                   |                                                                                                           |                 | FA00 2078 <sub>H</sub> (CPU2)                                                          |

|                   |                                                                                                           |                 | FA00 2078 <sub>H</sub> (sub-CPU)                                                       |

|                   | Security                                                                                                  |                 | 16-byte ID code authentication                                                         |

|                   | Security ID settings                                                                                      |                 | Not available                                                                          |

|                   | Security flag settings                                                                                    |                 | Not available                                                                          |

|                   | Activating the setting<br>Cryptographic Unit (                                                            |                 | Not possible                                                                           |

|                   | Connection interface                                                                                      | ;               | 4-pin LPD 5.5 MHz/11 MHz/16.5 MHz<br>(E1, E20 or E2)                                   |

|                   |                                                                                                           |                 | 20 MHz/25 MHz/33 MHz (E2 only)                                                         |

|                   |                                                                                                           |                 | JTAG (E2 only)                                                                         |

|                   |                                                                                                           |                 | 6.25 MHz/11 MHz/16.25 MHz/20 MHz/<br>25 MHz                                            |

| Programming-      | Security ID settings                                                                                      |                 | Available                                                                              |

| related items     | Security flag settings  Activating the settings of the Intelligent Cryptographic Unit (Slave type) (ICUS) |                 | Available                                                                              |

|                   |                                                                                                           |                 | Possible                                                                               |

|                   | Connection interface                                                                                      | ;               | 2-wire UART, CSI                                                                       |

Notes: 1. Only available for the local RAM and global RAM areas.

2. The function to stop peripheral I/O operation in a break is called the peripheral break function. Whether peripheral emulation functions are set or not is determined by the debugger. Refer to the manual for the debugger you are using for how to set them. Refer to the manual for the MCU you are using to check whether peripheral emulation functions are set.

- 3. For this function, any 32-bit value which is debugging information from the debugger is specified and held in the debugging startup register while the emulator is connected. This function can be used to determine the state of the emulator being connected or not from within user programs (refer to cautionary note in section 4.2.40).

- 4. The resolution of the measured times depends on the interface used for the connection (e.g., 90.9-nsec resolution for a 4-pin LPD connection running at 11 MHz).

Table 3-2 Specifications Specific to the E2 Emulator

| Broad Category          | Medium<br>Category              | Narrow Category                                | Specification                                                                                                                                                 |                                                                                                                                                                                                                                                                              |  |  |  |

|-------------------------|---------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Debugging-related items | Software tracing (LPD output)*1 |                                                |                                                                                                                                                               | Selection of a single CPU.  For multiple-core devices:  When the debugger is connected to the emulator, a single target CPU is selected. If the target CPU is changed, the debugger must be re-connected to the emulator (only available in the synchronous debugging mode). |  |  |  |

|                         |                                 | Destination for storage                        | "E2 storage": memory for storage in the E2 emulator                                                                                                           |                                                                                                                                                                                                                                                                              |  |  |  |

|                         |                                 | Internal buffer                                | Eight stages*4                                                                                                                                                |                                                                                                                                                                                                                                                                              |  |  |  |