**User's Manual**

# DAFCAN

# **CAN Interface with Diagnosis Support**

Hardware

# Addendum to AFCAN User's Manual

Document No. U18569EE1V1UM00 Date Published December 2008

© NEC Corporation 2008 Printed in Germany [MEMO]

### – NOTES FOR CMOS DEVICES ——

### () VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V<sub>DD</sub> or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

### **③ PRECAUTION AGAINST ESD**

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

## (5) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

All other product, brand, or trade names used in this publication are the trademarks or registered trademarks of their respective trademark owners.

Product specifications are subject to change without notice. To ensure that you have the latest product data, please contact your local NEC Electronics sales office.

# Legal Notes

- The information in this document is current as of December 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such NEC Electronics products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics

products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated

entirely. To minimize risks of damage to property or injury (including death) to persons arising from

defects in NEC Electronics products, customers must incorporate sufficient safety measures in their

design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to determine NEC Electronics 's willingness to support a given application.

- **Notes: 1.** "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- **2.** "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

- **3.** SuperFlash<sup>®</sup> is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan. This product uses SuperFlash<sup>®</sup> technology licensed from Silicon Storage Technology, Inc.

For further information, please contact:

### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/

### [America]

### NEC Electronics America, Inc.

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 http://www.am.necel.com/

### [Europe]

### NEC Electronics (Europe) GmbH

Arcadiastrasse 10 40472 Düsseldorf, Germany Tel: 0211-65030 http://www.eu.necel.com/

#### Hanover Office Podbielski Strasse 166 B 30177 Hanover

Tel: 0 511 33 40 2-0

### **Munich Office** Werner-Eckert-Strasse 9 81829 München Tel: 0 89 92 10 03-0

### Stuttgart Office

Industriestrasse 3 70565 Stuttgart Tel: 0 711 99 01 0-0

# **United Kingdom Branch**

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908-691-133

#### Succursale Française

9, rue Paul Dautier, B.P. 52180 78142 Velizy-Villacoublay Cédex France Tel: 01-3067-5800

### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

### Tyskland Filial

Täby Centrum Entrance S (7th floor) 18322 Täby, Sweden Tel: 08 638 72 00

### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02-667541

### **Branch The Netherlands**

Steijgerweg 6 5616 HS Eindhoven The Netherlands Tel: 040 265 40 10

### [Asia & Oceania]

NEC Electronics (China) Co., Ltd 7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China TEL: 010-8235-1155 http://www.cn.necel.com/

### NEC Electronics Shanghai Ltd.

Room 2509-2510, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai P.R. China P.C:200120 Tel: 021-5888-5400 http://www.cn.necel.com/

### NEC Electronics Hong Kong Ltd.

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318 http://www.hk.necel.com/

Seoul Branch

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737

NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-8175-9600

### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311 http://www.sg.necel.com/

G06.6-1A

# INTRODUCTION

| Readers                 | This manual is intented for users who want to understand the functions of the DAFCAN and to design application systems using the functions.       |                                                                                                                                                                        |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Purpose                 | This manual presents the hardware manual of DAFCAN.                                                                                               |                                                                                                                                                                        |  |  |

| Organization            | This system specification describes the following sections:                                                                                       |                                                                                                                                                                        |  |  |

| How to Read This Manual |                                                                                                                                                   |                                                                                                                                                                        |  |  |

|                         | It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers. |                                                                                                                                                                        |  |  |

|                         | To understand the overall functions of the DAFCAN macro:<br>Read this manual in the order of the CONTENTS.                                        |                                                                                                                                                                        |  |  |

|                         | Bars on the page borde                                                                                                                            | ers show major revised points.                                                                                                                                         |  |  |

| Legend                  | Symbols and notation a                                                                                                                            | are used as follows:                                                                                                                                                   |  |  |

|                         | Weight in data notation                                                                                                                           | : Left is high-order column, right is low order column                                                                                                                 |  |  |

|                         | Active low notation                                                                                                                               | : xxx (pin or signal name is over-scored) or /xxx (slash before signal name)                                                                                           |  |  |

|                         | Memory map address:                                                                                                                               | : High order at high stage and low order at low stage                                                                                                                  |  |  |

|                         | Note                                                                                                                                              | : Explanation of (Note) in the text                                                                                                                                    |  |  |

|                         | Caution                                                                                                                                           | : Item deserving extra attention                                                                                                                                       |  |  |

|                         | Remark                                                                                                                                            | : Supplementary explanation to the text                                                                                                                                |  |  |

|                         | Numeric notation                                                                                                                                  | : Binary xxxx or xxxB<br>Decimal xxxx<br>Hexadecimal xxxxH or 0x xxxx                                                                                                  |  |  |

|                         | Prefixes representing p                                                                                                                           | bowers of 2 (address space, memory capacity)<br>K (kilo) : $2^{10} = 1024$<br>M (mega) : $2^{20} = 1024^2 = 1,048,576$<br>G (giga) : $2^{30} = 1024^3 = 1,073,741,824$ |  |  |

# TABLE OF CONTENTS

| Chapter 1                                               | INTRODUCTION 17                                                                                                                                                                                                 |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                     | Overview of Functions                                                                                                                                                                                           |

| Chapter 2                                               | ARCHITECTURE                                                                                                                                                                                                    |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8    | CPU I/F20Global Macro Control20CAN Interrupt Generator20Message Control (MSG Ctrl)20Arbitration Logic21RXONLY_CH CAN machine21DIAG_CH CAN machine21Memory and Register Layout22                                 |

| Chapter 3                                               | Macro Initialisation and Control 23                                                                                                                                                                             |

| <b>3.1</b><br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5 | Global Macro Initialisation and Control24Global Macro Disabled (GOM=0).24Initialisations before Enabling the Global Macro24Global Macro Enabled24Switch-Off the Global Macro24Flowchart of the Initialisation27 |

| Chapter 4                                               | Message Buffer Initialisation and Configuration                                                                                                                                                                 |

| 4.1<br>4.2<br>4.3<br>4.4                                | Message Buffer Initialisation31Message Buffer to CAN I/F Channel Assignment32Configuration before switching to Mirror Mode34Configuration before switching to DIAG Side36                                       |

| Chapter 5                                               | DAFCAN Macro Initialisation and Control                                                                                                                                                                         |

| <b>5.1</b><br>5.1.1<br>5.1.2                            | CAN Bit Time Programming37Transitions for Operational Modes of DIAG_CH38Transition for Operational Modes of RXONLY_CH40                                                                                         |

| Chapter 6                                               | Macro Interrupts 41                                                                                                                                                                                             |

| Chapter 7                                               | Message Reception and Transmission                                                                                                                                                                              |

| 7.1<br>7.2<br>7.3<br>7.4                                | Principal Reception Process44Reception History44Reception of Remote Frames44Message Transmission44                                                                                                              |

| Chapter 8                                               | Operational Modes of RXONLY_CH 45                                                                                                                                                                               |

| 8.1<br>8.1.1<br>8.2<br>8.2.1<br>8.3                     | Receive-Only Mode45Processing received Frames in Receive-Only Mode of RXONLY_CH47Mirror Mode49Operations of the Mirror Mode Engine49Mirror Mode with TIF51                                                      |

| Chapter 9  | Transitions for Buffer Assignment                                     |

|------------|-----------------------------------------------------------------------|

| Chapter 10 | Register Description 54                                               |

| 10.1       | Registers of Global Macro Control                                     |

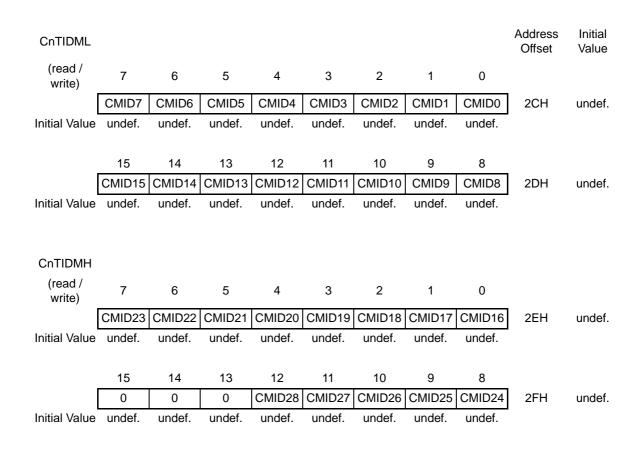

| 10.1.1     | CAN Transfer ID Reference Registers (CnTIDRmL, CnTIDRmH; m = 0 - 7)57 |

| 10.1.2     | CAN Transfer ID Mask Registers (CnTIDML, CnTIDMH)62                   |

| 10.2       | Registers of the CAN Module                                           |

| 10.2.1     | RXONLY_CH CAN Module Control Register (CnCTRL_R)67                    |

| 10.2.2     | RXONLY_CH CAN Module Last Error Code Register (CnLEC_R)68             |

| 10.2.3     | RXONLY_CH CAN Module Error Counter Register (CnERC_R)69               |

| 10.2.4     | RXONLY_CH CAN Module Interrupt Enable Register (CnIE_R)70             |

| 10.2.5     | RXONLY_CH CAN Module Interrupt Status Register (CnINTS_R)71           |

| 10.2.6     | RXONLY_CH CAN Module Bit-Rate Prescaler Register (CnBRP_R)72          |

| 10.2.7     | RXONLY_CH CAN Module Bit Rate Register (CnBTR_R)73                    |

| 10.2.8     | RXONLY_CH CAN Module Last In-Pointer Register (CnLIPT_R)74            |

| 10.2.9     | RXONLY_CH CAN Module Time Stamp Register (CnTS_R)75                   |

| 10.2.10    | RXONLY_CH CAN Module Bus Selector (CnBSEL_R)                          |

| 10.3       | Registers of Message Buffers77                                        |

| 10.3.1     | CAN Message Configuration Register (CnMCONFm)                         |

| 10.3.2     | CAN Message Identifier Registers (CnMIDLm, CnMIDHm)80                 |

| 10.3.3     | CAN Message Control Register (CnMCTRLm)                               |

| Figure 1-1: | Diagnosis Concept using DAFCAN and 4 other CAN Channels                      | . 17 |

|-------------|------------------------------------------------------------------------------|------|

| Figure 2-1: | Architecture of DIAG Macro                                                   | . 19 |

| Figure 2-2: | Register Address Layout                                                      | . 22 |

| Figure 3-1: | State Transitions of Global Macro Switching                                  | . 23 |

| Figure 3-2: | Shutdown Process (Normal Shutdown)                                           | . 25 |

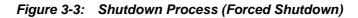

| Figure 3-3: | Shutdown Process (Forced Shutdown)                                           |      |

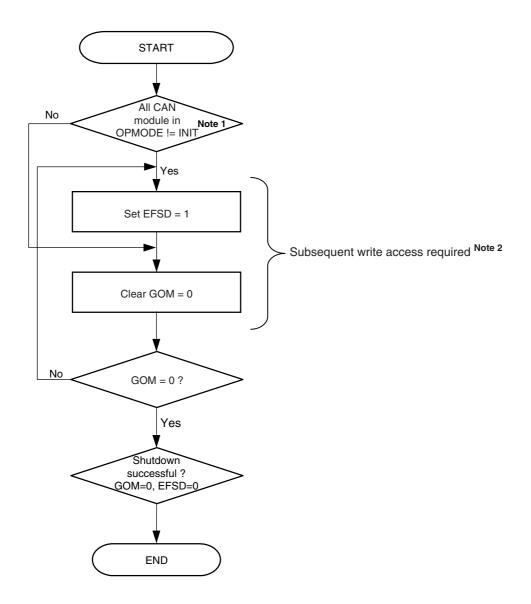

| Figure 3-4: | DAFCAN Macro Initialisation                                                  | . 27 |

| Figure 3-5: | Re-initialisation of the DIAG_CH CAN Module using 48 Buffers                 | . 28 |

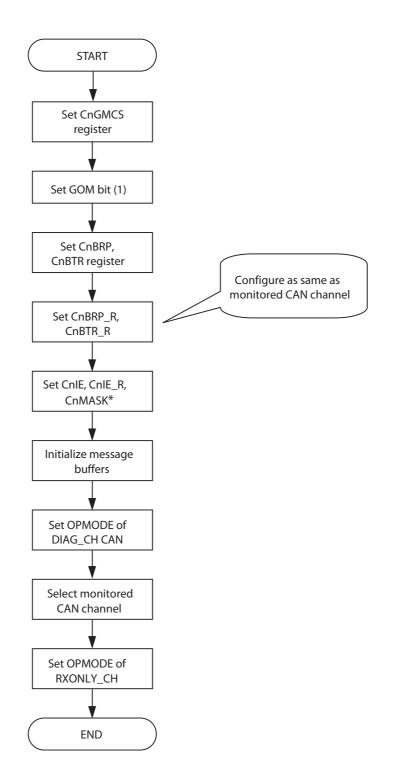

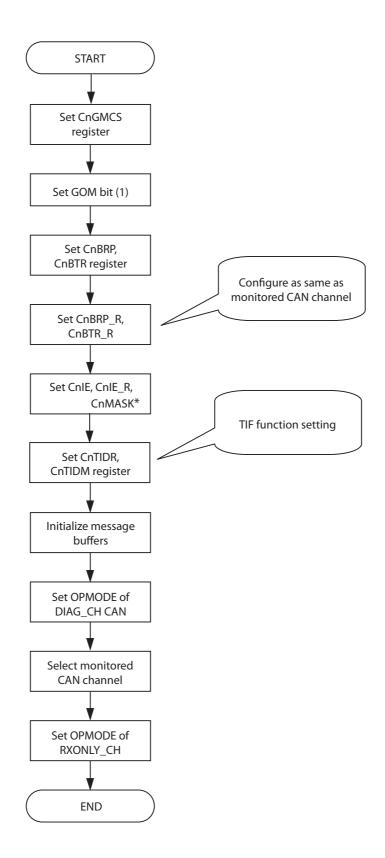

| Figure 3-6: | Re-initialisation of the DIAG_CH CAN Module using TX ID Filter Function      | . 29 |

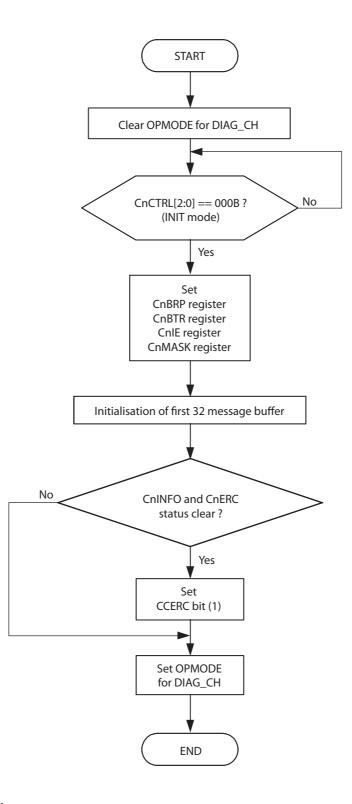

| Figure 3-7: | Re-initialisation of the DIAG_CH CAN Module using first 32 Buffers only      | . 30 |

| Figure 4-1: | CPU Write Access to a Message Buffer                                         | . 31 |

| Figure 4-2: | Operation in Mirror or Receive-only Mode of RXONLY_CH                        | . 32 |

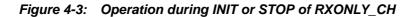

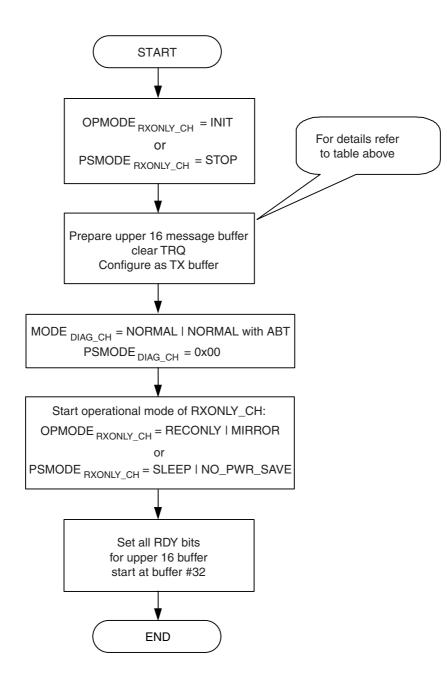

| Figure 4-3: | Operation during INIT or STOP of RXONLY_CH                                   | . 33 |

| Figure 4-4: | Set up of Mirror Mode, Mirror Mode w/ TIF or Receive-Only Mode for RXONLY_CH | 35   |

| Figure 4-5: | Cancellation of Mirror Mode or Receive-Only Mode for RXONLY_CH               | . 36 |

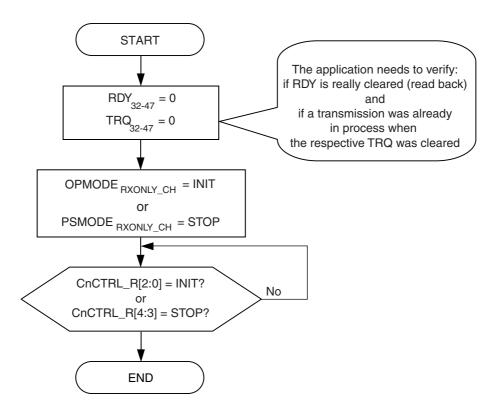

| Figure 5-1: | Transitions for Operational Modes of the DIAG_CH CAN module                  | . 38 |

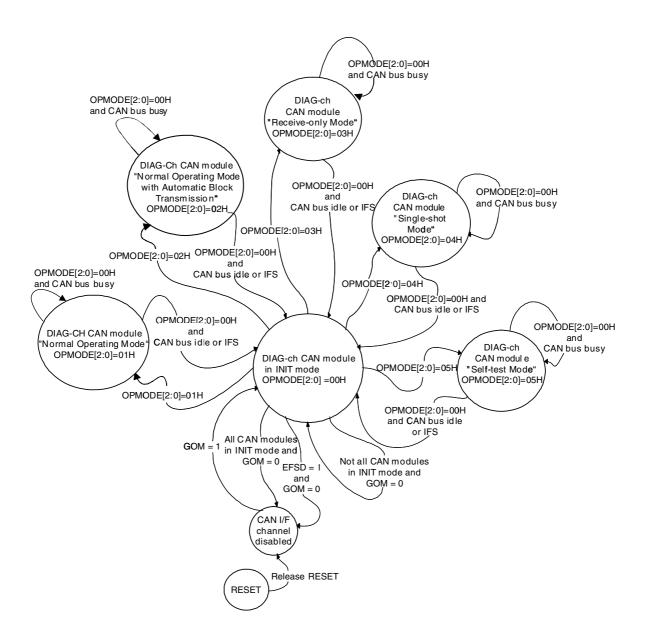

| Figure 5-2: | Transitions for operational modes of the RXONLY_CH CAN module                | . 40 |

| Figure 6-1: | Schematic of the DAFCAN Macro Interrupt Generation (1/2)                     | . 42 |

| Figure 8-1: | Reception Process of Receive-Only Mode                                       | . 45 |

| Figure 8-2: | Receive Operation for RXONLY_CH in Receive-Only Mode                         | . 48 |

| Figure 8-3: | Mirror Mode without Application Communication on DIAG_CH                     | . 50 |

| Figure 8-4: | Mirror Mode with interleaved Application Communication on DIAG_CH            |      |

| Figure 9-1: | Changing the Assignment of the upper 16 Buffers                              | . 52 |

|             |                                                                              |      |

| Table 1-1:  | Outline of DIAG Macro Functions                                             | 18 |

|-------------|-----------------------------------------------------------------------------|----|

| Table 4-1:  | Minimum Configuration of Message Buffer even when unused in the Application | 31 |

| Table 4-2:  | Message Buffer Assignment versus PS/OPMODE                                  | 33 |

| Table 6-1:  | List of all Macro Interrupt Sources                                         | 41 |

| Table 8-1:  | Differences in Reception Process between regular AFCAN and RXONLY_CH        | 46 |

| Table 10-1: | Global Macro Registers (CPU read access)                                    | 54 |

| Table 10-2: | Global Macro Registers (CPU write access)                                   | 56 |

| Table 10-3: | CAN Module Registers (CPU read access)                                      | 63 |

| Table 10-4: | CAN Module Registers (CPU write access)                                     | 65 |

| Table 10-5: | CAN Message Buffer Registers (CPU read access)                              | 77 |

| Table 10-6: | CAN Message Buffer Registers (CPU write access)                             | 78 |

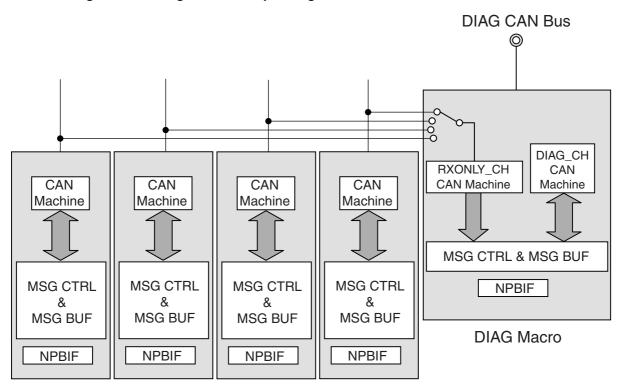

The DAFCAN (Diagnostic AFCAN) macro is in first place an ordinary single channel AFCAN macro with 48 message buffers. In difference to the single channel AFCAN macro the DAFCAN macro features two CAN channels. The channel, which can be operated as an ordinary CAN interface, is called diagnostic channel (DIAG\_CH).

For specific diagnostic purposes of the application a second CAN interface is available. This second channel has only limited operational modes because its main purpose is to listen only to the data traffic of one of the other single channel AFCAN macros. This channel is called listen-only channel (RXONLY\_CH). It provides the mirror function, which transfers the messages from the source CAN bus (monitored channel) to the diagnostic channel from where these messages are automatically sent onto the CAN bus. Furthermore, it provides the mirror mode with the Transfer ID Filter function (w/ TIF). This mode can transmit particular ID only from the source CAN channel to destination channel automatically.

The mirror function as part of a diagnosis concept including other CAN channels is shown in Figure 1-1.

Figure 1-1: Diagnosis Concept using DAFCAN and 4 other CAN Channels

# 4 x AFCAN Macro

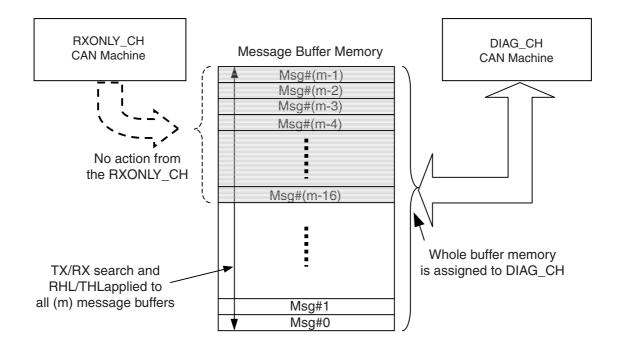

The RXONLY\_CH and the DIAG\_CH have independent control registers for power save (PSMODE) and operational (OPMODE) modes. The combination of both affects the message buffer allocation for the RXONLY\_CH. When RXONLY\_CH is in PSMODE == STOP or in OPMODE == INIT, the upper 16 message buffer are assigned to the DIAG\_CH. This offers the opportunity to use the DAFCAN macro as an ordinary CAN channel with 48 message buffers when monitoring of other CAN channels is not necessary.

# 1.1 Overview of Functions

| Feature                                                     | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Protocol                                                    | Active support of extended frame format (international standard ISO11898)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Channels                                                    | RXONLY_CH, DIAG_CH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Baud rate                                                   | Max. 1Mbit/s @ f <sub>CAN</sub> ≥ 16 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Message Storage                                             | RAM area with shared access (Accessing entities: CPU, RXONLY_CH CAN, DIAG_CH CAN)<br>The DAFCAN macro features 48 message buffers. The upper 16 buffer are assigned to the RXONLY_CH depending on operational and power save mode.                                                                                                                                                                                                                                                                                                                                       |  |  |

| Message<br>Organisation                                     | Each message buffer can be initialised either to be a transmit message buffer or a receive<br>message buffer.<br>A group of message buffers assigned as receive buffer can form a multi-buffer receive<br>block.<br>A group of message buffers assigned as transmit buffer can be used for automatic block<br>transfer.                                                                                                                                                                                                                                                  |  |  |

| Masks<br>(DIAG_CH only)                                     | The DIAG_CH features 4 masks. Each mask can be assigned to each message buffer.<br>There is no difference between global and local masks within one CAN module.<br>Mirror mode does not provide any masks. All messages are copied to DIAG_CH.<br>Mirror mode w/ TIF of the RXONLY_CH provides 8 reference transfer ID register<br>(CnTIDRnL/H) and 1 mask transfer ID register (CnTIDML/H) for filtering. Only message<br>matching the filter criteria are stored in the upper 16 message buffers. Only those mes-<br>sages stored here participate in the Mirror mode. |  |  |

| Application Support<br>for Message Han-<br>dling            | The DIAG_CH provides a fast mechanism to find receive message buffers with updated content (Reception History List).<br>The DIAG_CH provides a fast mechanism to find the transmit message buffers, from which a message frame has been sent (Transmission History List).<br>The RXONLY_CH does not provide these history lists.                                                                                                                                                                                                                                         |  |  |

| Remote Frame<br>Support                                     | Remote frame handling by message buffer defined for transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Time Stamp<br>Functions <sup>Note 1</sup><br>(DIAG_CH only) | Time stamp upon message reception<br>Trigger for time stamp capture selectable (SOF or EOF detection in a CAN message frame)<br>Append time stamp on transmission (specific bytes in the data field are replaced by the cap-<br>tured time stamp) <sup>Note 2</sup>                                                                                                                                                                                                                                                                                                      |  |  |

| Diagnostics                                                 | The DAFCAN macro features a mirror function. Messages received by RXONLY-CH are<br>automatically sent on the DIAG_CH. The RXONLY-CH input can be switched to any of the<br>other CAN channels of the device.<br>Readable error counters<br>Valid protocol activity flag for verification of bus connection<br>"Receive-only Mode"<br>CAN protocol error type decoding<br>"Self-test Mode" (DIAG_CH only)                                                                                                                                                                 |  |  |

| Power Save Modes                                            | Sleep Mode: Wake up from CAN bus<br>Stop Mode: No wake up from CAN bus<br>The RXONLY_CH CAN I/F module and the DIAG_CH CAN I/F module can be configured<br>independently to all these power save modes respectively.<br>The whole macro consumes minimum power when both CAN I/F modules are in such<br>modes simultaneously.                                                                                                                                                                                                                                            |  |  |

Table 1-1: Outline of DIAG Macro Functions

**Notes: 1.** The architecture of the DAFCAN macro is prepared for the integration of a TTCAN Module, but not all DAFCAN macro derivatives are equipped with a TTCAN Module.

**2.** The 'Append time stamp on transmission' function is offered only in AFCAN/DAFCAN macro derivatives, which are equipped with the Advanced Time Stamp function.

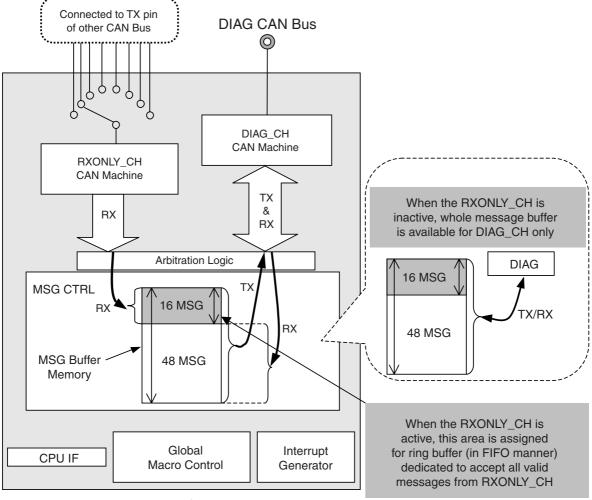

The DAFCAN macro is connected to a host CPU and provides two CAN bus interfaces. The DIAG\_CH CAN I/F module is dedicated for a particular CAN bus, the diagnostic CAN bus. The RXONLY\_CH CAN I/F module can be connected to several CAN buses via a programmable selector. The selector is located within the DAFCAN macro and provides connectivity for up to 8 sources.

The figure below shows an example of DAFCAN macro with 8 inputs for other CAN buses and 48 message buffers.

Figure 2-1: Architecture of DIAG Macro

DIAG Macro

The DAFCAN macro contains several sub-blocks that are described in the following chapters.

# 2.1 CPU I/F

The CPU I/F is the interface of the entire macro to the peripheral bus of the microcomputer system. The CPU I/F enables the CPU to access the control and status registers of all sub-blocks within the macro directly. The addresses of the control and status registers are mapped into the memory map of the microcomputer system.

The interrupt signals from the CAN Interrupt Generator to the Interrupt Controller of the microcomputer system are routed via the CPU I/F.

The macro clock f<sub>CAN</sub> is connected to a peripheral macro clock of the clock generator of the microcomputer system.

# 2.2 Global Macro Control

The Global Macro Control sub-block contains the logic that enables or disables the entire macro. As well the macro clock  $f_{CANMOD}$  is set here.

# 2.3 CAN Interrupt Generator

In the CAN Interrupt Generator all interrupt request signals from the CAN I/F channels are collected. Appropriated signal shaping is applied to those interrupt request signals for a proper connection to the interrupt request signal inputs of the interrupt controller in the microcomputer system (i.e. pulse generation).

# 2.4 Message Control (MSG Ctrl)

The MSG Ctrl sub-block provides the memory for the message buffers and its control.

The upper 16 message buffers have no static assignment to RXONLY\_CH or DIAG\_CH. The assignment of the message buffers depends on the status of RXONLY\_CH. The basic functions of these message buffers are:

When assigned to the RXONLY\_CH:

- Receive all data frames from RXONLY\_CH without any acceptance filtering when Mirror mode or Receive-Only mode is selected. In case of the Mirror mode w/ TIF, data/remote frames are filtered by mask register and reference ID registers.

- Receive all remote frames from RXONLY\_CH without any acceptance filtering.

- Behave as ring buffer in FIFO manner. Storage of received messages is calculated with help of LIPT of RXONLY\_CH.

- Automatically send all messages to DIAG\_CH in FIFO manner. The TX-search state machine of the DIAG-CH takes care to send these message on the diagnostic bus. Any TRQ by a FIFO candidate needs to start a TX-search, which always starts at message buffer #0. The TX-search always must be applied to both areas, the DIAG\_CH message buffers and the FIFO.

When assigned to the DIAG\_CH:

- Send data frames to DIAG\_CH

- Receive data frames from DIAG\_CH

- Receive remote frames from DIAG\_CH

- Send remote frames to DIAG\_CH

- Each message buffer contains its own identifier. Therefore a message buffer can be reserved to receive a data frame unambiguously or to transmit only a particular message frame.

- A mask can be assigned to a message buffer in case the reception of a group of data frames is required.

- Furthermore, message buffers can be grouped to build multi-buffer receive blocks (MBRB).

In other words, the complete message buffer memory (48 buffers) are fully assigned to DIAG\_CH with all related features of an ordinary AFCAN channel.

The lower message buffers (#0 to #31) are always assigned to the DIAG\_CH.

# 2.5 Arbitration Logic

The Arbitration Logic sub-block controls the access of the RXONLY\_CH and the DIAG\_CH to the MSG Ctrl sub-block.

# 2.6 RXONLY\_CH CAN machine

The RXONLY\_CH CAN machine sub-block contains logic of the CAN protocol transfer layer, which is dedicated to monitor a CAN BUS chosen by the selector. It never transmits any dominant bit on the monitored bus. The RXONLY\_CH is only connected to the monitored CAN channel via the RX-input terminal.

# 2.7 DIAG\_CH CAN machine

The DIAG\_CH CAN machine sub-block contains all logic for the CAN Protocol transfer layer. All protocol activities required for the reception of data frames, the transmission of message frames and the CAN protocol error management are executed automatically.

For transmission the DIAG\_CH CAN machine uses always all 48 message buffers. However the storage of received messages depends on the state of the RXONLY\_CH CAN machine. If the RXONLY\_CH CAN machine is 'in power save mode' (PSMODE = STOP) or in initialisation mode (OPMODE = INIT), all message buffer are assigned to the DIAG-CH. When RXONLY\_CH CAN machine is online or in sleep mode while the operating mode 'RXONLY' or 'Mirror Mode' is selected, only the lower 32 message buffer (#0 - #31) are used to store received messages from the DIAG\_CH CAN machine.

**Note:** When preparing for mirror mode while the upper 16 message buffers are still assigned to DIAG\_CH, the application needs to clear all pending TRQ bits of these buffers at first. Then, all RDY of these buffers need to be cleared as well. Then all these buffer need to be configured as receive message buffers before the initialisation state for the RXONLY\_CH is released; the buffers are assigned to RXONLY\_CH.

The acceptance filtering process, which decides whether a received data frame has to be stored into one of the assigned message buffers, is executed in the CAN module. The acceptance filtering process manages the storage into message buffers with and without an assigned mask, into multi-buffer receive blocks, and it resolves ambiguous storage situations.

In case more than one of the assigned message buffers are defined as transmit message buffer, more than one transmit request may be pending when the CAN module is able to get access to the CAN bus. The CAN module automatically detects the pending transmit request with the highest priority, which is evaluated by specific rules, and processes the transmission.

# 2.8 Memory and Register Layout

| Figure 2-2: | Register Address Layout |

|-------------|-------------------------|

|-------------|-------------------------|

| 07FH | CAN Module Register           |

|------|-------------------------------|

| 040H | (for both RXONLY and DIAG)    |

| 03FH |                               |

|      | Global Macro Control Register |

| 000H |                               |

Macro initialisation is defined as the software processes, which are necessary to use the DAFCAN macro after a RESET (i.e. system reset generated with the RESET pin of the microcomputer system).

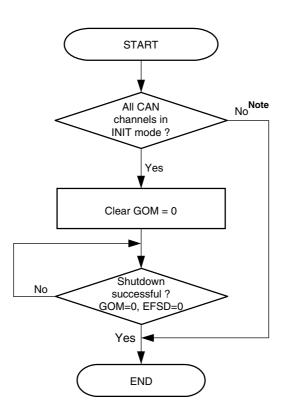

Global DAFCAN macro switch-off by software is performed by clearing the GOM bit (0).

After those 2 transitions the global macro is disabled. The CPU can check the status of the global macro by reading the GOM bit in the CnGMCTRL register.

SW write: EFSD =0 Global Macro is enabled (GOM = 1; EFSD = 1) SW write: GOM =0 SW write: EFSD =1 interim state Global Macro is Global Macro is enabled enabled (GOM = 0;)(GOM = 1;EFSD = 1) EFSD = 0SW write: GOM=1 HW transition Global Macro is SW write: GOM = 0 disabled AND (GOM = 0; (in all CAN EFSD = 0)modules OPMODE = 00H) Release RESET RESET

Figure 3-1: State Transitions of Global Macro Switching

# 3.1 Global Macro Initialisation and Control

# 3.1.1 Global Macro Disabled (GOM=0)

The global macro is disabled after a RESET or a global DAFCAN macro switch-off by software. The CPU can check the status of the macro by reading the GOM bit in the CnGMCTRL register.

Characteristic of global macro disabled (GOM=0):

- CAN I/F channel output signal CANnTX is fixed to recessive level (logical 1)

- Read and write access to the global macro registers CnGMCTRL, CnGMCS, CnGMABT, CnGMABTD is possible.

- No read access and no write access to the message buffers.

- CAN modules are disabled.

- No write access to the CAN module register (CnMASK1L, CnMASK1H, CnMASK2L, CnMASK2H, CnMASK3L, CnMASK3H, CnMASK4L, CnMASK4H, CnCTRL, CnLEC CnINFO, CnERC, CnIE, CnBRP, CnBTR, CnLIPT, CnRGPT, CnLOPT, CnTGPT, CnTS, CnCTRL\_R, CnLEC\_R, CnERC\_R, CnIE\_R, CnINTS\_R, CnBRP\_R, CnBTR\_R, CnLIPT\_R, CnBSEL\_R). Accidental write accesses to those registers are ignored by the hardware.

# 3.1.2 Initialisations before Enabling the Global Macro

The application software has to determine all settings for the macro clock  $f_{CANMOD}$  in the CnG-MCS register. The clock settings for the macro clock  $f_{CANMOD}$  must not be changed after the global macro is enabled.

# 3.1.3 Global Macro Enabled

The global macro is switched on by setting GOM bit (1) in CnGMCTRL register. Characteristics of global macro enabled (GOM=1):

- CAN I/F channels are enabled

- Both CAN modules are in INIT mode

- The CAN module register CnCTRL, CnLEC, CnINFO, CnERC, CnIE, CnINTS, CnBRP, CnBTR, CnTS, CnCTRL\_R, CnLEC\_R, CnERC\_R, CnIE\_R, CnINTS\_R, CnBRP\_R, CnBTR\_R, CnBSEL\_R contain their initial values upon switching on the global macro. The CAN module register CnLIPT, CnRGPT, CnLOPT, CnTGPT, CnLIPT\_R, CnLOPT\_R contain undefined values.

- Write access to the global macro register CnGMCS is ignored.

- Read and write access to all message buffers is possible.

- Read and write access to the CAN module registers (CnMASK1L, CnMASK1H, CnMASK2L, CnMASK2H, CnMASK3L, CnMASK3H, CnMASK4L, CnMASK4H, CnCTRL, CnLEC, CnERC, CnIE, CnINTS, CnBRP, CnBTR, CnTS, CnCTRL\_R, CnLEC\_R, CnIE\_R, CnINTS\_R, CnBRP\_R, CnBTR\_R, CnBSEL\_R) is possible. Read access to the CAN module registers CnLIPT, CnRGPT, CnLOPT, CnTGPT, CnLIPT\_R and is possible.

- The CAN module register CnTIDR0L/H, CnTIDR1L/H, CnTIDR2L/H, CnTIDR3L/H, CnTIDR4L/ H, CnTIDR5L/H, CnTIDR6L/H, CnTIDR7L/H, CnTIDML/H contain their initial values upon switching on the global macro.

# 3.1.4 Switch-Off the Global Macro

The global macro has not be switched off while one or more CAN modules are processing a message frame. A sudden interruption of a message frame transmission or reception will cause an error in other nodes connected to the same CAN bus. Before switching off the global macro the application software has to switch all CAN modules in INIT mode. Clearing the GOM bit in CnGMCTRL register will put a switch-off request to the global macro. The switch-off request is discarded in case one or more of the CAN modules are not properly set to INIT mode.

Some applications may require an immediate switch-off of the entire macro in an emergency, regardless of generating disturbance to the other nodes connected to the CAN bus. For such applications the EFSD bit in CnGMCTRL register can be set (1) to allow an immediate global macro switch-off without switching the CAN modules to a defined state (i.e. INIT mode) before-hand.

When using the 'forced shut down' function by setting EFSD bit (1) the subsequent access to the macro has to be the instruction to clear GOM bit (0). In case setting EFSD bit (1) is not directly followed by clearing GOM bit (0), the EFSD bit is cleared (0) automatically (i.e. the 'forced shut down' function is disabled). Also a read access to the CnGMCTRL register between setting of EFSD bit (1) and clearing GOM bit (0) will lead to an automatic clear (0) of EFSD bit.

**Note:** Consider to use forced shutdown procedure.

- Notes: 1. OPMODE:

- -Normal operation mode -Normal operation mode with ABT

- -Receive only mode

- -Single shot mode

- -Self test mode

- 2. Ensure that no CPU read or write access to any register happen between EFSD=1 and GOM=0.

To guarantee that also all interrupts have to be disabled.

# 3.1.5 Flowchart of the Initialisation

The following flowcharts describe the basic initialisation and in addition the re-initialisation of the CAN module. Note that the configuration for the baud rate of RXONLY\_CH should have the same configuration as the monitored CAN channel.

### Notes: 1. PSMODE for RXONLY\_CH - STOP mode

### 2. OPMODE:

-Normal operation mode

- -Normal operation mode with ABT

- -Receive only mode

- -Single shot mode

- -Self test mode

Figure 3-6: Re-initialisation of the DIAG\_CH CAN Module using TX ID Filter Function

Remark: OPMODE:

-Normal operation mode

-Normal operation mode with ABT

-Receive only mode

-Single shot mode

-Self test mode

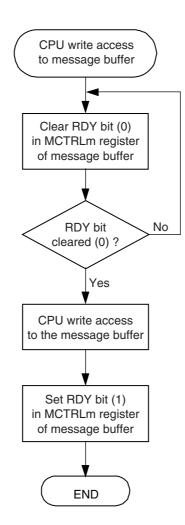

# 4.1 Message Buffer Initialisation

After a RESET or a global DAFCAN macro switch-off by software, the message buffers contain undefined values. A minimum initialisation for all message buffers, even for those not used in the application, is necessary before switching one or more CAN modules from INIT mode to one of the operational modes (refer to Figure 5-1, "Transitions for Operational Modes of the DIAG\_CH CAN module," on page 38 for details of the operational modes). The minimum initialisation has to include the proper configuration of the following bits and bit-strings in the message buffer registers MCTRLm and MCONFm to avoid unexpected behaviour of the macro in the operational modes.

| Bit        | Register | Minimum initialisation value |

|------------|----------|------------------------------|

| RDY CnMCTR |          | 0B                           |

| TRQ        | CnMCTRLm | 0B                           |

| DN         | CnMCTRLm | 0B                           |

| MA0 to MA2 | CnMCONFm | 0x000B                       |

The RDY bit in the MCTRLm register of each message buffer must be used as a semaphore to avoid access conflicts when writing to a message buffer.

# CHAPTER 4 MESSAGE BUFFER INITIALISATION AND CONFIGURATION

While RDY bit is cleared (0) the message buffer is not accessed by the assigned CAN I/F channel (CAN module and/or TTCAN module) and/or bridge module (RXONLY\_CH). Thus no message frame can be received in the message buffer or transmitted from the message buffer. Whenever the CPU wants to write into the message buffer, the RDY bit must be cleared (0).

Once the CPU has finished the write access to the message buffer it must set the RDY bit (1) to allow CAN protocol processing to the particular message buffer by the assigned CAN I/F channel.

CPU write accesses to a message buffer with RDY bit set (1) are ignored.

For the RXONLY\_CH the semaphore handling via RDY bit is identical to the rule mentioned above. However, the application is strongly advised to set all RDY bits (1) for the upper 16 message buffers in order to provide the maximum depth for the ring buffer in mirror mode. As well it is absolutely mandatory not to write to the RDY bit (clear or set the RDY bit) to any of the upper 16 message buffers while the RXONLY\_CH is operated in mirror mode or mirror mode w/ TIF. This will terminate the mirror mode or mirror mode w/ TIF or cause an erroneous sequence of monitored messages on the diagnostic CAN bus.

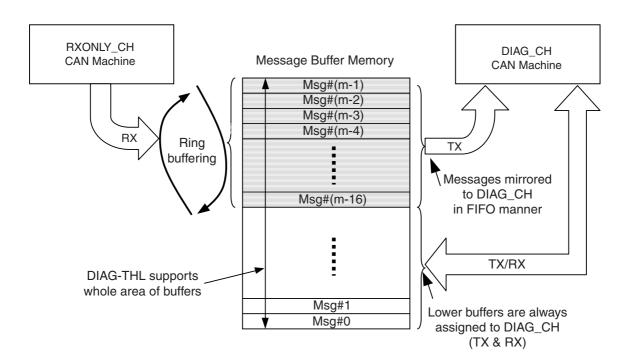

# 4.2 Message Buffer to CAN I/F Channel Assignment

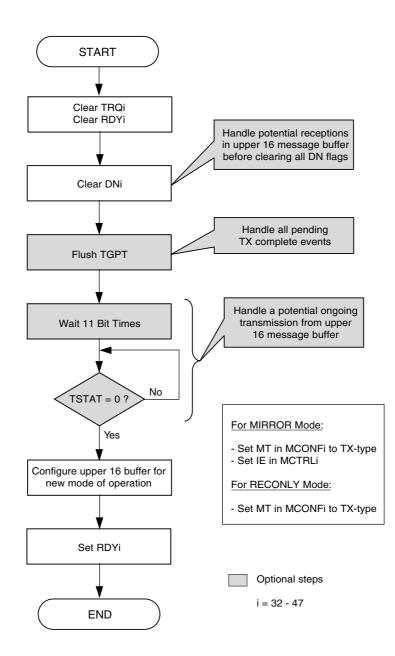

The area of upper 16 message buffers can be assigned to the DIAG\_CH or RXONLY\_CH while the rest of the message buffers is statically assigned to the DIAG\_CH as shown in the figures below.

# Figure 4-2: Operation in Mirror or Receive-only Mode of RXONLY\_CH

The assignment of the upper 16 message buffers depends on the OPMODE and PSMODE of RXONLY-CH CAN machine.

Basically, these buffers are assigned to the RXONLY\_CH while the RXONLY\_CH is operational mode (i.e. mirror mode / rec-only mode). And additionally, it must be assigned to the RXONLY\_CH while the RXONLY\_CH is in SLEEP mode because the wake-up event on the RXONLY\_CH is unpredictable. In STOP mode these buffers are assigned to the DIAG\_CH in order to provide a mode of operation where the DIAG\_CH uses all 48 buffers while the RXONLY\_CH uses minimum power. The user needs to con-

figure the upper16 message buffers before changing assignment (i.e. leaving initialisation or STOP mode of the RXONLY\_CH).

The assignment of message buffers versus operational and power-save modes is shown in the table below.

| OPMODE/<br>PSMODE | MIRROR mode | MIRROR mode<br>w/ TIF | Receive-only mode | INIT mode |

|-------------------|-------------|-----------------------|-------------------|-----------|

| NO PWR-SAVE       | RXONLY      | RXONLY                | RXONLY            |           |

| SLEEP             | RXONLY      | RXONLY                | RXONLY            | DIAG      |

| STOP              | DIAG        | DIAG                  | DIAG              |           |

| Table 4-2: | Message Buffer Assignment ve | ersus PS/OPMODE |

|------------|------------------------------|-----------------|

|            |                              |                 |

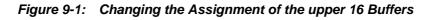

When the assignment of the upper 16 message buffers switches, the application should configure all buffers beforehand as follows.

# 4.3 Configuration before switching to Mirror Mode

For mirror mode operation all upper 16 message buffers shall be used as a ring buffer working in FIFO manner. Thus, the application has to prepare these buffers as TX-buffers beforehand as follows. Note that OWS setting is invalid (not necessary) because the non-overwriting of message buffers with DN = 1 is built in feature of operational modes of the RXONLY\_CH.

| Bit name | Configuration          |

|----------|------------------------|

| MOW      | Clear                  |

| IE       | Depends on application |

| DN       | Clear                  |

| TRQ      | Clear                  |

| MA[2:0]  | 001b                   |

| MT[2:0]  | 000b                   |

| RTR      | Don't care             |

| OWS      | Don't care             |

| IDE      | Don't care             |

| ID       | Don't care             |

| DLC      | Don't care             |

| MDATA    | Don't care             |

The flow of operations in order to change the assignment of message buffers to a CAN-channel is shown in the figure below. At first the application needs to apply RDY = 0 for the upper 16 message buffer or set the DIAG-CH into INIT mode before the new configuration can be written to the buffers.

Once the new configuration is set, the DIAG\_CH followed by RXONLY\_CH is put into its designated operational and power save mode. Finally the upper 16 message buffer are re-enabled by setting the RDY bit (1).

Figure 4-4: Set up of Mirror Mode, Mirror Mode w/ TIF or Receive-Only Mode for RXONLY\_CH

# 4.4 Configuration before switching to DIAG Side

All upper 16 message buffers can be assigned to the DIAG\_CH in order to use them as normal TX/RX message buffers by the application. It is not necessary to apply a particular configuration for these buffers before the assignment is linked again to the DIAG\_CH. However, it is recommended that the application clears RDY and TRQ bits before assigning the buffers to the DIAG\_CH or puts the DIAG\_CH into OPMODE = INIT or PSMODE = STOP before changing the assignment. Then, at least clear the RDY bits for the upper 16 message buffers before putting the DIAG\_CH to normal mode. This will ensure proper message handling during the transition.

Figure 4-5: Cancellation of Mirror Mode or Receive-Only Mode for RXONLY\_CH

When clearing the TRQ in the upper message buffer a transmission from one of these buffers may still be in process. In order to ensure correct message handling (i.e. transmission history list), it is recommended to wait for the first transmission completion interrupt of the DIAG\_CH before resuming the transition procedure.

After a RESET the registers CnGMCTRL, CnGMCS, CnGMABT, CnMASK1L, CnMASK1H, CnMASK2L, CnMASK2H, CnMASK3L, CnMASK3H, CnMASK4L, CnMASK4H, CnCTRL, CnLEC, CnINFO, CnERC, CnIE, CnINTS, CnBRP, CnBTR, CnTS, CnCTRL\_R, CnLEC\_R, CnERC\_R, CnIE\_R, CnINTS\_R, CnBRP\_R, CnBTR\_R, CnLIPT\_R, CnBSEL\_R of the CAN module in the CAN I/F channels contain their initial value.

Before switching the CAN module into an operational mode the registers (CnMASK1L, CnMASK1H, CnMASK2L, CnMASK2H, CnMASK3L, CnMASK3H, CnMASK4L, CnMASK4H, CnCTRL, CnIE, CnBRP, CnBTR, CnTS, CnCTRL\_R, CnIE\_R, CnBRP\_R, CnBTR\_R) must be initialised according the requirements of the application. Further, the CnLEC and CnLEC\_R registers must be set to its initial value (00H) and the VALID bit in the CnCTRL and CnCTRL\_R registers must be cleared (0) by the user.

## 5.1 CAN Bit Time Programming

The DIAG\_CH provides the registers CnBRP and CnBTR and the RXONLY\_CH provides CnBRP\_R and CnBTR\_R. The write access to these register has to be allowed only when the particular CAN module is in INIT mode. During an operational mode of the CAN module only reading of these registers has to be granted while the writing is blocked by hardware.

After proper setting of the CAN bit time, the CAN module can be released from INIT mode into one of its operational modes.

## 5.1.1 Transitions for Operational Modes of DIAG\_CH

The DIAG\_CH CAN machine can be switched the following operational modes:

- "Normal Operating Mode"

- "Normal Operating Mode with Automatic Block Transmission"

- "Receive-only Mode"

- "Single-shot Mode"

- "Self-test Mode"

Figure 5-1: Transitions for Operational Modes of the DIAG\_CH CAN module

The transitions from INIT mode to the operational modes is controlled by the bit-string OPMODE[2:0] in the CnCTRL register.

Changing from one operational mode into another operational mode requires to transit into INIT mode intermittently. The CAN module refuses CPU attempts to change from one operational mode into another operational mode directly.

Transition requests from the operational modes to the INIT mode are not directly accepted by the CAN module when the CAN bus is not idle (i.e. frame reception or transmission is ongoing), but it has to be kept until when the CAN module detects the first bit of intermission. As soon the above mentioned condition is detected, the transition from the operational mode to the INIT mode is executed and the bit-string OPMODE[2:0] value changes to 000B. The CPU has to confirm the proper transition into INIT mode by reading the OPMODE[2:0] bit-string until OPMODE[2:0] = 000B.

When a successful receive interrupt is detected for a specific CAN module that already entered INIT mode, this interrupt was generated by a reception process that coincided with the request of INIT mode by the CPU. The received message that caused this interrupt was still stored before INIT mode was becoming valid.

## 5.1.2 Transition for Operational Modes of RXONLY\_CH

The RXONLY-H CAN machine can be switched the following operational modes:

- "Mirror Mode"

- "Mirror Mode with Transfer ID Filter function (w/ TIF)"

- "Receive-only Mode"

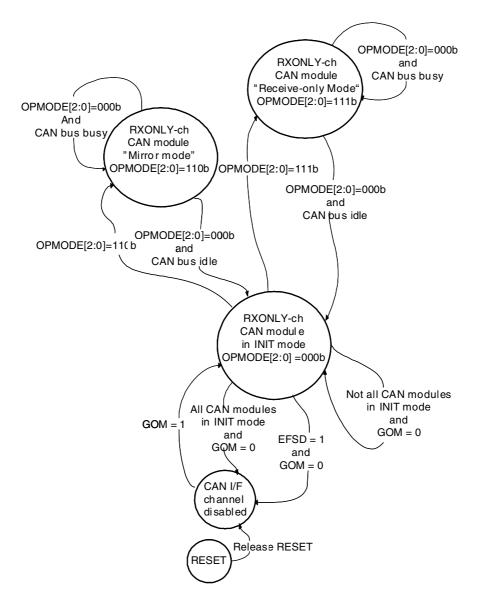

Figure 5-2: Transitions for operational modes of the RXONLY\_CH CAN module

The transitions from INIT mode to the operational modes is controlled by the bit-string OPMODE[2:0] in the CnCTRL\_R register.

The rules for changing from one to another operational mode are the same as for the DIAG\_CH.

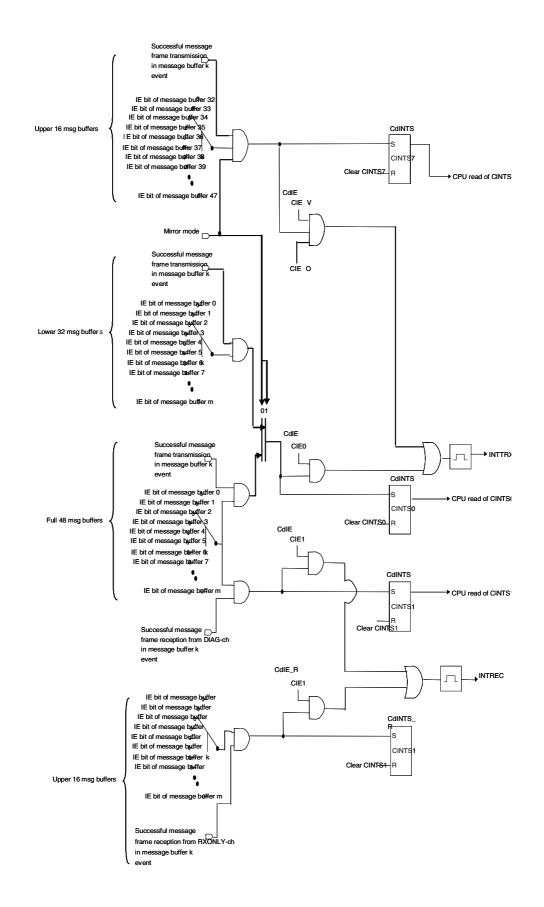

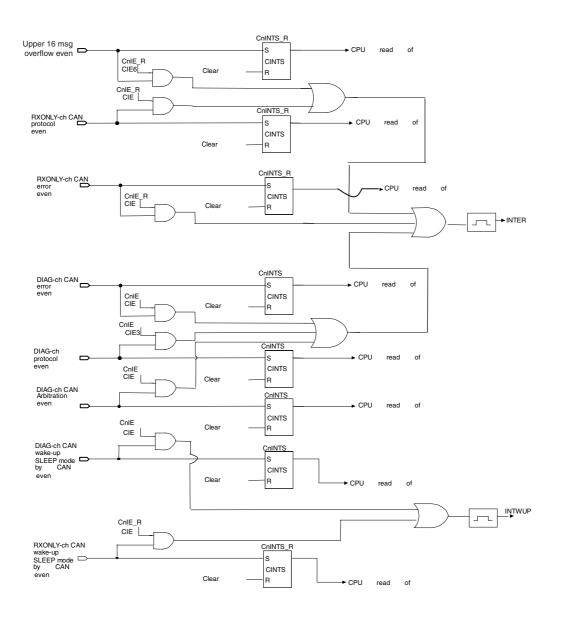

The DAFCAN macro provides 12 different interrupt source events. The occurrence of those interrupt source events is stored in interrupt status registers. Four separate interrupt request signals are generated from the 12 source events. The signals are routed to the interrupt controller in the microcomputer system. In case the interrupt controller in the microcomputer system does not provide a sufficient number of interrupt request signal inputs, the 4 interrupt request signals of a CAN module can be grouped (i.e. logical OR). With help of the interrupt status register the user can determine the actual interrupt source event for a particular interrupt. After determination of the interrupt source event the user must clear the corresponding interrupt status bit.

|    | Interrupt | Status Bit | Interrupt            | Enable Bit | Interrupt         |                                                                                                                                                                                                                                          |

|----|-----------|------------|----------------------|------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #  | Name      | Register   | Name                 | Register   | Request<br>Signal | Interrupt Source Description                                                                                                                                                                                                             |

| 1  | CINTS0    | CnINTS     | CIE0 <sup>Note</sup> | CnIE       | INTTRX            | CAN module interrupt status bit for interrupt event<br>'Message frame successfully transmitted from mes-<br>sage buffer m' by the DIAG_CH. The interrupt is also<br>provided for mirrored messages.                                      |

| 2  | CINTS1    | CnINTS     | CIE1 <sup>Note</sup> | CnIE       | INTREC            | CAN module interrupt status bit for interrupt event<br>'Valid message frame reception in message buffer m'<br>from the DIAG_CH.                                                                                                          |

| 3  | CINTS1    | CnINTS_R   | CIE1 <sup>Note</sup> | CnIE_R     |                   | CAN module interrupt status bit for interrupt event<br>'Valid message frame reception in one of the upper<br>16 message buffers from the RXONLY_CH.                                                                                      |

| 4  | CINTS2    | CnINTS     | CIE2                 | CnIE       |                   | CAN module error state interrupt status of the<br>DIAG_CH                                                                                                                                                                                |

| 5  | CINTS2    | CnINTS_R   | CIE2                 | CnIE_R     |                   | CAN module error state interrupt status of the RXONLY_CH                                                                                                                                                                                 |

| 6  | CINTS3    | CnINTS     | CIE3                 | CnIE       | INTERR            | CAN module protocol error interrupt status of the<br>DIAG_CH                                                                                                                                                                             |

| 7  | CINTS3    | CnINTS_R   | CIE3                 | CnIE_R     |                   | CAN module protocol error interrupt status of the RXONLY_CH                                                                                                                                                                              |

| 8  | CINTS4    | CnINTS     | CIE4                 | CnIE       |                   | CAN module arbitration loss interrupt status of the<br>DIAG_CH                                                                                                                                                                           |

| 9  | CINTS5    | CnINTS     | CIE5                 | CnIE       | INTWUP            | DIAG_CH CAN machine wake-up interrupt status bit<br>from SLEEP mode by CAN bus                                                                                                                                                           |

| 10 | CINTS5    | CnINTS_R   | CIE5                 | CnIE_R     |                   | RXONLY_CH CAN machine wake-up interrupt status<br>bit from SLEEP mode by CAN bus                                                                                                                                                         |

| 11 | CINTS6    | CnINTS_R   | CIE6                 | CnIE_R     | INTERR            | The buffer overflow interrupt status bit, which is set 1 when the RXONLY_CH CAN machine fails to store a message because the upper 16 message buffer are all occupied (i.e. DN <cnlipt_r +1=""> = 1).</cnlipt_r>                         |

| 12 | CINTS7    | CnINTS     | CIE7                 | CnIE       | INTTRX            | Signals a completed transmission for upper 16 mes-<br>sage buffer during Mirror Mode. The status bit and<br>CIE7 are only meaningful when RXONLY_CH is<br>operated in Mirror mode. CIE7 has no function when<br>CIE0 in CnIE is cleared. |

Table 6-1: List of all Macro Interrupt Sources

**Note:** The IE bit (message buffer interrupt enable bit) in the MCTRL register must set (1) for the message buffers, which shall participate in the interrupt generation process.

Figure 6-1: Schematic of the DAFCAN Macro Interrupt Generation (1/2)

Figure 6-1: Schematic of the DAFCAN Macro Interrupt Generation (2/2)

## 7.1 Principal Reception Process

In general all operations linked to acceptance filtering are only available on the DIAG\_CH. For the RXONLY\_CH only simple receive operations apply. These are mentioned more detailed in chapter Chapter 8 "Operational Modes of RXONLY\_CH" on page 45. The features of DIAG\_CH regarding reception are identical with those of the AFCAN macro, so these are not mentioned within this addendum.

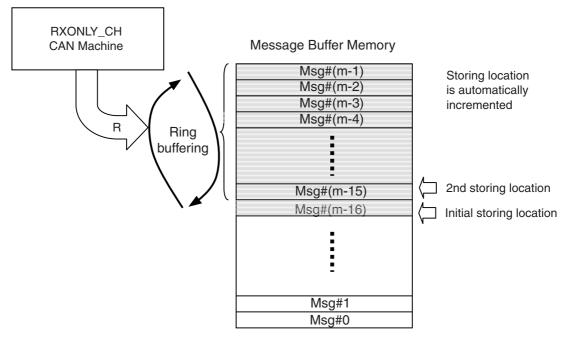

For the RXONLY\_CH the acceptance filtering is obsolete. Any valid message will be stored in the upper 16 message buffer of the DAFCAN macro when Mirror Mode, mirror mode w/ TIF or Receive-Only Mode is selected. In both modes the RXONLY\_CH will store the message in the next higher buffer number where it finds a buffer with its DN bit cleared. At buffer #47 is wraps around to buffer #32.

In Receive-Only Mode the application needs to read the messages and clear the DN bits in time to avoid the generation of the interrupt CINTS6 in CnINTS\_R.

In Mirror Mode the reception process will also set the DN bit but no receive interrupt is generated. Rather another state machine is triggered to evaluate if the TRQ of this message buffer can be set, and thus launch the transmission of the message on the DIAG\_CH. The state machine handling the setting of TRQ's for the upper 16 message buffers is activated every time the DIAG\_CH or the host CPU clears a TRQ bit. Even TRQ bits for the lower 32 message buffers need to be considered. When the state machine detects that the TRQ for the message buffer it flagged for transmission the last time was cleared, the TRQ for the next buffer is set unless the history list implies no pending entry.

As the DN bit is used by the RXONLY\_CH to detect an empty (already transmitted) buffer, the DN bit is cleared automatically after the message was transmitted successfully on the DIAG\_CH.

#### 7.2 Reception History

The RXONLY Channel does not support the Reception History List (RHL), as it is known for the standard AFCAN channels and DIAG\_CH. However, the functions of the Last-In-Message Pointer (LIPT) are implemented within the CnLIPT\_R register.

**Note:** The LIPT\_R value is maintained throughout the PSMODE = STOP for RXONLY\_CH. This register is only cleared when entering OPMODE = INIT.

Caution: The RGPT of the DAFCAN channel is not updated by the reception from the RXONLY\_CH.

### 7.3 Reception of Remote Frames

The reception of remote frames applies to both, the DIAG\_CH and the RXONLY\_CH. However, for RXONLY\_CH message storing follows different rules and acceptance filtering is not available.

A remote frame reception on the RXONLY\_CH is handled as a normal data frame reception into the upper 16 message buffers without any acceptance filtering. The message will be stored according the ring buffer method.

### 7.4 Message Transmission

As the RXONLY\_CH does only receive messages, only specific transmit operations by the DIAG\_CH that are linked to the mirror mode of the RXONLY\_CH are to be explained in chapter 8.2 on page 49. Regarding the transmission functionality of the DIAG\_CH, please refer to the standard AFCAN manual.

### 8.1 Receive–Only Mode

In Receive-only mode of the RXONLY\_CH CAN module every data and every remote frame, which is received from the CAN bus in the RXONLY\_CH CAN module without an error (i.e. valid reception), is stored in the upper 16 message buffers without any acceptance filtering.

Storing received messages from RXONLY\_CH requires the following conditions:

- The message buffer has to be assigned to the CAN I/F channel, which received the data frame (MA[2:0] bit-string in CnMCONFm register has to hold the values 001B).

- The message buffer has to be marked ready for CAN protocol processing (RDY bit set (1) in CnMCTRLm register)

- Additional condition necessary for Mirror Mode operation: The upper 16 message buffer need to be configured as transmit message buffer (MT[2:0] bit string in CnMCONFm has to hold the value 0x000B).

- Caution: In difference to a regular AFCAN channel, any message is accepted by the buffer although it is configured as a transmit message buffer that normally would not except to receive data frames. All transmit request bits of the upper 16 message buffer have to be cleared (TRQ bit reset (0) in CnMCTRLm register) especially before Mirror Mode shall be invoked. This is necessary because the setting of TRQ for the upper 16 message buffer is handled by the mirror mode machine.

The upper 16 message buffer behave as ring buffer as shown in the figure below.

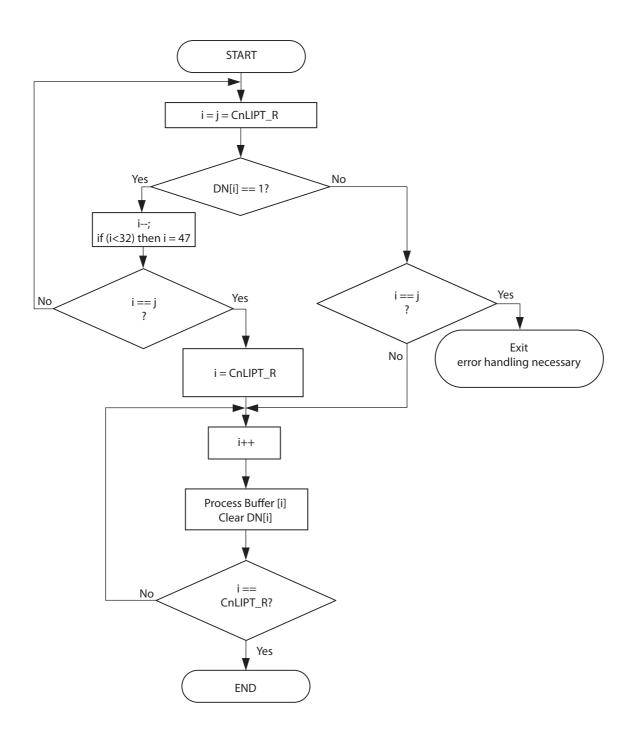

Figure 8-1: Reception Process of Receive-Only Mode

m = maximum number of message buffers = 48

The storing pointer is initialised to (m-16) at the time when switching the assignment of upper 16 message buffer.

The reception process of the RXONLY\_CH differs from the reception process of the regular AFCAN macro.

- There is no acceptance filtering; any data or remote frame will be received.

- No specific setting is required to receive standard and extended format frames in the upper 16 buffers during Receive-Only and Mirror Mode. IDE bit will be written by the RX-store machine with respect to the received frame type.

- For received remote frames the RTR bit will be set by the RX-Store machine.

The table below compares the differences for each data type of the buffer.

| Register                 | Bit String                  | DIAG /regular AFCAN                                                   | RXONLY_CH                                                                                                                                    |

|--------------------------|-----------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CnMDATAm0 –<br>CnMDATAm7 | -                           | Written by RX-Store machine<br>for remote frames value is kept        | Written by RX-Store machine                                                                                                                  |

| CnMDLCm                  | -                           | Written by RX-Store machine<br>for remote frames value is kept        | Written by RX-Store machine                                                                                                                  |

| CnMCONFm                 | OWS,<br>MT2-MT0,<br>MA2-MA0 | Set up by CPU during configuration                                    | Set up by CPU during configuration                                                                                                           |

|                          | RTR                         | Set up by CPU when preparing TX message                               | Written by RX-Store machine according received frame type                                                                                    |

| CnMIDHm/<br>CnMIDLm      | ID0-ID28                    | Written by RX-Store machine according rules of acceptance filtering   | Written by RX-Store machine as received in message                                                                                           |

| Chivilden                | IDE                         | Set up by CPU during configuration                                    | Set up at reception by RX-Store machine                                                                                                      |

|                          | MOW<br>IE                   | Set up by CPU during configuration                                    | Set up by CPU during configuration                                                                                                           |

|                          | DN                          | Set by RX-Store machine and cleared by CPU                            | Set by RX-Store machine and cleared by<br>CPU in Receive-Only mode.<br>Autonomously operated by RXONLY_CH<br>in Mirror mode                  |

| CnMCTRLm                 | TRQ                         | Set by CPU<br>(in ABT mode TRQ is set by ABT-<br>engine autonomously) | Set by RXONLY_CH when operated in<br>Mirror Mode                                                                                             |

|                          | RDY                         | Set/cleared by CPU                                                    | Cleared by CPU before RXONLY_CH is<br>put to Receive-Only or Mirror mode.<br>Then set again by CPU in order to ena-<br>ble storing messages. |

Table 8-1:

Differences in Reception Process between regular AFCAN and RXONLY\_CH

The transition into Receive-only mode is described in chapter 5.1.2 "Transition for Operational Modes of RXONLY\_CH" on page 40.

### 8.1.1 Processing received Frames in Receive-Only Mode of RXONLY\_CH

When the RXONLY\_CH is operated in Receive-Only mode, all valid messages are stored in the upper 16 message buffer. At initial start of that operating mode (i.e. when leaving INIT), the first message is stored in buffer 32. When resuming Receive-Only mode leaving SLEEP mode, the storage will resume from the last position (message buffer) reached previously. If the user has set the option to get an interrupt, a receive interrupt is signalled to the host CPU.

The CPU can identify the most recently stored message with the help of the CnLIPT\_R register. In case the CPU chooses to randomly poll the upper 16 message buffer for new messages and more than 1 message has its DN flag set, the sequence of their reception can be retrieved by a special algorithm.

In that case the CPU reads the CnLIPT\_R register and decrements the message buffer number by one. Then CPU checks if the DN flag of that buffer is set. If not set, the buffer with the oldest message was one position ahead (in reverse direction of the CPU search).

If the DN flag is set the CPU repeats decrementing the buffer number with wrap around from buffer number 32 to 47 until it encounters a DN flag that is not set or until it reaches the buffer number that equals CnLIPT\_R +1. In that case the CPU reads CnLIPT\_R again in order to find out if newly received messages have been stored while the CPU was searching for the oldest message.

Then, this secondly read value incremented by one points to the oldest message.

The CPU needs to clear the DN flag after processing the received messages in order to avoid an overflow situation, which generates an error interrupt. In case this interrupt occurs, the host CPU can directly start processing messages at buffer CnLIPT\_R+1, because the RXONLY\_CH does not overwrite any buffer with DN=1. Once the CPU has cleared the DN flag of buffer CnLIPT\_R+1, the RXONLY\_CH will resume storing received messages. Clearing DN flags at other locations beforehand, will not let the reception process resume because the RXONLY\_CH always stores messages in ascending order starting at CnLIPT\_R+1.

The flow chart below illustrates the necessary algorithms for the software.

Figure 8-2: Receive Operation for RXONLY\_CH in Receive-Only Mode

The exit that requires error handling is normally not encountered. In that case the application would process a receive interrupt but did not find any newly received message. Typically, the application has failed to clear the interrupt pending bit in a previous interrupt routine.

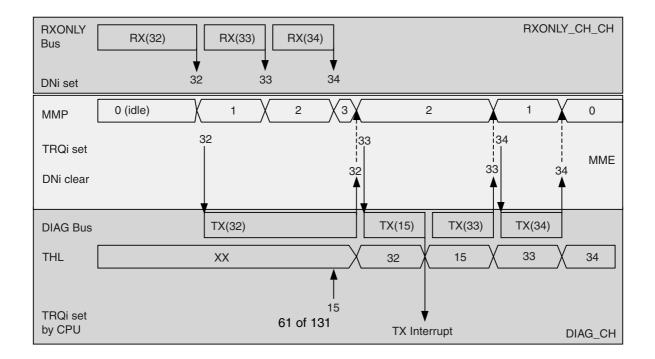

### 8.2 Mirror Mode

The DAFCAN macro features a message mirroring function. It automatically copies messages from the RXONLY\_CH to the bus served by the DIAG\_CH. When this function, the mirror mode, is enabled, any valid data frame and any valid remote frame received by the RXONLY\_CH will be stored in the upper 16 message buffers in the same manner as in Receive-Only mode. From that location these messages are automatically transmitted by the DIAG\_CH in FIFO manner. No acceptance filtering is applied to the frame receptions.

The message mirroring is activated when the DAFCAN macro is configured as the follows:

- The OPMODE of RXONLY\_CH CAN machine is configured as "Mirror mode".

- The OPMODE of DIAG\_CH CAN machine is configured as either "Normal operation mode" or "Normal operation mode with ABT"

- Neither of the CAN machines are in power save mode.