# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# AS17071

# **DEVICE FILE**

Version V1

PC-9800 Series (MS-DOS<sup>™</sup>) Base IBM PC/AT<sup>™</sup> (PC DOS<sup>™</sup>) Base

> Target Device: µPD17071 µPD17072 µPD17073

> > Document No. U11116EJ3V0UM00 (3rd edition) (Previous No. EEU--1512) Date Published April 1996 P Printed in Japan

SIMPLEHOST is a registered trademark of NEC Corporation. MS-DOS is a trademark of Microsoft Corporation. PC DOS and PC/AT are trademarks of IBM Corporation.

The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or of others.

# Major Revised Points in this Publication

| Page                | Contents                                                           |  |  |  |

|---------------------|--------------------------------------------------------------------|--|--|--|

| Throughout          | A description of the µPD17071 device files has been added.         |  |  |  |

| Cover, Introduction | AS17073 has been deleted.                                          |  |  |  |

|                     | The product name has been changed from AS17072 to AS17071.         |  |  |  |

| Introduction        | The explanation has been changed:                                  |  |  |  |

|                     | The $\mu$ PD17072 and 17073 device files have been included in the |  |  |  |

|                     | AS17071.                                                           |  |  |  |

The mark **★** shows major revised points.

.

#### Introduction

Device files are files those contain data (device data) that is unique to and dependent upon the 17K Series devices. This data is required when using the following 17K Series software development tools.

- · AS17K assembler or RA17K assembler package (under development)

- SIMPLEHOST<sup>®</sup>

The following device files are included in the AS17071.

- μPD17071 device file

- μPD17072 device file

- μPD17073 device file

The device files have the file extension .DEV.

#### [Files Included in the AS17071]

| File names                            |  |

|---------------------------------------|--|

| D17071 .DEV, D17072 .DEV, D17073 .DEV |  |

For details of the AS17K assembler and the use of device files bundled with the  $\mu$ PD17071, 17072 and AS17073, see the AS17K Assembler User's Manual (EEU-1287).

[MEMO]

## CONTENTS

| CHAPTE | ER 1 DEVICE DATA                                  | 1   |

|--------|---------------------------------------------------|-----|

| CHAPTE | ER 2 INSTRUCTION SET                              | 3   |

| 2.1    | Instruction Set Summary                           | 3   |

| 2,2    | Legend                                            | - 4 |

| 2.3    | Legend                                            | 5   |

| 2.4    | Macro Instructions Bundled with Assembler (AS17K) | 7   |

| СНАРТИ | ER 3 RESERVED SYMBOLS                             | 9   |

| 3.1    | Data Buffer (DBF)                                 | 10  |

| 3.2    | System Register (SYSREG)                          | 10  |

| 3.3    | LCD Segment Register                              | 10  |

| 3.4    | Port Register                                     | 11  |

| 3.5    | Peripheral Control Register                       | 12  |

| 3.6    | Peripheral Hardware Register                      | 16  |

| 3.7    | Other                                             | 16  |

|        | List of Reserved Words (in Alphabetical Order)    | 17  |

| 0.0    | 3.8.1 Instructions and pseudo-instructions        | 17  |

|        | 3.8.2 Registers and flags                         | 19  |

|        |                                                   |     |

| CHAPTI | ER 4 LOAD MODULE FILE FORMAT                      | 23  |

# [MEMO]

#### CHAPTER 1 DEVICE DATA

In assembly time, the device files provide the following data related to the device.

- (1) Program memory (ROM) capacity μPD17071: 2048 × 16 bits (0000H - 07FFH) μPD17072: 3072 × 16 bits (0000H - 08FFH) μPD17073: 4096 × 16 bits (0000H - 0FFFH)

- (2) Data memory (RAM) capacity μPD17071: 128 × 4 bits (BANK0, BANK1) μPD17072, 17073: 176 × 4 bits (BANK0, BANK1)

- (3) Usable instructions See CHAPTER 2 INSTRUCTION SET.

- (4) Peripheral control registers, port register, and peripheral hardware register read and write data See CHAPTER 3 RESERVED SYMBOLS.

- (5) Reserved symbols See CHAPTER 3 RESERVED SYMBOLS.

#### (6) Device files, device numbers, and SE board numbers

Device files contain a register of device numbers for each device and SE board numbers to indicate optimum SE boards for developing various products. These device files are also included in ICE files and PRO files output by the assembler (AS17K). These devices are used when the in-circuit emulator checks the development environment and during checking of mask orders.

| Device file (version) | Device name | Device number | SE board number | SE board |

|-----------------------|-------------|---------------|-----------------|----------|

|                       | PD17071 μ   | 58H           |                 |          |

| AS17071 (V1)          | μPD17072    | 4CH           | 4CH             | SE-17072 |

|                       | μPD17073    | 4FH           |                 |          |

#### Table 1-1. Relations among Device Files, Device Numbers, and SE Board Numbers

÷

# [MEMO]

· ·

• ...

• • • •

.

2

### CHAPTER 2 INSTRUCTION SET

# 2.1 Instruction Set Summary

| $\square$ | D15 |                                                                                                                           |                                                                        |      |                |

|-----------|-----|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|----------------|

| b14 - b11 |     |                                                                                                                           | 0                                                                      |      | 1              |

| BIN       | HEX |                                                                                                                           |                                                                        |      |                |

| 0000      | 0   | ADD                                                                                                                       | r, m                                                                   | ADD  | m, #n4         |

| 0001      | 1   | SUB                                                                                                                       | r, m                                                                   | SUB  | m, #n4         |

| 0010      | 2   | ADDC                                                                                                                      | r, m                                                                   | ADDC | m, #n4         |

| 0011      | 3   | SUBC                                                                                                                      | r, m                                                                   | SUBC | m, #n4         |

| 0100      | 4   | AND                                                                                                                       | r, m                                                                   | AND  | m, #n4         |

| 0101      | 5   | XOR                                                                                                                       | r, m                                                                   | XOR  | m, #n4         |

| 0110      | 6   | OR                                                                                                                        | r, m                                                                   | OR   | <b>m</b> , #n4 |

| 0111      | 7   | INC<br>RORC<br>MOVT<br>PUSH<br>POP<br>GET<br>PUT<br>BR<br>CALL<br>RET<br>RETSK<br>RETI<br>EI<br>DI<br>STOP<br>HALT<br>NOP | AR<br>r<br>DBF, @AR<br>AR<br>DBF, p<br>p, DBF<br>@AR<br>@AR<br>\$<br>h |      |                |

| 1000      | 8   | LD                                                                                                                        | r,m                                                                    | ST   | m, r           |

| 1001      | 9   | SKE                                                                                                                       | m, #n4                                                                 | SKGE | m, #n4         |

| 1010      | A   | MOV                                                                                                                       | @r,m                                                                   | MOV  | m, @r          |

| 1011      | В   | SKNE                                                                                                                      | m, #n4                                                                 | SKLT | m, #n4         |

| 1100      | С   | BR                                                                                                                        | addr (page 0)                                                          | CALL | addr           |

| 1101      | D   | BR                                                                                                                        | addr (page 1)                                                          | MOV  | m, #n4         |

| 1110      | E   |                                                                                                                           |                                                                        | SKT  | m, #n          |

| 1111      | F   |                                                                                                                           |                                                                        | SKF  | m, #n          |

# 2.2 Legend

| AR :    | Address register                                                         |

|---------|--------------------------------------------------------------------------|

| ASR :   | Address stack register indicated by stack pointers                       |

| addr :  | Program memory address (lower 11 bits)                                   |

| BANK :  | Bank register                                                            |

| CMP :   | Compare flag                                                             |

| CY :    | Carry flag                                                               |

| DBF :   | Data buffer                                                              |

| h :     | Halt cancellation conditions                                             |

| INTEF : | Interrupt enable flag                                                    |

| INTR :  | Register that is automatically saved to a stack when an interrupt occurs |

| INTSK : | Interrupt stack register                                                 |

| MP :    | Data memory row address pointer                                          |

| MPE:    | Memory pointer enable flag                                               |

| m :     | Data memory address indicated by mn and mc                               |

| MB :    | Data memory row address (high)                                           |

| mc :    | Data memory column address (low)                                         |

| n :     | Bit position (4 bits)                                                    |

| n4 :    | Immediate data (4 bits)                                                  |

| PAGE :  | Page (Bit 11 of program counter)                                         |

| PC :    | Program counter                                                          |

| р :     | Peripheral address                                                       |

| рн :    | Peripheral address (higher 3 bits)                                       |

| р. :    | Peripheral address (lower 4 bits)                                        |

|         | General register column address                                          |

|         | Stack pointer                                                            |

| s :     | Stop cancellation conditions                                             |

| (x) :   | × indicates addressed contents                                           |

|         |                                                                          |

# 2.3 Instruction List

| Instruction set | Mnemonic | Operand                                             | Operation                                                                                                                                 | I       | nstructio   | on code |      |

|-----------------|----------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|---------|------|

|                 |          |                                                     |                                                                                                                                           | Op code |             | Operand | ł    |

| Add             | ADD      | r, m                                                | (r) ← (r) + (m)                                                                                                                           | 00000   | ma          | mc      | r    |

|                 |          | m, #n4                                              | (m) ← (m) + n4                                                                                                                            | 10000   | Шя          | ma      | n4   |

|                 | ADDC     | r, m                                                | $(r) \leftarrow (r) + (m) + CY$                                                                                                           | 00010   | Шя          | mc      | r    |

|                 |          | m, #n4                                              | (m) ← (m) + n4 + CY                                                                                                                       | 10010   | ШR          | me      | n4   |

|                 | INC      | AR                                                  | AR ← AR + 1                                                                                                                               | 00111   | 000         | 1001    | 000  |

| Subtract        | SUB      | r, m                                                | $(r) \leftarrow (r) - (m)$                                                                                                                | 00001   | mв          | ma      | г    |

|                 |          | m, #n4                                              | (m) ← (m) - n4                                                                                                                            | 10001   | mв          | тc      | n4   |

|                 | SUBC     | r, m                                                | $(r) \leftarrow (r) - (m) - CY$                                                                                                           | 00011   | <b>m</b> a  | mc      | r    |

|                 |          | m, #n4                                              | (m) ← (m) - n4 - CY                                                                                                                       | 10011   | ma          | mc      | n4   |

| Logical         | OR       | r, m                                                | $(r) \leftarrow (r) \lor (m)$                                                                                                             | 00110   | ma          | mc      | 7    |

| operation       |          | m, #n4                                              | (m) ← (m) ∨ n4                                                                                                                            | 10110   | ma          | mc      | n4   |

|                 | AND      | <i>r</i> , m                                        | $(r) \leftarrow (r) \land (m)$                                                                                                            | 00100   | me          | mc      | r    |

|                 |          | m, #n4                                              | (m) ← (m) ∧ n4                                                                                                                            | 10100   | me          | mc      | n4   |

|                 | XOR      | r, m                                                | $(r) \leftarrow (r) \forall (m)$                                                                                                          | 00101   | ជាខ         | m¢      | r    |

|                 |          | m, #n4                                              | (m) ← (m) ∀ n4                                                                                                                            | 10101   | #1R         | ma      | л4   |

|                 |          | m, #n                                               | CMP $\leftarrow$ 0, if (m) $\land$ n = n, then skip                                                                                       | 11110   | Μя          | mc      | n    |

|                 |          | CMP $\leftarrow$ 0, if (m) $\land$ n = 0, then skip | 11111                                                                                                                                     | MA      | ma          | n       |      |

| Comparison      | SKE      | m, #n4                                              | (m) – n4, skip if zero                                                                                                                    | 01001   | ШR          | mc      | n4   |

|                 | SKNE     | m, #n4                                              | (m) – n4, skip if not zero                                                                                                                | 01011   | ma          | me      | n4   |

|                 | SKGE     | m, #n4                                              | (m) – n4, skip if not borrow                                                                                                              | 11001   | ma          | ma      | n4   |

|                 | SKLT     | m, #n4                                              | (m) – n4, skip if borrow                                                                                                                  | 11011   | ma          | mc      | n4   |

| Rotation        | RORC     | ſ                                                   | $ CY \rightarrow (r) \ {}_{b3} \rightarrow (r) \ {}_{b2} \rightarrow (r) \ {}_{b1} \rightarrow (r) \ {}_{b0}$                             | 00111   | 000         | 0111    | r    |

| Transfer        | LD       | r, m                                                | (r) ← (m)                                                                                                                                 | 01000   | <b>FTIR</b> | mc      | r    |

|                 | ST       | m, r                                                | (m) ← (r)                                                                                                                                 | 11000   | mв          | mc      | r    |

|                 | MOV      | @r, m                                               | if MPE = 1 : (MP, (r)) $\leftarrow$ (m)<br>if MPE = 0 : (BANK, ma, (r)) $\leftarrow$ (m)                                                  | 01010   | ma          | mc      | r    |

|                 |          | m, @r                                               | íf MPE = 1 : (m) ← (MP, (r))<br>if MPE = 0 : (m) ← (BANK, ma, (r))                                                                        | 11010   | ma          | ma      | ¢    |

|                 |          | m, #n4                                              | (m) ← n4                                                                                                                                  | 11101   | <b>M</b> R  | ma      | n4   |

|                 | MOVT     | DBF, @AR                                            | $SP \leftarrow SP-1$ , $ASR \leftarrow PC$ , $PC \leftarrow AR$ ,<br>$DBF \leftarrow (PC)$ , $PC \leftarrow ASR$ , $SP \leftarrow SP + 1$ | 00111   | 000         | 0001    | 000  |

|                 | PUSH     | AR                                                  | $SP \leftarrow SP - 1$ , $ASR \leftarrow AR$                                                                                              | 00111   | 000         | 1101    | 0000 |

|                 | POP      | AR                                                  | $AR \leftarrow ASR, SP \leftarrow SP + 1$                                                                                                 | 00111   | 000         | 1100    | 000  |

|                 | GET      | DBF, p                                              | D8F ← (p)                                                                                                                                 | 00111   | рн          | 1011    | p.   |

|                 | PUT      | p, DBF                                              | (p) ← DBF                                                                                                                                 | 00111   | рн          | 1010    | p.   |

| Instruction set | Mnemonic Operand | Ongrand | Operation                                                                                            | Instruction code |     |         |      |

|-----------------|------------------|---------|------------------------------------------------------------------------------------------------------|------------------|-----|---------|------|

| manucaon set    |                  | Operand | Operation                                                                                            | Op code          |     | Operand | I    |

| Branch          | 88               | addr    | Note                                                                                                 | Note             |     | addr    |      |

|                 |                  | @AR     | PC ← AR                                                                                              | 00111            | 000 | 0100    | 0000 |

| Subroutine      | CALL             | addr    | $SP \leftarrow SP - 1$ , $ASR \leftarrow PC$<br>$PC_{11} \leftarrow 0$ , $PC_{10:0} \leftarrow addr$ | 11100            |     | addr    |      |

|                 |                  | @AR     | $SP \leftarrow SP \rightarrow 1$ , $ASR \leftarrow PC$<br>$PC \leftarrow AR$                         | 00111            | 000 | 0101    | 0000 |

|                 | RET              |         | $PC \leftarrow ASR, SP \leftarrow SP + 1$                                                            | 00111            | 000 | 1110    | 0000 |

|                 | RETSK            |         | PC ← ASR, SP ← SP + 1 and skip                                                                       | 00111            | 001 | 1110    | 0000 |

|                 | RETI             |         | $PC \leftarrow ASR, INTR \leftarrow INTSK, SP \leftarrow SP + 1$                                     | 00111            | 010 | 1110    | 0000 |

|                 | El               |         | INTEF - 1                                                                                            | 00111            | 001 | 1111    | 0000 |

| Interrupt       | DI               |         | INTEF - 0                                                                                            | 00111            | 001 | 1111    | 0000 |

|                 | STOP             | s       | STOP                                                                                                 | 00111            | 010 | 1111    | S    |

| Olher           | HALT             | h       | HALT                                                                                                 | 00111            | 011 | 1111    | h    |

|                 | NOP              |         | No operation                                                                                         | 00111            | 100 | 1111    | 0000 |

Note The "BR addr" operation of the µPD17071, 17072 and 17073 and its op codes are as follows:

#### (a) μPD17071

| 1 | Mnemonic | Operand | Operation     | Op Code |

|---|----------|---------|---------------|---------|

|   | 8R       | addr    | PC10-0 ← addr | 01100   |

# (b) µPD17072, 17073

| Mnemonic | Operand | Operation               | Op Code |

|----------|---------|-------------------------|---------|

| BR       | addr    | PC10-0 ← addr, PAGE ← 0 | 01100   |

| 5.1      |         | PC10-0 ← addr, PAGE ← 1 | 01101   |

# 2.4 Macro Instructions Bundled with Assembler (AS17K)

#### Legend

flag n : FLG-type symbol

```

n : Bit No.

```

<> : Contents between <> symbols can be omitted.

| Instruction set | Mnemonic | Operand                                                | Operation                                                                                                          | n         |

|-----------------|----------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------|

| Bundled         | SKTn     | flag 1, flag n                                         | if (flag 1) to (flag n) = all "1", then skip                                                                       | 1 ≤ n ≤ 4 |

| macros          | SKFn     | flag 1, flag n                                         | if (flag 1) to (flag n) = all "0", then skip                                                                       | 1 ≤ n ≤ 4 |

|                 | SETn     | flag 1, flag n                                         | (flag 1) to (flag n) ← 1                                                                                           | 1 ≤ n ≤ 4 |

|                 | CLRn     | flag 1, ··· flag n                                     | (flag 1) to (flag n) ← 0                                                                                           | 1 ≤ n ≤ 4 |

|                 | NOTn     | flag 1, … flag n                                       | if (flag n) = "0", then (flag n) $\leftarrow 1$<br>if (flag n) = "1", then (flag n) $\leftarrow 0$                 | 1 ≤ n ≤ 4 |

|                 | INTFLG   | <not> flag 1,<br/>··· &lt;<not> flag n&gt;</not></not> | if description = NOT flag n, then (flag n) $\leftarrow 0$<br>if description = flag n, then (flag n) $\leftarrow 1$ | 1 ≤ n ≤ 4 |

|                 | BANKa    |                                                        | (BANK) ← n                                                                                                         | n ≃ 0, 1  |

[MEMO]

## CHAPTER 3 RESERVED SYMBOLS

The symbols defined for the  $\mu$ PD17071, 17072 and 17073 device files are described on the following pages. These symbols are listed below.

- Data buffer (DBF)

- System register (SYSREG)

- LCD segment register

- Port register

- · Peripheral control register

- · Peripheral hardware register

- Other

# 3.1 Data Buffer (DBF)

| Symbol name | Attribute | Value | R/W | Description         |

|-------------|-----------|-------|-----|---------------------|

| DBF3        | MEM       | 0.0CH | R/W | DBF bits b15 to b12 |

| DBF2        | MEM       | 0.0DH | R/W | DBF bits b11 to b8  |

| DBF1        | MEM       | 0.0EH | R/W | DBF bits b7 to b4   |

| DBF0        | MEM       | 0.0FH | R/W | DBF bits b3 to b0   |

# 3.2 System Register (SYSREG)

| Symbol name | Attribute | Value   | R/W | Description                     |

|-------------|-----------|---------|-----|---------------------------------|

| AR2         | MEM       | 0.75H   | R/W | Address register bits b11 to b8 |

| AR1         | MEM       | 0.76H   | R/W | Address register bits b7 to b4  |

| ARO         | MEM       | 0.77H   | R/W | Address register bits b3 to b0  |

| BANK        | MEM       | 0.79H   | R/W | Bank register                   |

| BCD         | FLG       | 0.7EH.0 | R/W | BCD flag                        |

| PSW         | MEM       | 0.7FH   | R/W | Program status word             |

| CMP         | FLG       | 0.7FH.3 | R/W | Compare Ilag                    |

| CY          | FLG       | 0.7FH.2 | R/W | Carry flag                      |

| Z           | FLG       | 0.7FH.1 | R/W | Zero flag                       |

# 3.3 LCD Segment Register

| Symbol name | Attribute | Value | R/W | Description          |

|-------------|-----------|-------|-----|----------------------|

| LCDD14      | MEM       | 1,41H | R/W | LCD segment register |

| LCDD13      | MEM       | 1.42H | R/W | LCD segment register |

| LCDD12      | MEM       | 1.43H | R/W | LCD segment register |

| LCDD11      | MEM       | 1.44H | R/W | LCD segment register |

| LCDD10      | MEM       | 1.45H | R/W | LCD segment register |

| LCDD9       | MEM       | 1.46H | R/W | LCD segment register |

| LCDD8       | MEM       | 1.47H | R/W | LCD segment register |

| LCDD7       | MEM       | 1.48H | R/W | LCD segment register |

| LCDD6       | MEM       | 1.49H | R/W | LCD segment register |

| LCDD5       | МЕМ       | 1.4AH | R/W | LCD segment register |

| LCDD4       | MEM       | 1.4BH | R/W | LCD segment register |

| LCDD3       | MEM       | 1.4CH | 8/W | LCD segment register |

| LCDD2       | MEM       | 1.4DH | R/W | LCD segment register |

| LCDD1       | MEM       | 1.4EH | R/W | LCD segment register |

| LCDDO       | MEM       | 1.4FH | R/W | LCD segment register |

#### 3.4 Port Register

| Symbol name | Attribute | Value   | R/W                 | Description    |

|-------------|-----------|---------|---------------------|----------------|

| P0A3        | FLG       | 0.70H.3 | R/W                 | Port 0A bit b3 |

| P0A2        | FLG       | 0.70H.2 | R/W                 | Port 0A bit b2 |

| P0A1        | FLG       | 0.70H.1 | R/W                 | Port 0A bit b1 |

| POAO        | FLG       | 0.70H.0 | R/W                 | Port 0A bit b0 |

| P0B3        | FLG       | 0.71H.3 | R/W                 | Port 0B bit b3 |

| P0B2        | FLG       | 0.71H.2 | R/W                 | Port 0B bit b2 |

| P0B1        | FLG       | 0.71H.1 | R/W                 | Port 0B bit b1 |

| P0B0        | FLG       | 0.71H.0 | R/W                 | Port 0B bit b0 |

| P0C1        | FLG       | 0.72H.1 | R/W                 | Port 0C bit 1  |

| P0C0        | FLG       | 0.72H.0 | R/W                 | Port 0C bit 0  |

| P0D3        | FLG       | 0.73H.3 | R/W                 | Port 0D bit 3  |

| P0D2        | FLG       | 0.73H.2 | R/W                 | Port 0D bit 2  |

| P1A3        | FLG       | 1.70H.3 | R/W <sup>Note</sup> | Port 1A bit 3  |

| P1A2        | FLG       | 1.70H.2 | R/W <sup>Note</sup> | Port 1A bit 2  |

| P1A1        | FLG       | 1.70H.1 | R/W <sup>Note</sup> | Port 1A bit 1  |

| P1A0        | FLG       | 1.70H.0 | R/W <sup>Note</sup> | Port 1A bit 0  |

| P1B3        | FLG       | 1.71H.3 | R/W                 | Port 1B bit 3  |

| P1B2        | FLG       | 1.71H,2 | R/W                 | Port 1B bit 2  |

| P1B1        | FLG       | 1.71H.1 | R/W                 | Port 1B bit 1  |

| P1B0        | FLG       | 1.71H.0 | R/W                 | Port 1B bit 0  |

| P1C0        | FLG       | 1.72H.0 | R/W                 | Port 1C bit 0  |

Note These ports are input-only ports. The assembler and IE-17K will not output error messages if an instruction to output from these ports has been entered. Also, if the messages are actually executed on a device, the operation will have no change.

# 3.5 Peripheral Control Register

# \* (1) μPD17071

| Symbol name | Attribute | Value   | R/W     | Description                                                |

|-------------|-----------|---------|---------|------------------------------------------------------------|

| LCDEN       | FLG       | 1.50H.0 | R/W     | LCD driver display start flag                              |

| BTMOCY      | FLG       | 1.51H.0 | R & Res | Basic timer zero carry-FF status detection flag            |

| CE          | FLG       | 1.52H.0 | R       | CE pin status detection flag                               |

| P1APLD3     | FLG       | 1.53H.3 | R/W     | P1A <sub>3</sub> /AD1 pin's pull-down resistor select flag |

| P1APLD2     | FLG       | 1.53H.2 | R/W     | P1A2/AD0 pin's pull-down resistor select flag              |

| P1APLD1     | FLG       | 1.53H.1 | R/W     | P1At pin's pull-down resistor select flag                  |

| P1APLD0     | FLG       | 1.53H.0 | R/W     | P1As pin's pull-down resistor select flag                  |

| SP          | MEM       | 1.54H   | R/W     | Stack pointer                                              |

| BTM1CKD     | FLG       | 1.59H.0 | R       | Basic timer 1 clock detection flag                         |

| BEEP0CK1    | FLG       | 1.5BH.1 | R/W     | BEEP clock select flag                                     |

| BEEPOCK0    | FLG       | 1.5BH.0 | R/W     | BEEP clock select flag                                     |

| IFCMD1      | FLG       | 1.62H.3 | R/W     | IF counter mode select flag                                |

| IFCMD0      | FLG       | 1.62H.2 | R/W     | IF counter mode select flag                                |

| IFCCK1      | FLG       | 1.62H.1 | R/W     | IF counter clock select flag                               |

| IFCCK0      | FLG       | 1.62H.0 | R/W     | IF counter clock select flag                               |

| IFCG        | FLG       | 1.63H.0 | R       | IF counter gate status detection flag (0: closed, 1: open) |

| IFCSTRT     | FLG       | 1.64H.1 | w       | IF counter count start flag                                |

| IFCRES      | FLG       | 1.64H.0 | w       | IF counter reset flag                                      |

| PLLMD3      | FLG       | 1.65H.3 | R       | PLL mode select flag (lixed to "0")                        |

| PLLMD2      | FLG       | 1.65H.2 | R       | PLL mode select flag (fixed to "0")                        |

| PLLMD1      | FLG       | 1.65H.1 | R/W     | PLL mode select flag                                       |

| PLLMD0      | FLG       | 1.65H.0 | R/W     | PLL mode select flag                                       |

| PLLRFCK3    | FLG       | 1.66H.3 | R       | PLL reference frequency select flag (fixed to "0")         |

| PLLRFCK2    | FLG       | 1.66H.2 | R/W     | PLL reference frequency select flag                        |

| PLLRFCK1    | FLG       | 1.66H.1 | R/W     | PLL reference frequency select flag                        |

| PLLRFCK0    | FLG       | 1.66H.0 | R/W     | PLL reference frequency select flag                        |

| PLLR17      | FLG       | 1.67H.3 | R/W     | PLL data flag                                              |

| PLLR16      | FLG       | 1.67원.2 | R/W     | PLL data flag                                              |

| PLLR15      | FLG       | 1.67H.1 | R/W     | PLL data flag                                              |

| PLLR14      | FLG       | 1.67H.0 | R/W     | PLL data flag                                              |

| PLLR13      | FLG       | 1.68H.3 | R/W     | PLL data ílag                                              |

| PLLR12      | FLG       | 1.68H.2 | R/W     | PLL data flag                                              |

| PLLR11      | FLG       | 1.68H.1 | R/W     | PLL data Ilag                                              |

| PLLR10      | FLG       | 1.68H.0 | R/W     | PLL data flag                                              |

| PLLR9       | FLG       | 1.69H.3 | R/W     | PLL, data ílag                                             |

| PLLR8       | FLG       | 1.69H.2 | R/W     | PLL data flag                                              |

| PLLR7       | FLG       | 1.69H.1 | R/W     | PLL data flag                                              |

| PLLR6       | FLG       | 1.69H.0 | R/W     | PLL data flag                                              |

| Symbol name | Attribute | Value   | R/W     | Description                      |

|-------------|-----------|---------|---------|----------------------------------|

| PLLR5       | FLG       | 1.6AH.3 | R/W     | PLL data flag                    |

| PLLR4       | FLG       | 1.6AH.2 | R/W     | PLL data flag                    |

| PLLR3       | FLG       | 1.6AH.1 | R/W     | PLL data flag                    |

| PLLR2       | FLG       | 1.6AH.0 | R/W     | PLL data flag                    |

| PLLR1       | FLG       | 1.6BH.3 | R/W     | PLL data flag                    |

| PLLPUT      | FLG       | 1.6CH.0 | w       | PLL data set flag                |

| PLLUL       | FLG       | 1.6DH.0 | R & Res | PLL unlock FF flag               |

| P0BBIO3     | FLG       | 1.6EH.3 | R/W     | P0Bs I/O select flag             |

| P0BBIO2     | FLG       | 1.6EH.2 | R/W     | P0B <sub>2</sub> I/O select flag |

| P0BBIO1     | FLG       | 1.6EH.1 | R/W     | P0Bi I/O select flag             |

| P0BBIO0     | FLG       | 1.6EH.0 | R/W     | P0B₀ I/O select flag             |

| P0DBIO3     | FLG       | 1.6FH.3 | R/W     | P0D <sub>3</sub> I/O select flag |

| PODBIO2     | FLG       | 1.6FH.2 | R/W     | P0Dz I/O select flag             |

| P0CBIO1     | FLG       | 1.6FH.1 | R/W     | P0Ci I/O select flag             |

| POCBIOO     | FLG       | 1.6FH.0 | R/W     | P0Co I/O select flag             |

#### (2) µPD17072, 17073

| Symbol name | Attribute | Value   | R/W     | Description                                                    |

|-------------|-----------|---------|---------|----------------------------------------------------------------|

| ADCON       | FLG       | 1.50H.1 | R/W     | Power supply setting flag for A/D converter control signal     |

| LCDEN       | FLG       | 1.50H.0 | R/W     | LCD driver enable flag                                         |

| BTMOCY      | FLG       | 1.51H.0 | R & Res | Basic timer zero carry-FF status detection flag                |

| CE          | FLG       | 1.52H.0 | R       | CE pin status detection flag                                   |

| P1APLD3     | FLG       | 1.53H.3 | R/W     | P1AJ/AD1 pin's pull-down resistor select tlag                  |

| P1APLD2     | FLG       | 1.53H.2 | R/W     | P1Az/AD0 pin's pull-down resistor select flag                  |

| P1APLD1     | FLG       | 1.53H.1 | R/W     | P1A1 pin's pull-down resistor select flag                      |

| P1APLD0     | FLG       | 1.53H.0 | R/W     | P1A₀ pin's pull-down resistor select ilag                      |

| SP          | МЕМ       | 1.54H   | R/W     | Stack pointer                                                  |

| SYSCK       | FLG       | 1.55H.0 | R/W     | System clock select flag (1: 106.6 µs, 0: 53.3 µs)             |

| INT         | FLG       | 1.56H.2 | R/W     | INT pin status detection flag                                  |

| BRM1CK      | FLG       | 1.56H.1 | R/W     | Basic timer 1 clock select flag                                |

| IEG         | FLG       | 1.56H.0 | R/W     | INT pin Interrupt request detection edge direction select flag |

| IPSIO       | FLG       | 1.57H.2 | R/W     | Serial interface interrupt enable flag                         |

| IPBTM1      | FLG       | 1.57H.1 | R/W     | Basic timer 1 interrupt enable flag                            |

| IP          | FLG       | 1.57H.0 | R/W     | INT pin interrupt enable flag                                  |

| IRQ         | FLG       | 1.58H.0 | R/W     | INT pin interrupt request detection flag                       |

| IRQBTM1     | FLG       | 1.59H.0 | R/W     | Basic timer 1 interrupt request detection flag                 |

| IRQSIO      | FLG       | 1.5AH.0 | R/W     | Serial interface interrupt request detection flag              |

| BEEPOCK1    | FLG       | 1.5BH.1 | R/W     | BEEP clock select flag                                         |

| BEEPOCKO    | FLG       | 1.58H.0 | R/W     | BEEP clock select flag                                         |

| ADCCH3      | FLG       | 1.5CH.3 | R       | A/D converter channel select flag (fixed to "0")               |

| ADCCH2      | FLG       | 1.5CH.2 | R       | A/D converter channel select flag (fixed to "0")               |

| ADCCH1      | FLG       | 1.5CH.1 | R/W     | A/D converter channel select flag                              |

| ADCCH0      | FLG       | 1.5CH.0 | R/W     | A/D converter channel select flag                              |

| ADCRFSEL3   | FLG       | 1.5DH.3 | R/W     | A/D converter reference voltage setting flag                   |

| ADCRFSEL2   | FLG       | 1.5DH.2 | R/W     | A/D converter reference voltage setting flag                   |

| ADCRFSEL1   | FLG       | 1.5DH.1 | R/W     | A/D converter reference voltage setting flag                   |

| ADCRFSEL0   | FLG       | 1.5DH.0 | R/W     | A/D converter reference voltage setting flag                   |

| ADCSTRT     | FLG       | 1.5EH.0 | R/W     | A/D converter comparison start flag                            |

| ADCCMP      | FLG       | 1.5FH.0 | R       | A/D converter comparison result detection flag                 |

| SIOSEL      | FLG       | 1.60H.2 | R/W     | Serial in/Serial out pin select flag                           |

| SIOHIZ      | FLG       | 1.60H.1 | R/W     | Serial interface/general-purpose port select flag              |

| SIOTS       | FLG       | 1.60H.0 | 8/₩     | Serial interface transmit/receive start flag                   |

| Symbol name | Attribute | Value   | R/W     | Description                                                |  |

|-------------|-----------|---------|---------|------------------------------------------------------------|--|

| SIOCK3      | FLG       | 1.61H.3 | R       | Serial interface I/O clock select flag (fixed to "0")      |  |

| SIOCK2      | FLG       | 1.61H.2 | R       | Serial interface I/O clock select flag (fixed to "0")      |  |

| SIOCK1      | FLG       | 1.61H.1 | R/W     | Serial interface I/O clock select flag                     |  |

| SIOCKO      | FLG       | 1.61H.0 | R/W     | Serial interface I/O clock select flag                     |  |

| IFCMD1      | FLG       | 1.62H.3 | R/W     | IF counter mode select flag                                |  |

| IFCMD0      | FLG       | 1.62H.2 | R/W     | IF counter mode select flag                                |  |

| IFCCK1      | FLG       | 1.62H.1 | R/W     | IF counter clock select flag                               |  |

| IFCCK0      | FLG       | 1.62H.0 | R/W     | IF counter clock select flag                               |  |

| IFCG        | FLG       | 1.63H.0 | R       | IF counter gate status detection flag (0: closed, 1: open) |  |

| IFCSTRT     | FLG       | 1.64H.1 | w       | IF counter count start flag                                |  |

| IFCRES      | FLG       | 1.64H.0 | Ŵ       | IF counter reset flag                                      |  |

| PLLMD3      | FLG       | 1.65H.3 | R       | PLL mode select flag (fixed to "0")                        |  |

| PLLMD2      | FLG       | 1.65H.2 | R       | PLL mode select flag (fixed to "0")                        |  |

| PLLMD1      | FLG       | 1.65H.1 | R/W     | PLL mode select flag                                       |  |

| PLLMD0      | FLG       | 1.65H.0 | R/W     | PLL mode select flag                                       |  |

| PLLRFCK3    | FLG       | 1.66H.3 | R       | PLL reference frequency select flag (fixed to "0")         |  |

| PLLRFCK2    | FLG       | 1.66H.2 | R/W     | PLL reference frequency select flag                        |  |

| PLLRFCK1    | FLG       | 1.66H.1 | R/W     | PLL reference frequency select flag                        |  |

| PLLRFCK0    | FLG       | 1.66H.0 | R/W     | PLL reference frequency select flag                        |  |

| PLLR17      | FLG       | 1.67H.3 | R/W     | PLL data flag                                              |  |

| PLLR16      | FLG       | 1.67H.2 | R/W     | PLL data flag                                              |  |

| PLLR15      | FLG       | 1.67H.1 | R/W     | PLŁ data flag                                              |  |

| PLLR14      | FLG       | 1.67H.0 | R/W     | PLL data flag                                              |  |

| PLLR13      | FLG       | 1.68H.3 | R/W     | PLL data flag                                              |  |

| PLLR12      | FLG       | 1.68H.2 | R/W     | PLL data flag                                              |  |

| PLLR11      | FLG       | 1.68H,1 | R/W     | PLL data fiag                                              |  |

| PLLR10      | FLG       | 1.68H.0 | R/W     | PLL data flag                                              |  |

| PLLR9       | FLG       | 1.69H.3 | R/W     | PLL data flag                                              |  |

| PLLR8       | FLG       | 1.69H.2 | R/W     | PLL data flag                                              |  |

| PLLR7       | FLG       | 1.69H.1 | R/W     | PLL data flag                                              |  |

| PLLR6       | FLG       | 1.69H.0 | R/W     | PLL data flag                                              |  |

| PLLR5       | FLG       | 1.6AH.3 | R/W     | PLL data flag                                              |  |

| PLLR4       | FLG       | 1.6AH.2 | R/W     | PLL data flag                                              |  |

| PLLR3       | FLG       | 1.6AH.1 | R/W     | PLL data ílag                                              |  |

| PLLR2       | FLG       | 1.6AH.0 | R/W     | PLL data flag                                              |  |

| PLLR1       | FLG       | 1.6BH.3 | R/W     | PLL data flag                                              |  |

| PLLPUT      | FLG       | 1.6CH.0 | W       | PLL data set flag                                          |  |

| PLLUL       | FLG       | 1.6DH.0 | R & Res | PLL unlock FF flag                                         |  |

#### CHAPTER 3 RESERVED SYMBOLS

| Symbol name | Attribute | Value   | R/W | Description                      |  |

|-------------|-----------|---------|-----|----------------------------------|--|

| P0BBIO3     | FLG       | 1.6EH.3 | R/W | P0Bo I/O select flag             |  |

| P0BBIO2     | FLG       | 1.6EH.2 | R/W | P082 I/O select flag             |  |

| P0BBIO1     | FLG       | 1.6EH.1 | R/W | P0Bi I/O select flag             |  |

| POBBIOO     | FLG       | 1.6EH.0 | R/W | P0B₀ I/O setect flag             |  |

| P0DBIO3     | FLG       | 1.6FH.3 | R/W | P0D <sub>3</sub> I/O select flag |  |

| P0DBIO2     | FLG       | 1.6FH.2 | R/W | P0D2 I/O select flag             |  |

| P0CBIO1     | FLG       | 1.6FH.1 | R/W | P0C1 I/O select flag             |  |

| POCBICO     | FLG       | 1.6FH.0 | R/W | P0Co I/O select flag             |  |

# 3.6 Peripheral Hardware Register

# **★** (1) μPD17071

| Symbol name | Attribute | Value | R/W | Description                                            |

|-------------|-----------|-------|-----|--------------------------------------------------------|

| AR          | DAT       | 40H   | R/W | GET/PUT/PUSH/CALL/BR/MOVT instruction address register |

| IFC         | DAT       | 43H   | R   | Middle frequency (IF) counter data register            |

#### (2) µPD17072, 17073

| Symbol name | Attribute | Value | R/W | Description                                            |

|-------------|-----------|-------|-----|--------------------------------------------------------|

| SIOSFR      | DAT       | 03H   | R/W | Serial interface presettable shift register            |

| AR          | DAT       | 40H   | R/W | GET/PUT/PUSH/CALL/BR/MOVT instruction address register |

| IFC         | DAT       | 43H   | R   | Middle frequency (IF) counter data register            |

#### 3.7 Other

| Symbol name | Attribute | Value | R/W | Description                                         |

|-------------|-----------|-------|-----|-----------------------------------------------------|

| OBF         | DAT       | 0FH   | -   | Fixed operand value for GET/PUT/MOVT instructions   |

| AR_EPA1     | DAT       | 8040H | -   | Operand (EPA bit ON) for CALL/BR/MOVT instructions  |

| AR_EPA0     | DAT       | 4040H | - 1 | Operand (EPA bit OFF) for CALL/BR/MOVT instructions |

# 3.8 List of Reserved Words (in Alphabetical Order)

#### 3.8.1 Instructions and pseudo-instructions

#### (1) µPD17071

| ADD     | EXTRN    | NIBBLE5V | SET2     |

|---------|----------|----------|----------|

| ADDC    | FLG      | NIBBLE6  | SET3     |

| AND     | GET      | NIBBLE6V | SET4     |

| BANK0   | GLOBAL   | NIBBLE7  | SFCOND   |

| BANK1   | HALT     | NIBBLE7V | SKE      |

| BELOW   | IF       | NIBBLE8  | SKF      |

| BR      | IFCHAR   | NIBBLE8V | SKF1     |

| C14344  | IFNCHAR  | NOBMAC   | SKF2     |

| C4444   | INC      | NOLIST   | SKF3     |

| CALL    | INCLUDE  | NOMAC    | SKF4     |

| CASE    | INITELG  | NOP      | SKGE     |

| CLR1    | IRP      | NOT1     | SKLT     |

| CLR2    | LAB      | NOT2     | SKNE     |

| CLR3    | LBMAC    | NOT3     | SKT      |

| CLR4    | LD       | NOT4     | SKT1     |

| CSEG    | LFCOND   | OBMAC    | SKT2     |

| DAT     | LIST     | OMAC     | SKT3     |

| DB      | LITERAL  | OR       | SKT4     |

| DW      | LMAC     | ORG      | SMAC     |

| EJECT   | MACRO    | OTHER    | ST       |

| ELSE    | MEM      | POP      | STOP     |

| END     | MOV      | PUBLIC   | SUB      |

| ENDCASE | MOVT     | PURGE    | SUBC     |

| ENDIF   | NIBBLE   | PUSH     | SUMMARY  |

| ENDIFC  | NIBBLE1  | PUT      | TAG      |

| ENDIFNC | NIBBLE2  | REPT     | TITLE    |

| ENDM    | NIBBLE2V | RET      | XOR      |

| ENDP    | NIBBLE3  | RETSK    | ZZZERROR |

| ENDR    | NIBBLE3V | RORC     | ZZZMCHK  |

| EOF     | NIBBLE4  | SBMAC    | ZZZMSG   |

| EXIT    | NIBBLE4V | SET      |          |

| EXITR   | NIBBLE5  | SET1     |          |

|         |          |          |          |

#### (2) µPD17072, 17073

| ADD     | EXITR    | NIBBLE5V | SET2     |

|---------|----------|----------|----------|

| ADDC    | EXTRN    | NIBBLE6  | SET3     |

| AND     | FLG      | NIBBLE6V | SET4     |

| BANK0   | GET      | NIBBLE7  | SECOND   |

| BANK1   | GLOBAL   | NIBBLE7V | SKE      |

| BELOW   | HALT     | NIBBLE8  | SKF      |

| BR      | IF       | NIBBLE8V | SKF1     |

| C14344  | IFCHAR   | NOBMAC   | SKF2     |

| C4444   | IFNCHAR  | NOLIST   | SKF3     |

| CALL    | INC      | NOMAC    | SKF4     |

| CASE    | INCLUDE  | NOP      | SKGE     |

| CLR1    | INITFLG  | NOT1     | SKLT     |

| CLR2    | IRP      | NOT2     | SKNE     |

| CLR3    | LAB      | NOT3     | SKT      |

| CLR4    | LBMAC    | NOT4     | SKT1     |

| CSEG    | LD       | OBMAC    | SKT2     |

| DAT     | LFCOND   | OMAC     | SKT3     |

| DB      | LIST     | OR       | SKT4     |

| DI      | LITERAL  | ORG      | SMAC     |

| DW      | LMAC     | OTHER    | ST       |

| EI      | MACRO    | POP      | STOP     |

| EJECT   | MEM      | PUBLIC   | SUB      |

| ELSE    | MOV      | PURGE    | SUBC     |

| END     | MOVT     | PUSH     | SUMMARY  |

| ENDCASE | NIBBLE   | PUT      | TAG      |

| ENDIF   | NIBBLE1  | REPT     | TITLE    |

| ENDIFC  | NIBBLE2  | RET      | XOR      |

| ENDIFNC | NIBBLE2V | RETI     | ZZZERROR |

| ENDM    | NIBBLE3  | RETSK    | ZZZMCHK  |

| ENDP    | NIBBLE3V | RORC     | ZZZMSG   |

| ENDR    | NIB8LE4  | SBMAC    |          |

| EOF     | NIBBLE4V | SET      |          |

| EXIT    | NIBBLE5  | SET1     |          |

# 3.8.2 Registers and flags

# (1) μPD17071

| AR       | LCDD12  | P1A0    | PLLR7     |

|----------|---------|---------|-----------|

| AR0      | LCDD13  | P1A1    | PLLR8     |

| AR1      | LCDD14  | P1A2    | PLLR9     |

| AR2      | LCDD2   | P1A3    | PLLRFCK0  |

| AR_EPA0  | LCDD3   | P1APLD0 | PLLRFCK1  |

| AR_EPA1  | LCDD4   | P1APLD1 | PLLRFCK2  |

| BANK     | LCDD5   | P1APLD2 | PLLRFCK3  |

| BCD      | LCDD6   | P1APLD3 | PLLUL     |

| BEEP0CK0 | LCDD7   | P1B0    | PSW       |

| BEEP0CK1 | LCDD8   | P1B1    | SP        |

| BTMOCY   | LCDD9   | P1B2    | Z         |

| 8TM1CKD  | LCDEN   | P1B3    | ZZZO      |

| CE       | POAO    | P1C0    | ZZZ1      |

| CMP      | POAt    | PLLMD0  | ZZZ2      |

| CY       | P0A2    | PLLMD1  | ZZZ3      |

| DBF      | POA3    | PLLMD2  | ZZZ4      |

| DBF0     | P0B0    | PLLMD3  | ZZZ5      |

| DBF1     | P0B1    | PLLPUT  | ZZZ6      |

| DBF2     | P0B2    | PLLR1   | ZZZ7      |

| DBF3     | P0B3    | PLLR10  | ZZZ8      |

| IFC      | POBBIÓO | PLLR11  | ZZZ9      |

| IFCCK0   | P0BBIO1 | PLLR12  | ZZZDEVID  |

| IFCCK1   | P0BBIO2 | PLLR13  | ZZZEPA    |

| IFCG     | P0BBIO3 | PLLR14  | ZZZLSARG  |

| IFCMD0   | P0C0    | PLLR15  | ZZZPRINT  |

| IFCMD1   | P0C1    | PLLR16  | ZZZSKIP   |

| IFCRES   | P0CBIO0 | PLLR17  | ZZZSYDOC  |

| IFCSTRT  | P0CBIO1 | PLLR2   | ZZZALBMAC |

| LCDD0    | P0D2    | PLLR3   | ZZZALMAC  |

| LCDD1    | P0D3    | PLLR4   | ZZZARGC   |

| LCDD10   | P0DBIO2 | PLLR5   | ZZZLINE   |

| LCDD11   | P0DBIO3 | PLLR6   |           |

|          |         |         |           |

\*

#### (2) µPD17072, 17073

| ADCCH0    | IFCG    | P083    | PLLR13   |

|-----------|---------|---------|----------|

| ADCCH1    | IFCMD0  | P0BBIO0 | PLLR14   |

| ADCCH2    | IFCMD1  | P0BBIO1 | PLLR15   |

| ADCCH3    | IFCRES  | P0BBIO2 | PLLR16   |

| ADCCMP    | IFCSTRT | P0BBIO3 | PLLR17   |

| ADCON     | INT     | P0C0    | PLLR2    |

| ADCRFSEL0 | IP      | P0C1    | PLLR3    |

| ADCRFSEL1 | IPBTM1  | POCBIO0 | PLLR4    |

| ADCRFSEL2 | IPSIO   | P0CBIO1 | PLLR5    |

| ADCRFSEL3 | IRQ     | P0D2    | PLLR6    |

| ADCSTRT   | IRQBTM1 | P0D3    | PLLR7    |

| AR        | IRQSIO  | P0D8IO2 | PLLR8    |

| AR0       | LCDD0   | P0DBIO3 | PLLR9    |

| AR1       | LCDD1   | P1A0    | PLLRFCK0 |

| AR2       | LCDD10  | P1A1    | PLLRFCK1 |

| AR_EPA0   | LCDD11  | P1A2    | PLLRFCK2 |

| AR_EPA1   | LCDD12  | P1A3    | PLLRFCK3 |

| BANK      | LCDD13  | P1APLD0 | PLLUL    |

| BCD       | LCDD14  | P1APLD1 | PSW      |

| BEEP0CK0  | LCDD2   | P1APLD2 | SIOCK0   |

| BEEPOCK1  | LCDD3   | P1APLD3 | SIOCK1   |

| BTM0CY    | LCDD4   | P1B0    | SIOCK2   |

| BTM1CK    | LCDD5   | P1B1    | SIOCK3   |

| CE        | LCDD6   | P1B2    | SIOHIZ   |

| CMP       | LCDD7   | P1B3    | SIOSEL   |

| CY        | LCDD8   | P1C0    | SIOSFR   |

| OBF       | LCDD9   | PLLMD0  | SIOTS    |

| DBF0      | LCDEN   | PLLMD1  | SP       |

| DBF1      | POAO    | PLLMD2  | SYSCK    |

| DBF2      | P0A1    | PLLMD3  | Z        |

| DBF3      | P0A2    | PLLPUT  | ZZZ0     |

| IEG       | POA3    | PLLR1   | ZZZ1     |

| IFC       | P080    | PLLR10  | ZZZ2     |

| IFCCK0    | P081    | PLLR11  | ZZZ3     |

| IFCCK1    | P082    | PLLR12  | ZZZ4     |

|           |         |         |          |

2225 2227 2228 2229 2220EVID 222EPA 222EPA 222ESARG 222PRINT 222SYDOC 222ALBMAC 222ALBMAC 222ALMAC 222ALMAC [MEMO]

#### CHAPTER 4 LOAD MODULE FILE FORMAT

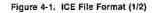

HEX-format load module files output by the assembler (AS17K) have two types of output file formats: ICE files and PRO files.

These two types of files must be used according to the target application. Besides having a user program area, they also have an assembly environment data area, an in-circuit emulator operating environment data area, and other areas.

#### (1) HEX-format load module file format

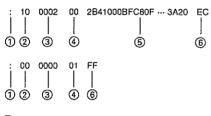

The data contained in HEX-format load module files output by the assembler is output in the following format.

[Example of HEX-format load module file format]

#### 1 Record mark

This indicates the start of a record.

#### (2) Code amount (2 digits)

This indicates the amount of code (byte data) stored in a record. This value is expressed as a hexadecimal number, with a maximum value of 10H (16 units). The value for the end record is 00H.

#### 3 Address (4 digits)

This indicates the start address of the code shown in a record. The value for the end record is 0000H, and has no relation to the address.

#### (4) Record type (2 digits)

A value of 00H indicates "data record" as the record type and a value of 01H indicates "end record."

(5) Code (up to 32 digits (16 bytes))

Code is output to this field one byte at a time, up to 16 bytes.

#### 6 Check sum (2 digits)

Data from fields (2), (3), (4), (5) and (6) is output to this field (with even parity) as byte data with an LSB value of 00H based on byte-unit sums.

#### (2) ICE files

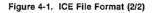

ICE files are output as HEX-format files exclusive to the in-circuit emulator (IE-17K, IE-17K-ET, or EMU-17K Note) output by the AS17K assembler. Figure 4-1 shows the output format assembled using the device files.

Note Manufactured by I.C Corp.

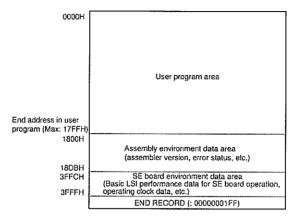

#### \* (a) μPD17071

Note Range for in-circuit emulator is 8000H to 9B9EH.

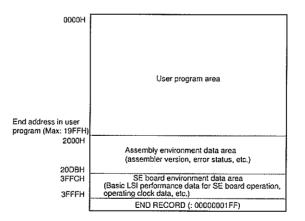

#### (b) µPD17072, 17073

Note Range for in-circuit emulator is 8000H to B998H.

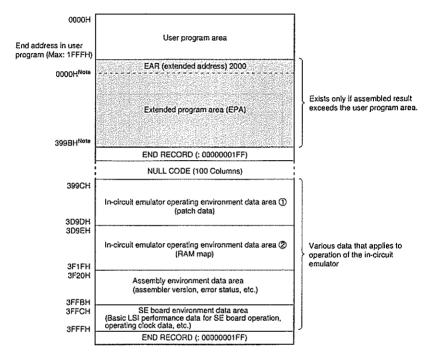

#### (3) PRO files

PRO files are output as HEX-format files exclusive to the PROM and single-write PROM products that are used for mask order and stand-alone SE board evaluations that are output by the AS17K assembler. These are output when "/PRO" is specified as an assembly option during assemble.

Figure 4-2 shows the output format assembled using the device files.

#### (a) μPD17071

Remark The range of 10D9H to 1FFBH does not exist in PRO files.

Figure 4-2. PRO File Format (2/2)

#### (b) μPD17072

Remark The range of 18DCH to 3FFBH does not exist in PRO files.

#### (c) µPD17073

Remark The range of 20DCH to 3FFBH does not exist in PRO files.

#### (4) File comparison of load module files

Even when there are no changes in the source file, changes may occur in the assembler results (i.e., the assembly environment data area). This is because the data in the assembly environment data area includes items such as the source file creation date.

#### Table 4-1. Items in Assembly Environment Data Area Which Are Subject to Change even when Source File Does not Change (1/3)

#### (a) μPD17071

| llem                                                                          | Address       |               |

|-------------------------------------------------------------------------------|---------------|---------------|

| nem                                                                           | ICE file      | PRO file      |

| Program name Note 1                                                           | 1F23H - 1F62H | 1000H - 103FH |

| (character string of up to 64 bytes, specified by assembly option /' PROG='.) |               |               |

| SIMPLEHOST data                                                               | 1FADH         | 108AH         |

| Error or warning status                                                       | 1FB0H         | 108DH         |

| Source file creation date (YY/MM/DD) and time Note 2                          | 1FBEH - 1FC7H | 109BH - 10A4H |

| Device name                                                                   | 1FC8H - 1FD7H | 10A5H - 10B4H |

| Device file version                                                           | 1FDCH, 1FDDH  | 10B9H, 10BAH  |

| Assembler version                                                             | 1FDEH + 1FE1H | 1088H - 108EH |

Notes 1. When using the RA17K (under development), the following 32 bytes are the program name area. In ICE files : 1F23H to 1F42H

In PRO files: 1000H to 101FH

The RA17K uses the remaining 32 bytes as a system reserved area.

2. The most recent creation date/time data among the modules is written in source files or sequence files.

#### Caution Do not make changes to load module files only.

Change load files by changing the source file and then reassembling. Revising load files only may cause the histories of other files to become mismatched, resulting in bugs.

#### Table 4-1. Items in Assembly Environment Data Area Which Are Subject to Change even when Source File Does not Change (2/3)

#### (b) µPD17072

| ltem                                                                          | Address       |               |

|-------------------------------------------------------------------------------|---------------|---------------|

| nem                                                                           | 1CE file      | PRO file      |

| Program name Note 1                                                           | 3F20H - 3F5FH | 1800H - 183FH |

| (character string of up to 64 bytes, specified by assembly option /' PROG='.) |               |               |

| SIMPLEHOST data                                                               | 3FADH         | 188DH         |

| Error or warning status                                                       | 3FB0H         | 1890H         |

| Source file creation date (YY/MM/DD) and time Note 2                          | 3F8EH - 3FC7H | 189EH - 18A7H |

| Device name                                                                   | 3FC8H - 3FD7H | 18A8H - 18B7H |

| Device file version                                                           | 3FDCH, 3FDDH  | 18BCH, 18BDH  |

| Assembler version                                                             | 3FDEH - 3FE1H | 18BEH - 18C1H |

Notes 1. When using the RA17K (under development), the following 32 bytes are the program name area. In ICE files : 3F20H to 3F3FH

In PRO files: 1800H to 181FH

The RA17K uses the remaining 32 bytes as a system reserved area.

2. The most recent creation date/time data among the modules is written in source files or sequence files.

Caution Do not make changes to load module files only.

Change load files by changing the source file and then reassembling. Revising load files only may cause the histories of other files to become mismatched, resulting in bugs.

#### Table 4-1. Items in Assembly Environment Data Area Which Are Subject to Change even when Source File Does not Change (3/3)

#### (c) μPD17073

| ltem                                                                          | Address       |               |

|-------------------------------------------------------------------------------|---------------|---------------|

| (en)                                                                          | ICE file      | PRO file      |

| Program name Noto 1                                                           | 3F20H - 3F5FH | 2000H - 203FH |

| (character string of up to 64 bytes, specified by assembly option /' PROG='.) |               |               |

| SIMPLEHOST data                                                               | 3FADH         | 208DH         |

| Error or warning status                                                       | 3FB0H         | 2090H         |

| Source file creation date (YY/MM/DD) and time Note 2                          | 3FBEH - 3FC7H | 209EH - 20A7H |

| Device name                                                                   | 3FC8H - 3FD7H | 20A8H - 20B7H |

| Device file version                                                           | 3FDCH, 3FDDH  | 20BCH, 20BDH  |

| Assembler version                                                             | 3FDEH - 3FE1H | 20BEH - 20C1H |

Notes 1. When using the RA17K (under development), the following 32 bytes are the program name area. In ICE files : 3F20H to 3F3FH

In PRO files: 2000H to 201FH

The RA17K uses the remaining 32 bytes as a system reserved area.

2. The most recent creation date/time data among the modules is written in source files or sequence files.

#### Caution Do not make changes to load module files only.

Change load files by changing the source file and then reassembling. Revising load files only may cause the histories of other files to become mismatched, resulting in bugs.

|                                                                                                   | Message                                                                                       | to our customers is complete, bug nee                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| From:                                                                                             |                                                                                               | and up-to-date, we readily accept that<br>errors may occur. Despite all the care and<br>precautions we've taken, you may<br>encounter problems in the documentation.<br>Please complete this form whenever |

| Company                                                                                           |                                                                                               | you'd like to report errors or suggest<br>improvements to us.                                                                                                                                              |

| Tel.                                                                                              | FAX                                                                                           |                                                                                                                                                                                                            |

| Address                                                                                           |                                                                                               | Thank you for your kind support.                                                                                                                                                                           |

| North America<br>NEC Electronics Inc.<br>Corporate Communications Dept.<br>Fax: 1-800-729-9288    | Hong Kong, Philippines, Oceania<br>NEC Electronics Hong Kong Ltd.<br>Fax: +852-2886-9022/9044 | Asian Nations except Philippines<br>NEC Electronics Singapore Pte. Ltd.<br>Fax: +65-250-3583                                                                                                               |