This document describes the Renesas Connectivity Production Line Tool. The Connectivity PLT hardware, as well as various software applications, are explained in detail. The purpose of this document is to guide users in the setup and operation of the tool. Please add functional and/or application names in keywords in Advanced Properties of the Word file.

## **Contents**

| Co  | ntents                | S         |                                              |    |  |  |  |

|-----|-----------------------|-----------|----------------------------------------------|----|--|--|--|

| Fiç | gures .               |           |                                              | 3  |  |  |  |

| Та  | bles5                 |           |                                              |    |  |  |  |

| 1.  | Terms and Definitions |           |                                              |    |  |  |  |

| 2.  | References            |           |                                              |    |  |  |  |

| 3.  | Intro                 | duction   | 1                                            | 8  |  |  |  |

| 4.  | Syst                  | tem Ove   | rview                                        | 9  |  |  |  |

|     | 4.1                   | Typical   | Setup                                        | 9  |  |  |  |

|     | 4.2                   | Typical   | Test Sequence                                | 9  |  |  |  |

| 5.  | Hard                  | dware Se  | etup                                         | 10 |  |  |  |

|     | 5.1                   | Power \$  | Supply Connections                           | 10 |  |  |  |

|     | 5.2                   | DUT Co    | onnections                                   | 10 |  |  |  |

|     | 5.3                   | GPIO C    | Connections                                  | 11 |  |  |  |

|     | 5.4                   | Daisy C   | Chaining                                     | 12 |  |  |  |

|     |                       | 5.4.1     | Addressing                                   | 13 |  |  |  |

|     |                       | 5.4.2     | Sleep Current Measurement Using External DMM | 13 |  |  |  |

|     | 5.5                   | Product   | tion Line Setup                              | 13 |  |  |  |

| 6.  | Insta                 | allation  |                                              | 16 |  |  |  |

|     | 6.1                   | Introduc  | ction                                        | 16 |  |  |  |

|     | 6.2                   | Archited  | cture and Different Setup Strategies         | 16 |  |  |  |

|     |                       | 6.2.1     | PLT Services                                 | 16 |  |  |  |

|     |                       | 6.2.2     | PLT Applications                             | 16 |  |  |  |

|     | 6.3                   | Installa  | tion                                         | 17 |  |  |  |

|     |                       | 6.3.1     | Standard Installation                        | 17 |  |  |  |

|     |                       | 6.3.2     | Remote System Installation                   | 17 |  |  |  |

|     | 6.4                   | Install N | Necessary Drivers                            | 19 |  |  |  |

|     | 6.5                   | Update    | and Uninstall                                | 19 |  |  |  |

| 7.  | Data                  | abase Se  | ervice                                       | 21 |  |  |  |

|     | 7.1                   | Installa  | tion                                         | 21 |  |  |  |

|     | 7.2                   | Databa    | se Structure                                 | 22 |  |  |  |

|     |                       | 7.2.1     | Devices Table                                | 22 |  |  |  |

|     |                       |           |                                              |    |  |  |  |

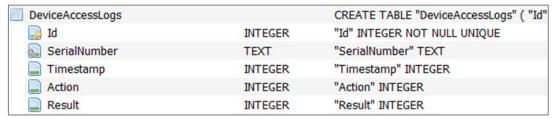

|    |     | 7.2.2     | Device Access Logs Table         | 22 |

|----|-----|-----------|----------------------------------|----|

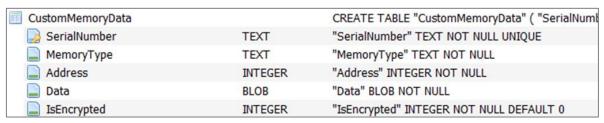

|    |     | 7.2.3     | Custom Memory Data Table         | 23 |

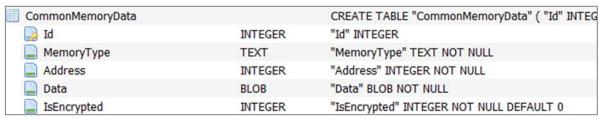

|    |     | 7.2.4     | Common Memory Data Table         | 24 |

|    | 7.3 | Data En   | ncryption                        | 24 |

| 8. | Con | nectivity | PLT Configuration                | 25 |

|    | 8.1 | Connec    | ctivity PLT Configuration Window | 25 |

|    | 8.2 | Configu   | ırations                         | 27 |

|    |     | 8.2.1     | Project Configuration            | 27 |

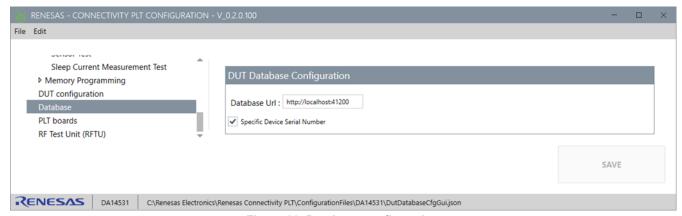

|    |     | 8.2.2     | Database Configuration           | 27 |

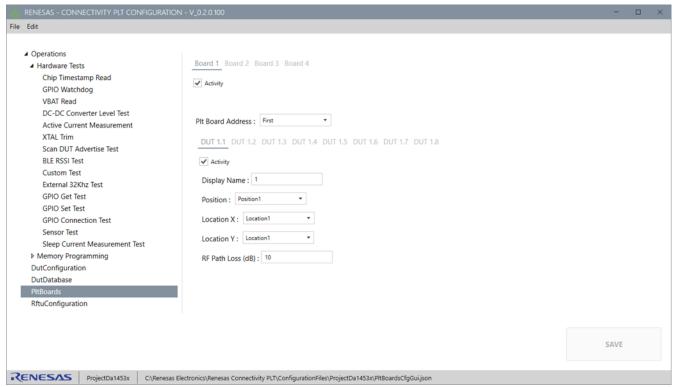

|    |     | 8.2.3     | PLT Boards Configuration         | 27 |

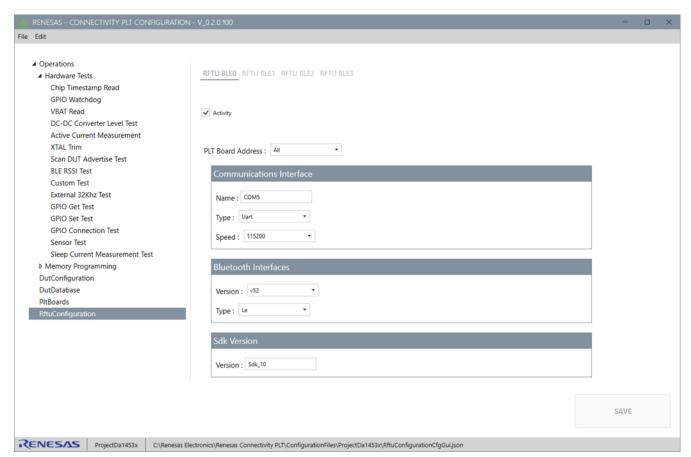

|    |     | 8.2.4     | RFTU Bluetooth LE Configuration  | 29 |

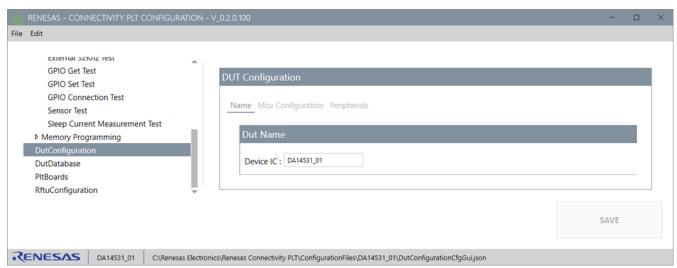

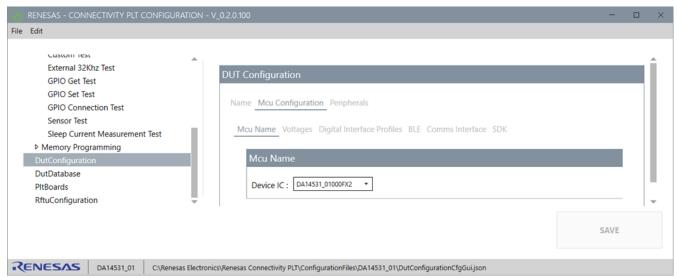

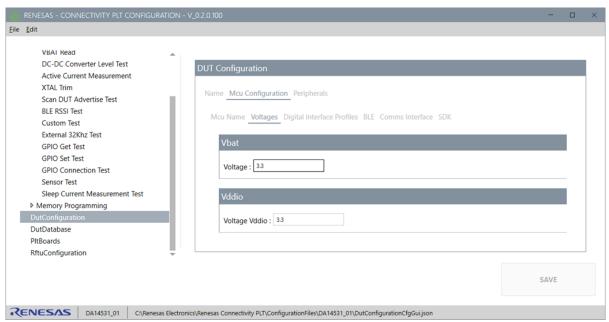

|    |     | 8.2.5     | DUT Configuration                | 31 |

|    |     | 8.2.6     | Configure Sequence Number        | 47 |

|    | 8.3 | Hardwa    | are Tests Configurations         | 47 |

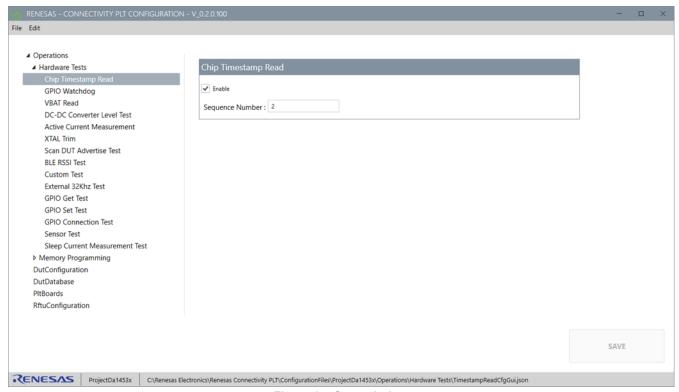

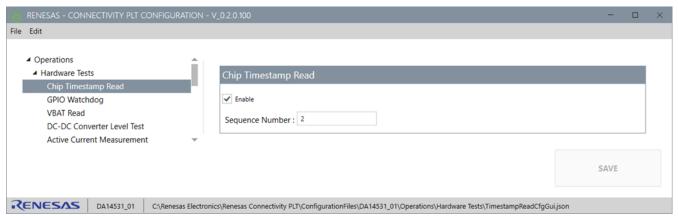

|    |     | 8.3.1     | Chip Timestamp Read              | 48 |

|    |     | 8.3.2     | GPIO Watchdog                    | 48 |

|    |     | 8.3.3     | VBAT Read                        | 49 |

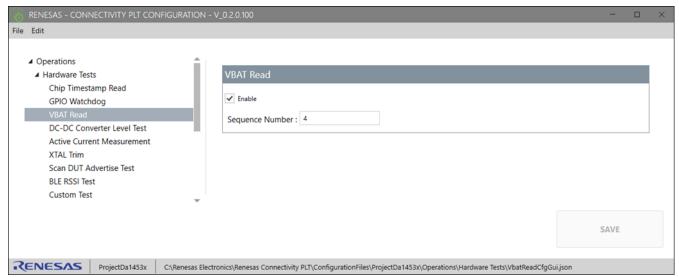

|    |     | 8.3.4     | DC-DC Converter Level Test       | 49 |

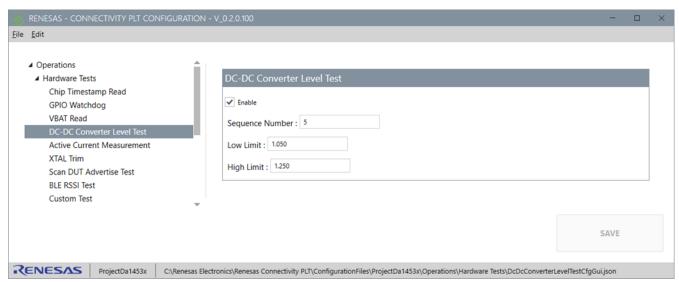

|    |     | 8.3.5     | Active Current Measurement       | 50 |

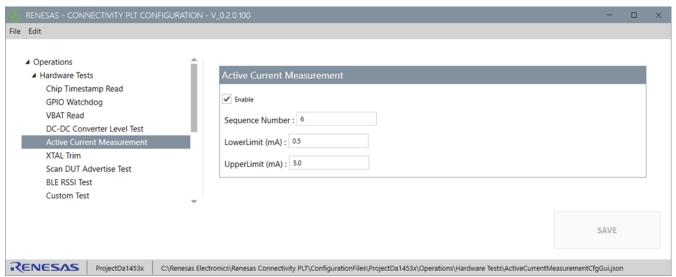

|    |     | 8.3.6     | XTAL Trim                        | 50 |

|    |     | 8.3.7     | Scan Dut Advertise               | 51 |

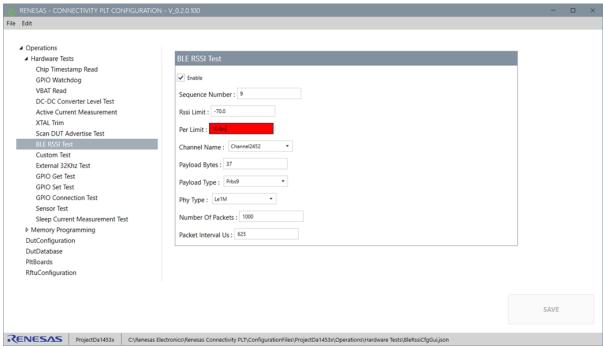

|    |     | 8.3.8     | Bluetooth LE RSSI Test           | 51 |

|    |     | 8.3.9     | Custom Test                      | 52 |

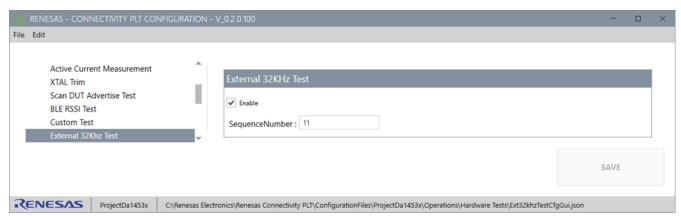

|    |     | 8.3.10    | External 32-kHz Test             | 53 |

|    |     | 8.3.11    | GPIO Get Test                    | 53 |

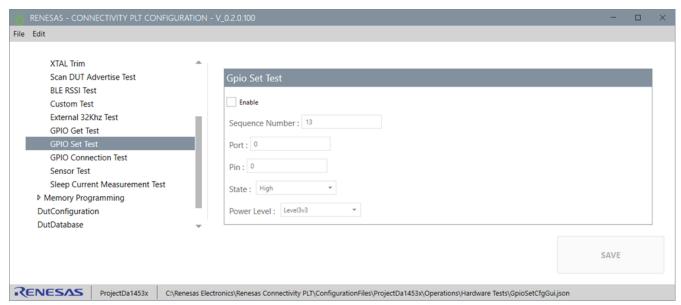

|    |     | 8.3.12    | GPIO Set Test                    | 54 |

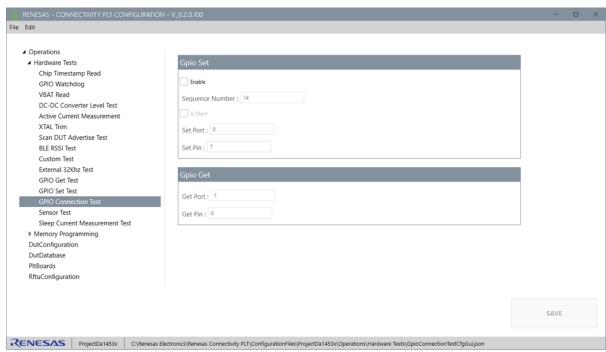

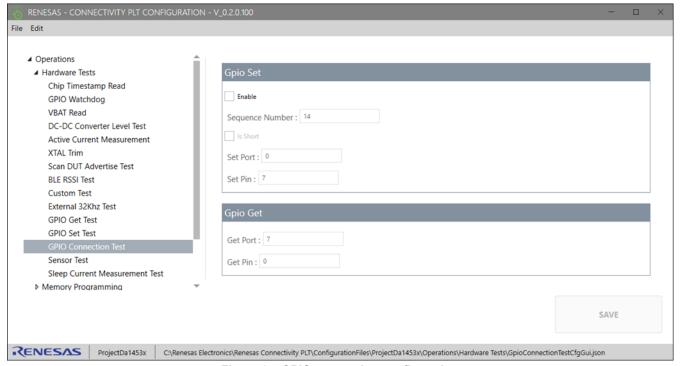

|    |     | 8.3.13    | GPIO Connection Test             | 54 |

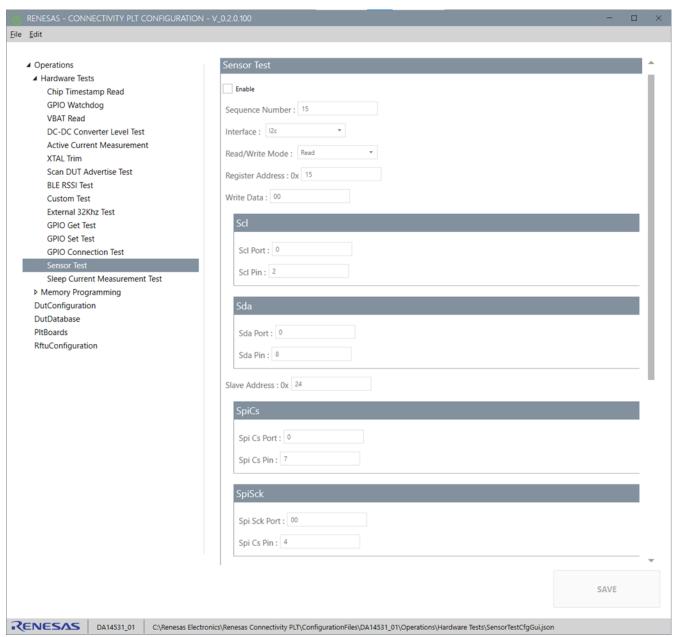

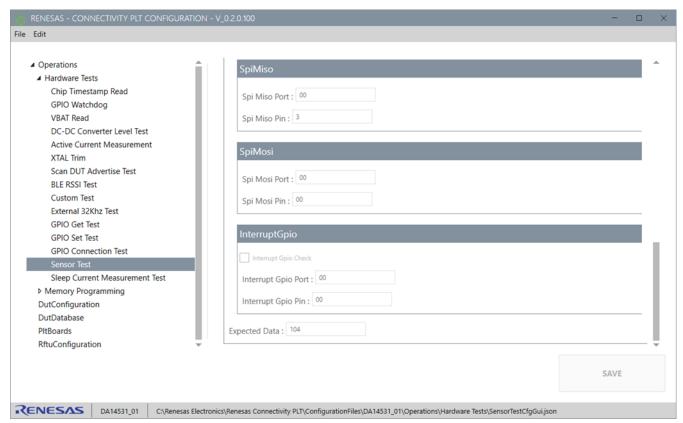

|    |     | 8.3.14    | Sensor Test                      | 54 |

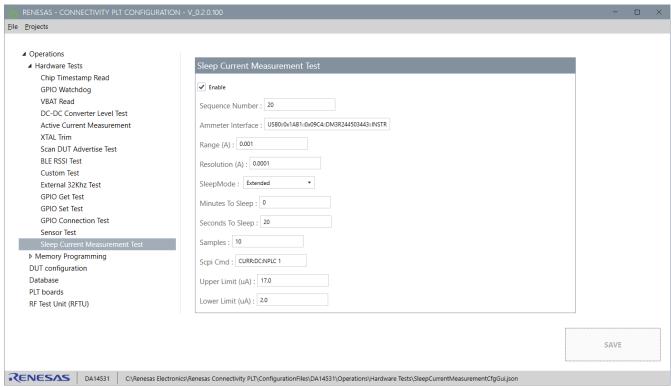

|    |     | 8.3.15    | Sleep Current Measurement Test   | 56 |

|    | 8.4 | Memory    | y Programming Configuration      | 58 |

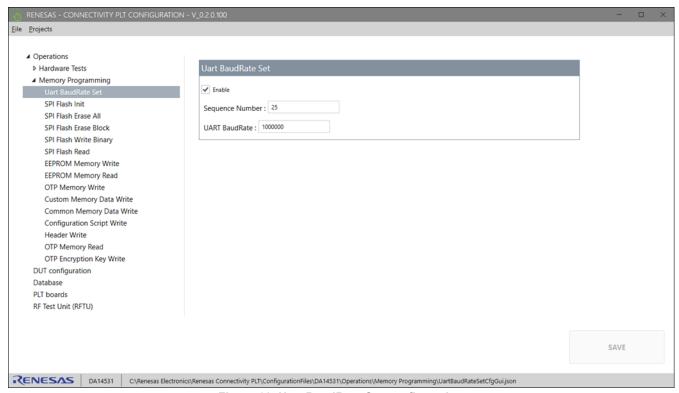

|    |     | 8.4.1     | Uart BaudRate Set                | 59 |

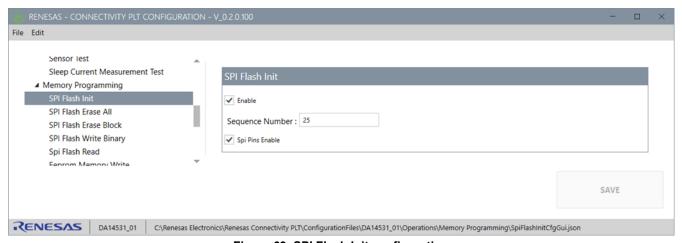

|    |     | 8.4.2     | SPI Flash Init                   | 59 |

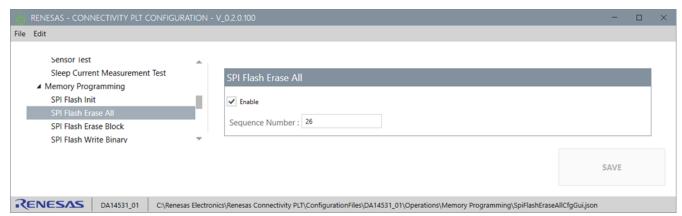

|    |     | 8.4.3     | SPI Flash Erase All              | 60 |

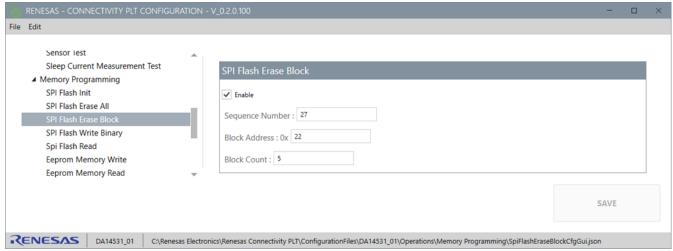

|    |     | 8.4.4     | SPI Flash Erase Block            | 60 |

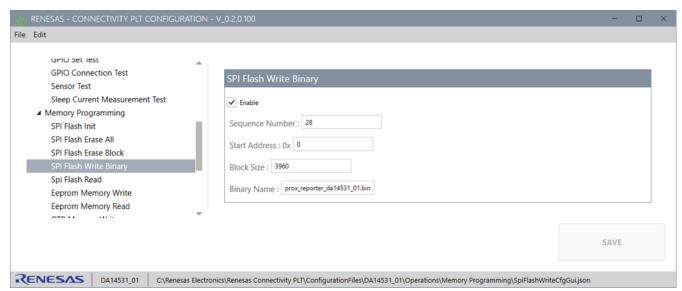

|    |     | 8.4.5     | SPI Flash Write Binary           | 61 |

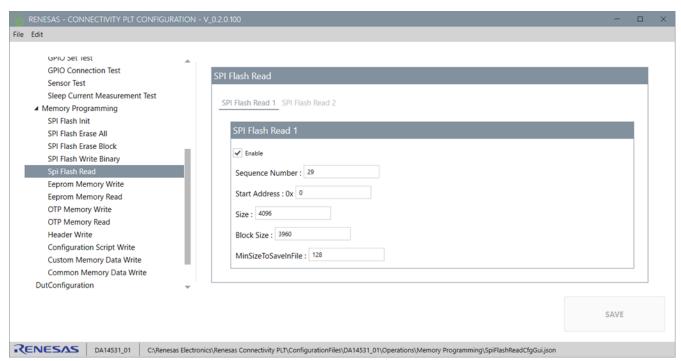

|    |     | 8.4.6     | SPI Flash Read                   | 62 |

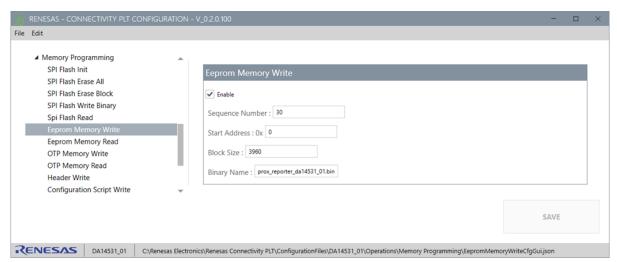

|    |     | 8.4.7     | EEPROM Memory Write              | 63 |

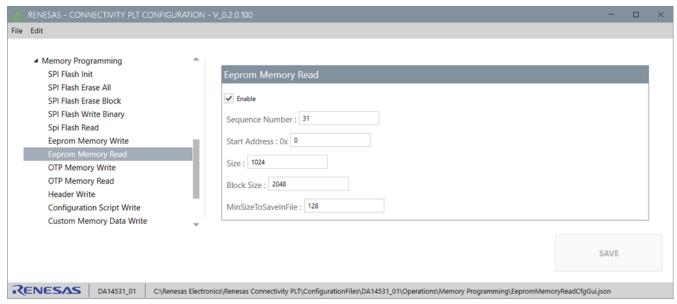

|    |     | 8.4.8     | EEPROM Memory Read               | 63 |

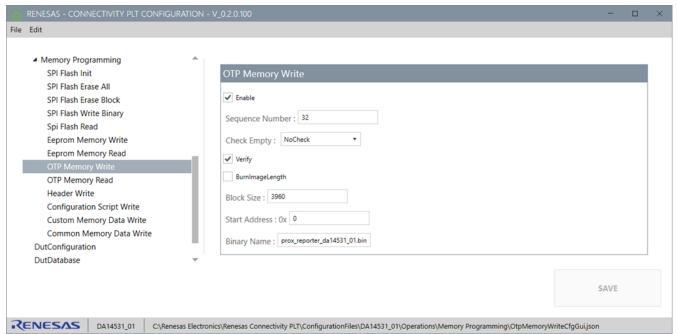

|    |     | 8.4.9     | OTP Memory Write                 | 64 |

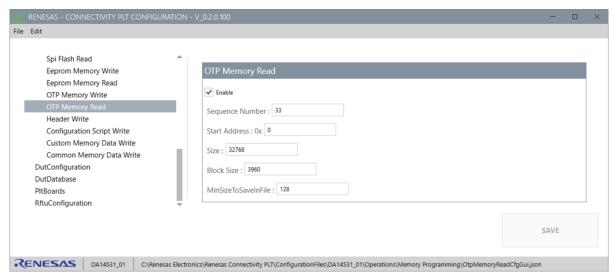

|    |     | 8.4.10    | OTP Memory Read                  | 65 |

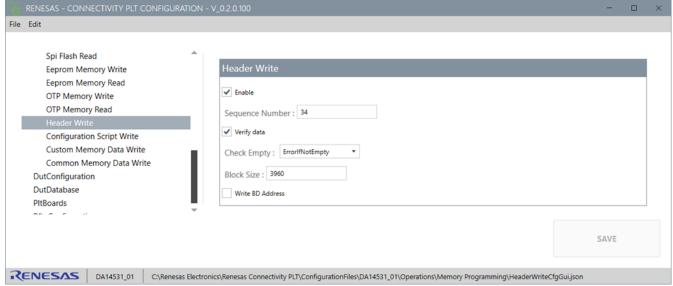

|    |     | 8.4.11    | Header Write                     | 65 |

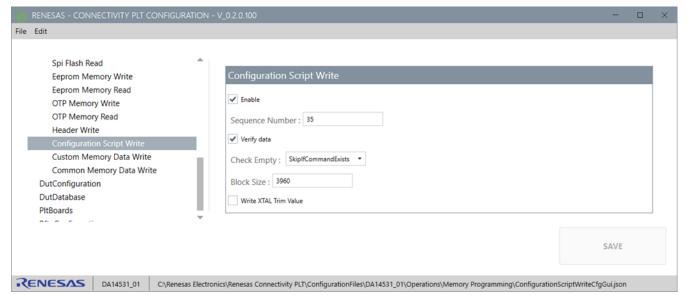

|    |     | 8.4.12    | Configuration Script Write       | 66 |

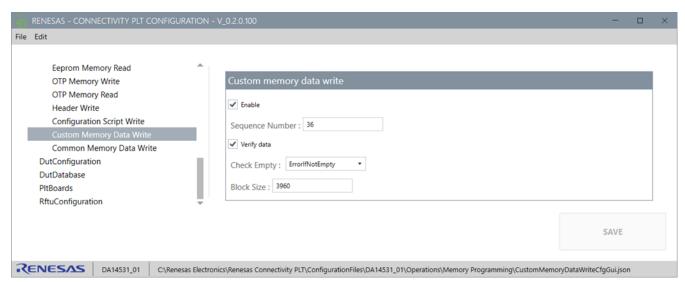

|     |        | 8.4.13      | Custom Memory Data Write                                                                                            | 67 |

|-----|--------|-------------|---------------------------------------------------------------------------------------------------------------------|----|

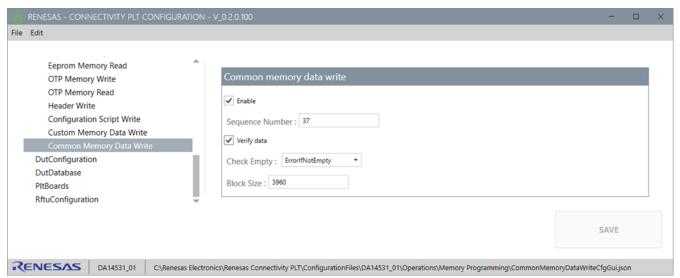

|     |        | 8.4.14      | Common Memory Data Write                                                                                            | 67 |

| 9.  | Con    | nectivity   | PLT Application                                                                                                     |    |

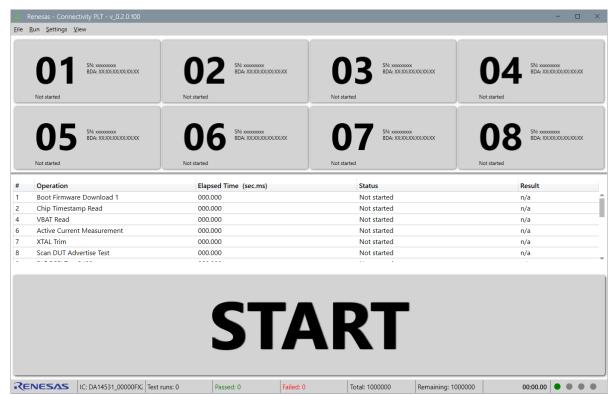

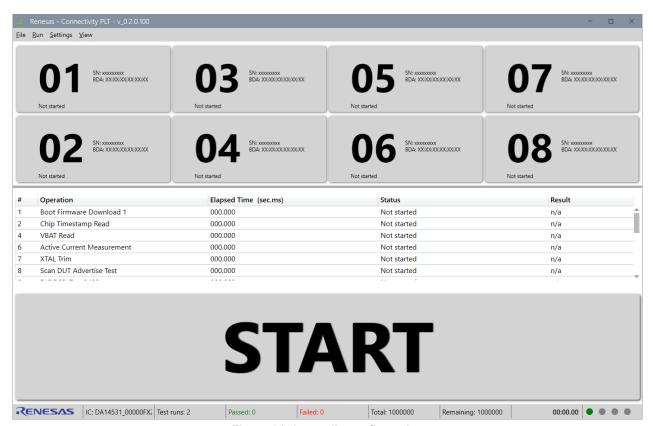

|     | 9.1    | -           | tivity PLT Application Main Execution Window                                                                        |    |

|     | 9.2    |             | ecution                                                                                                             |    |

|     | -      |             |                                                                                                                     |    |

|     | 9.3    |             | andling                                                                                                             |    |

|     |        | •           | PLT CLI Application                                                                                                 |    |

| 11. | Con    | nectivity   | PLT Core Service                                                                                                    | 82 |

|     | 11.1   | Operation   | on in Service Mode                                                                                                  | 82 |

|     | 11.2   | Operation   | on in CLI Mode                                                                                                      | 83 |

| 12. | Con    | nectivity   | PLT Service Agent                                                                                                   | 85 |

| 13. | Con    | nectivity   | PLT Firmware Update Application                                                                                     | 86 |

|     |        | _           | pdate                                                                                                               |    |

|     |        |             | Jpdate                                                                                                              |    |

| ۸   |        |             | formity Assessment                                                                                                  |    |

| Αр  | -      |             | -                                                                                                                   |    |

|     | A.1    |             | otice (Applicable to Evaluation Kits not FCC-Approved)                                                              |    |

|     | A.2    |             | KCA (Europe-UK)                                                                                                     |    |

|     | A.3    | WEEE        | Directive (2012/19/EU)                                                                                              | 90 |

|     | A.4    | RoHS C      | Compliance                                                                                                          | 90 |

| 14. | Rev    | ision His   | tory                                                                                                                | 92 |

|     | gur    |             | ard                                                                                                                 | 8  |

|     |        |             | tup                                                                                                                 |    |

| Fig | ure 3. | Power C     | connector J11                                                                                                       | 10 |

| _   |        |             | nnector                                                                                                             |    |

|     |        |             | nnector pin layout<br>onnector J10                                                                                  |    |

|     |        |             | ivity PLT chain                                                                                                     |    |

|     |        |             | ivity PLT chain alternative                                                                                         |    |

|     |        |             | ivity PLT in a shielded box                                                                                         |    |

|     |        |             | ctivity PLT chain in multiple shielded boxes                                                                        |    |

|     |        |             | ctivity PLT chain in single shielded box with multiple RF testing units<br>ctivity PLT chain in single shielded box |    |

|     |        |             | ctivity PLT Architecture                                                                                            |    |

| Fig | ure 14 | 4. CoreSe   | ervice Windows Service installation                                                                                 | 17 |

| _   |        |             | se Service Installation                                                                                             |    |

|     |        |             | se Host configurationpplication CoreService Host configuration                                                      |    |

|     |        |             | iver installer                                                                                                      |    |

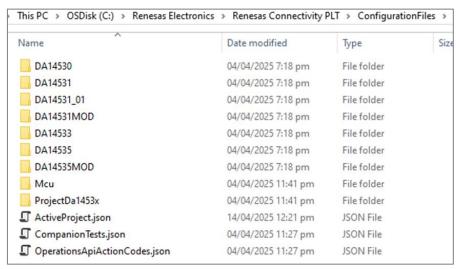

|     |        |             | uration files                                                                                                       |    |

| Fig | ure 20 | 0. Databa   | se Service Installation                                                                                             | 21 |

|     |        |             | se Devices table structure                                                                                          |    |

|     |        |             | se Device Access Logs table structurese Custom Memory data table                                                    |    |

|     |        |             | se Common Memory Data table structure                                                                               |    |

| Fig | ure 25 | 5. Start w  | indow                                                                                                               | 25 |

| _   |        |             | enu                                                                                                                 |    |

| Ηig | ure 27 | ∕. Input e⊦ | rror                                                                                                                | 26 |

| Figure 28. | Database configuration                   | .27 |

|------------|------------------------------------------|-----|

|            | PltBoards configuration                  |     |

|            | Default tile configuration               |     |

|            | 2-row tile configuration                 |     |

|            | RFTU Bluetooth LE configuration          |     |

|            | Dut configuration                        |     |

| _          | MCU name configuration                   |     |

|            | Voltages configuration                   |     |

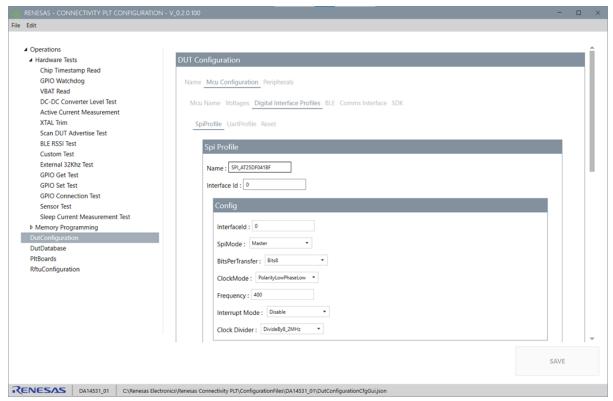

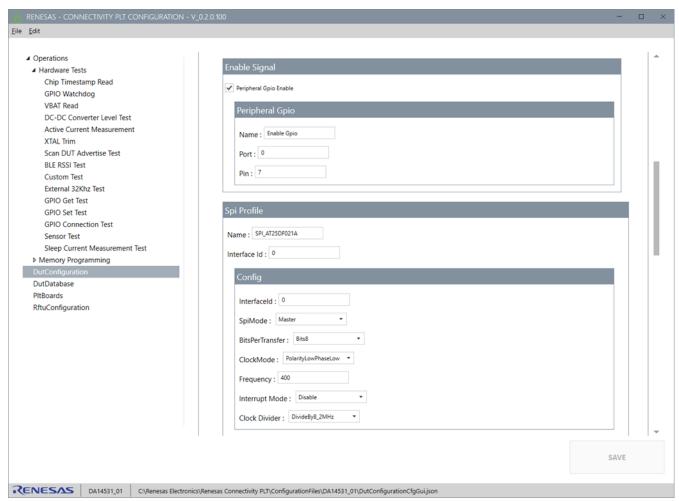

|            | SpiProfile configuration                 |     |

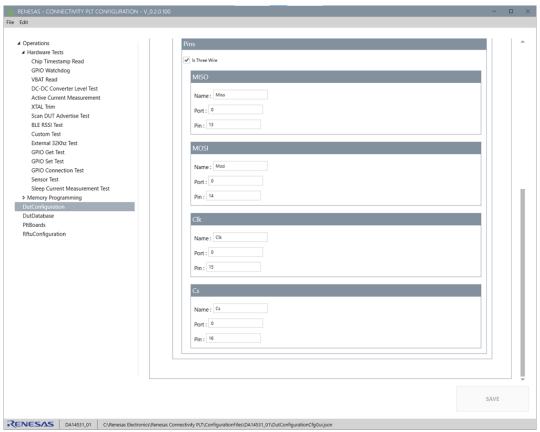

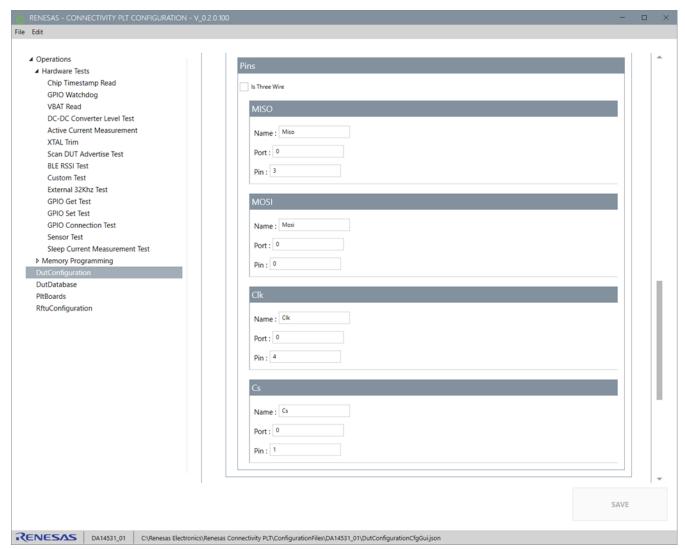

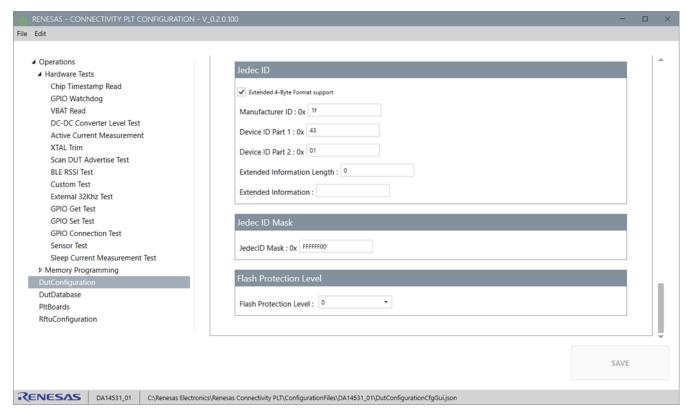

|            | Pin configuration                        |     |

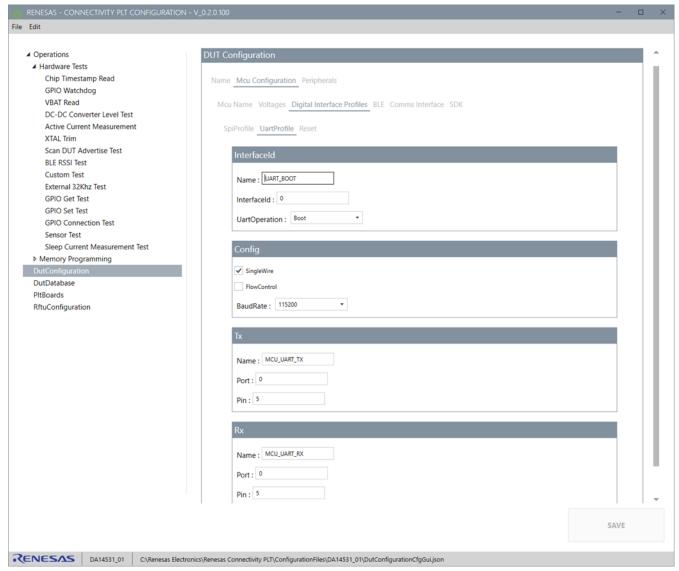

|            | UART profile configuration               |     |

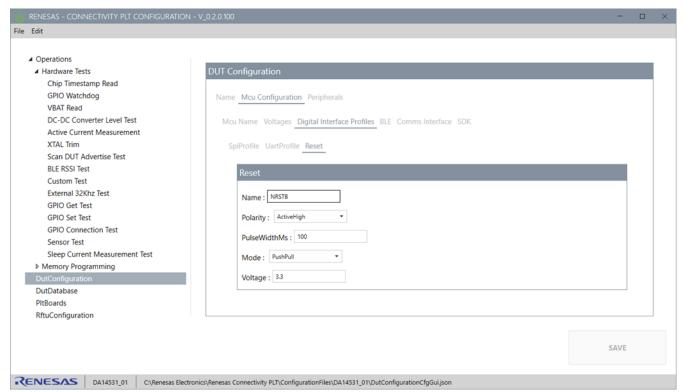

|            | Reset configuration                      |     |

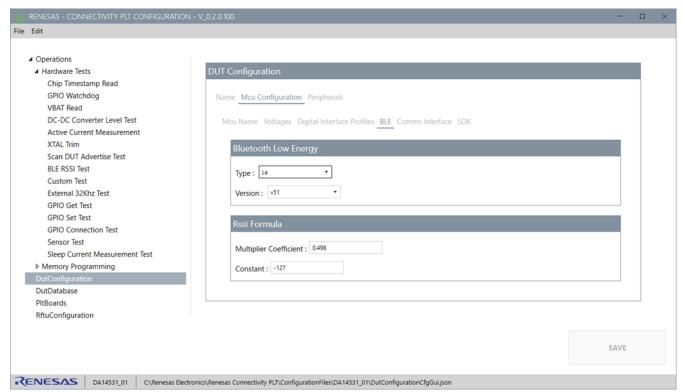

|            | Bluetooth LE configuration               |     |

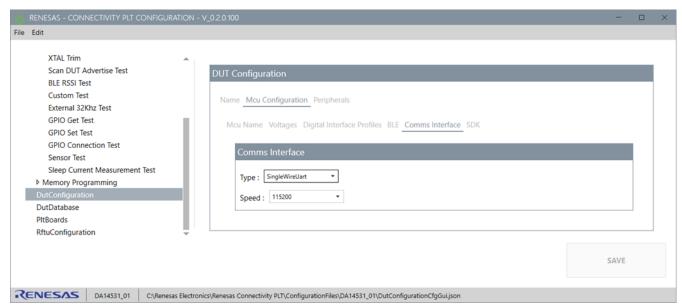

| Figure 41. | Comms interface configuration            | .38 |

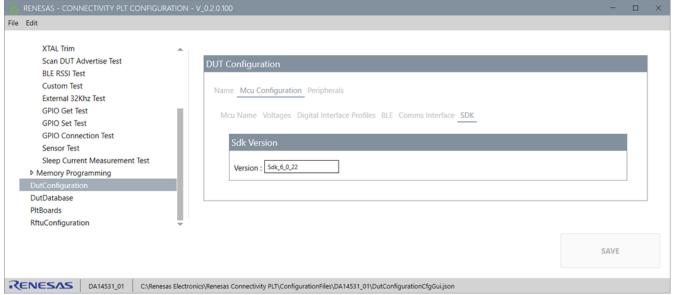

| Figure 42. | SDK configuration                        | .38 |

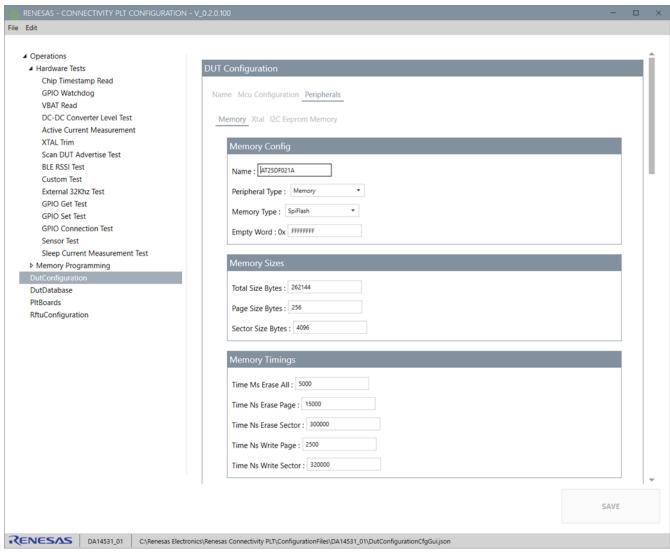

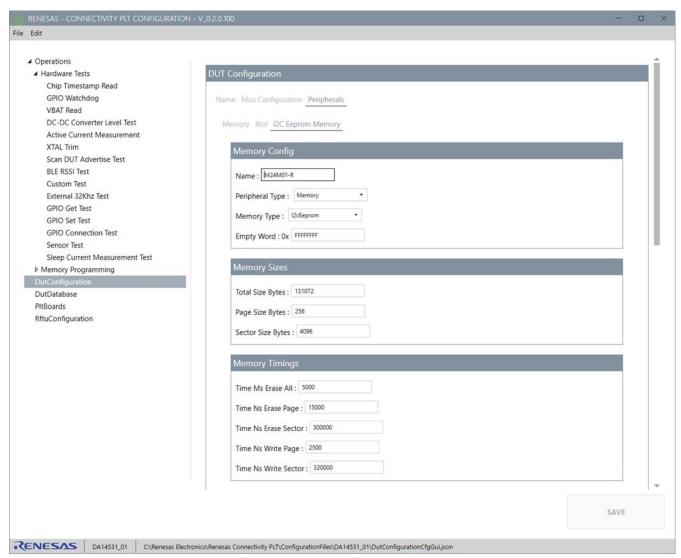

| Figure 43. | Memory configuration 1                   | .39 |

| Figure 44. | Memory configuration                     | .40 |

| Figure 45. | Pins configuration                       | .41 |

| Figure 46. | Memory configuration                     | .42 |

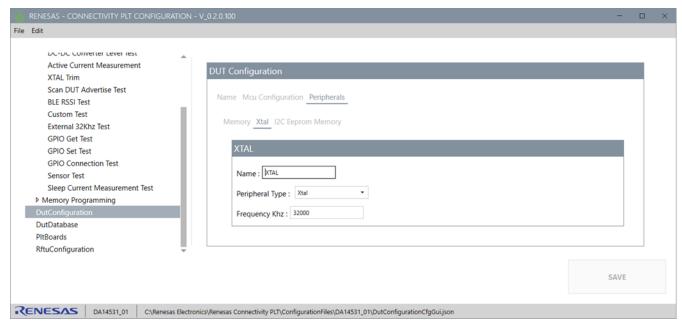

|            | Xtal configuration                       |     |

| Figure 48. | I2C EEPROM configuration 1               | .44 |

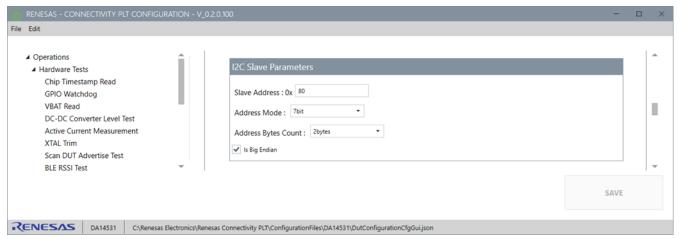

|            | I2C slave parameters                     |     |

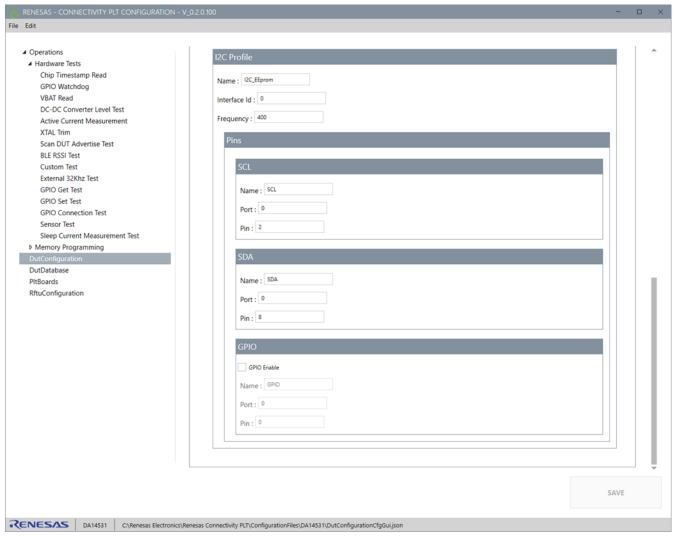

|            | I2C profile                              |     |

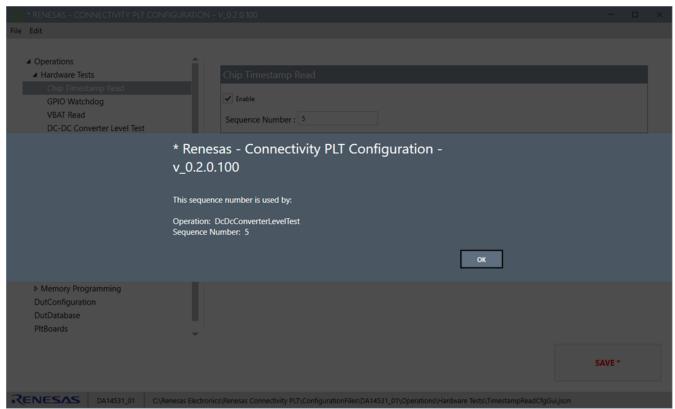

|            | Sequence number configuration            |     |

|            | Chip timestamp configuration             |     |

|            | GPIO watchdog configuration              |     |

|            | VBAT read configuration                  |     |

| Figure 55. | DC-DC converter configuration            | .50 |

|            | Active current measurement configuration |     |

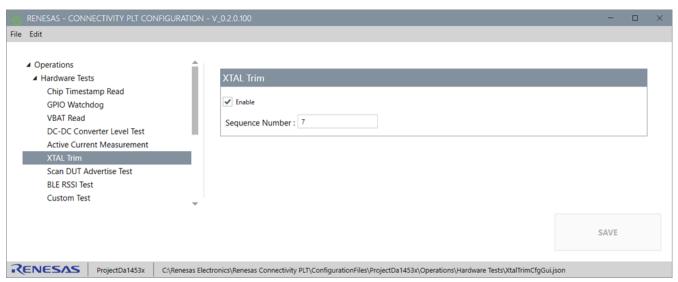

|            | XTAL configuration                       |     |

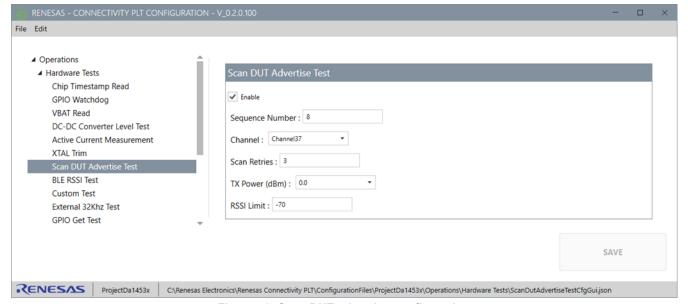

|            | Scan DUT advertise configuration         |     |

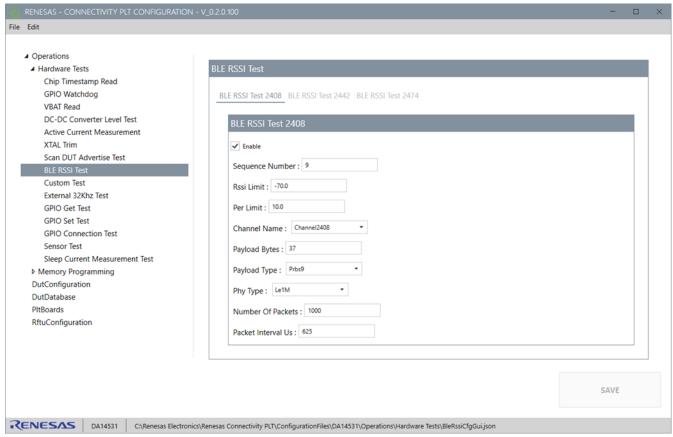

|            | Bluetooth LE RSSI configuration          |     |

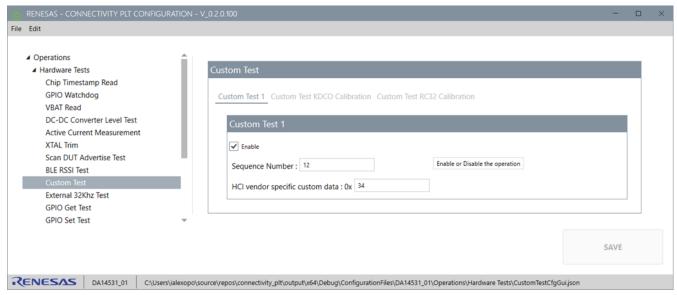

|            | Custom test configuration                |     |

| Figure 61. | Ext32kHz crystal test configuration      | .53 |

|            | GPIO get configuration                   |     |

|            | GPIO set configuration                   |     |

| _          | GPIO connection configuration            |     |

|            | Sensor test configuration 1              |     |

|            | Sensor test configuration 2              | .56 |

|            | Sleep current measurement configuration  |     |

|            | Uart BaudRate Set configuration          |     |

|            | SPI Flash Init configuration             |     |

|            | SPI Flash Frage Block configuration      |     |

|            | SPI Flash Block configuration            |     |

|            | SPI Flood configuration                  |     |

|            | SPI Flash Read configuration             |     |

|            | EEPROM Memory Write configuration        |     |

|            | OTP Memory Write configuration           |     |

|            | OTP Memory Read configuration            |     |

|            | Header Write configuration               |     |

|            | Configuration Script Write               |     |

|            | Custom Memory Write configuration        |     |

|            | Common Memory Write configuration        |     |

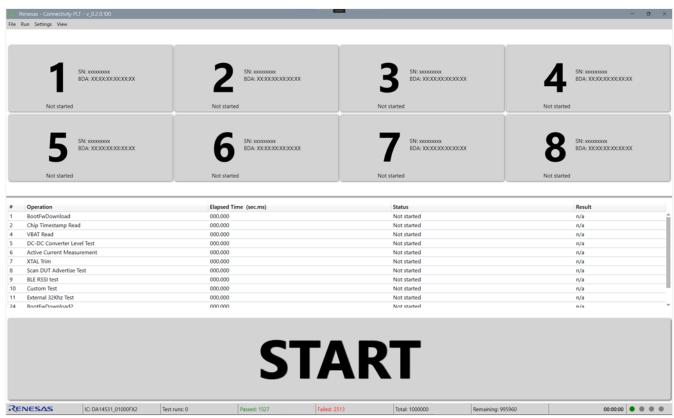

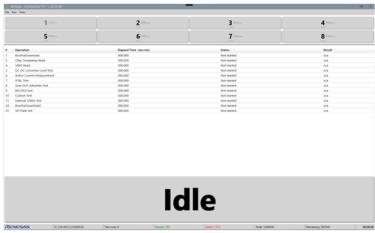

|            | Test execution start window              |     |

|            | DUTs grid                                |     |

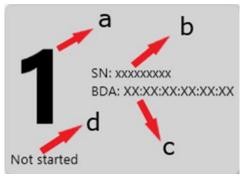

|            | Single DUT tile                          |     |

|            | Grid splitter top position               |     |

|            | Grid splitter bottom position            |     |

|            |                                          |     |

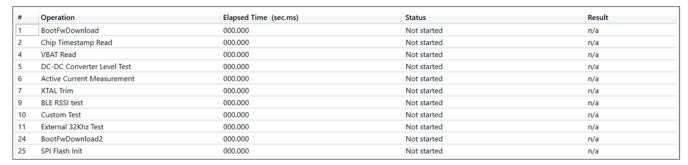

| Figure 87. Operations grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71                                                                                                                                                                                     |

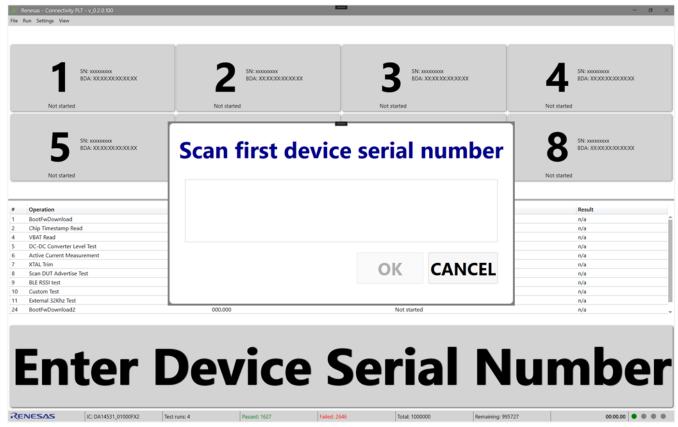

| Figure 88. Enter serial number screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

| Figure 89. Configuration reload warning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        |

| Figure 90. OTP write warning message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

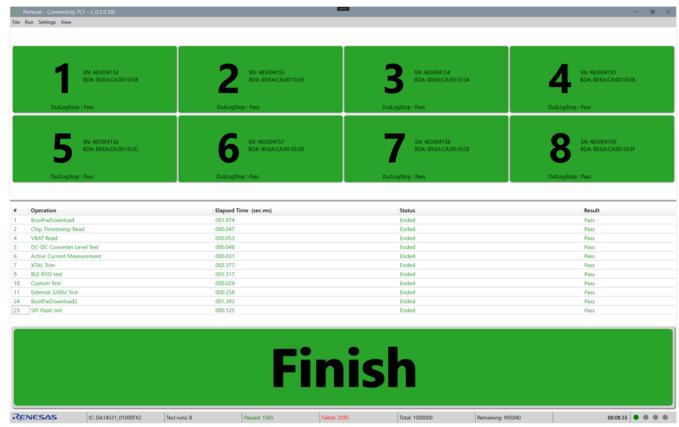

| Figure 91. Test execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                        |

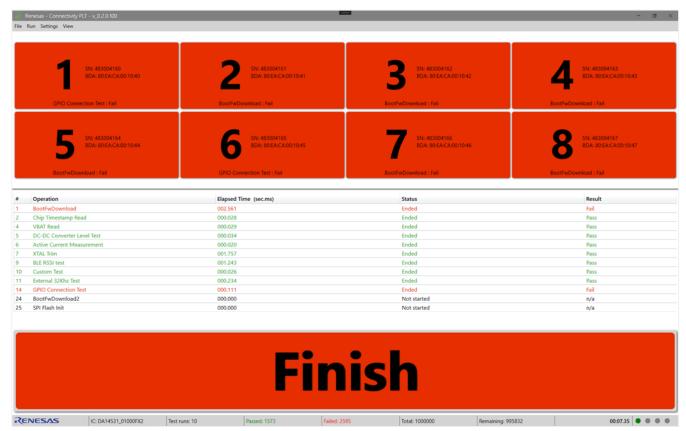

| Figure 92. DUTs fail during execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

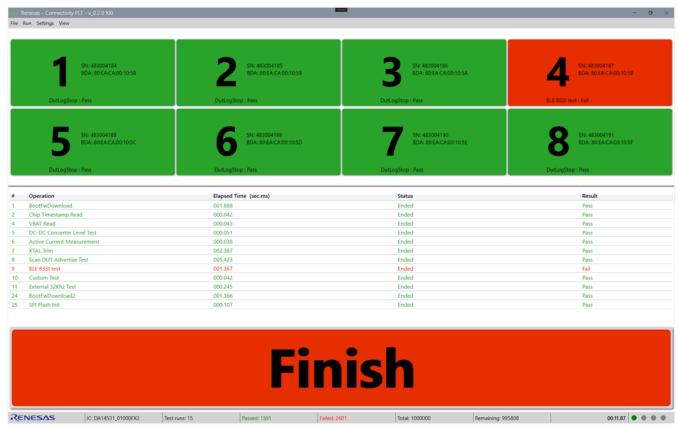

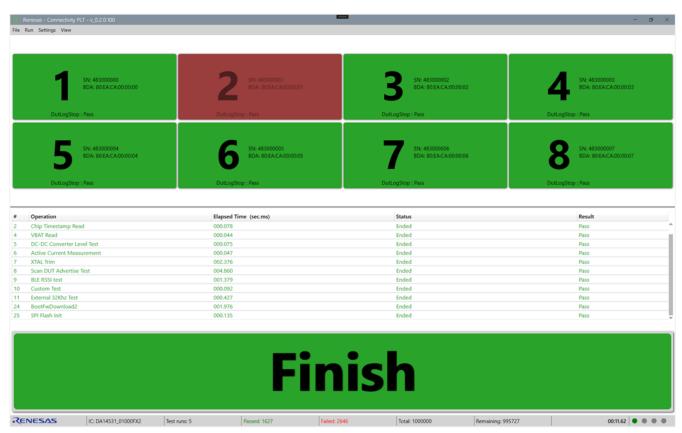

| Figure 93. Successful test sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        |

| Figure 94. Failed test sequenceFigure 95. Partially successful test sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                        |

| Figure 96. Click on DUT tile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                        |

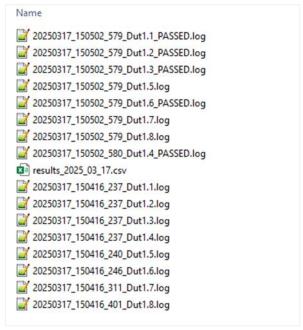

| Figure 97. Example of the log folder contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                        |

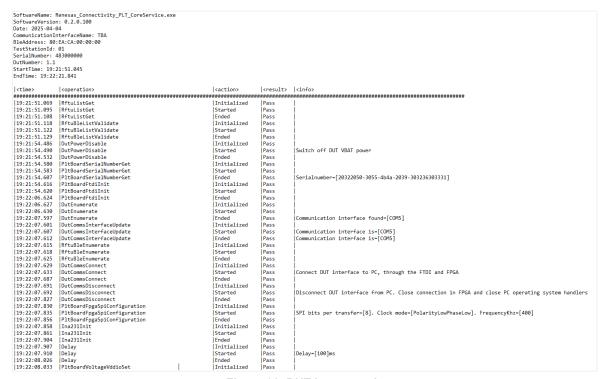

| Figure 98. DUT log example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |

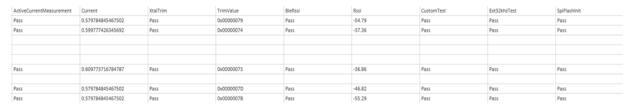

| Figure 99. CSV log example (part 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        |

| Figure 100. CSV log example (part 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

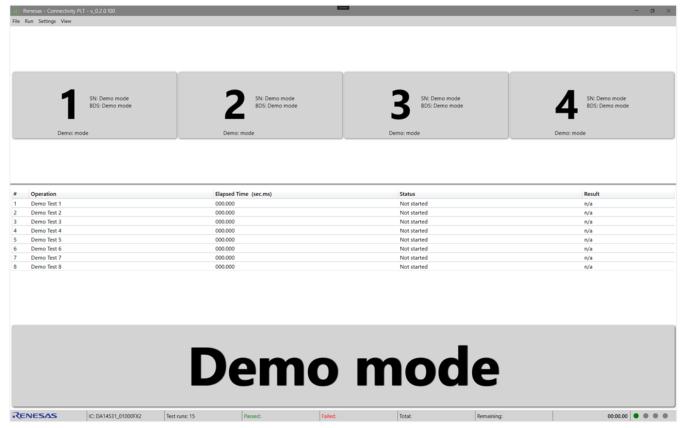

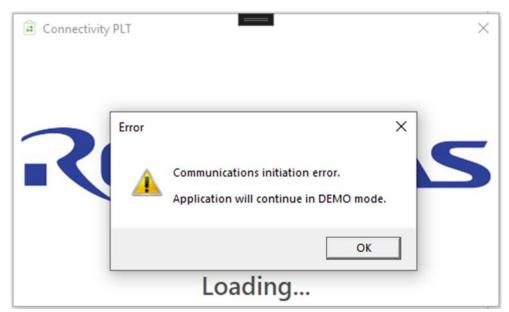

| Figure 101. Demo mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

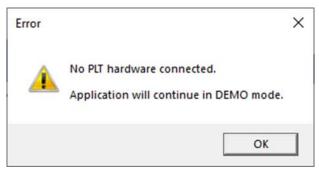

| Figure 102. Hardware communication error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                                                                                                                                                                     |

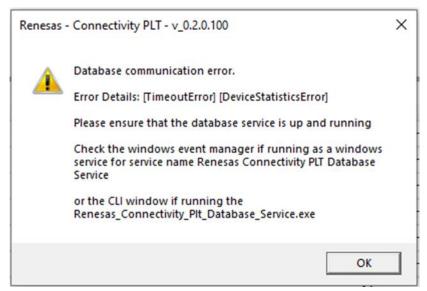

| Figure 103. Database communication error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                        |

| Figure 104. Core Service communication error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                        |

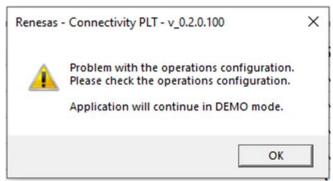

| Figure 105. Operations configuration error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |

| Figure 106. Execution CLI start screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |

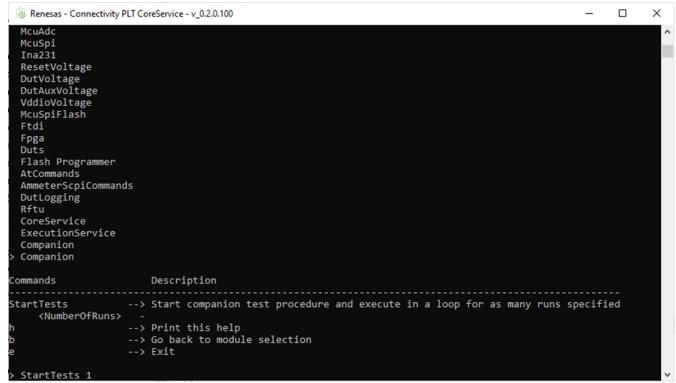

| Figure 107. Core Service in CLI mode initial screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        |

| Figure 108. Companion board tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |

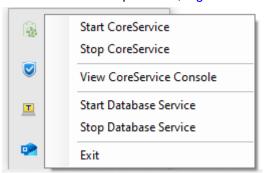

| Figure 109. Service Agent non                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                        |

| Figure 111. Service Agent Core Service log view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

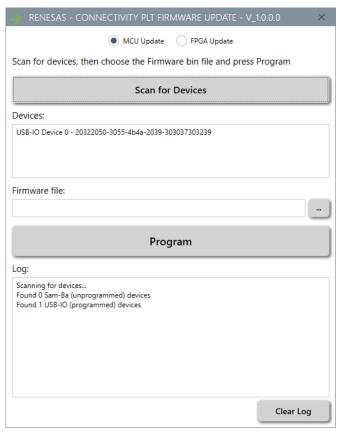

| Figure 112. Firmware update application initial screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |

| Figure 113. Device detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                        |

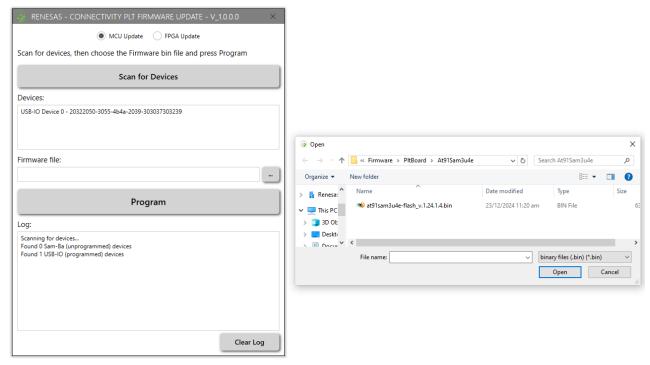

| Figure 114. Firmware update file browse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        |

| Figure 115. Firmware updatebin file loading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                        |

| Figure 116. Firmware update - Programing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                        |

| Figure 117. Example for firmware update log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 89                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| Table 1. Power supply characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

| Table 1. Power supply characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                                                                                                                                     |

| Table 1. Power supply characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11<br>12                                                                                                                                                                               |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PItBoards parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options. Table 7. SPI profile pin options                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PItBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                        |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options Table 11. Comms interface options                                                                                                                                                                                                                                                                                                     | 11 28 30 32 32 33 35 35 36                                                                                                                                                             |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PItBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options                                                                                                                                                                                                                                                                                                                                       | 11                                                                                                                                                                                     |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options Table 11. Comms interface options Table 12. SDK version                                                                                                                                                                                                                                                                               | 11 28 30 32 32 33 35 35 36 37 38                                                                                                                                                       |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options. Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options. Table 10. Bluetooth LE options. Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile                                                                                                                                                                                             | 11                                                                                                                                                                                     |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options. Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration                                                                                                                                                                  | 11 28 30 32 33 35 35 36 37 38 38 39 40 41                                                                                                                                              |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options. Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration                                                                                                                                    | 11       12       28       30       32       35       36       37       38       39       40       41       42       43                                                                |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration Table 17. Jedec configuration                                                                                                       | 11       12       28       30       32       35       36       37       38       39       40       41       42       43       43                                                       |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options. Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options. Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration Table 18. XTAL configuration Table 19. I2C configuration                                                                          | 11       12       28       30       32       35       36       37       38       39       40       41       42       43       43       44                                              |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options. Table 7. SPI profile pin options. Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options. Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration Table 18. XTAL configuration Table 19. I2C configuration Table 19. I2C configuration Table 19. I2C configuration                 | 11       12       28       30       32       35       36       37       38       39       40       41       42       43       44       44       44       44       44       44          |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration Table 18. XTAL configuration Table 19. I2C configuration Table 20. I2C size Table 21. I2C timings                                   | 11       12       28       30       32       33       35       36       37       38       38       39       40       41       42       43       44       44       44       44       45 |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration Table 18. XTAL configuration Table 19. I2C configuration Table 20. I2C size Table 21. I2C timings Table 22. I2C slave configuration | 11       12       30       32       35       36       37       38       39       40       41       42       43       44       44       45       45                                     |

| Table 1. Power supply characteristics Table 2. DUT connection characteristics Table 3. GPIO characteristics Table 4. PltBoards parameters Table 5. RFTU configurations options Table 6. SPI profile options Table 7. SPI profile pin options Table 8. UART options Table 9. Reset options Table 10. Bluetooth LE options Table 11. Comms interface options Table 12. SDK version Table 13. Memory configuration Table 14. Peripheral GPIO Table 15. SPI profile Table 16. Pins configuration Table 17. Jedec configuration Table 18. XTAL configuration Table 19. I2C configuration Table 20. I2C size Table 21. I2C timings                                   | 11       12       30       32       35       36       37       38       38       39       40       41       42       43       44       45       45       46                            |

| Table 25. Type of hardware tests            | 17 |

|---------------------------------------------|----|

|                                             |    |

| Table 26. Types of memory tests             |    |

| Table 27. Uart BaudRate Set configuration   |    |

| Table 28. SPI Flash Init configuration      | 60 |

| Table 29. SPI Flash Erase All configuration | 60 |

| Table 30. Flash erase block configuration   | 60 |

| Table 31. Flash write configuration         | 61 |

| Table 32. SPI Flash Read configuration      | 62 |

| Table 33. EEPROM Memory Write configuration | 63 |

| Table 34. EEPROM Memory Read configuration  | 64 |

| Table 35. OTP Memory Write configuration    | 64 |

| Table 36. OTP Memory Read configuration     | 65 |

| Table 37. Header Write configuration        | 66 |

| Table 38. Configuration Script Write        | 66 |

| Table 39. Custom Memory Write configuration |    |

| Table 40. Common Memory Write configuration |    |

| Table 41. CLI commands                      | 81 |

| Table 42. Core service messages             | 82 |

| Table 43. Core service error messages       |    |

| Table 44. Product standards                 |    |

| Table 45 Test standards                     | 91 |

# 1. Terms and Definitions

BDA Bluetooth® Device Address

Bluetooth LE Bluetooth® Low Energy

BT Classic Bluetooth® Classic

CS Configuration Script (a Renesas DA14xxx devices memory area related to production testing)

DMM Digital Multi Meter

DIP Switch Dual in-line package switches

DUT Device Under Test

HCI Host Controller Interface

PLT Production Line Tool

RF Radio Frequency

RFTU Radio Frequency Test Unit

## 2. References

- [1] DA14531 Datasheet, Renesas Electronics.

- [2] DA14535 USB kit DA14535-00FXDEVKT-U.

- [3] DA14695 USB kit DA14695-00HQDEVKT-U.

- [4] https://www.microchip.com/en-us/development-tool/sam-ba-in-system-programmer

- [5] https://www.ni.com/en/support/downloads/drivers/download.ni-visa.html#565016

Note 1 References are for the latest published version, unless otherwise indicated.

# 3. Introduction

The Renesas Connectivity PLT is designed to test, calibrate, and perform memory operations for multiple devices under test (DUTs) in parallel. Specifically, up to four Connectivity PLT boards with eight test sites each can be daisy chained to achieve 32 test sites.

The following parts are delivered with the tool:

- Hardware:

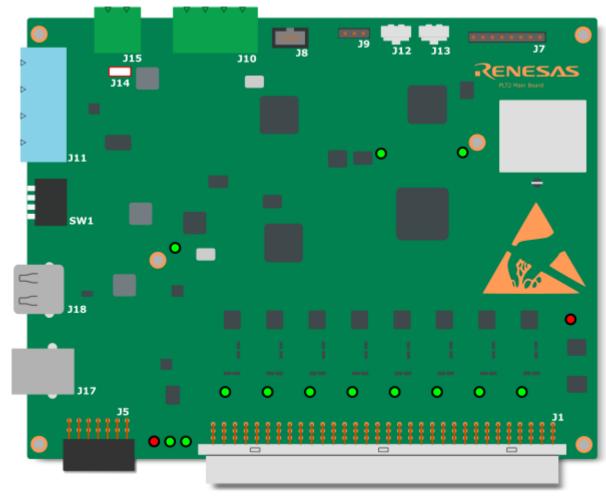

- Main board (Figure 1)

- Power cable

- Software:

- Installation package for Windows environment

- Documents

- User manual

- · Electrical schematics

- Gerber files

- Bill of Materials.

Figure 1. Main board

# 4. System Overview

# 4.1 Typical Setup

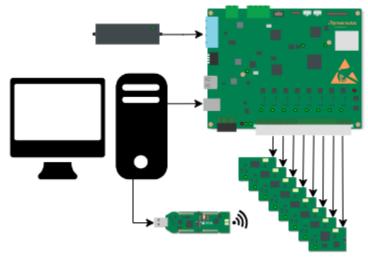

The Connectivity PLT is a configurable tool that can be adapted to the needs of the production line. Figure 2 shows a simple configuration that consists of a single Connectivity PLT board with eight connected DUT's powered by an external power supply. The host PC is connected to the Connectivity PLT board and to an RF test unit (in this case the SmartBond™ DA14695 Bluetooth® Low Energy 5.2 USB Development Kit). The host has a connected screen so it can run the Connectivity PLT execution application.

Figure 2. Basic setup

# 4.2 Typical Test Sequence

The tool performs the following actions:

- 1. The production test firmware is downloaded to the DUT.

- 2. Factory timestamp is read from OTP.

- 3. Automatic crystal (XTAL) trimming is performed.

- 4. RF RSSI RX tests are performed.

- 5. Advertise scan test is performed.

- 6. Flash programmer firmware is downloaded to RAM

- 7. The (customer) application firmware is downloaded (into OTP, QSPI flash).

- 8. The OTP Configuration Script and Header are written to OTP.

- 9. OTP and Flash memory are read back for verification.

- 10. DUTs are powered down.

All actions are performed at the same time on all DUTs up to 32 devices.

# 5. Hardware Setup

# 5.1 Power Supply Connections

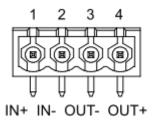

The Connectivity PLT is designed for use with an external power supply connected to J11. The type of connector is a four-pin terminal block (TBP01R1W-508-04BE). Table 1 shows the requirements for this power supply, and Figure 3 shows the pinout of J11, indicating that the power connector allows for daisy chaining.

Figure 3. Power Connector J11

Table 1. Power supply characteristics

| Parameter         | Description          | Conditions                    | Min | Тур | Max | Unit |

|-------------------|----------------------|-------------------------------|-----|-----|-----|------|

| Vin               | Input supply voltage |                               | 11  | 12  | 15  | V    |

| lin               | Input supply current | Single Connectivity PLT board | 2   |     |     | Α    |

| I <sub>IDLE</sub> | IDLE current draw    | Single Connectivity PLT board |     | 200 |     | mA   |

### 5.2 DUT Connections

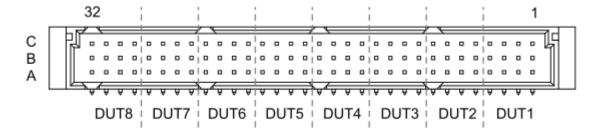

The DUT connector is an interface for up to eight application boards that can be connected. The type of connector is a 96pin DIN 41612 male connector from Amphenol (86093967113745ELF). Mating parts can be found on the producer's website. The power and the signals to the application board go through this connector. The connector is divided into eight sections, one section per DUT (Figure 4). The pin layout of each section is the same and can be found in Figure 5.

Figure 4. DUT connector

Figure 5. DUT connector pin layout

Table 2. DUT connection characteristics

| Parameter             | Description                     | Conditions                      | Min | Typical | Max | Unit |

|-----------------------|---------------------------------|---------------------------------|-----|---------|-----|------|

| V <sub>DUT</sub>      | Configurable DUT supply voltage |                                 | 1.1 |         | 5.0 | V    |

| I <sub>DUT</sub>      | DUT current                     | Independent of V <sub>DUT</sub> |     |         | 300 | mA   |

| V <sub>AUX</sub>      | Configurable Auxiliary voltage  |                                 | 0   |         | 5.0 | V    |

| laux                  |                                 | 1 kΩ series resistor            |     |         | 1   | mA   |

| AIN                   | Analog input voltage            |                                 | 0   |         | 5.0 | V    |

|                       | Input impedance                 |                                 |     | 830     |     | kΩ   |

|                       | ADC resolution (LSB)            |                                 |     | 1.25    |     | mV   |

| V <sub>GPIO</sub>     | Configurable GPIO voltage       |                                 | 1.2 |         | 3.3 | V    |

| V <sub>GPIO_OUT</sub> | GPIO out high voltage           | Percentage of V <sub>GPIO</sub> | 70  |         |     | %    |

|                       | GPIO out low voltage            | Percentage of V <sub>GPIO</sub> |     |         | 30  | %    |

| IGPIO_OUT             | GPIO output current             | Depends on FPGA setting         |     |         |     | mA   |

| V <sub>GPIO_IN</sub>  | GPIO in high threshold          | Percentage of V <sub>GPIO</sub> | 70  |         |     | %    |

|                       | GPIO in low threshold           | Percentage of V <sub>GPIO</sub> |     |         | 30  | %    |

|                       | GPIO in voltage range           |                                 | 0   |         | 3.3 | V    |

| V <sub>TX</sub>       | TX high voltage                 | Percentage of V <sub>GPIO</sub> | 70  |         |     | %    |

|                       | TX low voltage                  | Percentage of V <sub>GPIO</sub> |     |         | 30  | %    |

|                       | Configurable reset voltage      | Percentage of V <sub>GPIO</sub> | 70  |         |     | %    |

#### 5.3 **GPIO Connections**

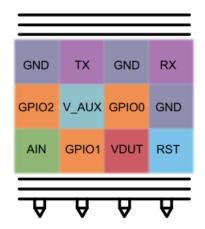

The GPIO connector is an optional galvanically isolated interface to external test equipment such as the testing fixture. The connector consists of one general purpose input and one general purpose output. The output does not supply its own power, it must be externally powered. The type of connector is a 4pin WR-TBL terminal block from Würth Elektronik (691313510004).

Figure 6. GPIO connector J10

Table 3. GPIO characteristics

| Parameter | Description                    | Min | Typical | Max | Unit |

|-----------|--------------------------------|-----|---------|-----|------|

| Vouтput   | General purpose output voltage |     | 24      | 80  | V    |

| Іоитрит   | General purpose output current |     |         | 5   | mA   |

| VINPUT    | General purpose input voltage  | 2   |         | 24  | V    |

# 5.4 Daisy Chaining

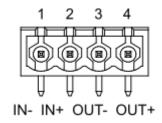

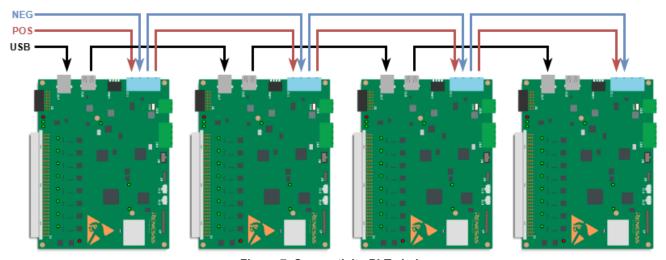

The Connectivity PLT allows for up to four Connectivity PLT mainboards to be connected in a chain. Each Connectivity PLT board has a USB in (J17) and a USB out (J18). Each output connects to the next board's input, up to a maximum of four boards, see Figure 7. The USB must be chained from board to board and cannot be connected in any other way (such as through a hub). The power may however be connected as desired, if the requirements mentioned in Section 5.1 are met. Figure 8 shows an example of alternative power connections.

Figure 7. Connectivity PLT chain

Figure 8. Connectivity PLT chain alternative

## 5.4.1 Addressing

When using multiple Connectivity PLT boards, the address on each of the boards needs to be set using DIP switches SW1. The switches are numbered, and the ON position is marked on the switch housing. The addressing is in binary format and switch number 1 is the least significant bit. For example, to set board number 3, switches 1 and 2 should be ON, and switches 3 and 4 should be OFF.

## 5.4.2 Sleep Current Measurement Using External DMM

Using externally connected current measurement equipment on J15, the Connectivity PLT can provide precise sleep current measurements for the DUTs. The current measurement is done on the VDUT rail so all DUT's are measured simultaneously. A jumper on J14 is used to bypass the external current measurement.

To set up the sleep current measurement with an external instrument, jumper J14 must be removed and a connection between J15 and the instrument needs to be made. Two wires from the positive and negative current measurement connections of the DMM must be connected to the terminal block for J15. The instrument must be NI VISA compatible through a USB connection or through a GPIB interface. The implemented protocol is compatible with Agilent/Keysight 3440x common among many DMMs.

The NI VISA drivers and software also need to be installed, see Section 6.4.

# 5.5 Production Line Setup

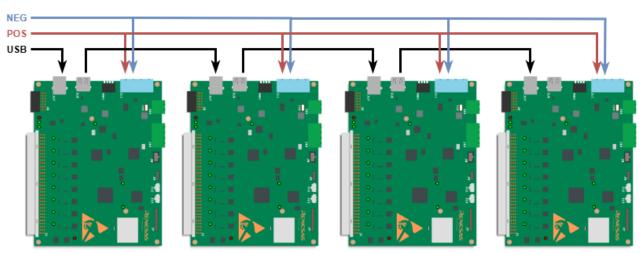

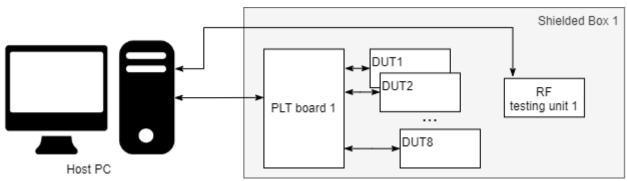

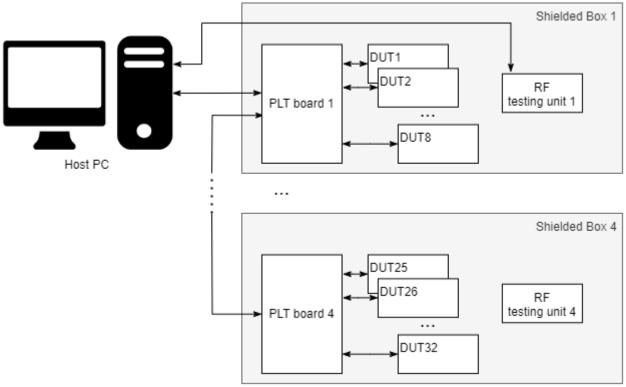

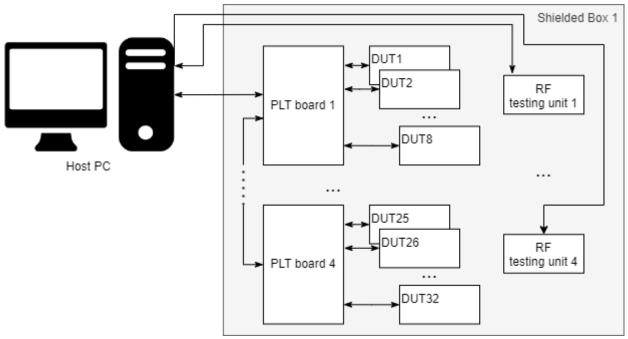

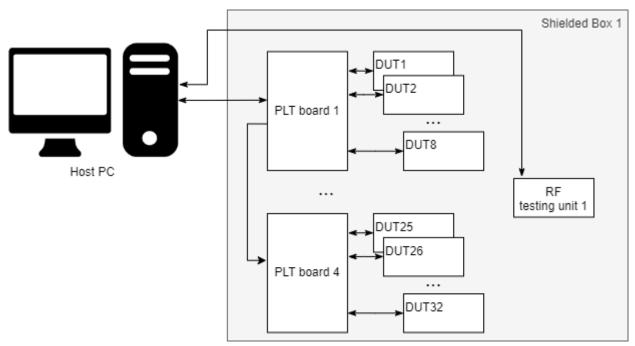

To deploy the Connectivity PLT in a production environment, there are some considerations that must be made regarding the RF environment. If any RF tests are to be performed by the Connectivity PLT, there should be minimal background noise and interference. The recommended way to achieve this in any production environment is to place the Connectivity PLT main board(s), DUT's, and RF testing unit in a shielded box. Figure 9 shows a single board and single RFTU setup, and Figure 12. When multiple PLT main boards and multiple RFTUs are used, they can be set up in multiple shieled boxes (Figure 11) or a single shielded box (Figure 12).

Figure 9. Connectivity PLT in a shielded box

Figure 10. Connectivity PLT chain in multiple shielded boxes

Figure 11. Connectivity PLT chain in single shielded box with multiple RF testing units

Figure 12. Connectivity PLT chain in single shielded box

### 6. Installation

#### 6.1 Introduction

This section provides information on how to install the Connectivity PLT software. The Connectivity PLT is not a single application but a group of services and applications that can be installed on a single host or multiple networked machines. The installation process differs depending on the individual setup of the production line.

A single installer is used for all types of installation.

## 6.2 Architecture and Different Setup Strategies

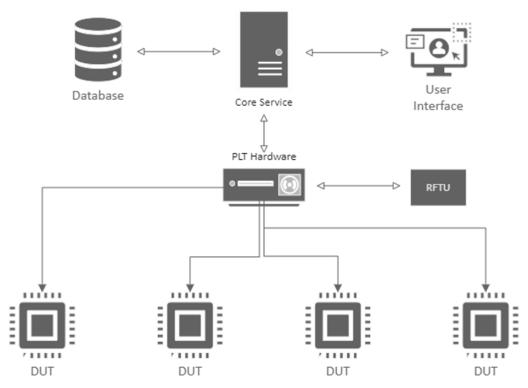

The Connectivity PLT is split into two services and a few user interface applications, see Figure 13.

Figure 13. Connectivity PLT Architecture

### 6.2.1 PLT Services

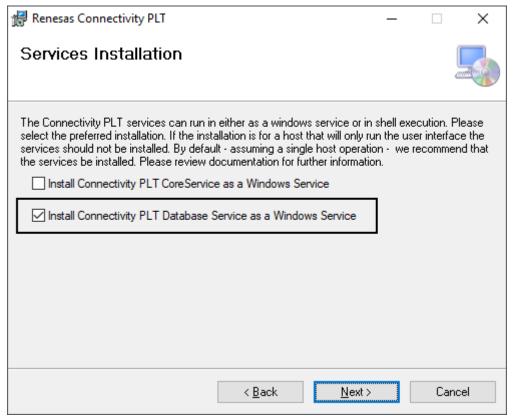

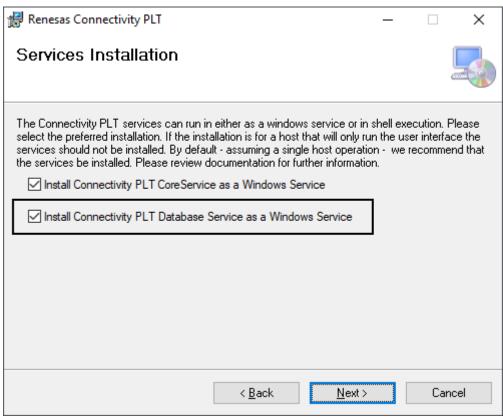

The Connectivity PLT installer can install two Windows services:

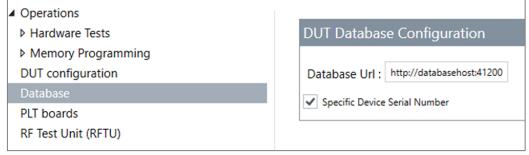

- The Renesas Connectivity PLT Database Service a host service for the main database that holds all the production related data such as serial numbers, BD addresses, test logs and results.

- The Renesas Connectivity PLT Core Service —the main service responsible for executing all operations at the host machine which has a physical connection to the PLT hardware.

These services can either be installed and run as windows services or can be manually started to run in a shell window and can be installed on the same system or on separate networked machines.

### 6.2.2 PLT Applications

- Connectivity PLT the main application which provides the user interface to the Connectivity PLT execution. This application can run on a separate but networked system to the core service or locally at the same system.

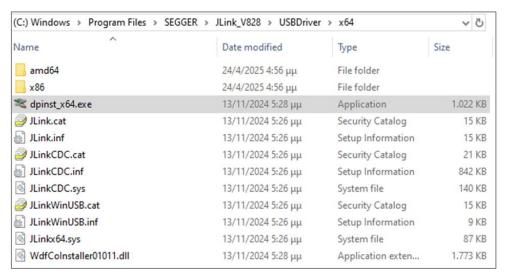

- Connectivity PLT CLI a command line interface with similar functionality to the main application but without