**User's Manual**

# V<sub>RC</sub>4171A™ Companion Chip

for VR41xx™ Family MIPS® RISC Microprocessors

| 1. | INTRODUCTION 1-1                                                                                                                                                                     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | PIN FUNCTIONS                                                                                                                                                                        |

| 3. | MAIN CLOCK CONTROL 3-1                                                                                                                                                               |

| 4. | CARD CONTROLLERS 4-1                                                                                                                                                                 |

|    | System Memory         4-3           Card Memory Access         4-3                                                                                                                   |

|    | Access of Card I/O Addresses                                                                                                                                                         |

|    | CompactFlash Cards                                                                                                                                                                   |

| 5. | LCD CONTROLLER5-1Functional Description5-1Hardware Cursor5-3                                                                                                                         |

| 6. | ADDRESS MAPPING/DECODING 6-1                                                                                                                                                         |

| 7. | Registers                                                                                                                                                                            |

|    | Top-Level Registers         7-5           Configuration Register I         7-5           Configuration Register II         7-7                                                       |

|    | Interrupt Status Register         7-8           GPIO/*PCS Control/Data Register         7-9           Programmable Chip Select (PCS) Function 1         7-10                         |

|    | *PCS[0] Upper Starting Address A[25:16] Register                                                                                                                                     |

|    | *PCS[1] Upper Starting Address A[25:16] Register                                                                                                                                     |

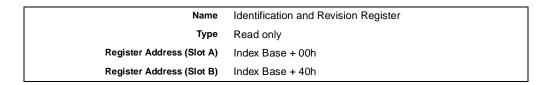

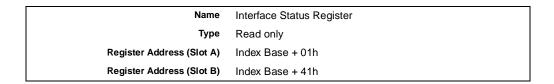

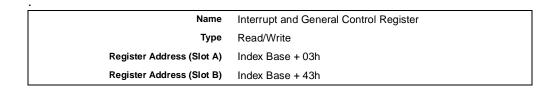

|    | PC Card Registers 7-20 Identification and Revision Register 7-20 Interface Status Register 7-21 Power and RESETDRV Control Register 7-22 Interrupt and General Control Register 7-23 |

|    | Card Status Change Register                                                                                                                                                          |

|     | I/O Control Register                                                                                                                            |              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|     | I/O Address Start Low-Byte Register I/O Address Start High-Byte Register I/O Address Stop Low-Byte Register I/O Address Stop High-Byte Register | 7-30<br>7-31 |

|     | System Memory Address Mapping Start Low-Byte Register                                                                                           | 7-35<br>7-36 |

|     | Card Memory Offset Address Low-Byte Register                                                                                                    |              |

|     | Card Detect and General Control Register                                                                                                        | 7-42         |

|     | Card Voltage Select Register                                                                                                                    |              |

| LCE | Panel Select Register Panel Control Register Power Mode Control Register                                                                        | 7-45<br>7-46 |

|     | VMCLK Enable Register                                                                                                                           |              |

|     | Video FIFO/Memory Interface Control Register                                                                                                    |              |

|     | Horizontal Display Register                                                                                                                     |              |

|     | Vertical Display End Register  Vertical Display Total Register  Vertical Retrace Start Register  Vertical Retrace End Register                  | 7-55<br>7-56 |

|     | Starting Address Register                                                                                                                       |              |

|     | Hardware Cursor Control Register                                                                                                                | 7-61         |

|     | Hardware Cursor Color 0A Register                                                                                                               |              |

iv

| Hardware Cursor Color 1A Register                         | 7-65 |

|-----------------------------------------------------------|------|

| Hardware Cursor Color 1B Register                         | 7-66 |

| Hardware Cursor Origin Register                           | 7-67 |

| RAM Write Address Register                                | 7-68 |

| RAM Write Port Register 0                                 | 7-69 |

| RAM Write Port Register 1                                 | 6-70 |

| RAM Read Address Register                                 | 7-71 |

| RAM Read Port Register 0                                  | 7-72 |

| RAM Read Port Register 1                                  | 7-73 |

| Scratch Pad Register 0                                    | 7-74 |

| Scratch Pad Register 1                                    | 7-75 |

| Hardware Cursor                                           | 7-76 |

| Nonindexed Modes                                          | 7-76 |

| Indexed Modes                                             | 7-76 |

| Hardware Cursor Inverted Color                            | 7-80 |

| Programming a Color                                       | 7-80 |

| Example Programs                                          | 7-82 |

| Starting Address of Displayed Memory                      | 7-82 |

| Hardware Cursor Data Pattern for Memory                   | 7-82 |

| 8. SYSTEM IIMPLEMENTATION                                 | 8-1  |

| 9. DESIGN CONSIDERATIONS                                  | 9-1  |

| Single Slot With One 68-Pin PC Card                       | 9-2  |

| Dual Slots With Two 68-Pin PC Cards                       | 9-4  |

| Dual Slots (A: 68-Pin PC Card / B: 50-Pin CompactFlash)   | 9-6  |

| Dual Slots (A: 68-Pin PC Card / B: 60-Pin Miniature Card) | 9-8  |

| 10. PACKAGE SPECIFICATIONS                                | 10-1 |

Contents

# Introduction

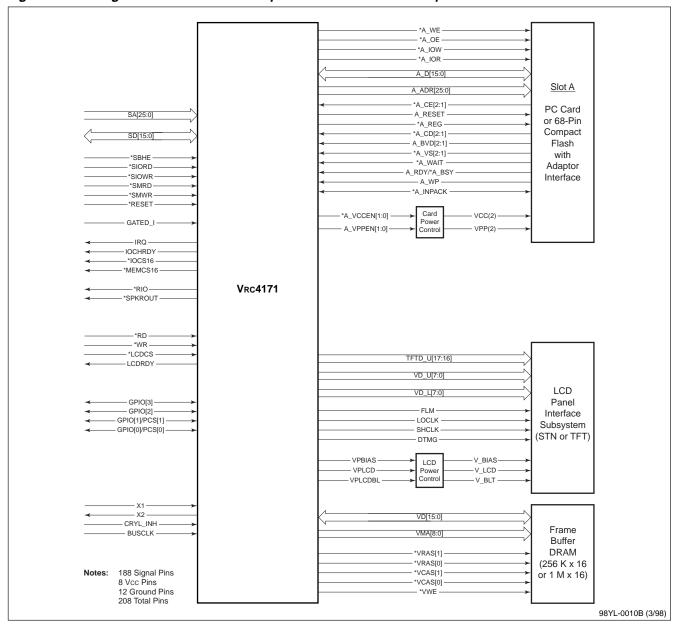

The VRC4171A<sup>™</sup> is a companion chip to NEC's 64-bit VR41xx<sup>™</sup> family of MIPS® RISC microprocessors. Together, these two devices form the essential engine for most Windows® CE-based handheld products.

### □ Processor Interface

- LCD module: \*RD, \*WR, \*LCDCS and LCDRDY signals from the VR41xx

- Other modules: mini-ISA-like 16-bit bus interface (as defined in the VR41xx)

- 256 x 18-bit on-chip color palette RAM for STN, DSTN, and TFT color panels

- On-chip hardware cursor control (32 x 32 x 2)

### □ LCD Panel Support

- 240- and 480-line single scans

- 480-line dual scans

- STN, DSTN, and TFT color panels

- Nonindexed true color (R, G, B): 15-bit (5-5-5) and 16-bit (5-6-5)

- Controller functions (320 x 240, 480 x 240, 640 x 240, and 640 x 480)

- Monochrome: up to 16 gray-scale levels (1, 2, or 4 bits/pixel)

- Color depth: 1, 2, 4, 5, 6, 8, or 16 bits/pixel

### □ Frame Buffer Memory

- One or two 3.3-volt 256K x 16-bit DRAMs (512K or 1 MB)

- One 1 MB x 16-bit DRAM (2 MB)

### □ PC Card<sup>™</sup> Slots (up to two)

- PC Card or CompactFlash<sup>™</sup> with adapter

- PC Card or CompactFlash or Miniature Card™

- PC Card controller: compliant with ExCA and PCMCIA release 2.1

- CompactFlash controller: compliant with release 1.1

- Miniature Card controller: compliant with release 1 (flash/ROM only)

### Other Features

- Up to four general-purpose I/O (GPIO) pins or up to two GPIO pins and two PCS pins

- 5-volt tolerance for LCD panel, frame buffer, and PC Card interface signals

- 208-pin LQFP package

- 3.3-volt ±5% operation

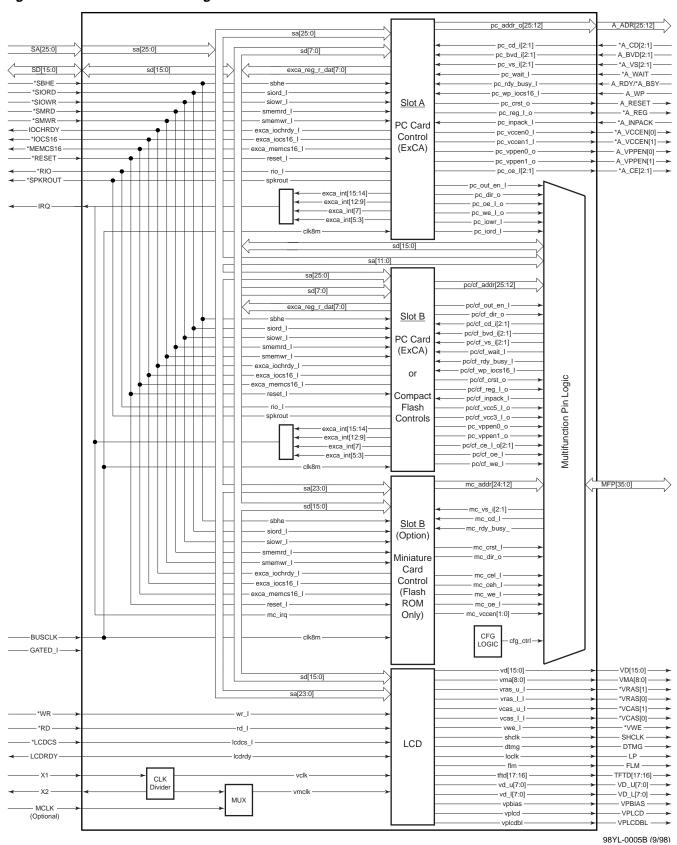

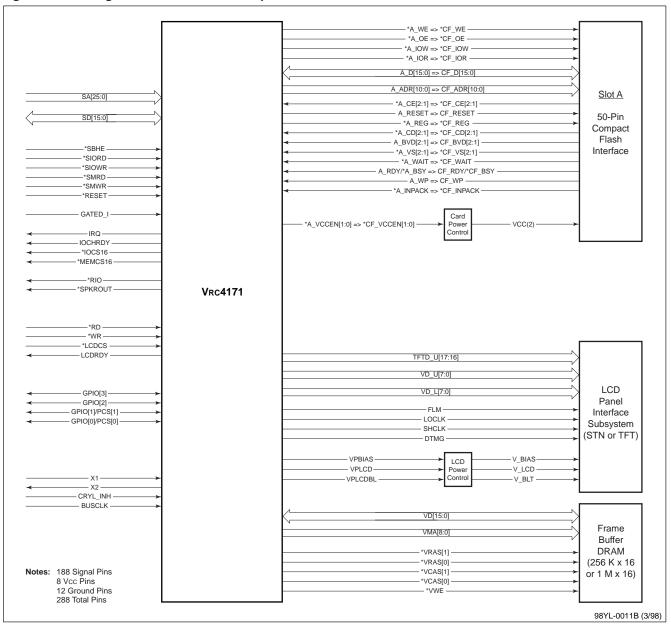

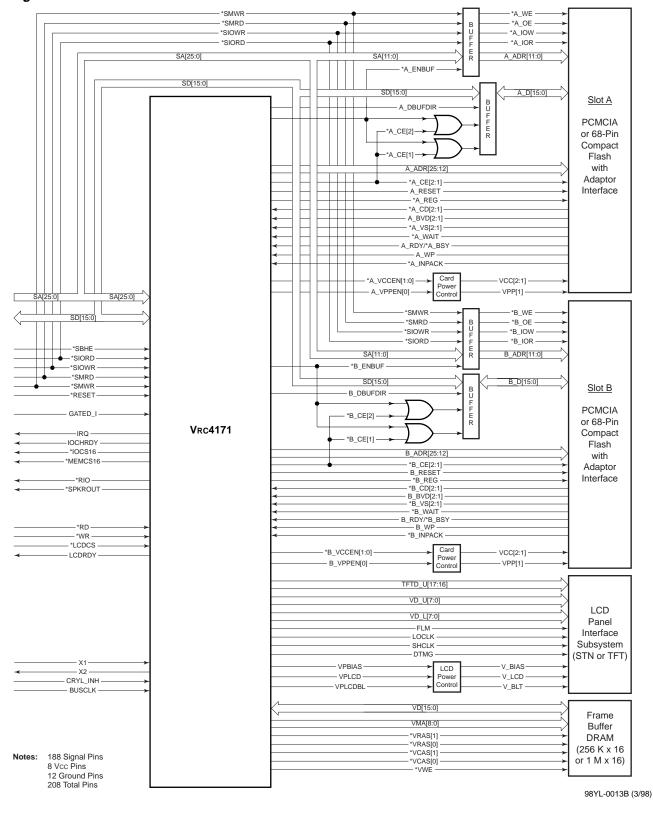

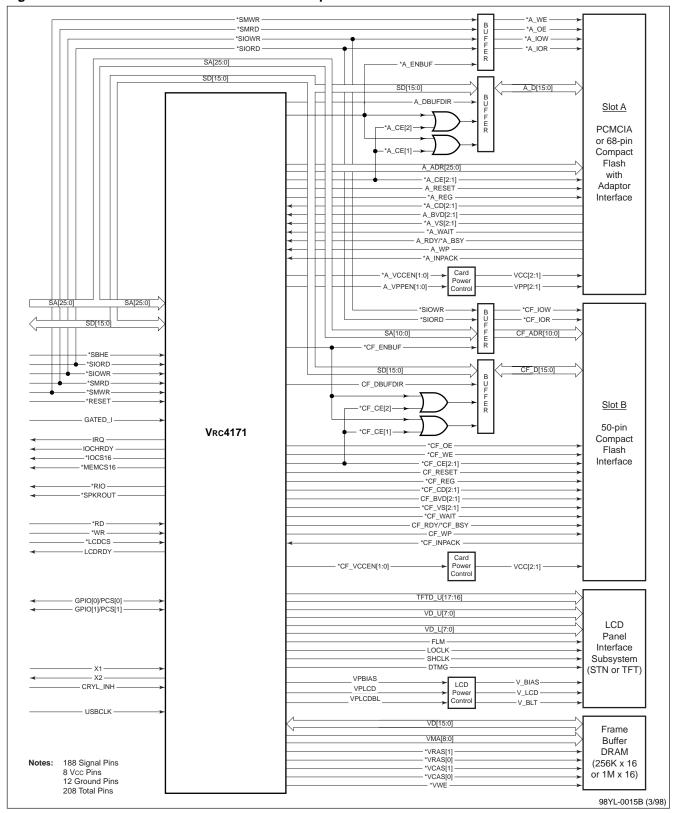

Figure 1-1. Internal Block Diagram

# Pin Functions 2

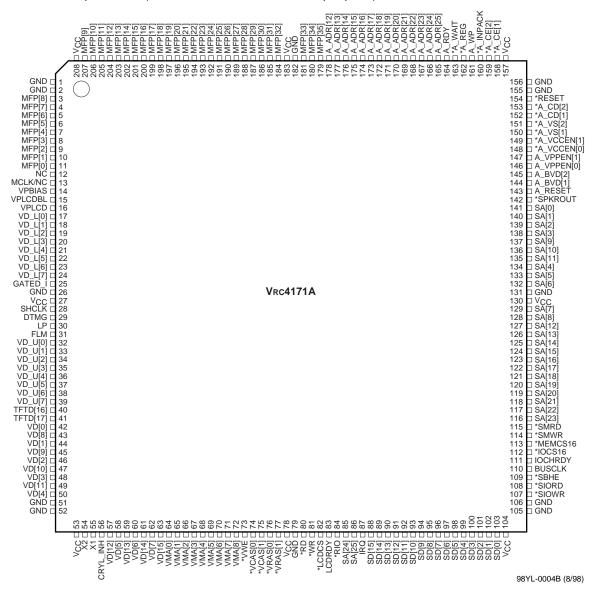

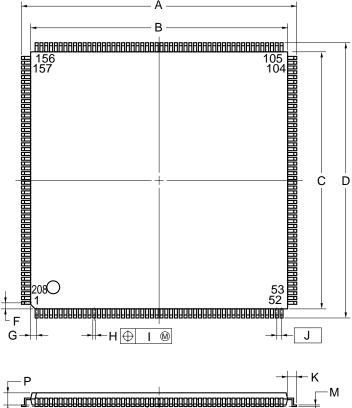

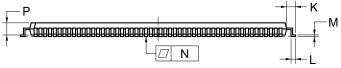

The VRC4171A companion chip has 208 total pins (Figure 2-1):

- 188 signal pins

- 20 power/ground pins

Table 2-1. Clock Pins

| Name               | No. | Туре | Drive | Function              | Description                                                                                                                                                                       |

|--------------------|-----|------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1                 | 55  | XTL  | _     | Crystal input         | Frequency operation ranges up to 50 MHz. Lower frequency crystals can be used for lower resolution LCD panels or lower bits/pixel displays to minimize overall power consumption. |

| X2                 | 54  | XTL  | _     | Crystal output        |                                                                                                                                                                                   |

| CRYL_INH           | 56  | I-S  | _     | Crystal inhibit input | Normally low; active high signal controls crystal oscillation to save power during suspend mode if a fast resume is not required (Note 2)                                         |

| BUSCLK             | 110 | CLK  | _     | ISA bus clock input   | Running at 8 MHz; actual operating frequency depends on the bit settings inside the V <sub>R</sub> 41xx                                                                           |

| GATED_I            | 25  | I-S  | _     | Gated_I input         | Normally low; active high isolates the device from any access and keeps it in this quiescent state until signal is deasserted ( <b>Note 2</b> )                                   |

| MCLK<br>(VRC4171A) | 13  | I    | -     | External clock input  | Internal 50 kΩ pulldown (optional MCLK input)                                                                                                                                     |

| Total pins         | 6   | •    | •     |                       |                                                                                                                                                                                   |

- Notes: 1. I-S: input buffer; Schmitt trigger

- Take care when asserting or deasserting gated input signals to ensure proper termination of normal accesses. Gated input signals: SA[25:0], SD[15:0], \*SIORD, \*SIOWR, \*SMRD, \*SMWR, \*RD, \*WR, \*LCDCS. \*SBHE is gated in the VRC4171A, but not in the VRC4171.

Figure 2-1. Pin Configuration

208-pin LQFP (28 mm x 28 mm with 0.5 mm pin pitch)

Table 2-2. System Bus Interface Pins

| Name       | No.                           | Туре | Drive | Function                                 | Description                                                                                                                       |

|------------|-------------------------------|------|-------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| SA[25:0]   | 85–86,<br>116–129,<br>132–141 | I    | -     | System address bus inputs                | 26-bit addresses                                                                                                                  |

| SD[15:0]   | 88–103                        | I/O  | 6 mA  | System data bus inputs                   | 16-bit data                                                                                                                       |

| *SBHE      | 109                           | I    | -     | System byte high enable input            | Active low                                                                                                                        |

| *SIORD     | 108                           | I–S  | -     | System I/O read command strobe input     | Active low                                                                                                                        |

| *SIOWR     | 107                           | I–S  | _     | System I/O write command strobe input    | Active low                                                                                                                        |

| *SMRD      | 115                           | I–S  | _     | System memory read command strobe input  | Active low                                                                                                                        |

| *SMWR      | 114                           | I–S  | -     | System memory write command strobe input | Active low                                                                                                                        |

| IOCHRDY    | 111                           | O–T  | 6 mA  | I/O channel ready output Active high     |                                                                                                                                   |

| *IOCS16    | 112                           | O–T  | 6 mA  | I/O 16-bit chip select output            | Active low; indicates to host that the current cycle is a 16-bit I/O access                                                       |

| *MEMCS16   | 113                           | O–T  | 6 mA  | Memory 16-bit chip select output         | Active low; indicates to host system that the current cycle is a 16-bit memory access                                             |

| *RESET     | 154                           | I–S  | -     | Reset input                              | Active low; should not directly connect to RSTOUT on V <sub>R</sub> 41xx (sometimes tri-stated)                                   |

| *RIO       | 84                            | 0    | 3 mA  | Ring indicator output                    | Active low; passed through *RI from I/O PC Card                                                                                   |

| *SPKROUT   | 142                           | 0    | 3 mA  | Digital audio signal output              | Active low; provides single amplitude (digital) audio waveform to drive the system speaker; passed through *SPKR from I/O PC Card |

| IRQ        | 87                            | 0    | 3 mA  | Interrupt request output                 | Active high                                                                                                                       |

| Total pins | 54                            |      |       |                                          |                                                                                                                                   |

- Notes: 1. I: input buffer 2. O: output buffer

- 3. I/O: bidirectional input/output buffer

- I–S: input buffer; Schmitt trigger

O–T: tri-statable output buffer

**Pin Functions**

Table 2-3. **LCD Graphics Controller Pins**

| Name           | No.             | Туре    | Drive | Function                                                                                                                                  | Description                                                                                                              |  |

|----------------|-----------------|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| *RD            | 80              | I–S     | _     | Read command input                                                                                                                        | Active low; asserted by the VR41xx to indicate a read cycle for RAM, ROM, or video memory                                |  |

| *WR            | 81              | I–S     | _     | Write command input  Active low; asserted by the V <sub>R</sub> 41xx to inc write cycle for RAM, ROM, or video mer                        |                                                                                                                          |  |

| *LCDCS         | 82              | I-S     | _     | (Note 6)  Active low; indicates a video memory r cycle when *LCDCS and *RD valid or memory write cycle when *LCDCS and are valid (Note 5) |                                                                                                                          |  |

| LCDRDY         | 83              | 0       | 6 mA  | Video memory data ready output                                                                                                            | Active high; indicates that video memory data is valid on the system data bus to V <sub>R</sub> 41xx CPU                 |  |

| VD[15:0]       | 42–50,<br>57–63 | I/O-5V  | 3 mA  | Video frame buffer memory data bus                                                                                                        | 16-bit data                                                                                                              |  |

| VMA[8:0]       | 64–72           | O-5 V   | 3 mA  | Video memory addresses                                                                                                                    | 9 bits for 256K x 16-bit DRAM                                                                                            |  |

| VRAS1/<br>VMA9 | 77              | O-5 V   | 3 mA  | Video memory upper row address strobe control 1 output                                                                                    | Active low signal for second 256K x 16-bit DRAM or 10th address bit of 1M x 16-bit DRAM; configured at power up (Note 7) |  |

| VRAS0          | 76              | O-5 V   | 3 mA  | Video memory upper row address strobe control 0 output                                                                                    | Active low                                                                                                               |  |

| *VCAS[1:0]     | 74–75           | I/O-5 V | 3 mA  | Video memory upper-byte/lower-byte column address strobe control outputs                                                                  | Active low                                                                                                               |  |

| *VWE           | 73              | O-5 V   | 3 mA  | Video memory write command input                                                                                                          | Active low                                                                                                               |  |

| SHCLK          | 28              | O-5 V   | 6 mA  | LCD shift clock output                                                                                                                    | Shifts data into x-driver of the panel                                                                                   |  |

| DTMG           | 29              | O-5 V   | 6 mA  | TFT panels data enable output                                                                                                             |                                                                                                                          |  |

| LP             | 30              | O-5 V   | 6 mA  | LCD line pulse output                                                                                                                     |                                                                                                                          |  |

| FLM            | 31              | O-5 V   | 6 mA  | LCD first line marker                                                                                                                     |                                                                                                                          |  |

| TFTD[17:16]    | 40–41           | O-5 V   | 6 mA  | TFT panel data output                                                                                                                     | Uppermost two data bits of TFT panels' 18 bits                                                                           |  |

| VD_U[7:0]      | 32–39           | O-5 V   | 6 mA  | LCD upper-half screen data output                                                                                                         | 8 bits                                                                                                                   |  |

| VD_L[7:0]      | 17–24           | O-5 V   | 6 mA  | LCD lower-half screen data output                                                                                                         | 8 bits                                                                                                                   |  |

| VPLCD          | 16              | O-5 V   | 3 mA  | LCD panel driver power control output                                                                                                     | Active high                                                                                                              |  |

| VPLCDBL        | 15              | O-5 V   | 3 mA  | LCD panel back light power control output                                                                                                 | Active high                                                                                                              |  |

| VPBIAS         | 14              | O-5 V   | 3 mA  | LCD panel bias power control output                                                                                                       | Active high                                                                                                              |  |

| Total pins     | 59              |         |       |                                                                                                                                           |                                                                                                                          |  |

- Notes: 1. I-S: input buffer; Schmitt trigger

- 2. O: output buffer

- 3. O-5 V: output buffer; 5 V tolerant

4. I/O-5 V; bidirectional input/output buffer; 5 V tolerant

- 5. A23=0 for video memory access; A23=1 for LCD control register access.

6. See Figure \_\_ for a hardware hookup example.

- 7. Refer to Video FIFO/Memory Interface Control Register D4-D3.

Table 2-4. PC Card Controller Pins (Partial)

| Name           | No.     | Туре   | Drive | Function                            | Description                                                                                                     |

|----------------|---------|--------|-------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| A_RESET        | 143     | O-T/5V | 6 mA  | Reset output                        | Active high                                                                                                     |

| A_ADR[25:12]   | 165-178 | O-T/5V | 6 mA  | Address bus                         |                                                                                                                 |

| A_BVD[2:1]     | 145-144 | I-S/5V | -     | Battery voltage detect inputs       | Active high                                                                                                     |

| *A_CD[2:1]     | 152-153 | I-S/5V | _     | Card detect inputs                  | Active low                                                                                                      |

| *A_CE[2:1]     | 158-159 | O-T/5V | 6 mA  | Chip enable output                  | Active low                                                                                                      |

| *A_VS[2:1]     | 150-151 | I-S/5V | _     | Voltage sense inputs                | Active low                                                                                                      |

| *A_REG         | 162     | O-T/5V | 6 mA  | Attribute memory chip select output | Active low                                                                                                      |

| A_RDY/*A_BSY   | 164     | I–5V   | -     | Drive ready / busy input            |                                                                                                                 |

| *A_WAIT        | 163     | I–5V   | _     | Wait input                          | Active low                                                                                                      |

| A_WP           | 161     | I–5V   | -     | Write protect input                 | Active high                                                                                                     |

| *A_VCCEN [1:0] | 148-149 | O-5V   | 3 mA  | Vcc enable outputs                  | Active low                                                                                                      |

| A_VPPEN [1:0]  | 146-147 | O-5V   | 3 mA  | Programming voltage enable outputs  | Active high                                                                                                     |

| *A_INPACK      | 160     | I/O-5V | 3 mA  | Input acknowledge input             | Active low data buffer enable signal eliminates external OR gate to minimize system component count (Table 2-6) |

| Total pins     | 32      |        | •     |                                     |                                                                                                                 |

- Notes: 1. O–T/5V: tri-statable output buffer; 5-volt tolerant 2. I–S/5V: input buffer; Schmitt trigger; 5-volt tolerant 3. I–5V: input buffer; 5-volt tolerant

- **4.** O–5V; output buffer; 5-volt tolerant

- 5. I/O-5V: bidirectional input/output buffer; 5-volt input tolerant

Table 2-5. Memory Card Slot Options

| Slot         | Туре                            | Condition                                                         |

|--------------|---------------------------------|-------------------------------------------------------------------|

| A (default)  | 68-pin PC Card                  | Without external buffers                                          |

|              | CompactFlash with adapter       |                                                                   |

| B (optional) | 68-pin PC Card                  | With external buffers (additional option with or without OR gate) |

|              | CompactFlash with adapter       |                                                                   |

|              | 50-pin CompactFlash             |                                                                   |

|              | Miniature Card (flash/ROM only) | 7                                                                 |

Table 2-6. **Multifunction Pins**

| Name       | No.                | Туре     | Drive | Single Slot     |                  |                        | Dual Slots                    |                        |                                    |

|------------|--------------------|----------|-------|-----------------|------------------|------------------------|-------------------------------|------------------------|------------------------------------|

|            |                    |          |       | A: PC Card      |                  | Card<br>Card           | A: PC Card<br>B: CompactFlash |                        | A: PC Card<br>B: Miniature<br>Card |

|            |                    |          |       |                 | With External OR | Without<br>External OR | With<br>External OR           | Without<br>External OR | With<br>External OR                |

| A_VPPEN[1] | 147                | O-5V     | 3 mA  | A_VPPEN[1]      | A_VPPEN[1]       | *A_DBUFEN [1]          | A_VPPEN[1]                    | *A_DBUFEN [1]          | A_VPPEN[1]                         |

| A_VPPEN[0] | 146                |          |       | A_VPPEN[0]      | A_VPPEN[0]       |                        | A_VPPEN[0]                    |                        | A_VPPEN[0]                         |

| *A_INPACK  | 160                | I/O-5V   |       | *A_INPACK       | *A_INPACK        | *A_DBUFEN [0]          | *A_INPACK                     | *A_DBUFEN [0]          | *A_INPACK                          |

| MFP[35]    | 179                | O-T/5V   | 6 mA  | A_ADR[11]       | B_ADR[25]        |                        | A_ADR[11]                     |                        | MC_ADR[24]                         |

| MFP[34:24] | 184-192<br>180-181 |          |       | A_ADR[10:0]     | B_ADR[24:14]     |                        | A_ADR[10:0]                   |                        | MC_ADR[23:13]                      |

| MFP[23]    | 193                | I/O-5    |       | A_D[15]         | B_ADR[13]        |                        | CF_OE                         |                        | MC_ADR[12]                         |

| MFP[22]    | 194                |          |       | A_D[14]         | B_ADR[12]        |                        | CF_WE                         |                        | MC_ADR[11]                         |

| MFP[21]    | 195                |          |       | A_D[13]         | *B_CE[2]         |                        | *CF_CE[2]                     |                        | *MC_OE                             |

| MFP[20]    | 196                |          |       | A_D[12]         | *B_CE[1]         |                        | *CF_CE[1]                     |                        | *MC_WE                             |

| MFP[19]    | 197                | I/O-S/5V |       | A_D[11]         | *B_CD[2]         |                        | *CF_CD[2]                     |                        | *MC_CEH                            |

| MFP[18]    | 198                |          |       | A_D[10]         | *B_CD[1]         |                        | *CF_CD[1]                     |                        | *MC_CEL                            |

| MFP[17]    | 199                |          |       | A_D[9]          | B_BVD[2]         |                        | CF_BVD[2]                     |                        | NC                                 |

| MFP[16]    | 200                |          |       | A_D[8]          | B_BVD[1]         |                        | CF_BVD[1]                     |                        | NC                                 |

| MFP[15:14] | 201-202            |          |       | A_D[7:6]        | *B_VS[2:1]       |                        | *CF_VS[2:1]                   |                        | *MC_VS[2:1]                        |

| MFP[13]    | 203                | I/O-5V   |       | A_D[5]          | B_RDY/*B_BSY     |                        | CF_RDY/<br>*CF_BSY            |                        | *MC_BUSY                           |

| MFP[12]    | 204                |          |       | A_D[4]          | *B_WAIT          |                        | *CF_WAIT                      |                        | NC                                 |

| MFP[11]    | 205                |          |       | A_D[3]          | B_WP             |                        | CF_WP                         |                        | NC                                 |

| MFP[10]    | 206                |          |       | A_D[2]          | *B_INPACK        | *B_DBUFEN [0]          | *CF_INPACK                    | *CF_DBUFEN [0]         | NC                                 |

| MFP[9]     | 207                |          |       | A_D[1]          | B_RESET          |                        | CF_RESET                      |                        | MC_RESET                           |

| MFP[8]     | 3                  |          |       | A_D[0]          | *B_REG           |                        | *CF_REG                       |                        | NC                                 |

| MFP[7]     | 4                  | O-T/5V   |       | *A_IOR          | *A_ENBUF         |                        | *A_ENBUF                      |                        | A_ENBUF                            |

| MFP[6]     | 5                  |          |       | *A_IOW          | A_DBUFDIR        |                        | A_DBUFDIR                     |                        | A_DBUFDIR                          |

| MFP[5]     | 6                  |          |       | *A_OE           | *B_ENBUF         |                        | *CF_ENBUF                     |                        | MC_ENBUF                           |

| MFP[4]     | 7                  |          |       | *A_WE           | B_DBUFDIR        |                        | CF_DBUFDIR                    |                        | MC_DBUFDIR                         |

| MFP[3]     | 8                  | I/O-5V   |       | GPIO[3]         | *B_VCCEN[1]      |                        | *CF_VCCEN[1]                  |                        | *MC_VCCEN [1]                      |

| MFP[2]     | 9                  |          |       | GPIO[2]         | *B_VCCEN[0]      |                        | *CF_VCCEN[0]                  |                        | *MC_VCCEN [0]                      |

| MFP[1]     | 10                 | 1        |       | GPIO[1]/*PCS[1] | B_VPPEN[1]       | *B_DBUFEN [1]          | GPIO[1]/*PCS[1]               | *CF_DBUFEN[1]          | MC_CD                              |

| MFP[0]     | 11                 |          |       | GPIO[0]/*PCS[0] | B_VPPEN[0]       |                        | GPIO[0]/*PCS[0]               |                        | MC_CINS                            |

| Total pins | 36                 |          |       | •               | •                | •                      |                               | •                      | •                                  |

Notes: 1. I: input buffer

2. I–S: input buffer; Schmitt trigger

3. I–5V: input buffer; 5-volt tolerant

4. I–S/5V: input buffer; 5-volt tolerant; Schmitt trigger

5. O: output buffer6. O-T: tri-statable output buffer

**7.** O–5 V: output buffer; 5-volt tolerant

8. I/O: bidirectional input/output buffer

9. I/O-S: bidirectional input/output buffer; Schmitt trigger input

**10.** I/O–5 V: bidirectional input/output buffer; 5-volt input tolerant

11. I/O-S/5 V: bidirectional input/output buffer; 5-volt input tolerant; Schmitt trigger input

**12.** Vcc: Power (3.3 volts)

13. GND: ground

Table 2-7. External Buffer Signals

| A: PC Card<br>B: None | A: PC Card<br>B: PC Card | A: PC Card<br>B: CompactFlash | A: PC Card<br>B: Miniature Card |

|-----------------------|--------------------------|-------------------------------|---------------------------------|

| _                     | A_ADR[11:0]              | _                             | _                               |

|                       | A_D[15:0]                | A_D[15:0]                     | A_D[15:0]                       |

|                       | *A_OE                    | *A_OE                         | *A_OE                           |

|                       | *A_WE                    | *A_WE                         | *A_WE                           |

|                       | *A_IOR                   | *A_IOR                        | *A_IOR                          |

|                       | *A_IOW                   | *A_IOW                        | *A_IOW                          |

|                       | B_ADR[11:0]              | CF_ADR[10:0]                  | MC_ADR[10:0]                    |

|                       | B_D[15:0]                | CF_D[15:0]                    | MC_D[15:0]                      |

|                       | *B_OE                    | _                             | _                               |

|                       | *B_WE                    | _                             | _                               |

|                       | *B_IOR                   | *CF_IOR                       |                                 |

|                       | *B_IOW                   | *CF_IOW                       |                                 |

**Note:** See Section 8 for implementation information.

Table 2-8. Miscellaneous Pins

| Pin Name   | Pin Numbers | Туре | Drive | Description             |

|------------|-------------|------|-------|-------------------------|

| NC         | 12–13       | _    | _     | Reserved; no connection |

| Total pins | 2           |      |       |                         |

Table 2-9. Power and Ground Pins

| Pin Name   | Pin Numbers                                        | Туре | Drive | Description |

|------------|----------------------------------------------------|------|-------|-------------|

| Vcc        | 27, 53, 78, 104, 130, 157, 183, 208                | Vcc  |       | 3.3 volts   |

| Ground     | 1, 2, 26, 51, 52, 79, 105, 106, 131, 155, 156, 182 | GND  |       | 0.0 volts   |

| Total pins | 20                                                 |      |       |             |

Pin Functions NEC

# Main Clock Control 3

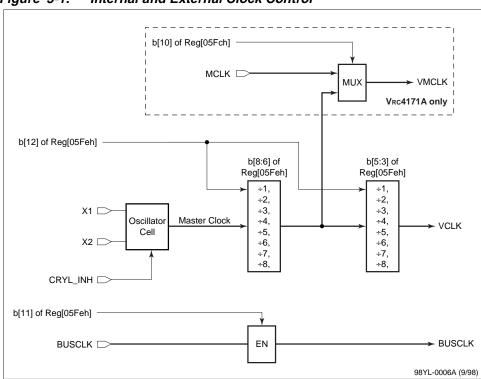

Figure 3-1. Internal and External Clock Control

**Note:** The dotted lines show the V<sub>RC</sub>4171A modification to switch (MUX) the driving source for the VMCLK output pin. This modification selects the original VMCLK signal or the new MCLK signal to output on the VMCLK pin.

Main Clock Control

Table 3-1. Main Clock Control Specifications

| Clock Type | Name     | Description                                                                            |  |  |  |

|------------|----------|----------------------------------------------------------------------------------------|--|--|--|

| External   | X1/X2    | Crystal input to generate clocks for the display controller                            |  |  |  |

|            | CRYL_INH | Crystal oscillation inhibit signal                                                     |  |  |  |

|            | MCLK     | External clock input for video memory clock                                            |  |  |  |

|            | BUSCLK   | 8-MHz system bus clock (actual frequency depends on bit setting inside the VR41xx CPU) |  |  |  |

| Internal   | VMCLK    | Video memory clock                                                                     |  |  |  |

|            | VCLK     | Video clock                                                                            |  |  |  |

# Card Controllers 4

Two independent card controllers in the VRc4171A are designed to work with a variety of commercially available memory cards:

- 68-pin PC Card (compliant with ExCA or the PCMCIA/JEIDA release 2.1 specification)

- 50-pin CompactFlash card or 68-pin CompactFlash card with PC Card adapter

- 60-pin Miniature Card

The VRC4171A supports one or two independent card slots, depending on the configuration needed (Table 4-1). The single-slot option does not require an external buffer, whereas the dual-slot option does (Table 4-2).

- Slot A supports standard PC Cards or 68-pin CompactFlash cards with a PC Card

- Slot B supports standard PC Cards, 50-pin CompactFlash cards, or 60-pin Miniature Cards, the latter of which are restricted to flash or ROM types only. There is no support for DRAM or SRAM Miniature Cards.

#### Table 4-1. **Card Options**

| Slot         | Cards Supported                 | Conditions                                      |

|--------------|---------------------------------|-------------------------------------------------|

| A (default ) | 68-pin PC Card                  | No external buffers                             |

|              | CompactFlash card with adapter  |                                                 |

| B (optional) | 68-pin PC Card                  | With external buffers (with or without OR gate) |

|              | CompactFlash card with adapter  |                                                 |

|              | 50-pin CompactFlash card        |                                                 |

|              | Miniature Card (flash/ROM only) |                                                 |

### Table 4-2. Slot Requirements

| Slot Co | onfiguration   |                                                                              |

|---------|----------------|------------------------------------------------------------------------------|

| Α       | В              | Requirements                                                                 |

| PC Card | None           | No external buffers required (with or without external OR gate)              |

| PC Card | PC Card        | Requires four external 16-bit buffers (with or without external OR gate)     |

| PC Card | CompactFlash   | Requires three external 16-bit buffers and one-half of external 4-bit buffer |

| PC Card | Miniature Card | Requires three external 16-bit buffers                                       |

Each card controller interfaces directly to either a synchronous or asynchronous ISA-compatible bus or equivalent (Figure 4-1). Card status information, accessible through the interface status register of each slot, includes the following types of information:

- · Detection of card insertion or removal

- · Memory write protect status

- Battery voltage warnings

- Power status

- Status of RDY/\*BSY signal

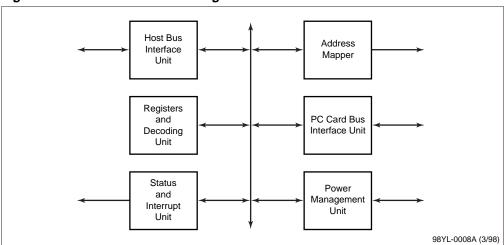

Figure 4-1. Controller Block Diagram

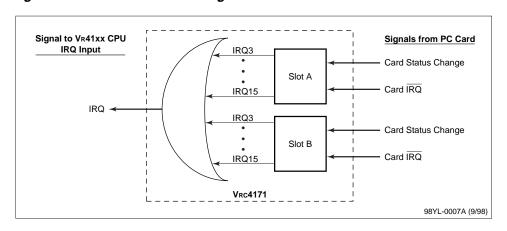

A change in status—for example, when a card is inserted or removed—causes a card status change interrupt. Various interrupt sources are enabled separately and independently in each card controller to support the PC's ISA bus software legacy use of interrupts (Figure 4-2). In MIPS design, there is only one interrupt, and a large OR gate collects all of the interrupt sources into one external interrupt output pin. That single VRC4171A external IRQ output drives the system's MIPS VR4111 CPU interrupt. The Interrupt and General Control register's IRQSEL bits steer the I/O card interrupt to an internal chip IRQ line (Table 7-21). The status of these IRQ lines can be checked by reading O5FAh, the Interrupt Status register (Table 7-7).

Figure 4-2. Internal IRQ Routing

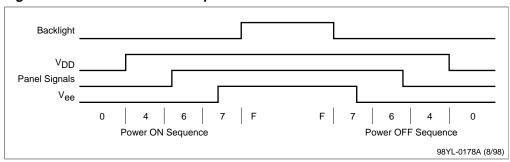

Each card controller implements power management for its own card socket via programmed options in the Power/RESETDRV Control register. Power sequencing delays specified by ExCA and PCMCIA release 2.1 are implemented in hardware.

When the memory and I/O windows are disabled and the socket is empty, each card controller automatically enters a lower-power-consuming state, the lowest level of which can be achieved by disabling all I/O and memory windows, tri-stating all output buffers, and removing power to the card socket.

When enabled for PC Card compliance, the controller operates interchangeably with two different types of PC Cards, either memory or I/O. Since the cards have different signal interface requirements, the controller incorporates multiplexers to redirect the appropriate signals (Table 4-3). These signals are configured correctly based on the setting of the CRDTYP bit in the Interrupt and General Control register. Each slot is controlled separately.

Table 4-3. GPIO/\*PCS Options

| A: PC Card                                                                                 | A: PC Card | A: PC Card                                                                           | A: PC Card        |

|--------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------|-------------------|

| B: None                                                                                    | B: PC Card | B: CompactFlash                                                                      | B: Miniature Card |

| Up to four GPIO pins or<br>two GPIO/*PCS pins<br>depending on the<br>selection (Table 2-6) | N/A        | Up to two GPIO pins or<br>two *PCS pins<br>depending on the<br>selection (Table 2-6) | N/A               |

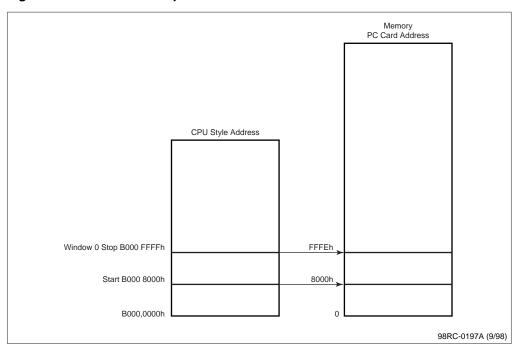

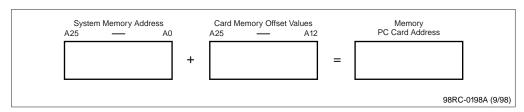

### **System Memory**

Each controller supports five independently enabled and controlled system memory address mapping windows, each of which may map into either the common or attribute memory space of the PC Card independently to control the following:

- Memory data bus width

- System bus wait states

- Software write protection

- Card enable control

Each controller also supports two independently enabled and controlled system I/O address mapping windows. A register provides access to the card information structure and card configuration registers within the PC Card's attribute memory, as described by the PCMCIA/ JEIDA specification.

#### Caution:

Do not overlap memory and I/O windows. When bit IO\_UADEC in the top-level Configuration register 1 is set to 0 (Table 7-5), the starting addresses of any memory window should be set to xx0600h or higher (up to 64K boundary xxFFFFh) to avoid conflict with internal register addresses. The ending memory address should not cross the 64K boundary. A good size for a memory window is 32K bytes, from xx8000h-xxFFFFh.

### Access of Card Memory

Card memory is accessed if all of these conditions are met.

- 1. The system memory address mapping window is enabled.

- 2. The system memory address is greater than or equal to the System Memory Address Mapping Start register A[25:12].

- 3. The system memory address is less than or equal to the System Memory Address Mapping Stop register A[25:12].

### Access of Card I/O Addresses

Card I/O addresses are accessed if all of these conditions are met.

- The I/O address mapping window is enabled.

- 2. The system I/O address is greater than or equal to the System I/O Address Mapping Start register A[15:0]; higher order addresses A[25:16] are set at a fixed value of "0100000000."

- 3. The system I/O address is less than or equal to the System I/O Address Mapping Stop register A[15:0]; higher order addresses A[25:16] are set at a fixed value of "0100000000."

- The setting of the IO\_UADEC bit does not affect control of the I/O Address Mapping window.

System software must account for each I/O address range assigned to a particular card. The reservation of a particular I/O address range for each card can reduce card power consumption since only one card is enabled during each I/O access.

### Caution:

When bit IO\_UADEC in Configuration register 1 is set to 0 (Table 7-5), the I/O address decoder for the top-level registers (Table 7-1) and the PC Card control registers (Table 7-2) does not include upper bits A[25:16]. It is recommended to set bit IO\_UADEC to 1 with software, unless the system hardware design interface dictates no fixed decoding of upper address bits A[25:16] for a system I/O address.

## CompactFlash Cards

In general, CompactFlash cards are electrically compatible with the PCMCIA ATA Standard, with minor differences that the VRC4171A handles transparently. CompactFlash cards have three modes of operation:

- 1. PC Card ATA using I/O modes

- 2. PC Card ATA using memory mode

- 3. True IDE mode

CompactFlash card configuration is controlled using the standard card configuration registers starting at address 200h in the attribute memory space. The second slot can be configured to support 50-pin CompactFlash cards.

### **Miniature Cards**

The Miniature Card controller supports only the flash and ROM requirements of the Miniature Card release 1.1 specification. Support for DRAM or SRAM Miniature Cards is not provided at this time.

# LCD Controller 5

The LCD controller is designed to work with a variety of STN and TFT color or monochrome LCD panels. It consists of the fundamental blocks shown in Figure 5-1.

Bus Write Interface Buffer Unit Display Memory/ Frame Buffer Memory Frame Buffer FIFO Power Memory DRAM Management Controller Unit Palette RAM Hardware Dithering Cursor Engine LCD Panel LCD Panel Control 98YL-0009A (9/98)

Figure 5-1. LCD Block Diagram

# Functional Description

- 1. The Bus Interface Unit (BIU) performs all handshaking between the system bus and the internal registers, memory write buffers, and power management unit.

- The write buffer enables memory write accesses to the frame buffer to occur between the processor system bus and the frame buffer DRAM without large latencies. The write buffer is designed to match the peak bandwidth of both the processor bus and the frame buffer DRAM.

- 3. The frame buffer FIFO separates the data read from the frame buffer memory during an active scan. The memory controller generates the address and controls the timing and access to the DRAM.

- 4. The palette RAM contains the color palette used for color display (Table 5-1). It is organized as 256 addresses by 18 bits (6 bits each for red, green, and blue color).

- 5. The dithering engine is used for color STN panels to provide the appearance of more colors by modulating the data as it is being written to the panel during a frame of refresh.

- The LCD panel controller functions as the timing generator for the memory read cycles to

the frame buffer FIFO and the data write cycles to the LCD panel. It provides the fundamental scanning synchronization timing signals such as frame and line synchronization and

retrace timing.

- 7. The hardware cursor function causes a 32 x 32-pixel by two-color cursor image to appear as an overlay on top of the frame buffer during display time. The hardware cursor interfaces to the memory for the cursor data and to the LCD panel control to switch the data output to the display. The hardware cursor data is stored in off-screen memory in the upper 512 bytes of the frame buffer. When displaying the pixels in the cursor area, the output from the frame buffer data is switched to the output of the cursor data

Table 5-1. TFT Panel Connection

| Color | Pin Name | Panel Name    |

|-------|----------|---------------|

| RED   | VUD_5    | RED 5 (MSB)   |

|       | VUD_4    | RED 4         |

|       | VUD_3    | RED 3         |

|       | VUD_2    | RED 2         |

|       | VUD_1    | RED 1         |

|       | VUD_0    | RED 0 (LSB)   |

| GREEN | VLD_3    | GREEN 5 (MSB) |

|       | VLD_2    | GREEN 4       |

|       | VLD_1    | GREEN 3       |

|       | VLD_0    | GREEN 2       |

|       | VUD_7    | GREEN 1       |

|       | VUD_6    | GREEN 0 (LSB) |

| BLUE  | TFTD_17  | BLUE 5 (MSB)  |

|       | TFTD_16  | BLUE 4        |

|       | VLD_7    | BLUE 3        |

|       | VLD_6    | BLUE 2        |

|       | VLD_5    | BLUE 1        |

|       | VLD_4    | BLUE 0 (LSB)  |

The graphics display data is stored in the LCD frame buffer memory and written to the frame buffer memory with a linear address. The display data is read out of the frame buffer by the LCD controller using the starting address and offset registers. This data is then clocked out to the LCD panel using a shift clock with timing based on the value in the horizontal and vertical control registers.

The pixel format used in 8-bit-per-pixel data is an address look-up table (LUT), most commonly referred to as the *color palette*. The 8-bit pixel data is used as an address into the palette RAM. For each address, a specific value of red, green, or blue is read out to the display (6 bits for each color and 18 bits total).

For formats of 5 and 6 bits per pixel, the upper used address bits are available for use as segments that make multiple simultaneous palettes available. This feature allows applications to switch palettes by reloading the on-chip palette, resulting in smoother transitions between applications that may only use a subset of the 256 color address locations available. For 1-, 2-, and 4-bit-per-pixel formats, color registers 0 through 3 are used as a pseudo-palette.

The 16-bit-per-pixel format is a direct color format. Table 5-2 shows 5-6-5 format, but a 5-5-5 format is also supported.

Table 5-2. 16-Bit 5-6-5 Pixel Format

|     | High Byte |    |    |    |     |    |   | Low Byte |   |   |     |    |   |   |   |

|-----|-----------|----|----|----|-----|----|---|----------|---|---|-----|----|---|---|---|

| 15  | 14        | 13 | 12 | 11 | 10  | 9  | 8 | 7        | 6 | 5 | 4   | 3  | 2 | 1 | 0 |

| 4   | 3         | 2  | 1  | 0  | 5   | 4  | 3 | 2        | 1 | 0 | 4   | 3  | 2 | 1 | 0 |

| RED | )         |    |    |    | GRE | EN |   |          |   |   | BLU | JE |   |   |   |

To map 16-bit pixel data to an 18-bit TFT panel, R0 and B0 must output logic 0 to the panel.

As shown in Table 5-3, the frame buffer origin is in the upper left of the display area.

Table 5-3. Frame Buffer Pixel Organization

| Pixel 00, Pixel 01 | Pixel 639    |

|--------------------|--------------|

| Pixel 640          |              |

| Pixel 153000       | Pixel 153599 |

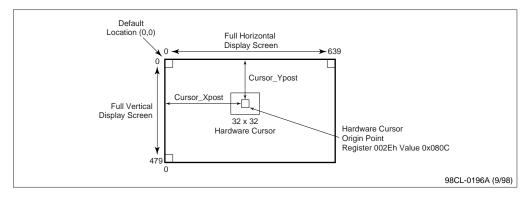

### Hardware Cursor

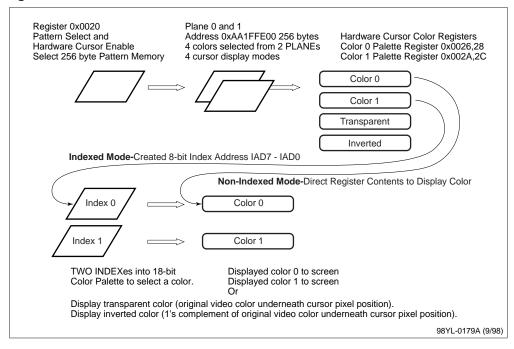

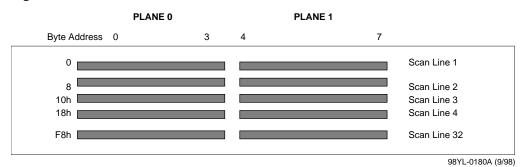

The hardware cursor operates in all standard graphic modes and supports a  $32 \times 32 \times 2$  user-defined pattern stored in the upper 512 bytes of display memory. The cursor pattern has two bits per pixel; each bit corresponds to a plane. Table 5-4 shows the cursor display state corresponding to the value of the cursor pattern. A single cursor pattern of  $32 \times 32 \times 2$  bits occupies 256 bytes of this uppoer 512 bytes of display memory. Two patterns of hardware cursor are supported.

Table 5-4. Cursor Display State

| Cursor Plane 0 | Cursor Plane 1 | Cursor Display State |

|----------------|----------------|----------------------|

| 0              | 0              | Cursor color 0       |

| 1              | 0              | Cursor color 1       |

| 0              | 1              | Transparent          |

| 1              | 1              | Invert video data    |

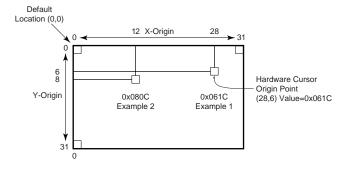

The cursor position is defined relative to the cursor offset from the top left of the display screen. Cursor position X is in pixels and is specified by register 22. Cursor position Y is in scan lines and is specified by register 24.

The cursor pattern data for cursor plane 0 and cursor plane 1 is loaded into display memory one cursor scan line at a time. For each cursor scan line, Cursor Plane 0 data (32 bits or 4 bytes) is loaded first, followed by the Cursor Plane 1 data (32 bits or 4 bytes). This loading sequence continues until all 32 scan lines have been loaded into display memory. The cursor pattern is mapped to the display memory using linear packed-pixel addressing.

LCD Controller NEC

# Address Decoding 6

### Table 6-1. Address Map

| Memory Type           | Starting Address | Ending Address |  |

|-----------------------|------------------|----------------|--|

| Display memory        | 0x0A000000       | 0x0A7FFFFF     |  |

| LCD control registers | 0x0A800000       | 0x0AFFFFF      |  |

| PC Card registers     | 0x15000000       | 0x15FFFFFF     |  |

Display memory is decoded by the LCD chip select signal. The  $V_R41xx$  CPU hardware decodes the fixed address for LCD display memory. Your system design may select a different address decoding scheme to drive the  $V_{RC}4171A$ 's \*LCDCS input signal on pin 82.

Access to the 16-bit LCD registers occrs when \*LCDCS = 0 and A23 = 1. If the  $V_R41xx$ 's \*LCDCS output signal is connected to the  $V_{RC}4171A$ 's \*LCDCS input signal, a 16-bit CPU-style memory access of 0xAA800000-0AA80005E will read or write the 16-bit LCD Controller registers. A CPU-style memory access of 0xAA000000-0xAA1FFFFF will read or write the external 2-MB LCD display memory/.

Table 6-2. Address Decoding

| Location                                   | Address                                                                                           | Comment                                                                |

|--------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Internal registers                         | Either 26 or 16 address bits,<br>depending on the IO_UADEC<br>setting in Configuration register I | A[25:16] set at 0100000000;<br>can't be changed                        |

| Two I/O windows (64K range)                | A[25:16]                                                                                          | Set at 0100000000; can't be changed (64K range)                        |

| Five memory windows (1 MB max. per window) | A[25:20], A[19:12}                                                                                | Programmable by software driver; used for address decoding (1 MB max.) |

# Registers 7

This section contains detailed information about the VRC4171A's registers.

Table 7-1. Top-Level Register Summary (16-Bit Accesses Only)

| Register Name                   | Address | Signal  | Description                             |

|---------------------------------|---------|---------|-----------------------------------------|

| Configuration register I        | 05FEh   |         |                                         |

| Configuration register II       | 05FCh   |         |                                         |

| Interrupt Status register       | 05FAh   |         |                                         |

| GPIO/*PCS Control/Data register | 05EEh   |         |                                         |

|                                 | 05ECh   | *PCS[0] | Upper addresses A[25:16] start register |

|                                 | 05EAh   | *PCS[0] | Lower addresses A[15:0] start register  |

|                                 | 05E8h   | *PCS[0] | Upper addresses A[25:16] stop register  |

|                                 | 05E6h   | *PCS[0] | Lower addresses A[15:0] stop register   |

|                                 | 05E4h   | *PCS[1] | Upper addresses A[25:16] start register |

|                                 | 05E2h   | *PCS[1] | Lower addresses A[15:0] start register  |

|                                 | 05DEh   | *PCS[1] | Upper addresses A[25:16] stop register  |

|                                 | 05DCh   | *PCS[1] | Lower addresses A[15:0] stop register   |

Two of the PC Card Controller registers are located in the I/O address space (Table 7-2). The remaining two PC Card Controller registers are accessed through the PC Card Controller Index registers (Table 7-3).

Table 7-2. 8-Bit PC Card Register I/O Address Space

| Register Name                     | Address |

|-----------------------------------|---------|

| PC Card Controller Index register | 03E0h   |

| PC Card Controller Data register  | 03E1h   |

Registers

Table 7-3. 8-Bit PC Card Controller Index Register

| Register Name                                            | Slot A | Slot B |

|----------------------------------------------------------|--------|--------|

| Identification and Revision register                     | 0000h  | 0040h  |

| Interface Status Register                                | 0001h  | 0041h  |

| Power and RESETDRV Control register                      | 0002h  | 0042h  |

| Interrupt and General Control register                   | 0003h  | 0043h  |

| Card Status Change register                              | 0004h  | 0044h  |

| Card Status Change Interrupt Configuration register      | 0005h  | 0045h  |

| Address Window Enable register                           | 0006h  | 0046h  |

| I/O Control register                                     | 0007h  | 0047h  |

| I/O Address 0 Start Low-Byte register                    | 0008h  | 0048h  |

| I/O Address 0 Start High-Byte register                   | 0009h  | 0049h  |

| I/O Address 0 Stop Low-Byte register                     | 000Ah  | 004Ah  |

| I/O Address 0 Stop High-Byte register                    | 000Bh  | 004Bh  |

| I/O Address 1 Start Low-Byte register                    | 000Ch  | 004Ch  |

| I/O Address 1 Start High-Byte register                   | 000Dh  | 004Dh  |

| I/O Address 1 Stop Low-Byte register                     | 000Eh  | 004Eh  |

| I/O Address 1 Stop High-Byte register                    | 000Fh  | 004Fh  |

| System Memory Address 0 Mapping Start Low-Byte register  | 0010h  | 0050h  |

| System Memory Address 0 Mapping Start-High Byte register | 0011h  | 0051h  |

| System Memory Address 0 Mapping Stop Low-Byte register   | 0012h  | 0052h  |

| System Memory Address 0 Mapping Stop High-Byte register  | 0013h  | 0053h  |

| Card Memory Offset Address 0 Low-Byte register           | 0014h  | 0054h  |

| Card Memory Offset Address 0 High-Byte register          | 0015h  | 0055h  |

| Card Detect and General Control register                 | 0016h  | 0056h  |

| System Memory Address 1 Mapping Start Low-Byte register  | 0018h  | 0058h  |

| System Memory Address 1 Mapping Start High-Byte register | 0019h  | 0059h  |

| System Memory Address 1 Mapping Stop Low-Byte register   | 001Ah  | 005Ah  |

| System Memory Address 1 Mapping Stop High-Byte register  | 001Bh  | 005Bh  |

| Card Memory Offset Address 1 Low-Byte register           | 001Ch  | 005Ch  |

| Card Memory Offset Address 1 High-Bbyte register         | 001Dh  | 005Dh  |

| Global Control register                                  | 001Eh  | 005Eh  |

| Card Voltage Sense register                              | 001Fh  | 005Fh  |

| System Memory Address 2 Mapping Start Low-Byte register  | 0020h  | 0060h  |

| System Memory Address 2 Mapping Start High-Byte register | 0021h  | 0061h  |

| System Memory Address 2 Mapping Stop Low-Byte register   | 0022h  | 0062h  |

| System Memory Address 2 Mapping Stop High-Byte register  | 0023h  | 0063h  |

| Card Memory Offset Address 2 Low-Byte register           | 0024h  | 0064h  |

| Card Memory Offset Address 2 High-Byte register          | 0025h  | 0065h  |

| System Memory Address 3 Mapping Start Low-Byte register  | 0028h  | 0068h  |

| System Memory Address 3 Mapping Start High-Byte register | 0029h  | 0069h  |

| System Memory Address 3 Mapping Stop Low-Byte register   | 002Ah  | 006Ah  |

| System Memory Address 3 Mapping Stop High-Byte register  | 002Bh  | 006Bh  |

Table 7-3. 8-Bit PC Card Controller Index Register (continued)

| Register Name                                            | Slot A | Slot B |

|----------------------------------------------------------|--------|--------|

| Card Memory Offset Address 3 Low-Byte register           | 002Ch  | 006Ch  |

| Card Memory Offset Address 3 High-Byte register          | 002Dh  | 006Dh  |

| Card Voltage Select register                             | 002Fh  | 006Fh  |

| System Memory Address 4 Mapping Start Low-Byte register  | 0030h  | 0070h  |

| System Memory Address 4 Mapping Start High-Byte register | 0031h  | 0071h  |

| System Memory Address 4 Mapping Stop Low-Byte register   | 0032h  | 0072h  |

| System Memory Address 4 Mapping Stop High-Byte register  | 0033h  | 0073h  |

| Card Memory Offset Address 4 Low-Byte register           | 0034h  | 0074h  |

| Card Memory Offset Address 4 High-Byte register          | 0035h  | 0075h  |

To access a register, write the index value listed in Table 7-3 for slot A or slot B into the PC Card Controller Index register at address 03E0h with an 8-bit access only. Read or write the 8-bit PC Controller Data register at byte address 03E1h with an 8-bit access only.

Table 7-4. 16-Bit LCD Register Summary

| Register Name                                  | Address |

|------------------------------------------------|---------|

| Panel Select register                          | 0000h   |

| LCD Panel Control register                     | 0002h   |

| Power Mode Control register                    | 0004h   |

| MCLK Enable register                           | 0006h   |

| VCLK Enable register                           | 0008h   |

| Video FIFO / Memory Interface Control register | 000Ah   |

| Pixel Adjustment / Vertical Half register      | 000Ch   |

| Reserved                                       | 000Eh   |

| Horizontal Display Control register            | 0010h   |

| Horizontal Retrace Control register            | 0012h   |

| Vertical Display End Control register          | 0014h   |

| Vertical Display Control register              | 0016h   |

| Vertical Retrace Start Control register        | 0018h   |

| Vertical Retrace End Control register          | 001Ah   |

| Starting Address register                      | 001Ch   |

| Offset register                                | 001Eh   |

| Hardware Cursor Control register               | 0020h   |

| Hardware Cursor X Position register            | 0022h   |

| Hardware Cursor Y Position register            | 0024h   |

| Hardware Cursor Color 0A register              | 0026h   |

| Hardware Cursor Color 0B register              | 0028h   |

| Hardware Cursor Color 1A register              | 002Ah   |

| Hardware Cursor Color 1B register              | 002Ch   |

| Hardware Cursor Origin register                | 002Eh   |

| Reserved                                       | 0030h   |

| Reserved                                       | 0032h   |

Registers

Table 7-4. 16-Bit LCD Register Summary (continued)

| Register Name                   | Address |

|---------------------------------|---------|

| Reserved                        | 0034h   |

| Reserved                        | 0036h   |

| Reserved                        | 0038h   |

| Reserved                        | 003Ah   |

| Reserved                        | 003Ch   |

| Reserved                        | 003Eh   |

| RAM Write Address register      | 0040h   |

| RAM Write Port 0 register       | 0042h   |

| RAM Write Port 1 register       | 0044h   |

| RAM Read Address register       | 0046h   |

| RAM Read Port 0 register        | 0048h   |

| RAM Read Port 1 register        | 004Ah   |

| Reserved                        | 004Ch   |

| Reserved                        | 004Eh   |

| Scratch Pad Register 0 register | 0050h   |

| Scratch Pad Register 1 register | 0052h   |

| Reserved                        | 0054h   |

| Reserved                        | 0056h   |

| Reserved                        | 0058h   |

| Reserved                        | 005Ah   |

| Reserved                        | 005Ch   |

| Reserved                        | 005Eh   |

Note:

The registers' reset status is 0 unless specified differently. Reserved and unused bits internal to a register are left undefined. They might be left floating and not driven to a default level high or low. Do not depend on these bits returning to a repeatable value. It is advisable to mask these bits to zero with software when performing a calculation using the contents of a register containing reserved and unused bits.

### **Top-Level Registers**

Top-level registers [05xxh] are accessed through 16-bit operations; *byte access is not supported*. All reserved bits are set to zero upon hardware reset and should always be written to zero to ensure proper device operation.

### Configuration Register I

| Name             | Configuration Register I |

|------------------|--------------------------|

| Туре             | Read/Write               |

| Register Address | 05FEh                    |

### Bits

| D15-D14       | D13   | D12     | D11       | D10      | D9       | D8-D6          | D5-D3         | D2-D0    |

|---------------|-------|---------|-----------|----------|----------|----------------|---------------|----------|

| MFP_CONF[1:0] | EN_OR | EN_VCLK | EN_BUSCLK | Reserved | IO_UADEC | VMCLK_DIV{2:0} | VCLK_DIV[2:0] | Reserved |

Table 7-5. Configuration Register 1

| Bit(s)  | Name          | Description                                                                                                                                                                                                                                                                                 |  |  |

|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D15-D14 | MFP_CONF[1:0] | Configure multifunction pin functions                                                                                                                                                                                                                                                       |  |  |

|         |               | Default = 0 for all bits                                                                                                                                                                                                                                                                    |  |  |

|         |               | 11 = A: PC Card / B: Miniature Card (flash/ROM only)                                                                                                                                                                                                                                        |  |  |

|         |               | 10 = A: PC Card / B: CompactFlash                                                                                                                                                                                                                                                           |  |  |

|         |               | 01 = A: PC Card / B: PC Card                                                                                                                                                                                                                                                                |  |  |

|         |               | 00 = A: PC Card / B: none                                                                                                                                                                                                                                                                   |  |  |

| D13     | EN_OR         | Default = 0                                                                                                                                                                                                                                                                                 |  |  |

|         |               | 1 = Enable external OR gate for PC Card slots                                                                                                                                                                                                                                               |  |  |

|         |               | See Table 2-6 for dual-slot options.                                                                                                                                                                                                                                                        |  |  |

| D12     | EN_VCLK       | Default = 1                                                                                                                                                                                                                                                                                 |  |  |

|         |               | 1 = Enable internal VMCLK and VCLK display clocks                                                                                                                                                                                                                                           |  |  |

| D11     | EN_BUSCLK     | Default = 0                                                                                                                                                                                                                                                                                 |  |  |

|         |               | 1 = Enable internal BUSCLK                                                                                                                                                                                                                                                                  |  |  |

| D10     | Reserved      | Default = 0                                                                                                                                                                                                                                                                                 |  |  |

| D9      | IO_UADEC      | Default = 0                                                                                                                                                                                                                                                                                 |  |  |

|         |               | I/O upper address decode                                                                                                                                                                                                                                                                    |  |  |

|         |               | 0 = I/O address decode does not include upper bits A[25:16]                                                                                                                                                                                                                                 |  |  |

|         |               | 1 = I/O address decode includes all upper bits A[25:16], where A[25:24] is set to "01" and A[23:16] to "00h"                                                                                                                                                                                |  |  |

|         |               | This option only affects the top-level registers and PC Card controller index and data registers. Upper addresses A[25:16] for the PC Card I/O windows are always set at "0100000000." Upper addresses A[25:16] for memory windows are always written by software to the PC Card registers. |  |  |

Registers

Table 7-5. Configuration Register 1 (continued)

| D8-D6 | VMCLK_DIV[2:0] | Default = 0 for all bits                    |

|-------|----------------|---------------------------------------------|

|       |                | Divider from master clock to generate VMCLK |

|       |                | 111 = master clock divide by 8              |

|       |                | 110 = master clock divide by 7              |

|       |                | 101 = master clock divide by 6              |

|       |                | 100 = master clock divide by 5              |

|       |                | 011 = master clock divide by 4              |