### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### RENESAS

**User's Manual**

# Phase-out/Discontinued

### V821<sup>™</sup>

32-/16-Bit Microprocessor

Hardware

$\mu$ **PD70741**

Document No. U10077EJ5V0UM00 (5th edition) Date Published February 1999 J CP(K)

© NEC Corporation 1995 Printed in Japan

[MEMO]

### SUMMARY OF CONTENTS

| CHAPTER 1  | OVERVIEW                                       | 23  |

|------------|------------------------------------------------|-----|

| CHAPTER 2  | PIN FUNCTIONS                                  | 31  |

| CHAPTER 3  | CPU FUNCTIONS                                  | 45  |

| CHAPTER 4  | INTERRUPT/EXCEPTION HANDLING FUNCTIONS         | 55  |

| CHAPTER 5  | BUS CONTROL FUNCTION                           | 75  |

| CHAPTER 6  | WAIT CONTROL FUNCITONS                         | 109 |

| CHAPTER 7  | MEMORY ACCESS CONTROL FUNCTIONS                | 119 |

| CHAPTER 8  | DMA FUNCTIONS (DMA CONTROLLER)                 | 139 |

| CHAPTER 9  | SERIAL INTERFACE FUNCTION                      | 155 |

| CHAPTER 10 | TIMER/COUNTER FUNCTIONS (REAL-TIME PULSE UNIT) | 183 |

| CHAPTER 11 | WATCHDOG TIMER FUNCTIONS                       | 213 |

| CHAPTER 12 | PORT FUNCTIONS                                 | 217 |

| CHAPTER 13 | CLOCK GENERATION FUNCTIONS                     | 221 |

| CHAPTER 14 | STANDBY FUNCTIONS                              | 225 |

| CHAPTER 15 | RESET FUNCTIONS                                | 237 |

| APPENDIX A | REGISTER INDEX                                 | 243 |

| APPENDIX B | GENERAL INDEX                                  | 247 |

### NOTES FOR CMOS DEVICES -

### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

V821 Family and V810 Family are trademarks of NEC Corporation.

UNIX is a registered trademark licensed by X/Open Company Limited in the US and other countries. Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

### **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### NEC Electronics (UK) Ltd.

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

### NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

### NEC Electronics (France) S.A.

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### NEC Electronics (France) S.A.

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### NEC Electronics (Germany) GmbH Scandinavia Office

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 65-253-8311 Fax: 65-250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

J98. 11

### **Major Changes**

| Page   | Description                                                                    |

|--------|--------------------------------------------------------------------------------|

| P. 24  | The μPD70741GC-25-7EA has been deleted from Section 1.2.                       |

| P. 25  | The μPD70741GC-25-7EA has been deleted from Section 1.3.                       |

| P. 27  | Section 1.4.1 has been modified.                                               |

| P. 123 | The description has been added to Section 7.1.5.                               |

| P. 151 | Figure 8-9 has been modified.                                                  |

| P. 221 | The clock generation function block diagram in Section 13.2 has been modified. |

| P. 223 | The description has been added to Section 13.3.2 (2).                          |

| P. 231 | The description has been added to Section 14.5.1.                              |

The mark  $\star$  shows major revised points.

[MEMO]

### PREFACE

| Intended readers      | : This manual is aimed at those users who wish to become familiar with the functions of the V821 ( $\mu$ PD70741), and those involved in designing systems based on the V821.                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose               | : The purpose of this manual is to assist users in understanding the hardware functions of the V821, as listed in "Configuration" below.                                                                                                                                                                                                                                                                                                                                                                                  |

| Configuration         | : The V821 User's Manual is provided as two volumes, Hardware (this manual)<br>and Architecture (V810 Family <sup>TM</sup> User's Manual, Architecture).                                                                                                                                                                                                                                                                                                                                                                  |

|                       | <ul> <li>Pin functions</li> <li>CPU functions</li> <li>Interrupt functions</li> <li>Bus control functions</li> <li>Built-in peripheral functions</li> <li>Reset functions</li> </ul> |

| How to use this manua | <ol> <li>Readers are assumed to be familiar with electronics, logic circuits, and micro-<br/>computers.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | For an explanation of the CPU functions -> Read <b>Chapter 3</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | <ul> <li>For an explanation of the instructions</li> <li>-&gt; Refer to the V810 Family User's Manual, Architecture (the companion volume to this manual).</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

|                       | To gain an overall understanding of the functions of the V821<br>-> Read this manual in its entirety.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       | To know the electrical characteristics<br>-> Refer to the <b>V821 Data Sheet</b> provided separately.                                                                                                                                                                                                                                                                                                                                                                                                                     |

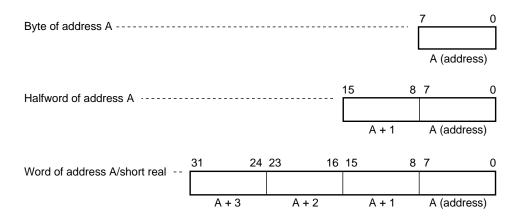

|                       | In this manual, 2-byte data is referred to as halfword data, while 4-byte data is referred to as word data.                                                                                                                                                                                                                                                                                                                                                                                                               |

| Legend | : Significance of data represent | ation : Left high, right low                                                                       |

|--------|----------------------------------|----------------------------------------------------------------------------------------------------|

|        | Representation of active low     | : xxx [bar above a pin or signal name)                                                             |

|        | Memory map address               | : Top upper, bottom lower                                                                          |

|        | Note                             | : Explanation of Note marked in text                                                               |

|        | Caution                          | : Note to which particular attention must be afforded                                              |

|        | Remark                           | : Supplementary explanation of text                                                                |

|        | Representation of numbers        | : xxxx or xxxxB for a binary number<br>xxxx for a decimal number<br>xxxxH for a hexadecimal number |

|        | Prefixes indicating powers of t  | two (address space, memory capacity):                                                              |

|        | K (kilo)                         | : 2 <sup>10</sup> = 1,024                                                                          |

|        | M (mega)                         | $2^{20} = 1,024^2$                                                                                 |

|        | G (giga)                         | $2^{30} = 1,024^3$                                                                                 |

|        |                                  |                                                                                                    |

**Related document** : Some related documents may be preliminary editions; Note, however, that whether a related document is preliminary is not indicated in this manual.

### ○ Documents related to devices

| Document name                           | Document number |

|-----------------------------------------|-----------------|

| V821 User's Manual, Hardware            | This manual     |

| V810 Family User's Manual, Architecture | U10082E         |

| μPD70741 Data Sheet                     | U11678E         |

### • Documents related to development tools (user's manual)

| Docur                | Document number                          |         |

|----------------------|------------------------------------------|---------|

| CA732 (C compiler)   | Operation (UNIX <sup>TM</sup> -based)    | U11013E |

|                      | Operation (Windows <sup>TM</sup> -based) | U11068E |

|                      | Assembly language                        | U11016E |

|                      | С                                        | U11010E |

|                      | Project manager                          | U11991E |

| RX732 (Real-time OS) | Basic                                    | U10346E |

|                      | Technical                                | U10490E |

|                      | Nucleus installation                     | U10347E |

### CONTENTS

| CHAPTER 1 | OVERVIEW |                                                   |    |

|-----------|----------|---------------------------------------------------|----|

|           | 1.1      | FEATURES                                          | 23 |

|           | 1.2      | ORDERING INFORMATION                              | 24 |

|           | 1.3      | PIN CONFIGURATION (TOP VIEW)                      | 25 |

|           | 1.4      | FUNCTIONAL BLOCK CONFIGURATION                    | 27 |

|           |          | 1.4.1 Internal Block Diagram                      | 27 |

|           |          | 1.4.2 Internal Units                              | 28 |

| CHAPTER 2 | PIN      | UNCTIONS                                          | 31 |

|           | 2.1      | PIN FUNCTIONS                                     | 31 |

|           |          | 2.1.1 Port Pins                                   | 31 |

|           |          | 2.1.2 Non-Port Pins                               | 32 |

|           | 2.2      | PIN STATES                                        | 34 |

|           | 2.3      | PIN FUNCTIONS                                     | 35 |

|           |          | 2.3.1 Address Bus                                 | 35 |

|           |          | 2.3.2 Data Bus                                    | 35 |

|           |          | 2.3.3 Bus Control Signals                         | 35 |

|           |          | 2.3.4 System Control Signals                      | 37 |

|           |          | 2.3.5 Interrupt Control Signals                   | 38 |

|           |          | 2.3.6 DRAM Control Signals                        | 38 |

|           |          | 2.3.7 DMA Control Signals                         | 39 |

|           |          | 2.3.8 Real-Time Pulse Control Signals             | 40 |

|           |          | 2.3.9 Serial Control Signals                      | 40 |

|           |          | 2.3.10 Watchdog Timer Control Signal              | 41 |

|           |          | 2.3.11 Port Control Signal                        | 41 |

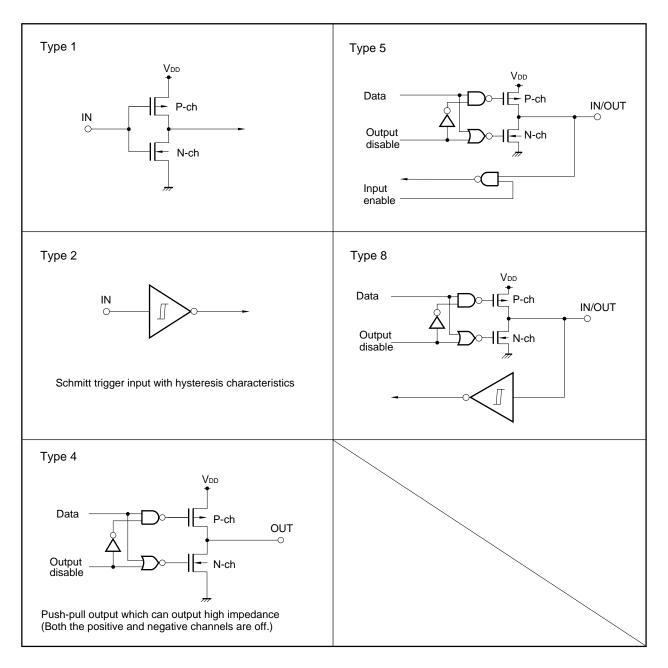

|           | 2.4      | PIN I/O CIRCUITS AND PROCESSING OF UNUSED PINS    | 42 |

|           | 2.5      | PIN I/O CIRCUITS                                  | 43 |

| CHAPTER 3 | CPU      | FUNCTIONS                                         | 45 |

|           | 3.1      | FEATURES                                          | 45 |

|           | 3.2      | ADDRESS SPACE                                     | 45 |

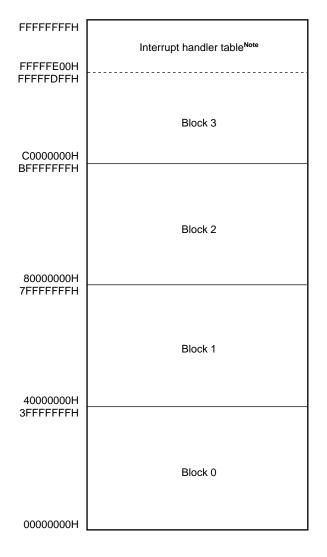

|           |          | 3.2.1 Memory Map                                  | 46 |

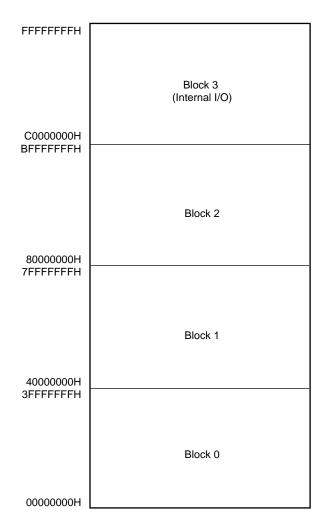

|           |          | 3.2.2 I/O Map                                     | 47 |

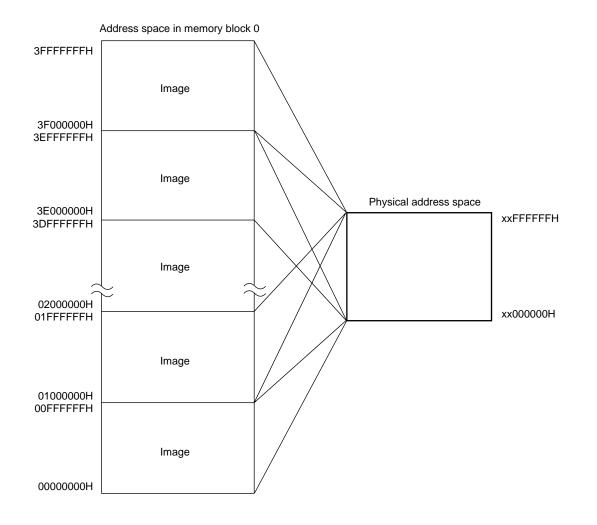

|           |          | 3.2.3 Images                                      | 47 |

|           |          | 3.2.4 Differences between the Memory and I/O Maps | 48 |

|           | 3.3      | CPU REGISTER SET                                  | 49 |

|           |          | 3.3.1 Program Register Set                        | 50 |

|           |      | 3.3.2 System Register Set                                         | 51 |  |  |

|-----------|------|-------------------------------------------------------------------|----|--|--|

|           | 3.4  | BUILT-IN PERIPHERAL I/O REGISTERS                                 | 52 |  |  |

| CHAPTER 4 | INTE | ERRUPT/EXCEPTION HANDLING FUNCTIONS                               | 55 |  |  |

|           | 4.1  | FEATURES                                                          | 55 |  |  |

|           | 4.2  | NONMASKABLE INTERRUPTS                                            | 58 |  |  |

|           |      | 4.2.1 Operation                                                   | 58 |  |  |

|           | 4.3  | MASKABLE INTERRUPTS                                               | 60 |  |  |

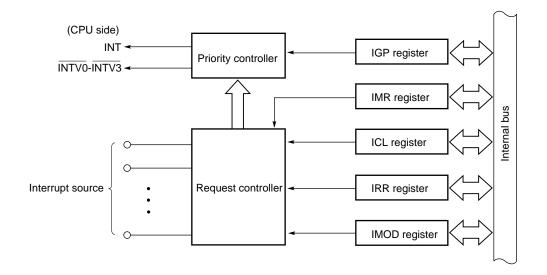

|           |      | 4.3.1 Block Diagram                                               | 60 |  |  |

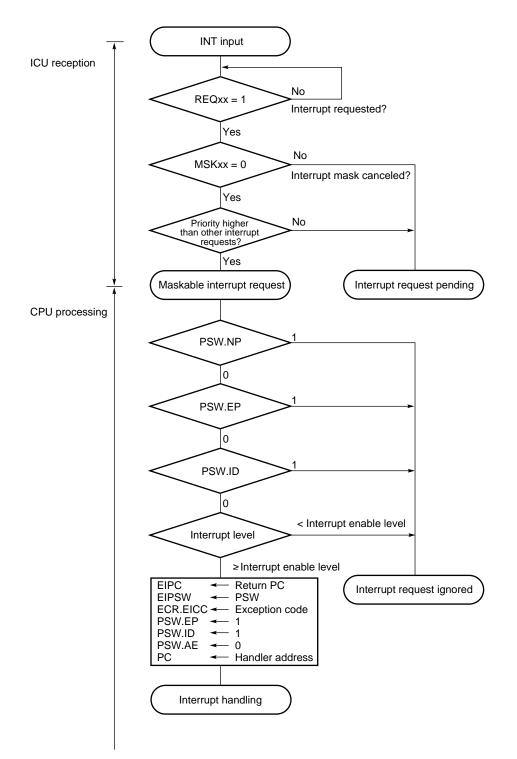

|           |      | 4.3.2 Operation                                                   | 61 |  |  |

|           |      | 4.3.3 Maskable Interrupt Priority                                 | 63 |  |  |

|           | 4.4  | CONTROL REGISTERS                                                 | 64 |  |  |

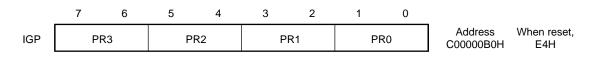

|           |      | 4.4.1 Interrupt Group Priority Register (IGP)                     | 64 |  |  |

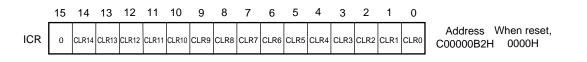

|           |      | 4.4.2 Interrupt Clear Register (ICR)                              | 66 |  |  |

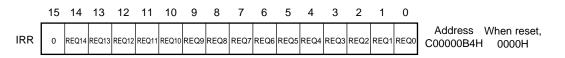

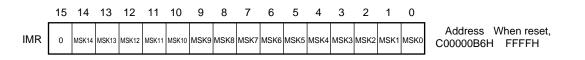

|           |      | 4.4.3 Interrupt Request Register (IRR)                            | 66 |  |  |

|           |      | 4.4.4 Interrupt Request Mask Register (IMR)                       | 67 |  |  |

|           |      | 4.4.5 ICU Mode Register (IMOD)                                    | 68 |  |  |

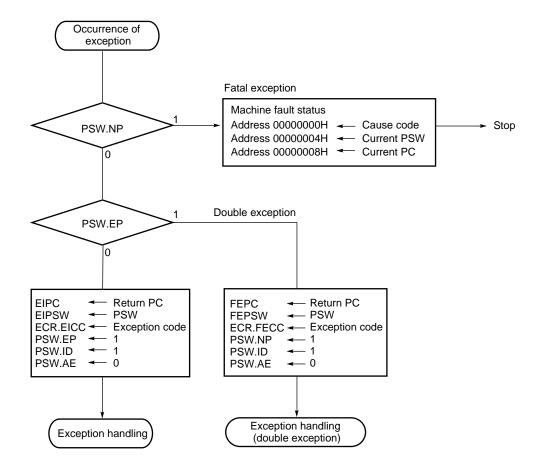

|           | 4.5  | EXCEPTION HANDLING (SOFTWARE EXCEPTION AND EXCEPTION              |    |  |  |

|           |      | TRAP)                                                             | 69 |  |  |

|           |      | 4.5.1 Operation                                                   | 70 |  |  |

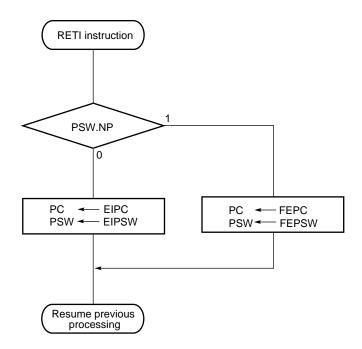

|           |      | 4.5.2 Return from an Exception or Interrupt                       | 72 |  |  |

|           | 4.6  | PRIORITY CONTROL                                                  | 73 |  |  |

|           |      | 4.6.1 Priorities of Interrupts and Exceptions                     | 73 |  |  |

|           |      | 4.6.2 Priorities of Floating-Point Exceptions                     | 74 |  |  |

| CHAPTER 5 | BUS  | CONTROL FUNCTION                                                  | 75 |  |  |

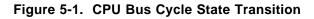

|           | 5.1  | CPU BUS STATES                                                    | 75 |  |  |

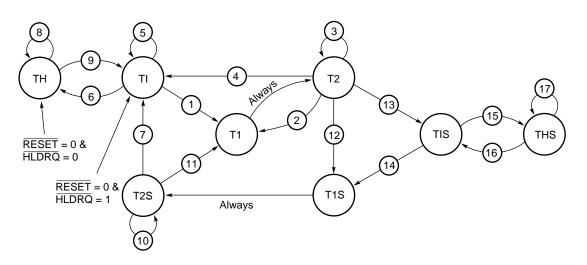

|           | 5.2  | DMAC BUS STATE                                                    | 77 |  |  |

|           | 5.3  | BUS PRIORITY                                                      | 80 |  |  |

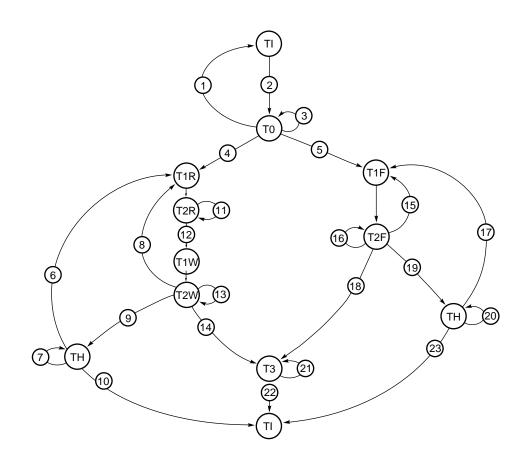

|           | 5.4  | DATA FLOW WHEN USING AN ADDITIONAL BUS CYCLE                      |    |  |  |

|           | 5.5  | RELATIONSHIP BETWEEN EXTERNAL ACCESSES AND THE DATA BUS           | 82 |  |  |

|           |      | 5.5.1 Relationship between External Access and Byte Enable Signal | 82 |  |  |

|           |      | 5.5.2 Operand Read                                                | 83 |  |  |

|           |      | 5.5.3 Operand Write                                               | 84 |  |  |

|           |      | 5.5.4 Notes on Bit Strings                                        | 85 |  |  |

|           | 5.6  | EXTERNAL I/O ACCESS                                               | 86 |  |  |

|           |      | 5.6.1 External I/O Read Cycle                                     | 86 |  |  |

|           |      | 5.6.2 External I/O Write Cycle                                    | 87 |  |  |

|           | 5.7  | INTERNAL I/O ACCESS                                               | 88 |  |  |

|           |      | 5.7.1 Internal I/O Read Cycle                                     | 88 |  |  |

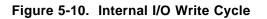

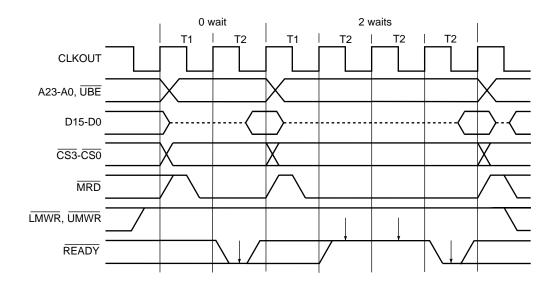

|           |                   | 5.7.2                                    | Internal I/O Write Cycle                                                                                 | 89                                            |

|-----------|-------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|           | 5.8               | SRAM                                     | (ROM) ACCESS                                                                                             | 90                                            |

|           |                   | 5.8.1                                    | SRAM (ROM) Read Cycle                                                                                    | 90                                            |

|           |                   | 5.8.2                                    | SRAM Write Cycle                                                                                         | 91                                            |

|           | 5.9               | PAGE-                                    | ROM ACCESS                                                                                               | 92                                            |

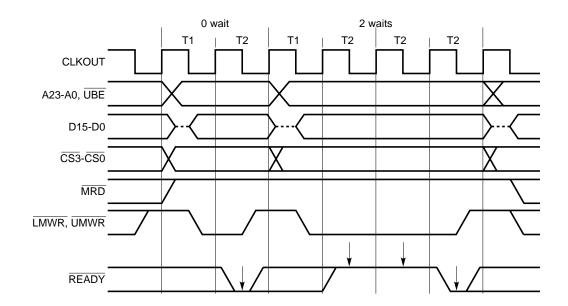

|           |                   | 5.9.1                                    | Page-ROM Read Cycle                                                                                      | 92                                            |

|           | 5.10              | DRAM                                     | ACCESS                                                                                                   | 93                                            |

|           |                   | 5.10.1                                   | DRAM Read Cycle                                                                                          | 93                                            |

|           |                   | 5.10.2                                   | DRAM Write Cycle                                                                                         | 95                                            |

|           |                   | 5.10.3                                   | CBR Refresh Cycle                                                                                        | 98                                            |

|           |                   | 5.10.4                                   | Self-Refresh Cycle                                                                                       | 99                                            |

|           |                   | 5.10.5                                   | Bus Cycle during Fly-by Transfer                                                                         | 100                                           |

|           | 5.11              | EXCEF                                    | PTION HANDLING CYCLES                                                                                    | 104                                           |

|           |                   | 5.11.1                                   | Machine Fault Cycle                                                                                      | 104                                           |

|           |                   | 5.11.2                                   | Halt Acknowledge Cycle                                                                                   | 105                                           |

|           | 5.12              | CONTR                                    | ROL SIGNAL TIMING                                                                                        | 106                                           |

|           |                   | 5.12.1                                   | Bus Hold                                                                                                 | 106                                           |

|           |                   | 5.12.2                                   | Bus Lock                                                                                                 | 108                                           |

| CHAPTER 6 | WAI               |                                          | ROL FUNCTIONS                                                                                            | 109                                           |

|           | 6.1               | FEATU                                    | IRES                                                                                                     | 109                                           |

|           | 6.2               | ADDRE                                    | ESS SPACES AND BLOCKS                                                                                    | 109                                           |

|           | 6.3               | CHIP S                                   | SELECT CREATION AND BUS CYCLE SELECTION FUNCTIONS                                                        | 110                                           |

|           | 6.4               | PROG                                     | RAMMABLE WAIT FUNCTION                                                                                   | 110                                           |

|           |                   | 6.4.1                                    | Wait Control Using the READY Pin                                                                         | 110                                           |

|           |                   | 6.4.2                                    | Wait Control during DMA Transfer                                                                         | 111                                           |

|           |                   | 6.4.3                                    | Bus Cycles during Which the Wait Function Is Effective                                                   | 111                                           |

|           | 6.5               | CONT                                     | ROL REGISTERS                                                                                            | 114                                           |

|           |                   | 6.5.1                                    | Bus Cycle Type Control Register (BCTC)                                                                   | 114                                           |

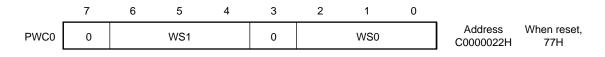

|           |                   | 6.5.2                                    | Programmable Wait Control Register 0 (PWC0)                                                              | 115                                           |

|           |                   |                                          |                                                                                                          |                                               |

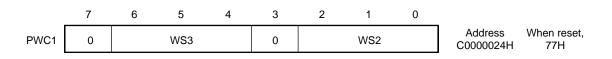

|           |                   | 6.5.3                                    | Programmable Wait Control Register 1 (PWC1)                                                              | 116                                           |

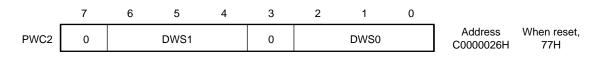

|           |                   | 6.5.3<br>6.5.4                           | Programmable Wait Control Register 1 (PWC1)<br>Programmable Wait Control Register 2 (PWC2)               |                                               |

| CHAPTER 7 | MEM               | 6.5.4                                    |                                                                                                          | 117                                           |

| CHAPTER 7 | <b>MEM</b><br>7.1 | 6.5.4<br>ORY A                           | Programmable Wait Control Register 2 (PWC2)                                                              | 117<br><b>119</b>                             |

| CHAPTER 7 |                   | 6.5.4<br>ORY A                           | Programmable Wait Control Register 2 (PWC2)                                                              | 117<br><b>119</b><br>119                      |

| CHAPTER 7 |                   | 6.5.4<br><b>ORY A</b><br>DRAM            | Programmable Wait Control Register 2 (PWC2)                                                              | 117<br><b>119</b><br>119<br>119               |

| CHAPTER 7 |                   | 6.5.4<br><b>ORY A</b><br>DRAM<br>7.1.1   | Programmable Wait Control Register 2 (PWC2)<br>CCESS CONTROL FUNCTIONS<br>CONTROLLER (DRAMC)<br>Features | 117<br><b>119</b><br>119<br>119<br>119        |

| CHAPTER 7 |                   | 6.5.4<br>ORY A<br>DRAM<br>7.1.1<br>7.1.2 | Programmable Wait Control Register 2 (PWC2)                                                              | 117<br><b>119</b><br>119<br>119<br>119<br>121 |

|           |      | 7.1.6   | Wait Control for DRAM Cycle                               | 127 |

|-----------|------|---------|-----------------------------------------------------------|-----|

|           |      | 7.1.7   | Refresh Function                                          | 129 |

|           |      | 7.1.8   | Self-Refresh Function                                     | 132 |

|           | 7.2  | ROM C   | CONTROLLER (ROMC)                                         | 134 |

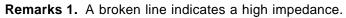

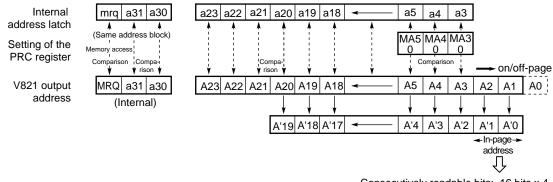

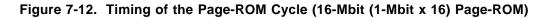

|           |      | 7.2.1   | on-page/off-page Decision                                 | 134 |

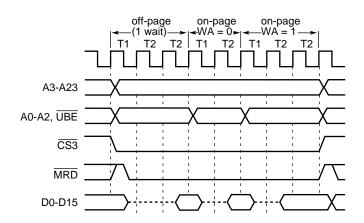

|           |      | 7.2.2   | Page-ROM Access                                           | 135 |

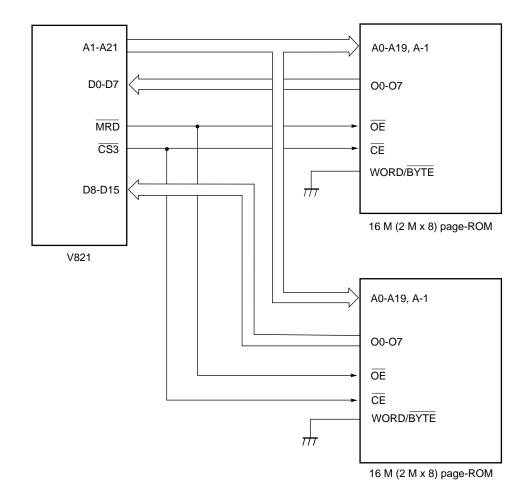

|           |      | 7.2.3   | Page-ROM Configuration Register (PRC)                     | 137 |

| CHAPTER 8 | DMA  | FUNCT   | TIONS (DMA CONTROLLER)                                    | 139 |

|           | 8.1  | FEATU   | IRES                                                      | 139 |

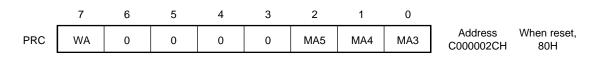

|           | 8.2  | CONFI   | GURATION                                                  | 140 |

|           | 8.3  | DMA C   | ONTROL REGISTERS                                          | 140 |

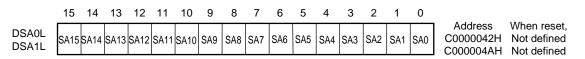

|           |      | 8.3.1   | DMA Source Address Registers 0 and 1 (DSA0 and DSA1)      | 140 |

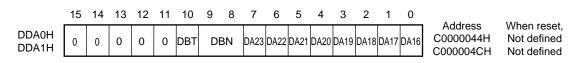

|           |      | 8.3.2   | DMA Destination Address Registers 0 and 1 (DDA0 and DDA1) | 141 |

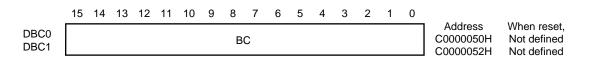

|           |      | 8.3.3   | DMA Byte Count Registers 0 and 1 (DBC0 and DBC1)          | 143 |

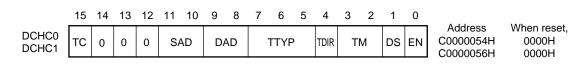

|           |      | 8.3.4   | DMA Channel Control Registers 0 and 1 (DCHC0 and DCHC1)   | 144 |

|           | 8.4  | TRANS   | SFER MODES                                                | 146 |

|           |      | 8.4.1   | Single Transfer Mode                                      | 146 |

|           |      | 8.4.2   | Single-Step Transfer Mode                                 | 146 |

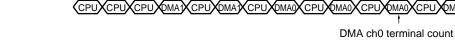

|           |      | 8.4.3   | Block Transfer Mode                                       | 147 |

|           | 8.5  | DMA T   | RANSFER TYPES AND TRANSFER OBJECTS                        | 148 |

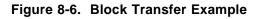

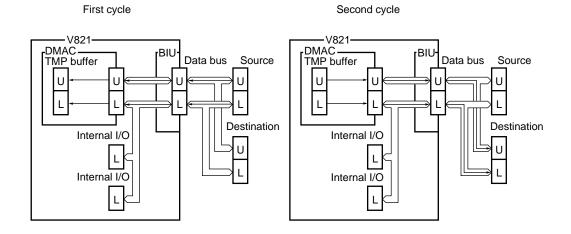

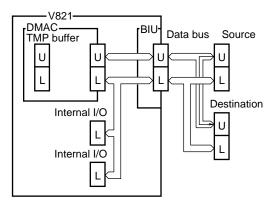

|           |      | 8.5.1   | Two-Cycle Transfer                                        | 148 |

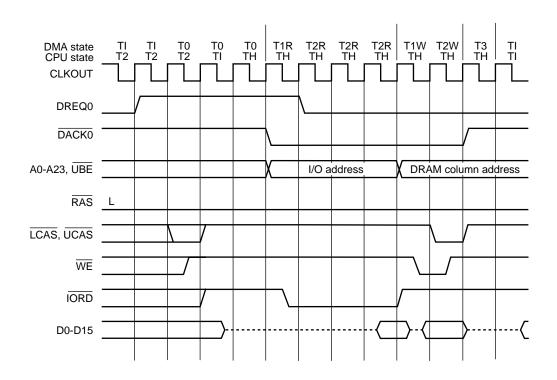

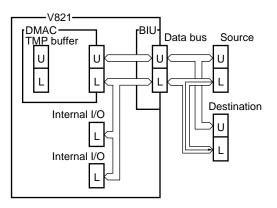

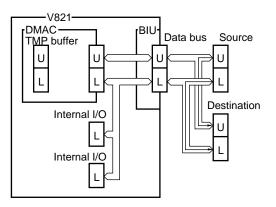

|           |      | 8.5.2   | Fly-by Transfer                                           | 149 |

|           |      | 8.5.3   | Transfer Objects                                          | 149 |

|           | 8.6  | DMA C   | HANNEL PRIORITIES                                         | 150 |

|           | 8.7  | DMA T   | RANSFER REQUESTS                                          | 150 |

|           | 8.8  | DMA T   | RANSFER END INTERRUPTS                                    | 150 |

|           | 8.9  | DMA T   | RANSFER END OUTPUT                                        | 151 |

|           | 8.10 | FORCI   | BLE INTERRUPTION                                          | 152 |

|           | 8.11 | DATA    | FLOW DURING DMA TRANSFER                                  | 152 |

| CHAPTER 9 | SER  | IAL INT | ERFACE FUNCTION                                           | 155 |

|           | 9.1  | FEATU   | IRES                                                      | 155 |

|           | 9.2  | ASYNC   | CHRONOUS SERIAL INTERFACE (UART)                          | 155 |

|           |      | 9.2.1   | Features                                                  | 155 |

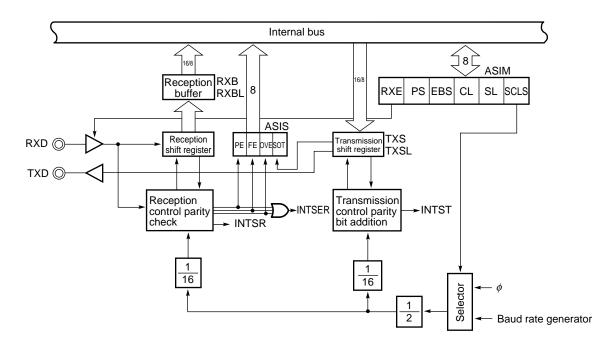

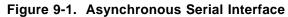

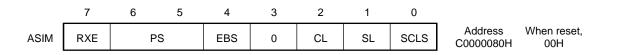

|           |      | 9.2.2   | Configuration                                             | 156 |

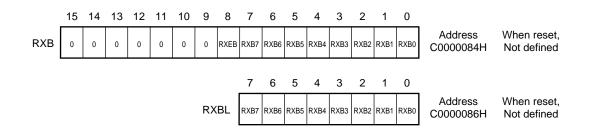

|           |      | 9.2.3   | UART Control Registers                                    | 158 |

|           |      | 9.2.4   | Interrupt Requests                                        | 164 |

|           |      | 9.2.5   | Operation                                                 | 165 |

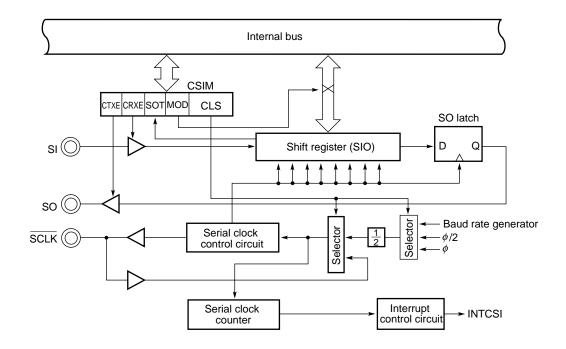

|           | 9.3  | SYNCH   | HRONOUS SERIAL INTERFACE (CSI)                            | 169 |

|            |      | 9.3.1 Features                                                 | 169 |

|------------|------|----------------------------------------------------------------|-----|

|            |      | 9.3.2 Configuration                                            | 170 |

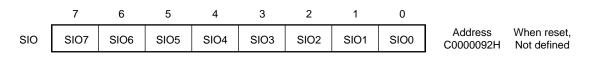

|            |      | 9.3.3 CSI Control Registers                                    | 171 |

|            |      | 9.3.4 Basic Operation                                          | 172 |

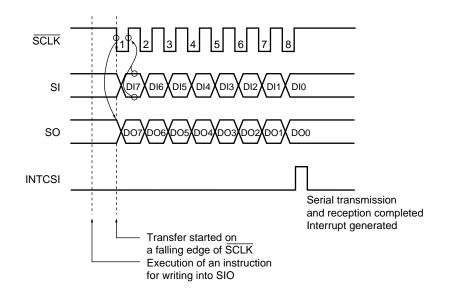

|            |      | 9.3.5 Transmission in Three-Wire Serial I/O Mode               | 174 |

|            |      | 9.3.6 Reception in Three-Wire Serial I/O Mode                  | 175 |

|            |      | 9.3.7 Transmission and Reception in Three-Wire Serial I/O Mode | 176 |

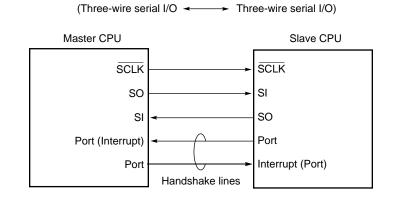

|            |      | 9.3.8 Example System Configuration                             | 177 |

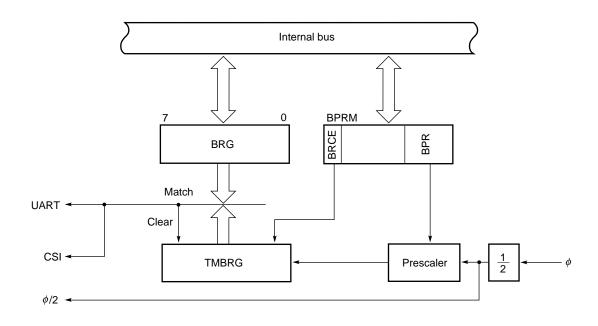

|            | 9.4  | BAUD RATE GENERATOR (BRG)                                      | 178 |

|            |      | 9.4.1 Configuration and Function                               | 178 |

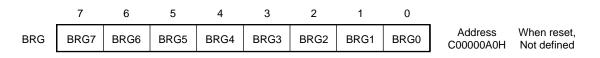

|            |      | 9.4.2 Baud Rate Generator Register (BRG)                       | 181 |

|            |      | 9.4.3 Baud Rate Generator Prescaler Mode Register (BPRM)       | 181 |

| CHAPTER 10 | ТІМЕ | ER/COUNTER FUNCTIONS (REAL-TIME PULSE UNIT)                    | 183 |

|            | 10.1 | FEATURES                                                       | 183 |

|            | 10.2 | BASIC CONFIGURATION                                            | 184 |

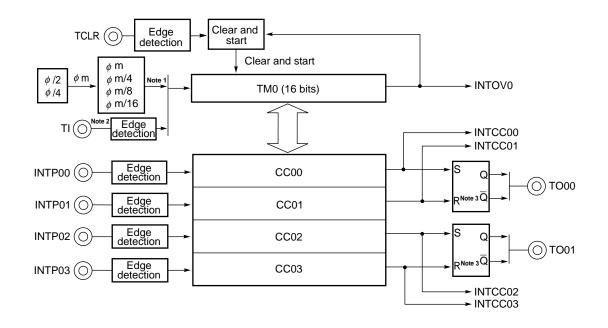

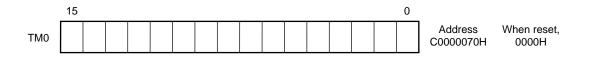

|            |      | 10.2.1 Timer 0                                                 | 186 |

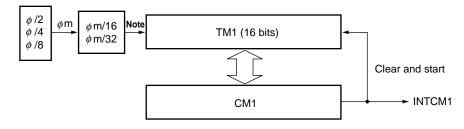

|            |      | 10.2.2 Timer 1                                                 | 188 |

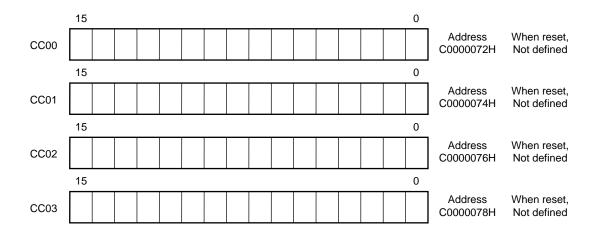

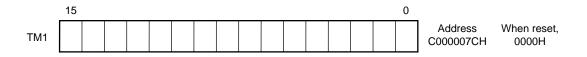

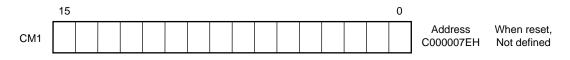

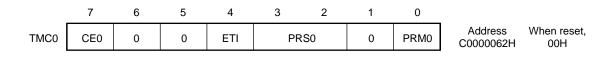

|            | 10.3 | CONTROL REGISTERS                                              | 189 |

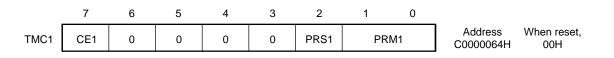

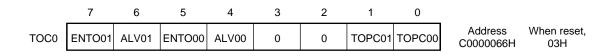

|            | 10.4 | OPERATION OF TIMER 0                                           | 195 |

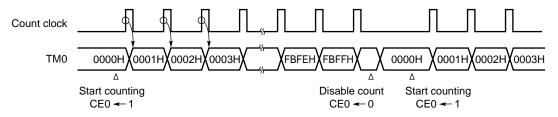

|            |      | 10.4.1 Counting                                                | 195 |

|            |      | 10.4.2 Count Clock Selection                                   | 195 |

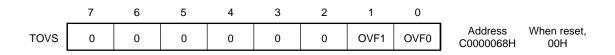

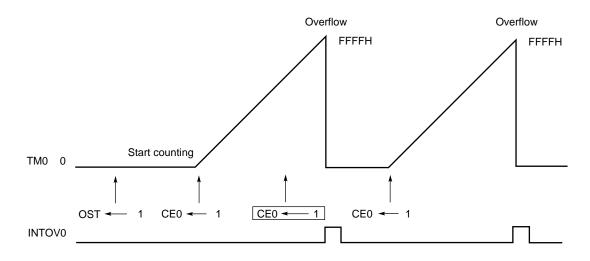

|            |      | 10.4.3 Overflow                                                | 196 |

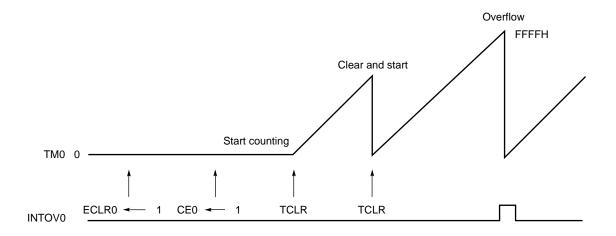

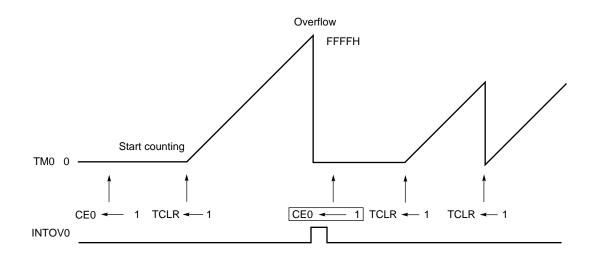

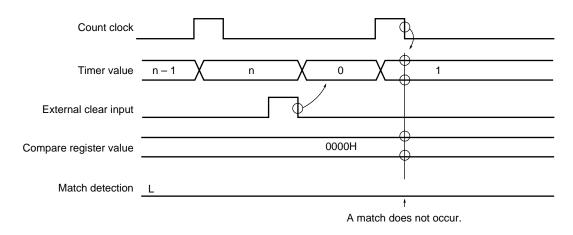

|            |      | 10.4.4 Clearing/Starting the Timer by the TCLR Input           |     |

|            |      | 10.4.5 Capturing                                               | 198 |

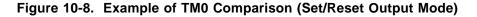

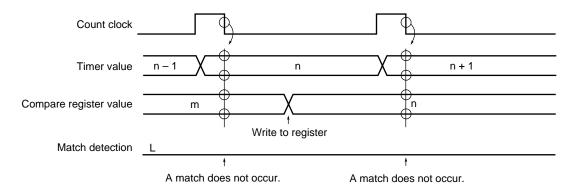

|            |      | 10.4.6 Comparison                                              | 199 |

|            | 10.5 | OPERATION OF TIMER 1                                           | 201 |

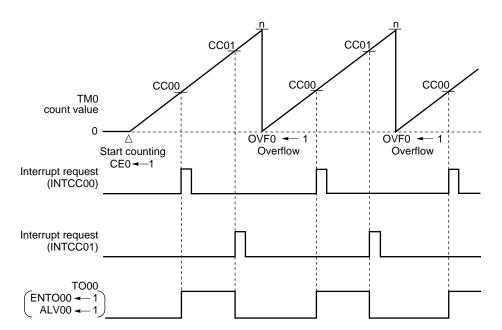

|            |      | 10.5.1 Counting                                                |     |

|            |      | 10.5.2 Input Clock Selection                                   |     |

|            |      | 10.5.3 Overflow                                                | 201 |

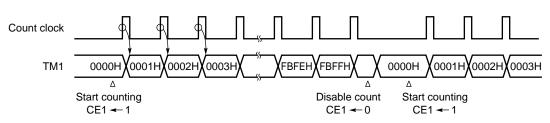

|            |      | 10.5.4 Comparison                                              | 202 |

|            | 10.6 | EXAMPLES OF APPLICATIONS                                       | 204 |

|            | 10.7 | CAUTIONS                                                       | 211 |

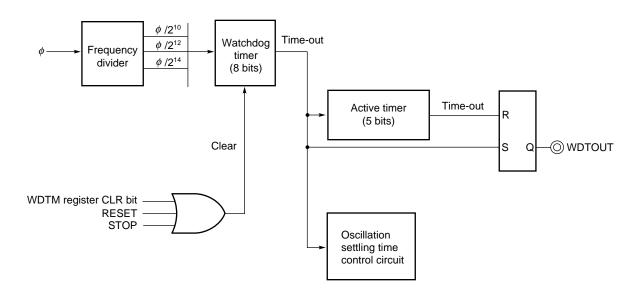

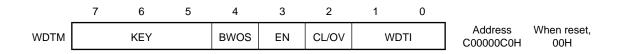

| CHAPTER 11 | WAT  | CHDOG TIMER FUNCTIONS                                          | 213 |

|            | 11.1 | FEATURES                                                       | 213 |

|            | 11.2 | CONFIGURATION                                                  | 213 |

|            | 11.3 | OPERATION                                                      | 214 |

|            | 11.4 | WDT MODE REGISTER (WDTM)                                       | 215 |

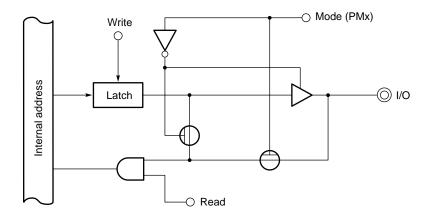

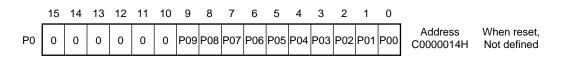

| CHAPTER 12 | PORT FUNCTIONS 2                                               |     |  |  |  |

|------------|----------------------------------------------------------------|-----|--|--|--|

|            | 12.1 FEATURES                                                  | 217 |  |  |  |

|            | 12.2 CONFIGURATION                                             | 217 |  |  |  |

|            | 12.3 PIN FUNCTIONS OF PORT 0                                   | 218 |  |  |  |

|            | 12.4 CONTROL REGISTER                                          | 219 |  |  |  |

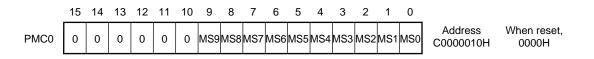

|            | 12.4.1 Port Mode Control Register 0 (PMC0)                     | 219 |  |  |  |

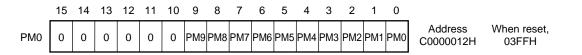

|            | 12.4.2 Port Mode Register 0 (PM0)                              | 219 |  |  |  |

| CHAPTER 13 | CLOCK GENERATION FUNCTIONS                                     | 221 |  |  |  |

|            | 13.1 FEATURES                                                  | 221 |  |  |  |

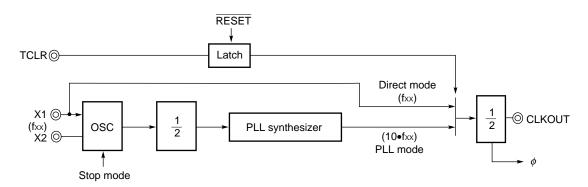

|            | 13.2 CONFIGURATION                                             | 221 |  |  |  |

|            | 13.3 INPUT CLOCK SELECTION                                     | 222 |  |  |  |

|            | 13.3.1 Direct Mode                                             | 222 |  |  |  |

|            | 13.3.2 PLL Mode                                                | 222 |  |  |  |

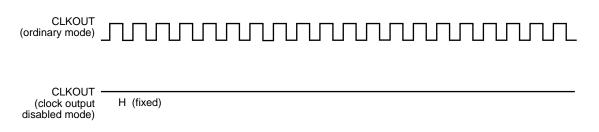

|            | 13.4 CLOCK OUTPUT CONTROL                                      | 223 |  |  |  |

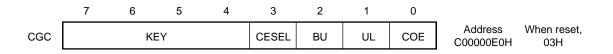

|            | 13.5 CLOCK CONTROL REGISTER (CGC)                              | 224 |  |  |  |

| CHAPTER 14 | STANDBY FUNCTIONS                                              | 225 |  |  |  |

|            | 14.1 FEATURES                                                  | 225 |  |  |  |

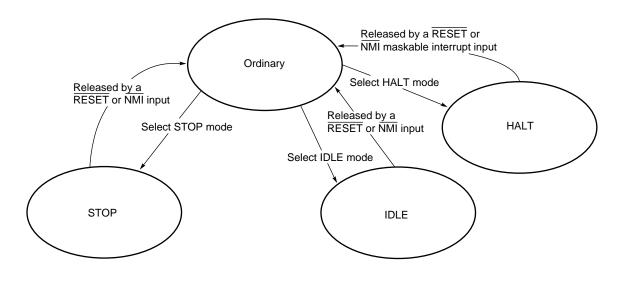

|            | 14.2 STANDBY MODE                                              | 225 |  |  |  |

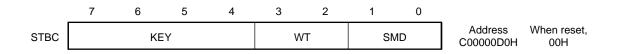

|            | 14.3 STANDBY CONTROL REGISTER (STBC)                           | 228 |  |  |  |

|            | 14.4 HALT MODE                                                 | 229 |  |  |  |

|            | 14.4.1 Placing the System in the HALT Mode and Operation State | 229 |  |  |  |

|            | 14.4.2 Releasing the System from the HALT Mode                 | 230 |  |  |  |

|            | 14.5 IDLE MODE                                                 | 231 |  |  |  |

|            | 14.5.1 Placing the System in the IDLE Mode and Operation State | 231 |  |  |  |

|            | 14.5.2 Releasing the System from the IDLE Mode                 | 233 |  |  |  |

|            | 14.6 STOP MODE                                                 | 234 |  |  |  |

|            | 14.6.1 Placing the System in the STOP Mode and Operation State | 234 |  |  |  |

|            | 14.6.2 Releasing the System from the STOP Mode                 | 235 |  |  |  |

|            | 14.7 SECURING OSCILLATION SETTLING TIME                        | 235 |  |  |  |

| CHAPTER 15 | RESET FUNCTIONS                                                | 237 |  |  |  |

|            | 15.1 FEATURES                                                  | 237 |  |  |  |

|            | 15.2 PIN FUNCTIONS                                             | 237 |  |  |  |

|            | 15.3 INITIALIZATION                                            | 239 |  |  |  |

| APPENDIX A | REGISTER INDEX                                                 | 243 |  |  |  |

|            | A.1 REGISTER NAMES                                             | 243 |  |  |  |

|            | A.2 REGISTER SYMBOLS                                           | 245 |  |  |  |

| APPENDIX B | GENERAL INDEX                                                  | 247 |  |  |  |

### LIST OF FIGURES

| Figure No. | Title                                                                            | Page |

|------------|----------------------------------------------------------------------------------|------|

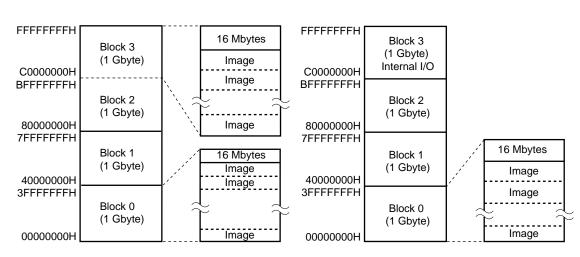

| 3-1.       | Memory Map                                                                       | 46   |

| 3-2.       | I/O Мар                                                                          | 47   |

| 3-3.       | Images in an Address Space                                                       | 48   |

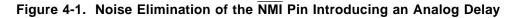

| 4-1.       | Noise Elimination of the $\overline{\text{NMI}}$ Pin Introducing an Analog Delay | 58   |

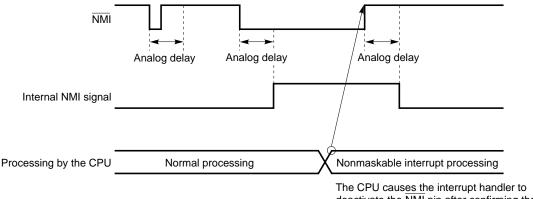

| 4-2.       | Nonmaskable Interrupt Handling Procedure                                         | 59   |

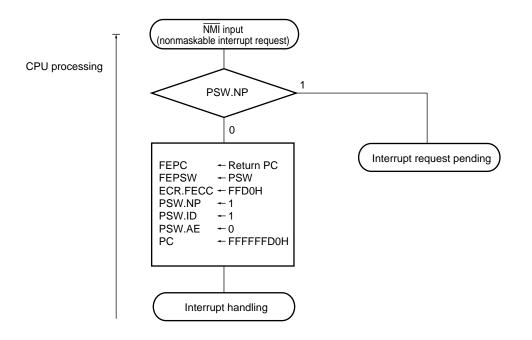

| 4-3.       | Accepting a Nonmaskable Interrupt Request                                        | 59   |

| 4-4.       | Maskable Interrupts                                                              | 60   |

| 4-5.       | Maskable Interrupt Handling Procedure                                            | 62   |

| 5-1.       | CPU Bus Cycle State Transition                                                   | 76   |

| 5-2.       | DMAC Bus Cycle State Transition                                                  | 78   |

| 5-3.       | Data Flow When an Additional Bus Cycle Is Used                                   | 81   |

| 5-4.       | Read Cycle                                                                       | 83   |

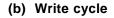

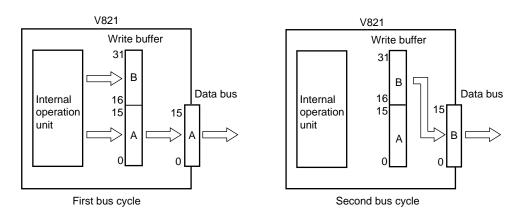

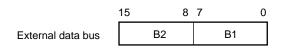

| 5-5.       | Write Cycle                                                                      | 84   |

| 5-6.       | Write Cycles for Bit Strings                                                     | 85   |

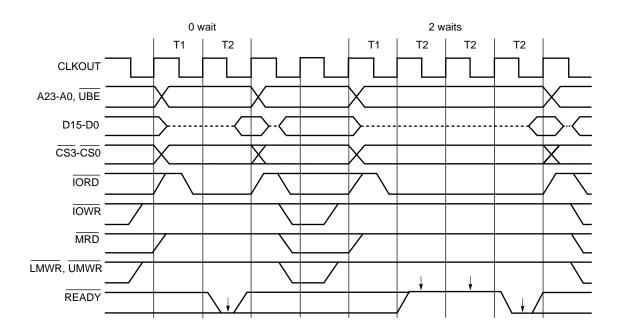

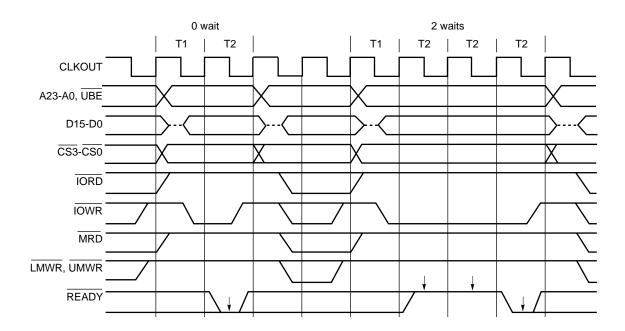

| 5-7.       | External I/O Read Cycle                                                          | 86   |

| 5-8.       | External I/O Write Cycle                                                         | 87   |

| 5-9.       | Internal I/O Read Cycle                                                          | 88   |

| 5-10.      | Internal I/O Write Cycle                                                         | 89   |

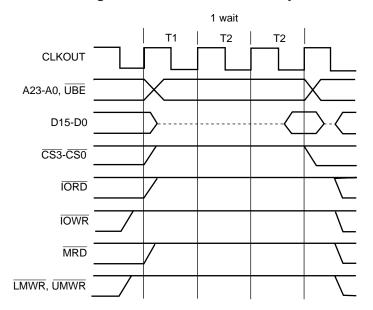

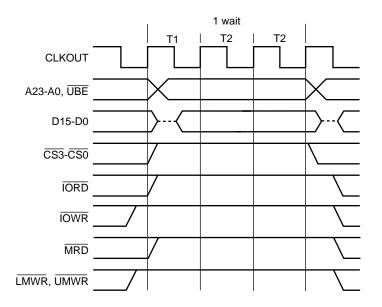

| 5-11.      | SRAM (ROM) Read Cycle                                                            | 90   |

| 5-12.      | SRAM Write Cycle                                                                 | 91   |

| 5-13.      | Page-ROM Read Cycle                                                              | 92   |

| 5-14.      | DRAM Read Cycle                                                                  | 94   |

| 5-15.      | DRAM Write Cycle                                                                 | 96   |

| 5-16.      | CBR Refresh Cycle                                                                | 98   |

| 5-17.      | CBR Self-Refresh Cycle                                                           | 99   |

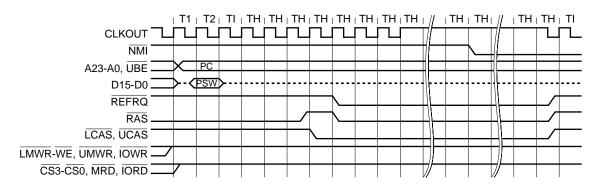

| 5-18.      | Fly-by Read Cycle during DMA Block Transfer (DRAM to External I/O Device)        | 100  |

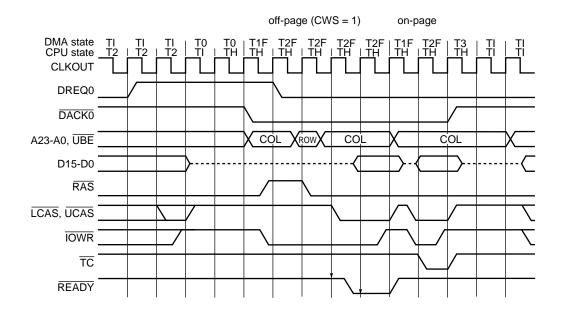

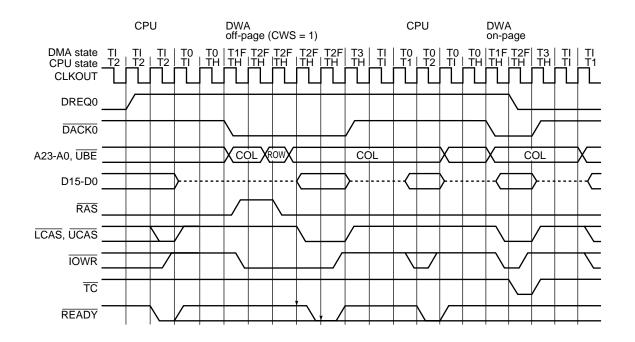

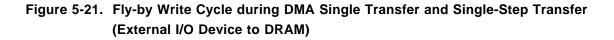

| 5-19.      | Fly-by Read Cycle during DMA Single Transfer and Single-Step Transfer            | 101  |

|            | (DRAM to External I/O Device)                                                    | 101  |

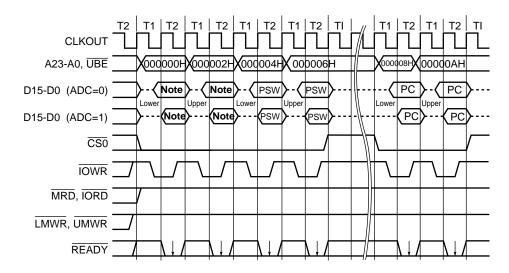

| 5-20.      | Fly-by Write Cycle during DMA Block Transfer (External I/O Device to DRAM)       | 102  |

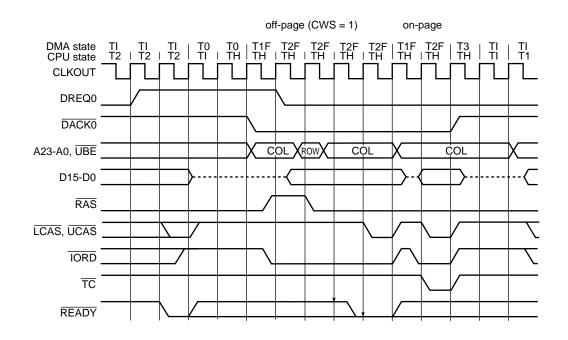

| 5-21.      | Fly-by Write Cycle during DMA Single Transfer and Single-Step Transfer           | 103  |

|            | (External I/O Device to DRAM)                                                    | 103  |

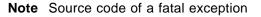

| 5-22.      | Machine Fault Cycle                                                              | 105  |

| 5-23.      | Halt Acknowledge Cycle                                                           | 105  |

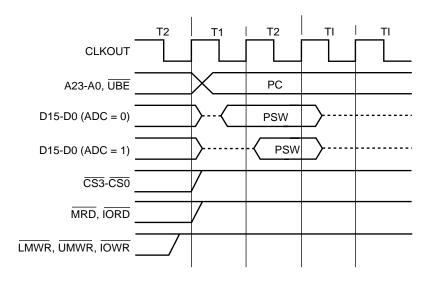

| 5-24.      | Bus Hold Cycle                                                                   | 107  |

| Figure No. | Title                                                                          |     |  |  |  |

|------------|--------------------------------------------------------------------------------|-----|--|--|--|

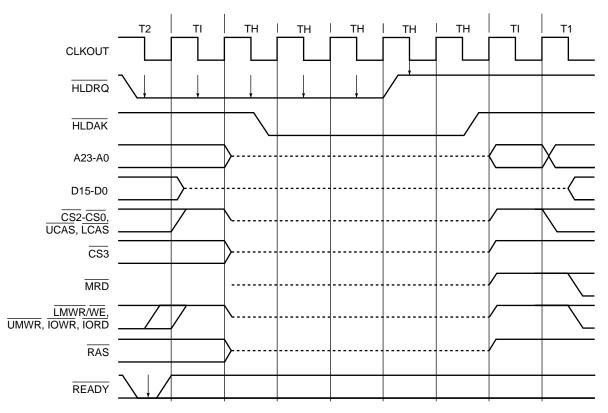

| 5-25.      | Bus Lock Cycle When the CAXI Instruction Is Executed                           | 108 |  |  |  |

| 6-1.       | Memory and I/O Maps                                                            | 109 |  |  |  |

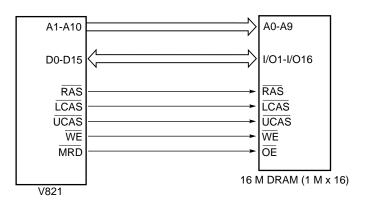

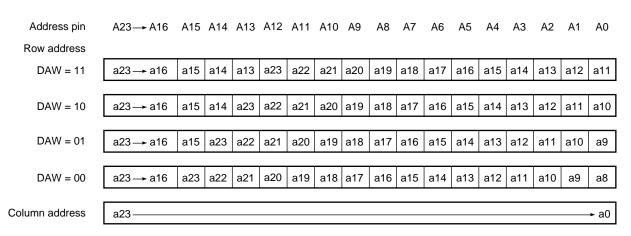

| 7-1.       | Connection of 16-Mbyte (1-Mbyte x 16) DRAM                                     | 120 |  |  |  |

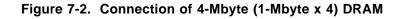

| 7-2.       | Connection of 4-Mbyte (1-Mbyte x 4) DRAM                                       | 120 |  |  |  |

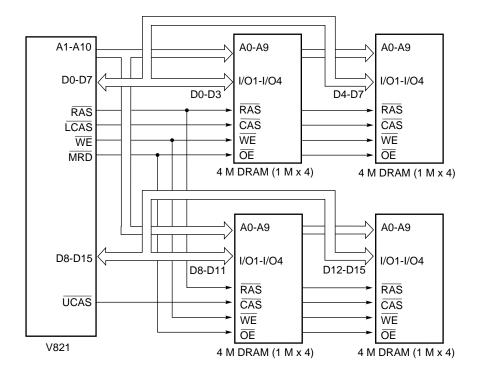

| 7-3.       | Output of Row and Column Addresses                                             | 121 |  |  |  |

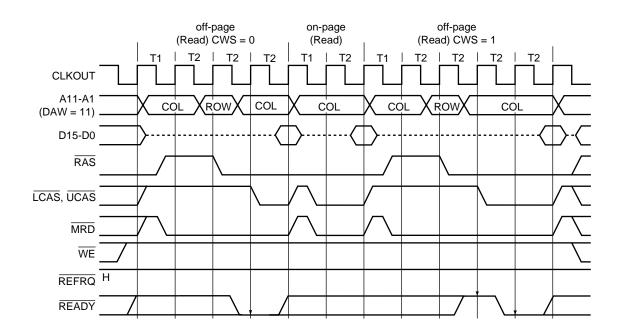

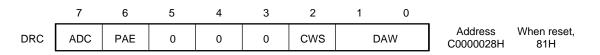

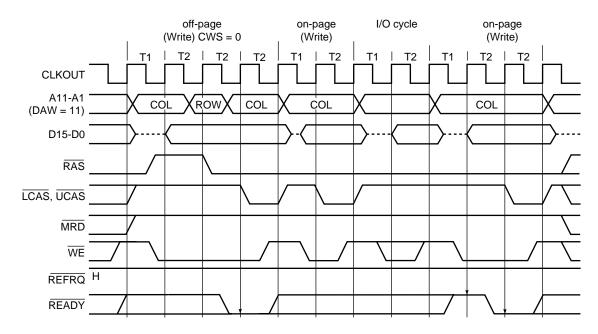

| 7-4.       | DRAM Read Cycle                                                                | 124 |  |  |  |

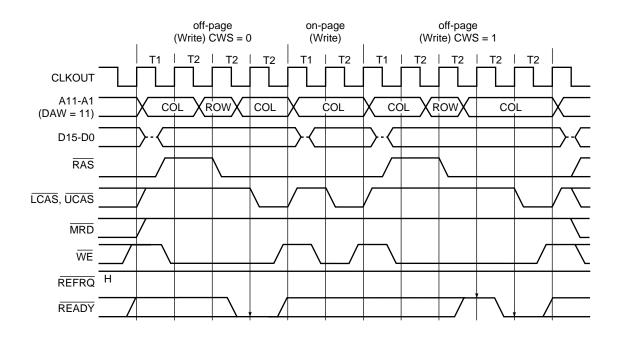

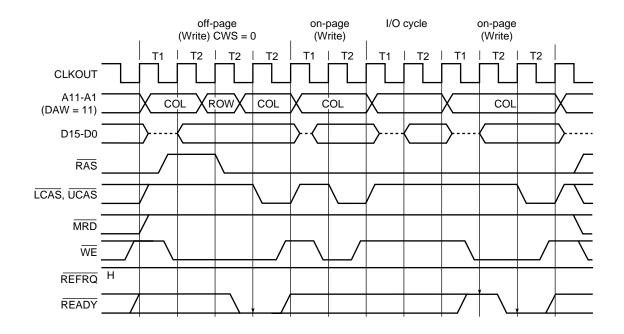

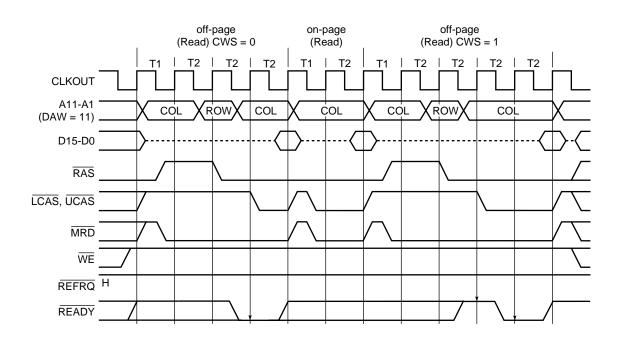

| 7-5.       | DRAM Write Cycle                                                               | 125 |  |  |  |

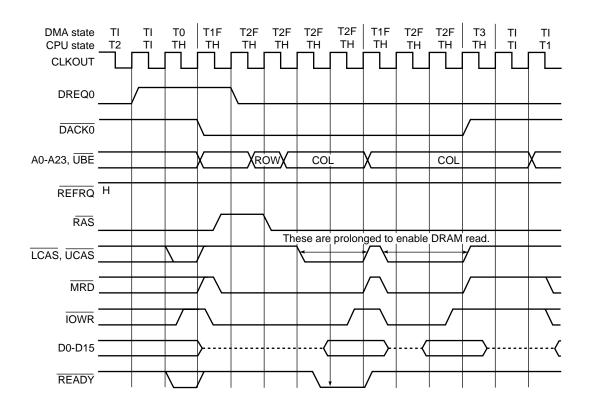

| 7-6.       | Insertion of Wait State (1 Wait) during DRAM Read for                          | 127 |  |  |  |

|            | Fly-by DMA Transfer (DRAM to External I/O)                                     | 127 |  |  |  |

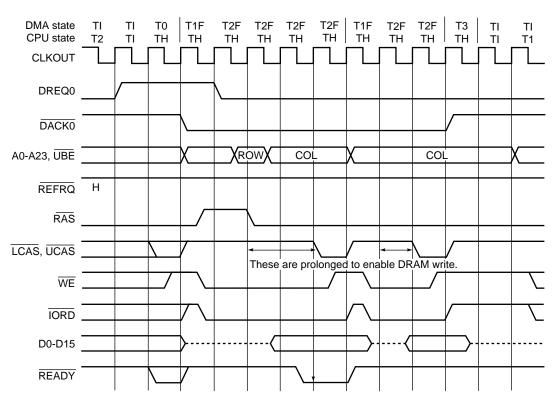

| 7-7.       | Insertion of Wait State (1 Wait) during DRAM Write for                         | 128 |  |  |  |

|            | Fly-by DMA Transfer (External I/O to DRAM)                                     | 128 |  |  |  |

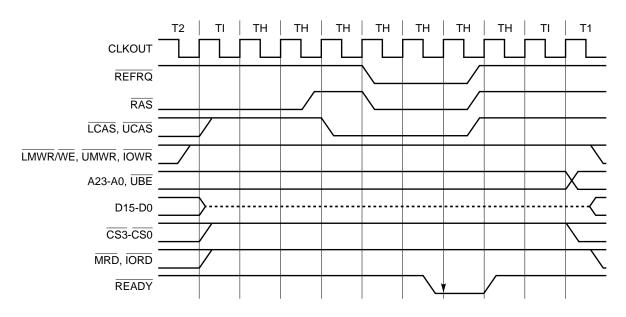

| 7-8.       | CBR Refresh Cycle                                                              |     |  |  |  |

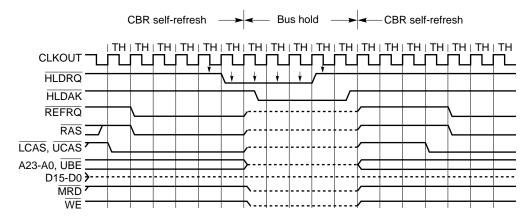

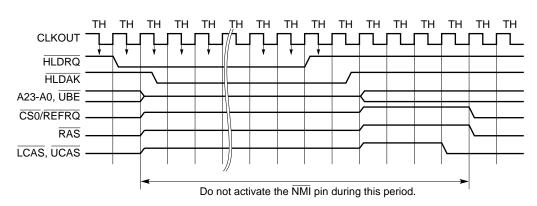

| 7-9.       | Cancellation of CBR Self Refresh with MMI Input                                | 132 |  |  |  |

| 7-10.      | Cancellation of CBR Self-Refresh with HLDRQ Input (in IDLE mode)               |     |  |  |  |

| 7-11.      | on-page/off-page Decision When ROM Having a Page Access Function Is            |     |  |  |  |

|            | Connected                                                                      | 134 |  |  |  |

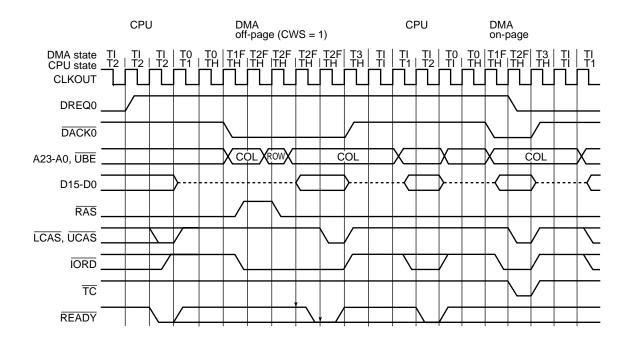

| 7-12.      | Timing of the Page-ROM Cycle (16-Mbit (1-Mbit x 16) Page-ROM)                  |     |  |  |  |

| 7-13.      | Connection of 16-Mbit (1-Mbit x 16) Page-ROM                                   |     |  |  |  |

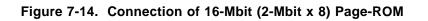

| 7-14.      | Connection of 16-Mbit (2-Mbit x 8) Page-ROM                                    |     |  |  |  |

| 8-1.       | Block Diagram of DMAC                                                          | 140 |  |  |  |

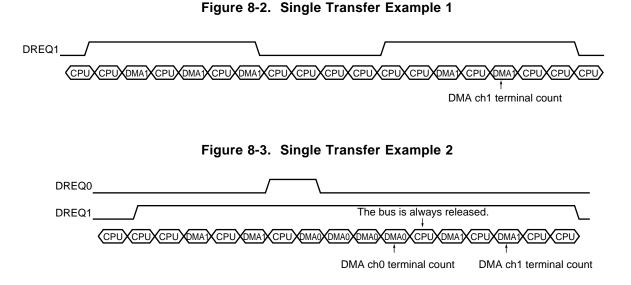

| 8-2.       | Single Transfer Example 1                                                      | 146 |  |  |  |

| 8-3.       | Single Transfer Example 2                                                      | 146 |  |  |  |

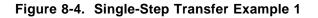

| 8-4.       | Single-Step Transfer Example 1                                                 | 146 |  |  |  |

| 8-5.       | Single-Step Transfer Example 2                                                 | 147 |  |  |  |

| 8-6.       | Block Transfer Example                                                         | 147 |  |  |  |

| 8-7.       | Timing of Two-Cycle, Single-Step DMA Transfer (External I/O to DRAM (on-page)) | 148 |  |  |  |

| 8-8.       | Timing of Fly-by DMA Transfer (DRAM (on-page) to External I/O)                 | 149 |  |  |  |

| 8-9.       | Timing of DMA Transfer End Output                                              | 151 |  |  |  |

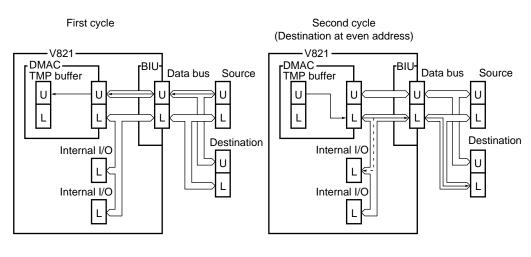

| 8-10.      | Data Flow during DMA Transfer (Two-Cycle Byte Transfer)                        | 152 |  |  |  |

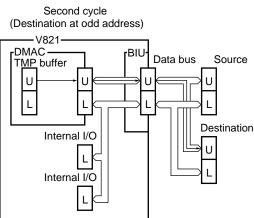

| 8-11.      | Data Flow during DMA Transfer (Two-Cycle, 16-Bit Transfer)                     |     |  |  |  |

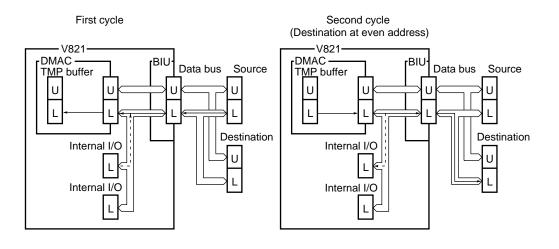

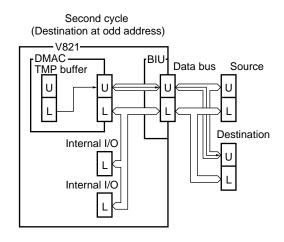

| 8-12.      | Data Flow during DMA Transfer (Fly-by Transfer)                                |     |  |  |  |

| 9-1.       | Asynchronous Serial Interface                                                  | 157 |  |  |  |

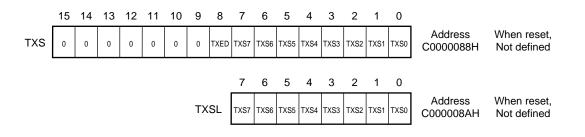

| 9-2.       | Format of Transmission and Reception Data Transferred                          | 165 |  |  |  |

|            | via Asynchronous Serial Interface                                              | 165 |  |  |  |

| Figure No. | Title                                                                         | Page  |  |  |  |

|------------|-------------------------------------------------------------------------------|-------|--|--|--|

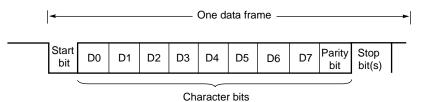

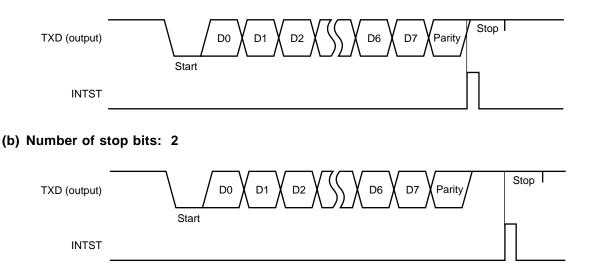

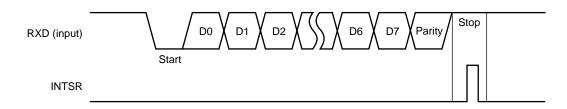

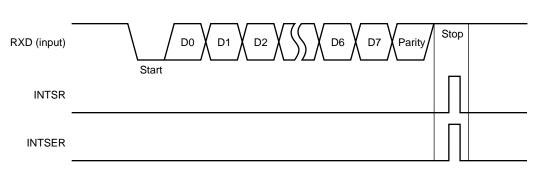

| 9-3.       | Timing of Transmission Completion Interrupt via Asynchronous Serial Interface | . 166 |  |  |  |

| 9-4.       | Timing of Reception Completion Interrupt via Asynchronous Serial Interface    | . 167 |  |  |  |

| 9-5.       | Timing of Reception Error                                                     |       |  |  |  |

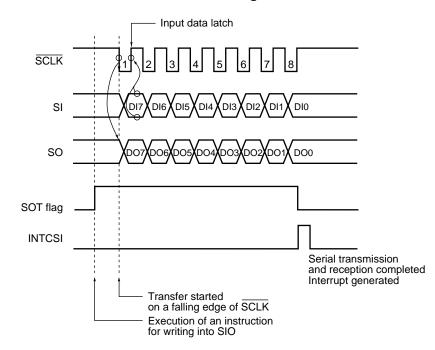

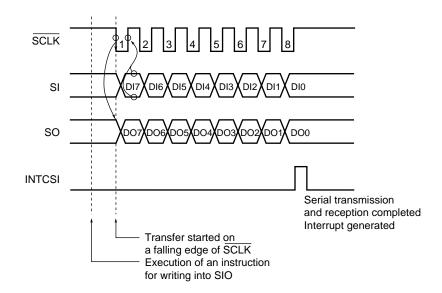

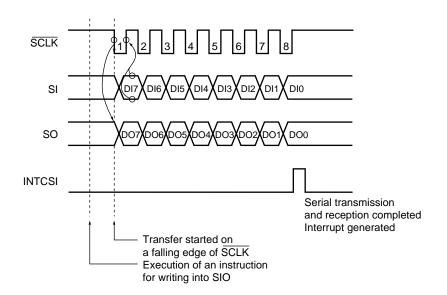

| 9-6.       | Timing of Three-Wire Serial I/O Mode (Transmission)                           | . 174 |  |  |  |

| 9-7.       | Timing of Three-Wire Serial I/O Mode (Reception)                              | . 175 |  |  |  |

| 9-8.       | Timing of Three-Wire Serial I/O Mode (Transmission and Reception)             | . 177 |  |  |  |

| 9-9.       | Example System Configuration Using CSI                                        | . 177 |  |  |  |

| 9-10.      | Block Diagram                                                                 | . 178 |  |  |  |

| 10-1.      | Basic Operation of Timer 0                                                    | . 195 |  |  |  |

| 10-2.      | Operation after an Overflow (When ECLR0 = 0 and OST = 1)                      | . 196 |  |  |  |

| 10-3.      | Clearing/Starting TM0 by a TCLR Input (When ECLR0 = 1 and OST = 0)            | . 197 |  |  |  |

| 10-4.      | Clearing/Starting TM0 by a TCLR Input and the Related Overflow                |       |  |  |  |

|            | (When ECLR0 = 0 and OST = 1)                                                  | . 197 |  |  |  |

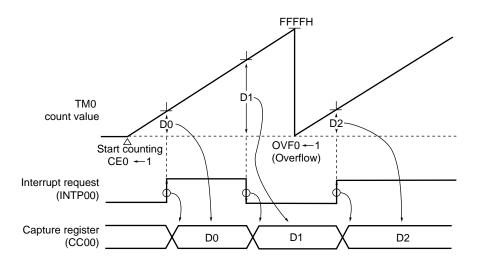

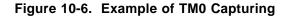

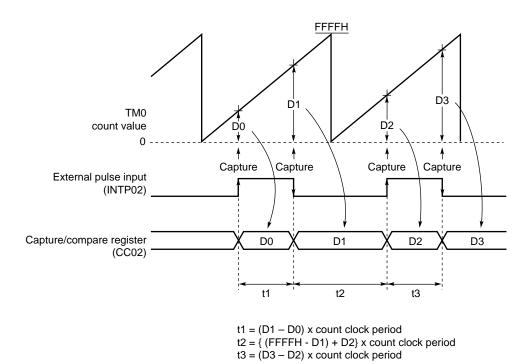

| 10-5.      | Example of TM0 Capturing (When Both Rising and Falling Edges Are Specified)   | . 198 |  |  |  |

| 10-6.      | Example of TM0 Capturing                                                      | . 199 |  |  |  |

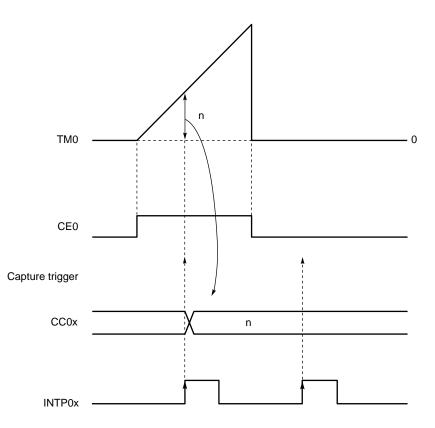

| 10-7.      | Example of Comparison                                                         | . 200 |  |  |  |

| 10-8.      | Example of TM0 Comparison (Set/Reset Output Mode)                             | . 200 |  |  |  |

| 10-9.      | Basic Operation of Timer 1                                                    | . 201 |  |  |  |

| 10-10.     | Operation from When CM1 Is 1 until It Is FFFFH                                | . 202 |  |  |  |

| 10-11.     | Operation with CM1 Cleared to 0                                               | . 203 |  |  |  |

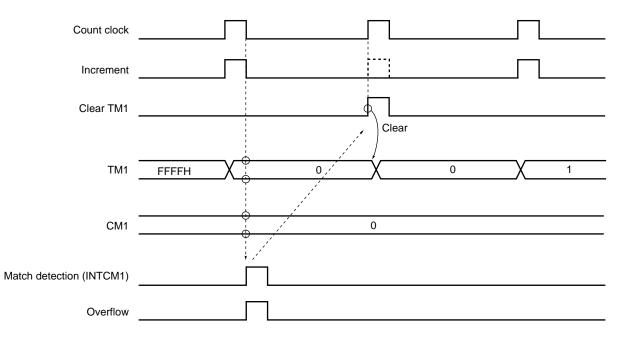

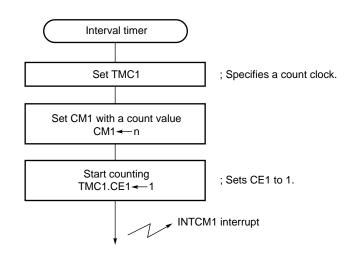

| 10-12.     | Interval Timer Operation Timing (Timer 1)                                     | . 204 |  |  |  |

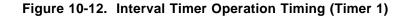

| 10-13.     | Interval Timer Operation Setting Procedure (Timer 1)                          | . 204 |  |  |  |

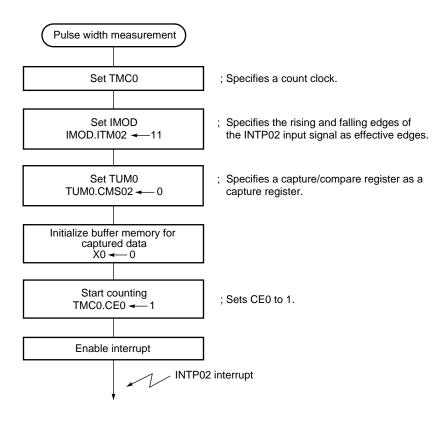

| 10-14.     | Pulse Width Measurement Timing (Timer 0)                                      | . 205 |  |  |  |

| 10-15.     | Pulse Width Measurement Setting Procedure (Timer 0)                           | . 206 |  |  |  |

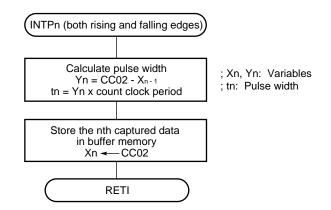

| 10-16.     | Pulse Width Calculation Interrupt Request Handling Routine (Timer 0)          | . 206 |  |  |  |

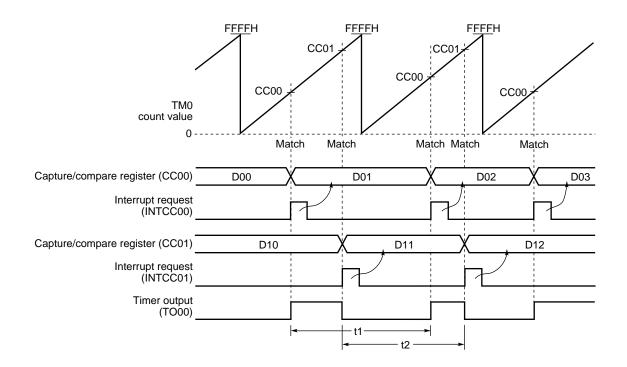

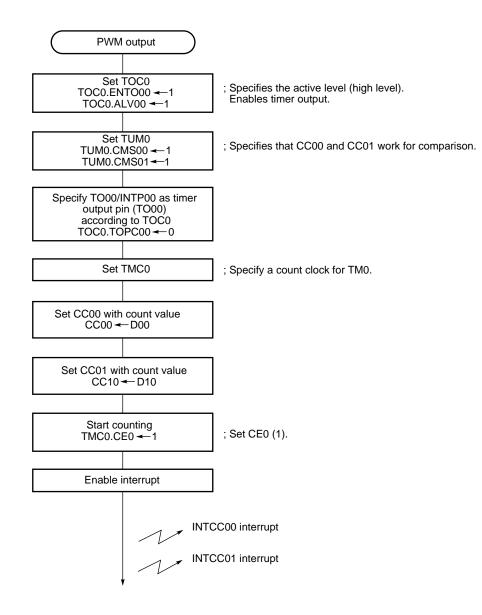

| 10-17.     | PWM Output Timing (TM0)                                                       | . 207 |  |  |  |

| 10-18.     | PWM Output Setting Procedure (Timer 0)                                        | . 208 |  |  |  |

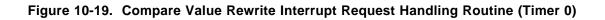

| 10-19.     | Compare Value Rewrite Interrupt Request Handling Routine (Timer 0)            | . 209 |  |  |  |

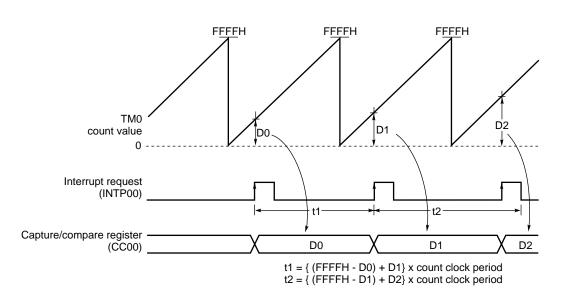

| 10-20.     | Pulse Width Measurement Timing (TM0)                                          | . 210 |  |  |  |

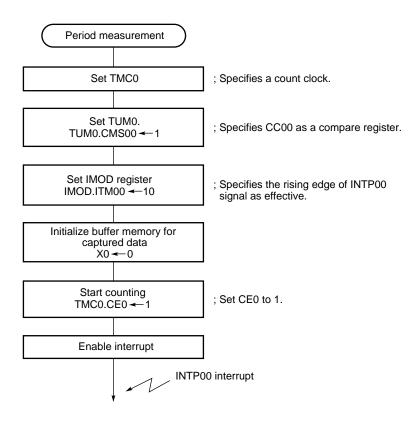

| 10-21.     | Period Measurement Setting Procedure (Timer 0)                                | . 210 |  |  |  |

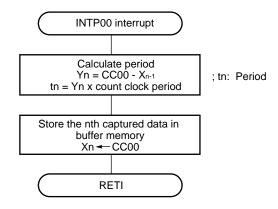

| 10-22.     | Period Calculation Interrupt Request Handling Routine (Timer 0)               | . 211 |  |  |  |

| 11-1.      | Watchdog Timer Block Diagram                                                  | . 213 |  |  |  |

| 14-1.      | Bus Hold in IDLE Mode and Restart of Self-Refresh                             | . 233 |  |  |  |

### LIST OF TABLES

| Table No. | Title                                                                                                                                | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|------|

| 3-1.      | Program Registers                                                                                                                    | 50   |

| 3-2.      | System Register Numbers                                                                                                              | 51   |

| 3-3.      | Built-in Peripheral I/O Registers                                                                                                    | 52   |

| 4-1.      | Interrupts                                                                                                                           | 56   |

| 4-2.      | Correspondence between Priorities, Exception Codes, Handler Addresses,<br>and Interrupt Levels (When the IGP Register Is Set to 4EH) | 65   |

| 4-3.      | Correspondence between Interrupt Control Register Bits and                                                                           |      |

|           | Interrupt Request Signals                                                                                                            | 67   |

| 4-4.      | Priorities of Interrupts and Exceptions                                                                                              | 73   |

| 4-5.      | Priorities of Floating-Point Exceptions                                                                                              | 74   |

| 5-1.      | Bus Priority                                                                                                                         | 80   |

| 5-2.      | Relationship between Addresses, Data Length, UBE, and Address Pins                                                                   | 82   |

| 5-3.      | Correspondence between the Address Bus and Data Bus in the Machine Fault Cycle                                                       | 104  |

| 6-1.      | Bus Cycles during Which the Wait Function Is Effective                                                                               | 112  |

| 6-2.      | Cycles during Which Programmable Waits Can Be Set, and                                                                               |      |

|           | Corresponding Control Registers                                                                                                      |      |

| 6-3.      | Number of Waits to Be Inserted during Fly-by DMA Transfer                                                                            |      |

|           | (at off-page Time during DRAM Cycle)                                                                                                 | 118  |

| 7-1.      | DRAM Control Pins                                                                                                                    | 119  |

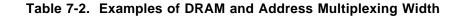

| 7-2.      | Examples of DRAM and Address Multiplexing Width                                                                                      | 121  |

| 7-3.      | Differences between on-page and off-page Cycles                                                                                      | 123  |

| 7-4.      | DRAM Refresh Intervals                                                                                                               | 130  |

| 7-5.      | Examples of Setting the Interval Factor                                                                                              | 130  |

| 8-1.      | Transfer Types vs. Transfer Objects                                                                                                  | 149  |

| 9-1.      | Generated Interrupts and Default Priorities                                                                                          | 164  |

| 9-2.      | BRG Setting Data                                                                                                                     | 180  |

| 10-1.     | Configuration of the RPU                                                                                                             | 184  |

| 10-2.     | Capture Trigger Signal for the 16-Bit Capture Register (TM0)                                                                         | 198  |

| Table No. | Title                                                           | Page |

|-----------|-----------------------------------------------------------------|------|

| 10-3.     | Interrupt Request Signal from the 16-Bit Compare Register (TM0) | 199  |

| 12-1.     | Port Operation                                                  | 220  |

| 14-1.     | Clock Generator Operation under Standby Control                 | 226  |

| 14-2.     | Operations during the HALT Mode                                 | 229  |

| 14-3.     | Operations during the IDLE Mode                                 | 232  |

| 14-4.     | Operations during the STOP Mode                                 | 234  |

| 14-5.     | Count Time Examples                                             | 236  |

| 15-1.     | Output State of Each Pin during a Reset                         | 238  |

| 15-2.     | Initial Value in Each Register after a Reset                    | 240  |

[MEMO]

### **CHAPTER 1 OVERVIEW**

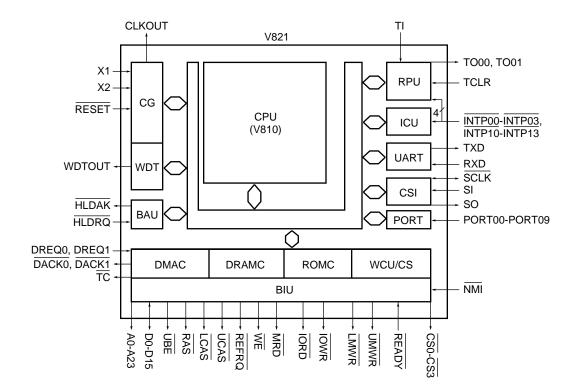

The V821 is a 32-/16-bit RISC microprocessor that uses, as its processor core, the high-performance 32-bit V810<sup>TM</sup> ( $\mu$ PD70732) microprocessor designed for built-in control applications. It incorporates peripheral functions such as a DRAM/ROM controller, 2-channel DMA controller, real-time pulse unit, serial interface, and interrupt controller.

The V821, which offers quick real-time response, high-speed integer instructions, bit string instructions, and floating-point instructions, is ideally suited to use in OA equipment such as printers and facsimiles, image processing devices such as those used in navigation units, portable devices, and other devices demanding excellent cost performance.

### **1.1 FEATURES**

| • 32-bit CPU core                                  | Compatible with V810 instructions<br>Built-in 1-Kbyte instruction cache memory<br>1-clock-pulse pitch pipeline<br>16-bit data bus<br>Internal 4-Gbyte linear addresses<br>General-purpose registers: 32 bits x 32          |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | Instruction group that can be applied to a wide range of fields (floating-<br>point instructions, bit string manipulation instructions)                                                                                    |

| <ul> <li>Interrupts/exceptions</li> </ul>          | Nonmaskable : 1 external input<br>Maskable : 8 external inputs<br>11 types of internal sources<br>Priorities can be specified in units of four groups.                                                                     |

| • Wait control unit                                | Capable of CS control over four blocks in both memory and I/O spaces.<br>Linear address space of each block: 16 Mbytes<br>Automatic insertion of 0-7 waits per block<br>Bus cycle (page-ROM, DRAM) selection function      |

| <ul> <li>Memory access control function</li> </ul> | S                                                                                                                                                                                                                          |

|                                                    | Supports DRAM high-speed page mode.                                                                                                                                                                                        |

|                                                    | Supports page-ROM page mode.                                                                                                                                                                                               |

| DMA controller                                     | 2 channels                                                                                                                                                                                                                 |

|                                                    | Maximum transfer count: 65,536<br>Two transfer types (fly-by (1-cycle) transfer and 2-cycle transfer)<br>Three transfer modes (single transfer, single-step transfer, and block<br>transfer)<br>Programmable wait function |

- Serial interfaces

Asynchronous serial interface (UART): 1 channel

Synchronous serial interface (CSI): 1 channel

Built-in dedicated baud rate generator

- Real-time pulse unit

16-bit timer/event counter: 1 channel Timer output: 2

16-bit capture/compare register: 4

16-bit interval timer: 1 channel

- Watchdog timer functions

- Clock generator Multiplication-by-5 function with a PLL clock synthesizer

Standby functions HALT, IDLE, and STOP modes Clock output control

### ★ 1.2 ORDERING INFORMATION

| Part number       | Package                           | Maximum operating frequency (MHz) |  |

|-------------------|-----------------------------------|-----------------------------------|--|

| μPD70741GC-25-8EU | 100-pin plastic LQFP (fine pitch) | 25                                |  |

|                   | (14 x 14 x 1.40 mm)               |                                   |  |

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

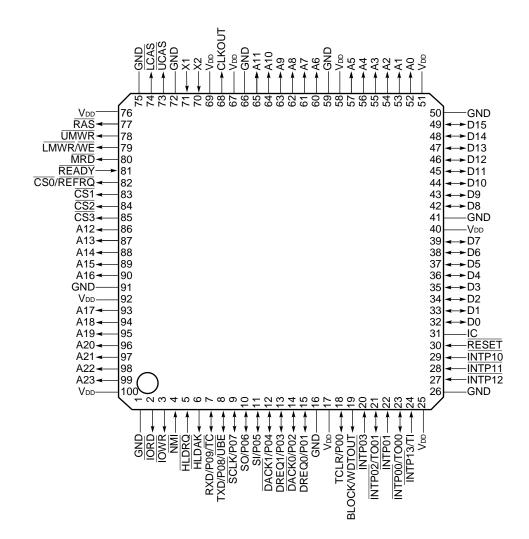

### ★ 1.3 PIN CONFIGURATION (TOP VIEW)

100-pin plastic LQFP (fine pitch) (14 x 14 mm)  $\mu$ PD70741GC-25-8EU

Caution Connect pin IC to GND via a resistor.

### Pin names

| A0-A23                       | : Address Bus                    |

|------------------------------|----------------------------------|

| BLOCK                        | : Bus Lock                       |

| CLKOUT                       | : System Clock Out               |

| CS0-CS3                      | : Chip Select                    |

| D0-D15                       | : Data Bus                       |

| DACKO, DACK1                 | : DMA Acknowledge                |

| DREQ0, DREQ1                 | : DMA Request                    |

| HLDAK                        | : Hold Acknowledge               |

| HLDRQ                        | : Hold Request                   |

| INTP00-INTP03, INTP10-INTP13 | : Interrupt Request              |

| IORD                         | : I/O Read                       |

| IOWR                         | : I/O Write                      |

| LCAS                         | : Lower Column Address Strobe    |

| LMWR                         | : Lower Memory Write             |

| MRD                          | : Memory Read                    |

| NMI                          | : Non-maskable Interrupt Request |

| P00-P09                      | : Port                           |

| RAS                          | : Row Address Strobe             |

| READY                        | : Ready                          |

| REFRQ                        | : Refresh Request                |

| RESET                        | : Reset                          |

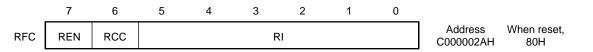

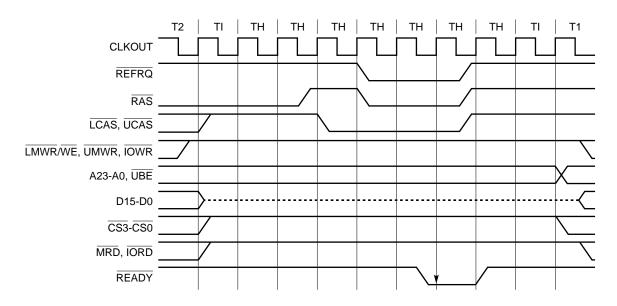

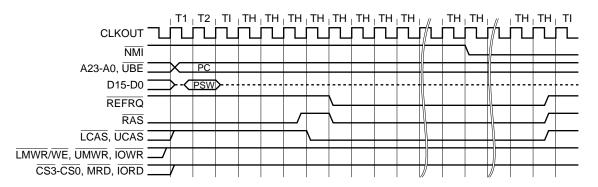

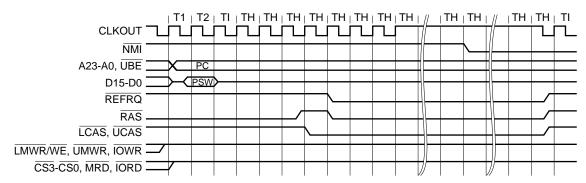

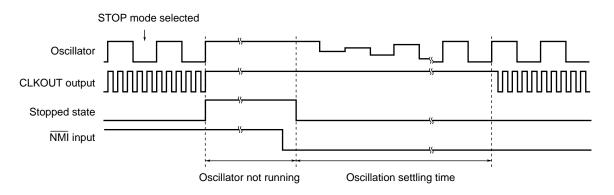

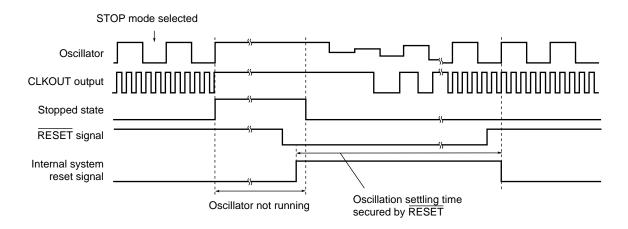

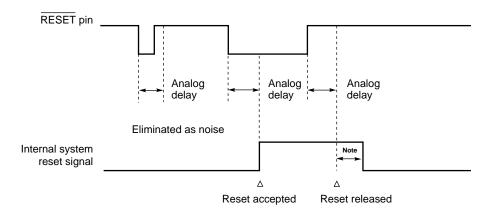

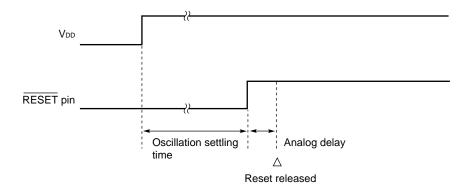

| RXD                          | : Receive Data                   |