# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# USER'S MANUAL

# V40HL<sup>TM</sup> and V50HL<sup>TM</sup> 16/8-BIT AND 16-BIT MICROPROCESSORS

**HARDWARE**

$\mu$ PD70208H  $\mu$ PD70216H

#### **NOTES FOR CMOS DEVICES -**

#### 1 PRECAUTION AGAINST-ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to Vpp or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# 3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

al: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

## Major Revisions in this Edition

| Page        | Description                                                       |  |

|-------------|-------------------------------------------------------------------|--|

| p. 24       | 3.2 (8) RESET Addition of description                             |  |

| p. 141      | Table 5-17 Internal Clock and Maximum Baud Rate Addition of items |  |

| p. 178      | 5.9.7 Incomplete interrupt Modification of Caution 2              |  |

| p. 222      | 5.10.12 Cascade connection Addition of µPD71037                   |  |

| p. 244      | Table 6-1 Validity of Walt State in Each Bus Cycle Modification   |  |

| p. 250, 251 | 6.3 Interrupt Function Addition of description                    |  |

| p. 252      | Table 6-3 Interrupt Sources Addition of Note                      |  |

| p. 269      | 6.6.3 (2) HALT mode Addition of description                       |  |

The mark \* shows major revised points.

#### INTRODUCTION

**Target users**

This manual is intended for engineers who wish to understand the functions of the  $\mu$ PD70208H and the  $\mu$ PD70216H (also called the V40HL and V50HL, respectively) and use these products to design application systems.

**Objectives**

The objective of this manual is to provide the user with an understanding of the  $\mu$ PD70208H and  $\mu$ PD70216H hardware functions, which are indicated in the organization shown below.

**Organization**

The  $\mu$ PD70208H and  $\mu$ PD70216H user's manuals are divided into two versions, the hardware version (this manual) and the instruction version (16-Bit V Series<sup>TM</sup> User's Manual – Instruction).

- General Description

- Pin Functions

- Architecture

- Internal Block Functions

- Internal/External Control Functions

- μPD8080AF Emulation

Instruction Version

- General Description

- Description of Instructions

- Instruction Map

- Table of μPD8086 and μPD8088 Mnemonic Correspondence

How to Read this Manual

Those who read this manual require a general understanding of electronics, logic circuits, and microprocessors. In this manual, descriptions of the part numbers  $\mu PD70208H$  and  $\mu PD70216H$  have been standardized to the V40HL and V50HL, respectively.

For users who already have experience with the  $\mu$ PD70208 and  $\mu$ PD70216 (also known as the V40<sup>TM</sup> and V50<sup>TM</sup>, respectively), the V40HL and V50HL are high-speed, low-power versions of the V40 and V50. Chiefly read section 1.5, entitled "Differences Between the V40HL and V50HL and the V40 and V50," to ascertain the differences between these products.

To ascertain the details of a register when the register name is known, read APPENDIX A, "REGISTER INDEX (IN ALPHABETICAL ORDER)."

To ascertain the details of a function when the function name is known, read APPENDIX B. "GENERAL INDEX."

To comprehend the details of instruction functions, refer to the separate manual "16-Bit V Series User's Manual – Instruction."

To comprehend the electrical characteristics of the V40HL and V50HL, refer to the separate data sheets.

To gain a general understanding of the V40HL and V50HL, read this manual in the sequence indicated in the table of contents.

#### Conventions

In general, in this manual uses the following conventions:

• Weighting of data notation: The high-order data are written on the left, while the

low-order data are written on the right.

• Active low notation : XXXX (over bar over pin and signal names).

• Memory map addresses : High-order addresses are on the top while low-order

addresses are on the bottom.

• The term "Note" placed in the text indicates that an additional or supplementary information will be provided somewhere below.

• The term "Caution" indicates an explanation that the reader should pay particular attention to.

• The term "Remark" indicates that a supplemental explanation of the text is provided.

• Numerical notation : Binary ... xxxx or xxxxB

Decimal ··· xxxx

Hexadecimal ... xxxxH

• Easily confused characters: 0 (zero) and the letter O.

1 (one), the upper-case letter I and the lower-case

letter I.

#### **Related Documents**

Brochure: U10652JNote Data Sheet: IC-3659

User's Manual Hardware: This manual

16-bit V series User's Manual Instructions: U11301E

Application Note Hardware Design: U10037E

Application Note Software: U10911E

Questions and Answers: U11123E

Register Application Table: IEM-5575Note

Note: This document number is that of Japanese-version document.

#### **CONTENTS**

| CHAPT  | ER 1   | GENERAL DESCRIPTION                                         |

|--------|--------|-------------------------------------------------------------|

| 1.1    | Featu  | ITOS                                                        |

| 1.2    | Orde   | ring Information                                            |

| 1.3    | Pin C  | onfigurations                                               |

| 1.4    | interr | nal Block Diagram 1                                         |

| 1.5    | Diffe  | rences Between the V40HL and V50HL and the V40 and V501     |

| 1.6    | Func   | tionai Overview 14                                          |

| CHAPT  | ER 2   | APPLICATIONS 17                                             |

| CHAPT  | ER 3   | PIN FUNCTIONS                                               |

| 3.1    | Pin F  | unction List 19                                             |

| 3.2    | Func   | tional Description of Pins                                  |

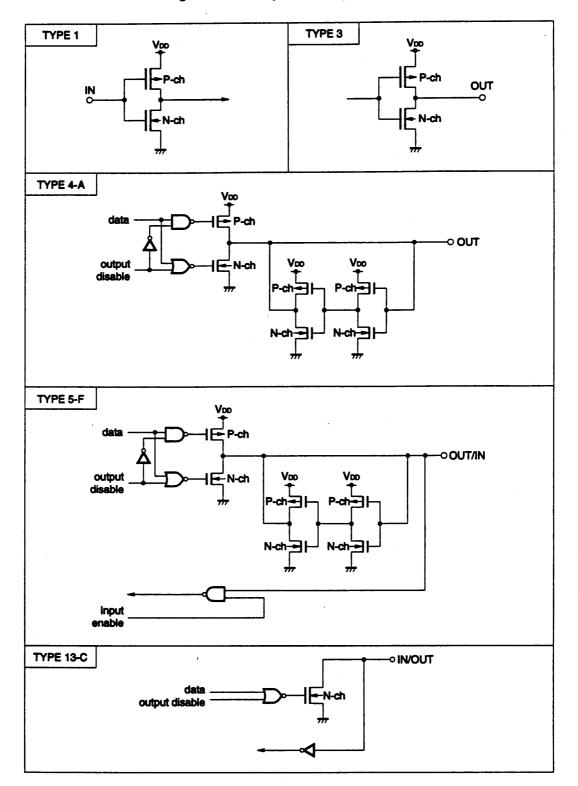

| 3.3    | Pin In | put/Output Circuits and Recommended Handling of Unused Pins |

| CHAPT  | ER 4   | ARCHITECTURE                                                |

| 4.1    | Memo   | ory and I/O Mapping                                         |

|        | 4.1.1  |                                                             |

|        | 4.1.2  | VO map and access methods                                   |

|        | 4.1.3  | System I/O area                                             |

|        | 4.1.4  | Memory I/O read and write timing                            |

|        | 4.1.4  | Memory I/O read and write timing                            |

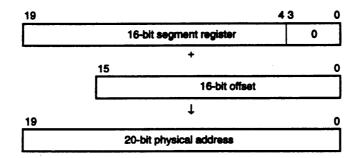

| 4.2    | Logic  | al Addresses and Physical Addresses62                       |

| 4.3    | Addr   | ess Generation                                              |

|        | 4.3.1  | Instruction address                                         |

|        | 4.3.2  | Data addressing 66                                          |

| 4.4    | Speed  | ding Up Instruction Execution                               |

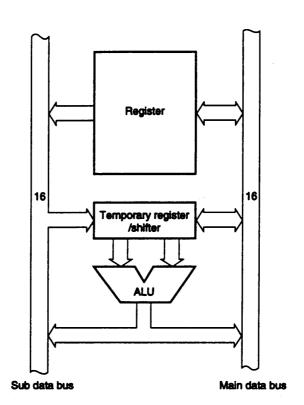

|        | 4.4.1  | Dual data buses                                             |

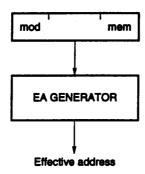

|        | 4.4.2  | Effective address generation circuit (EAG)                  |

|        | 4.4.3. | Temporary registers/shifters A/B (TA/TB)                    |

|        |        | Loop counter (LC)                                           |

|        | 4.4.5  | Program counter (PC) and prefetch pointer (PFP)             |

| CHAPTI | ER 5   | INTERNAL BLOCK FUNCTIONS 75                                 |

| 5.1    | CPU    | ······································                      |

| ·      | 5.1.1  | Features                                                    |

|        | 5.1.2  | Internal organization                                       |

| 5.2    | Clock  | Generator (CG)                                              |

|        | 5.2.1  | Features                                                    |

|        | 522    | Differences with the VAO and VEO                            |

|                 | 5.2.3          | Internal block                                        | 88  |

|-----------------|----------------|-------------------------------------------------------|-----|

| 5.3             | Bus Ir         | nterface Unit (BIU)                                   | 88  |

| 5.4             | Bus A          | rbitration Unit (BAU)                                 | 90  |

|                 | 5.4.1          | Priority                                              | 90  |

|                 | 5.4.2          | Bus wait operation                                    | 91  |

|                 | 5.4.3          | Timing of bus priority switching                      | 92  |

|                 | 5.4.4          | DMA request and hold request acceptance waiting times | 93  |

| 5.5             | Walt C         | Control Unit (WCU)                                    | 90  |

|                 | 5.5.1          | Features                                              | 96  |

|                 | 5.5.2          | Differences with the V40 and V50                      | 90  |

| 5.6             | Refres         | sh Control Unit (REFU)                                | 97  |

|                 | 5.6.1          | Features                                              | 97  |

|                 | 5.6.2          | Differences with the V40 and V50                      | 97  |

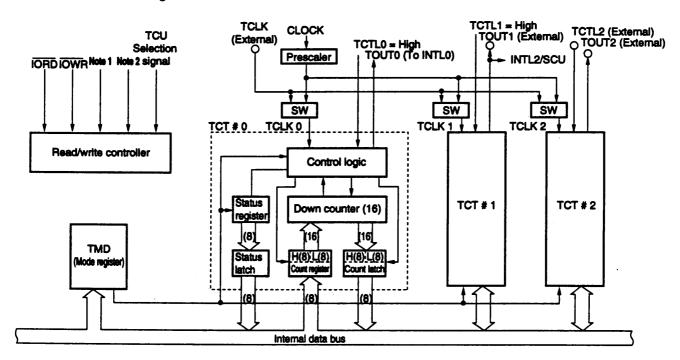

| 5.7             | Timer          | Counter Unit (TCU)                                    | 98  |

|                 | 5.7.1          | Features                                              | 98  |

|                 | 5.7.2          | Internal block diagram                                | 98  |

|                 | 5.7.3          | Addressing                                            |     |

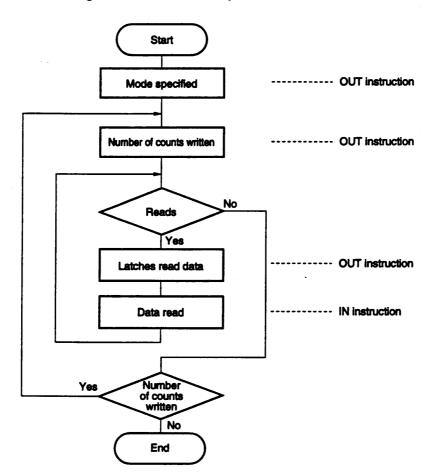

|                 | 5.7.4          | Operating procedures                                  |     |

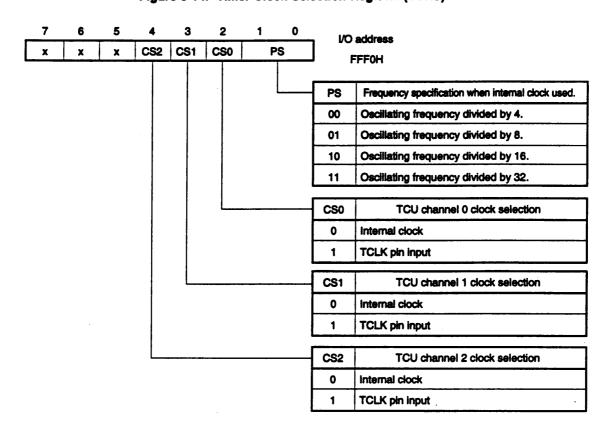

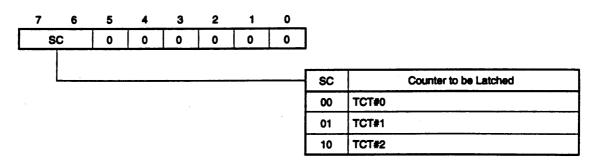

|                 | 5.7.5          | Registers and commands                                |     |

|                 | 5.7.6          | Count mode                                            |     |

|                 | 5.7.7          |                                                       |     |

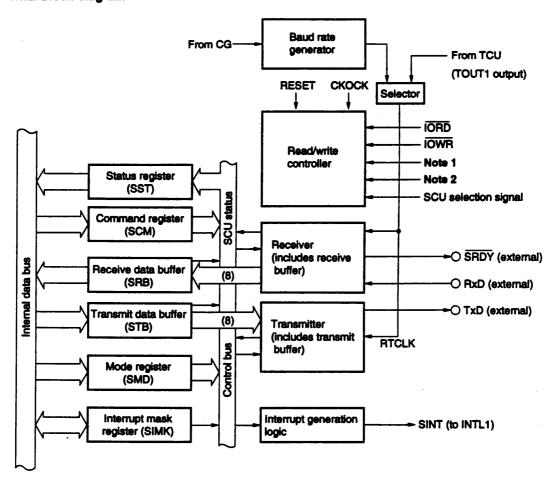

| 5.8             | Serial         | Control Unit (SCU)                                    |     |

|                 | 5.8.1          | Features                                              |     |

|                 | 5.8.2          | Differences with the V40 and V50                      |     |

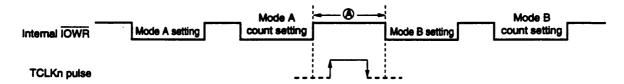

|                 | 5.8.3          | Internal block diagram                                |     |

|                 | 5.8.4          | Addressing                                            |     |

|                 | 5.8.5          | Initialization                                        |     |

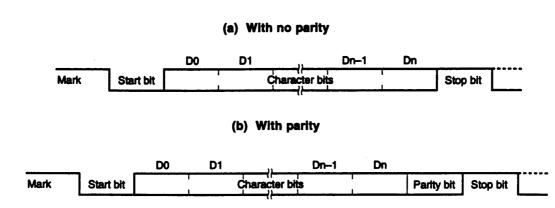

|                 | 5.8.6          | Serial data format                                    |     |

|                 | 5.8.7          | Operating procedures                                  |     |

|                 | 5.8.8          | Registers and commands                                |     |

|                 | 5.8.9          | Transmission and reception baud rates                 |     |

|                 |                | ·                                                     |     |

|                 |                | Serial transmission and reception                     |     |

| 5.9             |                | Precautions                                           |     |

| J. <del>J</del> | 5.9.1          | • • • • • • • • • • • • • • • • • • • •               | 148 |

|                 | 5.9.1<br>5.9.2 | Features                                              |     |

|                 |                | Internal block diagram                                | 148 |

|                 | 5.9.4          | Addressing                                            | 149 |

|                 | 5.9.4<br>5.9.5 |                                                       | 151 |

|                 |                | _                                                     | 152 |

|                 | 5.9.6          | Interrupt sequence                                    | 169 |

| F 40            | 5.9.7          | •                                                     | 178 |

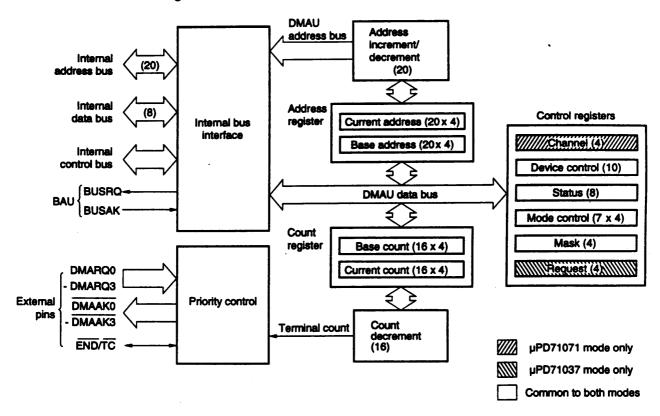

|                 |                | controller Unit (DMAU)                                |     |

| -               |                |                                                       | 179 |

|                 |                |                                                       | 179 |

|                 |                | Internal block diagram                                |     |

|                 |                | Differences between μPD71071 mode and μPD71071        |     |

|                 | 5.10.5         | Differences between μPD71037 mode and μPD71037        | 181 |

|       | 5.10.€   | 5 Differences between the μPD71071 and μPD/1037 modes                 | 181 |

|-------|----------|-----------------------------------------------------------------------|-----|

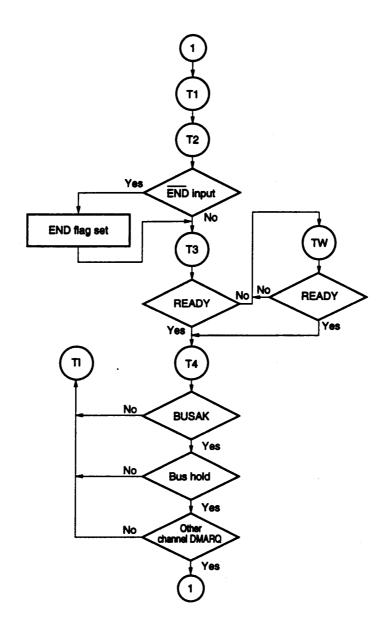

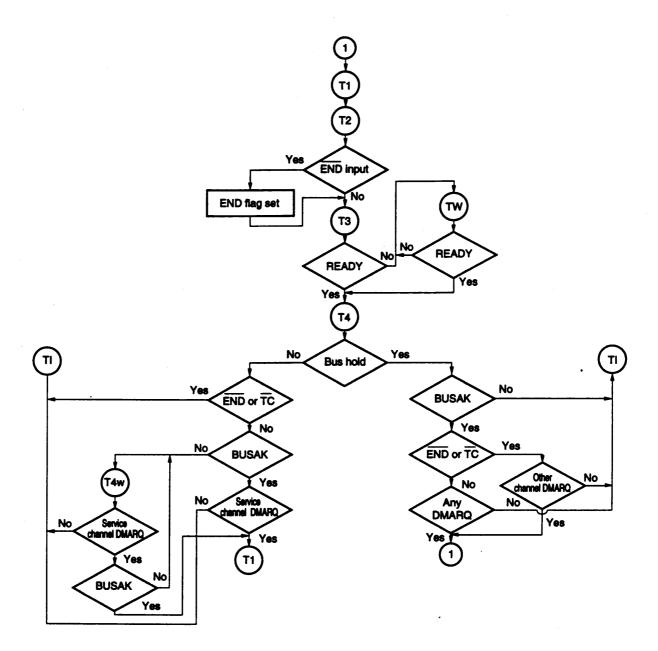

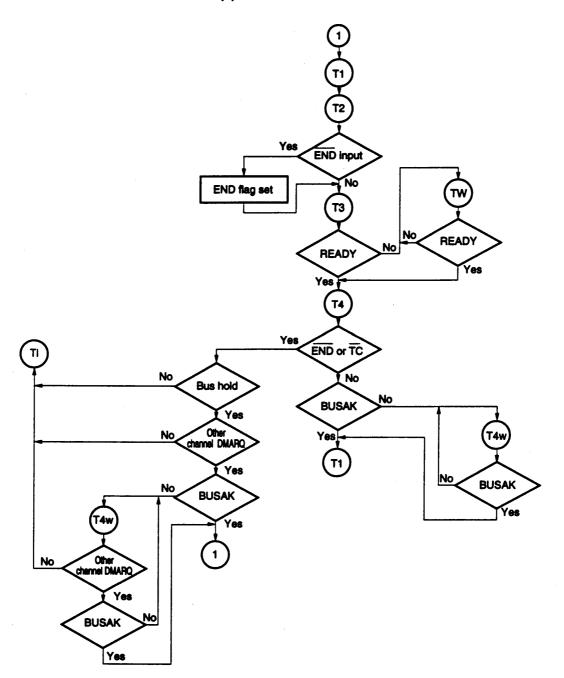

|       | . 5.10.7 | Basic operation of DMAU                                               | 183 |

|       | 5.10.8   | 3 µPD71071 mode                                                       | 188 |

|       | 5.10.9   | μPD71037 mode                                                         | 204 |

|       | 5.10.1   | 0 Transfer mode                                                       | 218 |

|       | 5.10.1   | 1 Auto initialization                                                 | 220 |

|       | 5.10.1   | 2 Cascade connection                                                  | 222 |

|       | 5.10.1   | 3 Status transition diagram                                           | 225 |

|       |          | 4 Precautions                                                         |     |

|       |          |                                                                       |     |

| CHAPT | ER 6     | INTERNAL/EXTERNAL CONTROL FUNCTIONS                                   | 231 |

|       |          | ·                                                                     |     |

| 6.1   | Wait i   | Function                                                              |     |

|       | 6.1.1    | Wait function by using READY pin                                      |     |

|       | 6.1.2    | Wait function by using WCU                                            |     |

|       | 6.1.3    | Relationship between WCU and READY pin                                |     |

| 6.2   | Refre    | sh Function                                                           | 245 |

|       | 6.2.1    | Refresh address                                                       | 245 |

|       | 6.2.2    | Refresh control register (RFC)                                        | 245 |

|       | 6.2.3    | REFU bus control                                                      | 247 |

|       | 6.2.4    | Refresh timing                                                        | 247 |

| 6.3   | Interr   | upt Function                                                          | 250 |

|       | 6.3.1    | Operation of ICU Interrupt                                            | 255 |

|       | 6.3.2    | BRK flag (single-step) interrupt                                      | 262 |

|       | 6.3.3    | Timing when interrupts not acknowledged                               | 262 |

|       | 6.3.4    | Interrupt processing during execution of block processing instruction | 263 |

| 6.4   | Bus H    | lold Function                                                         | 264 |

| 6.5   | Varial   | ble Instruction Cycle Time Function                                   | 266 |

| 6.6   | Stand    | by Function                                                           | 267 |

|       | 6.6.1    | Features                                                              | 267 |

|       | 6.6.2    | Standby control register (SBCR)                                       |     |

|       | 6.6.3    | HALT mode                                                             | 269 |

|       | 6.6.4    |                                                                       |     |

| 6.7   | Reset    | Function                                                              | 275 |

|       | 6.7.1    | CPU reset operation                                                   | 275 |

|       | 6.7.2    | Reset operations of system I/O area and internal peripheral units     |     |

|       | 6.7.3    | Output pin status at reset                                            | 279 |

|       |          |                                                                       |     |

| CHAPT | ER 7     | μPD8080AF EMULATION                                                   | 281 |

|       |          |                                                                       |     |

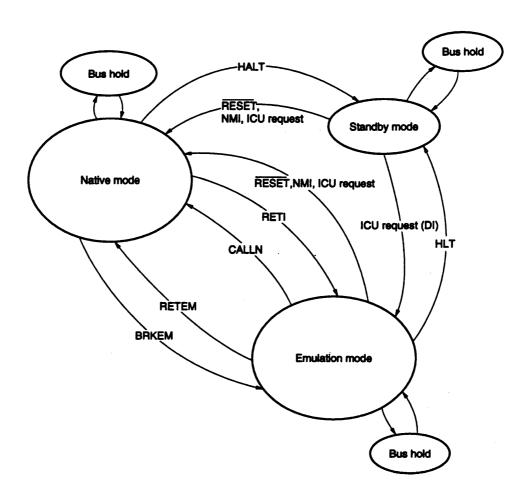

| 7.1   | Chang    | ging from Native Mode to Emulation Mode                               | 281 |

|       | 7.1.1    | BRKEM imm8 instruction                                                | 281 |

|       | 7.1.2    | RETI instruction                                                      | 282 |

| 7.2   | Chang    | ging Mode from Emulation Mode to Native Mode                          | 283 |

|       | 7.2.1    | RESET input                                                           | 283 |

|       | 7.2.2    | NMI and ICU request                                                   | 283 |

|       | 723      | CALLN imm8 instruction                                                | 283 |

|        | 7.2.4 | RETEM instruction                      | 284 |

|--------|-------|----------------------------------------|-----|

|        | 7.2.5 | Nesting of emulation                   | 285 |

| 7.3    | Emula | tion Mode                              | 285 |

|        |       |                                        |     |

| APPENE | DIX A | REGISTER INDEX (IN ALPHABETICAL ORDER) | 289 |

|        |       |                                        |     |

| APPEND | DIX B | GENERAL INDEX                          | 293 |

# LIST OF FIGURES (1/5)

| Figure No. | Title                                         | Page |

|------------|-----------------------------------------------|------|

| 2-1        | Handy Word-Processor Block Diagram            | . 17 |

| 2-2        | Facsimile Machine Block Diagram               | . 18 |

| 3-1        | Pin Input and Output Circuits                 | . 33 |

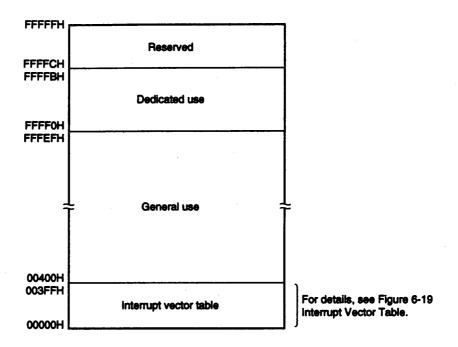

| 4-1        | Memory Map                                    | . 35 |

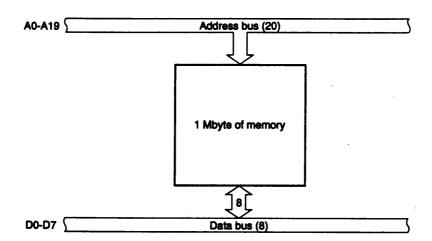

| 4-2        | V40HL Interfacing Between CPU and Memory      | . 36 |

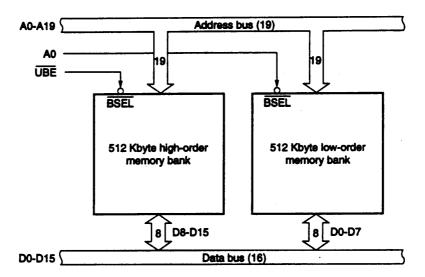

| 4-3        | V50HL Interfacing Between CPU and Memory      | . 37 |

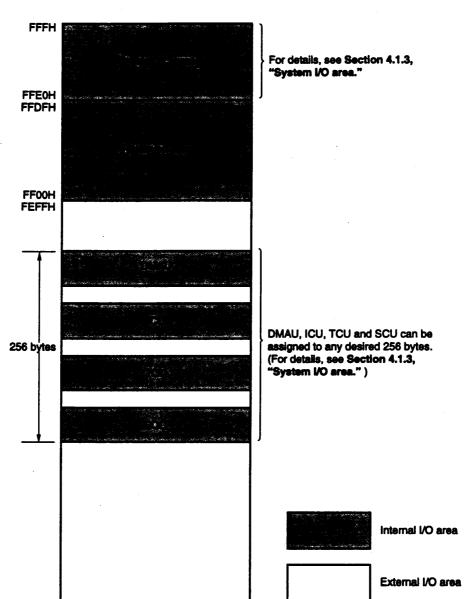

| 4-4        | VO Map                                        | . 39 |

| 4-5        | List of Registers in the System I/O Area      | . 41 |

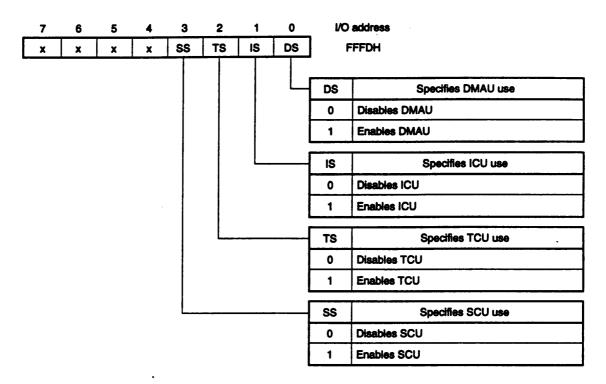

| 4-6        | On-Chip Peripheral Connection Register (OPCN) | 42   |

| 4-7        | On-Chip Peripheral Selection Register (OPSEL) | 43   |

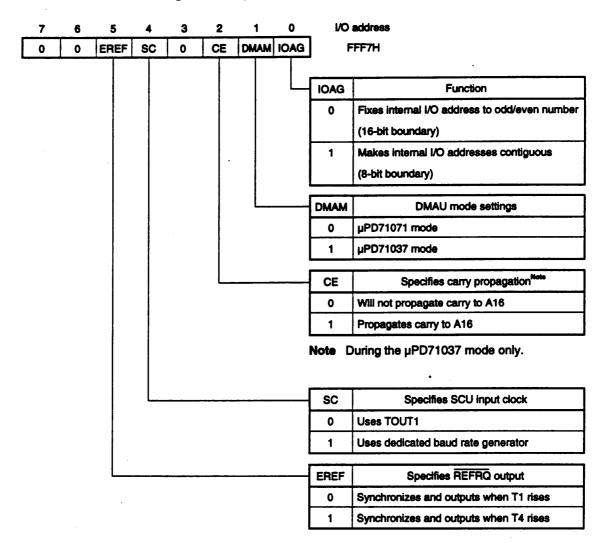

| 4-8        | System Control Register (SCTL)                | . 44 |

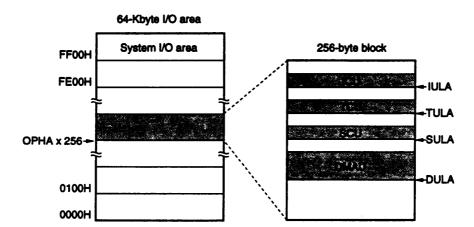

| 4-9        | Internal Peripheral Unit Mapping Example      | 46   |

| 4-10       | On-Chip Peripheral High Address Register      | 47   |

| 4-11       | TCU Low Address Register (TULA)               | 47   |

| 4-12       | SCU Low Address Register (SULA)               | 47   |

| 4-13       | ICU Low Address Register (IULA)               | 48   |

| 4-14       | DMAU Low Address Register (DULA)              | 48   |

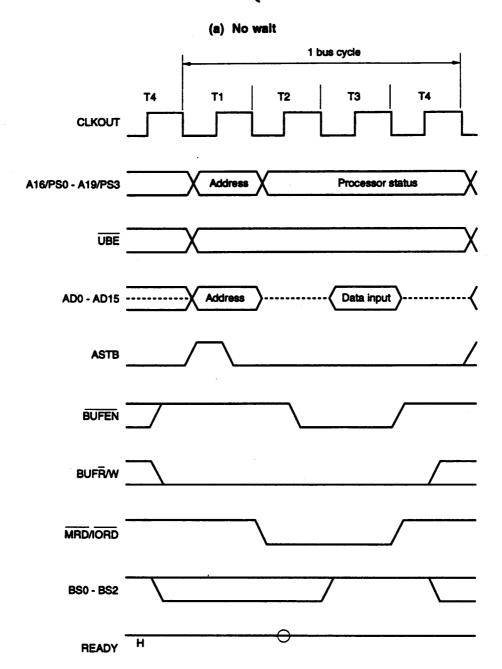

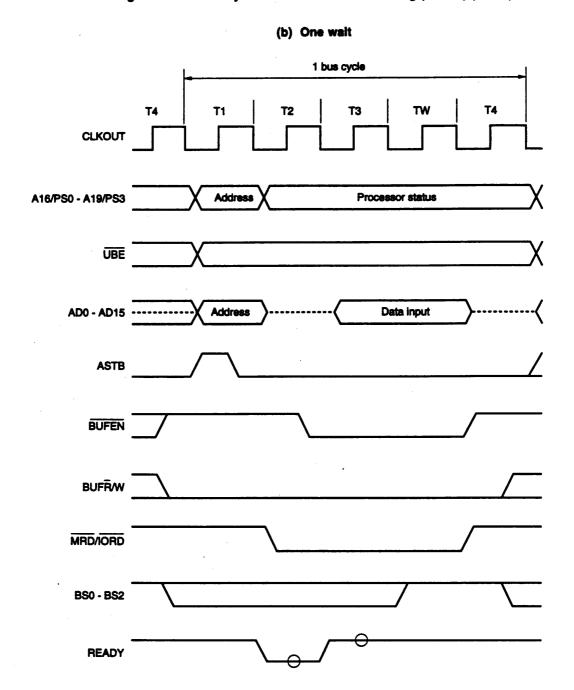

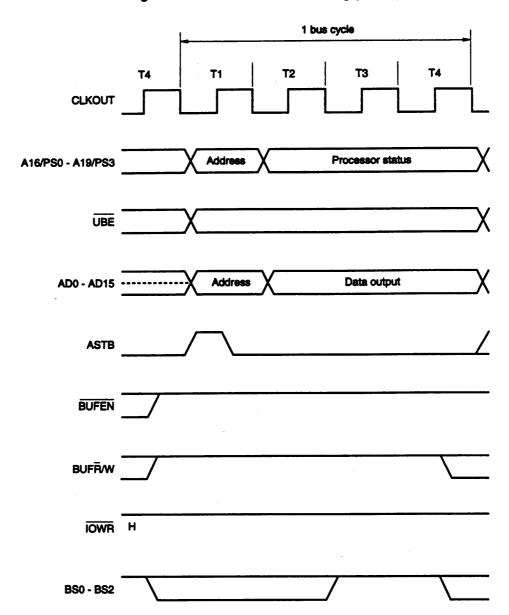

| 4-15       | Memory and External I/O Read Timing (V40HL)   | 50   |

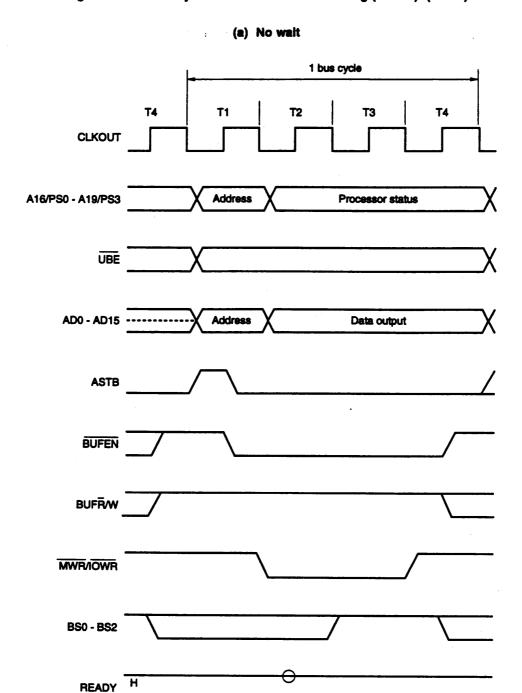

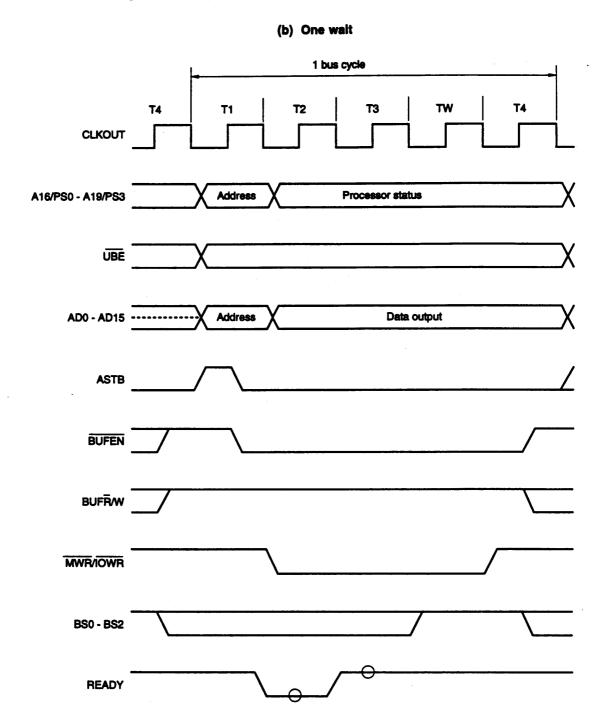

| 4-16       | Memory and External I/O Write Timing (V40HL)  | 52   |

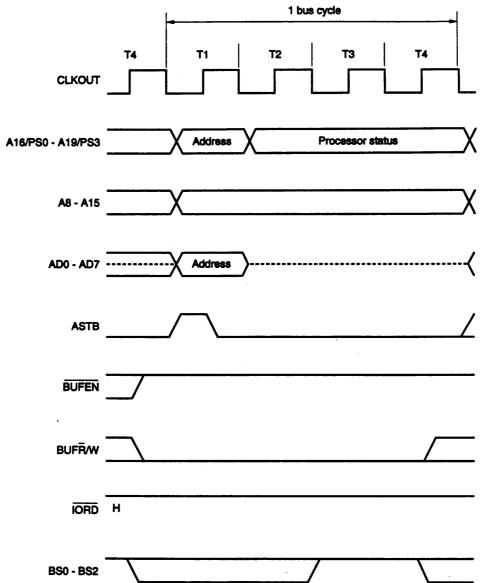

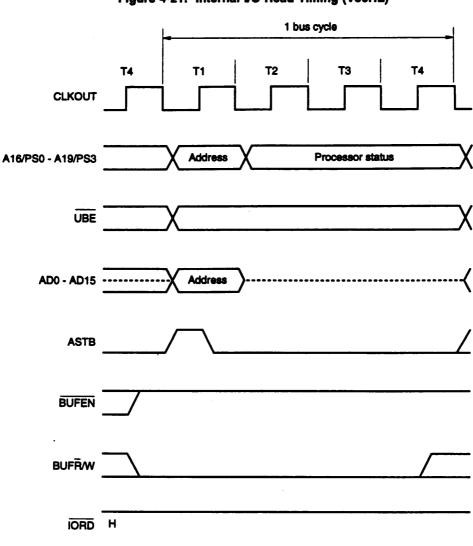

| 4-17       | Internal I/O Read Timing (V40HL)              | 54   |

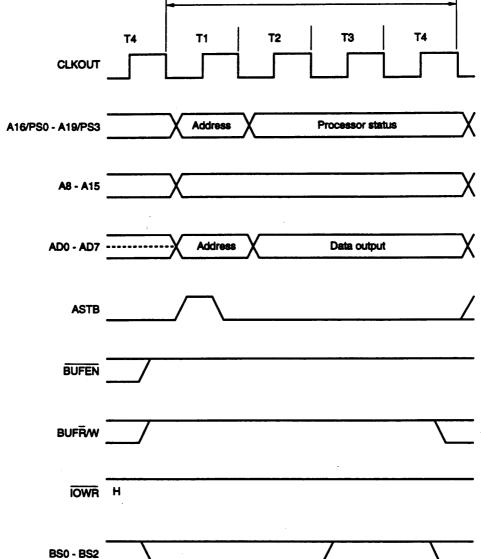

| 4-18       | Internal I/O Write Timing (V40HL)             | 55   |

| 4-19       | Memory and External I/O Read Timing (V50HL)   | 56   |

| 4-20       | Memory and External I/O Write Timing (V50HL)  | 58   |

| 4-21       | Internal I/O Read Timing (V50HL)              | 60   |

| 4-22       | Internal I/O Write Timing (V50HL)             | 61   |

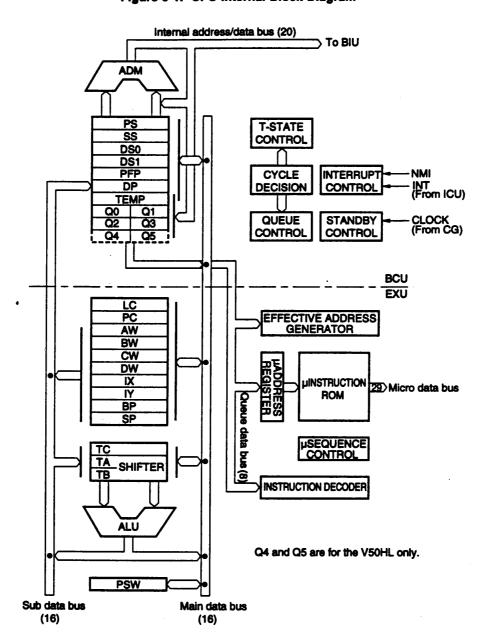

| 5-1        | CPU Internal Block Diagram                    | 76   |

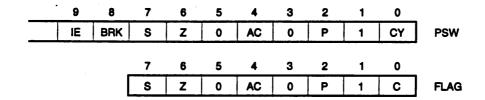

| 5-2        | PSW Bit Fields                                | 81   |

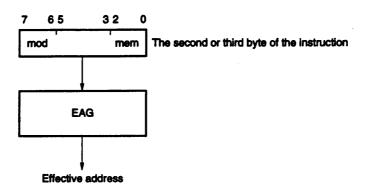

| 5-3        | Effective Address Generation                  |      |

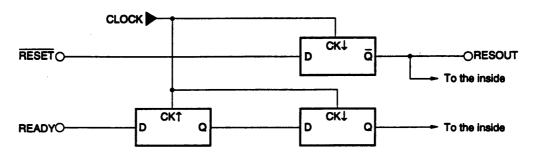

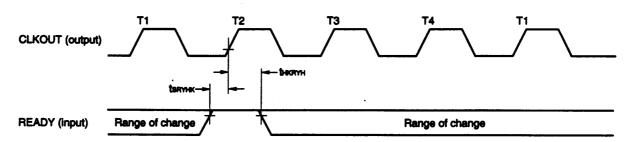

| 5-4        | Synchronizing the RESET and READY Signals     |      |

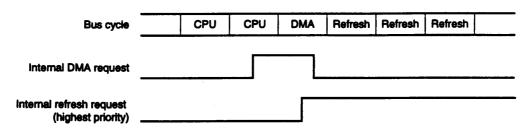

| 5-5        | Internal Bus Cycles                           | 91   |

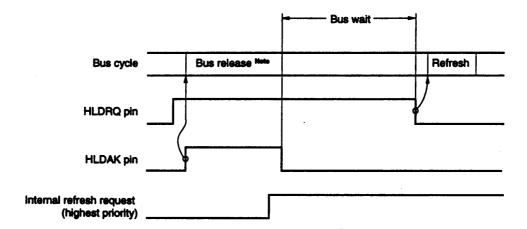

| 5-6        | Bus Waiting Operation                         | 01   |

# LIST OF FIGURES (2/5)

| Figure No. | Title                                                | Page |

|------------|------------------------------------------------------|------|

| 5-7        | Timing of Bus Priority Switching                     | 92   |

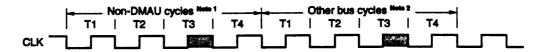

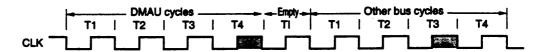

| 5-8        | Timing of Bus Master Switch Transition from Non-DMAU | 93   |

| 5-9        | Timing of Bus Master Switch Transition from DMAU     | 93   |

| 5-10       | Minimum Wait Time                                    | 94   |

| 5-11       | Maximum Wait Time                                    | 95   |

| 5-12       | TCU Basic Operational Procedures                     | 100  |

| 5-13       | TMD (For Mode Word)                                  | 102  |

| 5-14       | Timer Clock Selection Register (TCKS)                | 104  |

| 5-15       | Supply a Clock to the TCU                            | 105  |

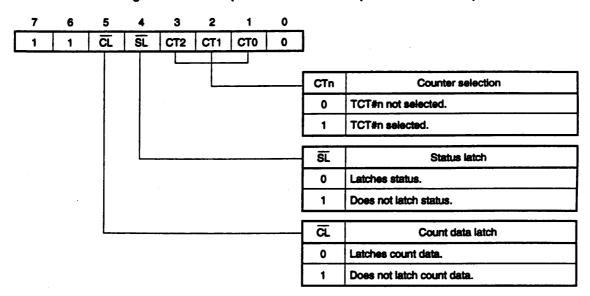

| 5-16       | TMD (When there is a count latch command)            | 107  |

| 5-17       | TMD (When there is a multiple latch command)         | 108  |

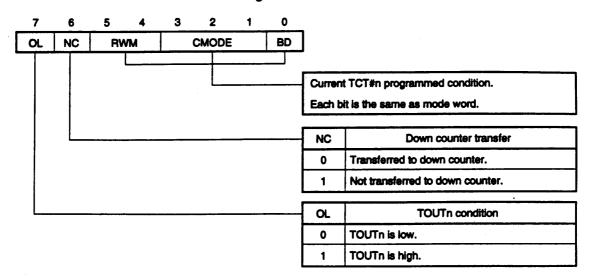

| 5-18       | TSTn                                                 | 109  |

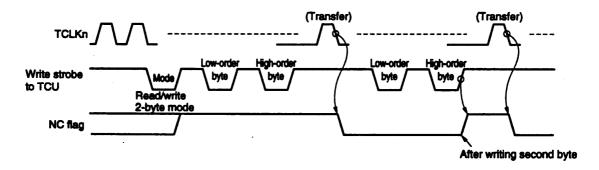

| 5-19       | Example of NC Flag Changes                           | 109  |

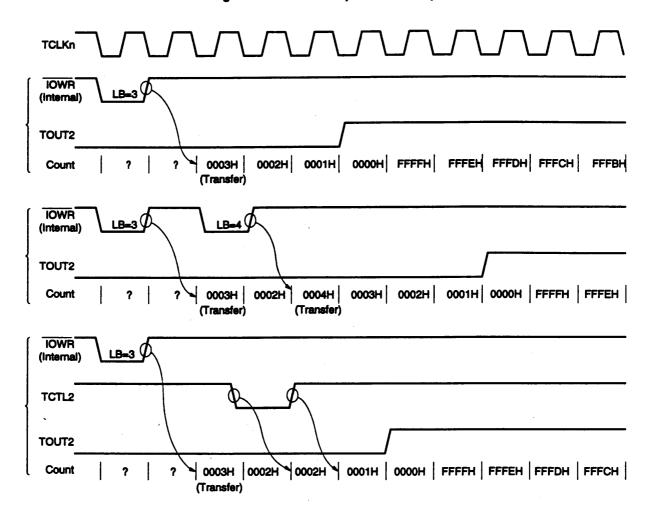

| 5-20       | Multiple Latch Command Execution Example             |      |

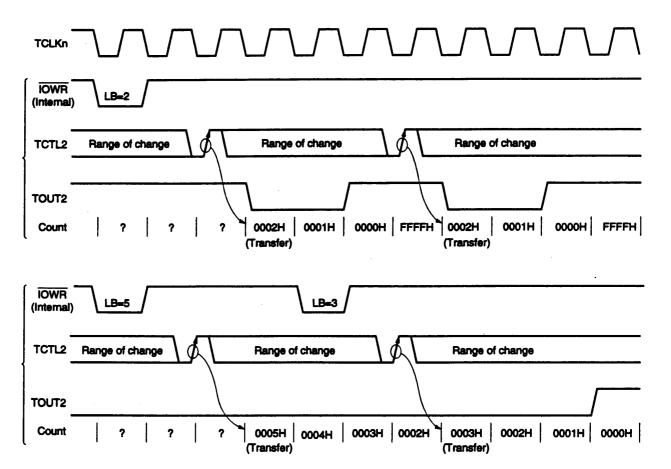

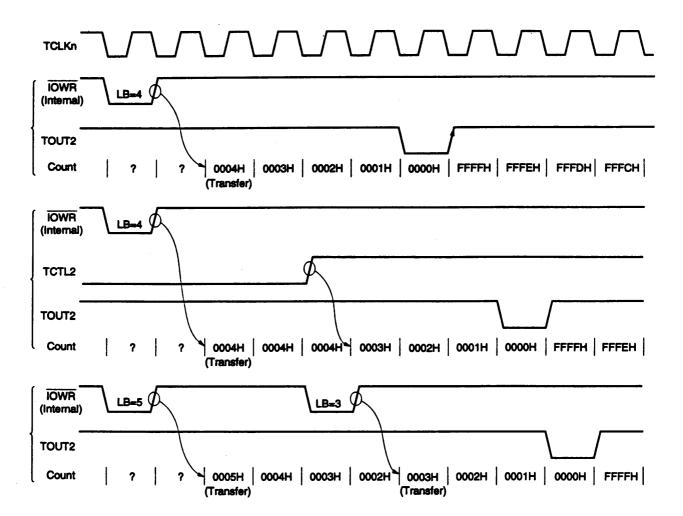

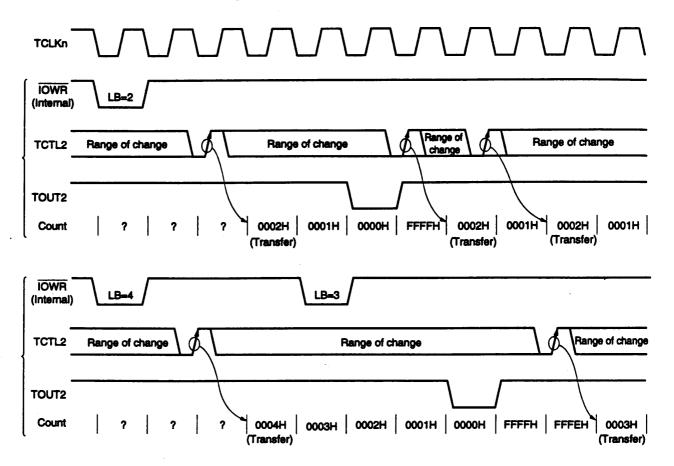

| 5-21       | Mode 0 Operation Example                             | 113  |

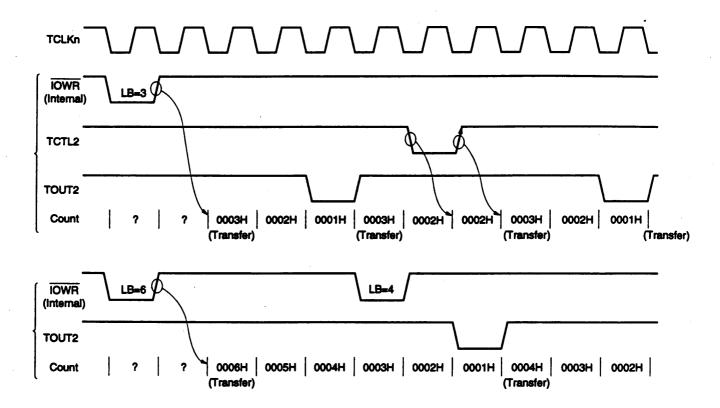

| 5-22       | Mode 1 Operation Example                             |      |

| 5-23       | Mode 2 Operation Example                             | 117  |

| 5-24       | Mode 3 Operation Example                             |      |

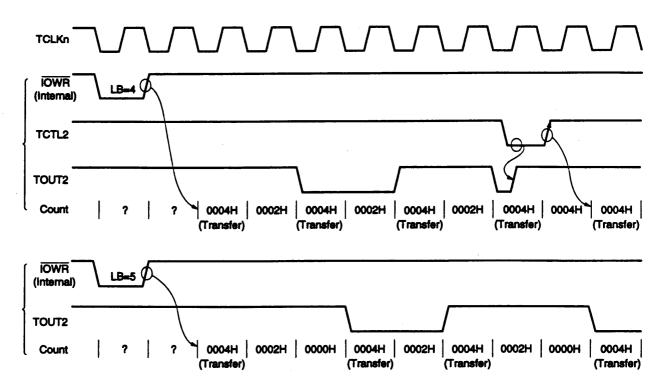

| 5-25       | Mode 4 Operation Example                             |      |

| 5-26       | Mode 5 Operation Example                             |      |

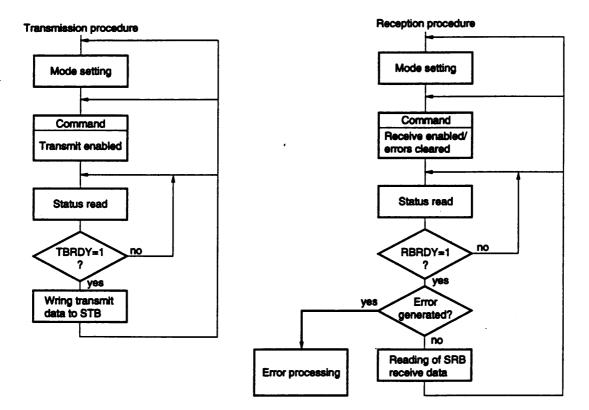

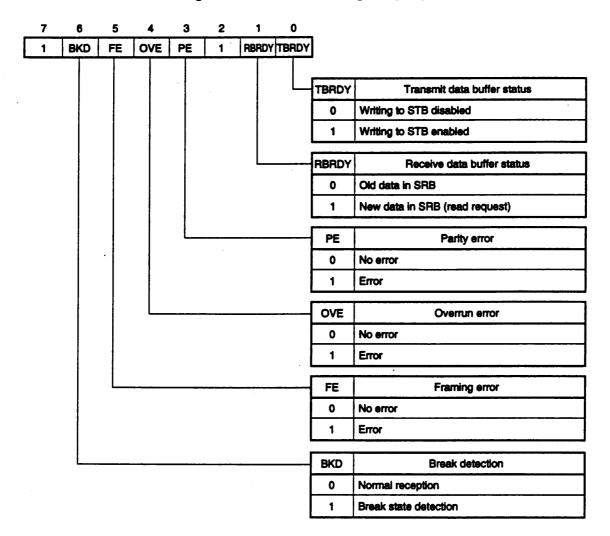

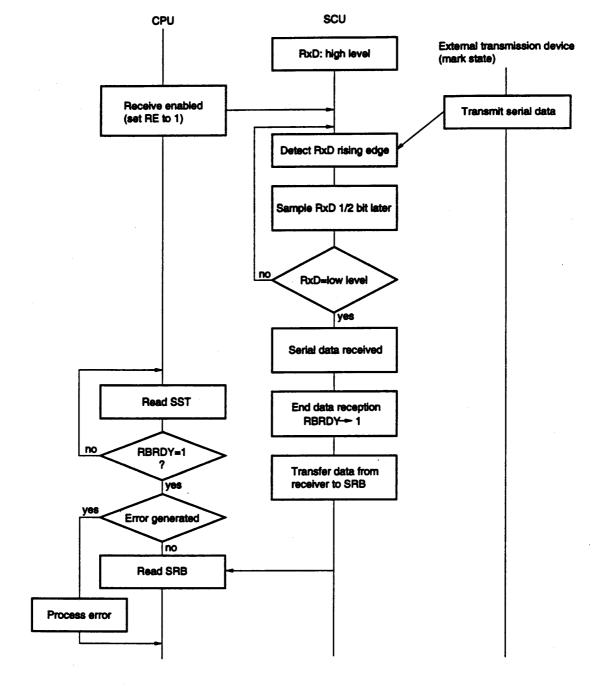

| 5-27       | Serial Data Format                                   |      |

| 5-28       | SCU Operating Procedures                             |      |

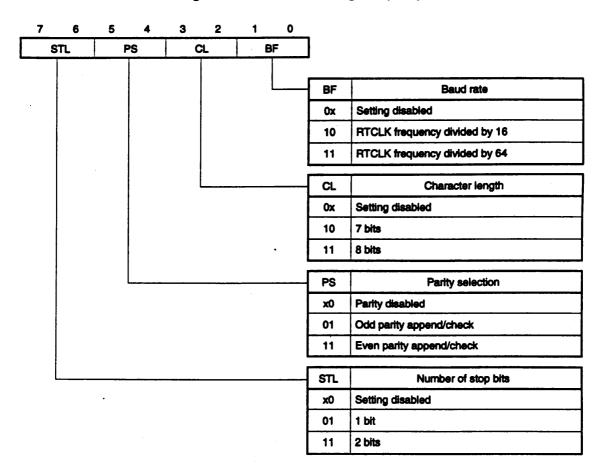

| 5-29       | Serial Mode Register (SMD)                           |      |

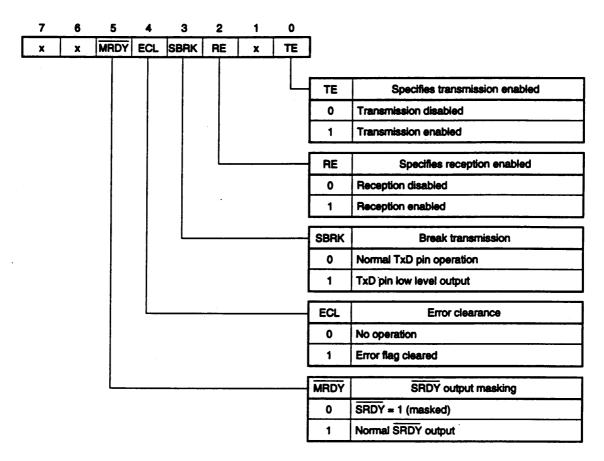

| 5-30       | Serial Command Register (SCM)                        |      |

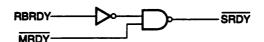

| 5-31       | SRDY Signal                                          |      |

| 5-32       | Serial Status Register (SST)                         |      |

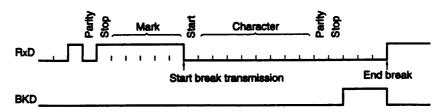

| 5-33       | Break Input and Detection                            |      |

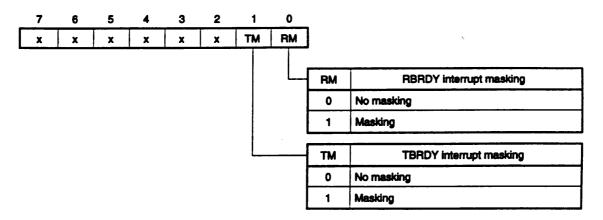

| 5-34       | Serial Interrupt Masking Register (SIMK)             |      |

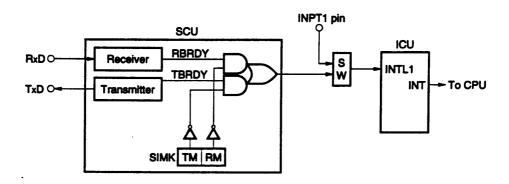

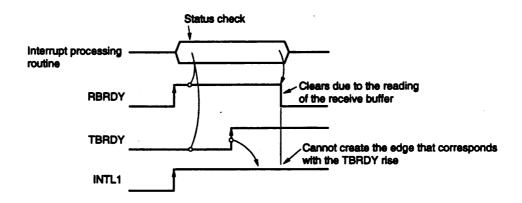

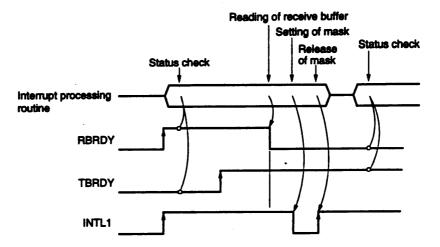

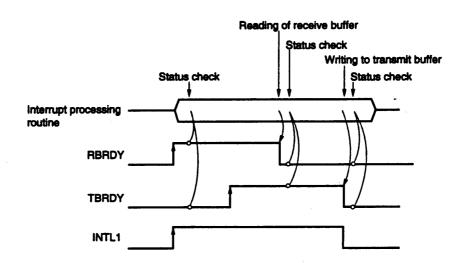

| 5-35       | Relationship Between the TM Bit, RM bit and INTL1    |      |

| 5-36       | Baud Rate Generator (BRC)                            |      |

| 5-37       | Baud Rate Clock Generation Diagram                   |      |

| 5-38       | Serial Transmit Operation                            |      |

| 5-39       | Serial Receive Operation                             |      |

| 5-40       | Initialization Sequence                              |      |

|            |                                                      |      |

# LIST OF FIGURES (3/5)

| Figure No. | Title                                                 | Page |

|------------|-------------------------------------------------------|------|

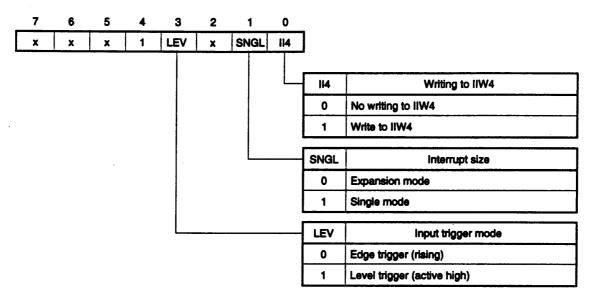

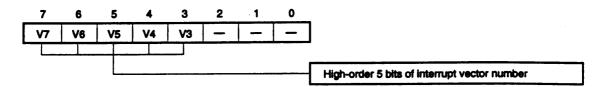

| 5-41       | Interrupt Initialization Word 1 Register (IIW1)       | 152  |

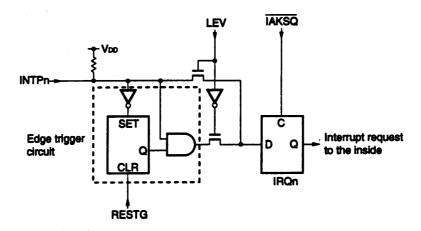

| 5-42       | Interrupt Request Input Circuit                       | 153  |

| 5-43       | Interrupt Initialization Word 2 Register (IIW2)       | 155  |

| 5-44       | Interrupt Vector Number Generation                    | 155  |

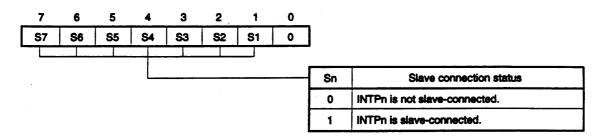

| 5-45       | Interrupt Initialization Word 3 Register (IIW3)       | 156  |

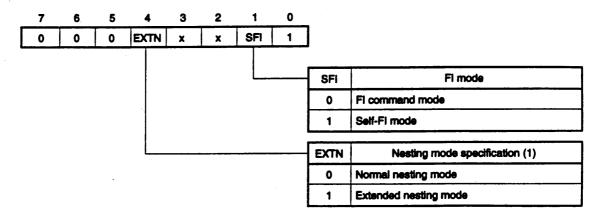

| 5-46       | Interrupt Initialization Word 4 Register (IIW4)       | 157  |

| 5-47       | Normal Nesting Mode                                   | 158  |

| 5-48       | Interrupt Mask Word Register (IMKW)                   | 160  |

| 5-49       | Interrupt Priority, Finish Word Register (IPFW)       | 161  |

| 5-50       | INTL Request Priorities (Rotating Priority)           | 162  |

| 5-51       | Interrupt Mode Word Register (IMDW)                   | 165  |

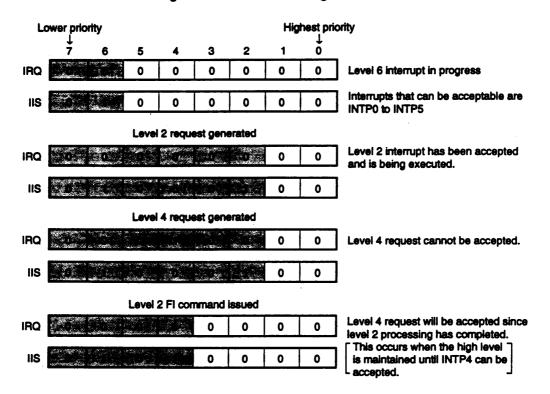

| 5-52       | Examples of the Exception Nesting Mode                | 166  |

| 5-53       | Interrupt Polling Register (IPOL)                     | 167  |

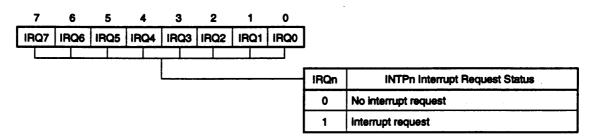

| 5-54       | Interrupt Request Register (IRQ)                      | 167  |

| 5-55       | Interrupt In-Service Register (IIS)                   | 168  |

| 5-56       | Interrupt Sequence                                    | 170  |

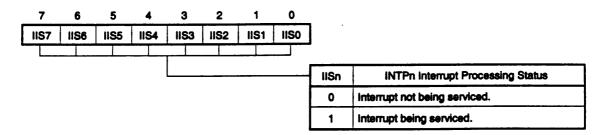

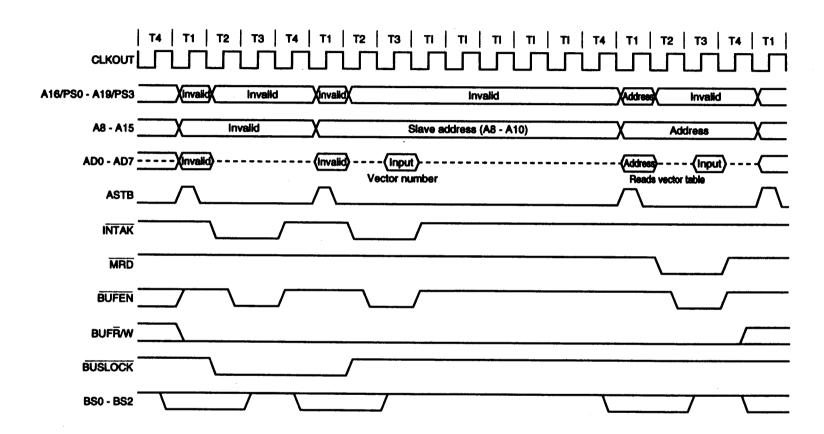

| 5-57       | Interrupt Acknowledge Timing Example (single mode)    | 171  |

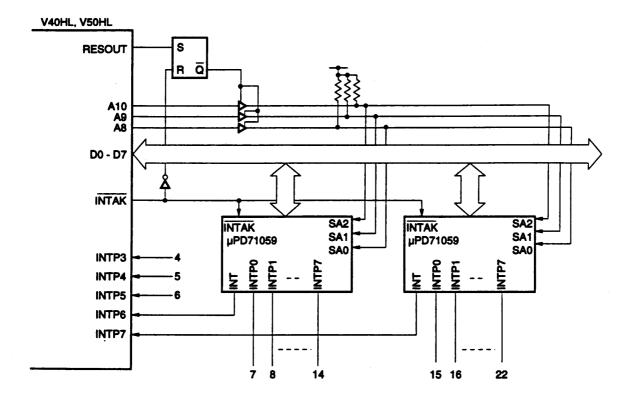

| 5-58       | Example of Connecting Slave in Expansion Mode         | 174  |

| 5-59       | Interrupt Sequence in Expansion Mode                  | 175  |

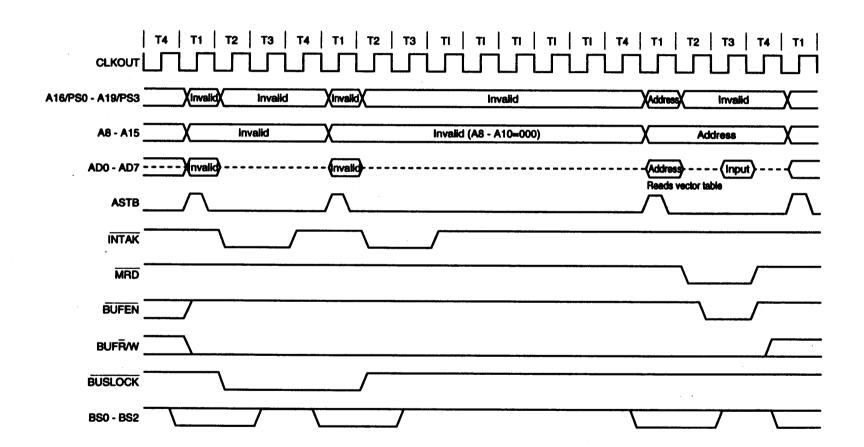

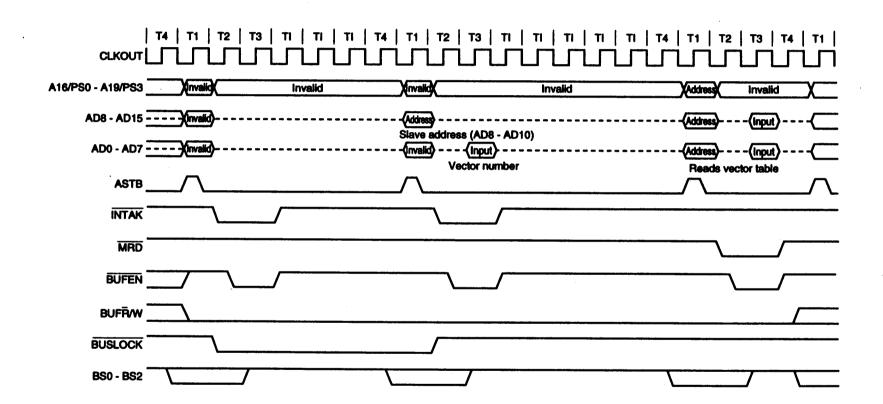

| 5-60       | Interrupt Acknowledge Timing Example (Expansion Mode) | 176  |

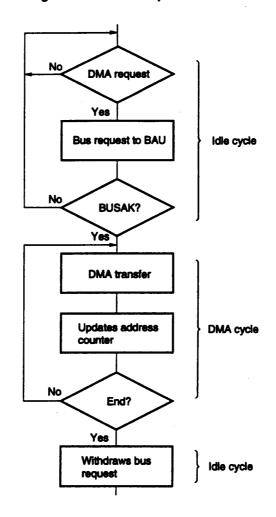

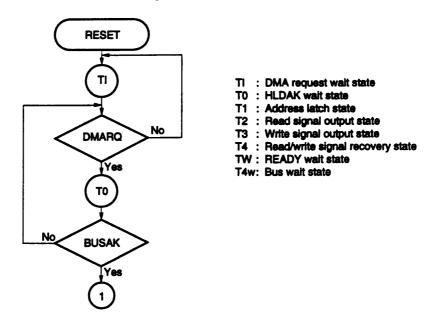

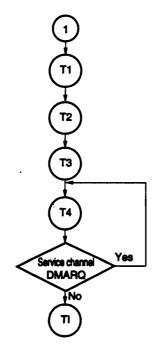

| 5-61       | DMAU Operation Flow                                   | 183  |

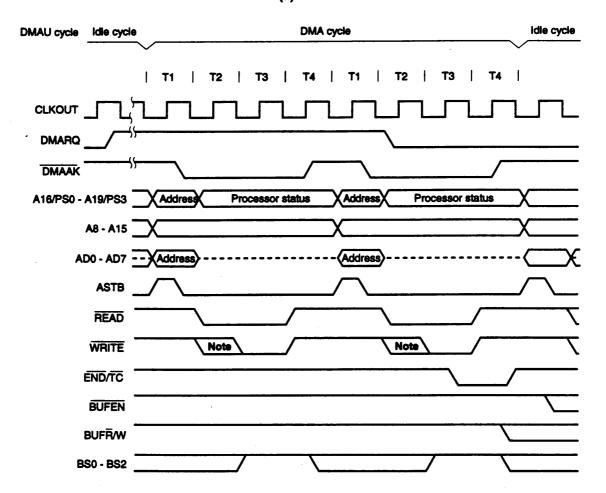

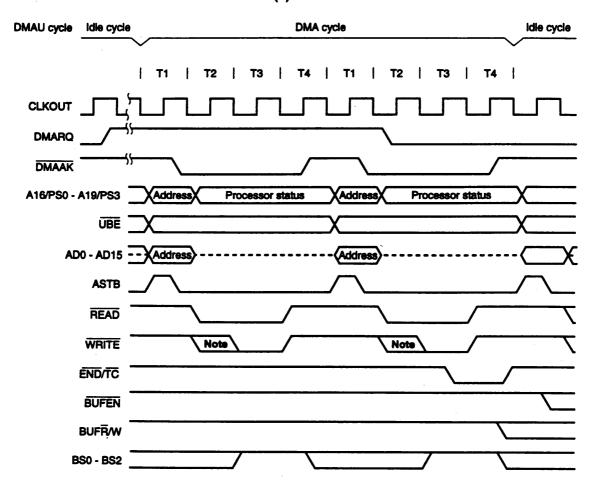

| 5-62       | DMA Timing                                            | 185  |

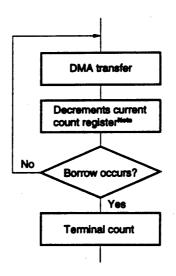

| 5-63       | Occurrence of Terminal Count (TC)                     | 187  |

| 5-64       | DMA Initialize Command Register (DICM)                |      |

| 5-65       | DMA Channel Register Read Command                     | 192  |

| 5-66       | DMA Channel Register Write Command                    |      |

| 5-67       | DMA Count Register Read/Write Command                 | 194  |

| 5-68       | DMA Address Register Read/Write Command               | 195  |

| 5-69       | DMA Device Control Register Read/Write Command        | 196  |

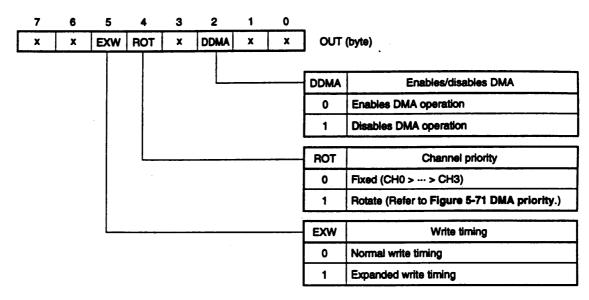

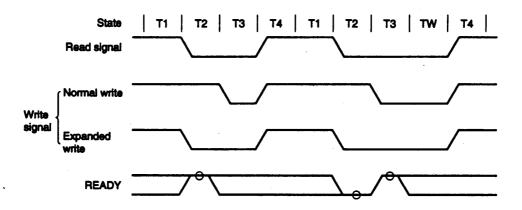

| 5-70       | Expanded Write Timing                                 | 197  |

| 5-71       | DMA Priority                                          |      |

| 5-72       | Difference in Bus Control Depending on Bus Mode       | 198  |

| 5-73       | DMA Mode Control Register Read/Write Command          |      |

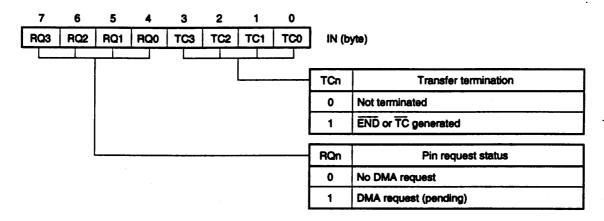

| 5-74       | DMA Status Register Read Command                      | 202  |

# LIST OF FIGURES (4/5)

| Figure No. | Title                                                   | Page  |

|------------|---------------------------------------------------------|-------|

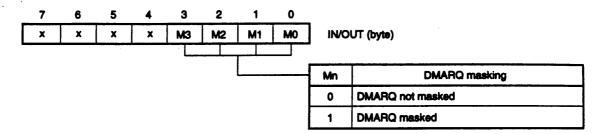

| 5-75       | DMA Mask Register Read/Write Command                    | 203   |

| 5-76       | Read Status Register (DRST)                             | 208   |

| 5-77       | Write Command Register (DWC)                            | 209   |

| 5-78       | Expanded Write Timing                                   | . 209 |

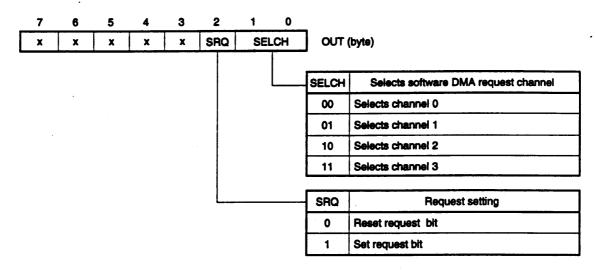

| 5-79       | Write Request Register (DWRQ)                           | . 211 |

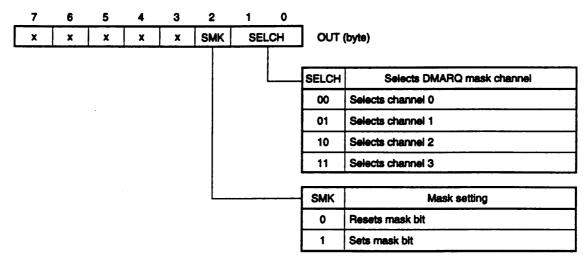

| 5-80       | Write Single Mask Register (DWSM)                       | . 212 |

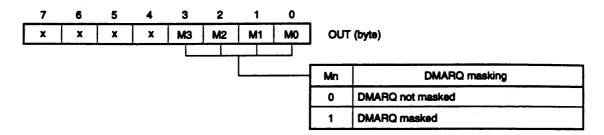

| 5-81       | Write All Mask Register (DWAM)                          | . 213 |

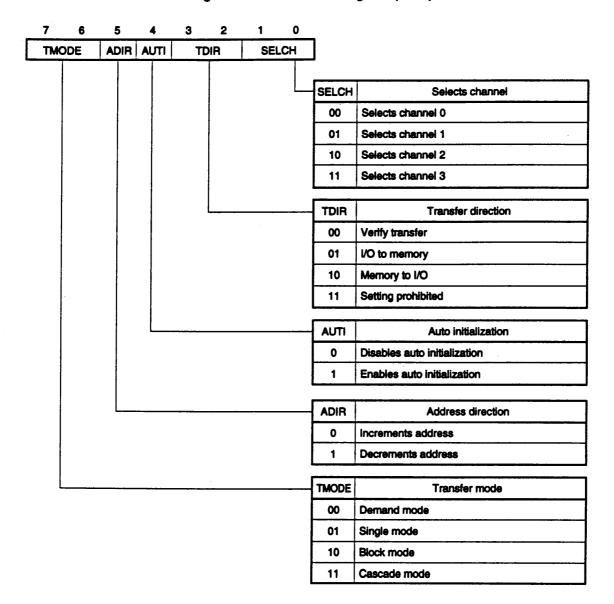

| 5-82       | Write Mode Register (DWM)                               |       |

| 5-83       | Bank Address Register (BADR)                            | . 216 |

| 5-84       | Bank Select Register (BSEL)                             | . 217 |

| 5-85       | Bank Registers (BNKR0 to BNKR3)                         | . 217 |

| 5-86       | Auto Initialization Application Example 1               | 220   |

| 5-87       | Auto Initialization Application Example 2               | . 221 |

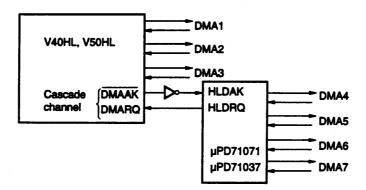

| 5-88       | Example of Cascade Connection                           | 222   |

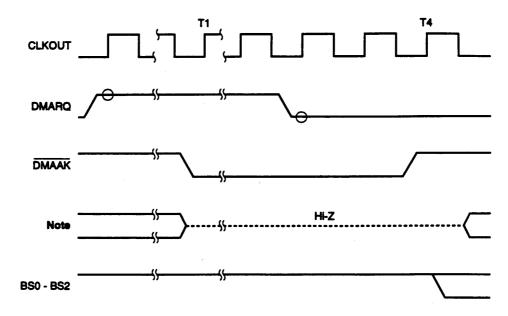

| 5-89       | Example of Cascade Timing                               | 223   |

| 5-90       | Idle Cycle                                              | 225   |

| 5-91       | DMA Cycle                                               | 225   |

| 5-92       | Terminal Count Generation                               | 229   |

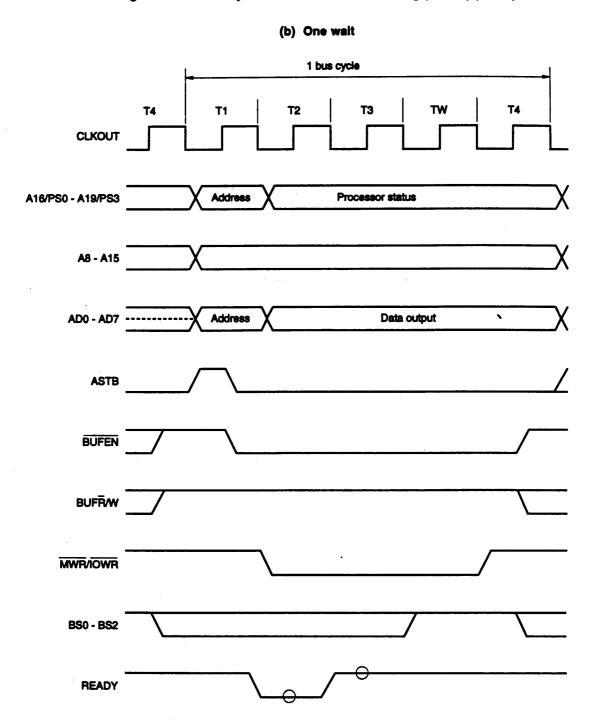

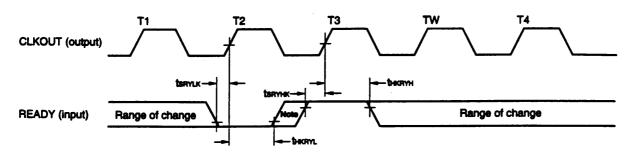

| 6-1        | Ready Timing (no-wait status)                           | 231   |

| 6-2        | Ready Timing (with 1 wait state inserted)               | 232   |

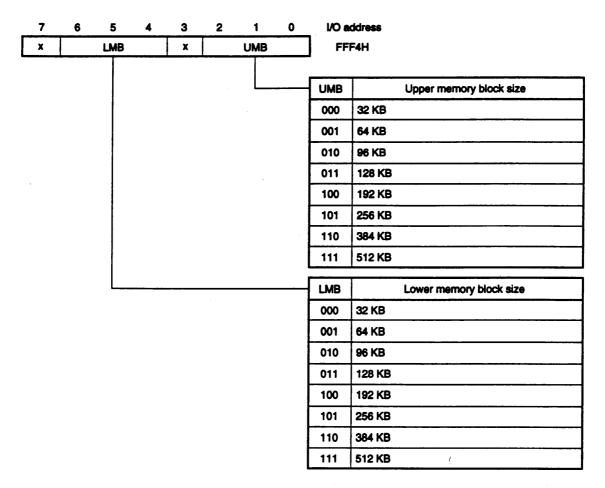

| 6-3        | Programmable Wait Memory Area Setting Register (WMB)    | 234   |

| 6-4        | Dividing Memory Space into Three Blocks                 | 235   |

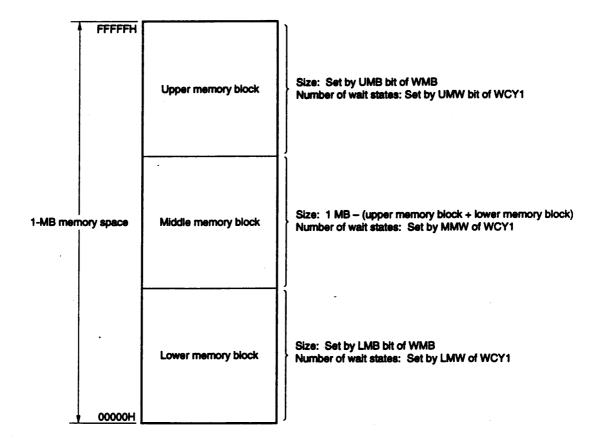

| 6-5        | Extended Wait Block Select Register (EXWB)              | 236   |

| 6-6        | Dividing Memory Space into Five Blocks                  | 237   |

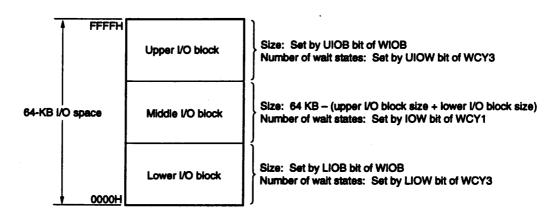

| 6-7        | Dividing I/O Space into Three Blocks                    | 237   |

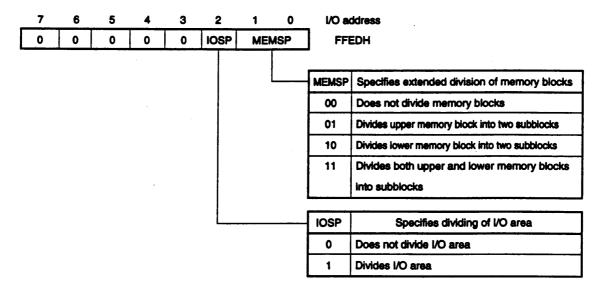

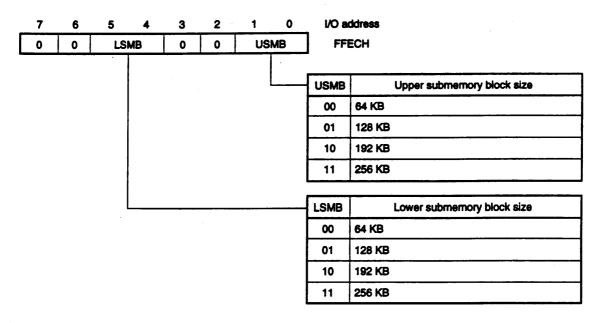

| 6-8        | Wait Submemory Block Setting Register (WSMB)            | 238   |

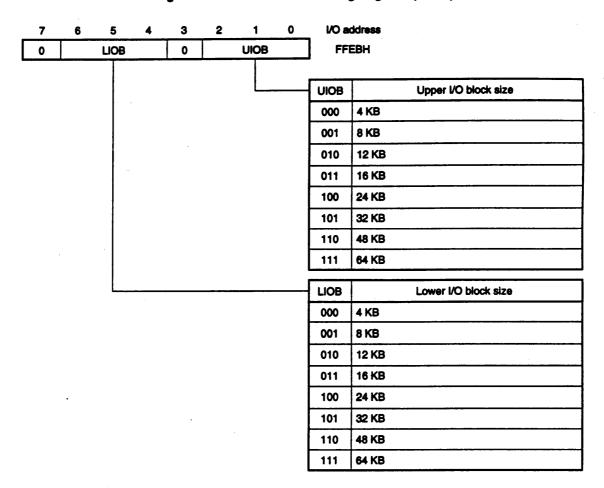

| 6-9        | Wait I/O Block Setting Register (WIOB)                  | 239   |

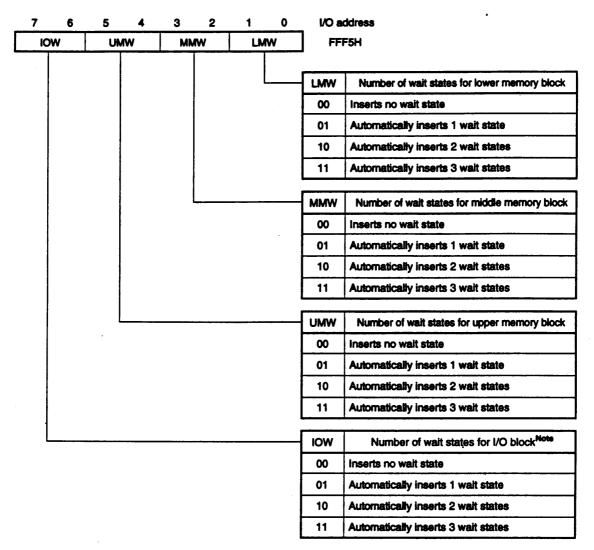

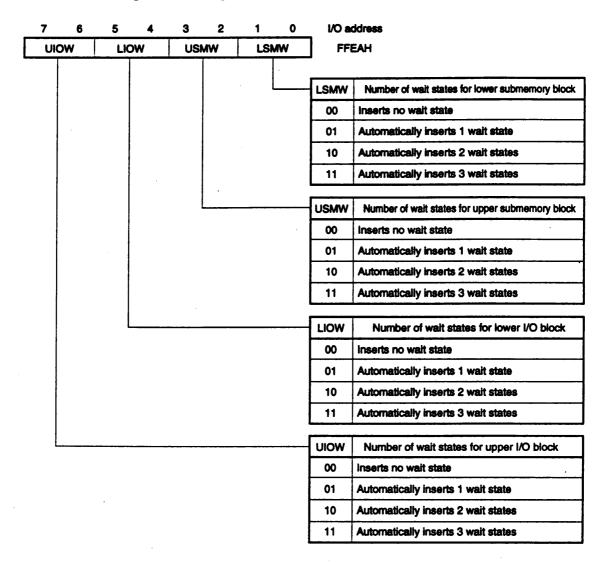

| 6-10       | Programmable Wait Cycle Setting Register 1 (WCY1)       | 240   |

| 6-11       | Programmable Wait Cycle Setting Register 3 (WCY3)       | 241   |

| 6-12       | Programmable Wait Cycle Setting Register 2 (WCY2)       | 242   |

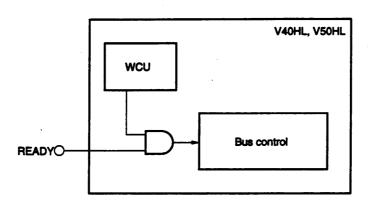

| 6-13       | Relationship between WCU and READY Pin                  | 243   |

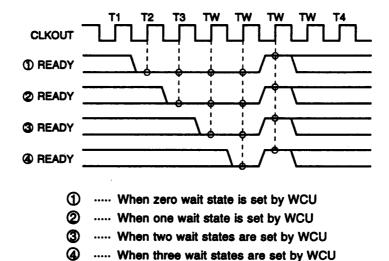

| 6-14       | Example of Bus Timing When 4 Clocks of TWs Are Inserted | 243   |

# LIST OF FIGURES (5/5)

| Figure No. | Title                                                                    | Page |

|------------|--------------------------------------------------------------------------|------|

| <br>6-15   | Refresh Control Register (RFC)                                           | 245  |

| 6-16       | Invalid Refresh Request                                                  |      |

| 6-17       | Refresh Timing                                                           | 248  |

| 6-18       | ICU Inputs                                                               | 250  |

| 6-19       | Interrupt Vector Table                                                   | 253  |

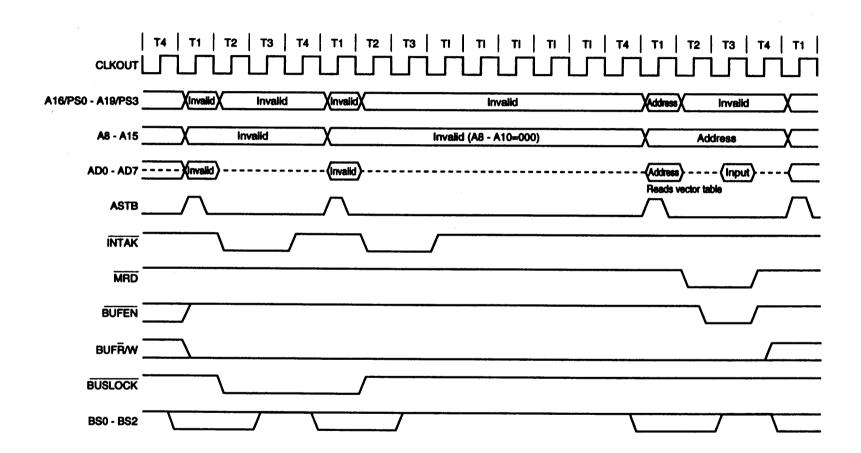

| 6-20       | Example of Interrupt Acknowledge Timing (single mode)                    | 258  |

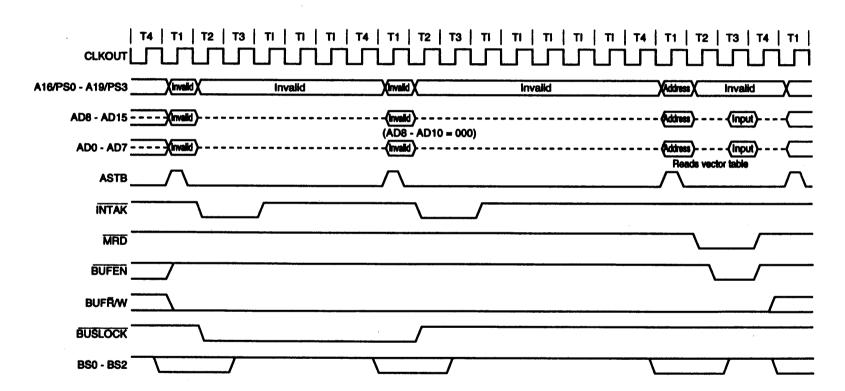

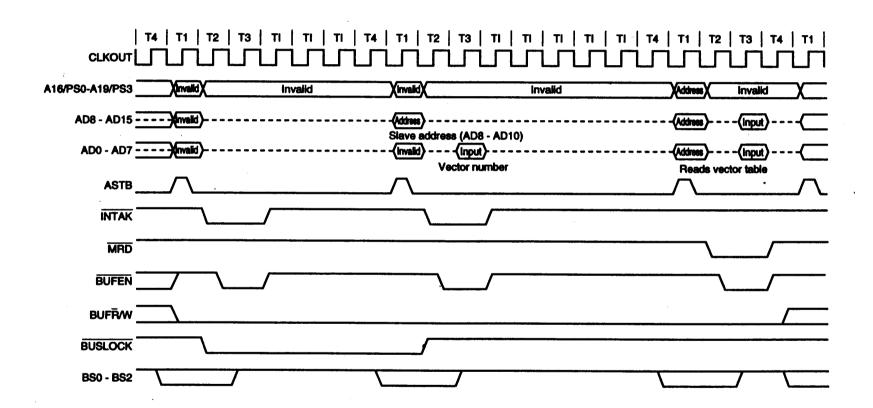

| 6-21       | Example of Interrupt Acknowledge Timing (expanded mode)                  | 260  |

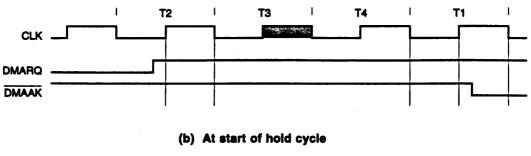

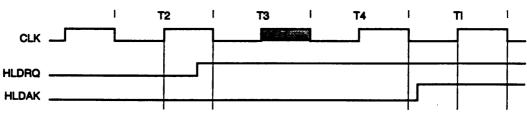

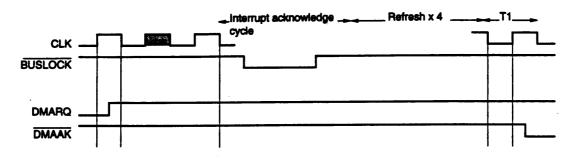

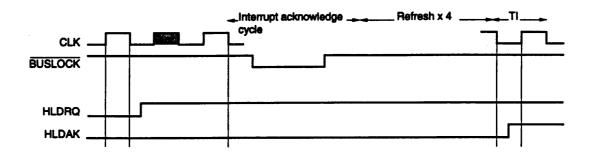

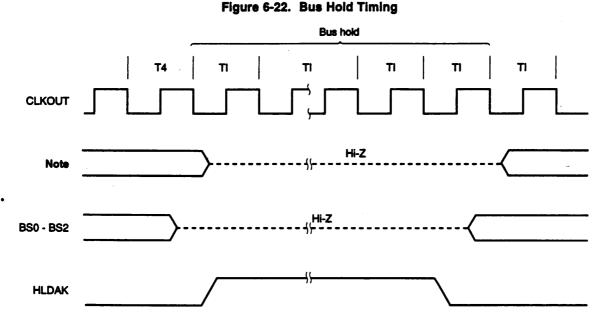

| 6-22       | Bus Hold Timing                                                          | 264  |

| 6-23       | Standby Control Register (SBCR)                                          | 268  |

| 7-1        | Changing Mode by BRKEM Instruction                                       | 281  |

| 7-2        | Changing Mode by RETI Instruction                                        | 282  |

| 7-3        | Changing Mode by NMI Input, ICU Interrupt Request, and CALLN Instruction | 283  |

| 7-4        | Changing Mode by RETEM Instruction                                       | 284  |

| 7-5        | Trouble due to Nesting of Emulation                                      | 285  |

| 7-6        | Correspondence of Register Set                                           | 286  |

| 7-7        | Correspondence of PSW and FLAG                                           | 286  |

| 7-8        | CPU Mode Transition                                                      | 287  |

|            |                                                                          |      |

Phase-out/Discontinued

[MEMO]

# LIST OF TABLES (1/2)

| Table No. | Title                                                                     | Page |

|-----------|---------------------------------------------------------------------------|------|

| 1-1       | Differences Between the V40HL and V50HL and the V40 and V50               | 13   |

| 3-1       | Pin Functions                                                             | 19   |

| 3-2       | Input/Output Circuits for Each Pin and Recommended Handling When Not Used | 31   |

| 4-1       | Memory Element Addresses and Data Organization                            | 36   |

| 4-2       | V50HL Data Access                                                         | 38   |

| 5-1       | Offset and Segment Register Combinations                                  | 78   |

| 5-2       | Bus Masters                                                               | 90   |

| 5-3       | TCU Internal Registers and Command Addresses                              | 99   |

| 5-4       | TCU Registers and Commands Addresses                                      | 101  |

| 5-5       | Writing to the Count Register                                             | 106  |

| 5-6       | Reading the Counter                                                       | 106  |

| 5-7       | NC Flag Changes                                                           | 109  |

| 5-8       | Mode 0 Operation                                                          | 112  |

| 5-9       | Mode 1 Operation                                                          | 114  |

| 5-10      | Mode 2 Operation                                                          | 116  |

| 5-11      | Mode 3 Operation                                                          | 118  |

| 5-12      | Mode 4 Operation                                                          | 120  |

| 5-13      | Mode 5 Operation                                                          | 122  |

| 5-14      | SCU Internal Register and Command Addresses                               | 127  |

| 5-15      | SCU Register and Command Addresses                                        | 131  |

| 5-16      | Baud Rate Settings                                                        | 140  |

| 5-17      | Internal Clock and Maximum Baud Rate                                      | 141  |

| 5-18      | ICU Internal Register and Command Addresses                               | 149  |

| 5-19      | ICU Register and Command Addresses                                        | 150  |

| 5-20      | General Description of the ICU Registers                                  | 152  |

| 5-21      | Differences between μPD71071 Mode and μPD71071                            | 181  |

| 5-22      | Differences between µPD71037 Mode and µPD71037                            | 181  |

| 5-23      | Registers of DMAU (μPD71071 mode)                                         | 188  |

| 5-24      | Addresses of DMAU Internal Registers (µPD71071 mode)                      | 189  |

| 5-25      | DMAU Command Address (μPD71071 mode)                                      | 190  |

| 5-26      | Initializing Registers by Reset                                           | 191  |

# LIST OF TABLES (2/2)

| Table No. | Title                                                              | Page |

|-----------|--------------------------------------------------------------------|------|

| 5-27      | Updating Current Registers                                         | 201  |

| 5-28      | A0 and UBE Signals during DMA Operation                            | 201  |

| 5-29      | Addresses of DMAU's Internal Registers (µPD71037 mode)             | 205  |

| 5-30      | Commands in µPD71037 Mode                                          | 207  |

| 5-31      | Transfer Modes and DMA Service End Conditions                      | 218  |

| 5-32      | DMA Operation for Each Combination of Transfer Mode and Bus Mode   | 219  |

| 5-33      | Pin Status During Cascade Connection                               | 224  |

| 6-1       | Validity of Wait State in Each Bus Cycle                           | 244  |

| 6-2       | REFU Bus Control                                                   | 247  |

| 6-3       | Interrupt Sources                                                  | 252  |

| 6-4       | Pin Status in Hold Status                                          | 265  |

| 6-5       | Relationship between Division Ratio and Internal Clock             | 266  |

| 6-6       | Pin Status in HALT Mode (when peripheral functions do not operate) | 270  |

| 6-7       | Pin Status in STOP Mode (when peripheral functions do not operate) | 273  |

| 6-8       | Resetting CPU                                                      | 275  |

| 6-9       | Resetting System I/O Area                                          | 276  |

| 6-10      | Resetting Internal Peripheral Unit                                 | 278  |

| 6-11      | Pin Status at Reset                                                | 279  |

|           |                                                                    |      |

#### CHAPTER 1 GENERAL DESCRIPTION

The V40HL is a 16/8-bit microprocessor that has a 16-bit architecture, an 8-bit data bus, and internal general-purpose peripheral functions.

The V50HL is a 16-bit microprocessor that has a 16-bit architecture, a 16-bit data bus, and internal general-purpose peripheral functions.

These products are the high-speed, low-power-consumption versions of the V40 and V50 microprocessors, and incorporate the following additional functions and enhanced functions:

- · 20-MHz maximum operating frequency

- Available 3-V power supply voltage

- STOP mode function

- · Available system clock input stop

- A variable instruction cycle function

- Addition of the μPD71037 mode to the DMA controller unit (DMAU)

The V40HL and V50HL are software-compatible with the V40 and V50, allowing the use of current programs without modifications. The V40HL and V50HL are also pin-compatible with the V40 and V50, which allows them to replace the V40 and V50.

The V40HL and V50HL are optimal for the control and data processing of a variety of compact, high-speed, low-voltage-operation and low-power-consumption products, and have applications in the following areas:

- · Personal computers

- · Dedicated word processors

- · Handy terminals

- Printers

- Facsimile machines

- · Robots and numerical machine control

- · Communications control

#### 1.1 Features

The V40HL and V50HL feature the following:

- High-speed and low-power-consumption versions of the V40 and V50

- Operating supply voltage of 3 V or 5 V

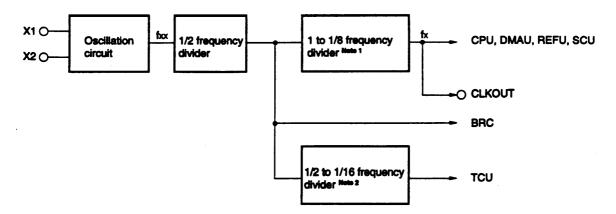

- Maximum operating frequencies of 10, 12.5, 16, and 20 MHz (when externally-supplied frequency is 20, 25, 32, and 40 MHz)

- Use of high-performance 16/8-bit and 16-bit CPUs (equivalent to the V20HL™ and V30HL™)

Minimum instruction execution times

: 100 ns (at 20-MHz, 5-V operation)

200 ns (at 10-MHz, 3-V operation)

• Multiply/divide instruction execution times : 0.95 to 2.8 µs (at 20-MHz, 5-V operation)

1.9 to 5.6 µs (at 10-MHz, 3-V operation)

- Standby functions:

- HALT mode: loo (max.) = 2.2 mA/MHz (at 5-V operation) and 1.5 mA/MHz (at 3-V operation)

- STOP mode: lob (max.) = 50  $\mu$ A (at 5-V operation) and 30  $\mu$ A (at 3-V operation)

- External system clock input stop

- When stopping external clock input: loo (max.) = 50  $\mu$ A (at 5-V operation) and 30  $\mu$ A (at 3-V operation)

- External clock frequency can be varied from the DC level to the maximum operating frequency.

- Variable instruction cycle function

- General-purpose peripheral functions:

- Clock generator (CG)

- Bus interface unit (BIU)

- Bus arbitration unit (BAU)

- Wait control unit (WCU)

- Refresh control unit (REFU)

- Timer/counter unit (TCU)

- Serial control unit (SCU)

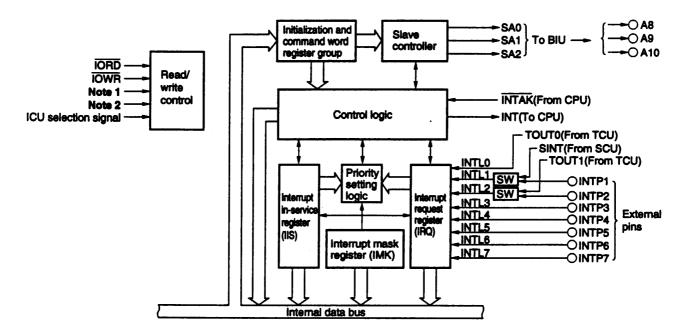

- Interrupt control unit (ICU)

- DMA control unit (DMAU)

## 1.2 Ordering Information

## (1) V40HL

| Part Number        | Package Type                                                         | Maximum operating frequency (MHz) |

|--------------------|----------------------------------------------------------------------|-----------------------------------|

| μPD70208HGF-10-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 10                                |

| μPD70208HGF-12-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 12.5                              |

| μPD70208HGF-16-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 16                                |

| μPD70208HGF-20-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 20                                |

| μPD70208HGK-10-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 10                                |

| μPD70208HGK-12-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 12.5                              |

| μPD70208HGK-16-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 16                                |

| μPD70208HGK-20-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 20                                |

| μPD70208HLP-10     | 68-pin plastic QFJ (950 x 950 mils)                                  | 10                                |

| μPD70208HLP-12     | 68-pin plastic QFJ (950 x 950 mils)                                  | 12.5                              |

| μPD70208HLP-16     | 68-pin plastic QFJ (950 x 950 mils)                                  | 16                                |

| μPD70208HLP-20     | 68-pin plastic QFJ (950 x 950 mils)                                  | 20                                |

Remark Plastic QFJ is the new name for the PLCC.

# (2) V50HL

| Part Number        | Package Type                                                         | Maximum operating frequency (MHz) |

|--------------------|----------------------------------------------------------------------|-----------------------------------|

| μPD70216HGF-10-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 10                                |

| μPD70216HGF-12-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 12.5                              |

| μPD70216HGF-16-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 16                                |

| μPD70216HGF-20-3B9 | 80-pin plastic QFP (14 x 20 mm) (2.7-mm resin thickness)             | 20                                |

| μPD70216HGK-10-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 10                                |

| μPD70216HGK-12-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 12.5                              |

| μPD70216HGK-16-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 16                                |

| μPD70216HGK-20-9EU | 80-pin plastic TQFP (fine pitch) (12 x 12 mm) (1-mm resin thickness) | 20                                |

| μPD70216HLP-10     | 68-pin plastic QFJ (950 x 950 mils)                                  | 10                                |

| μPD70216HLP-12     | 68-pin plastic QFJ (950 x 950 mils)                                  | 12.5                              |

| μPD70216HLP-16     | 68-pin plastic QFJ (950 x 950 mils)                                  | 16                                |

| μPD70216HLP-20     | 68-pin plastic QFJ (950 x 950 mils)                                  | 20                                |

Remark Plastic QFJ is the new name for the PLCC.

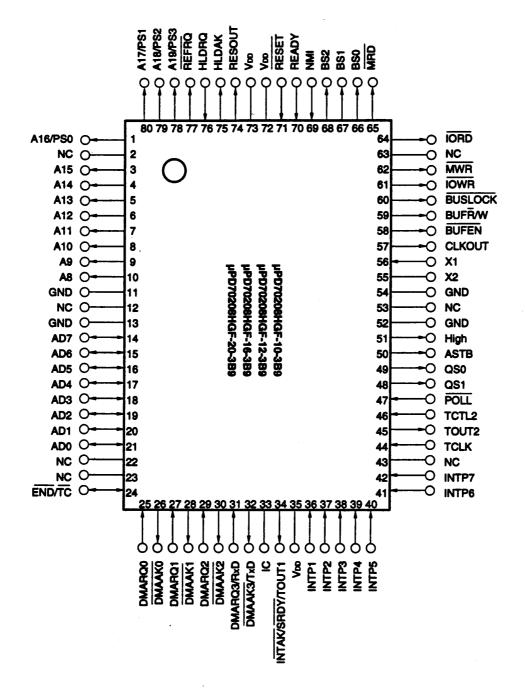

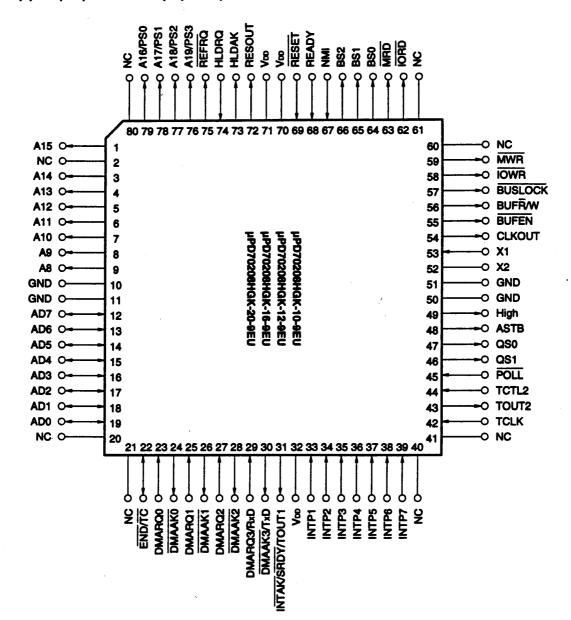

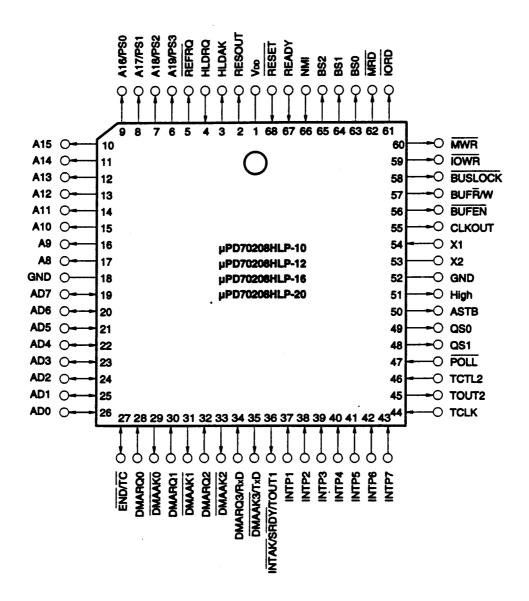

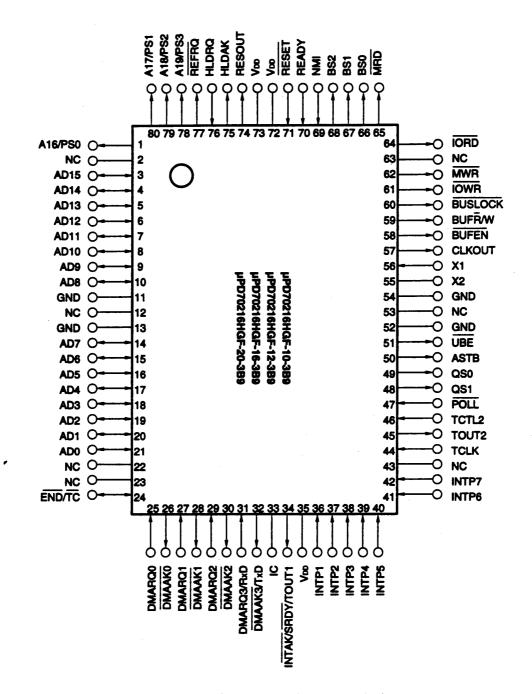

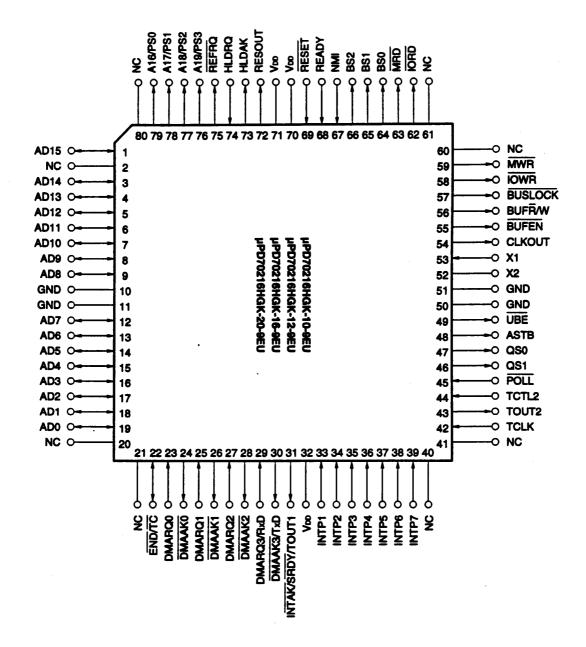

#### 1.3 Pin Configurations

## (1) V40HL

#### (a) 80-pin plastic QFP (Top View)

Caution Connect nothing to the IC pin.

#### (b) 80-pin plastic TQFP (Top View)

#### (c) 68-pin plastic QFJ (Top View)

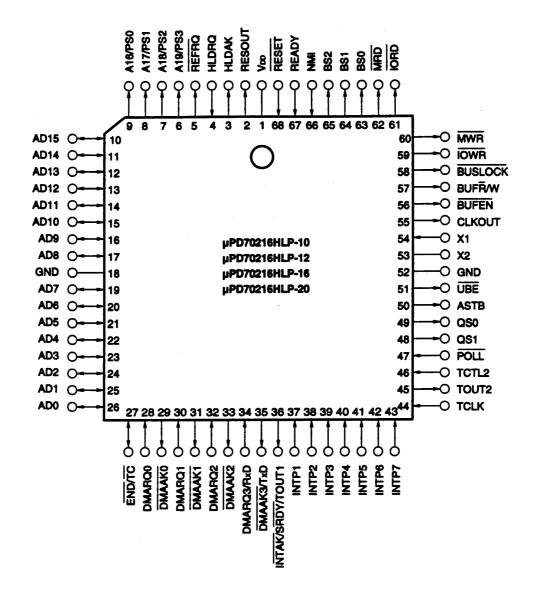

#### (2) V50HL

#### (a) 80-pin plastic QFP (Top View)

Caution Connect nothing to the IC pin.

#### (b) 80-pin plastic TQFP (Top View)

#### (c) 68-pin plastic QFJ (Top View)

#### Pin Identification

AD0 to AD15:

Address Bus/Data Bus

A8 to A15:

Address Bus

A16/PS0 to A19/PS3:

Address/Processor Status

REFRQ:

Refresh Request

HLDRQ:

Hold Request

HLDAK:

Hold Acknowledge

RESET:

Reset

**RESOUT:**

**Reset Output**

**READY:**

Ready

NMI:

Non-Maskable Interrupt Request

MRD:

Memory Read

MWR:

**Memory Write**

IORD:

I/O Read I/O Write

ASTB:

Address Strobe

UBE:

Upper Byte Enable

High:

High Level Output

**BUSLOCK:**

Bus Lock

POLL:

Poll

BUFR/W:

**Buffer Read/Write**

**BUFEN**:

**Buffer Enable**

X1, X2:

Crystal

CLKOUT:

**Clock Output**

BS0 to BS2:

Bus Status

QS0, QS1:

Queue Status

TOUT2:

Timer Output 2

TCTL2:

**Timer Control 2**

TCLK:

**Timer Clock**

INTP1 to INTP7:

Interrupt Request from Peripherals

INTAK/SRDY/TOUT1:

Interrupt Acknowledge/Serial Ready/Timer Output 1

DMAAK3/TxD:

DMA Acknowledge/Transmit Data

DMARQ3/RxD:

DMA Request/Receive Data

DMAAK0 to DMAAK2:

DMA Acknowledge

DMARQ0 to DMARQ2:

DMA Request

END/TC:

**End/Terminal Count**

VDD:

**Power Supply**

GND:

Ground

Internally Connected

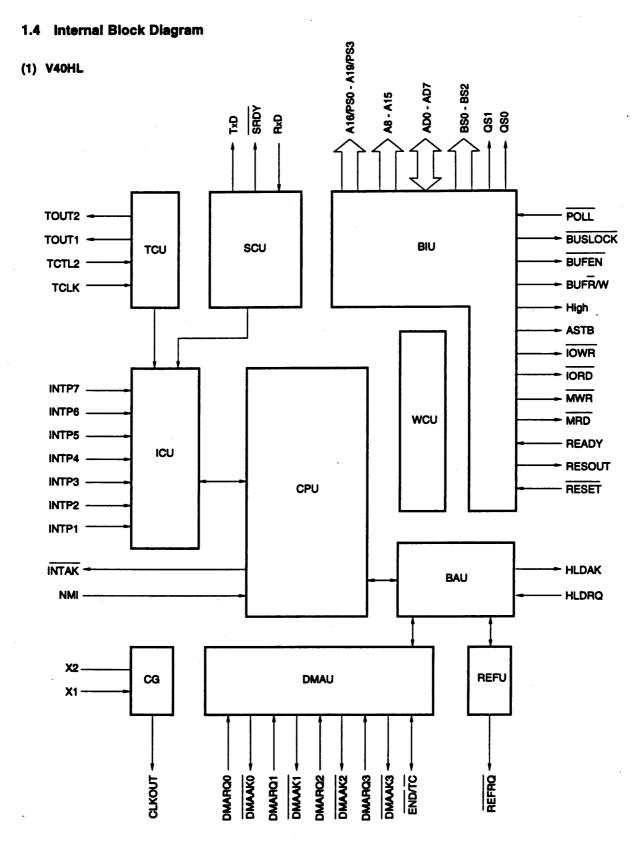

CPU: Central processing unit

CG : Clock generator

BIU : Bus interface unit

BAU : Bus arbitration unit

WCU: Wait control unit

REFU: Refresh control unit

TCU: Timer/counter unit

SCU: Serial control unit

ICU: Interrupt control unit

DMAU: DMA control unit

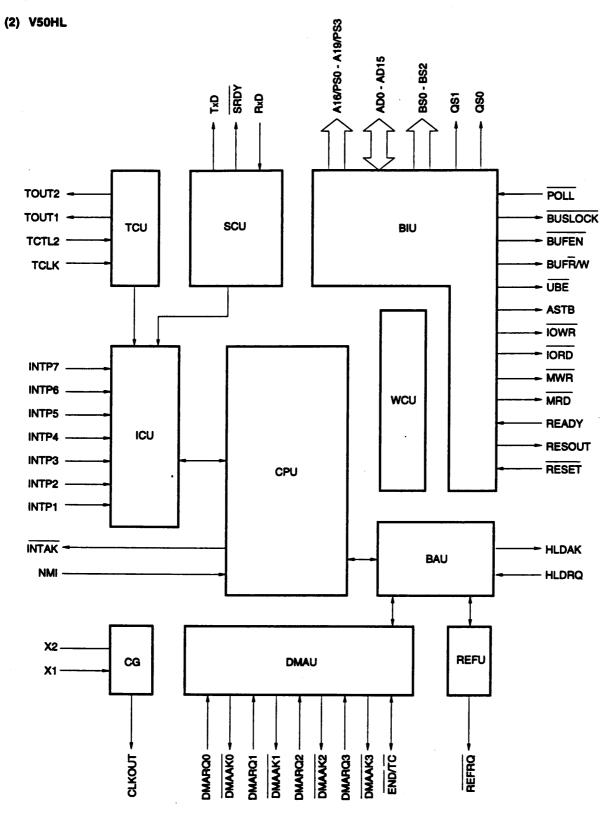

CPU: Central processing unit

CG: Clock generator

BIU: Bus interface unit

BAU: Bus arbitration unit

WCU: Wait control unit

REFU: Refresh control unit

TCU: Timer/counter unit

SCU: Serial control unit

ICU: Interrupt control unit

DMAU: DMA control unit

#### 1.5 Differences Between the V40HL and V50HL and the V40 and V50

The major differences between the V40HL and V50HL and the V40 and V50 are shown below in Table 1-1.

Table 1-1. Differences Between the V40HL and V50HL and the V40 and V50

| Item Operating supply voltages  |             | V40HL, V50HL                                                 | V40, V50                                                                                    |

|---------------------------------|-------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                 |             | 3 V, 5 V                                                     | 5 V                                                                                         |

| Operating frequencies           | V00 = 5 V   | MAX.: 10, 12.5, 16, 20 MHz<br>MIN.: DC                       | MAX.: 8, 10 MHz<br>MIN. : 2 MHz                                                             |

|                                 | Vpo = 3 V   | MAX.: 5, 6.25, 8, 10 MHz<br>MIN.: DC                         | No operation                                                                                |

| Clock generators (CG)           |             | Variable frequency division ratio                            | Fixed frequency division ratio                                                              |

|                                 |             | Variable instruction cycle times                             | Fixed instruction cycle time                                                                |

|                                 |             | 40-MHz maximum input frequency                               | 20-MHz maximum input frequency                                                              |

| Internal I/O remapping function |             | I/O boundary can be remapped to an 8-bit or 16-bit boundary. | The V40 can be remapped to an 8-bit boundary. The V50 can be remapped to a 16-bit boundary. |

| Wait control unit (WCU)         |             | Memory area: 5 segments Note 1                               | Memory area: 3 segments                                                                     |

|                                 |             | I/O area: 3 segments <sup>Note 2</sup>                       | I/O area: No segments                                                                       |

| Refresh control unit (REFU)     |             | 16-bit refresh address                                       | 9-bit refresh address                                                                       |

|                                 |             | Supports REFRQ expansion timing.                             | No REFRQ expansion timing                                                                   |

| Serial control                  | unit (SCU)  | On-chip dedicated baud rate generator                        | No on-chip dedicated baud rate generator                                                    |

| DMA control                     | unit (DMAU) | μPD71071 or μPD71037 subset (either function is available)   | μPD71071 subset                                                                             |

| Standby func                    | tions       | HALT and STOP modes                                          | HALT mode only                                                                              |

Notes 1. Divides into three partitions after reset.

2. No division into partitions.

# 1.6 Functional Overview

| Part Number                                 |           | V40HL                                                                                                                                                                                                                                             | V50HL            |  |

|---------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| Item                                        |           |                                                                                                                                                                                                                                                   |                  |  |

| CPU                                         |           | V20HL equivalent                                                                                                                                                                                                                                  | V30HL equivalent |  |

| Internal data bus width                     | -         | 16 bits                                                                                                                                                                                                                                           |                  |  |

| External data bus widt                      |           | 8 bits                                                                                                                                                                                                                                            | 16 bits          |  |

| Operating ambient temperature               |           | -40 to +85 °C                                                                                                                                                                                                                                     |                  |  |

| Operating supply voltages                   |           | Voo = 5 V ±10 %<br>Voo = 3 V ±10 %                                                                                                                                                                                                                |                  |  |

| Maximum operating frequencies               | VDD = 5 V | 10, 12.5, 16, 20 MHz<br>(when externally-supplied frequency is 20, 25, 32, and 40 MHz)                                                                                                                                                            |                  |  |

|                                             | V00 = 3 V | 5, 6.25, 8, 10 MHz<br>(when externally supplied frequency is 10, 12.5, 16, and 20 MHz)                                                                                                                                                            |                  |  |

| Minimum instruction execution times         | V00 = 5 V | 200, 160, 125, 100 ns<br>(when maximum operating frequencies are at 10, 12.5, 16, and 20 MHz)                                                                                                                                                     |                  |  |

|                                             | Vpc = 3 V | 400, 320, 250, 200 ns<br>(when maximum operating frequencies are 5, 6.25, 8, and 10 MHz)                                                                                                                                                          |                  |  |

| Multiply/divide instruction execution times | V00 = 5 V | 1.9 to 5.6, 1.5 to 4.5, 1.2 to 3.5, 0.95 to 2.8 μs<br>(when maximum operating frequencies are 10, 12.5, 16, and 20 MHz)                                                                                                                           |                  |  |

|                                             | V00 = 3 V | 3.8 to 11.2, 3.0 to 9.0, 2.4 to 7.0, 1.9 to 5.6 μs<br>(when maximum operating frequencies are 5, 6.25, 8, and 10 MHz)                                                                                                                             |                  |  |

| Memory space                                |           | 1 MB (512 Kwords)                                                                                                                                                                                                                                 |                  |  |

| I/O area                                    |           | 64 KB (32 Kwords)                                                                                                                                                                                                                                 |                  |  |

| Number of instructions                      |           | 101                                                                                                                                                                                                                                               |                  |  |

| Number of registers                         |           | 12                                                                                                                                                                                                                                                |                  |  |

| Clock generator (CG)                        |           | Variable instruction cycle time function (Variable frequency division ratios of oscillator: 1/2, 1/4, 1/8, or 1/16-divide)     40-MHz Maximum input frequency                                                                                     |                  |  |

| Wait control unit (WCU)                     |           | <ul> <li>Memory space can be divided into five partitions. I/O space can be divided into three partitions.</li> <li>From zero to three waits can be inserted to the following cycles:</li> <li>CPU cycle, DMA cycle, and refresh cycle</li> </ul> |                  |  |

| Refresh control unit (REFU)                 |           | Lowest priority refresh/highest priority refresh     7 refresh queues     16-bit refresh address     Supports REFRQ expansion timing (REFRQ becomes active from the T1 state)                                                                     |                  |  |

| Timer/counter unit (TCU)                    |           | μPD71054 equivalent                                                                                                                                                                                                                               |                  |  |

| Serial control unit (SCU)                   |           | <ul> <li>μPD71051 (asynchronous) equivalent</li> <li>On-chip dedicated baud rate generator</li> </ul>                                                                                                                                             |                  |  |

#### CHAPTER 1 GENERAL DESCRIPTION

(continued)

| Item                                    | Part Number | V40HL                                                                                                                                                                             | V50HL |

|-----------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Interrupt control unit (ICU)            |             | <ul> <li>μPD71059 equivalent (vector mode only)</li> <li>μPD71059 can be cascade-connected.</li> </ul>                                                                            |       |

| DMA control unit (DMAU)                 |             | <ul> <li>Two operating modes: μPD71071 and μPD71037 modes</li> <li>20-bit address bus</li> <li>Four DMA channels</li> </ul>                                                       |       |

| Interrupt functions                     |             | 7 external interrupts; 3 internal interrupts                                                                                                                                      |       |

| Standby functions V <sub>DD</sub> = 5 V |             | • HALT mode: loo (MAX.) = 2.2 mA/MHz<br>• STOP mode: loo (MAX.) = 50 µA                                                                                                           |       |

| •                                       | V00 = 3 V   | • HALT mode: loo (MAX.) = 1.5 mA/MHz<br>• STOP mode: loo (MAX.) = 30 µA                                                                                                           |       |

| Packages                                |             | <ul> <li>80-pin plastic QFP (14 x 20-mm body; 2.7-mm resin thickness)</li> <li>80-pin plastic TQFP (12 x 12-mm body; 1-mm resin thickness)</li> <li>68-pin plastic QFJ</li> </ul> |       |

| Miscellaneous                           |             | Internal bus interface unit (BIU)     Internal bus arbitration unit (BAU)                                                                                                         |       |

Phase-out/Discontinued

# [MEMO]

#### **CHAPTER 2 APPLICATIONS**

Office equipment, as represented by machines such as dedicated word-processing computers, is becoming more compact today as it shifts from desk-top models to portable models.

The V40HL and V50HL are low-power consumption microprocessors that especially satisfy the demand for compactness in this type of equipment. In addition, because they are able to operate at low voltage, they also accommodate battery-driven systems.

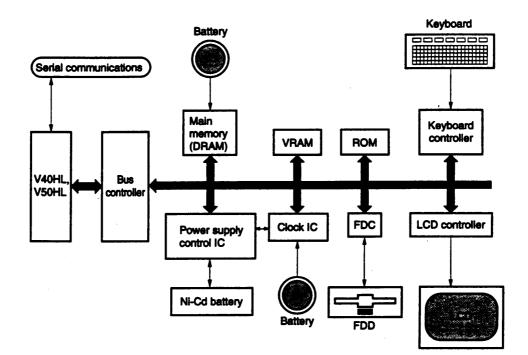

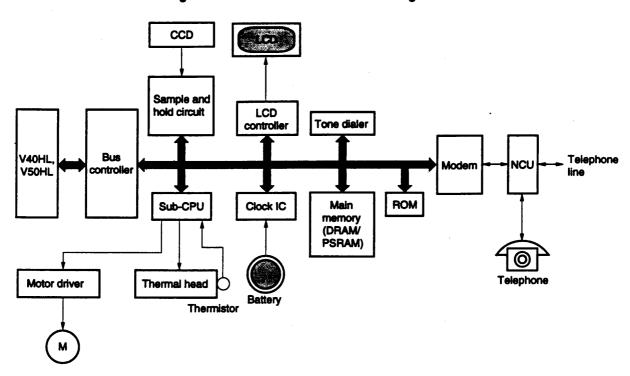

Figure 2-1 shows a block diagram of a typical handy word-processing computer, while Figure 2-2 shows that of a facsimile machine.

Figure 2-1. Handy Word-Processor Block Diagram

Figure 2-2. Facsimile Machine Block Diagram

# **CHAPTER 3 PIN FUNCTIONS**

# 3.1 Pin Function List

The functions of each pin are shown below in Table 3-1.

Table 3-1. Pin Functions (1 of 2)

| Symbol                   | Input/Output         | Function                                        |  |

|--------------------------|----------------------|-------------------------------------------------|--|

| AD0 to AD15Notes 1, 3    | 3-state input/output | Time division address/data bus                  |  |

| AD0 to AD7Notes 2, 3     | 3-state input/output | Time division address/data bus                  |  |

| A8 to A15Notes 2, 3      | 3-state output       | Address bus                                     |  |

| A16/PS0 to A19/PS3Note 3 | 3-state output       | Time division address/processor status          |  |

| REFRQ                    | Output               | Refresh request                                 |  |

| HLDRQ                    | Input                | Bus hold request                                |  |

| HLDAK                    | Output               | Bus hold acknowledge                            |  |

| RESET                    | input                | Reset                                           |  |

| RESOUT                   | Output               | System reset output                             |  |

| READY                    | input                | Bus cycle end                                   |  |

| NMI                      | Input                | Nonmaskable interrupt                           |  |

| MRDNote 3                | 3-state output       | Memory read strobe                              |  |

| MWRNote 3                | 3-state output       | Memory write strobe                             |  |

| IORDNote 3               | 3-state output       | I/O read strobe                                 |  |

| IOWRNote 3               | 3-state output       | I/O write strobe                                |  |

| ASTB                     | Output               | Address strobe                                  |  |

| UBENotes 1, 3            | 3-state output       | Data bus high-order byte enable                 |  |

| HighNote 2               | 3-state output       | High level output                               |  |

| BUSLOCKNote \$           | 3-state output       | Bus lock                                        |  |

| POLL                     | Input                | Polling of floating point operation coprocessor |  |

| BUFR/WNote 3             | 3-state output       | Buffer read/write                               |  |

| BUFENNote 3              | 3-state output       | Buffer enable                                   |  |

| X1                       | Input                | Crystal/external clock                          |  |

| X2                       | -                    |                                                 |  |

| CLKOUT                   | Output               | Clock output                                    |  |

| BS0 to BS2Note 3         | 3-state output       | Bus status                                      |  |

| QS0, QS1                 | Output               | Queue status                                    |  |

Table 3-1. Pin Functions (2 of 2)

| Symbol           | Input/Output | Function                                                   |  |

|------------------|--------------|------------------------------------------------------------|--|

| TOUT2            | Output       | Timer 2 output                                             |  |

| TCTL2            | Input        | Timer 2 control                                            |  |

| TCLK             | Input        | Timer clock                                                |  |

| INTP1 to INTP7   | Input        | Maskable interrupt                                         |  |

| INTAK/SRDY/TOUT1 | Output       | Interrupt acknowledge/serial receive enable/timer 1 output |  |

| DMAAK3/TxD       | Output       | DMA acknowledge 3/serial communications data               |  |

| DMARQ3/RxD       | Input        | DMA request 3/serial receive data                          |  |

| DMAAK0 to DMAAK2 | Output       | DMA acknowledge                                            |  |

| DMARQ0 to DMARQ2 | Input        | DMA request                                                |  |

| END/TC           | Input/output | Forced DMA service end/DMA service complete                |  |

| Voo              | _            | Positive power voltage supply pin                          |  |

| GND              |              | Ground potential pin                                       |  |

| IC               | _            | Internally-connected pin (cannot be connected externally)  |  |

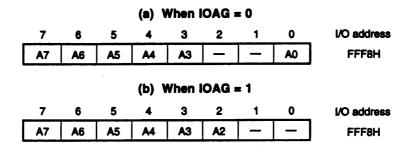

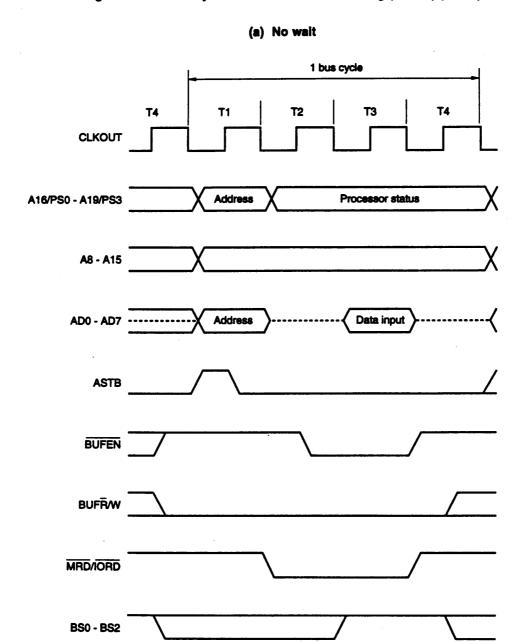

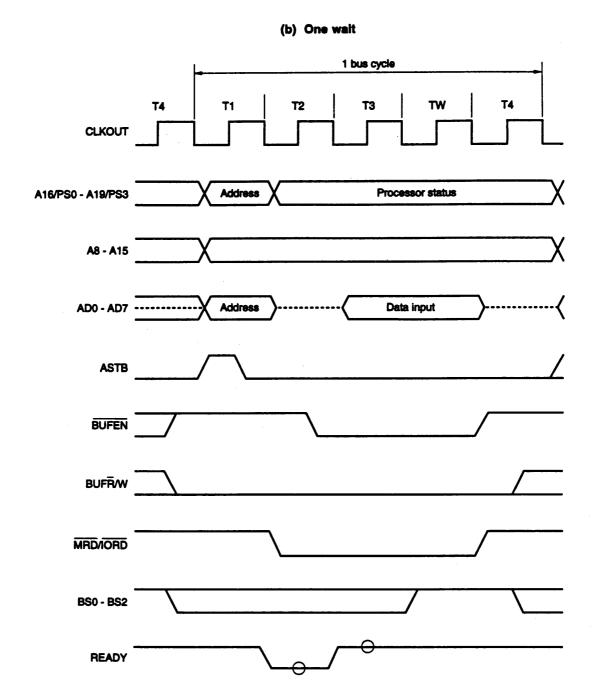

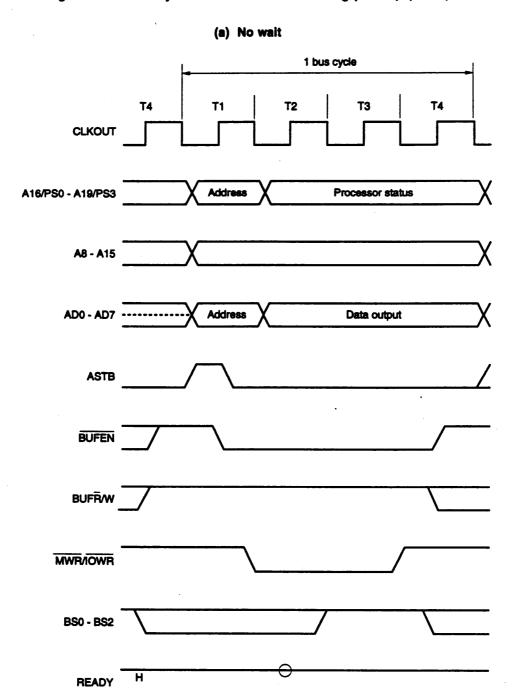

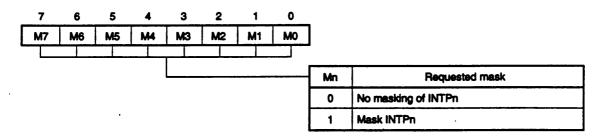

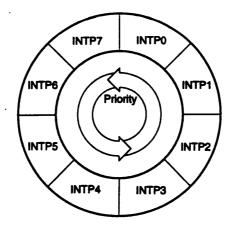

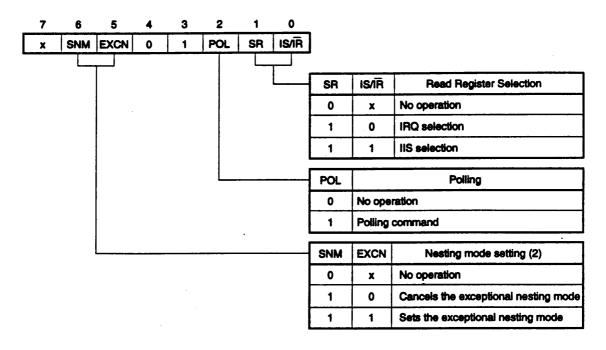

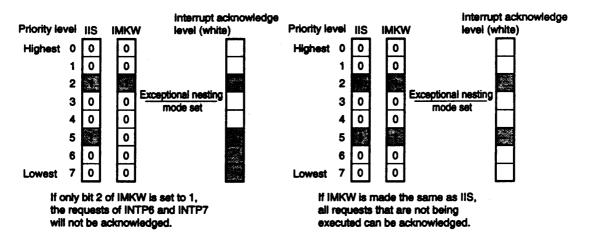

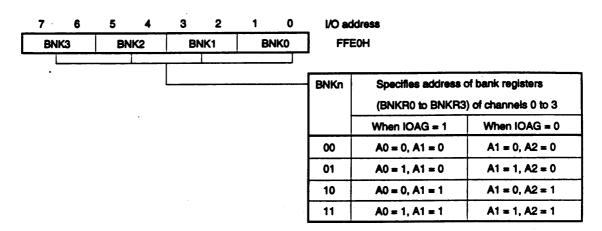

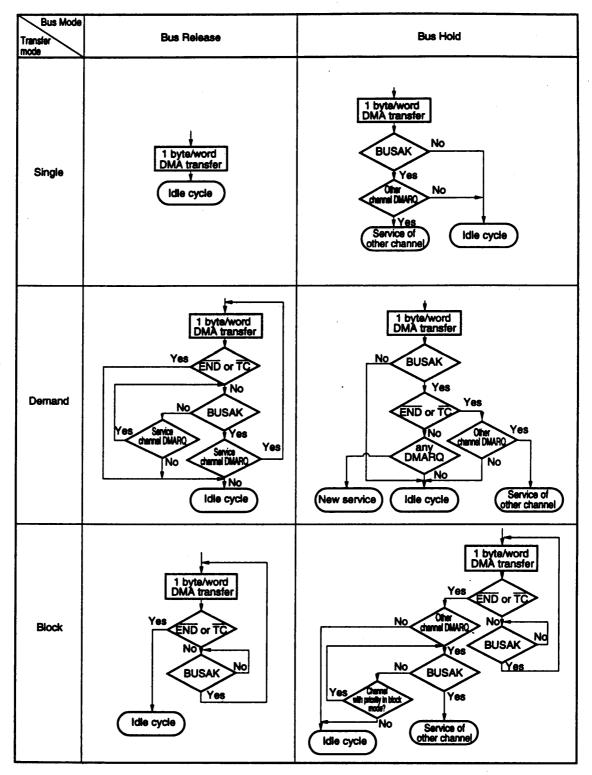

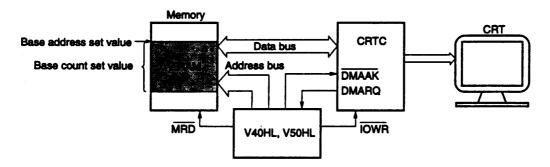

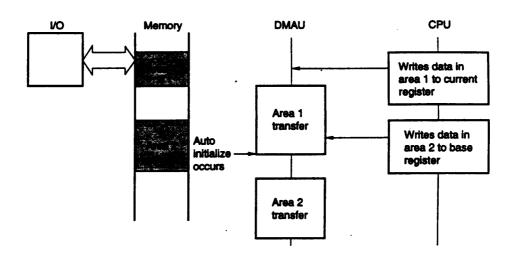

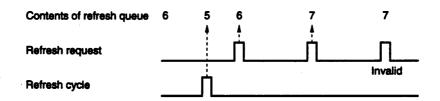

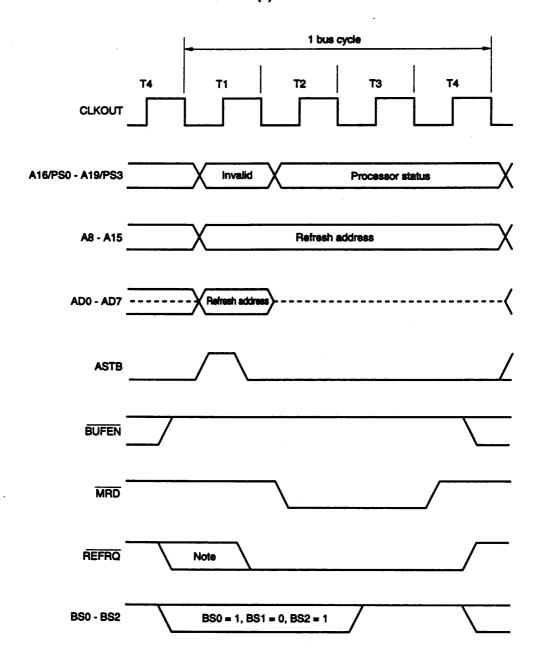

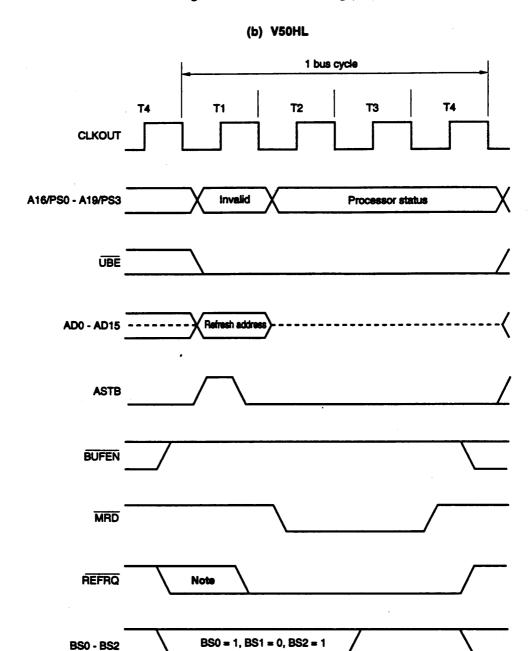

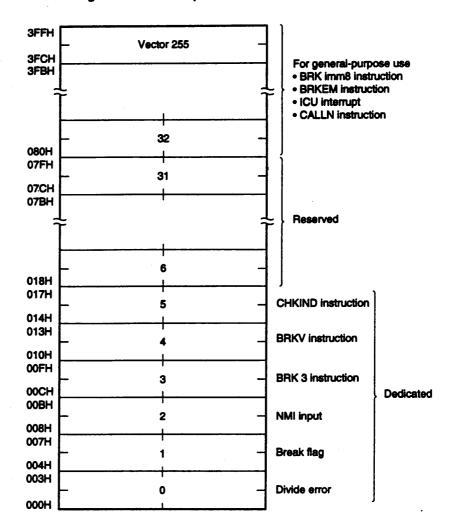

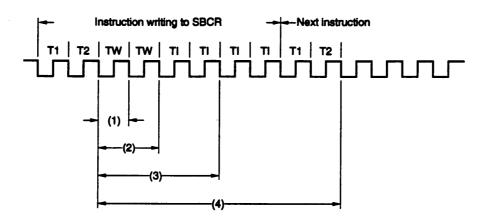

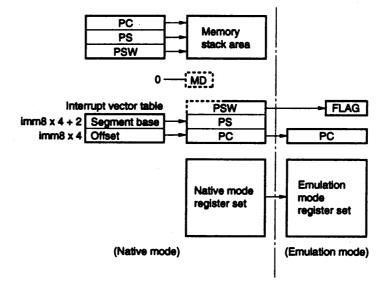

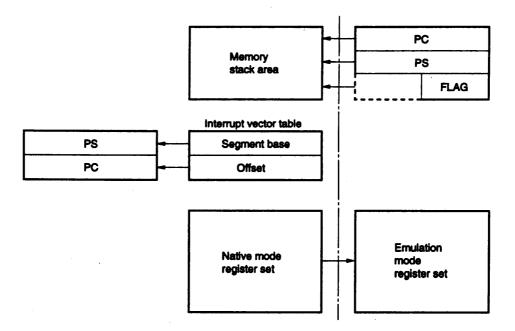

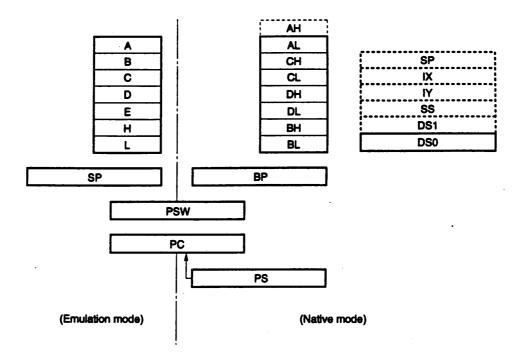

# Notes 1. V50HL only