# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **User's Manual**

$\mu$ PD98410

(NEASCOT-X10™)

1.2G ATM SWITCH LSI

Document No. S12523EJ2V0UMJ1 (2nd edition) Date Published October 2000 N CP(K) [MEMO]

Phase-out/Discontinued

#### NOTES FOR CMOS DEVICES

# 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

#### NEASCOT-X10 is a trademark of NEC Corporation.

The export of this product from Japan is prohibited without governmental license. To export or re-export this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information in this document is current as of October, 1998. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

#### **PREFACE**

Readers This manual is intended for user engineers who wish to understand the functions of

the  $\mu$ PD98410 and design application systems using it.

Purpose This manual explains the hardware functions of the μPD98410 in the following

organization.

**Organization** This manual consists of the following chapters.

General

· Pin functions

· Functional outline

· Internal registers

• JTAG boundary scan

Limitations

FAQ (Frequency Asked Questions)

**How to Read This Manual**

It is assumed that the readers of this manual have a general knowledge of electricity, logic circuits, and microcomputers.

To understand the overall functions of the  $\mu$ PD98410  $\rightarrow$  Read this manual in the order of Table of Contents.

If you have any questions about the operation of the  $\mu$ PD98410

$\rightarrow$  Read CHAPTER 7  $\,$  FAQ (Frequently Asked Questions).

Conventions Data significance : Left: high-order digit, right: low-order digit

Active low : xxx\_B (\_B following pin or signal name)

Memory map address : Top: high-order, bottom: low-order

Note : Explanation of part of text marked Note

**Caution** : Important information

Remark : Supplementary information

Numeric notation : Binary ... xxxx or xxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Related documentation

Some of the related documents are preliminary editions but are not so specified below.

Pamphlet : \$12131EData sheet : \$12624EApplication Note: \$13107E

[MEMO]

Phase-out/Discontinued

# **CONTENTS**

| CHAPTE | R 1 GENERAL                                     | 15       |

|--------|-------------------------------------------------|----------|

| 1.1    | Features                                        | 15       |

| 1.2    | Ordering Information                            | 15       |

| 1.3    | Example of System Configuration (Application)   | 16       |

| 1.4    | Block Diagram                                   | 17       |

| 1.5    | Pin Configuration                               | 18       |

| CHAPTE | R 2 PIN FUNCTIONS                               | 19       |

| 2.1    | Pin Configuration (Bottom View)                 | 19       |

| 2.2    | Pin Layout                                      | 21       |

| 2.3    | Pin Functions                                   | 27       |

|        | 2.3.1 Power supply                              | 27       |

|        | 2.3.2 UTOPIA interface                          | 28       |

| 2.4    | Memory Interface Signals                        | 32       |

|        | 2.4.1 Microprocessor interface signals          | 34       |

|        | 2.4.2 JTAG                                      | 36       |

|        | 2.4.3 Others                                    | 36       |

| 2.5    | Recommended Connections of Unused Pins          | 37       |

| 2.6    | Pin Status at Reset                             | 38       |

| 3.1    | TR 3 FUNCTIONAL OUTLINE                         | 39<br>39 |

| J. 1   | 3.1.1 Input port interface                      | 40       |

|        | 3.1.2 Output port interface                     | 41       |

| 3.2    | Polling                                         | 42       |

| 0.2    | 3.2.1 Outline of polling                        | 42       |

|        | 3.2.2 Polling during cell output                | 44       |

|        | 3.2.3 Polling during cell input                 | 50       |

| 3.3    | Header Translation                              | 56       |

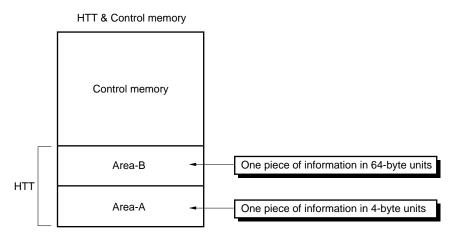

| 0.0    | 3.3.1 HTT (Header Translation Table) memory map | 56       |

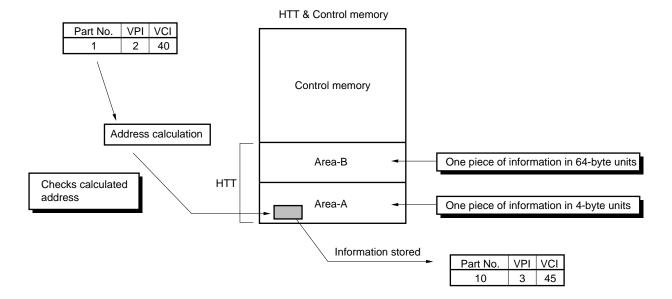

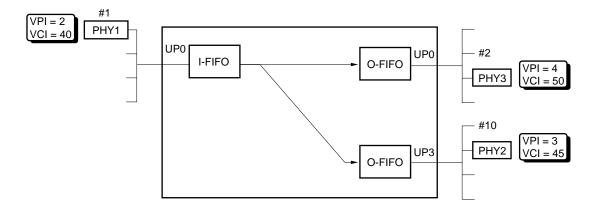

|        | 3.3.2 General                                   | 57       |

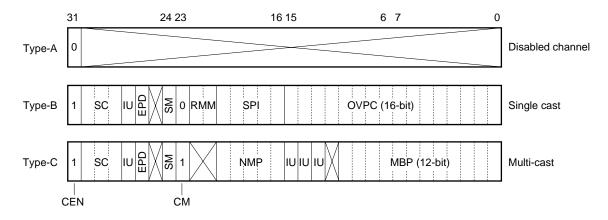

|        | 3.3.3 Format of HTT                             | 60       |

|        | 3.3.4 Accessing HTT                             | 63       |

|        | 3.3.5 Flow of header translation                | 68       |

|        | 3.3.6 Accessing HTT with RM cell                | 72       |

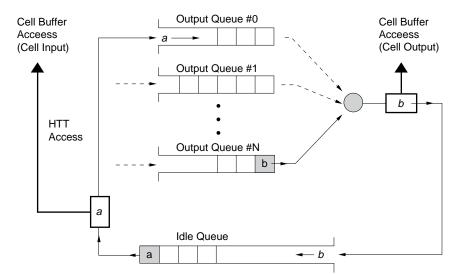

| 3.4    | Queue Control                                   | 75       |

|        | 3.4.1 Single cast                               | 75       |

|        | 3.4.2 Multi-cast                                | 76       |

|        | 3.4.3 Congestion control                        | 77       |

|        | 3.4.4 Cell discard by class                     | 81       |

|        | 3.4.5 EPD (Early Packet Discard) control        | 82       |

|        | 3.4.6 PPD (Partial Packet Discard) control      | 84       |

|        | 3.4.7 Minimum queue length                      | 85       |

|        |                                                 | 55       |

| 3.5    | ABR Congestion Control                                                                     | . 00  |

|--------|--------------------------------------------------------------------------------------------|-------|

|        | 3.5.1 EFCI (Explicit Forward Congestion Indicator)                                         | . 88  |

|        | 3.5.2 RM cell CI/NI marking (Resource Management Cell CI/NI Congestion Indication Marking) | 88    |

|        | 3.5.3 RM cell merge (Resource Management Cell Merge)                                       | 89    |

| 3.6    | WFQ (Weighted Fairness Queue)                                                              | . 90  |

|        | 3.6.1 General                                                                              | . 90  |

|        | 3.6.2 Counters and flags used                                                              | . 90  |

| 3.7    | Peak Rate Shaping Function                                                                 |       |

|        | 3.7.1 General                                                                              |       |

|        | 3.7.2 Details                                                                              |       |

| 3.8    | Successive Transmission                                                                    |       |

| 3.9    | Interrupt Request                                                                          |       |

| 0.0    | 3.9.1 Parity error                                                                         |       |

|        | 3.9.2 Input port overrun                                                                   |       |

|        | 3.9.3 Queue pointer error                                                                  |       |

|        | 3.9.4 Cast count error                                                                     |       |

|        | 3.9.5 Cell buffer memory shortage                                                          |       |

|        | 3.9.6 Control memory shortage                                                              |       |

|        | 3.9.7 HEC/CRC error                                                                        |       |

|        | 3.9.8 Header translation error                                                             |       |

|        | 3.9.9 Exceeding buffer threshold value                                                     |       |

|        | 3.9.10 Count over detection                                                                |       |

| 3 10   | Monitoring                                                                                 |       |

| 3.10   | 3.10.1 Monitor register                                                                    |       |

|        | 3.10.2 Cell discard count due to exceeded threshold value                                  |       |

|        | 3.10.3 Cell discard count due to header translation error                                  |       |

|        | 3.10.4 Cell discard count due to HEC error or CRC error                                    |       |

|        | 3.10.5 Cell discard count due to control/cell buffer memory shortage                       |       |

|        | 3.10.6 Counting number of received cells                                                   |       |

| 3.11   | · ·                                                                                        |       |

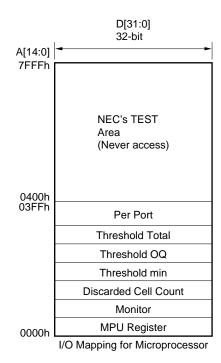

| 3.11   | 3.11.1 I/O mapping and memory mapping                                                      |       |

|        | 3.11.2 32-bit multiplexed synchronous bus (HSEL = Low)                                     |       |

|        | 3.11.3 16-bit separated asynchronous bus (HSEL = High)                                     |       |

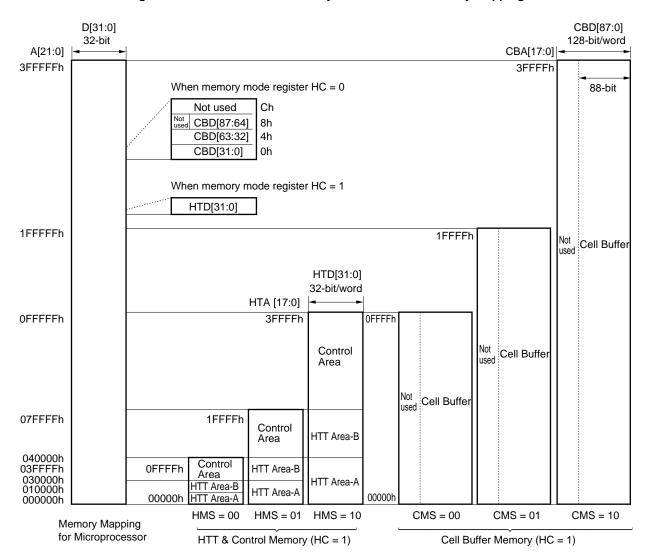

| 2 12   | External Memory Interface                                                                  |       |

| 3.12   | 3.12.1 HTT & control memory interface                                                      |       |

|        | 3.12.2 Cell buffer interface                                                               |       |

|        | 3.12.2 Gen buner interface                                                                 | . 113 |

| CHAPTE | R 4 INTERNAL REGISTERS                                                                     | . 123 |

|        |                                                                                            | •     |

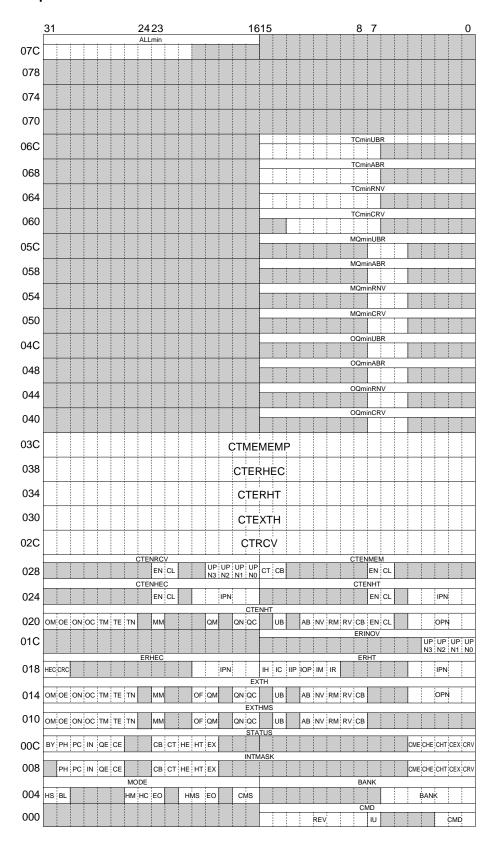

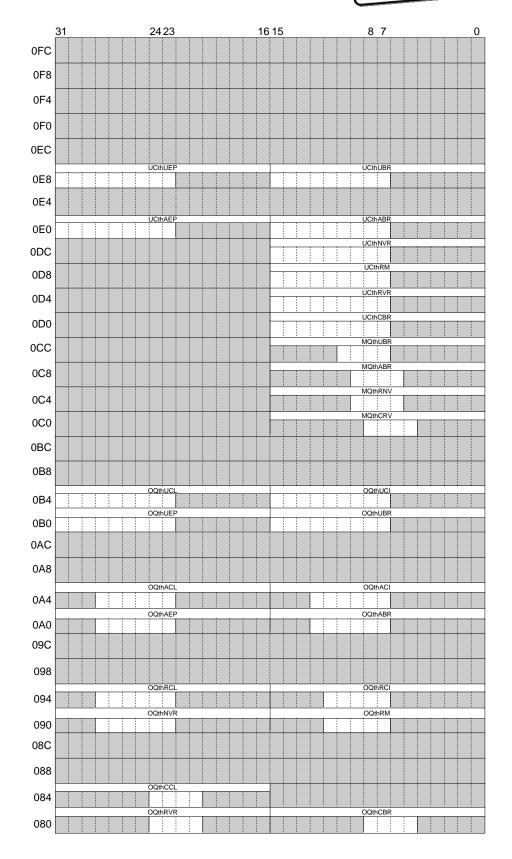

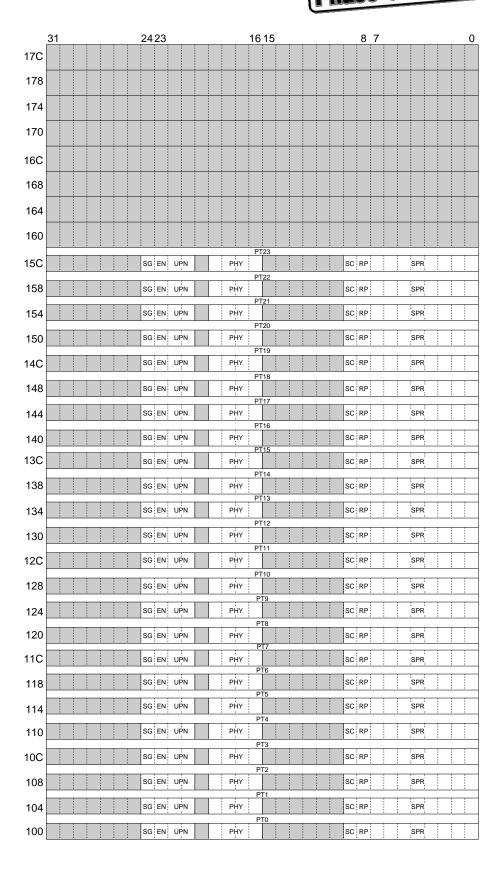

| 4.1    | Register List                                                                              | . 123 |

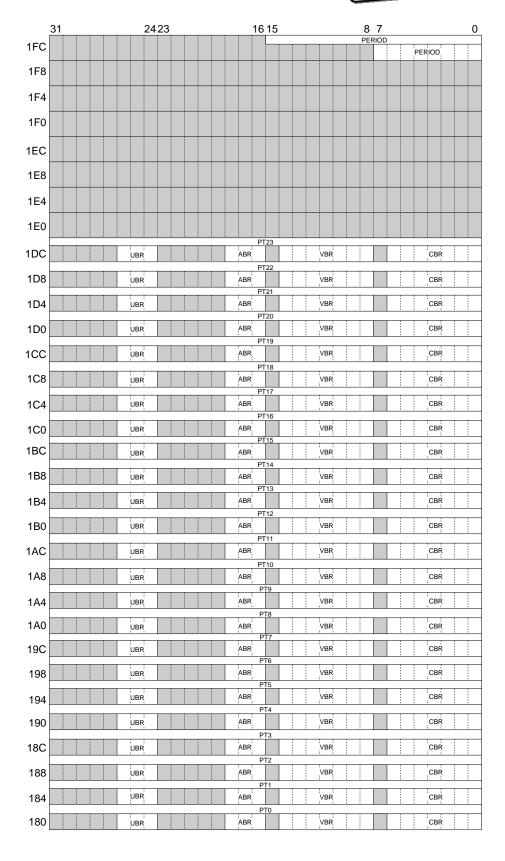

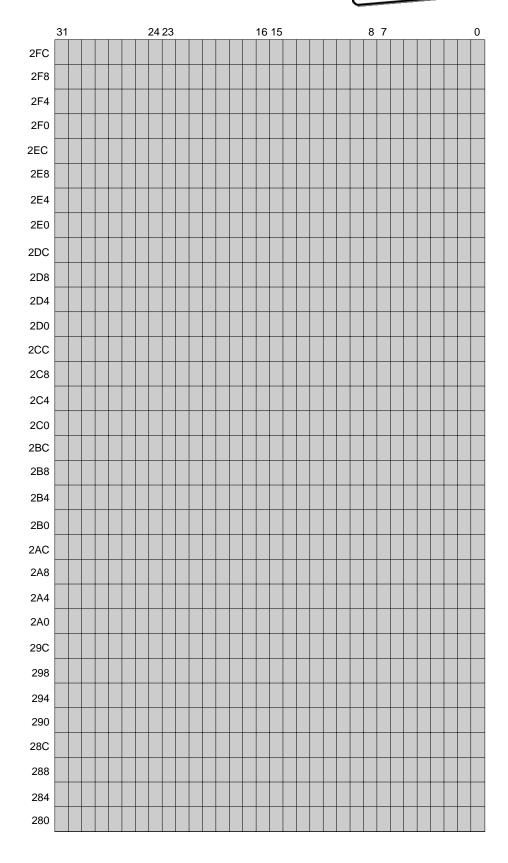

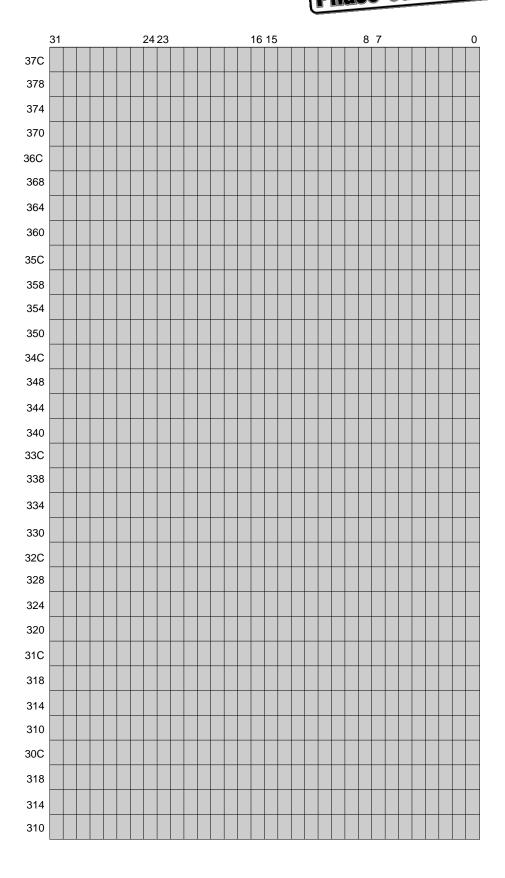

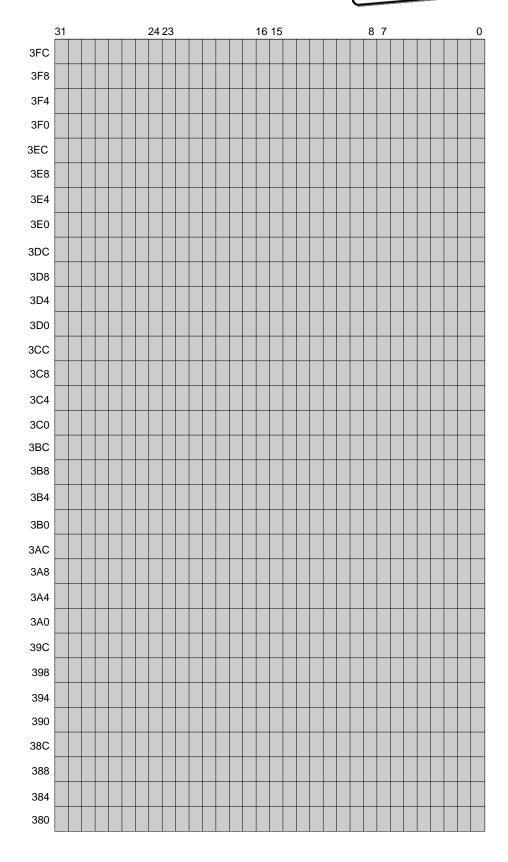

| 4.2    | Register Map                                                                               | . 125 |

| 4.3    | Register Functions                                                                         | . 133 |

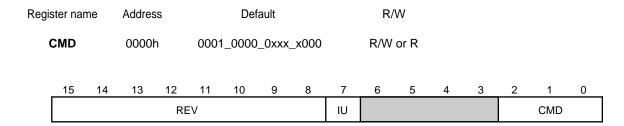

|        | 4.3.1 Command register (0000h)                                                             | . 133 |

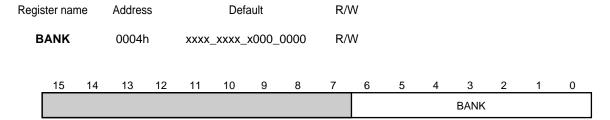

|        | 4.3.2 Memory bank register (0004h)                                                         | . 134 |

|        | 4.3.3 Memory mode register (0006h)                                                         | . 134 |

|        | 4.3.4 Interrupt mask register (0008h)                                                      | . 136 |

|        | 4.3.5 Status register (000Ch)                                                              | . 137 |

|        | 4.3.6 Threshold value exceeding discard indication mask register (0010h)                   | 139   |

|        | 4.3.7 Threshold value exceeding discard indication register (0014h)                        | 139   |

|        |                                                                                            |       |

|            | 4.3.8 Header translation error discard indication register (0018h)                      | 142 |  |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

|            | 4.3.9 HEC/CRC error discard indication register (001Ah)                                 | 144 |  |  |  |  |  |  |  |

|            | 4.3.10 Input port overrun error discard indication register (001Ch)                     | 145 |  |  |  |  |  |  |  |

|            | 4.3.11 Threshold value exceeding discard cell count enable register (0020h)             |     |  |  |  |  |  |  |  |

|            | 4.3.12 Header translation error discard cell count enable register (0024h)              | 147 |  |  |  |  |  |  |  |

|            | 4.3.13 HEC/CRC error discard cell count enable register (0026h)                         | 148 |  |  |  |  |  |  |  |

|            | 4.3.14 Control/cell buffer memory shortage discard cell count enable register (0028h)   | 149 |  |  |  |  |  |  |  |

|            | 4.3.15 Receive cell count enable register (002Ah)                                       | 150 |  |  |  |  |  |  |  |

|            | 4.3.16 Receive cell count register (002Ch)                                              | 151 |  |  |  |  |  |  |  |

|            | 4.3.17 Threshold value exceeding discard cell count register (0030h)                    | 152 |  |  |  |  |  |  |  |

|            | 4.3.18 Header translation error discard cell count register (0034h)                     | 153 |  |  |  |  |  |  |  |

|            | 4.3.19 HEC/CRC error discard cell count register (0038h)                                | 154 |  |  |  |  |  |  |  |

|            | 4.3.20 Control/cell buffer memory shortage discard cell count register (003Ch)          | 155 |  |  |  |  |  |  |  |

|            | 4.3.21 Output queue minimum threshold value registers (0040h, 0044h, 0048h, 004Ch)      | 156 |  |  |  |  |  |  |  |

|            | 4.3.22 Multi-cast queue minimum threshold value registers (0050h, 0054h, 0058h, 005Ch)  | 157 |  |  |  |  |  |  |  |

|            | 4.3.23 TC (Total Cell) counter minimum threshold registers (0060h, 0064h, 0068h, 006Ch) | 158 |  |  |  |  |  |  |  |

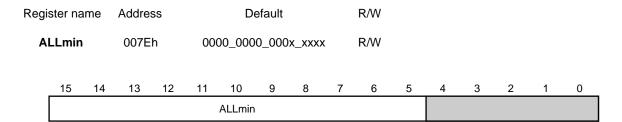

|            | 4.3.24 Total number of cells minimum threshold value register (007Eh)                   | 159 |  |  |  |  |  |  |  |

|            | 4.3.25 Output queue maximum threshold value registers                                   |     |  |  |  |  |  |  |  |

|            | (0080h, 0082h, 0090h, 0092h, 00A0h, 00B0h)                                              | 160 |  |  |  |  |  |  |  |

|            | 4.3.26 Output queue EPD threshold value registers (00A2h, 00B2h)                        |     |  |  |  |  |  |  |  |

|            | 4.3.27 Output queue EFCI threshold value registers (0094h, 00A4h, 00B4h)                |     |  |  |  |  |  |  |  |

|            | 4.3.28 Output queue CLP threshold value registers (0086h, 0096h, 00A6h, 00B6h)          |     |  |  |  |  |  |  |  |

|            | 4.3.29 Multi-cast queue maximum threshold value registers (00C0h, 00C4h, 00C8h, 00CCh)  |     |  |  |  |  |  |  |  |

|            | 4.3.30 UC (Used Cell) counter maximum threshold value register                          |     |  |  |  |  |  |  |  |

|            | (00D0h, 00D4h, 00D8h, 00DCh, 00E0h, 00E8h)                                              | 165 |  |  |  |  |  |  |  |

|            | 4.3.31 UC (Used Cell) Counter EPD threshold value registers (00E2h, 00EAh)              |     |  |  |  |  |  |  |  |

|            | 4.3.32 Port configuration register                                                      |     |  |  |  |  |  |  |  |

|            | 4.3.33 Class priority control register                                                  |     |  |  |  |  |  |  |  |

|            | 4.3.34 Cycle count register (01FCh)                                                     |     |  |  |  |  |  |  |  |

|            | 4.3.35 Header translation configuration register                                        |     |  |  |  |  |  |  |  |

|            | noise Treater Rancialer Comgaration Cogletor                                            |     |  |  |  |  |  |  |  |

| CHAPTE     | R 5 JTAG BOUNDARY SCAN                                                                  | 173 |  |  |  |  |  |  |  |

| 5.1        | Footures                                                                                | 172 |  |  |  |  |  |  |  |

| 5.1<br>5.2 | Features Internal Configuration of Boundary Scan Circuit                                |     |  |  |  |  |  |  |  |

| 3.2        | 5.2.1 Instruction register                                                              |     |  |  |  |  |  |  |  |

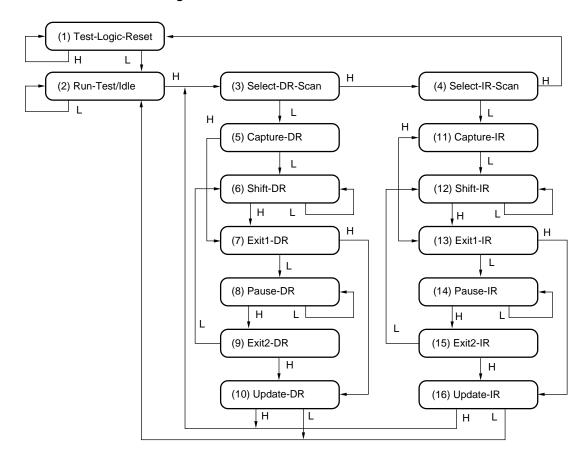

|            | 5.2.2 TAP (Test Access Port) controller                                                 |     |  |  |  |  |  |  |  |

|            | ,                                                                                       |     |  |  |  |  |  |  |  |

|            | 5.2.3 Bypass register                                                                   |     |  |  |  |  |  |  |  |

| <b>5</b> 2 | 5.2.4 Boundary scan register                                                            |     |  |  |  |  |  |  |  |

| 5.3        | Pin Function                                                                            |     |  |  |  |  |  |  |  |

|            | 5.3.1 JCK (JTAG Mode Solett) rin                                                        |     |  |  |  |  |  |  |  |

|            | 5.3.2 JMS (JTAG Mode Select) pin                                                        |     |  |  |  |  |  |  |  |

|            | 5.3.3 JDI (JTAC Data Input) pin                                                         |     |  |  |  |  |  |  |  |

|            | 5.3.4 JDO (JTAG Data Output) pin                                                        |     |  |  |  |  |  |  |  |

| <b>.</b> . | 5.3.5 JRST_B (JTAG Reset) pin                                                           |     |  |  |  |  |  |  |  |

| 5.4        | Operation Description                                                                   |     |  |  |  |  |  |  |  |

|            | 5.4.1 TAP controller                                                                    |     |  |  |  |  |  |  |  |

|            | 5.4.2 TAP controller state                                                              | 1/6 |  |  |  |  |  |  |  |

| 5.5    | TAP Controller Operation          |            |

|--------|-----------------------------------|------------|

| 5.6    | Initializing TAP Controller       |            |

| 5.7    | Instruction Register              | 184        |

|        | 5.7.1 BYPASS instruction          | 185        |

|        | 5.7.2 EXTEST instruction          | 185        |

|        |                                   |            |

| 5.8    | Boundary Scan Data Bit Definition | 185        |

|        | Boundary Scan Data Bit Definition |            |

|        |                                   | 187        |

| CHAPTE | R 6 LIMITATIONS                   | 187<br>187 |

# LIST OF FIGURES (1/2)

| Figure | e No. Title                                                                                  | Page |

|--------|----------------------------------------------------------------------------------------------|------|

|        |                                                                                              |      |

| 3-1    | Example of Connecting UTOPIA Receive Interface                                               | 40   |

| 3-2    | Example of Connecting UTOPIA Transmit Interface                                              | 41   |

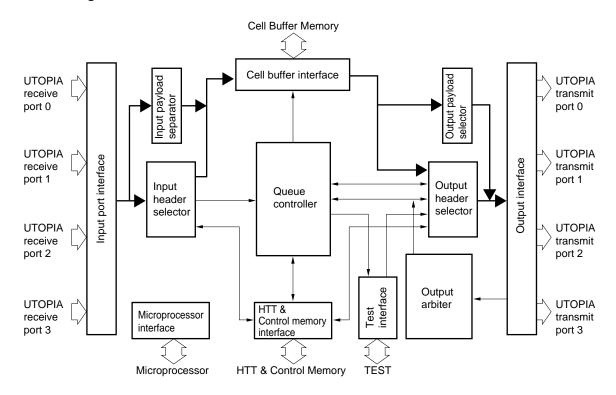

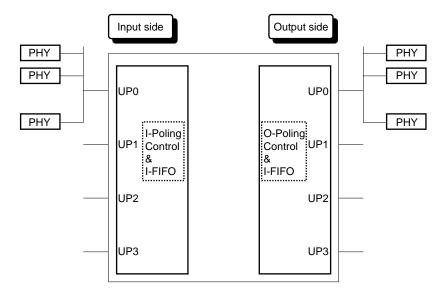

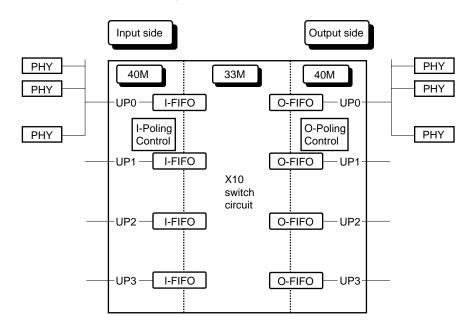

| 3-3    | Functional Blocks of μPD98410                                                                | 42   |

| 3-4    | Clock Relation                                                                               | 44   |

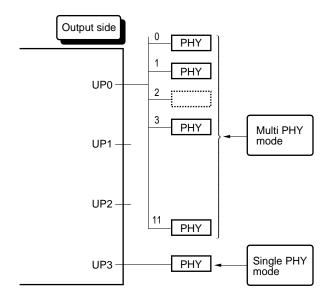

| 3-5    | Single PHY Mode and Multi-PHY Mode                                                           | 44   |

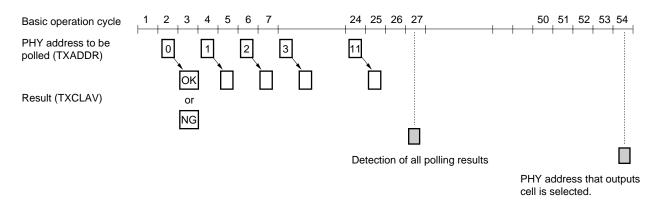

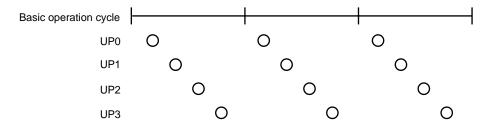

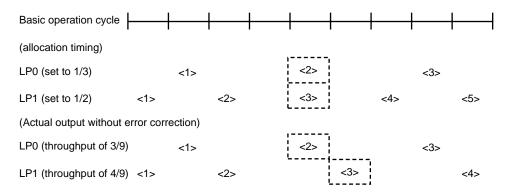

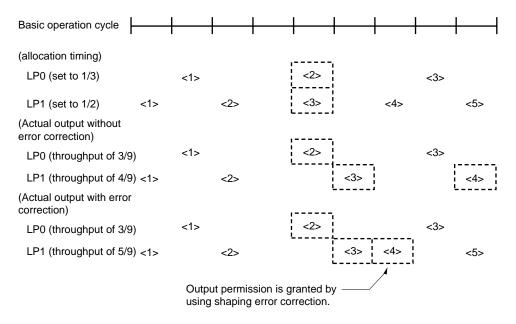

| 3-6    | Relationship between Polling Control and Basic Operation Cycle (in multi-PHY mode)           | 45   |

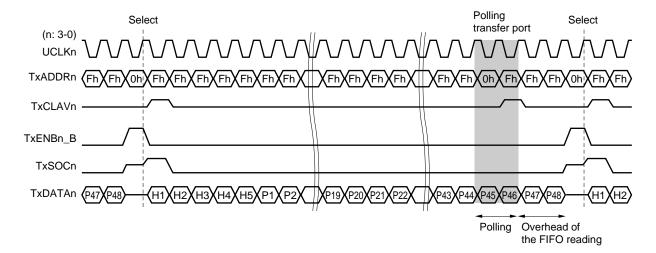

| 3-7    | Polling Operation during Cell Output                                                         | 46   |

| 3-8    | Polling Operation during Cell Output                                                         | 47   |

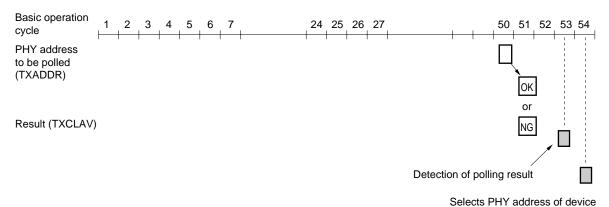

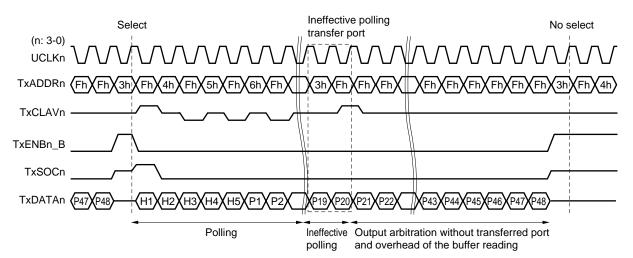

| 3-9    | Relationship between Polling Control and Basic Operation Cycle (single PHY mode)             | 48   |

| 3-10   | Control of Successive Output                                                                 | 49   |

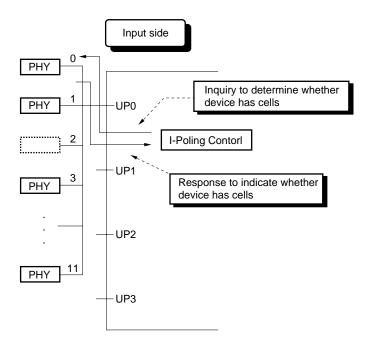

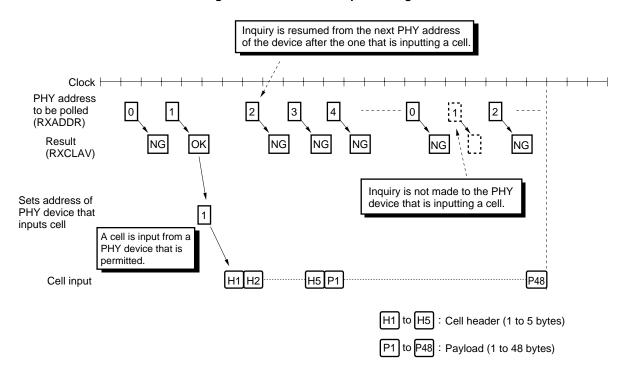

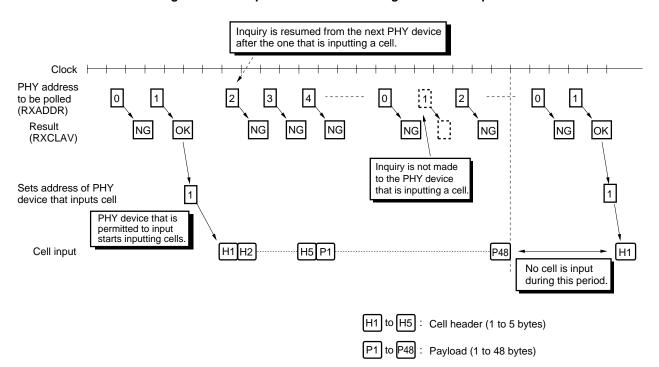

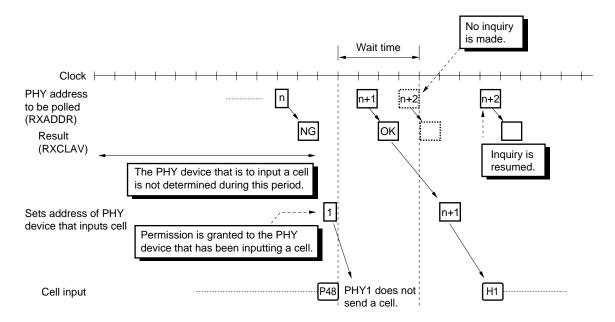

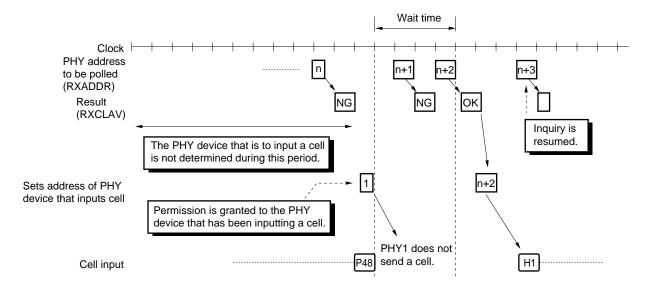

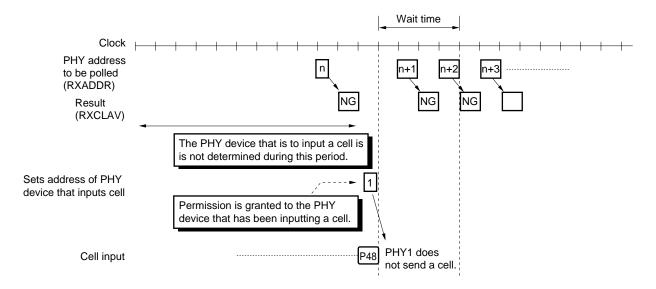

| 3-11   | Basic Operation of Polling during Cell Input                                                 | 50   |

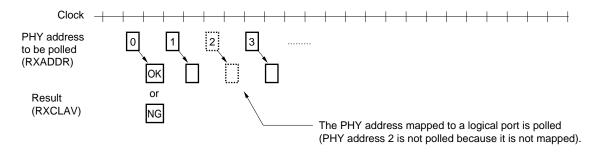

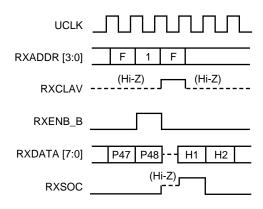

| 3-12   | Relationship between Polling Control and Basic Operation Cycle (during cell input)           | 50   |

| 3-13   | Basic Cell Input Timing 1                                                                    | 51   |

| 3-14   | Basic Cell Input Timing 2                                                                    | 52   |

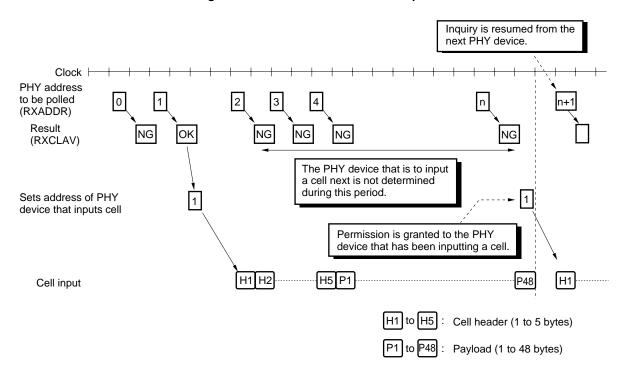

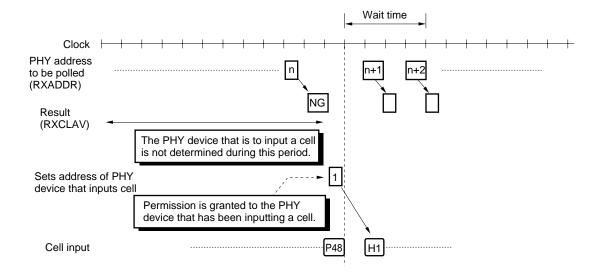

| 3-15   | Drop in Transfer Rate during Successive Input                                                | 52   |

| 3-16   | Control of Successive Input                                                                  |      |

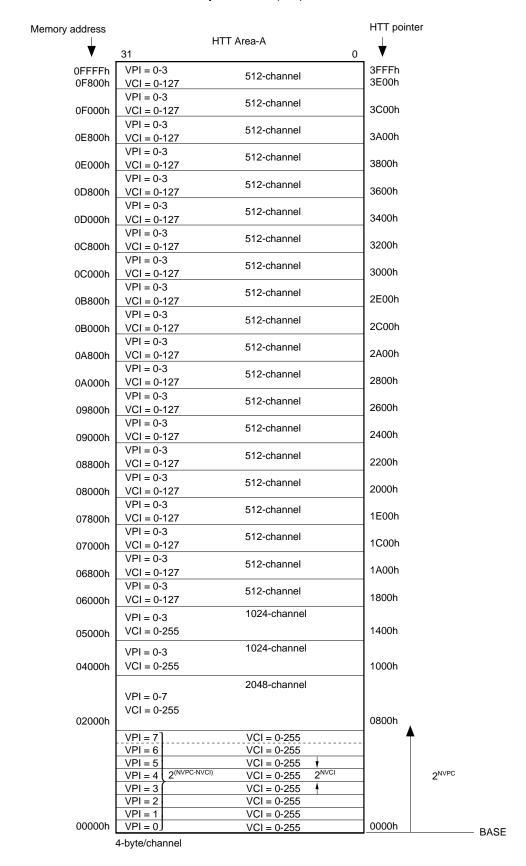

| 3-17   | HTT & Control Memory Map                                                                     | 56   |

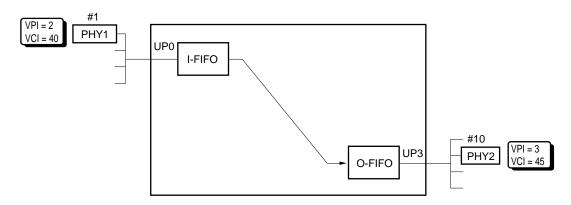

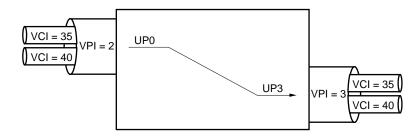

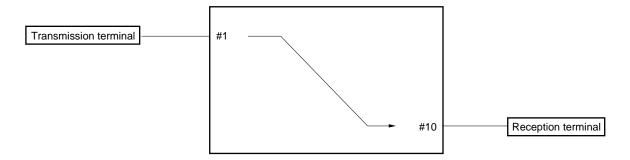

| 3-18   | Example of Single Cast                                                                       |      |

| 3-19   | HTT (Header Translation Table)                                                               |      |

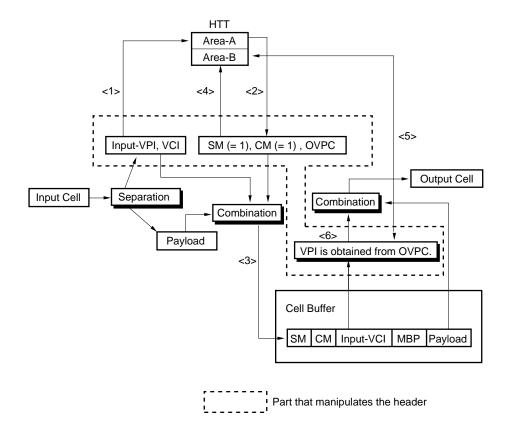

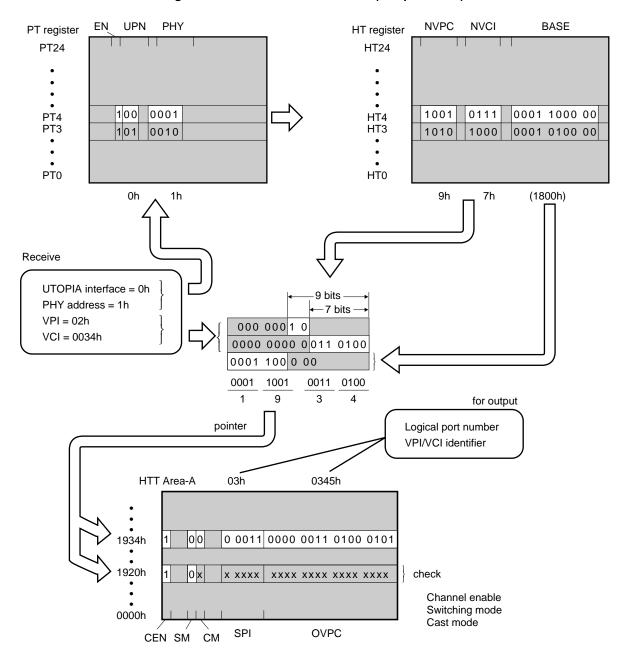

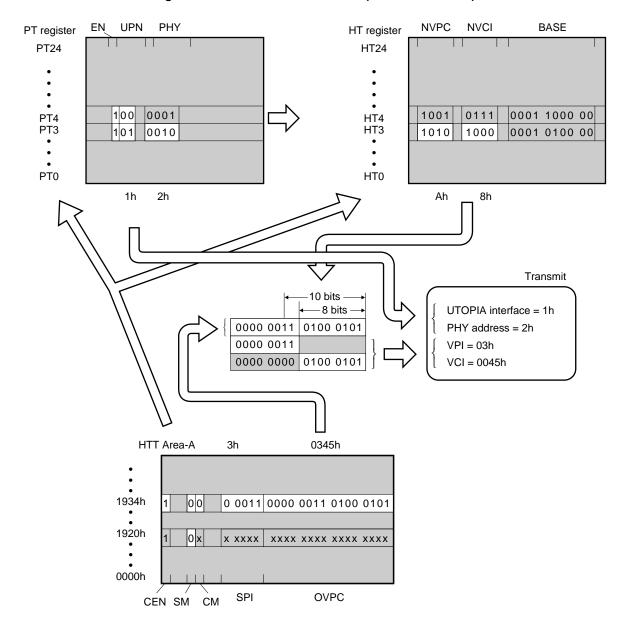

| 3-20   | Flow of Header Translation Information in Single-Cast Mode                                   |      |

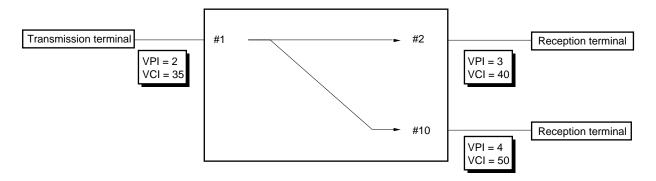

| 3-21   | Example of Multi-Cast                                                                        |      |

| 3-22   | Flow of Header Translation Information in Multi-Cast Mode                                    |      |

| 3-23   | HTT Area-A Format                                                                            |      |

| 3-24   | HTT Area-B Format                                                                            | 62   |

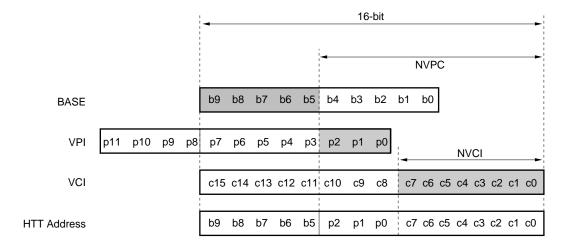

| 3-25   | VP Connection and VC Connection                                                              |      |

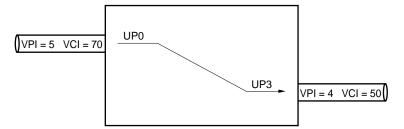

| 3-26   | Difference in Access to HTT between VPC and VCC (single cast)                                |      |

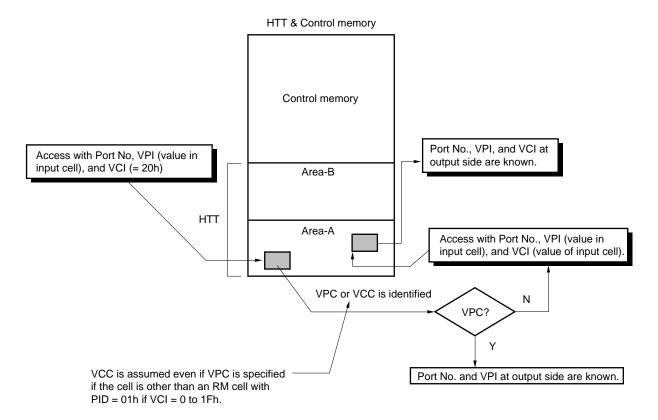

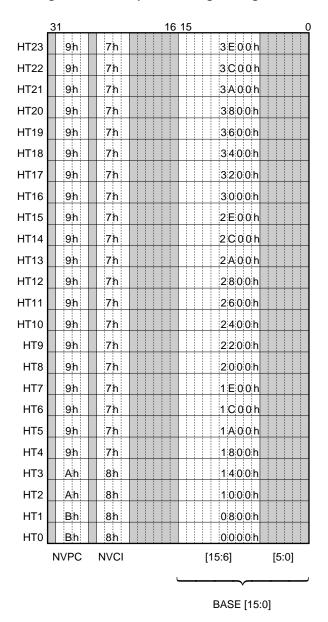

| 3-27   | Calculating HTT Address                                                                      |      |

| 3-28   | Setting Format of OVPC                                                                       |      |

| 3-29   | Flow of Header Translation in VCC and Single Cast Modes                                      |      |

| 3-30   | Flow of Header Translation in VCC and Multi-Cast Modes                                       |      |

| 3-31   | Flow of Header Translation in VPC and Single Cast Modes                                      |      |

| 3-32   | Flow of Header Translation in VPC and Multi-Cast Modes                                       |      |

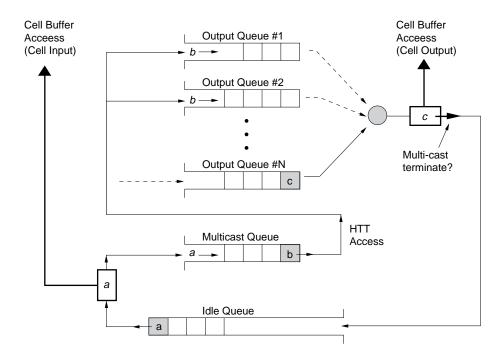

| 3-33   | Queuing of Cell Address (Single Cast)                                                        |      |

| 3-34   | Queuing of Cell Address (Multi-Cast)                                                         |      |

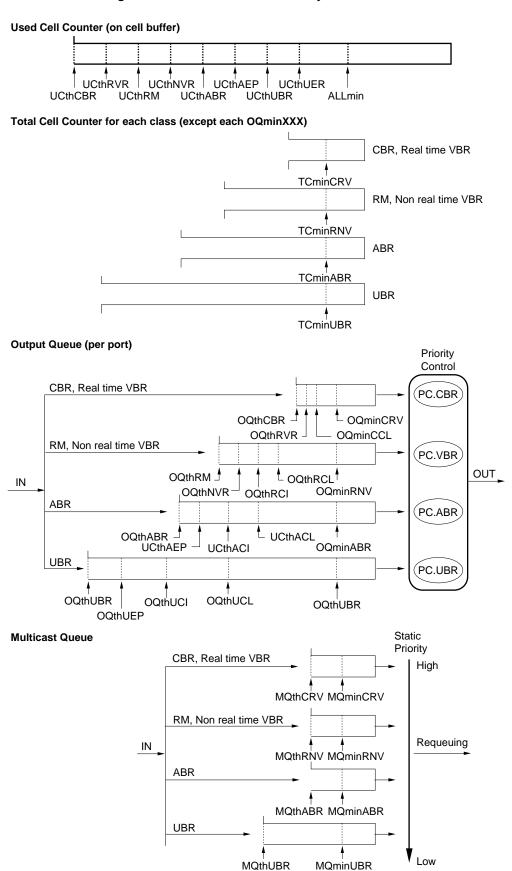

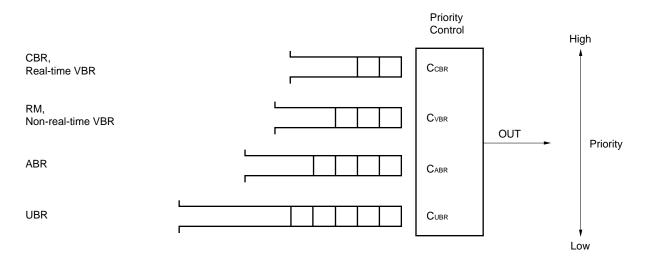

| 3-35   | Queues and Counters by Service Class                                                         |      |

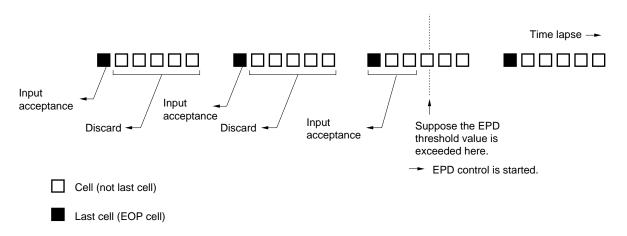

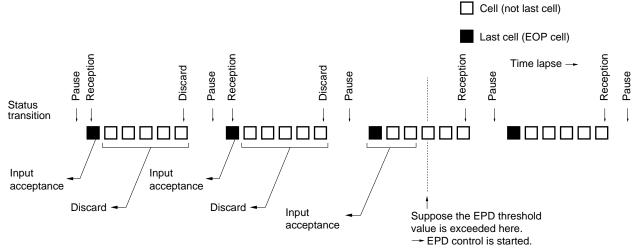

| 3-36   | When EPD Control Is Enabled                                                                  |      |

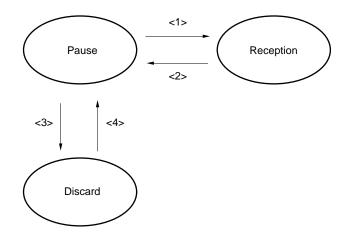

| 3-37   | Status Transition When EOP Control Is Enabled                                                |      |

| 3-38   | Status Transition of EPD Control                                                             |      |

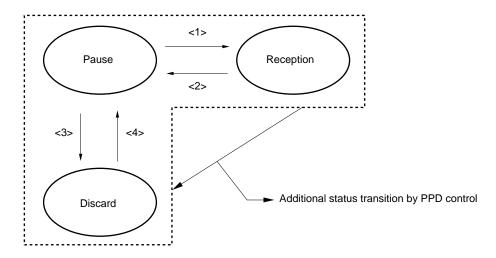

| 3-39   | Status Transition of PPD Control                                                             |      |

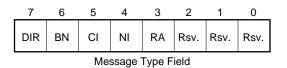

| 3-40   | RM Cell Configuration (ATM Forum TM Ver. 4.0)                                                |      |

| 3-41   | Output Queue and Counter                                                                     |      |

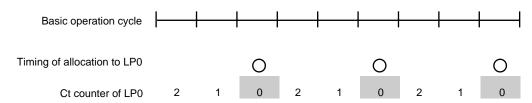

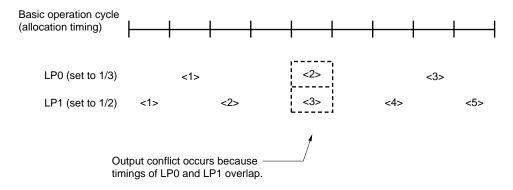

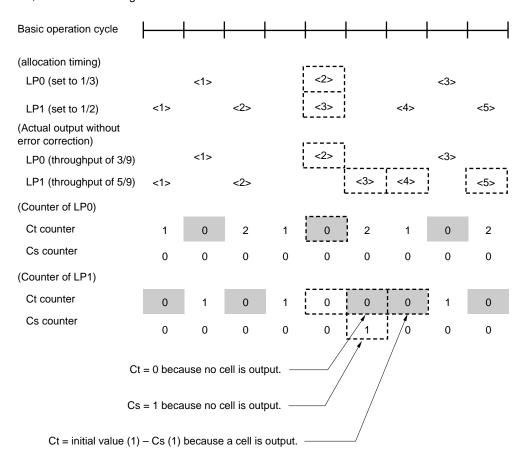

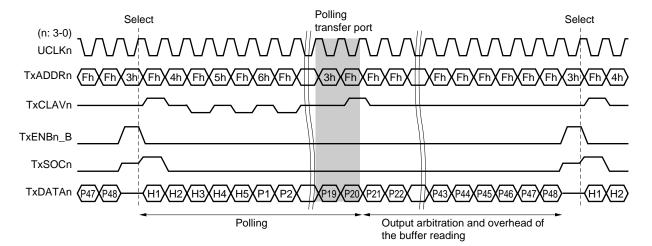

| 3-42   | Relationship between Internal Basic Cycle and Output Enable Timing of Each UTOPIA Interface. |      |

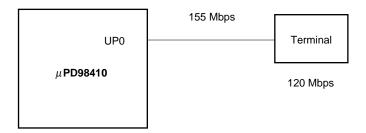

| 3-43   | Example of Connection between µPD98410 and Terminal                                          |      |

| 3-44   | Polling Timing (a)                                                                           |      |

|        | · -···· · · · · · · · · · · · · · · · ·                                                      |      |

# LIST OF FIGURES (2/2)

| Figure No. Title |                                                                    | Page |

|------------------|--------------------------------------------------------------------|------|

|                  |                                                                    |      |

| 3-45             | Polling Timing (b)                                                 | 101  |

| 3-46             | Polling Timing (c)                                                 | 102  |

| 3-47             | I/O Register Mapping                                               | 111  |

| 3-48             | HTT & Control Memory and Cell Buffer Memory Mapping                | 112  |

| 3-49             | Access Timing of 32-Bit Multiplexed Synchronous Bus                | 114  |

| 3-50             | Access Timing of 16-Bit Separated Asynchronous Bus                 | 116  |

| 3-51             | Memory Map of 16-Bit Separated Asynchronous Bus                    | 117  |

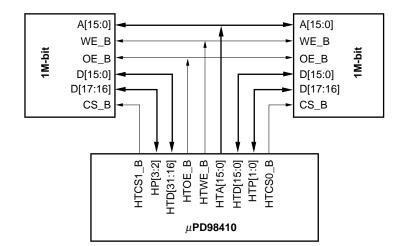

| 3-52             | Example of Connecting HTT & Control Memory (minimum configuration) | 118  |

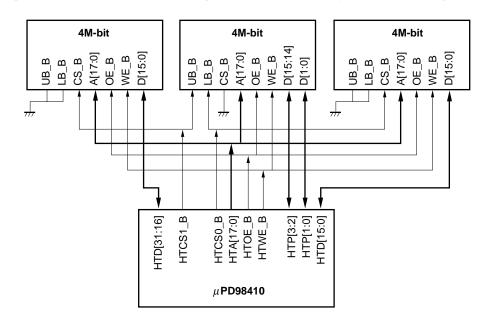

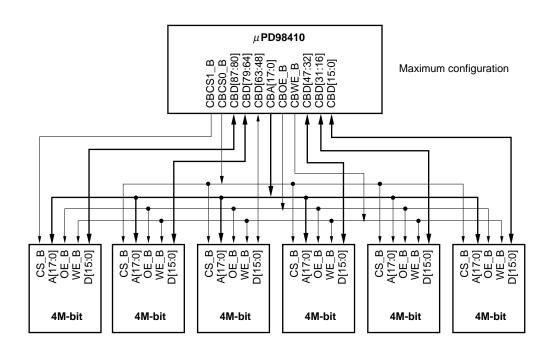

| 3-53             | Example of Connecting HTT & Control Memory (maximum configuration) | 119  |

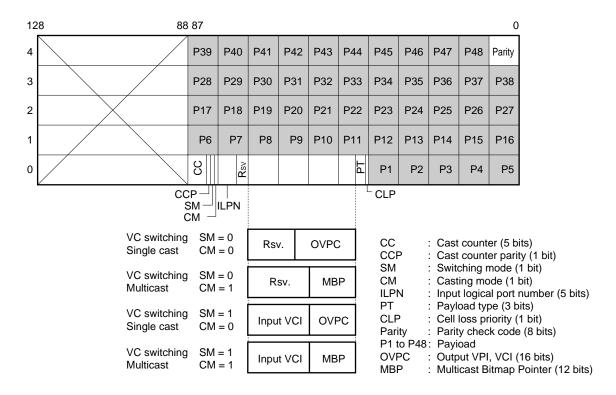

| 3-54             | Cell Buffer Storage Format                                         | 120  |

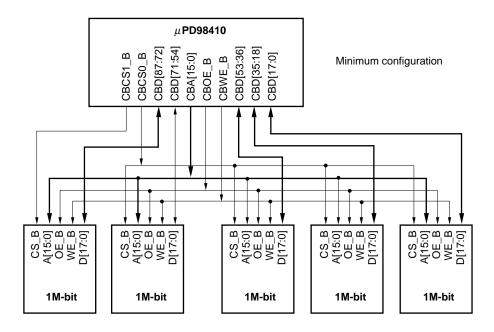

| 3-55             | Example of Connecting Cell Buffer Memory                           | 121  |

| 5-1              | Block Diagram of Boundary Scan Circuit                             | 174  |

| 5-2              | State Transition of TAP Controller                                 | 176  |

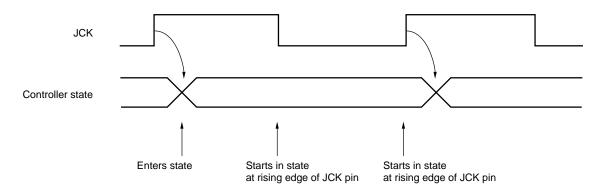

| 5-3              | Operation Timing in Controller State                               | 177  |

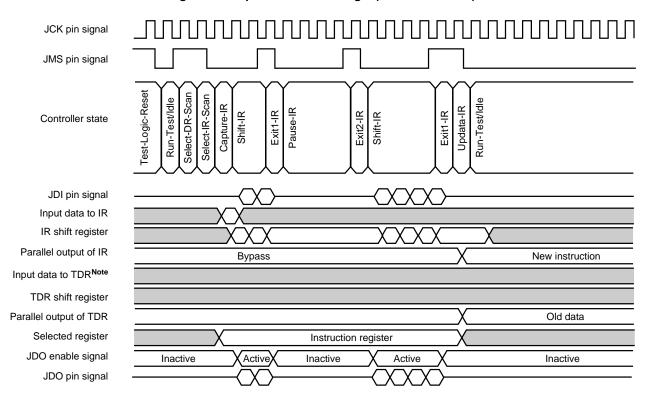

| 5-4              | Operation of Test Logic (instruction scan)                         | 182  |

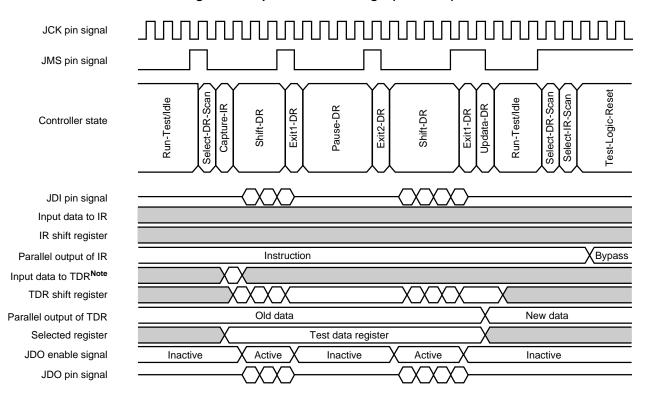

| 5-5              | Operation of Test Logic (data scan)                                | 183  |

| 7-1              | Header Translation Flow (overall)                                  | 203  |

| 7-2              | Header Translation Flow (reception side)                           | 204  |

| 7-3              | Header Translation Flow (transmission side)                        | 205  |

| 7-4              | Example of Setting HT Registers                                    | 206  |

| 7-5              | Example of HTT Memory Mapping                                      | 207  |

# LIST OF TABLES

| Table. No. Title |                                                                           |     |  |  |  |

|------------------|---------------------------------------------------------------------------|-----|--|--|--|

|                  |                                                                           |     |  |  |  |

| 2-1              | Receive Interface Signals                                                 |     |  |  |  |

| 2-2              | Transmit Interface Signal                                                 |     |  |  |  |

| 2-3              | HTT & Control Memory Interface Signals                                    |     |  |  |  |

| 2-4              | Cell Buffer Memory Interface Signals                                      | 33  |  |  |  |

| 2-5              | Microprocessor Interface                                                  | 34  |  |  |  |

| 2-6              | 32-Bit Multiplexed Synchronous Interface                                  | 34  |  |  |  |

| 2-7              | 16-Bit Separated Asynchronous Interface                                   | 35  |  |  |  |

| 2-8              | JTAG Interface Signals                                                    | 36  |  |  |  |

| 2-9              | Other Interface Signals                                                   | 36  |  |  |  |

| 2-10             | Recommended Connections of Unused Pins                                    | 37  |  |  |  |

| 2-11             | Pin Status at Reset                                                       | 38  |  |  |  |

| 3-1              | Maximum Transfer Rate and UTOPIA Clock Rate                               | 39  |  |  |  |

| 3-2              | Cell Discard Threshold Value Related to Total Number of Cells             | 81  |  |  |  |

| 3-3              | Cell Discard Threshold Value of Output Queue Length                       | 81  |  |  |  |

| 3-4              | Cell Discard Threshold Values Related to Multi-Cast Queue Length          | 82  |  |  |  |

| 3-5              | Minimum Queue Length Related to Total Number of Cells (Used Cell Counter) | 85  |  |  |  |

| 3-6              | Minimum Queue Length Related to Total Number of Cells of Each Class       |     |  |  |  |

|                  | (Total Cell Counter for each class)                                       | 85  |  |  |  |

| 3-7              | Minimum Queue Length Related to Output Queue Length                       | 86  |  |  |  |

| 3-8              | Minimum Queue Length Related to Multi-Cast Queue                          | 86  |  |  |  |

| 3-9              | Classification and Names of Threshold Values                              | 87  |  |  |  |

| 3-10             | EFCI Threshold Value Related to Output Queue                              | 88  |  |  |  |

| 3-11             | CI Threshold Values Related to Output Queue Length                        | 89  |  |  |  |

| 3-12             | PHY Device Connected and Mode Setting of μPD98410                         | 99  |  |  |  |

| 3-13             | Microprocessor Interface Pin                                              | 109 |  |  |  |

| 3-14             | Selecting Subject to Access                                               | 110 |  |  |  |

| 3-15             | Access Bit Width for Each Access Type                                     | 110 |  |  |  |

| 5-1              | Operation in Each Controller State                                        | 181 |  |  |  |

[MEMO]

Phase-out/Discontinued

# **CHAPTER 1 GENERAL**

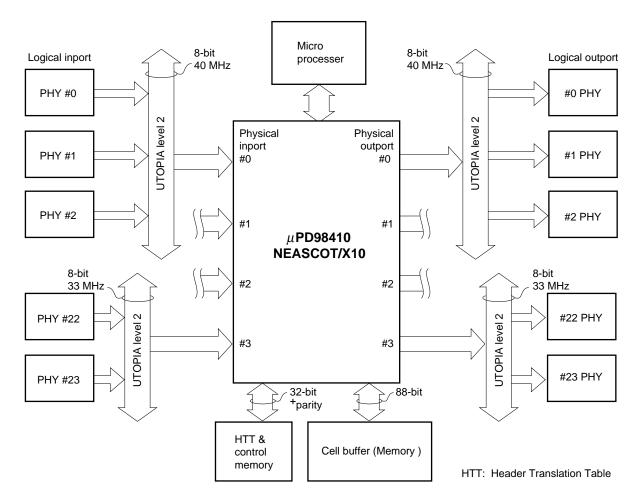

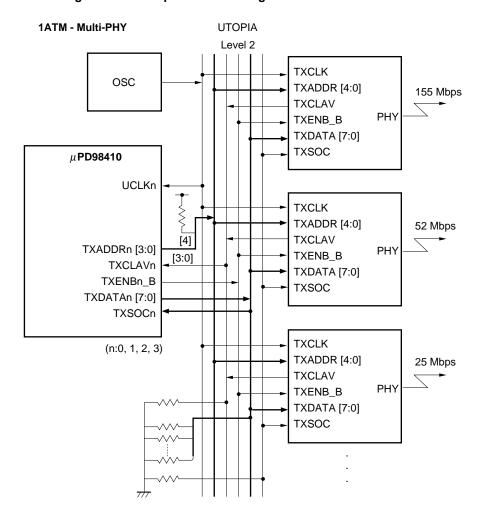

The  $\mu$ PD98410 (NEASCOT-X10) is an LSI integrating ATM switch functions on a single chip. It has four UTOPIA Level2 interfaces and can switch 24  $\times$  24 circuits by connecting multiple PHY devices. This LSI employs a shared buffer non-blocking type switch and realizes a switch capacity of 1.2G bps by using an externally connected SRAM for buffering cells.

#### 1.1 Features

- Conforms to ATM FORUM UNI Version 3.1 & 4.0

- · Realizes all switch functions with a single chip

- · Non-blocking type with switch capacity of 1.2G bps

- Can switch 24 logical ports via four UTOPIA Level2 (8 bits/40 MHz) interfaces

- Multi-speed (155M bps, 52M bps, 25M bps, etc.)

- Supports 16K/32K/64K VP/VC and 1K/2K/4K multi-cast VP/VC

- · Shared buffer architecture using standard SRAM

- Cell buffer capacity: 12.8K/25.6K/51.2K cells

- Supports four QOS classes (CBR, VBR, ABR, UBR)

- ABR traffic control (binary mode)

- Supports EPD (Early Packet Discard) and PPD (Partial Packet Discard)

- +3.3-V single power source (directly connectable with +5-V TTL level signals)

- Test function: Supports JTAG (IEEE 1149.1)

#### 1.2 Ordering Information

| Part Number   | Package                          |

|---------------|----------------------------------|

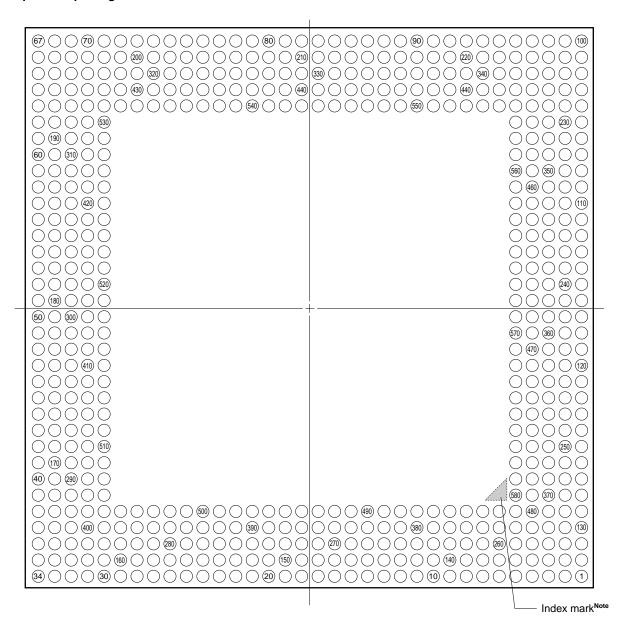

| μPD98410S2-K6 | 580-pin plastic BGA (45 × 45 mm) |

# 1.3 Example of System Configuration (Application)

The  $\mu$ PD98410 can be used to realize an ATM layer cell switching function by connecting it to a microprocessor, SRAM for use as a cell buffer, and a header translation table (HTT)/SRAM for storing control information as shown below.

## 1.4 Block Diagram

#### 1.5 Pin Configuration

# **CHAPTER 2 PIN FUNCTIONS**

#### 2.1 Pin Configuration (Bottom View)

#### 580-pin BGA package

**Note** The index mark is shown in Top View.

#### Pin name

(1) Power (4) CPU Interface

VDD

: Supply Voltage

HSEL

: Host Bus Mode Select

GND

: Ground

IOCS\_B

: I/O Chip Select

MCS\_B

: Memory Chip Select

(2) UTOPIA RDY\_B, RDY: I/O Ready, Memory Ready

RXADDR\*3 - RXADDR\*0 : Receive Address INT : Interrupt Request RXDATA\*7 - RXDATA\*0 : Receive Data Bus HCLK : Host Clock

RXSOC3 - RXSOC0 : Receive Start of Cell AD31 - AD0 : Address and Data

RXENB3\_B - RXENB0\_B: Receive Enable Data Transfers R/W\_B : Read/Write

RXCLAV3 - RXCLAV0 : Receive Cell Buffer Available UWE\_B : Upper Word Enable

UCLK3 - UCLK0 : UTOPIA Clock A15 - A0 : Address TXADDR\*3 - TXADDR\*0 : Transmit Address D15 - D0 : Data

TXDATA\*7 - TXDATA\*0 : Transmit Data Bus WR\_B : Write Strobe

TXSOC3 - TXSOC0 : Transmit Start of Cell RD\_B : Read Strobe

TXENB3\_B - TXENB0\_B: Transmit Enable Data

TXCLAV3 - TXCLAV0 : Transmit Cell Buffer Available (5) JTAG

JDI : JTAG Data Input

3) Memory Interface JDO : JTAG Data Output

(3) Memory Interface JDO : JTAG Data Output HTA17 - HTA0 : HTT Memory Address JCK : JTAG Data Clock HTD31 - HTD0 : HTT Memory Data Bus JMS : JTAG Mode Select

HTP3 - HTP0 : HTT Memory Data Bus Parity JRST\_B : JTAG Reset

HTCS1\_B, HTCS0\_B: HTT Memory Chip Select

HTWE\_B : HTT Memory Write Enable (6) Other

HTOE\_B : HTT Memory Output Enable SWCLK : System Clock

CBA17 - CBA0 : Cell Buffer Memory Address RESET\_B : Hardware Reset

CBD87 - CBD0 : Cell Buffer Memory Data Bus IC : Internal Connected

CBCS1\_B, CBCS0\_B: Cell Buffer Memory Chip Select CG : Connect Ground

CBWE\_B : Cell Buffer Memory Write Enable PU : Pull-up

CBOE\_B : Cell Buffer Memory Output Enable

$<sup>* = 0 \</sup>text{ to } 3$

# 2.2 Pin Layout

(1/6)

| J       |                 |     |         |                 |     |         |                 | (1/6) |

|---------|-----------------|-----|---------|-----------------|-----|---------|-----------------|-------|

| Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O   |

| 1       | GND             |     | 37      | CBD72           | I/O | 73      | RXDATA05        | I     |

| 2       | GND             |     | 38      | CBD69           | I/O | 74      | V <sub>DD</sub> |       |

| 3       | IC              | 0   | 39      | CBD66           | I/O | 75      | GND             |       |

| 4       | IC              | 0   | 40      | CBD63           | I/O | 76      | RXCLAV0         | I     |

| 5       | CG              | I   | 41      | IC              | 0   | 77      | V <sub>DD</sub> |       |

| 6       | IC              | 0   | 42      | CBD58           | I/O | 78      | TXADDR01        | 0     |

| 7       | JRST_B          | 1   | 43      | CBD56           | I/O | 79      | TXENB0_B        | 0     |

| 8       | RXDATA36        | I   | 44      | CBD51           | I/O | 80      | TXDATA04        | 0     |

| 9       | RXDATA32        | I   | 45      | CBD49           | I/O | 81      | TXDATA00        | 0     |

| 10      | IC              | 0   | 46      | CBD46           | I/O | 82      | RXDATA26        | I     |

| 11      | RXSOC3          | I   | 47      | CBWE_B          | 0   | 83      | V <sub>DD</sub> |       |

| 12      | RXADDR31        | 0   | 48      | CBA17           | 0   | 84      | RXDATA25        | I     |

| 13      | TXADDR31        | 0   | 49      | GND             |     | 85      | GND             |       |

| 14      | TXENB3_B        | 0   | 50      | CBA13           | 0   | 86      | GND             |       |

| 15      | V <sub>DD</sub> |     | 51      | IC              | 0   | 87      | RXCLAV2         | I     |

| 16      | TXDATA32        | 0   | 52      | CBA9            | 0   | 88      | RXADDR21        | 0     |

| 17      | TXDATA30        | 0   | 53      | CBA7            | 0   | 89      | TXADDR21        | 0     |

| 18      | TXDATA31        | 0   | 54      | CBA4            | 0   | 90      | TXCLAV2         | I     |

| 19      | RXDATA17        | I   | 55      | CBA0            | 0   | 91      | GND             |       |

| 20      | RXDATA13        | I   | 56      | CBD41           | I/O | 92      | TXDATA23        | 0     |

| 21      | RXDATA10        | I   | 57      | CBD37           | I/O | 93      | TXDATA20        | 0     |

| 22      | RXENB1_B        | 0   | 58      | CBD35           | I/O | 94      | IOCS_B          | I     |

| 23      | V <sub>DD</sub> |     | 59      | CBD30           | I/O | 95      | RDY_B/RDY       | 0     |

| 24      | RXADDR10        | 0   | 60      | V <sub>DD</sub> |     | 96      | CG              | I     |

| 25      | GND             |     | 61      | CBD24           | I/O | 97      | CG              | 1     |

| 26      | V <sub>DD</sub> |     | 62      | CBD20           | I/O | 98      | IC              | 0     |

| 27      | TXDATA15        | 0   | 63      | CBD17           | I/O | 99      | GND             |       |

| 28      | TXDATA11        | 0   | 64      | CBD15           | I/O | 100     | GND             |       |

| 29      | CBD86           | I/O | 65      | GND             |     | 101     | GND             |       |

| 30      | CBD84           | I/O | 66      | GND             |     | 102     | IC              | 0     |

| 31      | CBD80           | I/O | 67      | GND             |     | 103     | VDD             |       |

| 32      | V <sub>DD</sub> |     | 68      | GND             |     | 104     | AD18/A2         | I/O   |

| 33      | GND             |     | 69      | CBD10           | I/O | 105     | AD14/D14        | I/O   |

| 34      | GND             |     | 70      | CBD7            | I/O | 106     | AD10/D10        | I/O   |

| 35      | GND             |     | 71      | CBD4            | I/O | 107     | AD6/D6          | I/O   |

| 36      | CBD74           | I/O | 72      | CBD2            | I/O | 108     | AD3/D3          | I/O   |

|         |                 |     |         |                 |     |         |                 |       |

(2/6)

|         |                 |     |         |                 |     |         |                 | (2/6) |

|---------|-----------------|-----|---------|-----------------|-----|---------|-----------------|-------|

| Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O   |

| 109     | AD1/D1          | I/O | 146     | TXDATA36        | 0   | 183     | CBA2            | 0     |

| 110     | HTA14           | 0   | 147     | TXDATA33        | 0   | 184     | CBD42           | I/O   |

| 111     | V <sub>DD</sub> |     | 148     | TXDATA34        | 0   | 185     | CBD38           | I/O   |

| 112     | HTA9            | 0   | 149     | GND             |     | 186     | V <sub>DD</sub> |       |

| 113     | $V_{DD}$        |     | 150     | RXDATA15        | I   | 187     | CBD33           | I/O   |

| 114     | GND             |     | 151     | RXDATA12        | I   | 188     | CBD28           | I/O   |

| 115     | HTCS1_B         | 0   | 152     | V <sub>DD</sub> |     | 189     | CBD26           | I/O   |

| 116     | GND             |     | 153     | RXCLAV1         | I   | 190     | CBD23           | I/O   |

| 117     | HTCS0_B         | 0   | 154     | RXADDR11        | 0   | 191     | GND             |       |

| 118     | VDD             |     | 155     | TXADDR12        | 0   | 192     | VDD             |       |

| 119     | HTD29           | I/O | 156     | TXCLAV1         | I   | 193     | CBD13           | I/O   |

| 120     | HTD26           | I/O | 157     | TXDATA17        | 0   | 194     | CBD12           | I/O   |

| 121     | HTD23           | I/O | 158     | TXDATA13        | 0   | 195     | GND             |       |

| 122     | HTD20           | I/O | 159     | TXDATA10        | 0   | 196     | CBD9            | I/O   |

| 123     | HTD16           | I/O | 160     | V <sub>DD</sub> |     | 197     | CBD8            | I/O   |

| 124     | HTD15           | I/O | 161     | CBD82           | I/O | 198     | IC              | 0     |

| 125     | HTD10           | I/O | 162     | CBD78           | I/O | 199     | V <sub>DD</sub> |       |

| 126     | V <sub>DD</sub> |     | 163     | CBD77           | I/O | 200     | RXDATA06        | I     |

| 127     | HTD5            | I/O | 164     | GND             |     | 201     | RXDATA03        | I     |

| 128     | HTD2            | I/O | 165     | CBD76           | I/O | 202     | RXDATA01        | I     |

| 129     | SWCLK           | I   | 166     | CBD73           | I/O | 203     | RXSOC0          | I     |

| 130     | V <sub>DD</sub> |     | 167     | V <sub>DD</sub> |     | 204     | RXADDR02        | 0     |

| 131     | GND             |     | 168     | CBD67           | I/O | 205     | TXADDR03        | 0     |

| 132     | GND             |     | 169     | IC              | 0   | 206     | TXCLAV0         | I     |

| 133     | GND             |     | 170     | CBD62           | I/O | 207     | TXDATA06        | 0     |

| 134     | CG              | 1   | 171     | CBD59           | I/O | 208     | TXDATA02        | 0     |

| 135     | CG              | I   | 172     | CBD57           | I/O | 209     | V <sub>DD</sub> |       |

| 136     | IC              | 0   | 173     | CBD53           | I/O | 210     | RXDATA27        | I     |

| 137     | V <sub>DD</sub> |     | 174     | V <sub>DD</sub> |     | 211     | RXDATA23        | I     |

| 138     | GND             |     | 175     | GND             |     | 212     | RXDATA21        | I     |

| 139     | V <sub>DD</sub> |     | 176     | CBCS1_B         | 0   | 213     | RXENB2_B        | 0     |

| 140     | RXDATA34        | I   | 177     | V <sub>DD</sub> |     | 214     | RXADDR23        | 0     |

| 141     | RXDATA30        | I   | 178     | CBA15           | 0   | 215     | TXADDR23        | 0     |

| 142     | V <sub>DD</sub> |     | 179     | CBOE_B          | 0   | 216     | TXADDR20        | 0     |

| 143     | RXADDR33        | 0   | 180     | CBA11           | 0   | 217     | TXENB2_B        | 0     |

| 144     | TXADDR33        | 0   | 181     | V <sub>DD</sub> |     | 218     | TXDATA25        | 0     |

| 145     | TXCLAV3         | I   | 182     | CBA6            | 0   | 219     | TXDATA22        | 0     |

# CHAPTER 2 PIN FUNCTIONS Phase-out/Discontinued

(3/6)

|         | I               |     | I       | 1               |     | 1       | T               | (3/6) |

|---------|-----------------|-----|---------|-----------------|-----|---------|-----------------|-------|

| Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O   |

| 220     | HCLK            | I   | 256     | IC              | I/O | 293     | V <sub>DD</sub> |       |

| 221     | MCS_B           | I   | 257     | IC              | I/O | 294     | CBD54           | I/O   |

| 222     | R/W_B/          | 1   | 258     | GND             |     | 295     | CBD52           | I/O   |

|         | WR_B            |     | 259     | GND             |     | 296     | CBD48           | I/O   |

| 223     | AD31/A15        | I/O | 260     | JDI             | 1   | 297     | CBD47           | I/O   |

| 224     | AD28/A12        | I/O | 261     | JCK             | 1   | 298     | CBD45           | I/O   |

| 225     | AD27/A11        | I/O | 262     | RXDATA37        | 1   | 299     | CBCS0_B         | 0     |

| 226     | GND             |     | 263     | RXDATA33        | 1   | 300     | CBA16           | 0     |

| 227     | AD25/A9         | I/O | 264     | RXDATA31        | I   | 301     | CBA12           | 0     |

| 228     | AD22/A6         | I/O | 265     | RXENB3_B        | 0   | 302     | CBA10           | 0     |

| 229     | AD20/A4         | I/O | 266     | RXADDR32        | 0   | 303     | CBA5            | 0     |

| 230     | AD16/A0         | I/O | 267     | RXADDR30        | 0   | 304     | GND             |       |

| 231     | AD12/D12        | I/O | 268     | TXADDR32        | 0   | 305     | CBA1            | 0     |

| 232     | AD8/D8          | I/O | 269     | TXSOC3          | 0   | 306     | GND             |       |

| 233     | $V_{DD}$        |     | 270     | TXDATA37        | 0   | 307     | CBD39           | I/O   |

| 234     | AD2/D2          | I/O | 271     | V <sub>DD</sub> |     | 308     | CBD34           | I/O   |

| 235     | GND             |     | 272     | RXDATA14        | 1   | 309     | GND             |       |

| 236     | HTA12           | 0   | 273     | GND             |     | 310     | CBD29           | I/O   |

| 237     | GND             |     | 274     | RXDATA11        | 1   | 311     | CBD25           | I/O   |

| 238     | HTA6            | 0   | 275     | IC              | 0   | 312     | CBD21           | I/O   |

| 239     | HTA4            | 0   | 276     | RXSOC1          | 1   | 313     | CBD18           | I/O   |

| 240     | HTA1            | 0   | 277     | RXADDR13        | 0   | 314     | CBD14           | I/O   |

| 241     | HTA3            | 0   | 278     | TXADDR13        | 0   | 315     | CBD11           | I/O   |

| 242     | HTOE_B          | 0   | 279     | TXADDR10        | 0   | 316     | GND             |       |

| 243     | HTD31           | I/O | 280     | TXENB1_B        | 0   | 317     | CBD5            | I/O   |

| 244     | HTD28           | I/O | 281     | TXDATA14        | 0   | 318     | CBD1            | I/O   |

| 245     | HTD24           | I/O | 282     | TXDATA12        | 0   | 319     | RXDATA07        | I     |

| 246     | GND             |     | 283     | CBD85           | I/O | 320     | RXDATA04        | I     |

| 247     | HTD17           | I/O | 284     | GND             |     | 321     | RXDATA00        | I     |

| 248     | V <sub>DD</sub> |     | 285     | CBD79           | I/O | 322     | RXENB0_B        | 0     |

| 249     | NTD13           | I/O | 286     | GND             |     | 323     | RXADDR01        | 0     |

| 250     | HTD8            | I/O | 287     | V <sub>DD</sub> |     | 324     | TXADDR02        | 0     |

| 251     | HTD7            | I/O | 288     | CBD70           | I/O | 325     | TXADDR00        | 0     |

| 252     | HTD4            | I/O | 289     | CBD68           | I/O | 326     | TXSOC0          | 0     |

| 253     | HTD0            | I/O | 290     | CBD65           | I/O | 327     | TXDATA05        | 0     |

| 254     | RESET_B         | I   | 291     | GND             |     | 328     | TXDATA03        | 0     |

| 255     | IC              | I/O | 292     | GND             |     | 329     | RXDATA24        | I     |

(4/6)

|         |                 |     |         |                 |     |         |                 | (4/6) |

|---------|-----------------|-----|---------|-----------------|-----|---------|-----------------|-------|

| Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O   |

| 330     | RXDATA20        | 1   | 368     | HTD9            | I/O | 406     | CBD60           | I/O   |

| 331     | UCLK2           | 1   | 369     | HTD6            | I/O | 407     | CBD55           | I/O   |

| 332     | RXSOC2          | I   | 370     | GND             |     | 408     | GND             |       |

| 333     | RXADDR22        | 0   | 371     | V <sub>DD</sub> |     | 409     | CBD50           | I/O   |

| 334     | GND             |     | 372     | IC              | I/O | 410     | V <sub>DD</sub> |       |

| 335     | TXADDR22        | 0   | 373     | IC              | 0   | 411     | CBD44           | I/O   |

| 336     | TXSOC2          | 0   | 374     | V <sub>DD</sub> |     | 412     | V <sub>DD</sub> |       |

| 337     | TXDATA26        | 0   | 375     | CG              | 1   | 413     | CBA14           | 0     |

| 338     | V <sub>DD</sub> |     | 376     | JDO             | 0   | 414     | V <sub>DD</sub> |       |

| 339     | VDD             |     | 377     | JMS             | I   | 415     | CBA8            | 0     |

| 340     | HSEL            | I   | 378     | RXDATA35        | 1   | 416     | V <sub>DD</sub> |       |

| 341     | VDD             |     | 379     | GND             |     | 417     | CBA3            | 0     |

| 342     | AD30/A14        | I/O | 380     | UCLK3           | 1   | 418     | CBD43           | I/O   |

| 343     | AD29/A13        | I/O | 381     | RXCLAV3         | 1   | 419     | CBD40           | I/O   |

| 344     | AD26/A10        | I/O | 382     | GND             |     | 420     | CBD36           | I/O   |

| 345     | AD23/A7         | I/O | 383     | TXADDR30        | 0   | 421     | CBD32           | I/O   |

| 346     | AD19/A3         | I/O | 384     | V <sub>DD</sub> |     | 422     | CBD31           | I/O   |

| 347     | GND             |     | 385     | TXDATA35        | 0   | 423     | CBD27           | I/O   |

| 348     | AD13/D13        | I/O | 386     | V <sub>DD</sub> |     | 424     | CBD22           | I/O   |

| 349     | AD09/D09        | I/O | 387     | RXDATA16        | 1   | 425     | CBD19           | I/O   |

| 350     | AD7/D7          | I/O | 388     | V <sub>DD</sub> |     | 426     | CBD16           | I/O   |

| 351     | AD4/D4          | I/O | 389     | UCLK1           | I   | 427     | IC              | 0     |

| 352     | HTA17           | 0   | 390     | V <sub>DD</sub> |     | 428     | CBD6            | I/O   |

| 353     | HTA15           | 0   | 391     | GND             |     | 429     | CBD3            | I/O   |

| 354     | HTA11           | 0   | 392     | RXADDR12        | 0   | 430     | CBD0            | I/O   |

| 355     | HTA10           | 0   | 393     | TXADDR11        | 0   | 431     | GND             |       |

| 356     | HTA8            | 0   | 394     | TXSOC1          | 0   | 432     | RXDATA02        | I     |

| 357     | HTA5            | 0   | 395     | TXDATA16        | 0   | 433     | UCLK0           | I     |

| 358     | HTA2            | 0   | 396     | GND             |     | 434     | RXADDR03        | 0     |

| 359     | HTWE_B          | 0   | 397     | CBD87           | I/O | 435     | RXADDR00        | 0     |

| 360     | HTP3            | I/O | 398     | CBD83           | I/O | 436     | GND             |       |

| 361     | HTD27           | I/O | 399     | CBD81           | I/O | 437     | TXDATA07        | 0     |

| 362     | GND             |     | 400     | CBD75           | I/O | 438     | V <sub>DD</sub> |       |

| 363     | HTP2            | I/O | 401     | CBD71           | I/O | 439     | TXDATA01        | 0     |

| 364     | HTD21           | I/O | 402     | GND             |     | 440     | VDD             |       |

| 365     | HTD18           | I/O | 403     | IC              | 0   | 441     | RXDATA22        | I     |

| 366     | HTD14           | I/O | 404     | CBD64           | I/O | 442     | VDD             |       |

| 367     | HTD11           | I/O | 405     | CBD61           | I/O | 443     | V <sub>DD</sub> |       |

# CHAPTER 2 PIN FUNCTIONS Phase-out/Discontinued

(5/6)

| Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | (5/6) |

|---------|-----------------|-----|---------|-----------------|-----|---------|-----------------|-------|

| 444     | V <sub>DD</sub> |     | 481     | V <sub>DD</sub> |     | 518     | GND             |       |

| 445     | RXADDR20        | 0   | 482     | GND             |     | 519     | V <sub>DD</sub> |       |

| 446     | V <sub>DD</sub> |     | 483     | V <sub>DD</sub> |     | 520     | GND             |       |

| 447     | TXDATA27        | 0   | 484     | GND             |     | 521     | V <sub>DD</sub> |       |

| 448     | TXDATA24        | 0   | 485     | V <sub>DD</sub> |     | 522     | GND             |       |

| 449     | TXDATA21        | 0   | 486     | GND             |     | 523     | V <sub>DD</sub> |       |

| 450     | GND             |     | 487     | V <sub>DD</sub> |     | 524     | GND             |       |

| 451     | INT             | 0   | 488     | GND             |     | 525     | V <sub>DD</sub> |       |

| 452     | UWE_B/RD_B      | I   | 489     | V <sub>DD</sub> |     | 526     | GND             |       |

| 453     | GND             |     | 490     | GND             |     | 527     | VDD             |       |

| 454     | AD24/A8         | I/O | 491     | V <sub>DD</sub> |     | 528     | GND             |       |

| 455     | AD21/A5         | I/O | 492     | GND             |     | 529     | VDD             |       |

| 456     | AD17/A1         | I/O | 493     | V <sub>DD</sub> |     | 530     | GND             |       |

| 457     | AD15/D15        | I/O | 494     | GND             |     | 531     | V <sub>DD</sub> |       |

| 458     | AD11/D11        | I/O | 495     | V <sub>DD</sub> |     | 532     | GND             |       |

| 459     | GND             |     | 496     | GND             |     | 533     | V <sub>DD</sub> |       |

| 460     | AD5/D5          | I/O | 497     | V <sub>DD</sub> |     | 534     | GND             |       |

| 461     | AD0/D0          | I/O | 498     | GND             |     | 535     | V <sub>DD</sub> |       |

| 462     | HTA16           | 0   | 499     | V <sub>DD</sub> |     | 536     | GND             |       |

| 463     | HTA13           | 0   | 500     | GND             |     | 537     | V <sub>DD</sub> |       |

| 464     | V <sub>DD</sub> |     | 501     | V <sub>DD</sub> |     | 538     | GND             |       |

| 465     | HTA7            | 0   | 502     | GND             |     | 539     | V <sub>DD</sub> |       |

| 466     | V <sub>DD</sub> |     | 503     | V <sub>DD</sub> |     | 540     | GND             |       |

| 467     | HTA0            | 0   | 504     | GND             |     | 541     | V <sub>DD</sub> |       |

| 468     | V <sub>DD</sub> |     | 505     | V <sub>DD</sub> |     | 542     | GND             |       |

| 469     | HTD30           | I/O | 506     | GND             |     | 543     | V <sub>DD</sub> |       |

| 470     | V <sub>DD</sub> |     | 507     | V <sub>DD</sub> |     | 544     | GND             |       |

| 471     | HTD25           | I/O | 508     | GND             |     | 545     | V <sub>DD</sub> |       |

| 472     | HTD22           | I/O | 509     | V <sub>DD</sub> |     | 546     | GND             |       |

| 473     | HTD19           | I/O | 510     | GND             |     | 547     | V <sub>DD</sub> |       |

| 474     | HTP1            | I/O | 511     | V <sub>DD</sub> |     | 548     | GND             |       |

| 475     | HTD12           | I/O | 512     | GND             |     | 549     | V <sub>DD</sub> |       |

| 476     | GND             |     | 513     | V <sub>DD</sub> |     | 550     | GND             |       |

| 477     | HTP0            | I/O | 514     | GND             |     | 551     | V <sub>DD</sub> |       |

| 478     | HTD3            | I/O | 515     | VDD             |     | 552     | GND             |       |

| 479     | HTD1            | I/O | 516     | GND             |     | 553     | V <sub>DD</sub> |       |

| 480     | PU              | I   | 517     | VDD             |     | 554     | GND             |       |

#### **CHAPTER 2 PIN FUNCTIONS**

(6/6)

| Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O | Pin No. | Pin Name        | I/O |

|---------|-----------------|-----|---------|-----------------|-----|---------|-----------------|-----|

| 555     | V <sub>DD</sub> |     | 564     | GND             |     | 573     | V <sub>DD</sub> |     |

| 556     | GND             |     | 565     | V <sub>DD</sub> |     | 574     | GND             |     |

| 557     | V <sub>DD</sub> |     | 566     | GND             |     | 575     | V <sub>DD</sub> |     |

| 558     | GND             |     | 567     | V <sub>DD</sub> |     | 576     | GND             |     |

| 559     | $V_{DD}$        |     | 568     | GND             |     | 577     | $V_{DD}$        |     |

| 560     | GND             |     | 569     | V <sub>DD</sub> |     | 578     | GND             |     |

| 561     | $V_{DD}$        |     | 570     | GND             |     | 579     | $V_{DD}$        |     |

| 562     | GND             |     | 571     | V <sub>DD</sub> |     | 580     | GND             |     |

| 563     | V <sub>DD</sub> |     | 572     | GND             |     |         |                 |     |

## 2.3 Pin Functions

Although the  $\mu$ PD98410 is a device operating at 3.3 V, it can be directly connected to a PHY device, CPU, and memory with a 5-V TTL interface.

# 2.3.1 Power supply

| Pin Name | Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O | Function                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------|

| VDD      | 15, 23, 26, 32, 60, 74, 77, 83, 103, 111, 113, 118, 126, 130, 137, 139, 142, 152, 160, 167, 174, 177, 181, 186, 192, 199, 209, 233, 248, 271, 287, 293, 338, 339, 341, 371, 374, 384, 386, 388, 390, 410, 412, 414, 416, 438, 440, 442, 443, 444, 446, 464, 466, 468, 470, 481, 483, 485, 487, 489, 491, 493, 495, 497, 499, 501, 503, 505, 507, 509, 511, 513, 515, 517, 519, 521, 523, 525, 527, 529, 531, 533, 535, 537, 539, 541, 543, 545, 547, 549, 551, 553, 555, 557, 559, 561, 563, 565, 567, 569, 571, 573, 575, 577, 579                | _   | These pins supply a power of +3.3 V $\pm$ 5%. |

| GND      | 1, 2, 25, 33, 34, 35, 49, 65, 66, 67, 68, 75, 85, 86, 91, 99, 100, 101, 114, 116, 131, 132, 133, 138, 149, 164, 175, 191, 195, 226, 235, 237, 246, 258, 259, 273, 284, 286, 291, 292, 304, 306, 309, 316, 334, 347, 362, 370, 379, 382, 391, 396, 402, 408, 431, 436, 450, 453, 459, 476, 482, 484, 486, 488, 490, 492, 494, 496, 498, 500, 502, 504, 506, 508, 510, 512, 514, 516, 518, 520, 522, 524, 526, 528, 530, 532, 534, 536, 538, 540, 542, 544, 546, 548, 550, 552, 554, 556, 558, 560, 562, 564, 566, 568, 570, 572, 574, 576, 578, 580 | _   | These are ground pins.                        |

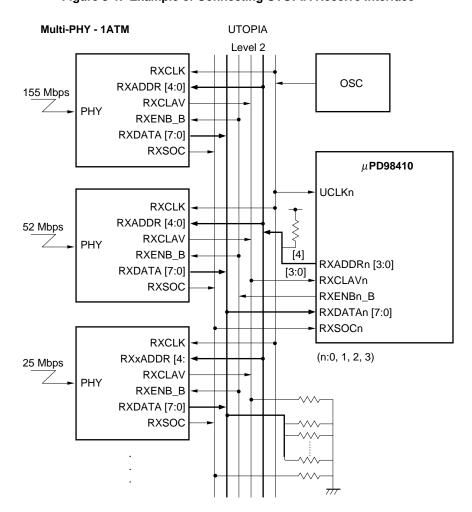

## 2.3.2 UTOPIA interface

The  $\mu$ PD98410 employs a UTOPIA Level2 (cell level transfer) interface between PHY layer and ATM layer. Tables 2-1 and 2-2 lists the interface signals.

Table 2-1. Receive Interface Signals (1/2)

| Symbol                 | Pin No.                                  | I/O | Function                                                                                                                                                                                          |

|------------------------|------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXADDR03 -<br>RXADDR00 | 434, 204, 323, 435                       | 0   | Multi-PHY select address of receive interface 0. RXADDR03 is the MSB.                                                                                                                             |

| RXDATA07 -<br>RXDATA00 | 319, 200, 73, 320, 201, 432,<br>202, 321 | I   | Cell data input of receive interface 0. Cell data is input from a PHY layer device in byte units. The $\mu$ PD98410 reads the data at the rising edge of UCLK0. RXDATA07 is the MSB.              |

| RXSOC0                 | 203                                      | I   | Cell transfer start signal of receive interface 0.  This signal is input from a PHY layer device in synchronization with the first byte of cell data.                                             |

| RXENB0_B               | 322                                      | 0   | Transfer enable signal of receive interface 0. This signal informs a PHY layer device that the $\mu$ PD98410 is ready for reception in the next clock cycle.                                      |

| RXCLAV0                | 76                                       | I   | Cell transfer enable signal of receive interface 0. This pin inputs a signal that indicates that no more cells will be supplied to the $\mu$ PD98410 after the current cell has been transferred. |

| UCLK0                  | 433                                      | I   | UTOPIA clock input of receive interface 0.  Data is transferred/received in synchronization with the rising edge of this clock.                                                                   |

| RXADDR13 -<br>RXADDR10 | 277, 392, 154, 24                        | 0   | Multi-PHY select address of receive interface 1. RXADDR13 is the MSB.                                                                                                                             |

| RXDATA17 -<br>RXDATA10 | 19, 387, 150, 272, 20, 151, 274, 21      | I   | Cell data input of receive interface 1. Cell data is input from a PHY layer device in byte units. The $\mu$ PD98410 reads the data at the rising edge of UCLK1. RXDATA17 is the MSB.              |

| RXSOC1                 | 276                                      | ı   | Cell transfer start signal of receive interface 1.  This signal is input from a PHY layer device in synchronization with the first byte of cell data.                                             |

| RXENB1_B               | 22                                       | 0   | Transfer enable signal of receive interface 1. This signal informs a PHY layer device that the $\mu$ PD98410 is ready for reception in the next clock cycle.                                      |

| RXCLAV1                | 153                                      | I   | Cell transfer enable signal of receive interface 1. This pin inputs a signal that indicates that no more cells will be supplied to the $\mu$ PD98410 after the current cell has been transferred. |

| UCLK1                  | 389                                      | I   | UTOPIA clock input of receive interface 1.  Data is transferred/received in synchronization with the rising edge of this clock.                                                                   |

# Table 2-1. Receive Interface Signals (2/2)

| Symbol                 | Pin No.                                 | I/O | Function                                                                                                                                                                                          |

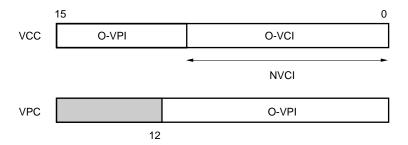

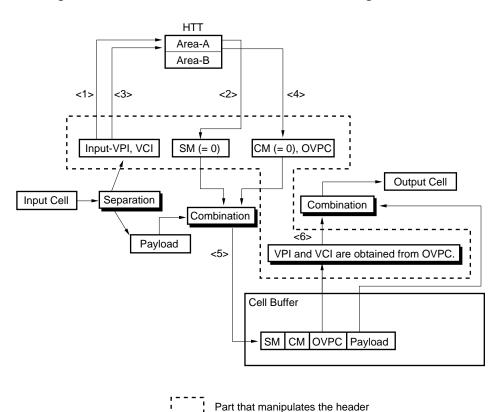

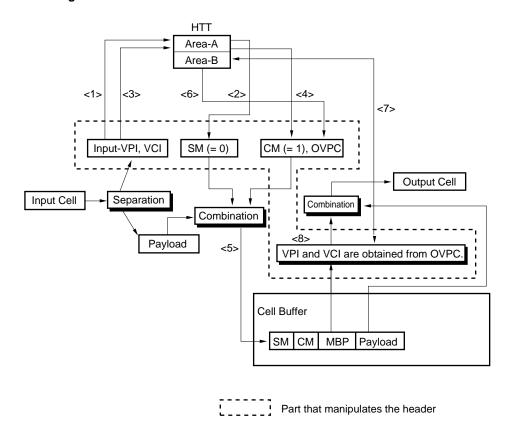

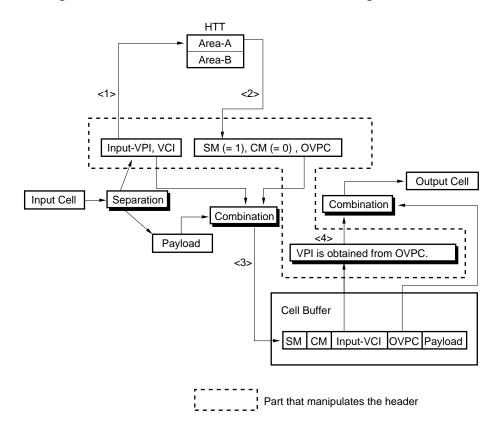

|------------------------|-----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|