# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

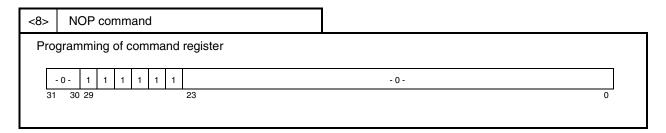

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

# **User's Manual**

# $\mu$ PD98401A

(NEASCOT-S15™)

**ATM SAR CHIP**

[MEMO]

#### NOTES FOR CMOS DEVICES

# (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# ③ STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

#### **NEASCOT-S15** is a trademark of NEC Corporation.

- The information in this document is current as of June, 2002. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data

books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products

and/or types are available in every country. Please check with an NEC sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

# **Major Revisions in this Edition**

| Page                                                            | Description |  |  |  |

|-----------------------------------------------------------------|-------------|--|--|--|

| p.26 Addition of Remark in <b>2.2.5 JTAG boundary scan pins</b> |             |  |  |  |

The mark ★ shows major revised points.

#### **PREFACE**

Readers This manual is intended for user engineers who wish to understand the functions of

the  $\mu$ PD98401A and design application systems using it.

Purpose This manual explains the hardware functions of the  $\mu$ PD98401A in the following

organization.

**Organization** This manual consists of the following chapters.

Overview

Pin function

· Functional outline

Interfaces

Operations of μPD98401A

Commands

· Internal registers

JTAG boundary scan

**How to Read This Manual**

It is assumed that the readers of this manual have a general knowledge of electricity, logic circuits, and microcomputers.

To understand the overall functions of the  $\mu$ PD98401A  $\rightarrow$  Read this manual in the order of Table of Contents.

For the electrical characteristics of the  $\mu$ PD98401A  $\rightarrow$  Refer to the Data Sheet separately available.

Legend Data significance : Left: high-order digit, right: low-order digit

Active low : xxx\_B (\_B following pin or signal name)

Memory map address : Top: high-order, bottom: low-order

Note : Explanation of part of text marked Note

Caution

: Important information

Remark

: Supplementary information

Numeric notation

: Binary ... xxxx or xxxB

Decimal ... ××××

$Hexadecimal \dots \times\!\!\times\!\!\times\!\! H$

**Related documents**

Some of the related documents are preliminary editions but are not so specified below.

Brochure: S11847EData sheet: S12100E

# **CONTENTS**

| CHAPTE | R 1 OVERVIEW                            | 14 |

|--------|-----------------------------------------|----|

| 1.1    | Features                                | 14 |

| 1.2    | Ordering Information                    | 14 |

| 1.3    | Example of System Configuration         | 15 |

| 1.4    | Block Diagram                           | 15 |

| 1.5    | Pin Configuration                       | 16 |

| CHAPTE | R 2 PIN FUNCTION                        | 17 |

| 2.1    | Pin Configuration (Top View)            | 17 |

| 2.2    | Pin Function                            | 19 |

|        | 2.2.1 PHY device interface pin          | 19 |

|        | 2.2.2 Bus interface pins                | 21 |

|        | 2.2.3 Bus monitor pins                  | 24 |

|        | 2.2.4 Control memory interface pins     | 25 |

|        | 2.2.5 JTAG boundary scan pins           | 26 |

|        | 2.2.6 Test pin                          | 27 |

|        | 2.2.7 Power supply and ground pins      | 27 |

|        | 2.2.8 Pin status during and after reset | 28 |

| СНАРТЕ | R 3 FUNCTIONAL OUTLINE                  | 29 |

| 3.1    | Functional Outline of µPD98401A         | 29 |

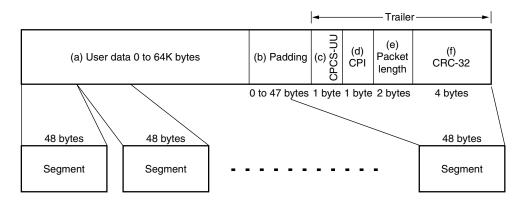

| 3.2    | AAL-5 SAR Sublayer Function             | 31 |

| 3.3    | ATM Layer Functions                     | 32 |

|        | 3.3.1 Creation of cells                 | 32 |

|        | 3.3.2 Setting of cell transmission rate | 35 |

|        | 3.3.3 Support of non-AAL-5 traffic      | 35 |

| CHAPTE | R 4 INTERFACES                          | 36 |

| 4.1    | Bus Interface                           | 36 |

|        | 4.1.1 Bus operation control pins        | 36 |

|        | 4.1.2 Parity check function             | 38 |

|        | 4.1.3 Master (DMA) operation            | 39 |

|        | 4.1.4 Slave operation                   | 56 |

|        | 4.1.5 Little/big endian select function | 60 |

| 4.2    | PHY Device Interface                    | 62 |

|        | 4.2.1 UTOPIA interface                  | 62 |

|        | 4.2.2 PHY device control interface      | 68 |

| 4.3    | Control Memory Interface                | 70 |

| 5.1   | Initialization                                              | 73              |

|-------|-------------------------------------------------------------|-----------------|

| 5.2   | Setting of Control Memory                                   | 7               |

| 5.3   | Setting of Mailbox                                          | 80              |

|       | 5.3.1 Setting of mailbox                                    | 8               |

|       | 5.3.2 Operation of mailbox                                  | 8               |

| 5.4   | Transmission Function                                       | 8               |

|       | 5.4.1 Transmission processing flow                          | 82              |

|       | 5.4.2 Structure of transmit data                            | 8               |

|       | 5.4.3 Transmit channel (transmit VC)                        | 90              |

|       | 5.4.4 Traffic Control                                       | 94              |

|       | 5.4.5 Transmission operation                                | 109             |

|       | 5.4.6 Support of non-AAL-5 traffic                          | 11              |

|       | 5.4.7 Issuance of transmit indication                       | 112             |

| 5.5   | Reception Function                                          | 11:             |

|       | 5.5.1 Reception processing flow                             | 110             |

|       | 5.5.2 Structure of receive data                             | 114             |

|       | 5.5.3 Receive channel (receive VC)                          | 119             |

|       | 5.5.4 Setting of receive look-up table                      |                 |

|       | 5.5.5 Reception operation                                   |                 |

|       | 5.5.6 Issuance of receive indication                        |                 |

|       | 5.5.7 Reception of non-AAL-5 traffic                        | 134             |

| 5.6   | Transmit/Receive Indication                                 |                 |

| 5.7   | Interrupt Function                                          |                 |

| 5.8   | Loopback Function                                           |                 |

| 5.9   | Global Shutdown Function                                    |                 |

| HAPTE | R 6 COMMANDS                                                | 14 <sup>-</sup> |

| 6.1   | Command Register (CMR) and Command Extension Register (CER) |                 |

| 6.2   | Busy Flag                                                   |                 |

| 6.3   | Commands Returning Command Indication                       |                 |

| 6.4   | Commands Using Command Extension Register                   |                 |

| 6.5   | Support of Multi-Host System (lock flag)                    |                 |

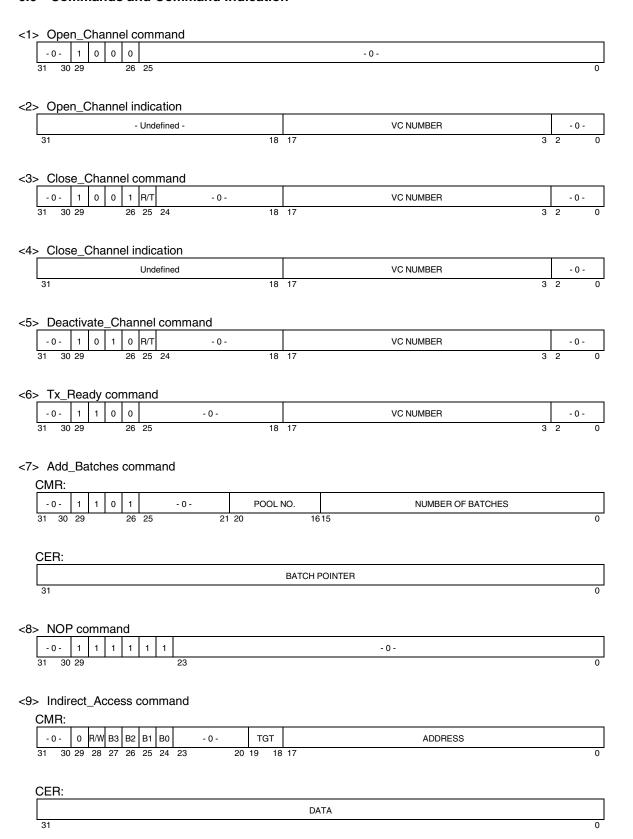

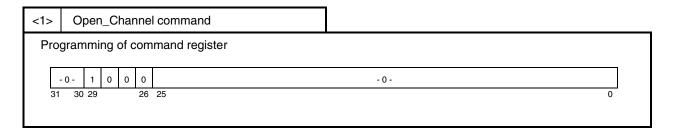

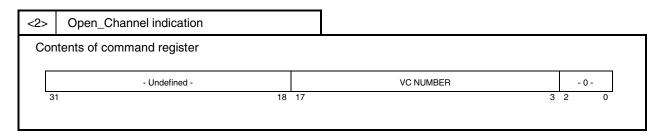

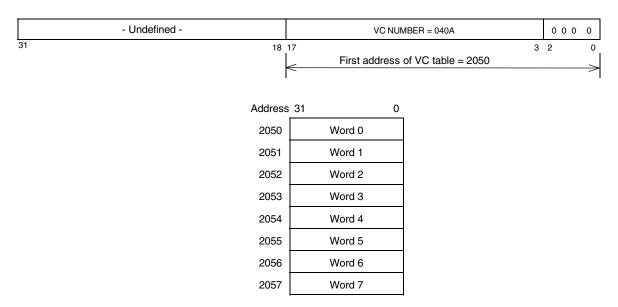

| 6.6   | Commands and Command Indication                             |                 |

|       | Command Details                                             |                 |

| 0.7   | Command Details                                             | 140             |

| HAPTE | R 7 INTERNAL REGISTERS                                      | 15              |

| 7.1   | Register List                                               |                 |

| 7.2   | Direct Address Registers                                    |                 |

| 7.3   | Indirect Address Registers                                  | 166             |

|       |                                                             |                 |

|       | R 8 JTAG BOUNDARY SCAN                                      | 170             |

| 8.2        | Inter  | nal Configuration of Boundary Scan Circuit | 171 |

|------------|--------|--------------------------------------------|-----|

|            | 8.2.1  | Instruction register                       | 171 |

|            | 8.2.2  | TAP (Test Access Port) controller          | 171 |

|            | 8.2.3  | Bypass register                            | 171 |

|            | 8.2.4  | Boundary scan register                     | 171 |

| 8.3        | Pin F  | unction                                    | 172 |

|            | 8.3.1  | JCK (JTAG Clock) pin                       | 172 |

|            | 8.3.2  | JMS (JTAG Mode Select) pin                 | 172 |

|            | 8.3.3  | JDI (JTAG Data Input) pin                  | 172 |

|            | 8.3.4  | JDO (JTAG Data Output) pin                 | 172 |

|            | 8.3.5  | JRST_B (JTAG Reset) pin                    | 172 |

| 8.4        | Oper   | ation Description                          | 173 |

|            | 8.4.1  | TAP controller                             | 173 |

|            | 8.4.2  | TAP controller state                       | 173 |

| 8.5        | TAP    | Controller Operation                       | 178 |

| 8.6        | Initia | lizing TAP Controller                      | 181 |

| 8.7        | Instru | uction Register                            | 181 |

|            | 8.7.1  | BYPASS instruction                         | 182 |

|            | 8.7.2  | EXTEST instruction                         | 182 |

|            | 8.7.3  | Boundary scan data bit definition          | 183 |

| APPEND     | IX A   | DIFFERENCES FROM μPD98401                  | 187 |

| <b>A.1</b> | Addit  | tional Functions                           | 187 |

| A.2        | Diffe  | rences                                     | 187 |

| APPEND     | ІХ В   | DESCRIPTOR/INDICATION LIST                 | 188 |

| APPEND     | іх с   | TRANSMIT/RECEIVE VC TABLE                  | 192 |

| ADDENID    | IV D   | COMMAND LIST                               | 104 |

# LIST OF FIGURES (1/3)

| Figure | No. Title                                                            | Page |

|--------|----------------------------------------------------------------------|------|

| 3-1    | Functions of μPD98401A                                               | 29   |

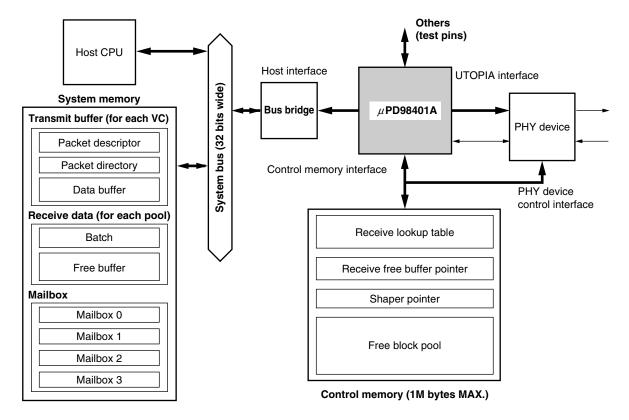

| 3-2    | System Outline of μPD98401A                                          | 30   |

| 3-3    | PDU Format of ALL-5                                                  | 31   |

| 3-4    | Cell Structure of User Network Interface (UNI)                       | 32   |

| 4-1    | Bus Interface Signals                                                | 36   |

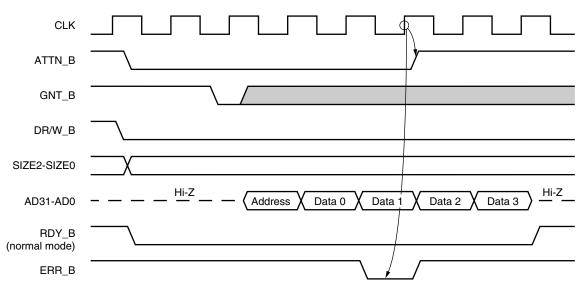

| 4-2    | Input Timing of ERR_B Signal (4-word burst)                          | 37   |

| 4-3    | Input Example of ERR_B Signal (4-word burst)                         | 37   |

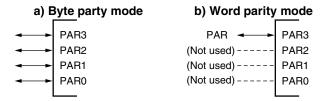

| 4-4    | Difference in Pins Used Depending on Byte/Word Parity Mode           | 38   |

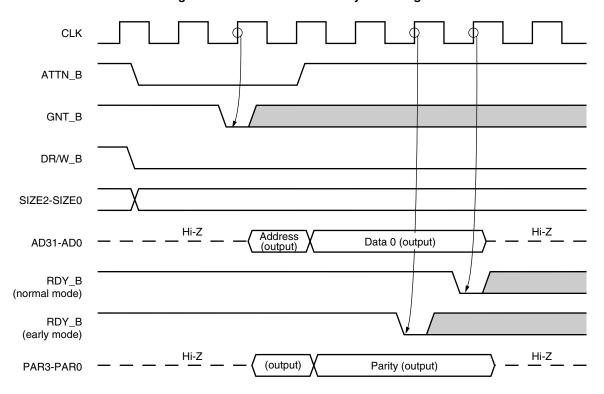

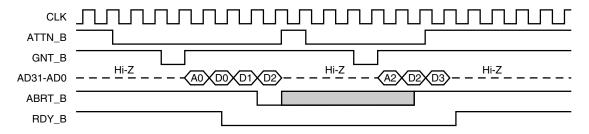

| 4-5    | 1-Word Write DMA Cycle Timing                                        | 40   |

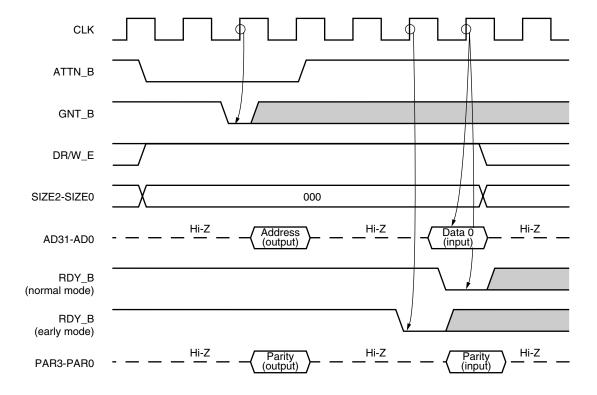

| 4-6    | 1-Word Read DMA Cycle Timing                                         | 40   |

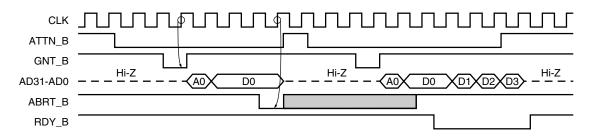

| 4-7    | ABRT_B Signal Input Timing                                           | 42   |

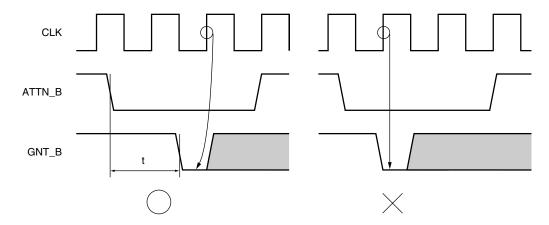

| 4-8    | Relations between ATTN_B and GNT_B                                   | 43   |

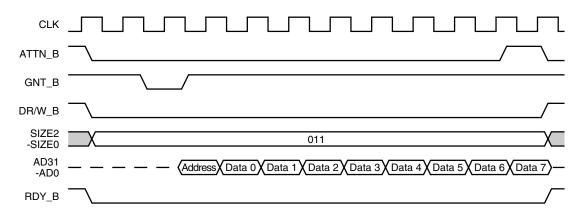

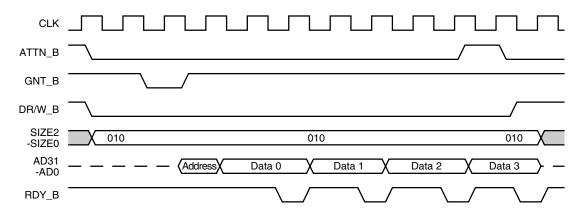

| 4-9    | Burst Write Cycle Timing                                             | 45   |

| 4-10   | Transmit Cell Data Byte Alignment (big endian)                       | 48   |

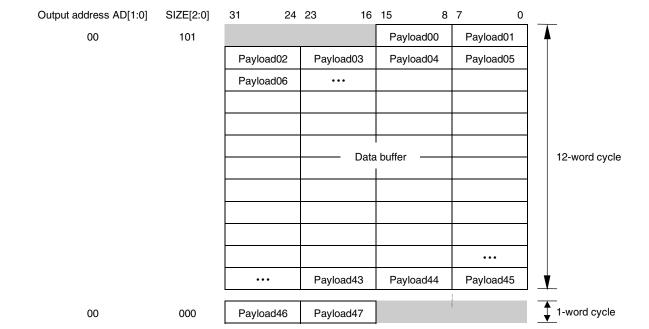

| 4-11   | AD[1:0] Pin and SIZE[2:0] Pin Output during Byte Alignment DMA Write | 49   |

| 4-12   | Example of Storing Cell Data by Byte Alignment                       | 50   |

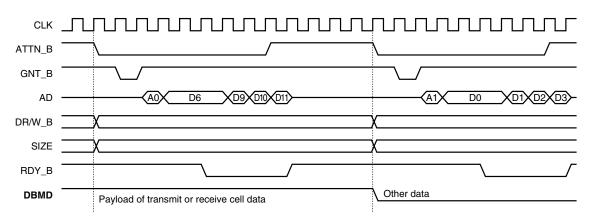

| 4-13   | DBMD Signal Output Timing Example 1                                  | 51   |

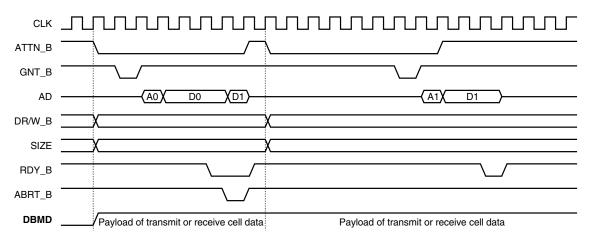

| 4-14   | DBMD Signal Output Timing Example 2 (if aborted)                     | 51   |

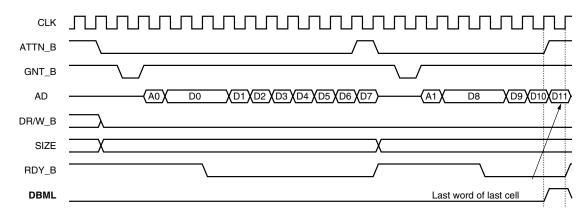

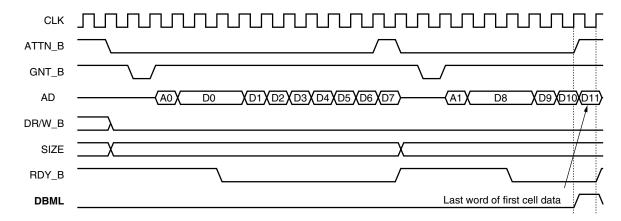

| 4-15   | DBML Output Timing.                                                  | 53   |

| 4-16   | DBMF Output Timing                                                   | 53   |

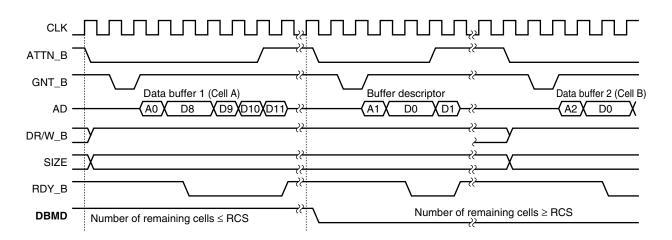

| 4-17   | DBMR Output Timing Example in Multi-Buffer Mode                      | 54   |

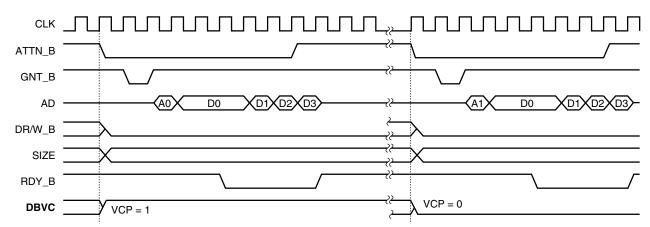

| 4-18   | DBVC Output Timing Example                                           | 55   |

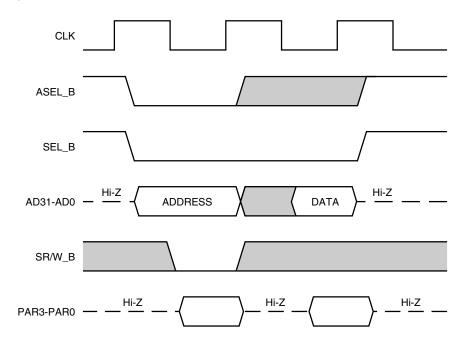

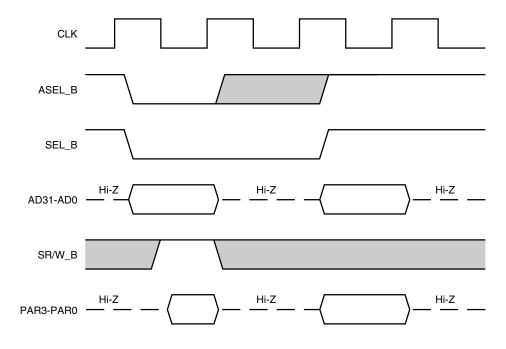

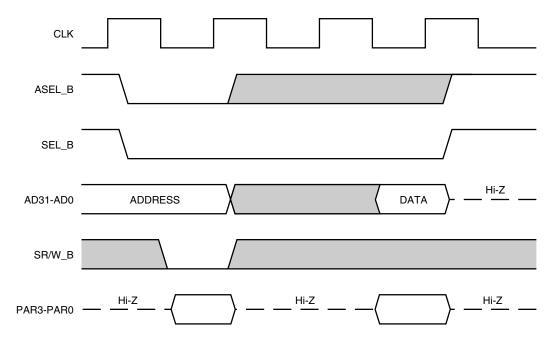

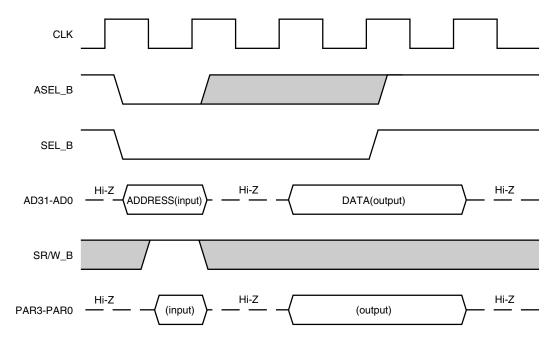

| 4-19   | Slave Access Timing                                                  | 57   |

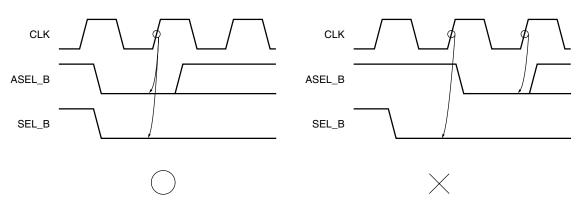

| 4-20   | Input Timing of SEL_B and ASEL_B Signals                             | 59   |

| 4-21   | Format of Little Endian                                              | 60   |

| 4-22   | Format of Big Endian                                                 | 60   |

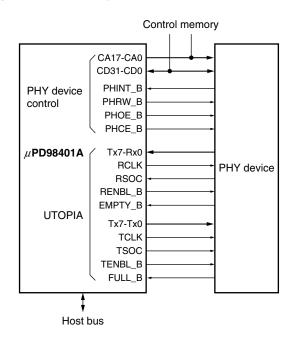

| 4-23   | PHY Layer Interface for Data and Control                             | 62   |

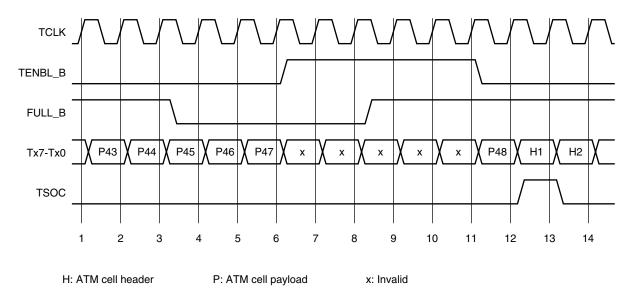

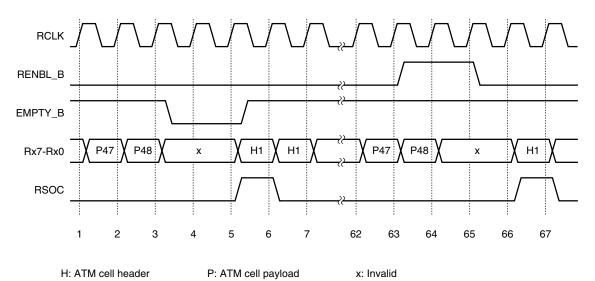

| 4-24   | Octet-Level Handshake Transmission Timing                            | 64   |

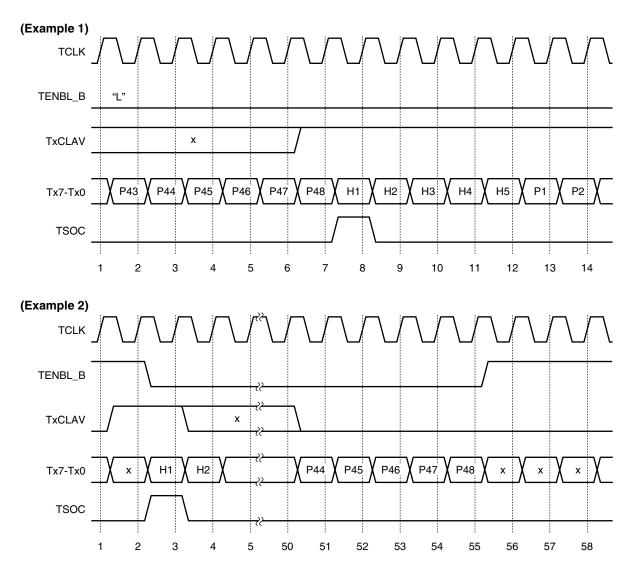

| 4-25   | Cell-Level Handshake Transmission Timing                             | 65   |

| 4-26   | Octet-Level Handshake Reception Timing                               | 66   |

| 4-27   | Cell-Level Handshake Reception Timing                                | 67   |

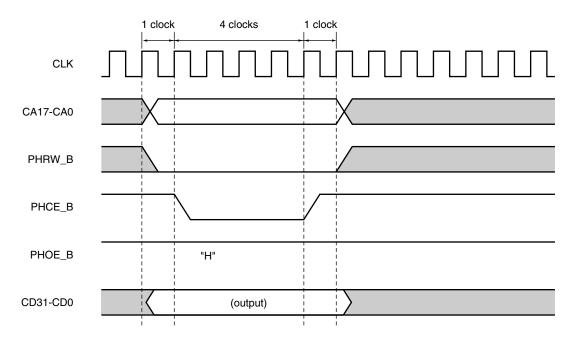

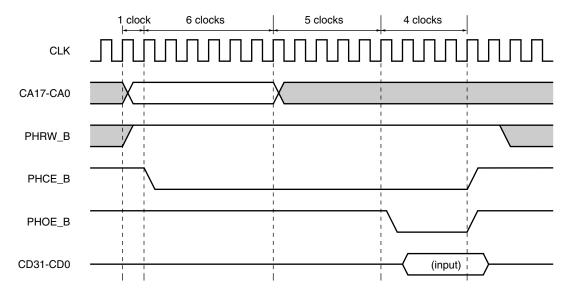

| 4-28   | PHY Device Control Signal Timing                                     | 69   |

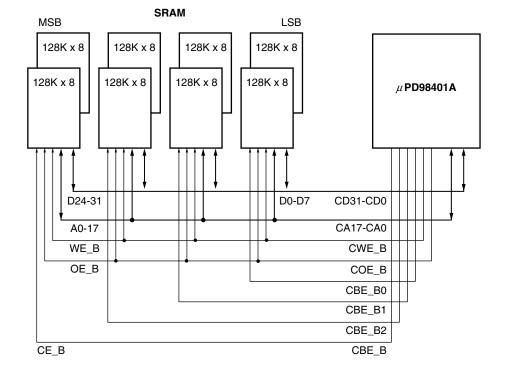

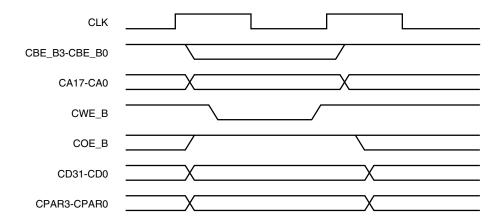

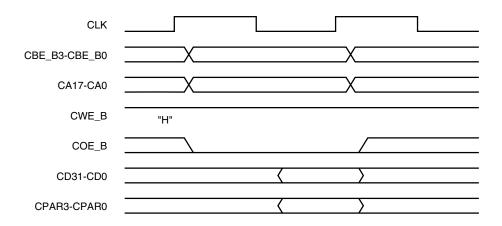

| 4-29   | Control Memory Interface Using Standard SRAM                         | 70   |

| 4-30   | Control Memory Access Timing                                         | 72   |

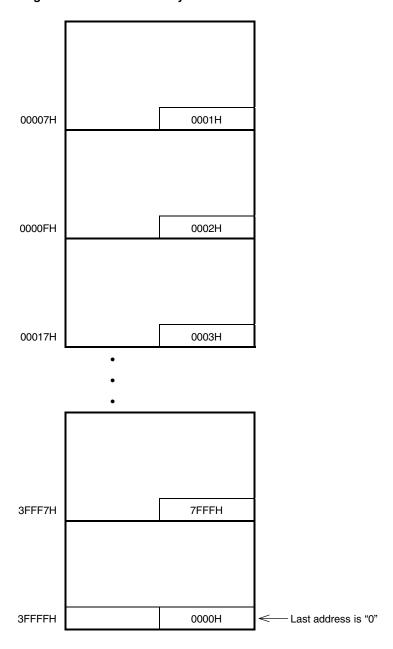

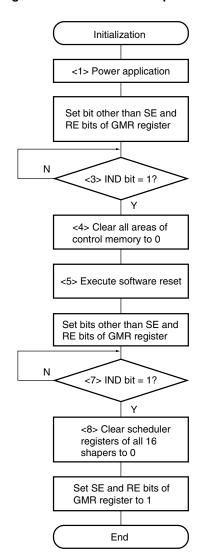

| 5-1    | Control Memory after Initialization                                  | 74   |

| 5-2    | Initialization Sequence                                              | 76   |

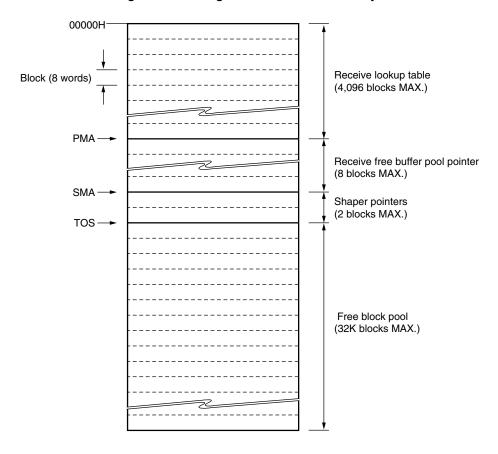

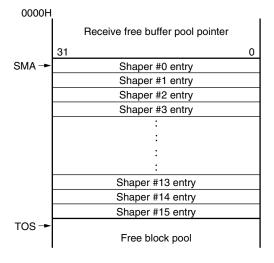

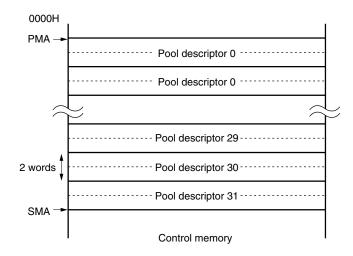

| 5-3    | Configuration of Control Memory                                      | 78   |

| 5-4    | Stack of Free Block Pool                                             | 79   |

| 5-5    | Structure of Mailbox                                                 | 81   |

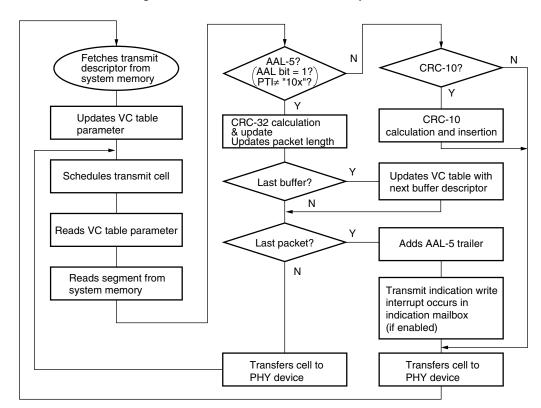

| 5-6    | Outline of Transmission Flow                                         | 82   |

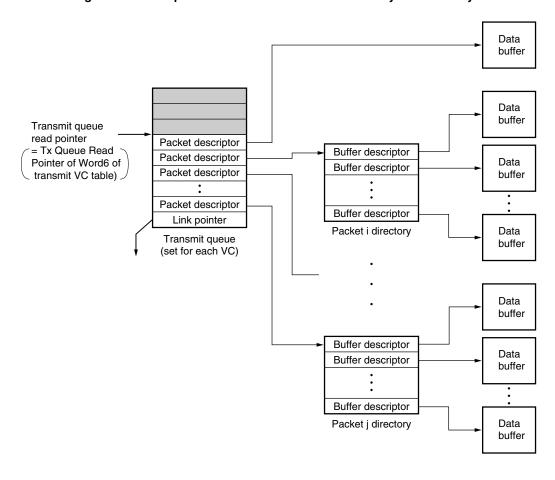

| 5-7    | Example of Structure of Transmit Data in System Memory               | 83   |

# LIST OF FIGURES (2/3)

| Figure | No. Title                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------|------|

|        |                                                                                            |      |

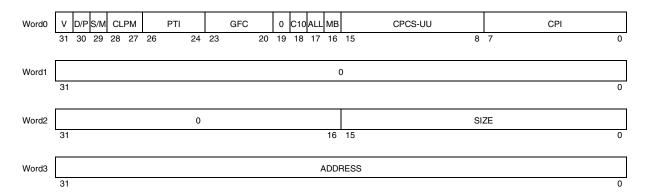

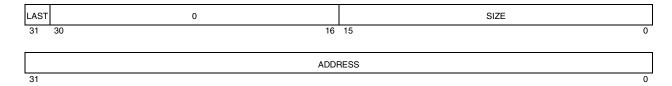

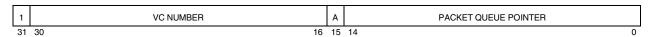

| 5-8    | Format of Packet Descriptor                                                                | 84   |

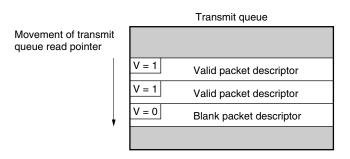

| 5-9    | Location of Blank Descriptor                                                               | 85   |

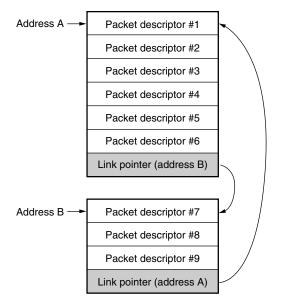

| 5-10   | Example of Arrangement of Transmit Queue                                                   | 85   |

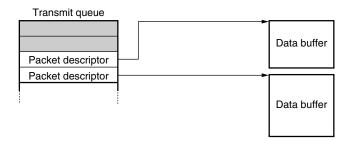

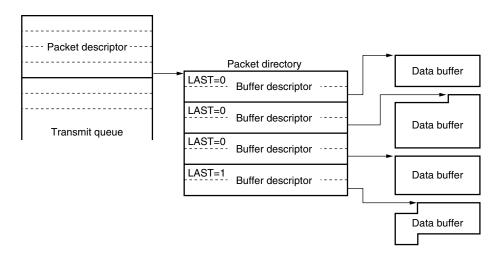

| 5-11   | Single-Buffer Mode                                                                         | 86   |

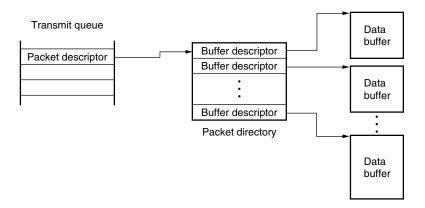

| 5-12   | Multi-Buffer Mode                                                                          | 86   |

| 5-13   | Insertion of CRC-10                                                                        | 88   |

| 5-14   | Format of Packet Descriptor                                                                | 89   |

| 5-15   | Setting of LAST Bit                                                                        | 89   |

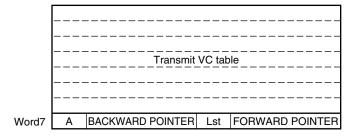

| 5-16   | Structure of Transmit VC Table                                                             | 91   |

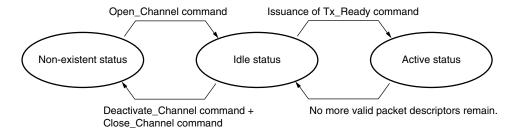

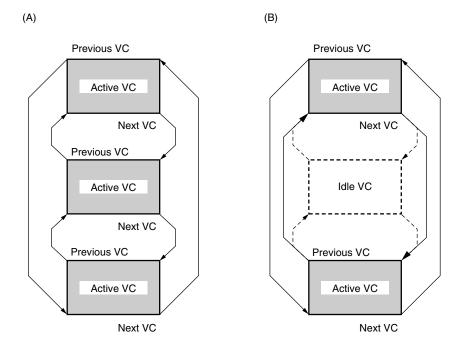

| 5-17   | Status of Transmit Channel                                                                 | 94   |

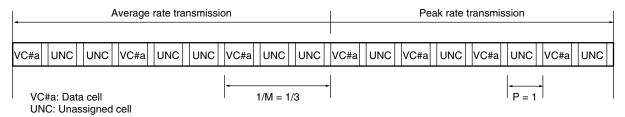

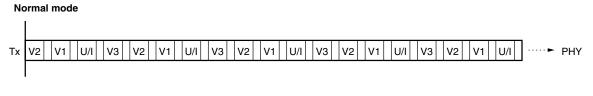

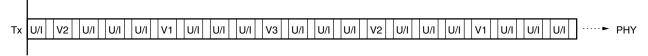

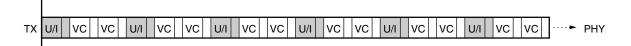

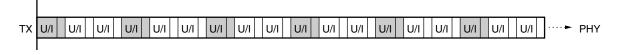

| 5-18   | Example of Transmitting Cell (1 VC transmission, where I/M = 1/2, P = 1, C = 1, ICM = "0") | 94   |

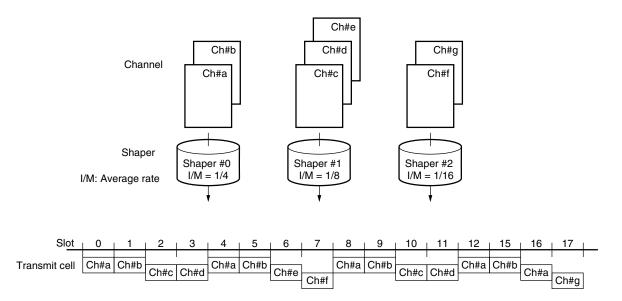

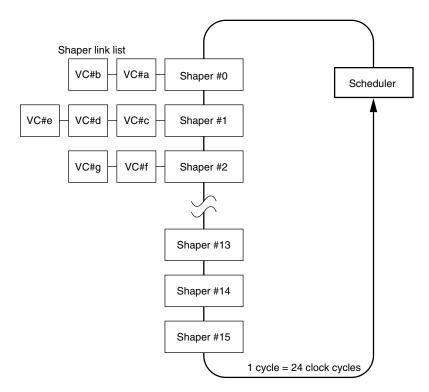

| 5-19   | Concept of Scheduling Function                                                             | 95   |

| 5-20   | Concept of Scheduler Operation                                                             | 95   |

| 5-21   | Example of Actions of Parameters                                                           | 97   |

| 5-22   | Pointers Used for Linking                                                                  | 98   |

| 5-23   | Linking/Releasing Transmit VC to/from Traffic Shaper                                       | 99   |

| 5-24   | Shaper Pointer Entry of Control Memory                                                     | 100  |

| 5-25   | Shaper Status                                                                              | 101  |

| 5-26   | Cell Transmission Sequence According to Priority                                           | 106  |

| 5-27   | Differences in Cell Transmission Procedure by Mode                                         | 107  |

| 5-28   | Outline of Transmission Operation                                                          | 110  |

| 5-29   | Outline of Reception Flow                                                                  | 113  |

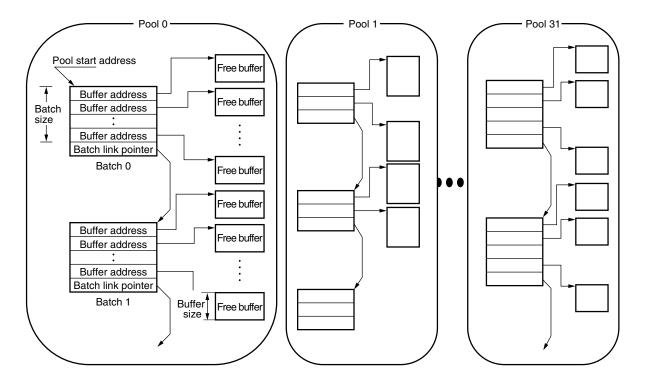

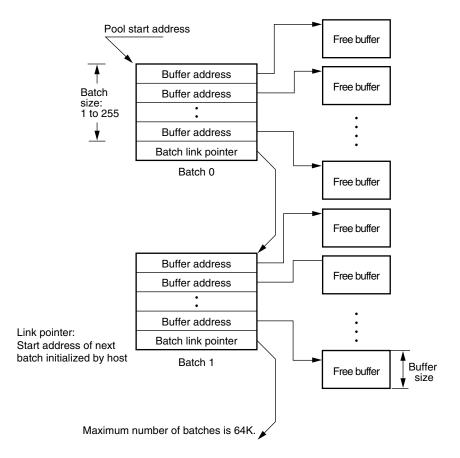

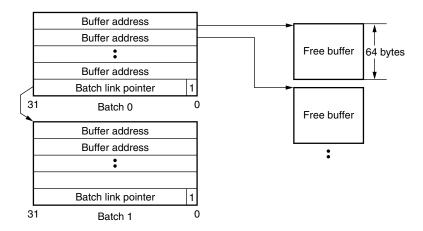

| 5-30   | Structure of Receive Pool in System Memory                                                 | 114  |

| 5-31   | Configuration of Pool                                                                      |      |

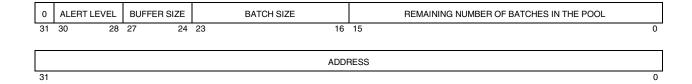

| 5-32   | Location of Pool Descriptor in Receive Free Buffer Pool Pointer                            | 117  |

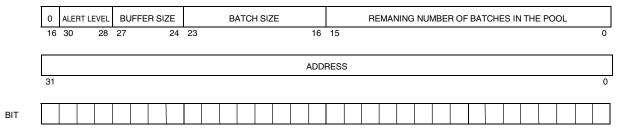

| 5-33   | Format of Pool Descriptor                                                                  | 117  |

| 5-34   | Raw Cell Pool                                                                              | 119  |

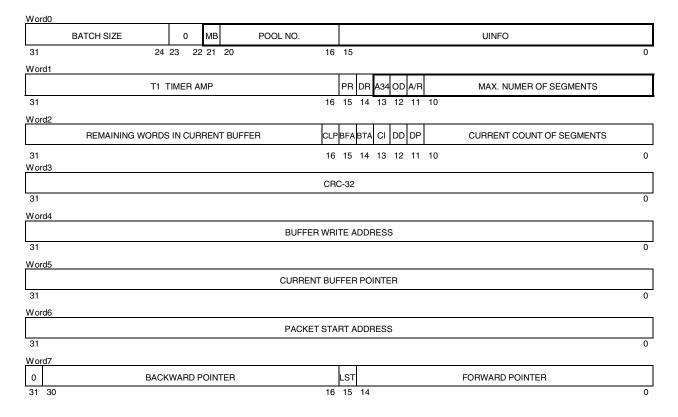

| 5-35   | Receive VC Table                                                                           | 120  |

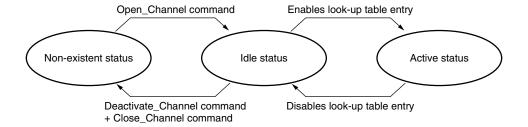

| 5-36   | Receive Channel Status                                                                     | 122  |

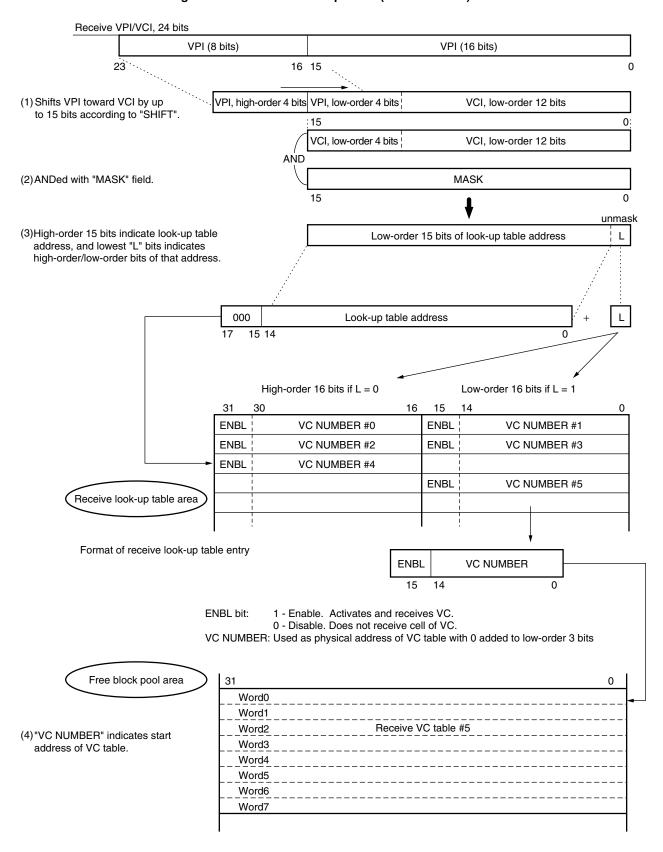

| 5-37   | Receive Look-up Table (when SHIF = 4)                                                      | 124  |

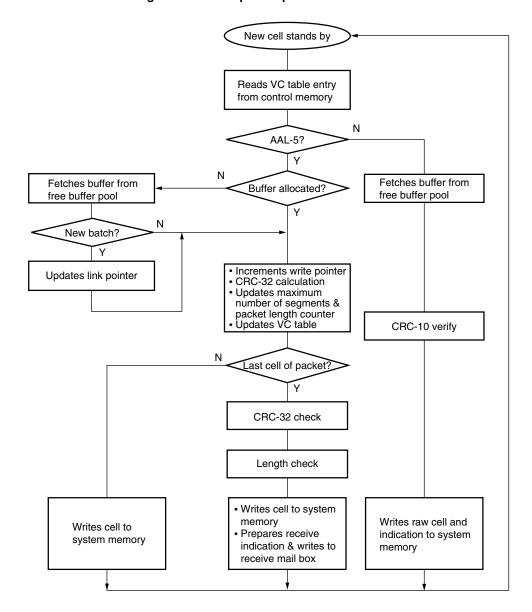

| 5-38   | Reception Operation Flowchart                                                              | 126  |

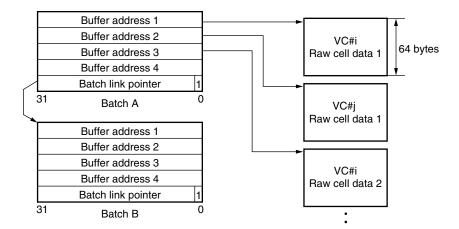

| 5-39   | Configuration Example of Receive Data                                                      | 127  |

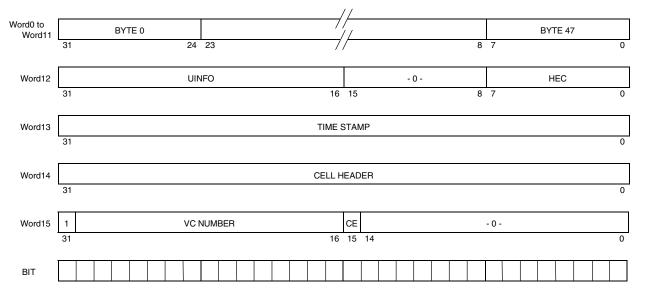

| 5-40   | Structure of Raw Cell Data Storage Pool                                                    | 129  |

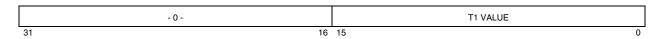

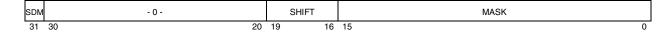

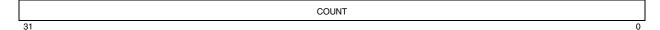

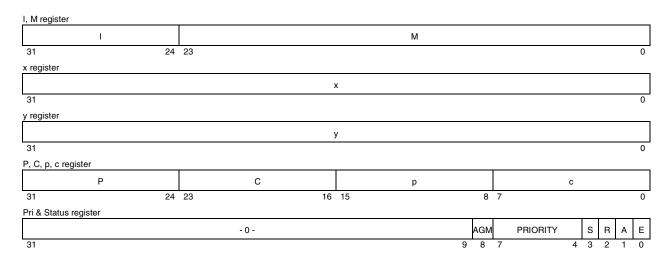

| 5-41   | Reassembly Timer (T1)                                                                      | 130  |

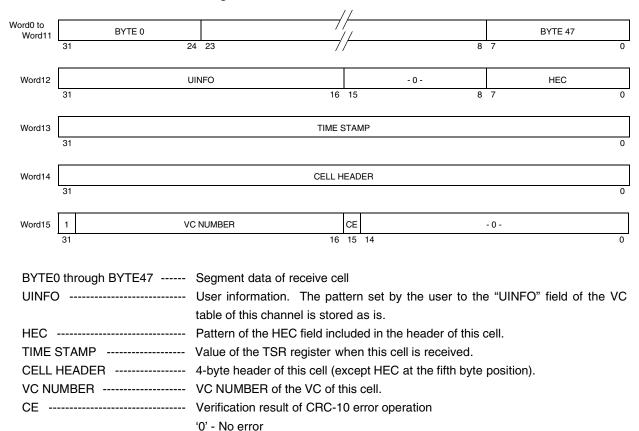

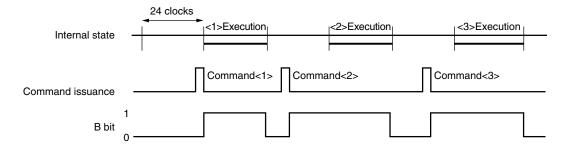

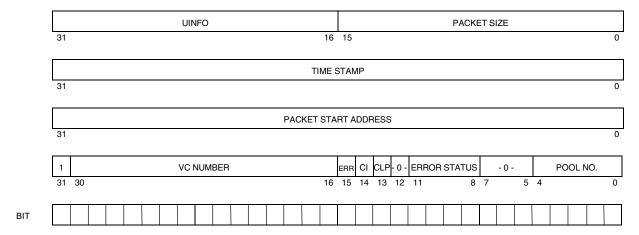

| 5-42   | Format of Raw Cell Data                                                                    | 135  |

| 5-43   | Loopback Mode                                                                              | 140  |

| U +U   | Loopada, Modo                                                                              | 170  |

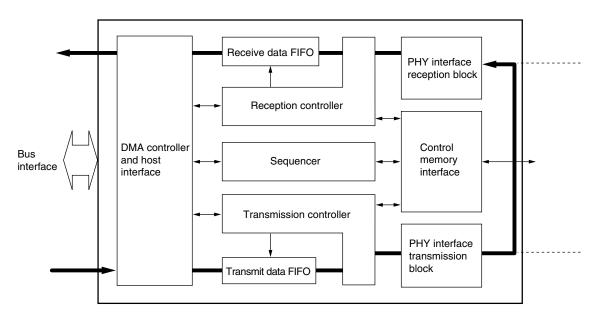

| 6-1    | Command Issuance and B Bit                                                                 | 142  |

| 6-2    | Status Transition of Command Register                                                      | 144  |

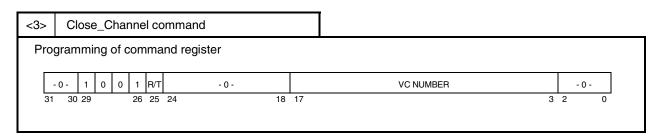

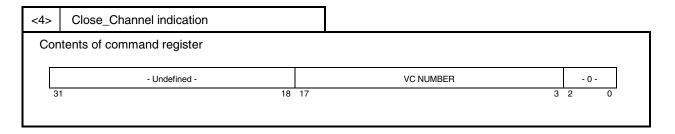

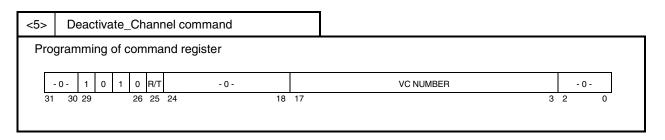

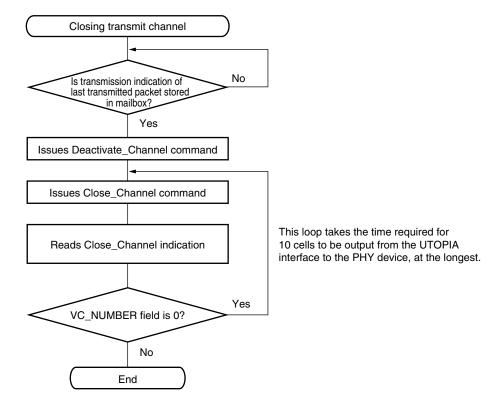

| 6-3    | Closing Transmit Channel                                                                   | 149  |

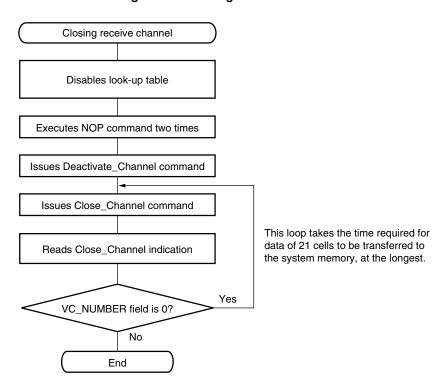

| 6-4    | Closing Receive Channel                                                                    | 150  |

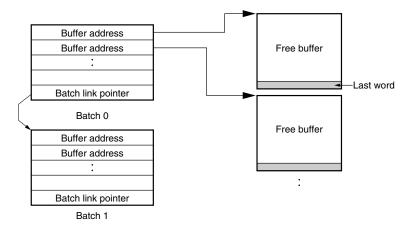

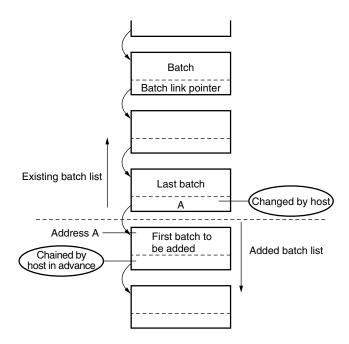

| 6-5    | Work of Host before Issuance of Add_Batches Command                                        | 152  |

# LIST OF FIGURES (3/3)

| Figure | No. Title                                  | Page |  |

|--------|--------------------------------------------|------|--|

|        |                                            |      |  |

| 8-1    | Block Diagram of Boundary Scan Circuit     | 171  |  |

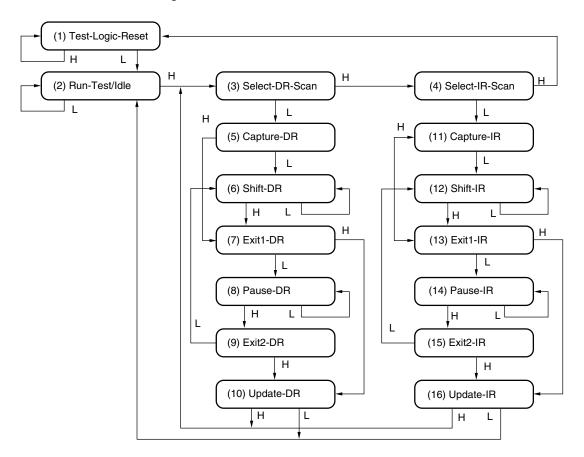

| 8-2    | State Transition of TAP Controller         | 173  |  |

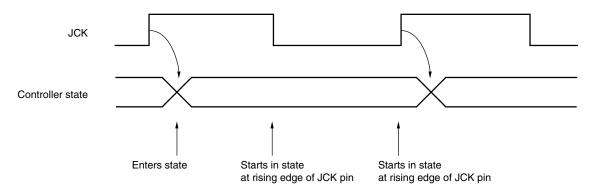

| 8-3    | Operation Timing in Controller State       | 174  |  |

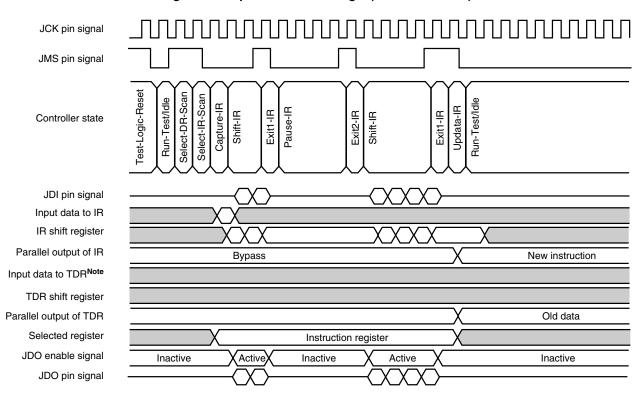

| 8-4    | Operation of Test Logic (instruction scan) | 179  |  |

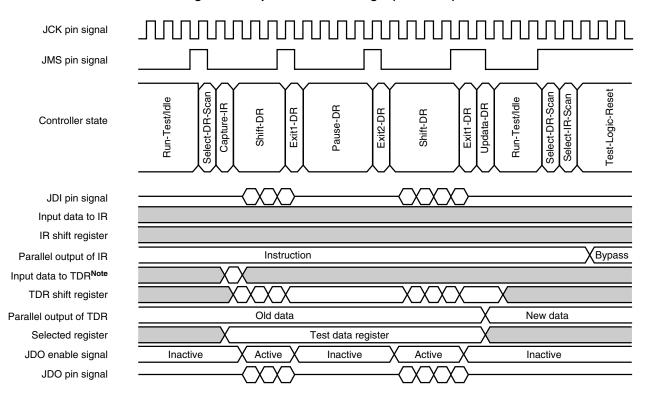

| 8-5    | Operation of Test Logic (data scan)        | 180  |  |

# **LIST OF TABLES**

| Table | No. Title                                                                | Page |

|-------|--------------------------------------------------------------------------|------|

|       |                                                                          |      |

| 4-1   | Bus Parity Mode Select Bit                                               | 38   |

| 4-2   | Selecting Burst Size to Be Enabled                                       | 43   |

| 4-3   | DMA Transfer by μPD98401A                                                | 44   |

| 4-4   | Burst Size under Execution                                               | 44   |

| 4-5   | Burst Transfer Transition in Each Case                                   | 47   |

| 5-1   | Mailbox Operation of µPD98401A                                           | 81   |

| 5-2   | Function of Packet Descriptor                                            | 84   |

| 5-3   | Description of Bits of Scheduler Register                                | 97   |

| 5-4   | Summary of Data Supported by $\mu$ PD98401A Transmission Function        | 112  |

| 5-5   | Types of Receive Data and Usable Pool                                    | 118  |

| 5-6   | Errors Occurring in Any of First, Intermediate, and Last Cells of Packet | 133  |

| 5-7   | Error Taking Precedence When Occurring with Other Errors                 | 133  |

| 6-1   | Command Type                                                             | 141  |

| 6-2   | Operation of L Bit When Register Is Accessed                             | 144  |

| 8-1   | Operation in Each Controller State                                       | 178  |

| 8-2   | μPD98401A Boundary Scan Data Bit Definition                              | 183  |

#### **CHAPTER 1 OVERVIEW**

The  $\mu$ PD98401A is a high-performance SAR chip that segments and reassembles ATM cells. This chip can interface with an ATM network when it is included in a workstation, computer, front-end processor, network hub, or router. The  $\mu$ PD98401A conforms to the ATM Forum Recommendation, and provides the functions of the AAL-5 SAR sublayer and ATM layer.

The  $\mu$ PD98401A is compatible with its predecessor,  $\mu$ PD98401, in terms of hardware and software.

#### 1.1 Features

- · Conforms to ATM Forum

- AAL-5 SAR sublayer and ATM layer functions

- · Hardware support of AAL-5 processing

- Processing of non-AAL-5 traffic (AAL-3/4 cell, OAM cell, RM cell) by software with raw cell processing function

- Hardware support of generation/verification of CRC-10 for non-AAL-5 traffic

- Supports up to 32K virtual channels (VC)

- Provided with 16 traffic shapers that carry out transmission scheduling (control of average rate/peak rate) so as to set different transmission rate for each VC

- · Interface and commands for controlling PHY device

- Employs "UTOPIA interface" as cell transfer interface with PHY device

- · Octet-level handshake

- · Cell-level handshake

- · 32-bit general-purpose bus interface

- High-speed DMAC (supports 1-, 2-, 4-, 8-, 12-, and 16-word burst)

- JTAG boundary scan test function (IEEE1149.1)

- · CMOS process

- +5 V single power source

#### 1.2 Ordering Information

| Part Number     | Package                                           |

|-----------------|---------------------------------------------------|

| μPD98401AGD-MML | 208-pin plastic QFP (fine pitch) (28 $\times$ 28) |

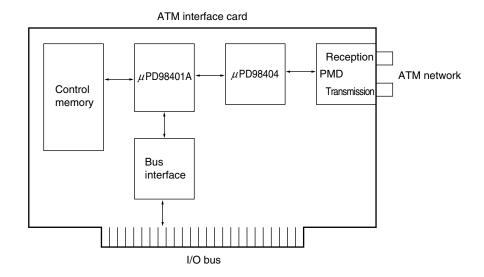

# 1.3 Example of System Configuration

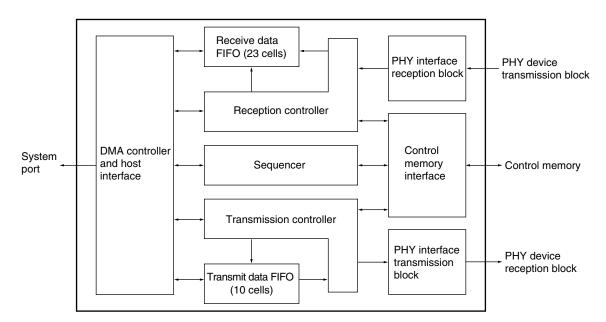

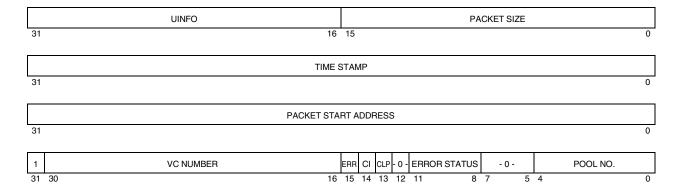

# 1.4 Block Diagram

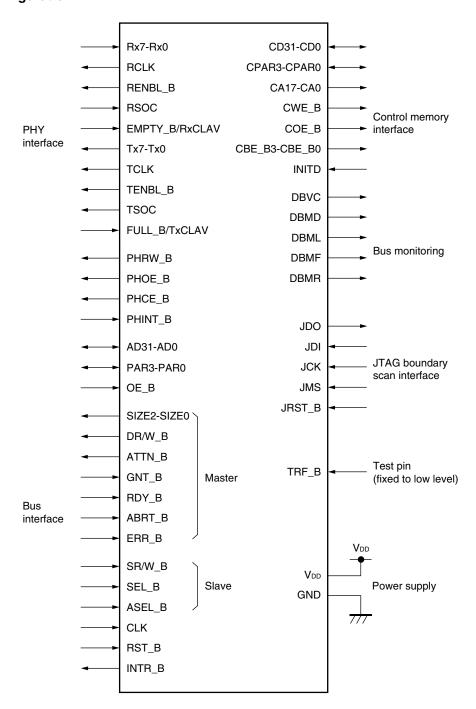

# 1.5 Pin Configuration

#### **CHAPTER 2 PIN FUNCTION**

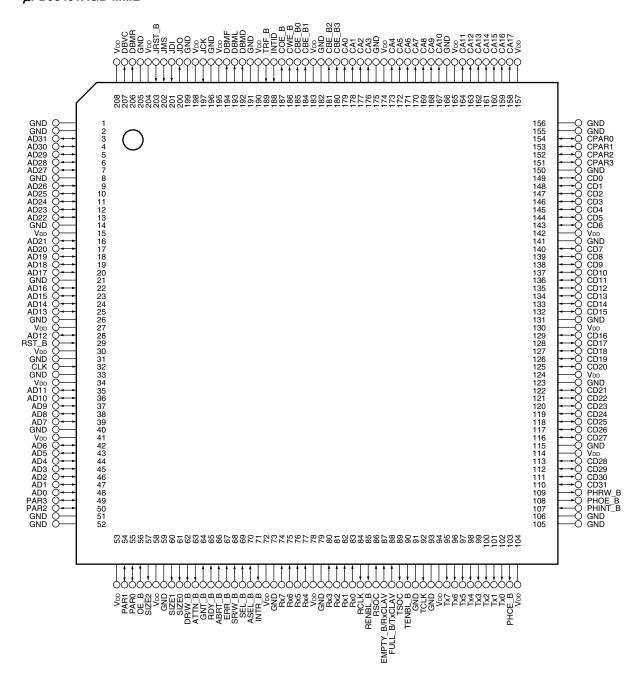

# 2.1 Pin Configuration (Top View)

208-pin plastic QFP (fine pitch) (28 × 28)

#### $\mu$ PD98401AGD-MML

ABRT\_B : Abort PHCE B : PHY Chip Enable : Address/Data AD31\_AD0 PHINT\_B : PHY Interrupt : Slave Address Select ASEL B PHOE\_B : PHY Output Enable : Attention/Burst Frame ATTN\_B PHRW\_B : PHY Read/Write CA17-CA0 : Control Memory Address RCLK : Receive Clock RDY\_B CBE\_B3\_CBE\_B0 : Local Port Byte Enable : Target Ready CD31-CD0 : Control Memory Data RENBL B : Receive Enable : Receive Start Cell

: Clock CLK **RSOC**

COE B : Control Memory Output Enable RST\_B Reset CPAR3-CPAR0 : Control Memory Parity Rx7-Rx0 : Receive Data Bus : Slave Select CWE B : Control Memory Write Enable SEL\_B DBMD : DMA Bus Monitor Data SIZE2-SIZE0 : Burst Size

**DBMF** : DMA Bus Monitor First SR/W\_B : Slave Read/Write DBML : DMA Bus Monitor Last **TCLK** : Transmit Clock **DBMR** : DMA Bus Monitor Remaining : Transmit Enable TENBL\_B **DBVC** : DMA Bus Monitor VC TSOC : Transmit Start of Cell

DR/W\_B : DMA Read/Write TRF\_B : Delay Select

EMPTY\_B/RxCLAV: PHY Output Buffer Empty Tx7-Tx0 : Transmit Data Bus

ERR\_B  $V_{DD}$ : Power Supply

: PHY Buffer Ful FULL\_B/TxCLAV

: Grant GNT B

: Interrupt INTR\_B JCK : JTAG Test Pin JDI : JTAG Test Pin **JDO** : JTAG Test Pin **JMS** : JTAG Test Pin

: Ground

: Initialization Disable

: JTAG Test Pin JRST B OE B : Output Enable PAR3-PAR0 : Bus Parity

**GND**

INITD

#### 2.2 Pin Function

The  $\mu$ PD98401A is a package having 208 pins, of which 152 pins are function pins and 56 pins are V<sub>DD</sub> and GND pins. A detailed explanation of how to use each pin, and the points to be noted in using the pins are given in CHAPTER 4 INTERFACES. Be sure to refer to this chapter.

# 2.2.1 PHY device interface pin

PHY device interfaces include a UTOPIA interface through which the  $\mu$ PD98401A transfers ATM cells with a PHY device, and a PHY control interface by which the  $\mu$ PD98401A controls the PHY device.

# (1) UTOPIA interface

(1/2)

|                    |                    |     |           | (1/2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|--------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name           | Pin No.            | I/O | I/O Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Rx7-Rx4<br>Rx3-Rx0 | 74 - 77<br>80 - 83 | I   | TTL       | Receive Data Bus.<br>Rx7 through Rx0 constitute an 8-bit input bus which inputs data received from a network in byte format from a PHY device. The $\mu$ PD98401A loads data in at the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                         |

| RSOC               | 86                 | I   | TTL       | Receive Start Cell.  The RSOC signal is input in synchronization with the first byte of the cell data from a PHY device. This signal remains high while the first byte of the header is input to Rx7 through Rx0.                                                                                                                                                                                                                                                                                                                                                   |

| RENBL_B            | 85                 | 0   | CMOS      | Receive Enable. The RENBL_B signal indicates to a PHY device that the $\mu$ PD98401A is ready to receive data in the next clock cycle. This signal goes high during and after reset.                                                                                                                                                                                                                                                                                                                                                                                |

| EMPTY_B/<br>RxCLAV | 87                 | I   | TTL       | PHY Output Buffer Empty/Rx Cell Available. This signal notifies the $\mu$ PD98401A that there is no cell data to be transferred in the receive FIFO and that no receive data can be supplied to the PHY device. When the UTOPIA interface is in the octet-level handshake mode, this signal serves as EMPTY_B, indicating that the data on Rx7 through Rx0 are invalid in the current clock cycle. In the cell-level handshake mode, it serves as RxCLAV, indicating that there is no cell to be supplied next after the transfer of the current cell is completed. |

| RCLK               | 84                 | 0   | CMOS      | Receive Clock.  This is a synchronization clock used to transfer cell data with the PHY cell device at the recieve side. The system clock input to the CLK pin is output from this pin as is, immediately after reset.                                                                                                                                                                                                                                                                                                                                              |

| Tx7-Tx0            | 95 - 102           | 0   | CMOS      | Transmit Data Bus. Tx7 through Tx0 constitute an 8-bit output bus which outputs transmit data in byte format to a PHY device. The $\mu$ PD98401A outputs data at the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                           |

| TSOC               | 89                 | 0   | CMOS      | Transmit Start of Cell.  The TSOC signal is output in synchronization with the first byte of transmit cell data.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

(2/2)

| Pin Name          | Pin No. | I/O | I/O Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

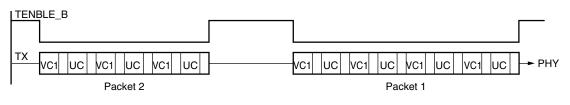

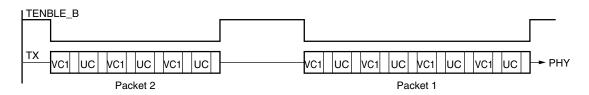

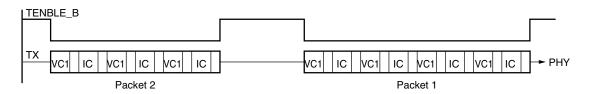

| TENBL_B           | 90      | 0   | CMOS      | Transmit Enable.  The TENBL_B signal indicates to a PHY device that data has been output to Tx7 through Tx0 in the current clock cycle. This signal remains high during reset, and goes high after reset.                                                                                                                                                                                                                                                                 |

| FULL_B/<br>TxCLAV | 88      |     | TTL       | PHY Buffer Full/Tx Cell Available. The FULL_B signal notifies the µPD98401A that the input buffer is full and that the PHY device can receive no more data. When the UTOPIA interface is in the octet-level handshake mode, the PHY device inputs an inactive level to receive cell of data. In the cell-level handshake mode, this signal indicates that the PHY device can receive all the next one cell of data after the current cell has been completely transferred |

| TCLK              | 92      | 0   | CMOS      | Transmit Clock.  This is a synchronization clock used to transfer cell data with the PHY device at the transmission side. The system clock input to the CLK pin is output from this pin as is.                                                                                                                                                                                                                                                                            |

# (2) PHY device control interface

| Pin Name | Pin No. | I/O | I/O Level | Function                                                                                                                                                                                                                |

|----------|---------|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHRW_B   | 109     | 0   | CMOS      | PHY Read/Write. The µPD98401A indicates the direction in which the PHY device is controlled, by using PHRW_B. This signal goes low after reset.  1: Read  0: Write                                                      |

| PHOE_B   | 108     | 0   | CMOS      | PHY Output Enable. The $\mu$ PD98401A enables output from the PHY device by making PHOE_B low                                                                                                                           |

| PHCE_B   | 103     | 0   | CMOS      | PHY Chip Enable.  The $\mu$ PD98401A makes PHCE_B low to access a PHY device. This signal goes high after reset.                                                                                                        |

| PHINT_B  | 107     | I   | TTL       | PHY Interrupt.  This is an interrupt input signal from a PHY device. The PHY device indicates to the µPD98401A that it has an interrupt source, by inputting a low level to PHINT_B. This signal goes high after reset. |

# 2.2.2 Bus interface pins

The bus interface is a general-purpose bus interface compatible with most generally used I/O buses (such as PCI, S bus, GIO, and AP bus).

(1/3)

|                                                                                 |                                                                   |                |                    |                                                                          |                                                                                                         |                                                                                          | (1/3                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------|--------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                        | Pin No.                                                           | I/O            | I/O Level          |                                                                          |                                                                                                         | F                                                                                        | unction                                                                                                                                                                                                                                                                                                                                            |

| AD31-AD27<br>AD26-AD22<br>AD21-AD17<br>AD16-AD13<br>AD12<br>AD11-AD7<br>AD6-AD0 | 3 - 7<br>9 - 13<br>16 - 20<br>22 - 25<br>28<br>35 - 39<br>42 - 48 | I/O<br>3-state | TTL in<br>CMOS out | I/O pins m<br>input/outp<br>at the se                                    | ugh AD0 colultiplexing a ut, AD31 throcond clock                                                        | n address bugh AD0 tand onwa                                                             | 2-bit address/data bus. These pins are bus and a data bus. At the first clock of ransfer an address. They transfer data rd. The AD bus goes into a high-3401A does not access the bus.                                                                                                                                                             |

| PAR3<br>PAR2<br>PAR1<br>PAR0                                                    | 49<br>50<br>54<br>55                                              | I/O<br>3-state | TTL in<br>CMOS out | is set by word or b indicates parity of A an input/c output and When the | indicate the GMR. Enallyte parity cathe parity of D7 through utput pin. I when data $\mu$ PD98401 $\mu$ | bling or distant be specified AD31 the AD0. If we lit serves a sis written, a A does not | D31 through AD0. A parity check mode sabling parity, odd or even parity, and ified. If byte parity is specified, PAR3 rough AD24, and PAR0 indicates the ord parity is specified, PAR3 serves as as an output pin when an address is and as an input pin when data is read. access the bus, PAR3 through PAR0 Pull up these pins when they are not |

| OE_B                                                                            | 56                                                                | _              | TTL                | PAR3 thro<br>impedance<br>an option<br>necessary                         | pin is low,<br>ough PAR0<br>e state while<br>pin. Fix th                                                | as 3-state a high levolis pin to let the bus                                             | $^{0.000}$ 28401A uses AD31 through AD0 and $^{1/0}$ pins. These pins go into a high-rel is being input to OE_B. This pin is ow level in a system where it is not of the $^{\mu}$ PD98401A in a high-impedance                                                                                                                                     |

| SIZE2<br>SIZE1<br>SIZE0                                                         | 57<br>60<br>61                                                    | 0              | CMOS               |                                                                          | ough SIZE0<br>s are used t                                                                              |                                                                                          | the size of the current DMA transfer.  a bus (such as S bus) requiring clear                                                                                                                                                                                                                                                                       |

|                                                                                 |                                                                   |                |                    | l <del>                                    </del>                        |                                                                                                         |                                                                                          |                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                 |                                                                   |                |                    | 0                                                                        | 0                                                                                                       | 0                                                                                        | 1-word transfer                                                                                                                                                                                                                                                                                                                                    |

|                                                                                 |                                                                   |                |                    | 0                                                                        | 0                                                                                                       | 1                                                                                        | 2-word burst 4-word burst                                                                                                                                                                                                                                                                                                                          |

|                                                                                 |                                                                   |                |                    | 0                                                                        | 1                                                                                                       | 0                                                                                        | 4-word burst<br>8-word burst                                                                                                                                                                                                                                                                                                                       |

|                                                                                 |                                                                   |                |                    | 1                                                                        | 0                                                                                                       | 0                                                                                        | 16-word burst                                                                                                                                                                                                                                                                                                                                      |

|                                                                                 |                                                                   |                |                    | 1                                                                        | 0                                                                                                       | 1                                                                                        | 12-word burst                                                                                                                                                                                                                                                                                                                                      |

|                                                                                 |                                                                   |                |                    | 1                                                                        | 1                                                                                                       | 0                                                                                        | Undefined                                                                                                                                                                                                                                                                                                                                          |

|                                                                                 |                                                                   |                |                    | 1                                                                        | 1                                                                                                       | 1                                                                                        | Reception side byte alignment                                                                                                                                                                                                                                                                                                                      |

|                                                                                 |                                                                   |                |                    |                                                                          |                                                                                                         |                                                                                          |                                                                                                                                                                                                                                                                                                                                                    |

(2/3)

| Pin Name | Pin No. | I/O | I/O Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DR/W_B   | 62      | 0   | CMOS      | DMA Read/Write.  DR/W_B indicates the direction of DMA access.  1: Read access  0: Write access  This pin is set to 1 after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ATTN_B   | 63      | 0   | CMOS      | Attention/Burst Frame (DMA request). The $\mu$ PD98401A makes the ATTN_B signal low when it performs a DMA operation. The ATTN_B signal becomes inactive at the rising edge of CLK when the data to be transferred by means of DMA has decreased to 1 word.                                                                                                                                                                                                                                                                                                                                                                        |

| GNT_B    | 64      | I   | πL        | Grant The GNT_B signal inputs a low level when the bus arbiter grants the $\mu$ PD98401A use of the bus in response to a DMA request from the $\mu$ PD98401A. The $\mu$ PD98401A recognizes that it has been granted use of the bus and starts DMA operation when the GNT_B signal goes low (active). Make sure that the GNT_B signal falls at least one system clock cycle after the rising of the ATTN_B signal. The GNT_B signal must be returned to the high (inactive) level before the $\mu$ PD98401A makes the ATTN_B signal low (active) to issue the next DMA cycle request.                                              |

| RDY_B    | 65      | I   | ΠL        | Target Ready. RDY_B indicates to the $\mu$ PD98401A in the DMA cycle that the target device is ready for input/output. During the DMA read operation of the $\mu$ PD98401A, the RDY_B signal is made low if valid data is on AD31 through AD0. During the DMA write operation of the $\mu$ PD98401A, the RDY_B signal is made low if the target device is ready for receiving data. The sampling timing of the RDY_B and ABRT_B signals of the $\mu$ PD98401A can be advanced by one clock (early mode) by using an internal register (GMR register).                                                                              |

| ABRT_B   | 66      | I   | TTL       | Abort. ABRT_B is used to abort a DMA transfer cycle. If this signal goes low while data is being transferred in a DMA transfer cycle, DMA transfer is aborted in that cycle and the ATTN_B signal is deasserted inactive. After that, the $\mu$ PD98401A asserts the ATTN_B signal active again, and resumes burst starting from the aborted data. While a low level is input to ABRT_B, the RDY_B signal is ignored. The user can advance the sampling timing of the RDY_B and ABRT_B signals of the $\mu$ PD98401A by one clock (early mode) by using an internal register (GMR register). Pull up this pin when it is not used. |

| ERR_B    | 67      | I   | TTL       | Error. This pin is used by a device that manages the bus to forcibly stop the operation of the $\mu$ PD98401A when occurrence of an error is detected on the system bus. When a low level is input to this pin, the $\mu$ PD98401A stops all bus operations, sets the system bus error bit (bit 25) of the GSR register (when not masked), and generates an interrupt. Pull up this pin when it is not used.                                                                                                                                                                                                                       |

(3/3)

| Pin Name | Pin No. | I/O | I/O Level                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR/W_B   | 68      | ı   | TTL                       | Slave Read/Write.  The SR/W_B signal determines the direction in which the slave is accessed.  1: Read access 2: Write access                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SEL_B    | 69      | I   | TTL                       | Slave Select.  This signal goes low (active) when the µPD98401A is accessed as a slave. The SEL_B signal must goes low as soon as or after the ASEL_B signal has gone low. An inactive period of at least 2 system clock cycles must be inserted between when the SEL_B signal has become inactive and when it becomes active again.                                                                                                                                                                                                                                     |

| ASEL_B   | 70      | ı   | TTL                       | Slave Address Select.  The ASEL_B signal is used to select the direct address register of the $\mu$ PD98401A.  When a low level is input to ASEL_B, the $\mu$ PD98401A samples the AD bus at the first rising edge of CLK.                                                                                                                                                                                                                                                                                                                                               |

| CLK      | 32      | I   | TTL                       | Clock.  This pin inputs the system clock. Input a clock in a range of 8 to 33 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RST_B    | 29      | ı   | TTL                       | Reset. The RST_B signal initializes the $\mu$ PD98401A (on starting, etc.). After reset, the $\mu$ PD98401A can start normal operation. When a low level is input to RST_B, the internal state machine and registers of the $\mu$ PD98401A are reset, and all 3-state signals go into a high-impedance state. The reset input is asynchronous. When this signal is input during operation, the operating status at that time is lost. Hold RST_B low at least for the duration of one clock. After reset, do not access the $\mu$ PD98401A for at least 20 clock cycles. |

| INTR_B   | 71      | 0   | Nch open-<br>drain output | Interrupt. This is an open-drain signal and must be pulled up. INTR_B informs the CPU that the interrupt bit (unmasked) of the GSR register is set.                                                                                                                                                                                                                                                                                                                                                                                                                      |

# 2.2.3 Bus monitor pins

The bus monitor pins indicate the type of data under DMA transfer. These five pins are enabled when the BME bit of the GMR register is set to 1; they go into a high-impedance state when the BME bit is 0.

| Pin Name | Pin No. | I/O          | I/O Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBMD     | 192     | O<br>3-state | CMOS      | DMA Bus Monitor Data.  This pin indicates that the payload of an AAL-5 cell is under DMA transfer. This pin is enabled when the BME bit of the GMR register is set to 1, and goes into a high-impedance state when the BME bit is 0. The DBMD signal changes in synchronization with the falling of the ATTN_B signal. The high level of this signal indicates that the payload of an ALL-5 packet transmit/receive cell is under DMA transfer, and low level indicates that the other data is being transferred.                                                                                 |

| DBML     | 193     | O<br>3-state | CMOS      | DMA Bus Monitor Last.  If one-word data currently under DMA transfer satisfies any of the following conditions, this pin goes high in synchronization with output of the data.  • Last 1 word of last cell of AAL-5 packet  • 1-word data to be written to last word of receive buffer  • Last 1-word data of last cell of receive packet in which MAX. NUMBER OF SEGMENTS error has occurred  When this pin is low, it indicates that the data is other than above. This pin is enabled when the BME bit of the GMR register is set to 1; it goes into a high-impedance state when the bit is 0. |

| DBMF     | 194     | O<br>3-state | CMOS      | DMA Bus Monitor First.  This pin indicates that the data under DMA transfer is the start cell of a receive AAL-5 packet. This pin is enabled when the BME bit of the GMR register is set to 1; it goes into a high-impedance state when the bit is 0. This pin goes high in synchronization with the last word data of the first cell of an AAL-5 packet.                                                                                                                                                                                                                                         |

| DBMR     | 206     | O<br>3-state | CMOS      | DMA Bus Monitor Remaining.  This pin indicates that the number of cells remaining in the transmit buffer is equal to, or has dropped below the value assigned to the RCS register. This pin is enabled when the BME bit of the GMR register is set to 1; it goes into a high-impedance state when the bit is 0.                                                                                                                                                                                                                                                                                   |

| DBVC     | 207     | O<br>3-state | CMOS      | DMA Bus Monitor VC.  Reports that the data currently being transferred by means of DMA is of the VC for which the VCP bit of the receive VC table is set to 1. This pin is asserted active in synchronization with the falling of ATTN_B. It is enabled when the BME bit of the GMR register is set to 1; it goes into a high-impedance state when the BME bit is reset to 0.                                                                                                                                                                                                                     |

# 2.2.4 Control memory interface pins

These pins constitute an interface through which the  $\mu$ PD98401A accesses an external control memory and a PHY device. A 18-bit address bus and a 32-bit data bus are used. The control memory of the host is accessed only via this interface.

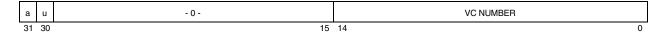

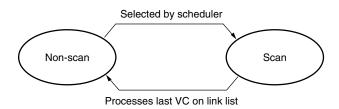

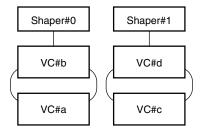

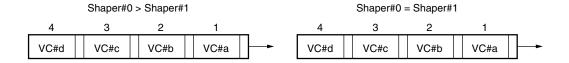

| Pin Name                                                   | Pin No.                                             | I/O            | I/O Level           | Function                                                                                                                                                                                                                                                                         |