### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# Phase-out/Discontinued

### μ**PD78366A**

### **16-/8-BIT SINGLE-CHIP MICROCONTROLLER**

Hardware

μ**PD78363A** μ**PD78365A** μ**PD78366A** μ**PD78368A** μ**PD78P368A**

Document No. U10205EJ3V0UM00 (3rd edition) Date Published August 1997 N

© NEC Corporation 1995 Printed in Japan [MEMO]

### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### 2 HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### ③ STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

QTOP is a trademark of NEC Corporation.

MS-DOS and Windows are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT and PC DOS are trademarks of IBM Corporation.

HP9000 series 700 and HP-UX are trademarks of Hewlett-Packard Company.

SPARCstation is a trademark of SPARC International, Inc.

SunOS is a trademark of Sun Microsystems Inc.

NEWS and NEWS-OS are trademarks of Sony Corporation.

TRON stands for The Realtime Operating system Nucleus.

ITRON stands for Industrial TRON.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

License not needed:

#### μPD78365A, 78P368AKL-S

The customer must judge the need for licence:  $\mu$ PD78363A, 78366A, 78368A, 78P368AGF-3B9

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

### **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

NEC Electronics (Germany) GmbH Duesseldorf, Germany

Tel: 0211-65 03 02 Fax: 0211-65 03 490

NEC Electronics (UK) Ltd.

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

NEC Electronics (France) S.A. Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

NEC Electronics (Germany) GmbH Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

Phase-out/Discontinued

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

**NEC do Brasil S.A.** Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

### Major Revisions in This Version

**Phase-out/Discontinued**

| Page        | Contents                                                                      |

|-------------|-------------------------------------------------------------------------------|

| Throughtout | The $\mu$ PD78368A has been added as a target device.                         |

|             | The $\mu$ PD78P368AKL-S has been developed.                                   |

| P.204, 205  | CHAPTER 8 A/D CONVERTER                                                       |

|             | 8.2 A/D Converter Mode Register (ADM)                                         |

|             | The conversion time by setting the FR bit has been changed.                   |

| P.274, 275  | CHAPTER 10 CLOCKED SERIAL INTERFACE                                           |

|             | 10.6.1 SBI data format                                                        |

|             | A caution has been added regarding the bus release signal and command signal. |

The mark  $\star$  shows major revised points.

### PREFACE

| Users                   | <ul> <li>application program development.</li> <li>This manual describes the following processor</li> <li>μPD78363A, 78365A, 78366A, 7836</li> <li>Note In addition to the other products 78362A, and 78P364A. For description of the other products 78362A, and 78P364A.</li> </ul> |                                                                                                                                                                                                                                        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose                 | The purpose of this manual is to help unde subseries as listed below.                                                                                                                                                                                                                | rstand the hardware capabilities of the $\mu$ PD78366A                                                                                                                                                                                 |

| Organization            | The $\mu$ PD78366A subseries manual is some manual) and Instructions.                                                                                                                                                                                                                | eparated into two parts: Hardware (the present                                                                                                                                                                                         |

|                         | Hardware                                                                                                                                                                                                                                                                             | Instructions                                                                                                                                                                                                                           |

|                         | <ul> <li>Pin functions</li> <li>Internal hardware function</li> <li>Interrupts</li> <li>List of instruction set</li> </ul>                                                                                                                                                           | <ul> <li>CPU functions</li> <li>Addressing</li> <li>List of instruction set</li> <li>Explanation of each instruction</li> </ul>                                                                                                        |

| Read them be            | Caution $$                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                        |

| How to read this manual | Before using this manual, the user should logical circuit, and microcontroller fields.                                                                                                                                                                                               | Ild have a general knowledge of the electronics,                                                                                                                                                                                       |

|                         | → Unless otherwise specified, the $\mu$<br>throughout this manual. When<br>78P368A, take $\mu$ PD78366A for $\mu$ F                                                                                                                                                                  | <b>78365A, 78368A, and 78P368A manual:</b><br>PD78366A is treated as the representative model<br>you use the $\mu$ PD78363A, 78365A, 78368A, or<br>PD78363A, 78365A, 78368A, or 78P368A.<br>e one-time PROM and EPROM models, the term |

- To check the details of a register if you know the name of the register:  $\rightarrow$  Look it up in APPENDIX C REGISTER INDEX.

- To know the detailed functions:

- $\rightarrow$  Look it up in APPENDIX D FUNCTION INDEX.

- To know the  $\mu$ PD78366A subseries instruction function in detail:  $\rightarrow$  Refer to the  $\mu$ PD78365 User's Manual Instruction (U12117E).

- To understand the general functions of the  $\mu$ PD78366A subseries:

- $\rightarrow~$  Read the entire manual in the order of the table of contents.

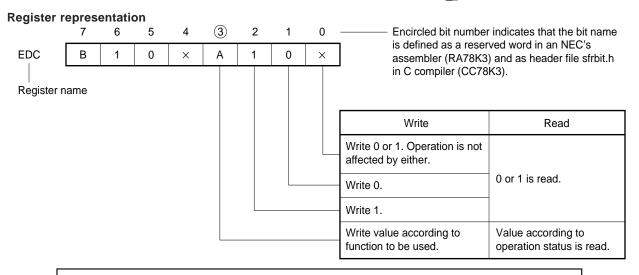

| Legend | Data weight        | : Higher digits on the left side<br>Lower digits on the right side |

|--------|--------------------|--------------------------------------------------------------------|

|        | Active low         | : xxxx (Pins and signal names are over-scored.)                    |

|        | Memory map address | : Low-order address on the upper side                              |

|        |                    | High-order address on the lower side                               |

|        | Note               | : Explanation of the indicated part of the text                    |

|        | Caution            | : Information requesting the user's special attention              |

|        | Remark             | : Supplementary information                                        |

|        | Numeric value      | : Binary: XXXXB or XXXX                                            |

|        |                    | Decimal: XXXX                                                      |

|        |                    | Hexadecimal: xxxxH                                                 |

### Never write the combination of codes marked "setting prohibited" in the register chart.

Confusing characters : 0 (zero), O (oh)

: 1 (numeral), I (lowercase of L), I (uppercase of i)

#### Related Documents

### • Documents related to devices

| Document Name                                  | Document No. |             |

|------------------------------------------------|--------------|-------------|

|                                                | Japanese     | English     |

| μPD78362A Data Sheet                           | U10098J      | 10098E      |

| $\mu$ PD78P364A Data Sheet                     | U10106J      | 10106E      |

| μPD78363A, 78365A, 78366A Data Sheet           | U11109J      | U11109E     |

| $\mu$ PD78P368A Data Sheet                     | U11373J      | U11373E     |

| $\mu$ PD78362A User's Manual -Hardware         | U10745J      | U10745E     |

| $\mu$ PD78366A User's Manual -Hardware         | U10205J      | This manual |

| $\mu$ PD78356 User's Manual -Instruction       | U12117J      | U12117E     |

| $\mu$ PD78362A Special Function Register Table | U10210J      | -           |

| $\mu$ PD78366A Special Function Register Table | U10107J      | -           |

| μPD78352A Instruction Set                      | U11955J      | -           |

### · Documents related to development tools

| Document Name                |          | Document No. |          |

|------------------------------|----------|--------------|----------|

|                              |          | Japanese     | English  |

| IE-78350-R User's Manual     | Hardware | EEU-754      | EEU-1366 |

|                              | Software | EEU-753      | EEU-1376 |

| IE-78365-R-EM1 User's Manual |          | EEU-924      | EEU-1454 |

| EP-78365GF-R User's Manual   |          | EEU-955      | EEU-1488 |

Caution The related documents are subject to change without notice. Be sure to use the latest version for your design work.

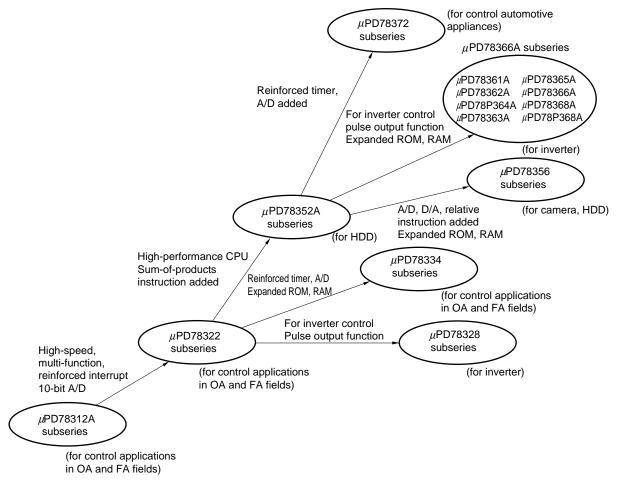

**78K/III Series Product Development**

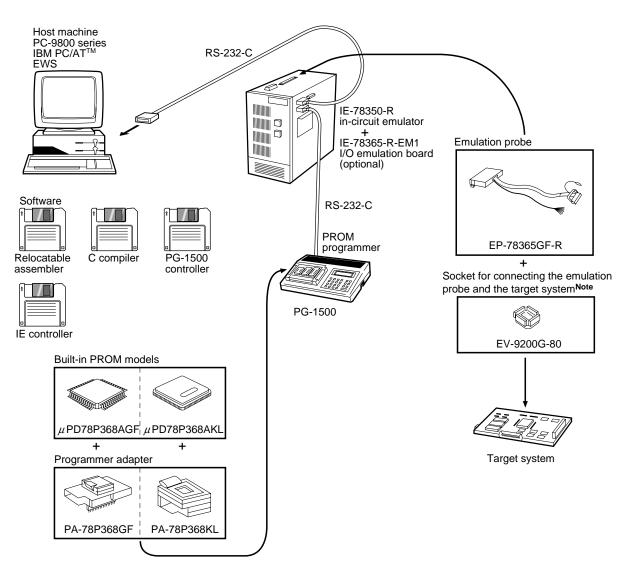

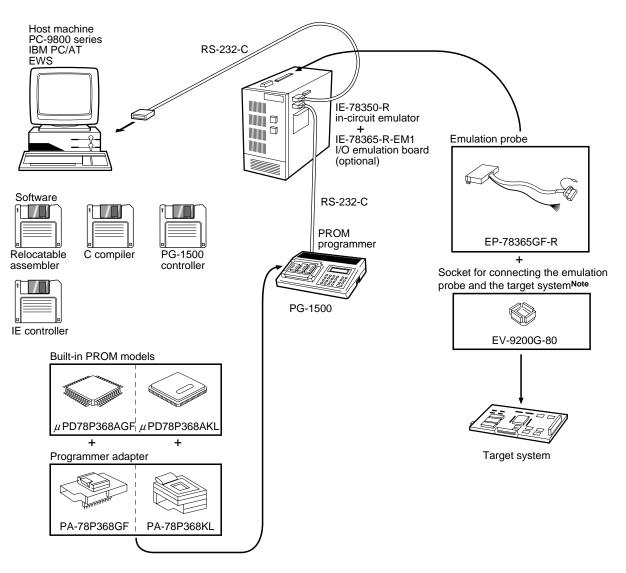

DEVELOPMENT TOOL CONFIGURATION (WHEN USING IE CONTROLLER)

Note A socket is provided with the emulation probe.

Remarks 1. Host machine and PG-1500 can be directly connected by RS-232-C.

2. 3.5-inch FD represents the distributed media of software in this figure.

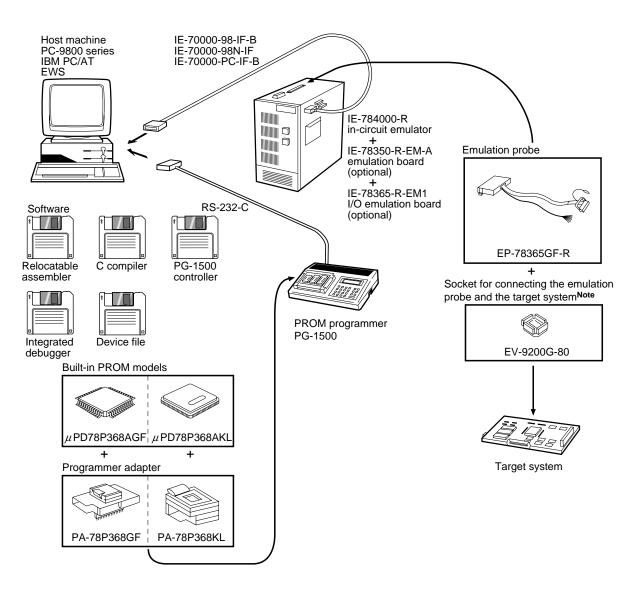

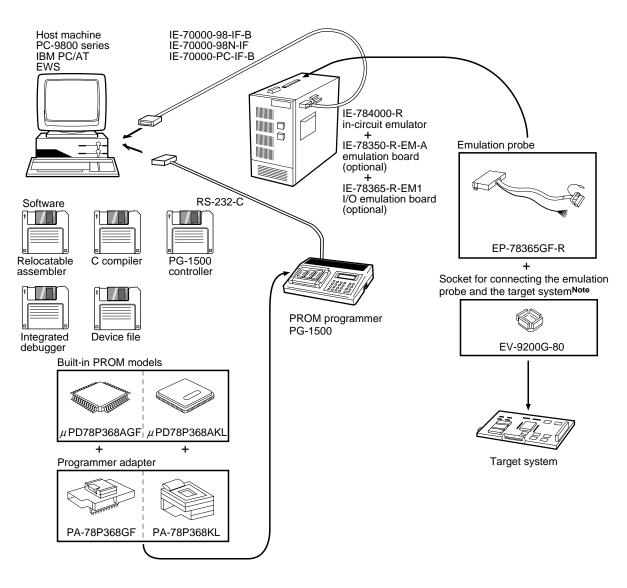

### DEVELOPMENT TOOL CONFIGURATION (WHEN USING INTEGRATED DEBUGGER)

**Note** A socket is provided with the emulation probe.

- Remarks 1. Desk top-type PC represents host machine in this figure.

- 2. 3.5-inch FD represents the distributed media of software in this figure.

### TABLE OF CONTENTS

| CHAPTE | R 1 GENERAL                                                                               | 1  |

|--------|-------------------------------------------------------------------------------------------|----|

| 1.1    | Features                                                                                  | 2  |

| 1.2    | Application Fields                                                                        | 3  |

| 1.3    | Ordering Information                                                                      | 3  |

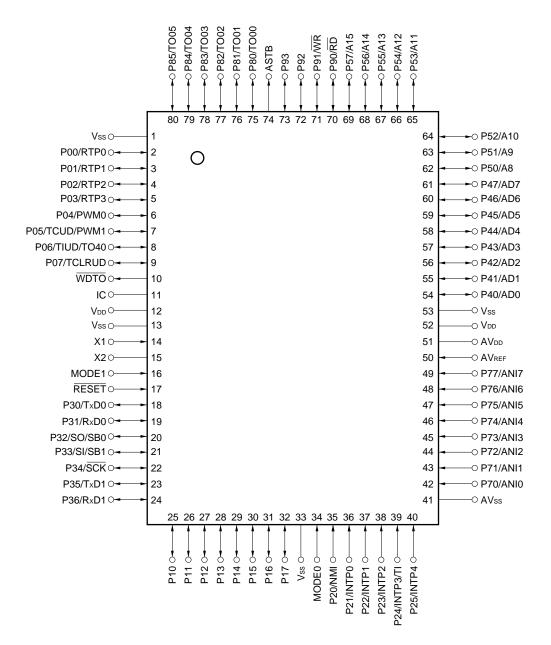

| 1.4    | Pin Configuration (Top View)                                                              | 4  |

|        | 1.4.1 Normal operation mode                                                               | 4  |

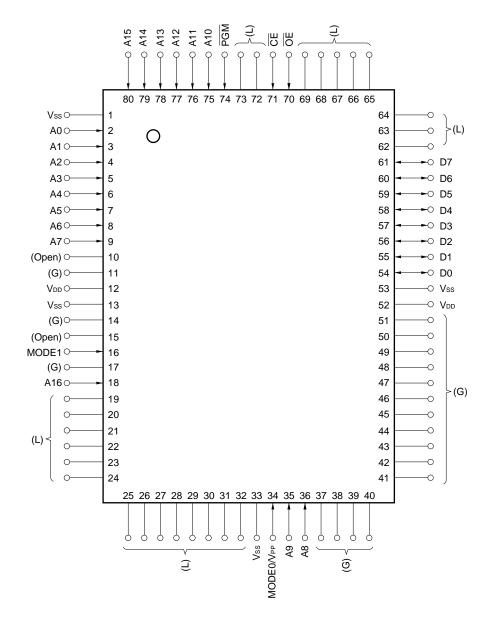

|        | 1.4.2 PROM programming mode (μPD78P368A only: MODE0/V <sub>PP</sub> = H, MODE1 = L)       | 6  |

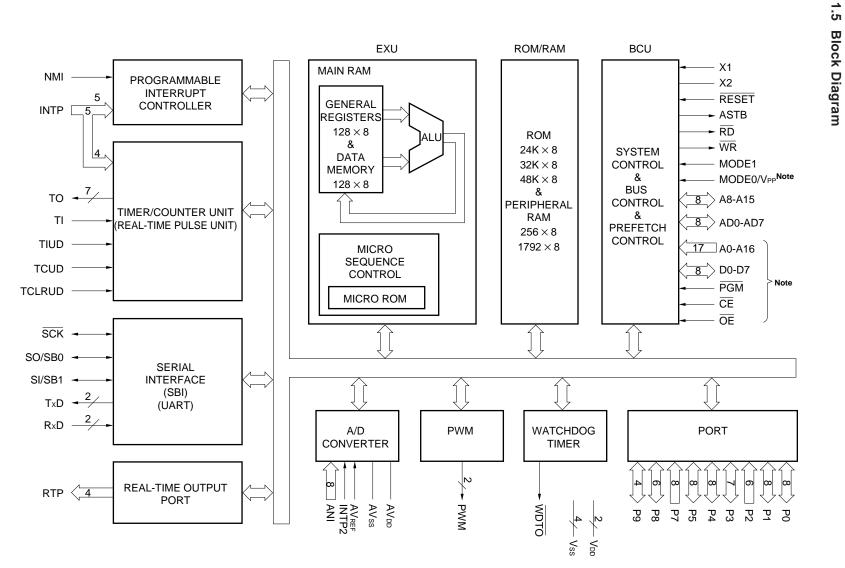

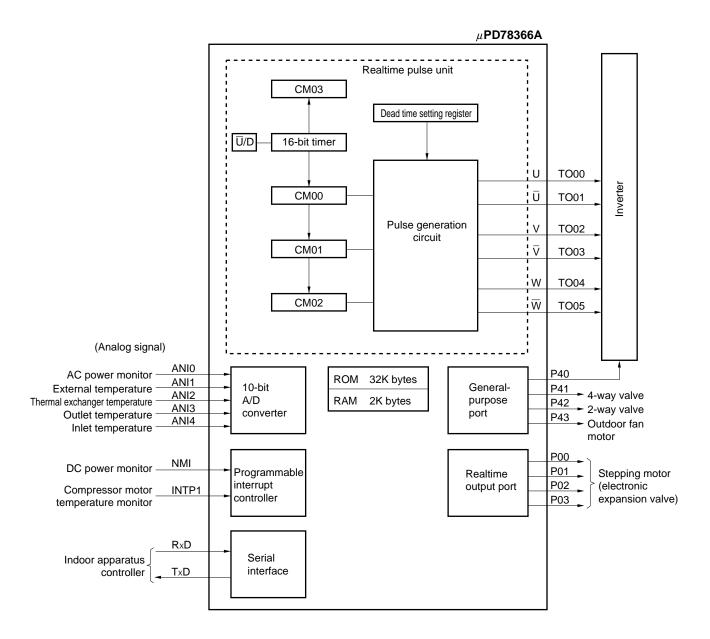

| 1.5    | Block Diagram                                                                             | 8  |

| 1.6    | Functional Outline                                                                        | 9  |

| 1.7    | Differences among $\mu$ PD78366A Subseries Products                                       | 11 |

| 1.8    | Application Example                                                                       | 12 |

| CHAPTE | R 2 PIN FUNCTIONS                                                                         | 13 |

| 2.1    | Pin Function List                                                                         | 13 |

|        | 2.1.1 Normal operation mode                                                               | 13 |

|        | 2.1.2 PROM programming mode ( $\mu$ PD78P368A only: MODE0/V <sub>PP</sub> = H, MODE1 = L) | 16 |

| 2.2    | Pin Functions                                                                             | 17 |

|        | 2.2.1 Normal operation mode                                                               | 17 |

|        | 2.2.2 PROM programming mode (µPD78P368A only)                                             | 25 |

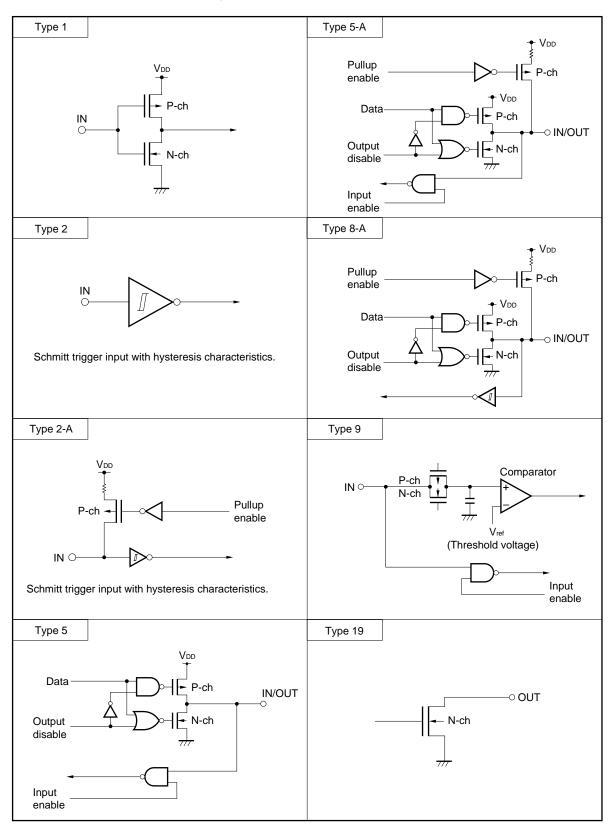

| 2.3    | I/O Circuits and Processing of Unused Pins                                                | 26 |

| CHAPTE | R 3 CPU ARCHITECTURE                                                                      | 29 |

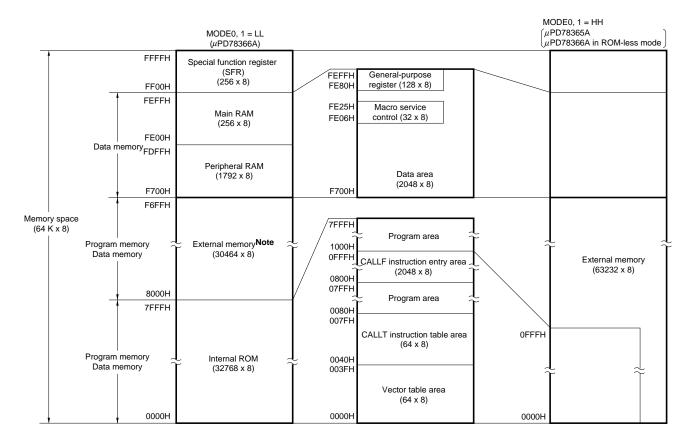

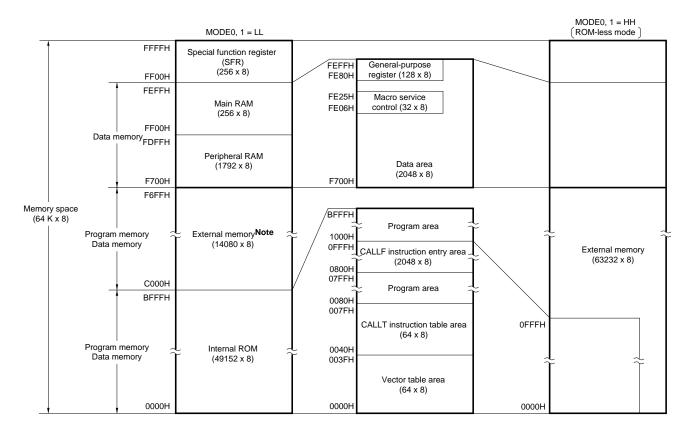

| 3.1    | Memory Space                                                                              | 29 |

|        | 3.1.1 Vector table area                                                                   | 34 |

|        | 3.1.2 CALLT instruction table area                                                        | 35 |

|        | 3.1.3 CALLF instruction entry area                                                        | 35 |

|        | 3.1.4 Internal RAM area                                                                   | 35 |

|        | 3.1.5 Special function register area                                                      | 39 |

|        | 3.1.6 External memory area                                                                | 39 |

| 3.2    | Processor Register                                                                        | 40 |

|        | 3.2.1 Control register                                                                    | 41 |

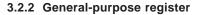

|        | 3.2.2 General-purpose register                                                            | 47 |

|        | 3.2.3 Special function register (SFR)                                                     | 49 |

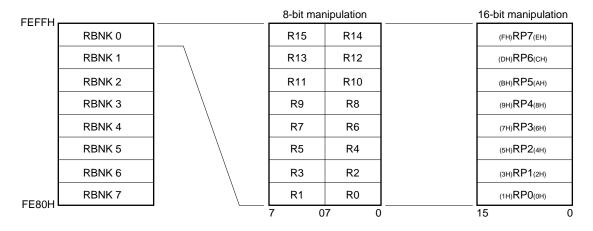

| 3.3    | Data Memory Addressing                                                                    | 56 |

|        | 3.3.1 General-purpose register addressing                                                 | 59 |

|        | 3.3.2 Short direct addressing                                                             | 60 |

|        | 3.3.3 Special function register (SFR) addressing                                          | 60 |

| CHAPTE | R 4 SUMMARY OF BLOCK FUNCTION                                                             | 61 |

| 4.1    | Execution Unit                                                                            | 61 |

| 4.2    | Bus Control Unit                                                                          | 61 |

|     |             | -       | am Memory and Data Memory           | 61       |

|-----|-------------|---------|-------------------------------------|----------|

| 4   | .4          |         |                                     | 62       |

| -   | .5          |         | ïme Pulse Unit                      | 62       |

|     |             |         | ime Output Port                     | 62       |

|     |             |         | onverter                            | 63       |

| -   |             |         | Interface                           | 63       |

| -   |             |         | Output Unit                         | 63       |

|     |             |         | dog Timer                           | 63       |

| 4   | .11         | Interru | ıpt Controller                      | 63       |

| СНА | PTER        | 8 5 PO  | RT FUNCTIONS                        | 65       |

| 5   | 5.1         | Hardw   | are Configuration                   | 65       |

| 5   | 5.2         | Port F  | unctions                            | 75       |

|     |             | 5.2.1   | Functions and features of I/O ports | 76       |

|     |             | 5.2.2   | I/O mode setting                    | 77       |

|     |             | 5.2.3   | Control mode setting                | 79       |

|     |             | 5.2.4   | Specifying pull-up resistor         | 86       |

| СНА | PTER        | 8 6 CL  | OCK GENERATOR                       | 89       |

| СНА | PTER        | 7 RE    | AL-TIME PULSE UNIT                  | 93       |

| 7   | <b>'</b> .1 |         | Configuration                       | 94       |

| -   |             |         | 0                                   | 94<br>94 |

| '   |             | 7.2.1   | Configuration                       | 94       |

|     |             | 7.2.2   | Control registers                   | 102      |

|     |             | 7.2.3   | Operation                           | 110      |

| 7   |             | -       | 1                                   | 141      |

| -   | -           | 7.3.1   | Configuration                       | 141      |

|     |             | 7.3.2   | Control registers                   | 142      |

|     |             | 7.3.3   | Operation                           | 143      |

| 7   | <b>.</b> 4  | Timer   | 2                                   | 144      |

|     |             | 7.4.1   | Configuration                       | 144      |

|     |             | 7.4.2   | Control registers                   | 146      |

|     |             | 7.4.3   | Operation                           | 150      |

| 7   | .5          | Timer   | 3                                   | 156      |

|     |             | 7.5.1   | Configuration                       | 156      |

|     |             | 7.5.2   | Control registers                   | 158      |

|     |             | 7.5.3   | Operation                           | 163      |

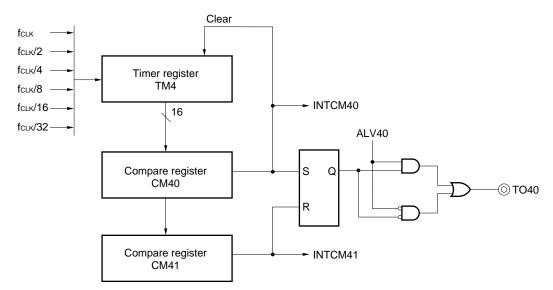

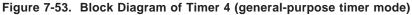

| 7   | .6          | Timer   | 4                                   | 171      |

|     |             | 7.6.1   | Configuration                       | 171      |

|     |             | 7.6.2   | Control registers                   | 173      |

|     |             | 7.6.3   | Operation                           | 180      |

| 7   | .7          | Real-T  | ime Output Function                 | 195      |

|     |             | 7.7.1   | Configuration                       | 195      |

|     |             | 7.7.2   | Control registers                   | 196      |

|     |             | 7.7.3   | Operation                           | 197      |

| CHAPTE     | R 8 A/D CONVERTER                                                    | 199        |

|------------|----------------------------------------------------------------------|------------|

| 0.4        |                                                                      | 000        |

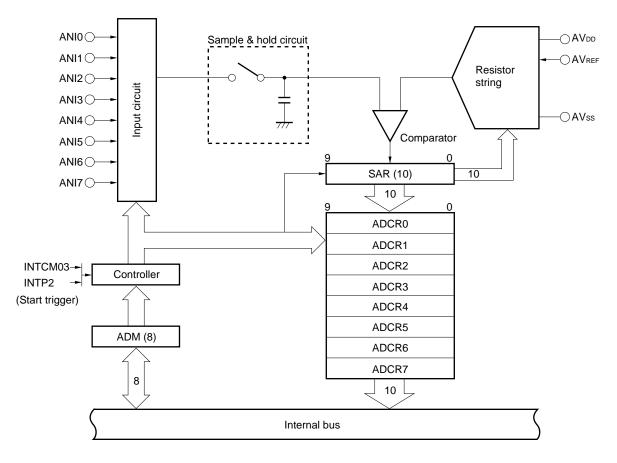

| 8.1        | Configuration                                                        | 200        |

| 8.2        | A/D Converter Mode Register (ADM)                                    | 203        |

| 8.3        | A/D Conversion Result Register (ADCR)                                | 207        |

| 8.4        | Operation                                                            | 209        |

|            | 8.4.1 Basic operation of A/D converter                               | 209        |

|            | 8.4.2 Operation mode of A/D converter                                | 213        |

| 8.5        | How to Read A/D Converter Characteristic Tables                      | 222        |

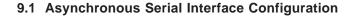

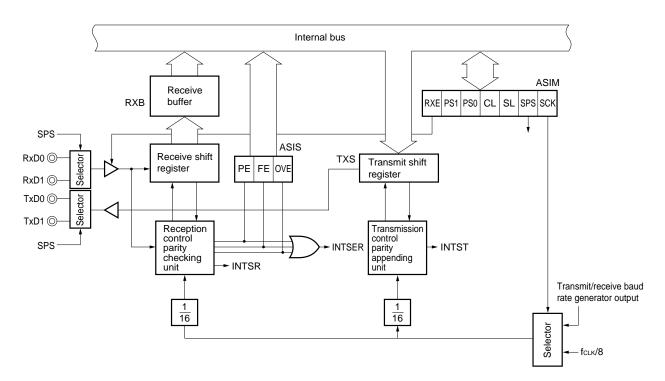

| CHAPTE     | R 9 ASYNCHRONOUS SERIAL INTERFACE                                    | 225        |

| 9.1        | Asynchronous Serial Interface Configuration                          | 226        |

| 9.2        | Selecting Pins for Serial Communication                              | 228        |

| 9.3        | Setting Pins for Serial Communication                                | 230        |

| 9.4        | Data Format Setting                                                  | 232        |

| 9.5        | Baud Rate Setting                                                    | 234        |

|            | 9.5.1 Baud rate generator configuration                              | 236        |

|            | 9.5.2 Specific baud rate setting                                     | 238        |

| 9.6        | Transmitting Data                                                    | 240        |

| 9.7        | Receiving Data                                                       | 242        |

| 9.8        | Transmitting/Receiving Data Using Macro Service                      | 242        |

| 9.0<br>9.9 | If Reception Error Occurs                                            | 244<br>246 |

| 9.9        | I Reception Error Occurs                                             | 240        |

| CHAPTE     | R 10 CLOCKED SERIAL INTERFACE                                        | 249        |

| 10.1       | Clocked Serial Interface Configuration                               | 250        |

| 10.2       | Setting Pins for Serial Communication                                | 252        |

| 10.3       | Baud Rate Setting                                                    | 254        |

|            | 10.3.1 Baud rate generator configuration                             | 256        |

|            | 10.3.2 Specific baud rate setting                                    | 258        |

| 10.4       | Two Operation Modes of Clocked Serial Interface                      | 260        |

| 10.5       | Three-Wire Serial I/O Mode Setting                                   | 262        |

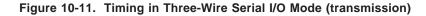

|            | 10.5.1 Transmission in three-wire serial I/O mode                    | 264        |

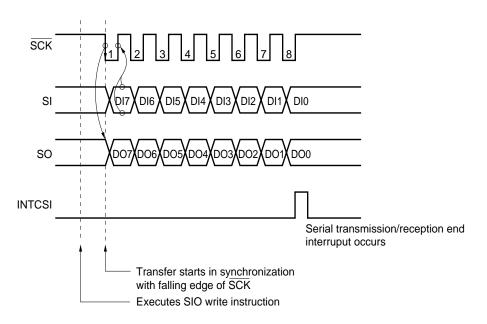

|            | 10.5.2 Reception in three-wire serial I/O mode                       | 266        |

|            | 10.5.3 Transmission/reception in three-wire serial I/O mode          | 268        |

|            | 10.5.4 Corrective action in case shift operation is not synchronized | 271        |

| 10.6       | SBI Mode Setting                                                     | 272        |

|            | 10.6.1 SBI data format                                               | 274        |

|            | 10.6.2 Controlling and detecting status of serial bus                | 280        |

|            | 10.6.3 Communicating with SBI                                        | 286        |

|            | 10.6.4 Operation only when address is received                       | 290        |

|            |                                                                      | 200        |

| CHAPTE     | R 11 PWM SIGNAL OUTPUT FUNCTION                                      | 293        |

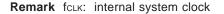

| 11.1       | Configuration                                                        | 293        |

| 11.2       | Control Register                                                     | 295        |

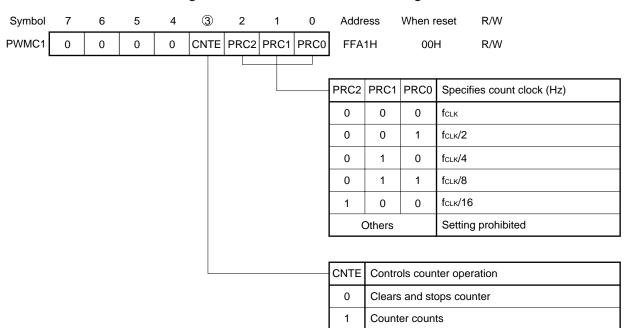

|            | 11.2.1 PWM control registers (PWMC0, PWMC1)                          | 295        |

|            |                                                                      |            |

|         | 11.2.2 PWM buffer registers (PWM0, PWM1)                               | 296        |

|---------|------------------------------------------------------------------------|------------|

|         | 11.2.3 Compare registers (CMP0, CMP1)                                  | 296        |

| 11.3    | Operation                                                              | 297        |

|         |                                                                        |            |

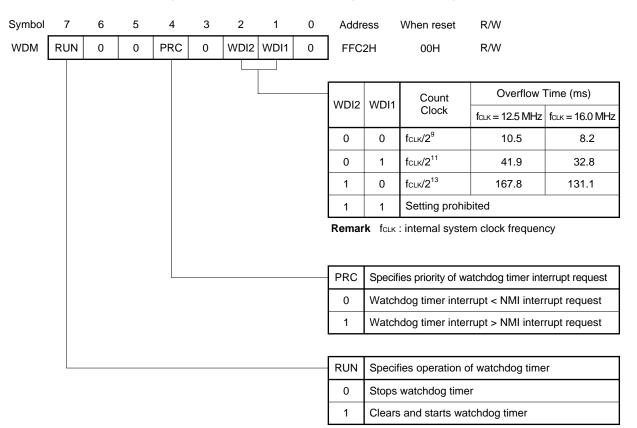

| CHAPTER | R 12 WATCHDOG TIMER                                                    | 299        |

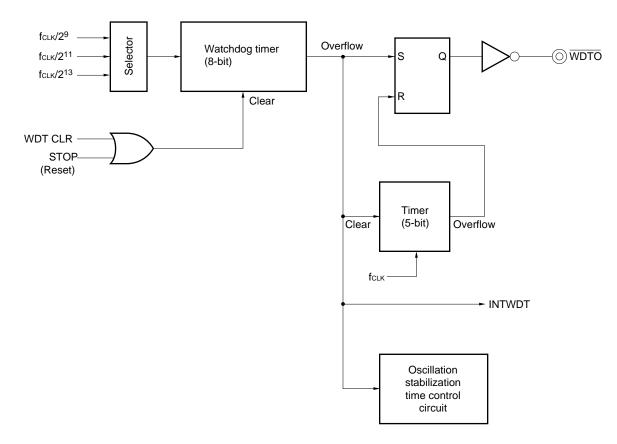

| 12.1    | Configuration                                                          | 299        |

| 12.1    | Watchdog Timer Mode Register (WDM)                                     | 300        |

| 12.3    | Watchdog Timer Output Pin                                              | 302        |

| 12.4    | Application Example                                                    | 302        |

|         |                                                                        |            |

| CHAPTER | R 13 INTERRUPT FUNCTION                                                | 303        |

| 13.1    | Interrupt Requests                                                     | 305        |

|         | 13.1.1 Non-maskable interrupt                                          | 305        |

|         | 13.1.2 Maskable interrupt                                              | 305        |

|         | 13.1.3 Software interrupt                                              | 305        |

|         | 13.1.4 Op-code trap interrupt                                          | 306        |

| 13.2    | Interrupt Servicing Mode                                               | <b>306</b> |

| 10.2    | 13.2.1 Vectored interrupt service                                      | 306        |

|         | 13.2.2 Macro service                                                   | 306        |

|         | 13.2.3 Context switching                                               | 306        |

| 13.3    | Control Registers                                                      | <b>307</b> |

| 10.0    | 13.3.1 Interrupt control registers                                     | 309        |

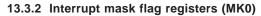

|         | 13.3.2 Interrupt mask flag registers (MK0)                             | 313        |

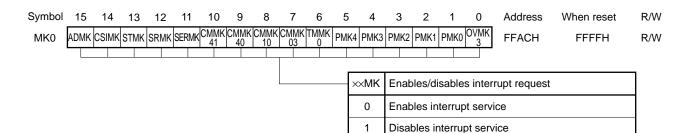

|         | 13.3.3 Interrupt mode control register (IMC)                           | 315        |

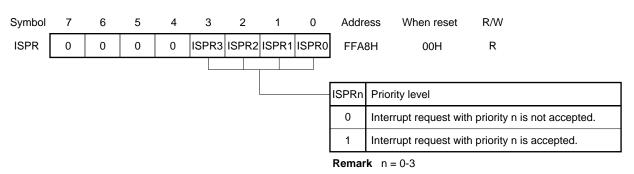

|         | 13.3.4 In-service priority register (ISPR)                             | 316        |

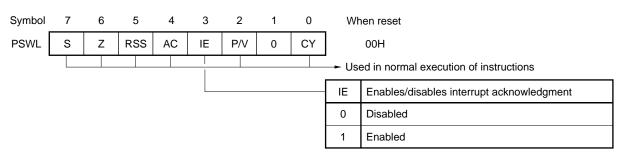

|         | 13.3.5 Program status word (PSW)                                       | 317        |

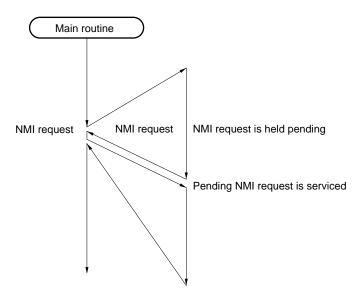

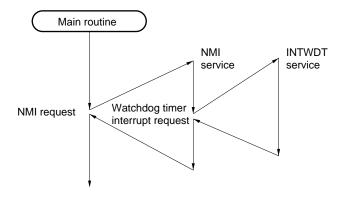

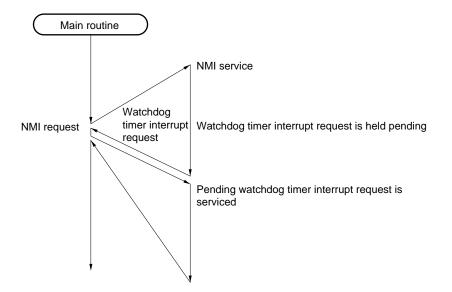

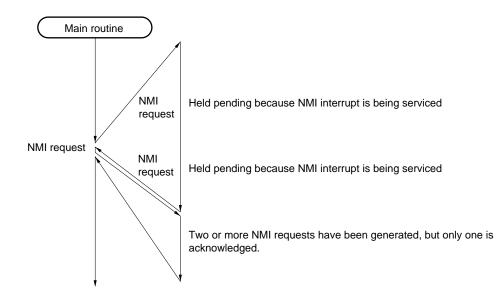

| 13.4    | Non-Maskable Interrupt Acknowledgment Operation                        | 318        |

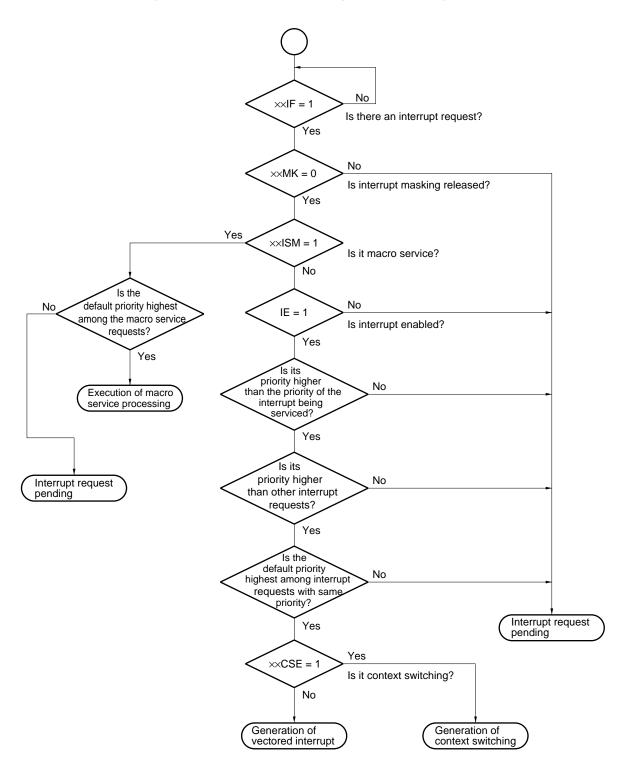

| 13.5    | Maskable Interrupt Acknowledgment Operation                            | 322        |

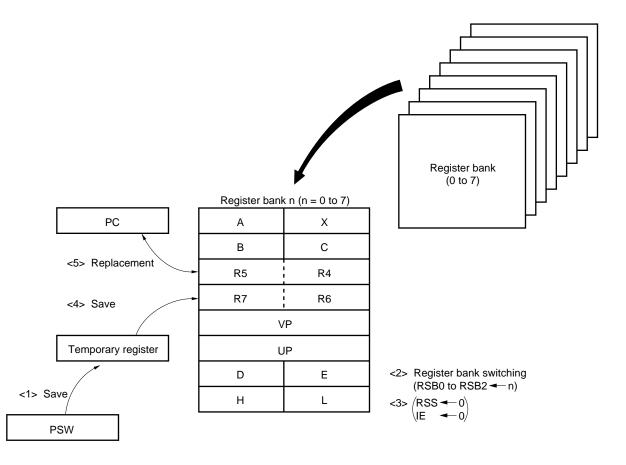

| 10.0    | 13.5.1 Vectored interrupt                                              | 324        |

|         | 13.5.2 Context switching                                               | 324        |

|         | 13.5.3 Maskable interrupt priority                                     | 326        |

| 13.6    | Software Interrupt Acknowledgment Operation                            | 332        |

| 10.0    | 13.6.1 Software interrupt acknowledgment operation by BRK instruction  | 332        |

|         | 13.6.2 Software interrupt (context switching) acknowledgment operation | 552        |

|         | by BRKCS instruction                                                   | 332        |

| 13.7    | Op-Code Trap Interrupt Acknowledgment Operation                        | 335        |

| 13.8    | Macro Service Function                                                 | 336        |

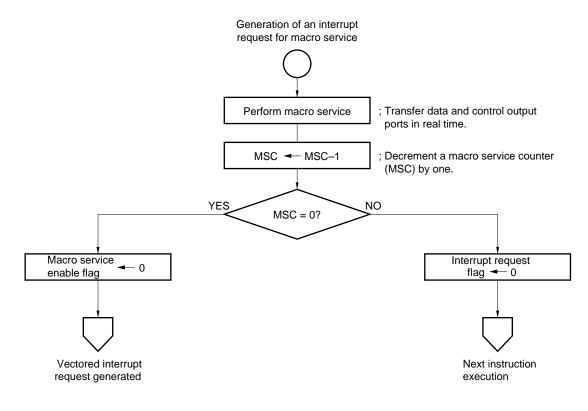

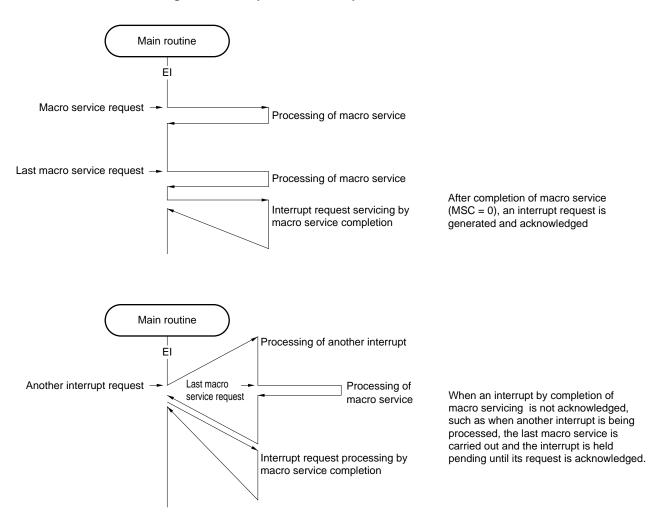

| 10.0    | 13.8.1 Outline of macro service                                        | 336        |

|         | 13.8.2 Basic function of macro service                                 | 339        |

|         | 13.8.3 Operation at completion of macro service                        | 341        |

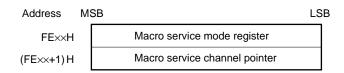

|         | 13.8.4 Macro service control register                                  | 341<br>342 |

|         | 13.8.5 Macro service mode                                              | 342<br>344 |

|         | 13.8.6 Macro service operation                                         | 344<br>344 |

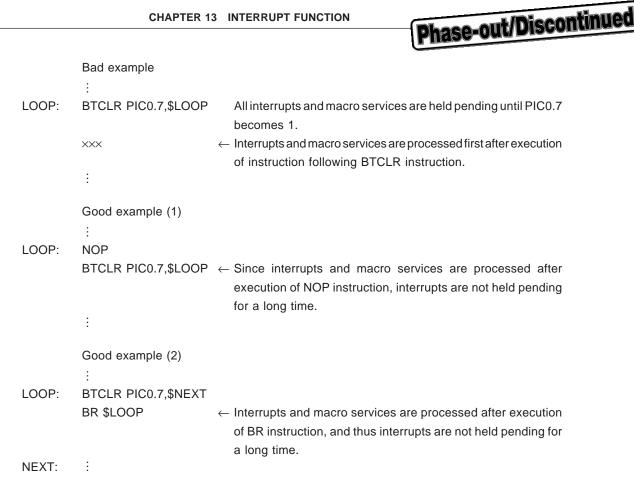

| 13.9    | ·                                                                      | 344        |

| 13.9    | Cases where Interrupt Request and Macro Service are                    | 254        |

| 40.40   | Temporarily Held Pending                                               | 354        |

| 13.10   | Instructions whose Execution Is Temporarily Suspended by Interrupts    | 250        |

|         | and Macro Services                                                     | 356        |

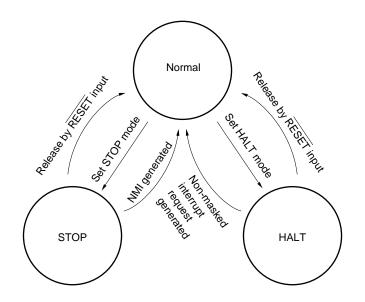

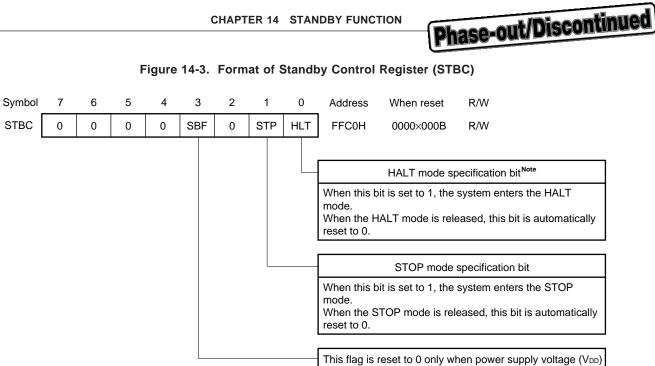

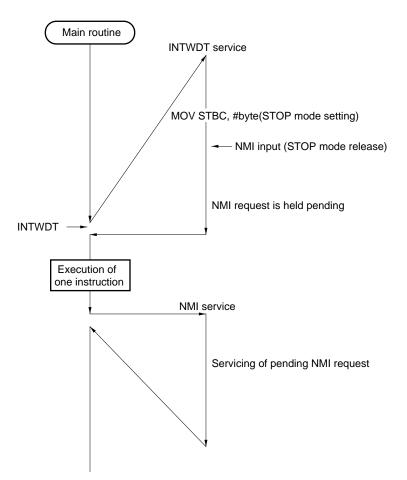

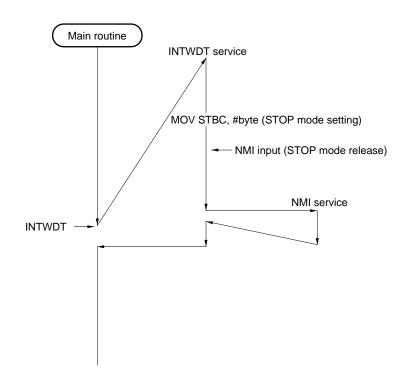

| CHAPTE | R 14 STANDBY FUNCTION                                                   | 357 |

|--------|-------------------------------------------------------------------------|-----|

| 14.1   | Function Overview                                                       | 357 |

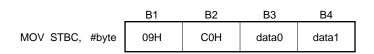

| 14.2   | Standby Control Register (STBC)                                         | 358 |

|        |                                                                         |     |

| 14.3   | Operation                                                               | 360 |

|        | 14.3.1 HALT mode                                                        | 360 |

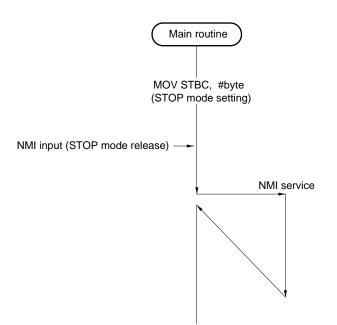

|        | 14.3.2 STOP mode                                                        | 363 |

| CHAPTE | R 15 RESET FUNCTION                                                     | 373 |

| CHAPTE | R 16 BUS INTERFACE FUNCTION                                             | 377 |

| 46.4   | External Device Expension Expetien for UDD702004                        | 077 |

| 16.1   | External Device Expansion Function for µPD78366A                        | 377 |

| 16.2   | Access to External Devices by $\mu$ PD78365A                            | 383 |

| 16.3   | Control Registers                                                       | 384 |

|        | 16.3.1 Memory expansion mode register                                   | 384 |

|        | 16.3.2 Programmable wait control register                               | 386 |

|        |                                                                         |     |

| CHAPTE | R 17 PROGRAMMING FOR $\mu$ PD78P368A                                    | 389 |

| 47.4   | On easting Made                                                         | 200 |

| 17.1   | Operating Mode                                                          | 390 |

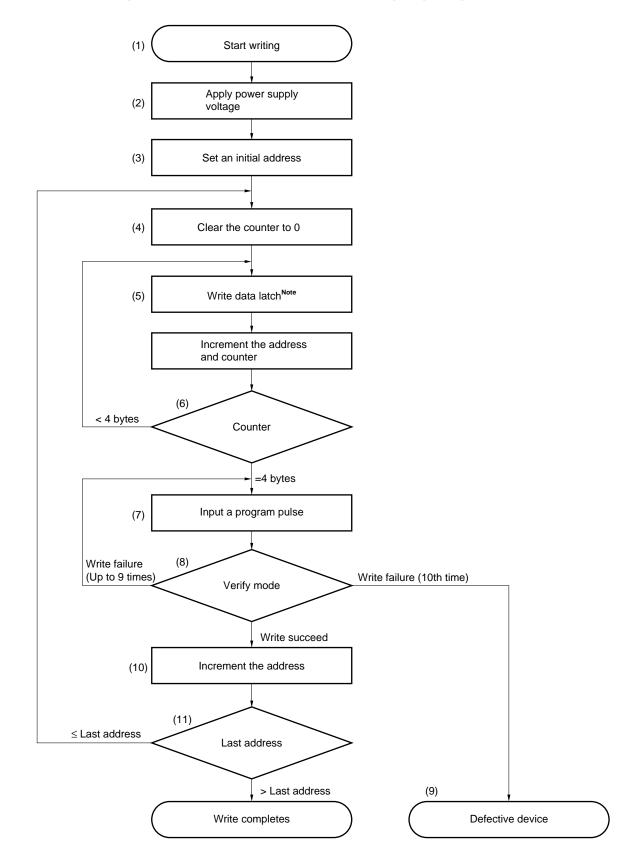

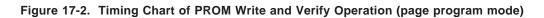

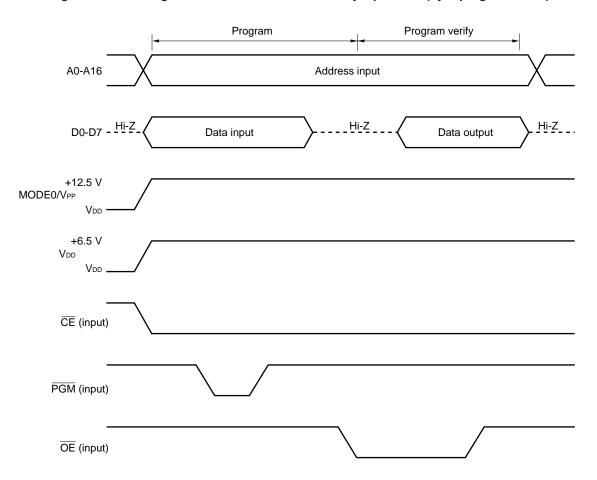

| 17.2   | Procedure for Writing on PROM (Page Program Mode)                       | 391 |

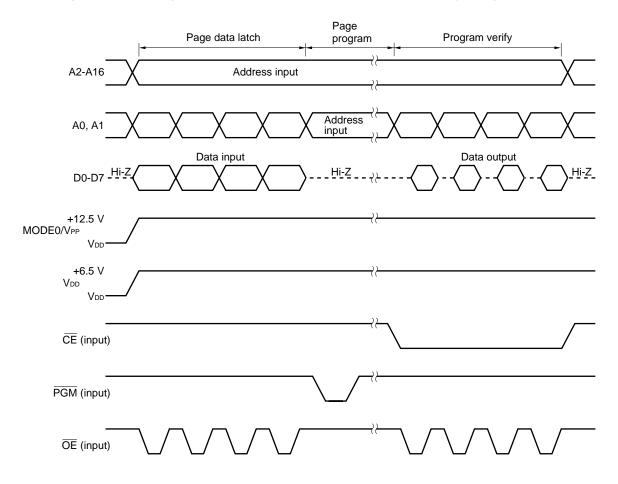

| 17.3   | Procedure for Writing on PROM (Byte Program Mode)                       | 394 |

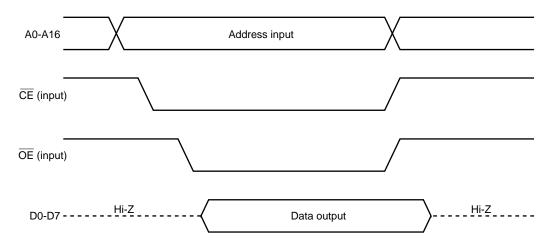

| 17.4   | Procedure for Reading from PROM                                         | 397 |

| 17.5   | Erasure Characteristics (µPD78P368AKL only)                             | 398 |

| 17.6   | Sticker on Erasure Window (µPD78P368AKL only)                           | 398 |

| 17.7   | Screening of One-Time PROM Products                                     | 398 |

|        |                                                                         |     |

| CHAPTE | R 18 INSTRUCTION SET                                                    | 399 |

| 18.1   | Operand Identifier and Description                                      | 399 |

| 18.2   | Legend                                                                  | 402 |

| 18.3   | Notational Symbols in Flag Operation Field                              | 403 |

|        |                                                                         |     |

| 18.4   | Differences between $\mu$ PD78366A and $\mu$ PD78328 in Instruction Set | 403 |

| 18.5   | Operations of Basic Instructions                                        | 404 |

| CHAPTE | R 19 INSTRUCTION EXECUTION RATE                                         | 421 |

|        |                                                                         |     |

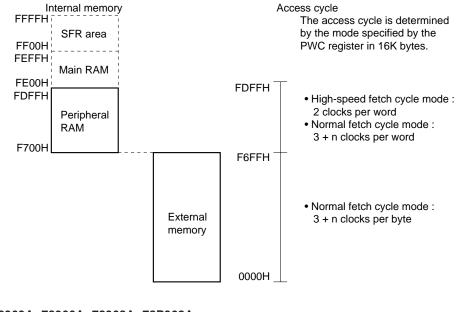

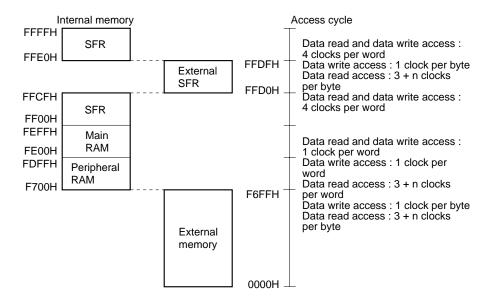

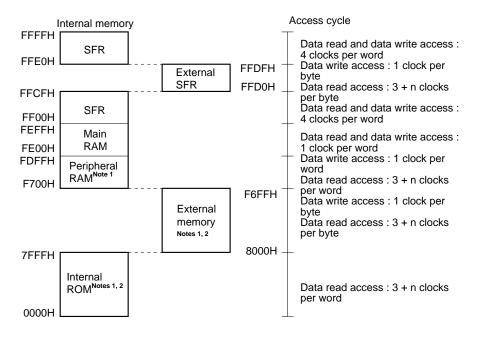

| 19.1   | Memory Space and Access Speed                                           | 421 |

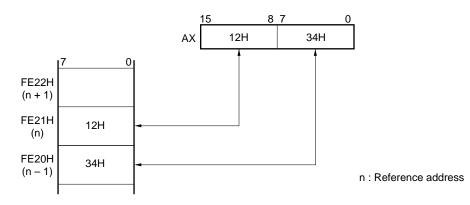

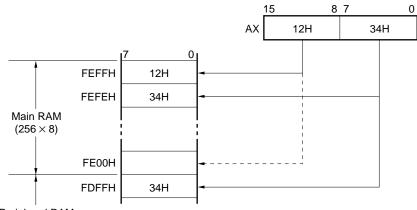

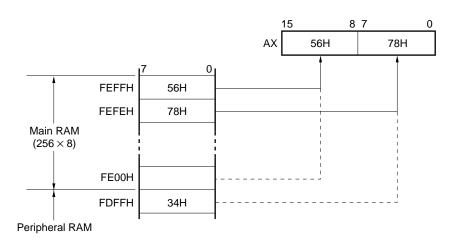

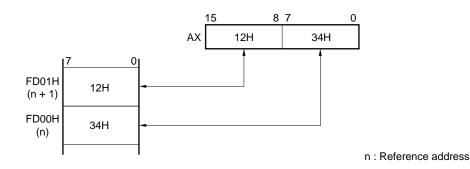

|        | 19.1.1 Main RAM and peripheral RAM                                      | 421 |

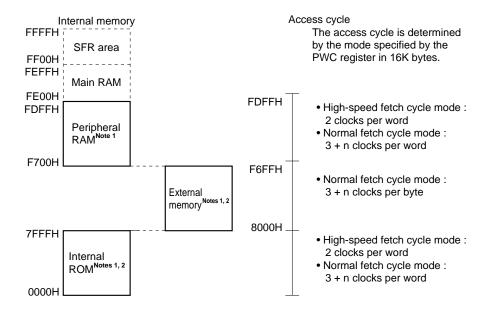

|        | 19.1.2 Memory access                                                    | 422 |

| 19.2   | Interrupt Execution Rate                                                | 428 |

| 19.3   | Calculating Number of Execution Clocks                                  | 429 |

|        |                                                                         | .20 |

| CHAPTE | R 20 CAUTIONS                                                           | 433 |

| 20.1   | Cautions for CHAPTER 2 PIN FUNCTIONS                                    | 433 |

| 20.2   | Cautions for CHAPTER 3 CPU ARCHITECTURE                                 | 433 |

|        | Cautions for CHAPTER 5 PORT FUNCTIONS                                   | 434 |

|        |                                                                         |     |

| 20.4 Cautions for CHAPTER 6 CLOCK GENERATOR                                | 435 |

|----------------------------------------------------------------------------|-----|

| 20.5 Cautions for CHAPTER 7 REAL-TIME PULSE UNIT                           | 436 |

| 20.6 Cautions for CHAPTER 8 A/D CONVERTER                                  | 438 |

| 20.7 Cautions for CHAPTER 9 ASYNCHRONOUS SERIAL INTERFACE                  | 439 |

| 20.8 Cautions for CHAPTER 10 CLOCKED SERIAL INTERFACE                      | 440 |

| 20.9 Cautions for CHAPTER 11 PWM SIGNAL OUTPUT FUNCTION                    | 440 |

| 20.10 Cautions for CHAPTER 12 WATCHDOG TIMER                               | 440 |

| 20.11 Cautions for CHAPTER 13 INTERRUPT FUNCTION                           | 441 |

| 20.12 Cautions for CHAPTER 14 STANDBY FUNCTION                             | 444 |

| 20.13 Cautions for CHAPTER 15 RESET FUNCTION                               | 444 |

| 20.14 Cautions for CHAPTER 16 BUS INTERFACE FUNCTION                       | 445 |

| 20.15 Cautions for CHAPTER 19 INSTRUCTION EXECUTION RATE                   | 445 |

|                                                                            |     |

| APPENDIX A DIFFERENCE BETWEEN $\mu$ PD78366A AND $\mu$ PD78328             | 447 |

|                                                                            |     |

| APPENDIX B TOOLS                                                           | 451 |

|                                                                            |     |

| B.1 Development Tools                                                      | 451 |

| B.2 Built-In Software                                                      | 456 |

|                                                                            |     |

| APPENDIX C REGISTER INDEX                                                  | 459 |

|                                                                            |     |

| C.1 Register Index (In Alphabetical Order with Respect to Register Name)   | 459 |

| C.2 Register Index (In Alphabetical Order with Respect to Register Symbol) | 462 |

|                                                                            |     |

| APPENDIX D FUNCTION INDEX                                                  | 467 |

|                                                                            |     |

| APPENDIX E REVISION HISTORY                                                | 475 |

|                                                                            |     |

### LIST OF FIGURES (1/6)

| Figure No. | Title                                                                                       | Page |

|------------|---------------------------------------------------------------------------------------------|------|

| 2-1        | I/O Circuit of Each Pin                                                                     | 27   |

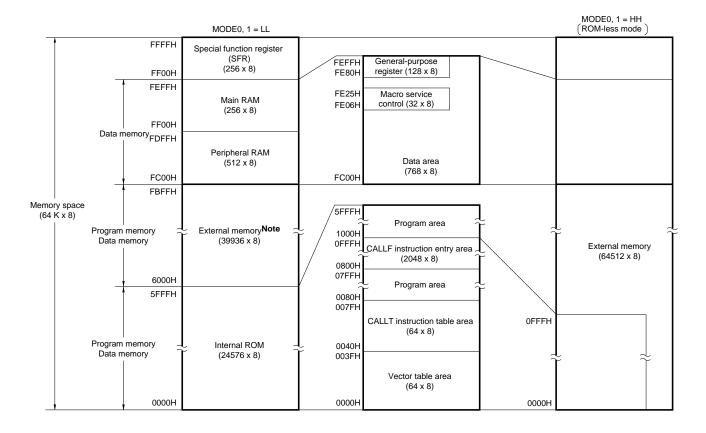

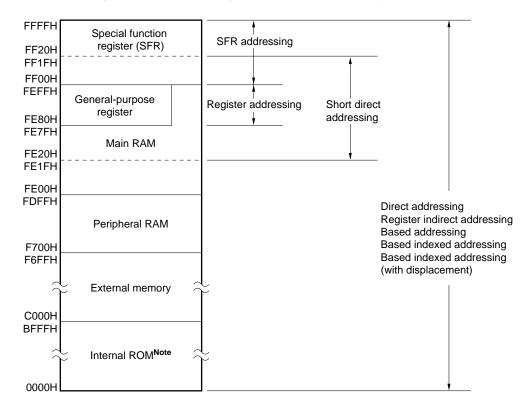

| 3-1        | Memory Map (µPD78365A, 78366A)                                                              | 30   |

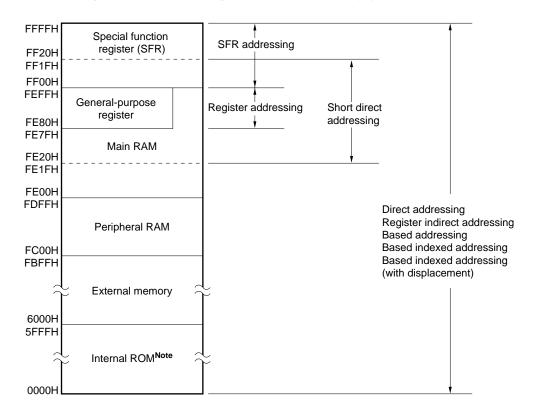

| 3-2        | Memory Map (µPD78368A)                                                                      | 31   |

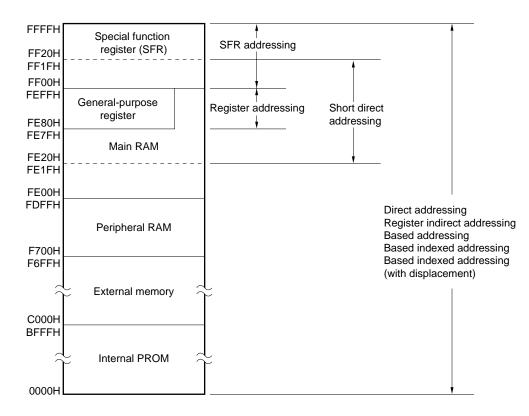

| 3-3        | Memory Map (µPD78363A)                                                                      | 32   |

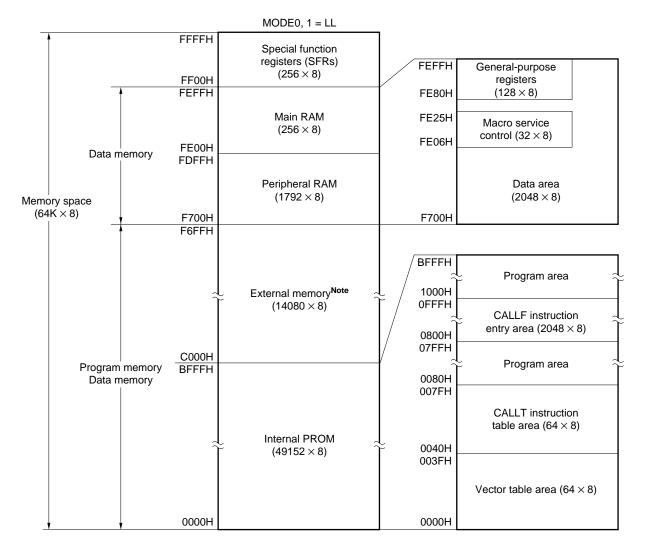

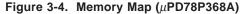

| 3-4        | Memory Map (μPD78P368A)                                                                     | 33   |

| 3-5        | Register Configuration                                                                      | 40   |

| 3-6        | Format of Program Status Word                                                               | 42   |

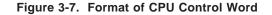

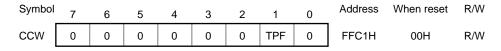

| 3-7        | Format of CPU Control Word                                                                  | 46   |

| 3-8        | Manipulation Bits of General-Purpose Registers                                              | 47   |

| 3-9        | Addressing Space of Data Memory (µPD78365A, 78366A)                                         | 56   |

| 3-10       | Addressing Space of Data Memory (µPD78368A)                                                 | 57   |

| 3-11       | Addressing Space of Data Memory (µPD78363A)                                                 | 58   |

| 3-12       | Addressing Space of Data Memory (µPD78P368A)                                                | 59   |

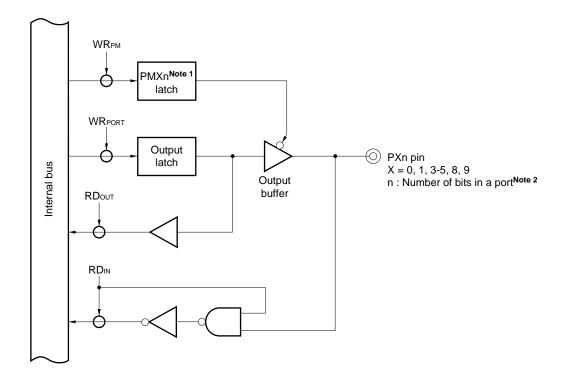

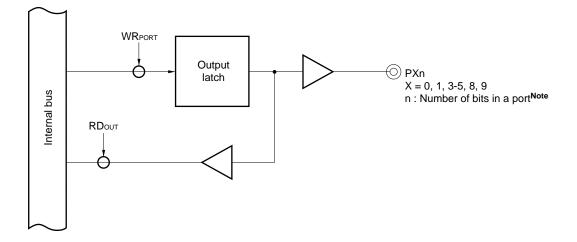

| 5-1        | Basic I/O Port Configuration                                                                | 66   |

| 5-2        | Port Specified as Output Port                                                               | 67   |

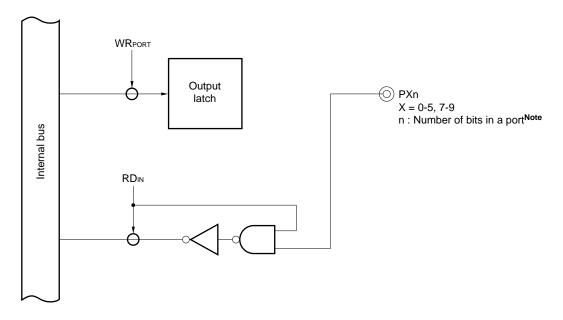

| 5-3        | Port Specified as Input Port                                                                | 68   |

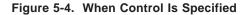

| 5-4        | When Control Is Specified                                                                   | 69   |

| 5-5        | Format of Port Read Control Register                                                        | 72   |

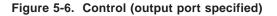

| 5-6        | Control (output port specified)                                                             | 73   |

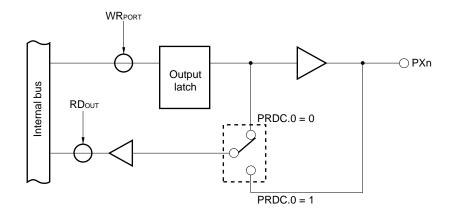

| 5-7        | Port Configuration                                                                          | 75   |

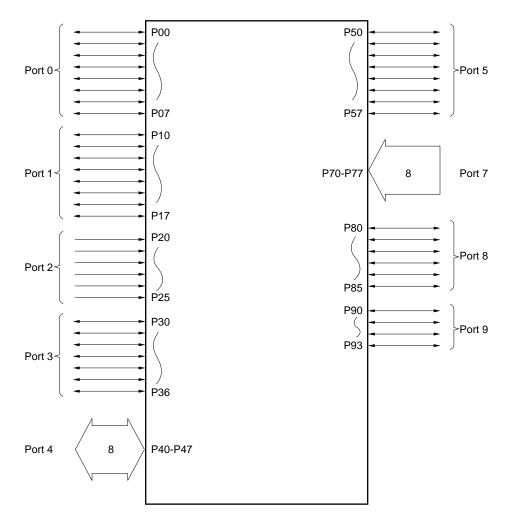

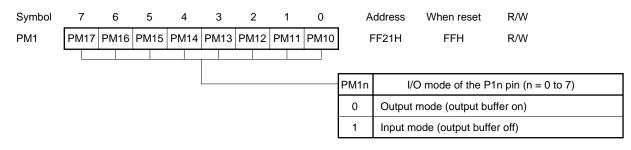

| 5-8        | Format of Port 0 Mode Register                                                              | 77   |

| 5-9        | Format of Port 1 Mode Register                                                              | 77   |

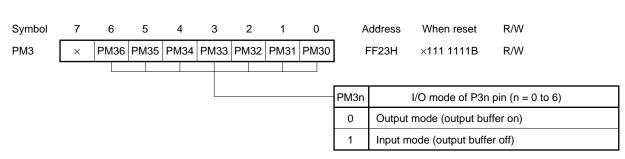

| 5-10       | Format of Port 3 Mode Register                                                              | 78   |

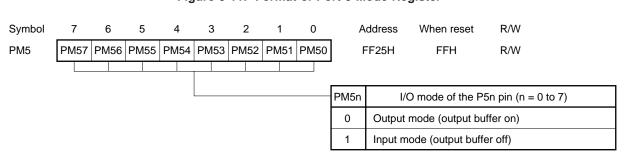

| 5-11       | Format of Port 5 Mode Register                                                              | 78   |

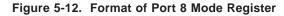

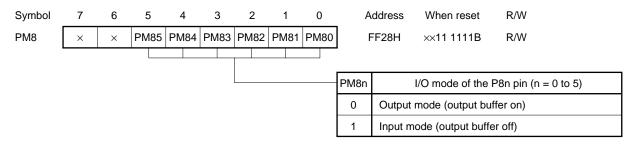

| 5-12       | Format of Port 8 Mode Register                                                              | 78   |

| 5-13       | Format of Port 9 Mode Register                                                              | 79   |

| 5-14       | Format of Port 0 Mode Control Register                                                      | 82   |

| 5-15       | Format of Port 3 Mode Control Register                                                      | 83   |

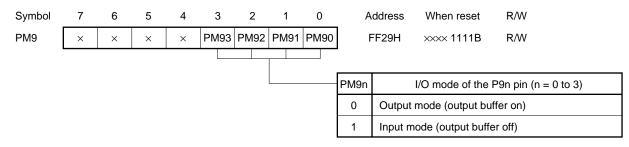

| 5-16       | Format of Port 8 Mode Control Register                                                      | 84   |

| 5-17       | Format of Memory Expansion Mode Register                                                    | 85   |

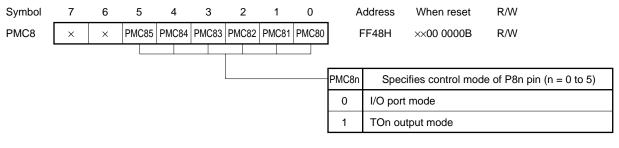

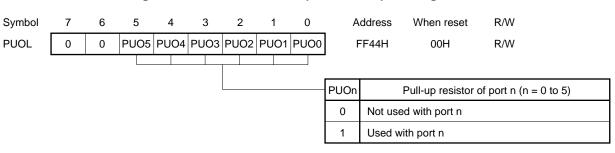

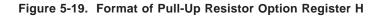

| 5-18       | Format of Pull-Up Resistor Option Register L                                                | 87   |

| 5-19       | Format of Pull-Up Resistor Option Register H                                                | 87   |

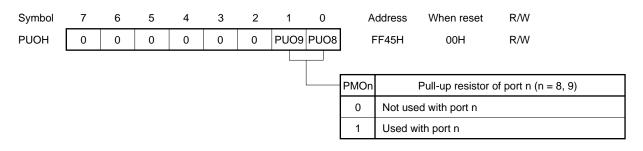

| 6-1        | Block Diagram of Clock Generator                                                            | 89   |

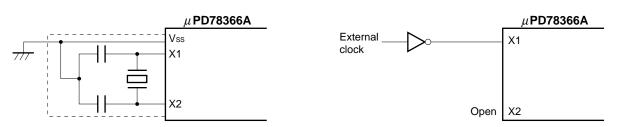

| 6-2        | External Circuitry of System Clock Oscillation Circuit                                      | 90   |

| 6-3        | Examples of Wrong Resonator Connection Circuitry                                            | 91   |

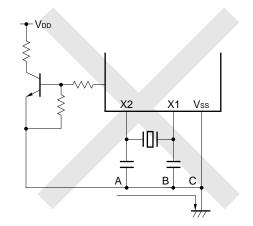

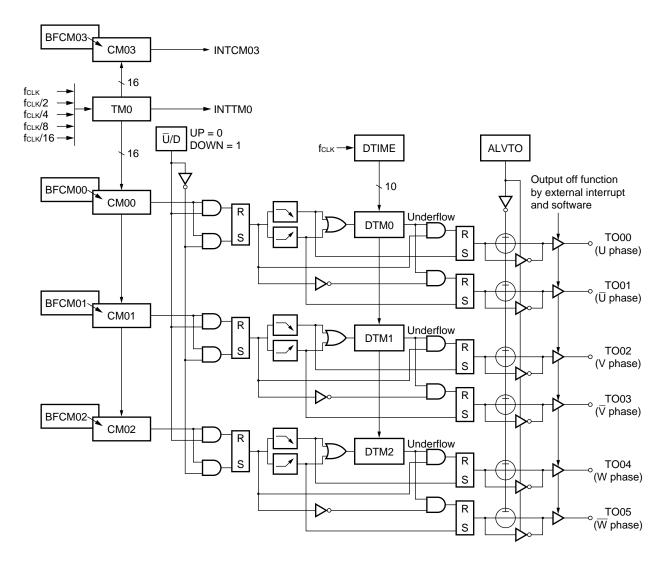

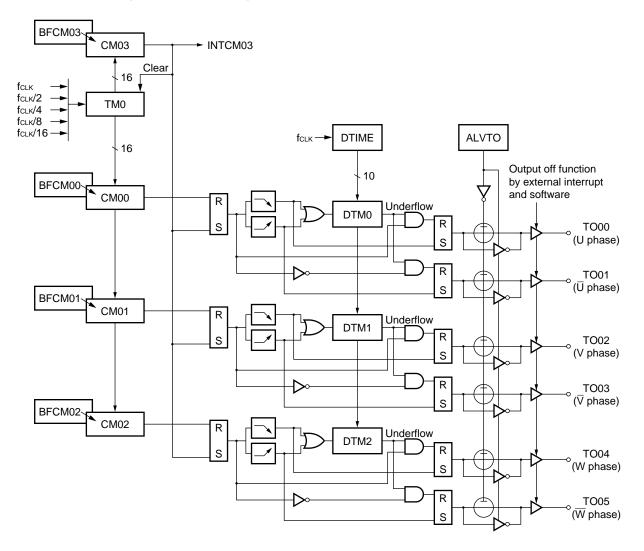

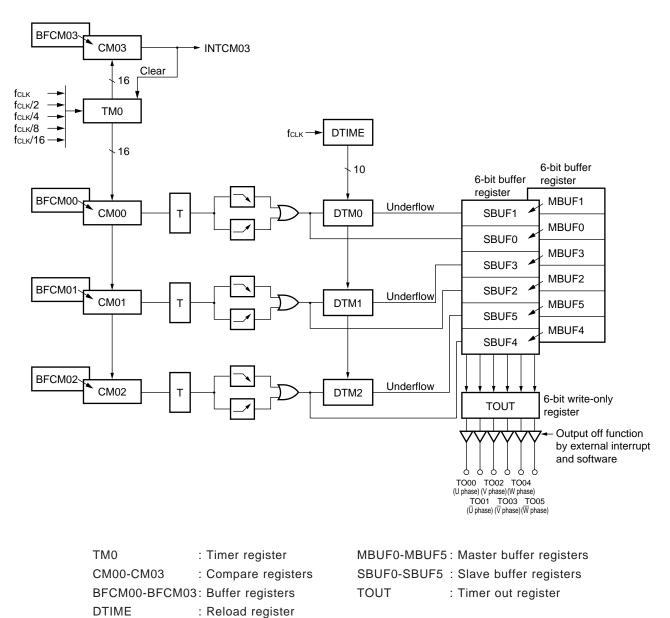

| 7-1        | Block Diagram of Timer 0 (PWM mode 0 symmetric triangular wave, asymmetric triangular wave) | 95   |

| 7-2        | Block Diagram of Timer 0 (PWM mode 0 toothed wave)                                          | 96   |

| 7-3        | Block Diagram of Timer 0 (PWM mode 1)                                                       | 97   |

### LIST OF FIGURES (2/6)

| Figure No. | Title                                                                           | Page |

|------------|---------------------------------------------------------------------------------|------|

| 7-4        | Format of Timer Unit Mode Register 0                                            | 103  |

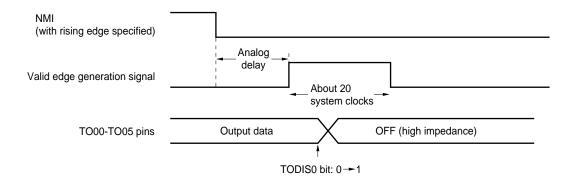

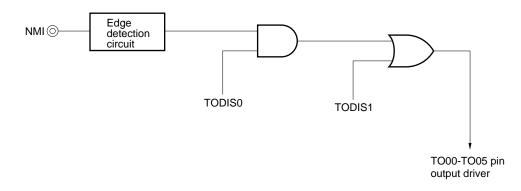

| 7-5        | Configuration of Output Driver off Function                                     | 105  |

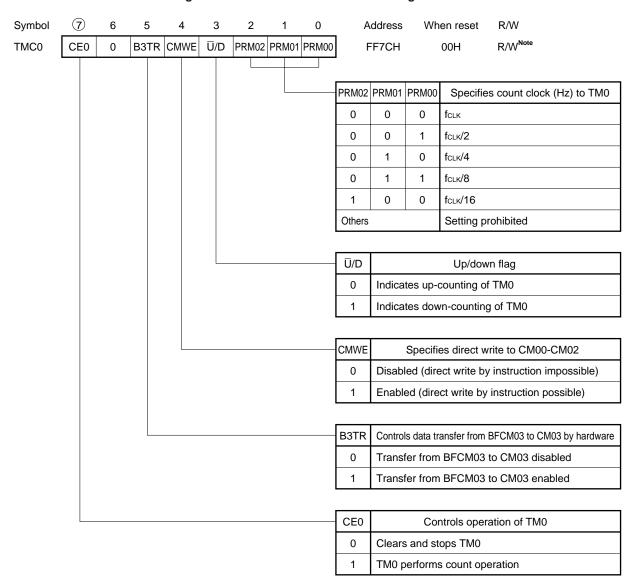

| 7-6        | Format of Timer Control Register 0                                              | 106  |

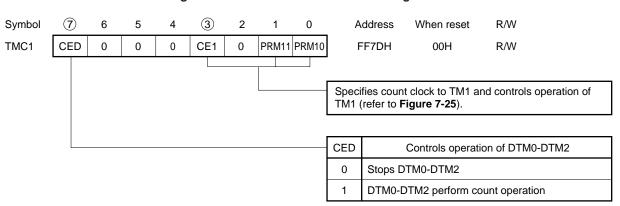

| 7-7        | Format of Timer Control Register 1                                              | 108  |

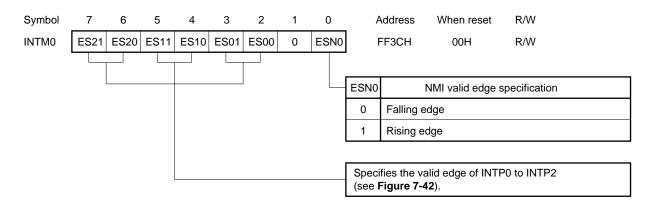

| 7-8        | External Interrupt Mode Register 0 Format                                       | 109  |

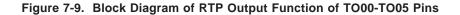

| 7-9        | Block Diagram of RTP Output Function of TO00-TO05 Pins                          | 111  |

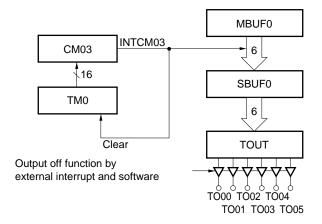

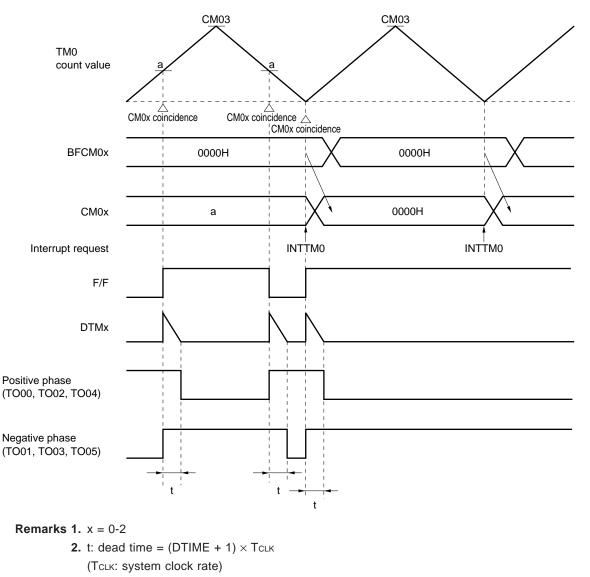

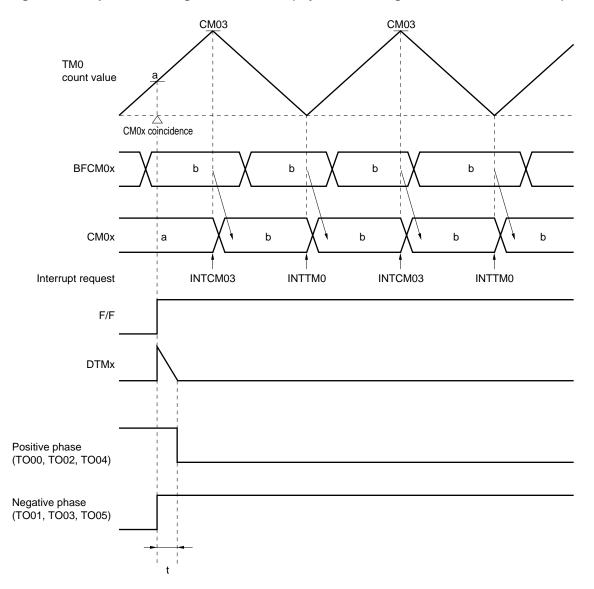

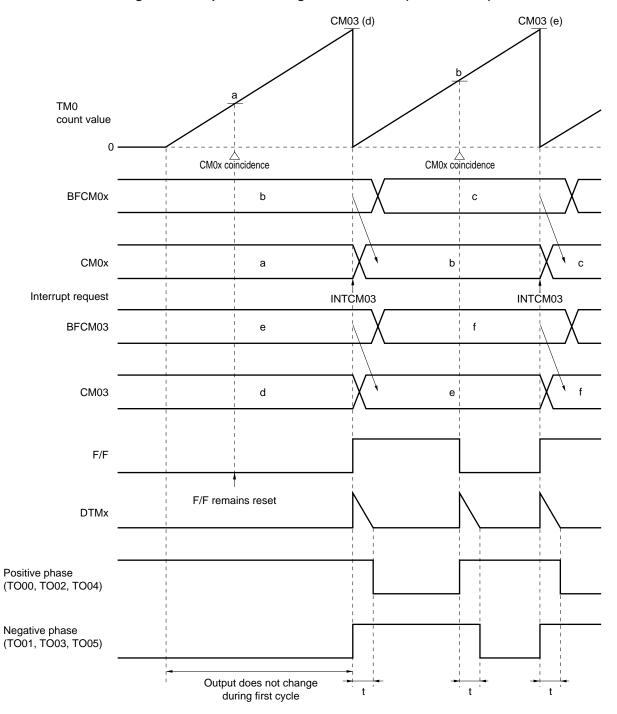

| 7-10       | Operation Timing in PWM Mode 0 (symmetric triangular wave)                      | 116  |

| 7-11       | Operation Timing in PWM Mode 0 (symmetric triangular wave, BFCM0x $\geq$ CM03)  | 117  |

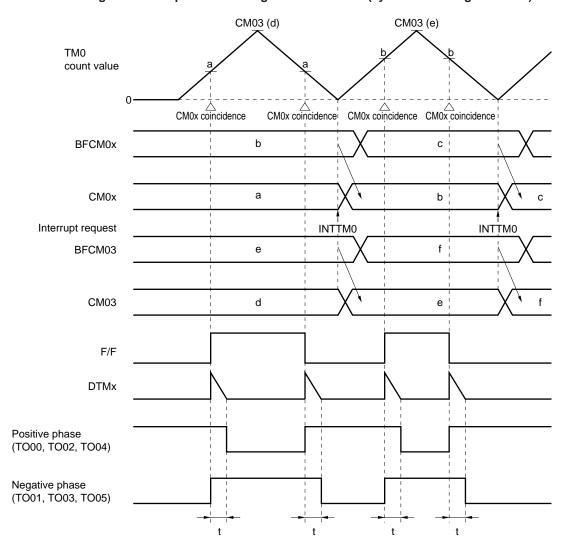

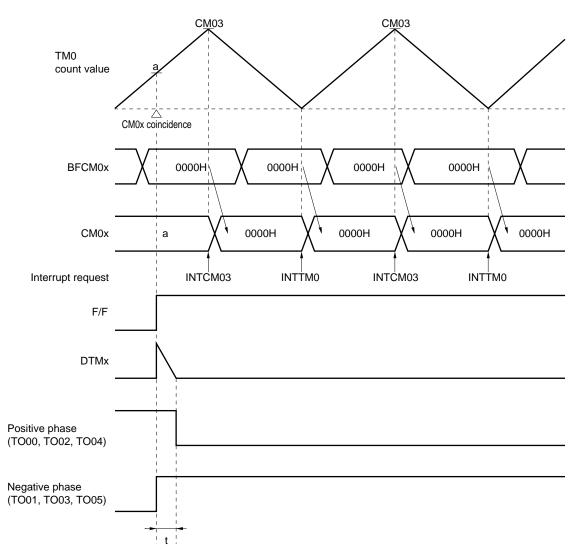

| 7-12       | Operation Timing in PWM Mode 0 (symmetric triangular wave, BFCM0x = 0000H)      | 118  |

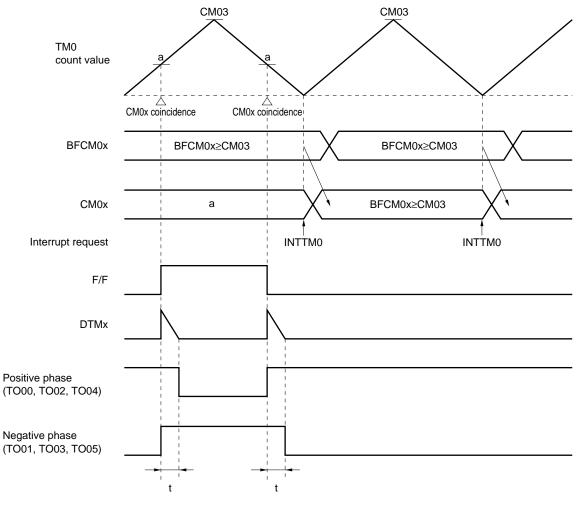

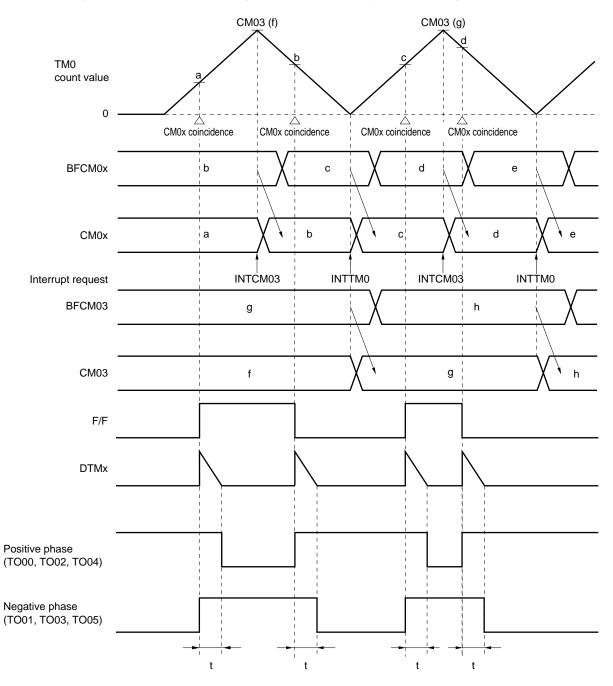

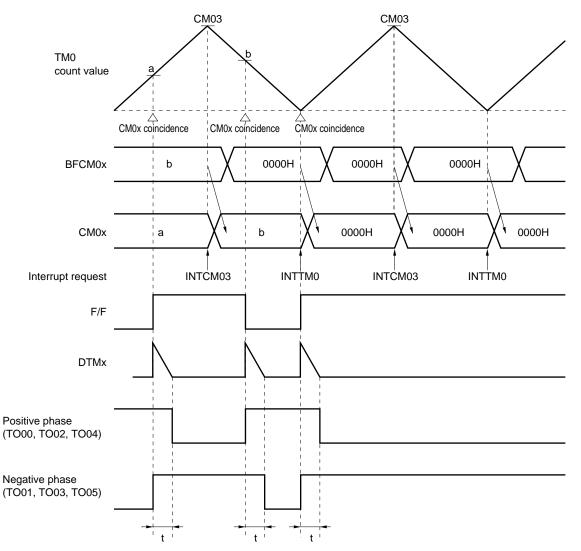

| 7-13       | Operation Timing in PWM Mode 0 (asymmetric triangular wave)                     | 123  |

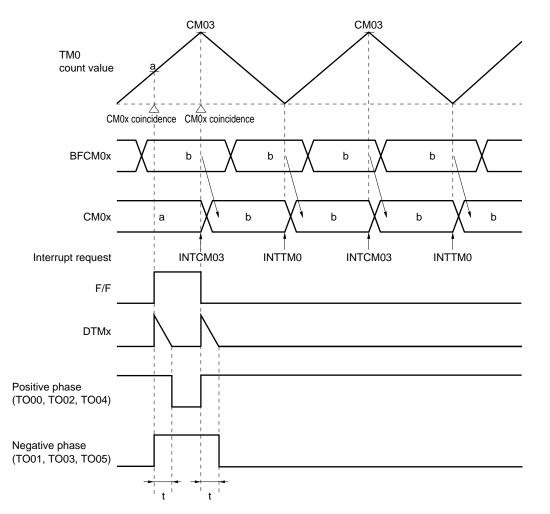

| 7-14       | Operation Timing in PWM Mode 0 (asymmetric triangular wave, BFCM0x $\geq$ CM03) | 124  |

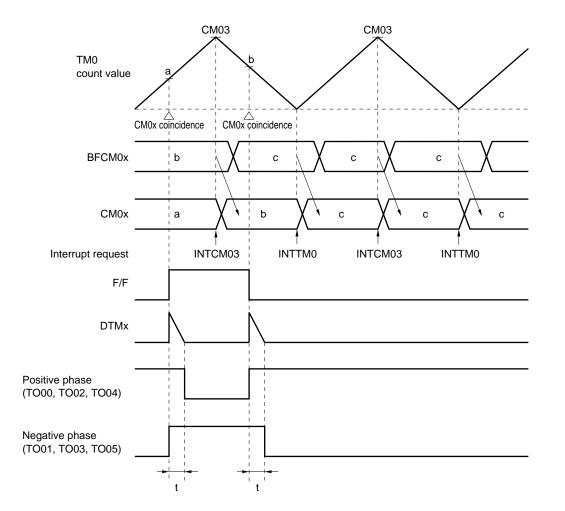

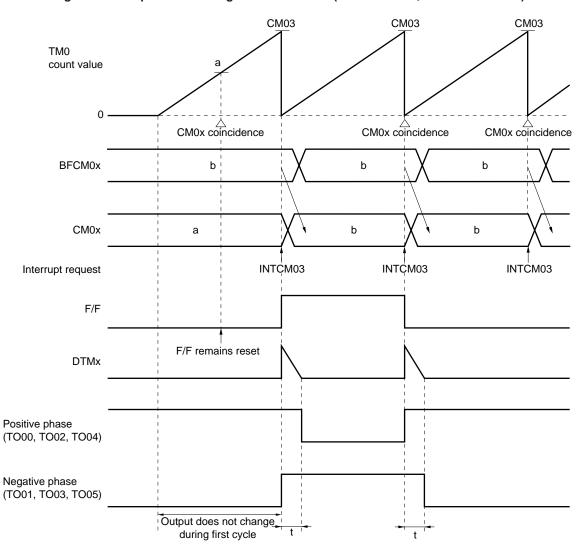

| 7-15       | Operation Timing in PWM Mode 0 (asymmetric triangular wave, BFCM0X > CM03)      | 125  |

| 7-16       | Operation Timing in PWM Mode 0 (asymmetric triangular wave, BFCM0x = 0000H) (1) | 126  |

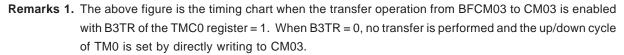

| 7-17       | Operation Timing in PWM Mode 0 (asymmetric triangular wave, BFCM0x = 0000H) (2) | 127  |

| 7-18       | Operation Timing in PWM Mode 0 (asymmetric triangular wave, BFCM0x = CM03)      | 128  |

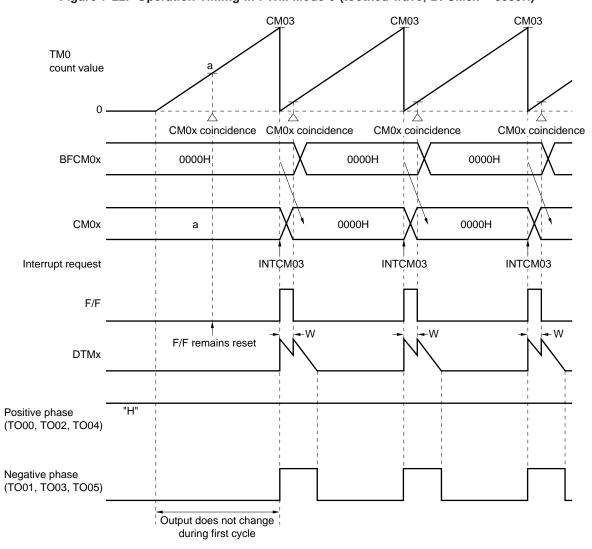

| 7-19       | Operation Timing in PWM Mode 0 (toothed wave)                                   | 132  |

| 7-20       | Operation Timing in PWM Mode 0 (toothed wave, BFCM0x > CM03)                    | 133  |

| 7-21       | Operation Timing in PWM Mode 0 (toothed wave, BFCM0x = CM03)                    | 134  |

| 7-22       | Operation Timing in PWM Mode 0 (toothed wave, BFCM0x = 0000H)                   | 135  |

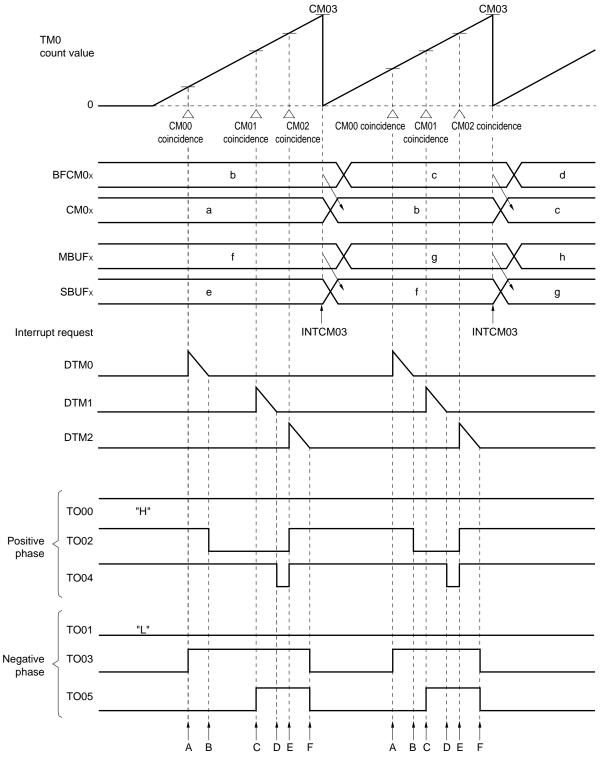

| 7-23       | Operation Timing in PWM Mode 1                                                  | 140  |

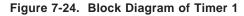

| 7-24       | Block Diagram of Timer 1                                                        | 141  |

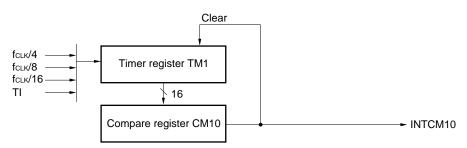

| 7-25       | Format of Timer Control Register 1                                              | 142  |

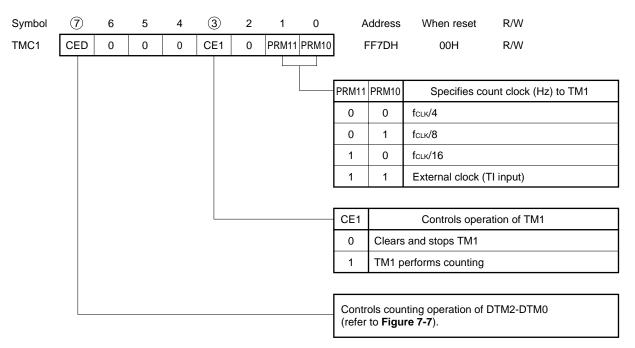

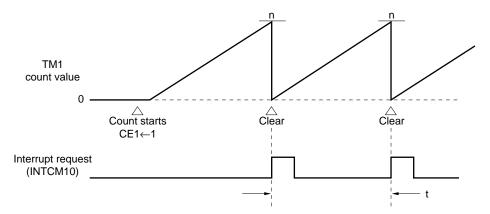

| 7-26       | Example of Compare Operation (TM1, interval timer mode)                         | 143  |

| 7-27       | Block Diagram of Timer 2                                                        | 144  |

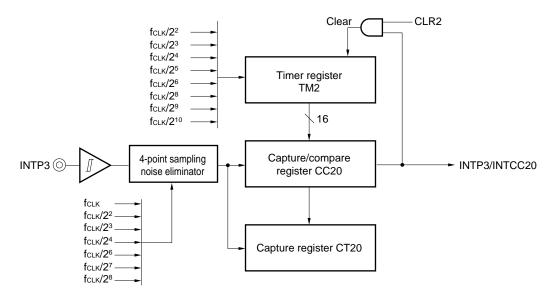

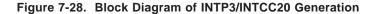

| 7-28       | Block Diagram of INTP3/INTCC20 Generation                                       | 145  |

| 7-29       | Format of Timer Control Register 2                                              | 147  |

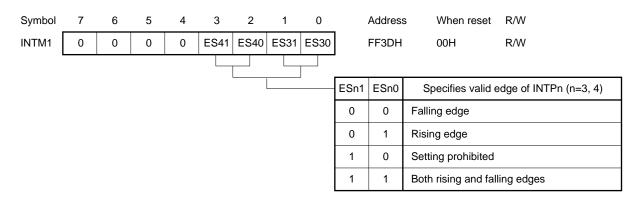

| 7-30       | Format of External Interrupt Mode Register 1                                    | 148  |

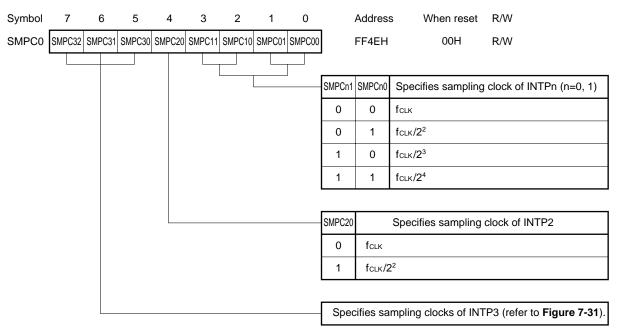

| 7-31       | Format of Sampling Control Register 0                                           | 149  |

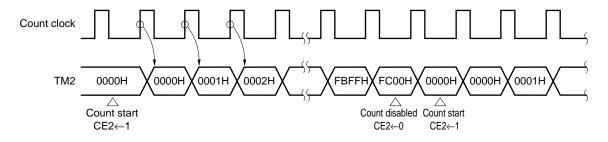

| 7-32       | Basic Operation of Timer 2 (TM2)                                                | 150  |

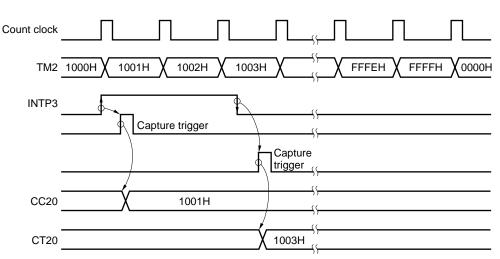

| 7-33       | Example of TM2 Capture Operation (free-running operation)                       | 152  |

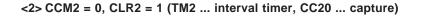

| 7-34       | Example of TM2 Capture Operation (interval operation)                           | 152  |

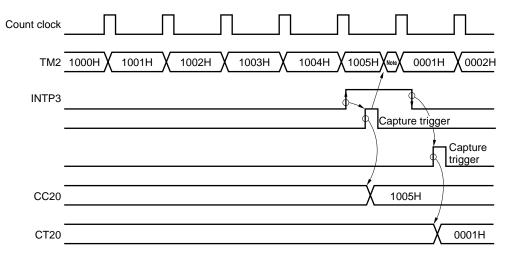

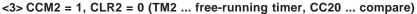

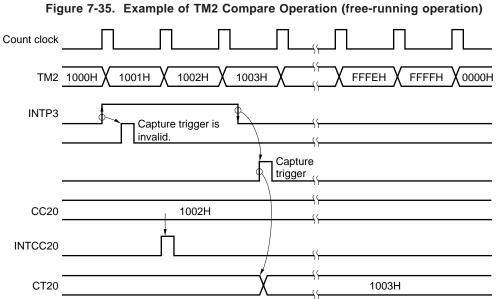

| 7-35       | Example of TM2 Compare Operation (free-running operation)                       | 153  |

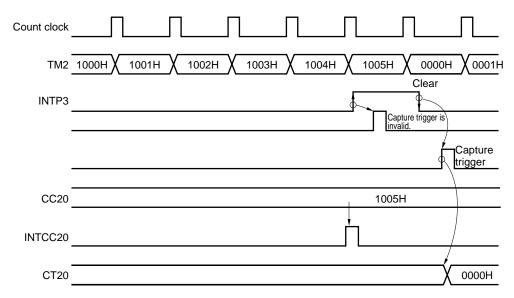

| 7-36       | Example of TM2 Compare Operation (interval operation)                           | 153  |

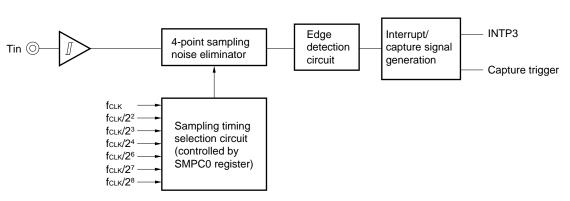

| 7-37       | Block Diagram of Sampling Circuit (TM2)                                         | 154  |

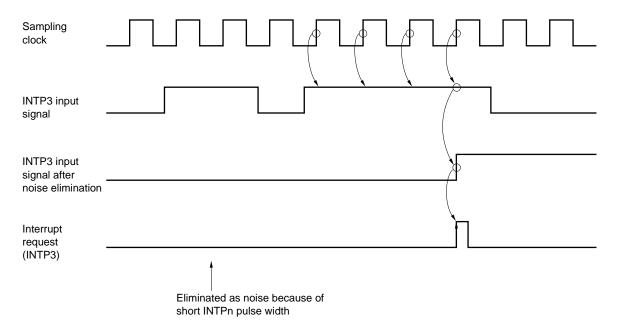

| 7-38       | Sampling Timing Chart (TM2)                                                     | 154  |

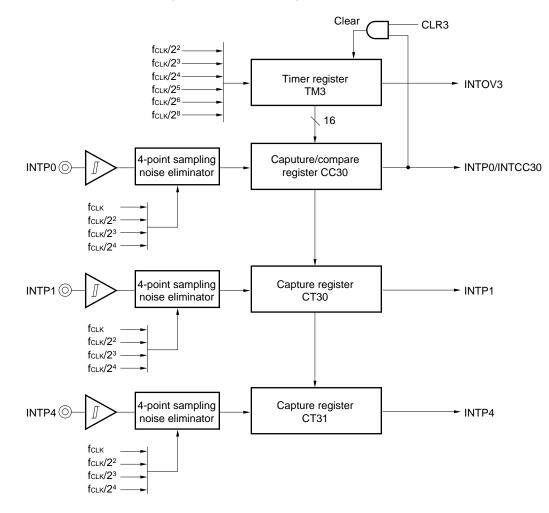

| 7-39       | Block Diagram of Timer 3                                                        | 156  |

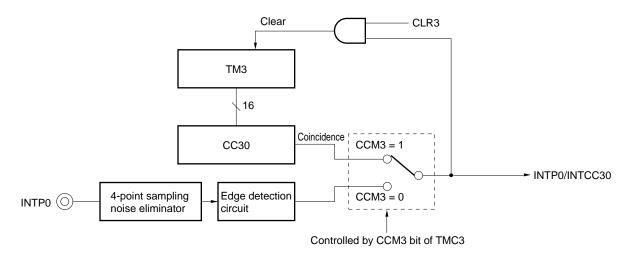

| 7-40       | Block Diagram of INTP0/INTCC30 Generation                                       | 157  |

| 7-41       | Format of Timer Control Register 3 (TMC3)                                       | 159  |

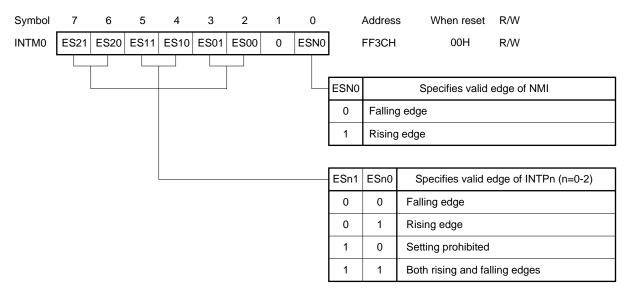

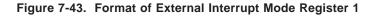

| 7-42       | Format of External Interrupt Mode Register 0                                    | 160  |

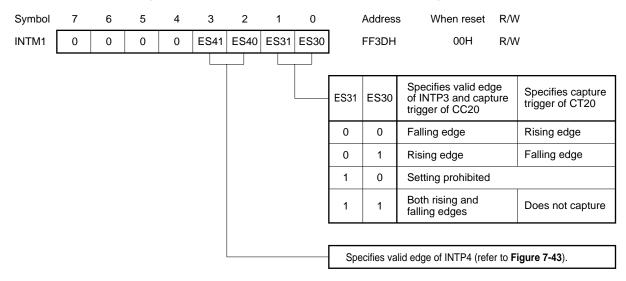

| 7-43       | Format of External Interrupt Mode Register 1                                    | 160  |

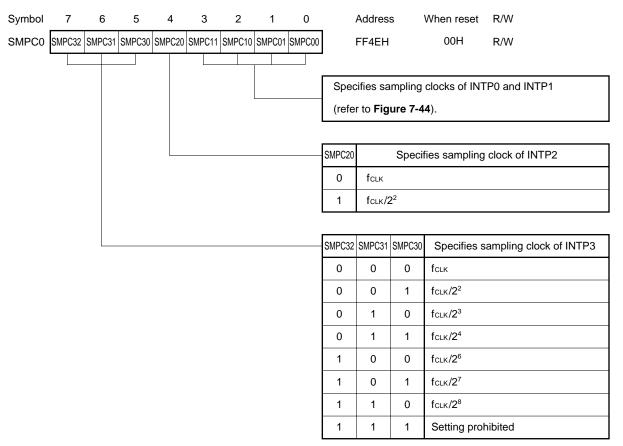

| 7-44       | Format of Sampling Control Register 0                                           | 161  |

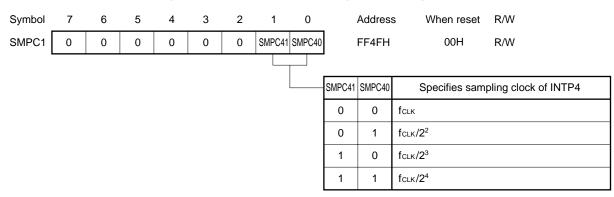

| 7-45       | Format of Sampling Control Register 1                                           | 162  |

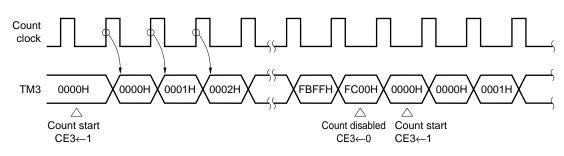

| 7-46       | Basic Operation of Timer 3 (TM3)                                                | 163  |

### LIST OF FIGURES (3/6)

| Figure No. | Title                                                                          | Page |

|------------|--------------------------------------------------------------------------------|------|

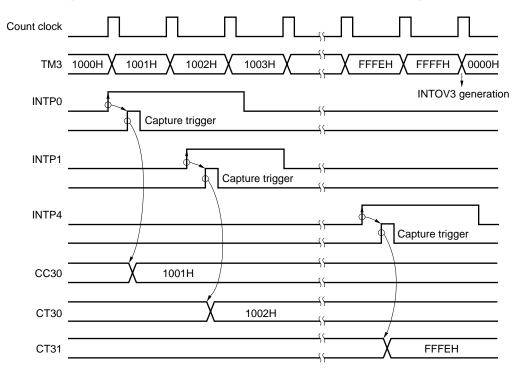

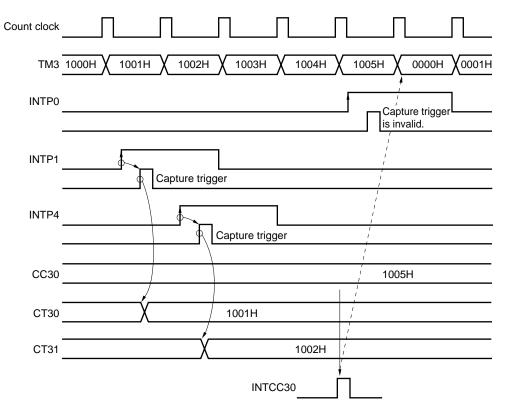

| 7-47       | Example of TM3 Capture Operation (free-running operation)                      | 165  |

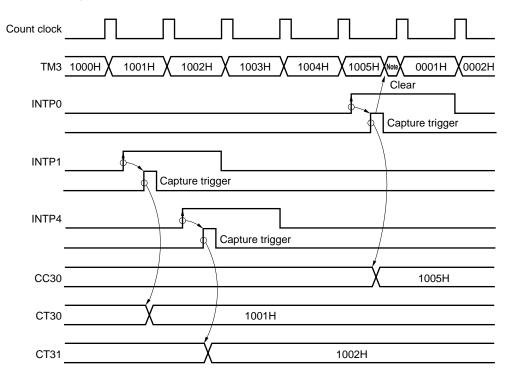

| 7-48       | Example of TM3 Capture Operation (interval operation)                          |      |

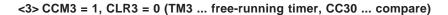

| 7-49       | Example of TM3 Compare Operation (free-running operation)                      | 167  |

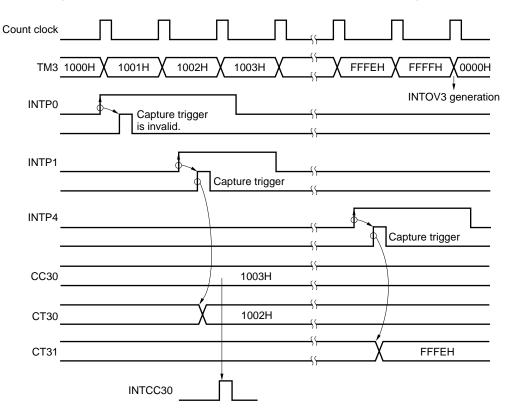

| 7-50       | Example of TM3 Compare Operation (interval operation)                          |      |

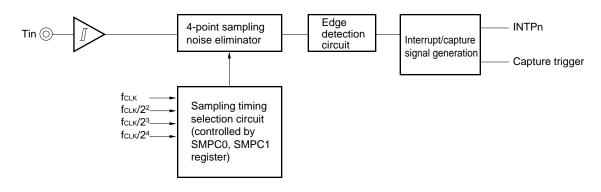

| 7-51       | Block Diagram of Sampling Circuit (TM3)                                        |      |

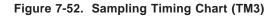

| 7-52       | Sampling Timing Chart (TM3)                                                    | 169  |

| 7-53       | Block Diagram of Timer 4 (general-purpose timer mode)                          | 171  |

| 7-54       | Block Diagram of Timer 4 (UDC mode)                                            | 171  |

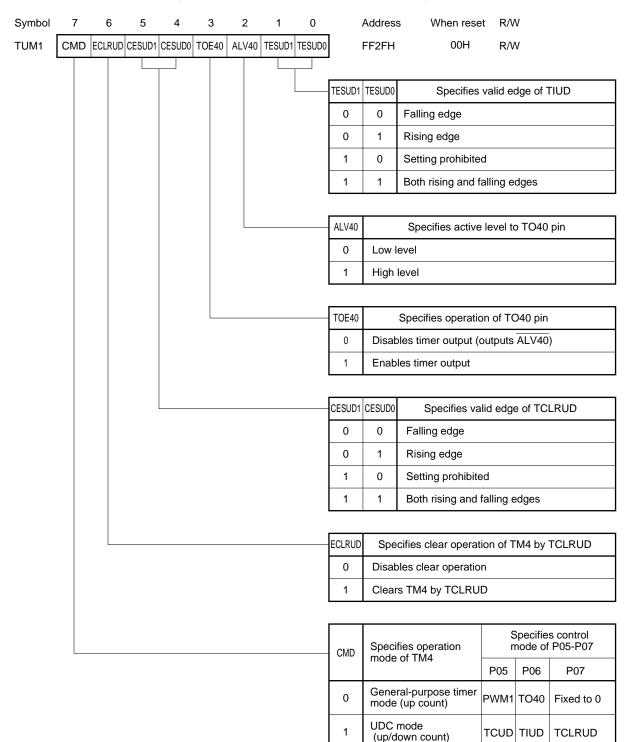

| 7-55       | Format of Timer Unit Mode Register 1                                           | 174  |

| 7-56       | Format of Timer Control Register 4                                             | 176  |

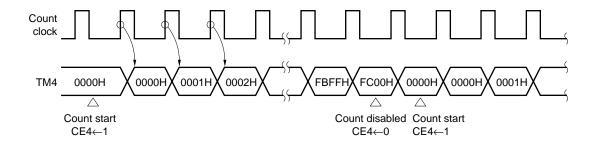

| 7-57       | Basic Operation of Timer 4 (TM4)                                               | 180  |

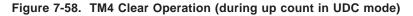

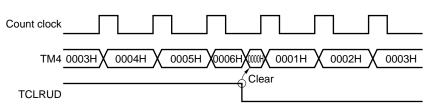

| 7-58       | TM4 Clear Operation (during up count in UDC mode)                              | 184  |

| 7-59       | TM4 Clear Operation (during down count in UDC mode)                            | 184  |

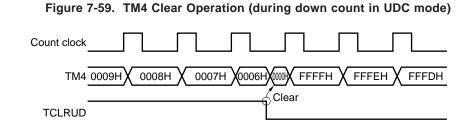

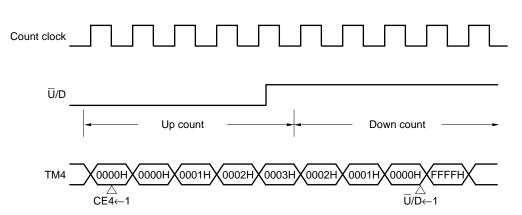

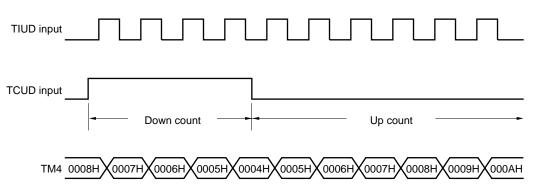

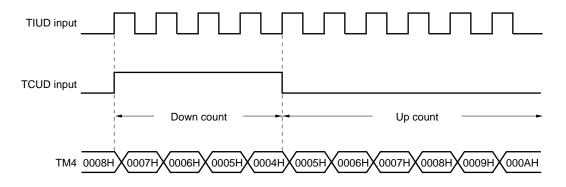

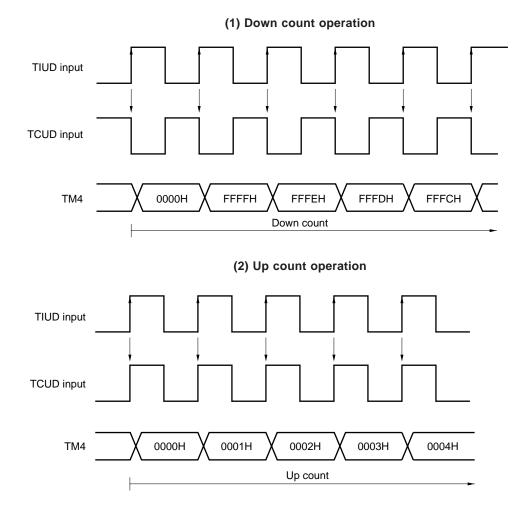

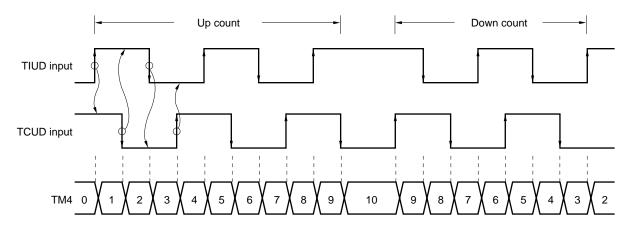

| 7-60       | Internal Clock Operation in UDC Mode                                           |      |

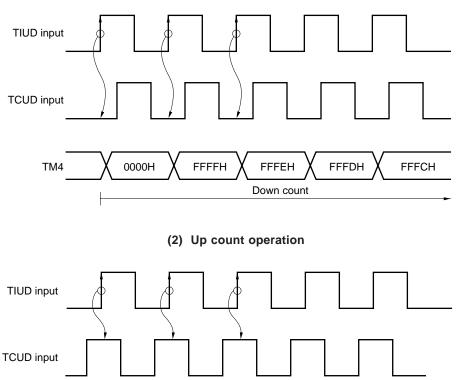

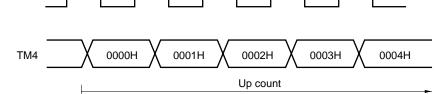

| 7-61       | Example of Operation in Mode 1 (when valid edge of TIUD pin is rising edge)    | 187  |

| 7-62       | Example of Operation in Mode 1 (when valid edge of TIUD pin is rising edge)    | 187  |

| 7-63       | Example of Operation in Mode 2 (when valid edge of TIUD pin is rising edge)    | 188  |

| 7-64       | Example of Operation in Mode 3 (when valid edge of TIUD pin is rising edge)    | 189  |

| 7-65       | Example of Operation in Mode 3 (when valid edge of TIUD pin is rising edge)    | 190  |

| 7-66       | Example of Operation in Mode 4                                                 | 191  |

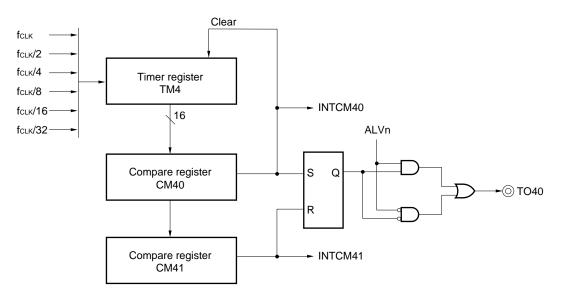

| 7-67       | Block Diagram of Timer 4 (PWM output operation)                                | 192  |

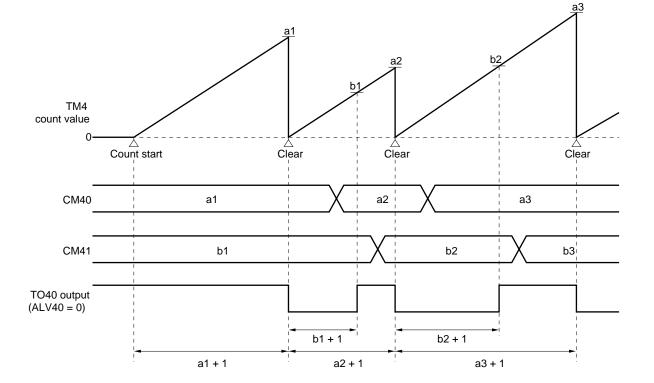

| 7-68       | Example of PWM Output Operation of TO40                                        |      |

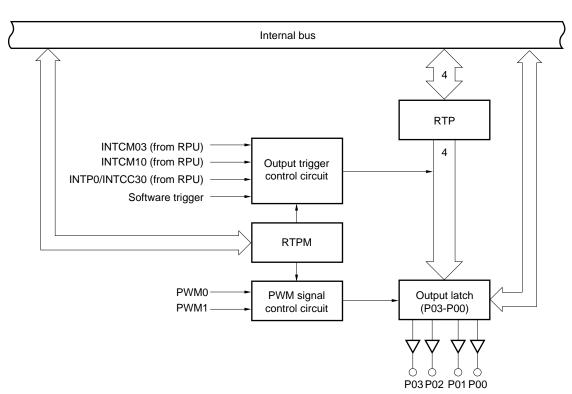

| 7-69       | Block Diagram of Real-Time Output Port                                         |      |

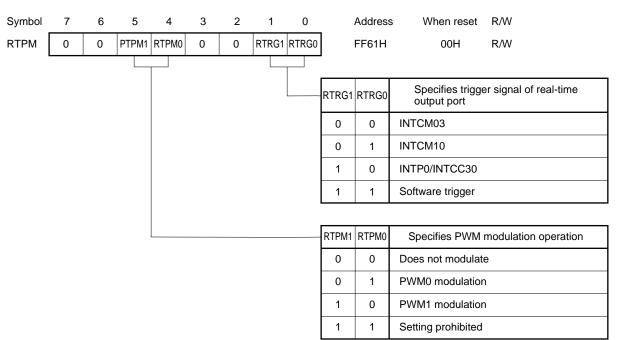

| 7-70       | Format of Real-Time Output Port Mode Register                                  | 196  |

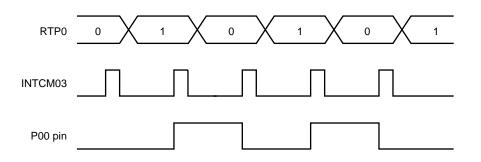

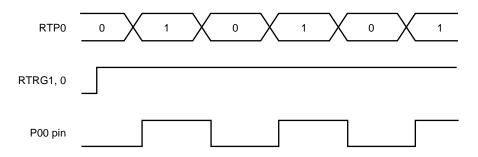

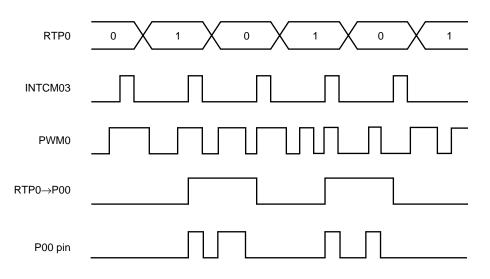

| 7-71       | Example of Real-Time Output Function Operation (P00 pin)                       |      |

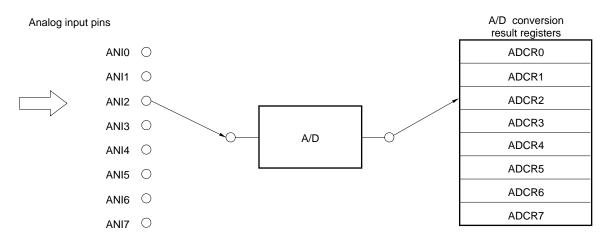

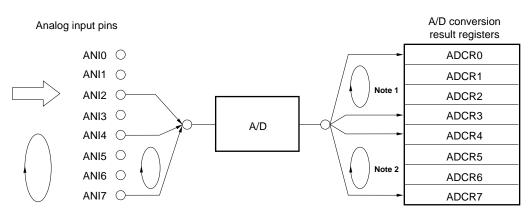

| 8-1        | Block Diagram of A/D Converter                                                 | 200  |

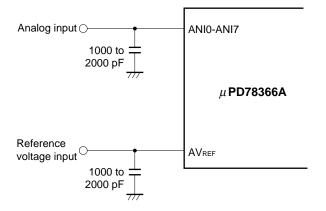

| 8-2        | Example of Connecting Capacitor to A/D Converter Pin                           | 201  |

| 8-3        | Format of A/D Converter Mode Register                                          | 204  |

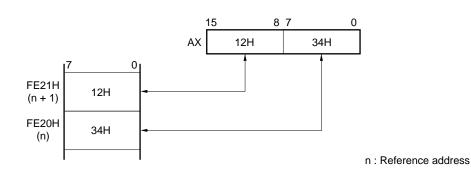

| 8-4        | Word Access to ADCR Register                                                   | 207  |

| 8-5        | Byte Access to ADCR Register                                                   | 208  |

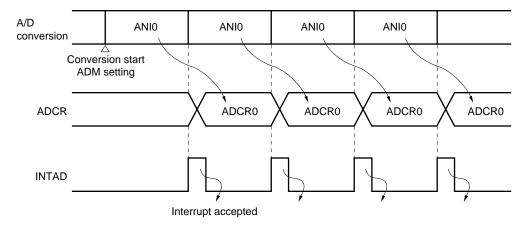

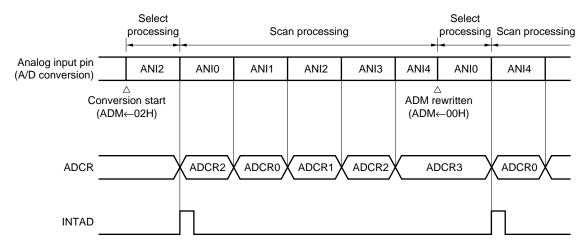

| 8-6        | A/D Conversion Basic Operation (in select mode, with software trigger)         | 209  |

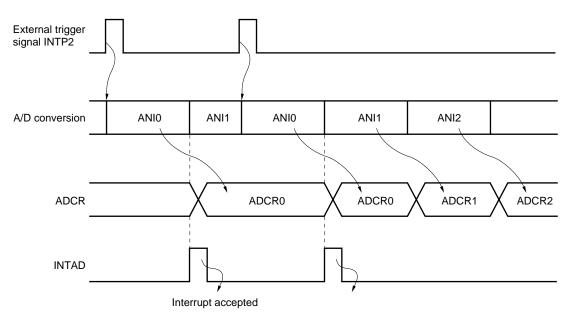

| 8-7        | A/D Conversion Basic Operation (in mixed mode, with external trigger)          | 210  |

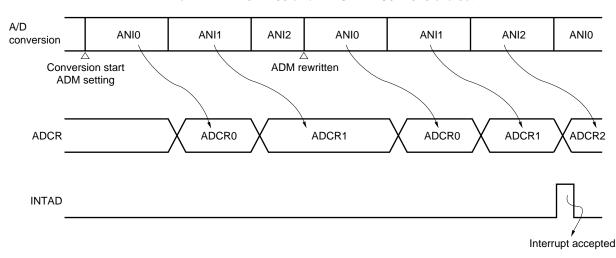

| 8-8        | Rewriting ADM during A/D Conversion (in scan mode, with software trigger)      | 211  |

| 8-9        | A/D Conversion in Select Mode (1-buffer mode)                                  | 213  |

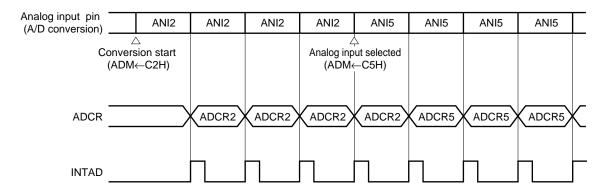

| 8-10       | Example of Operation Timing in Select Mode (1-buffer mode)                     | 214  |

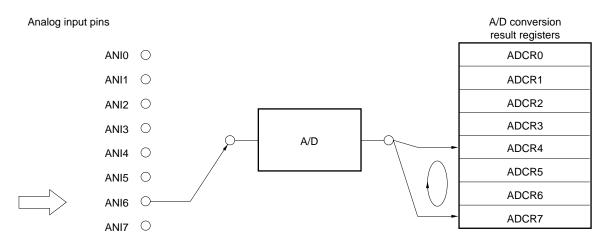

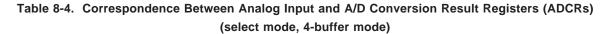

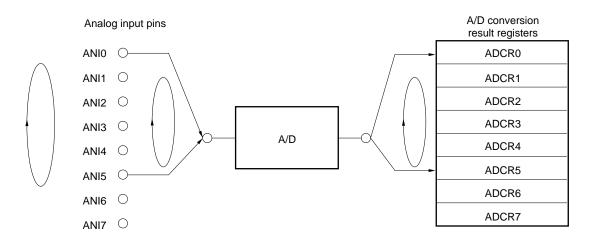

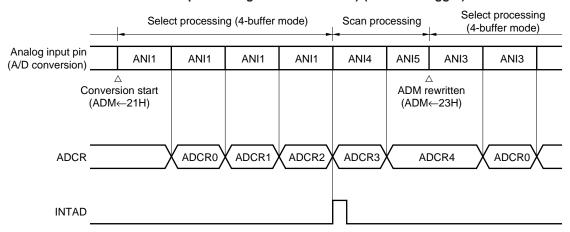

| 8-11       | A/D Conversion in Select Mode (4-buffer mode)                                  | 215  |

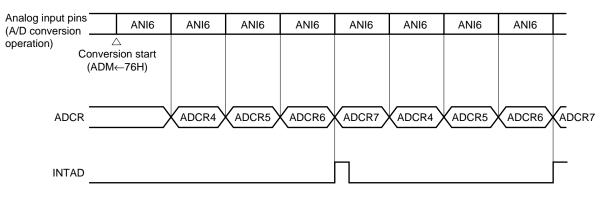

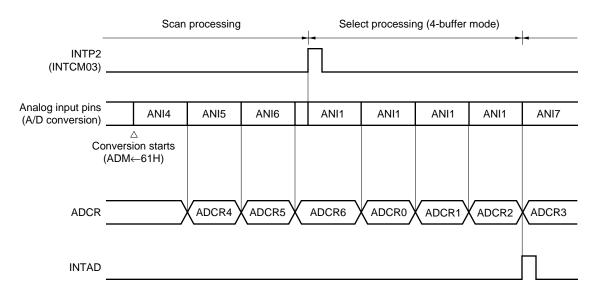

| 8-12       | Example of Operation Timing in Select Mode (in 4-buffer mode)                  | 215  |

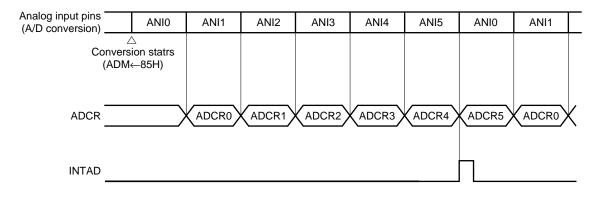

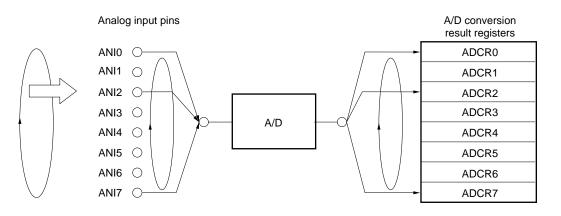

| 8-13       | A/D Conversion in Scan Mode                                                    | 216  |

| 8-14       | Example of Operation Timing in Scan Mode                                       | 217  |

| 8-15       | A/D Conversion in Mixed Mode (select processing in 1-buffer mode)              | 218  |

| 8-16       | Example of Operation Timing in Mixed Mode (select processing in 1-buffer mode) |      |

|            | (software trigger)                                                             | 219  |

### LIST OF FIGURES (4/6)

| Figure No. | Title                                                                          | Page |

|------------|--------------------------------------------------------------------------------|------|

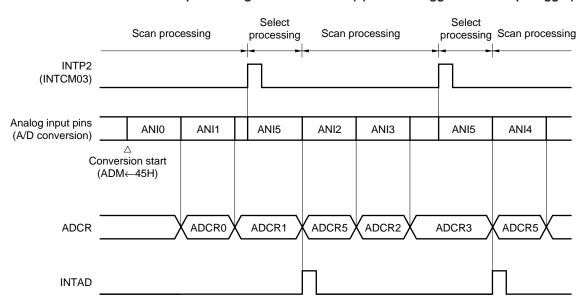

| 8-17       | Example of Operation Timing in Mixed Mode (select processing in 1-buffer mode) |      |

|            | (external trigger or interrupt trigger)                                        | 219  |

| 8-18       | A/D Conversion Timing in Mixed Mode (select processing in 4-buffer mode)       | 220  |

| 8-19       | Example of Operation Timing in Mixed Mode (select processing in 4-buffer mode) |      |

|            | (software trigger)                                                             | 221  |

| 8-20       | Example of Operation Timing in Mixed Mode (select processing in 4-buffer mode) |      |

|            | (external trigger or interrupt trigger)                                        | 221  |

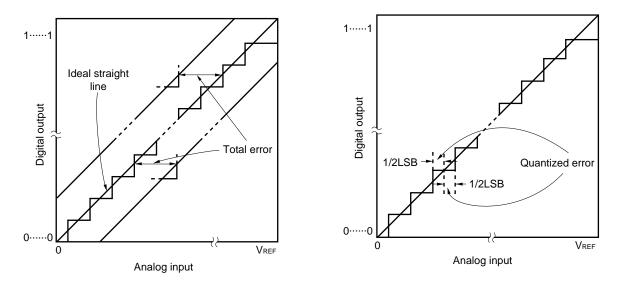

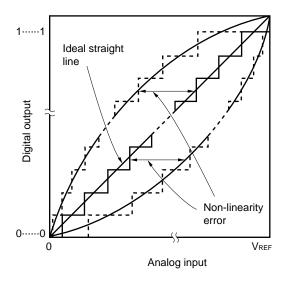

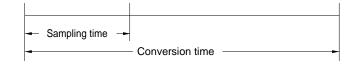

| 8-21       | Total Error                                                                    | 223  |

| 8-22       | Quantized Error                                                                | 223  |

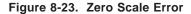

| 8-23       | Zero Scale Error                                                               | 224  |

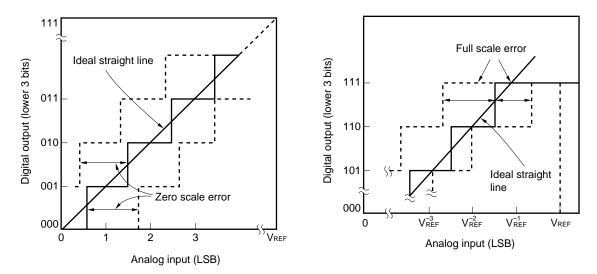

| 8-24       | Full Scale Error                                                               | 224  |

| 8-25       | Non-Linearity Error                                                            | 224  |

| 9-1        | Block Diagram of Asynchronous Serial Interface                                 | 227  |

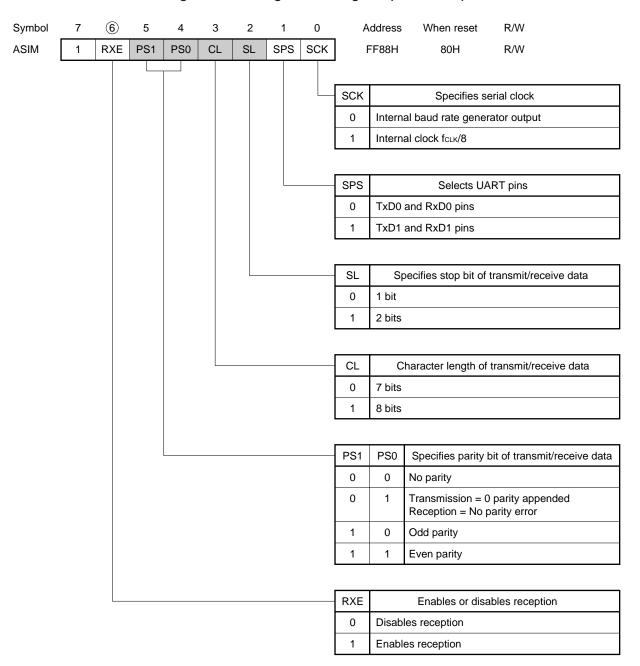

| 9-2        | Setting of ASIM Register (pin selection)                                       | 229  |

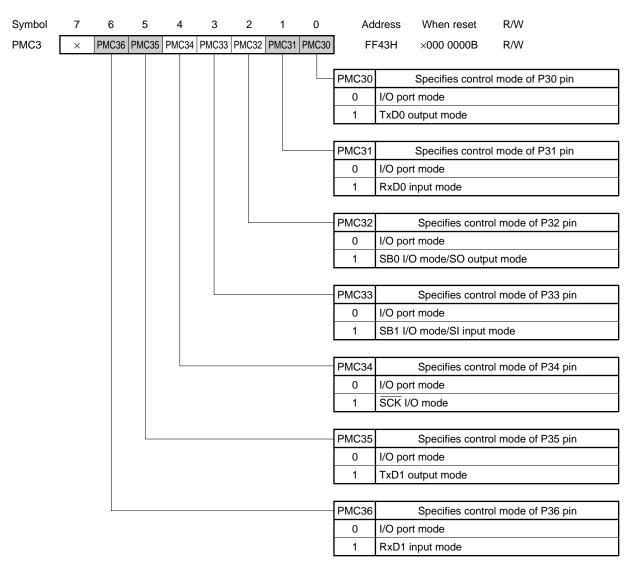

| 9-3        | Format of Port 3 Mode Control Register                                         | 230  |

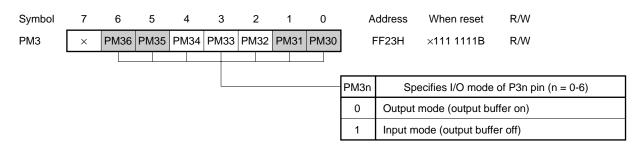

| 9-4        | Format of Port 3 Mode Register                                                 | 231  |

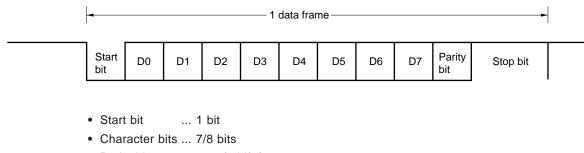

| 9-5        | Format of Transmit/Receive Data of Asynchronous Serial Interface               | 232  |

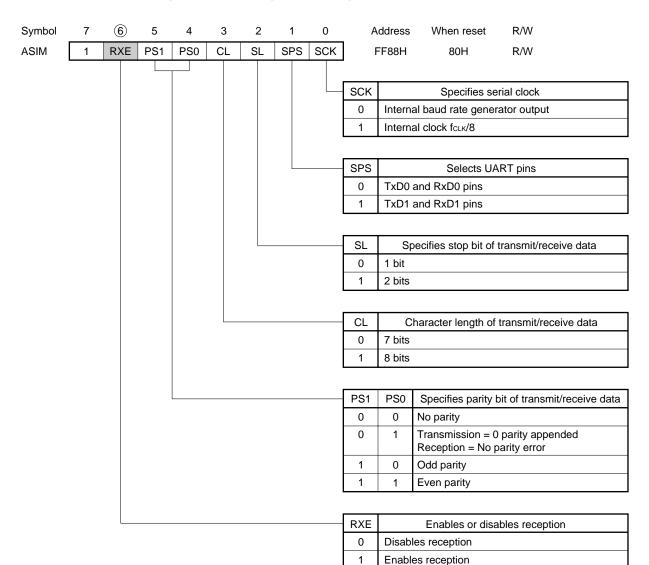

| 9-6        | Setting of ASIM Register (data format)                                         | 233  |

| 9-7        | Setting of ASIM Register (serial clock)                                        | 235  |

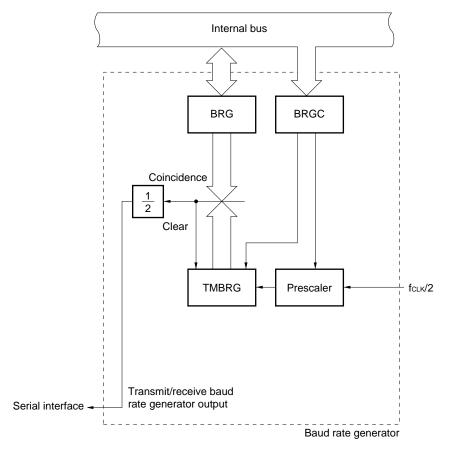

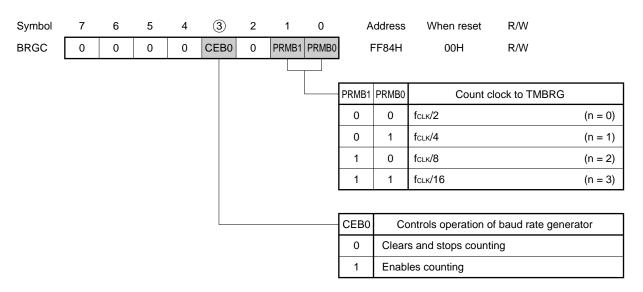

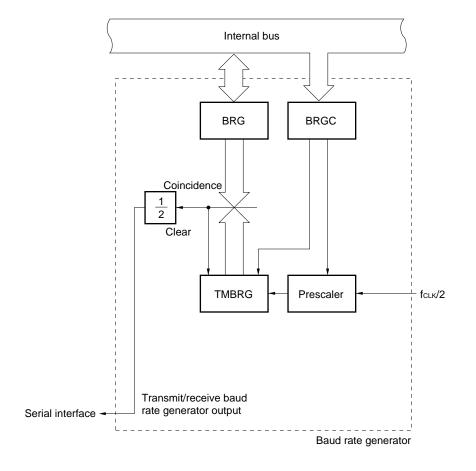

| 9-8        | Block Diagram of Baud Rate Generator                                           | 237  |

| 9-9        | Format of Baud Rate Generator Control Register                                 | 237  |

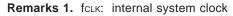

| 9-10       | Asynchronous Serial Interface Transmission End Interrupt Timing                | 241  |

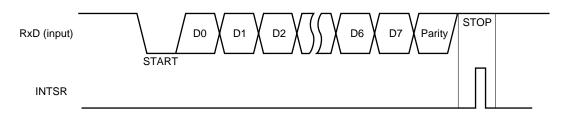

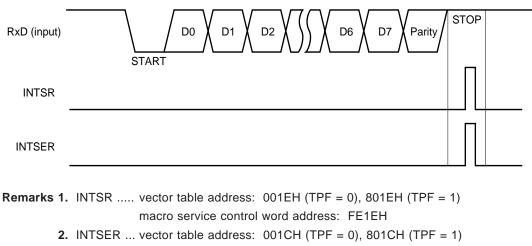

| 9-11       | Asynchronous Serial Interface Reception End Interrupt Timing                   | 242  |

| 9-12       | Setting of ASIM Register (reception enabled)                                   | 243  |

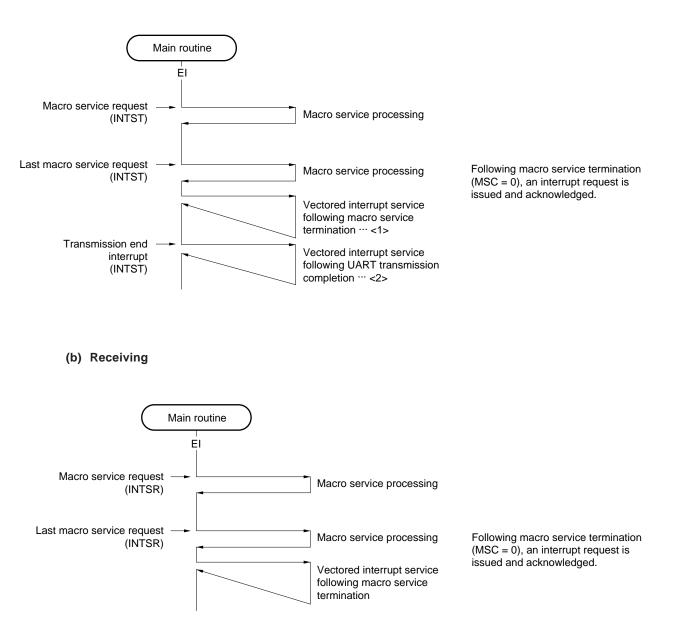

| 9-13       | UART Transmitting/Receiving Using Macro Service                                | 245  |

| 9-14       | Reception Error Timing                                                         | 246  |

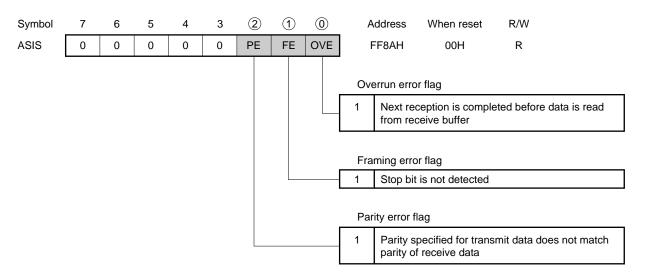

| 9-15       | Format of Asynchronous Serial Interface Status Register                        | 247  |

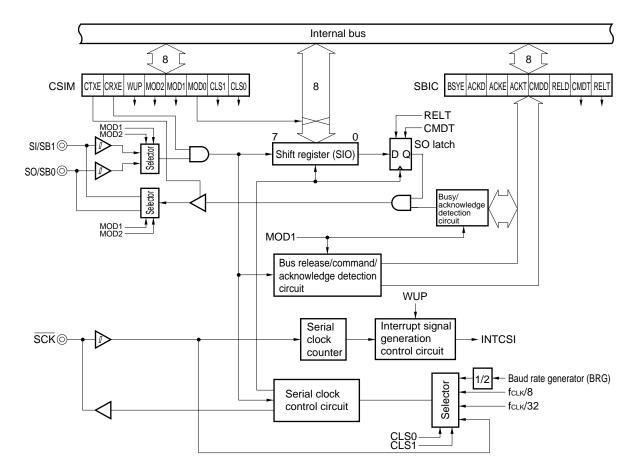

| 10-1       | Block Diagram of Clocked Serial Interface                                      | 251  |

| 10-2       | Format of Port 3 Mode Control Register                                         | 252  |

| 10-3       | Format of Port 3 Mode Register                                                 | 253  |

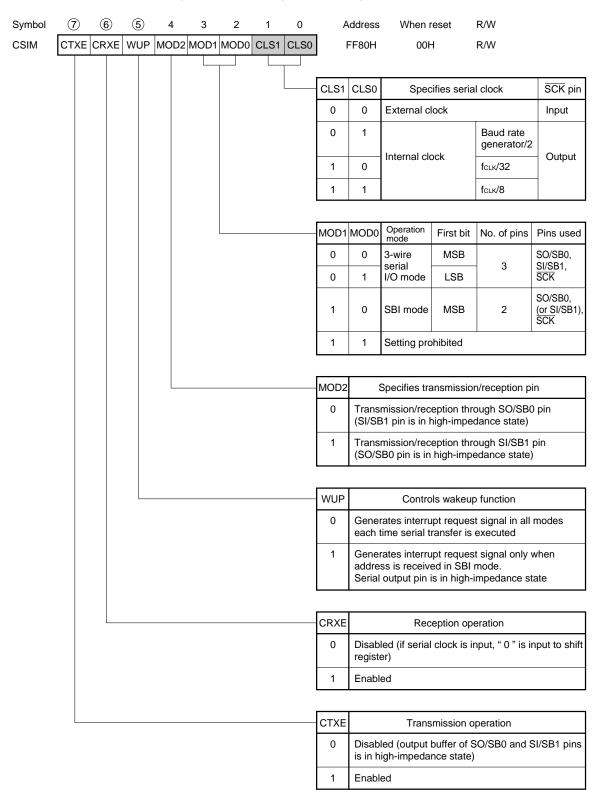

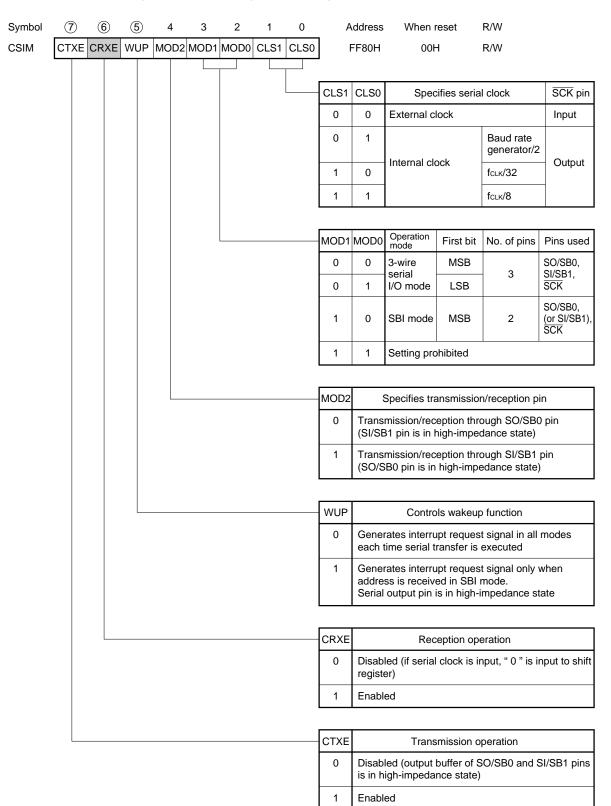

| 10-4       | Setting of CSIM Register (serial clock)                                        | 255  |

| 10-5       | Block Diagram of Baud Rate Generator                                           | 257  |

| 10-6       | Format of Baud Rate Generator Control Register                                 | 259  |

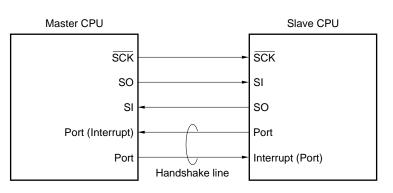

| 10-7       | Example of System Configuration in Three-Wire Serial I/O Mode                  | 260  |

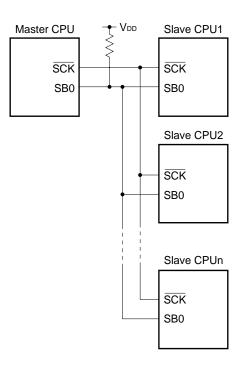

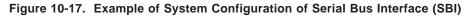

| 10-8       | Example of System Configuration in Serial Bus Interface (SBI) Mode             | 261  |

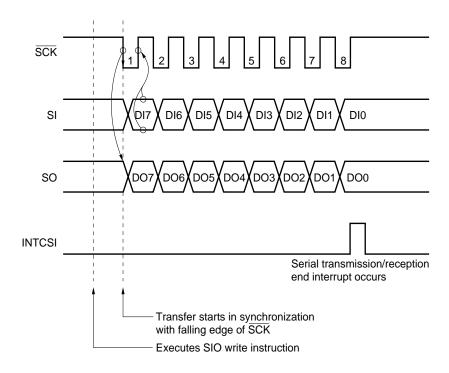

| 10-9       | Timing in Three-Wire Serial I/O Mode                                           | 262  |

| 10-10      | Setting of CSIM Register (three-wire serial I/O mode)                          | 263  |

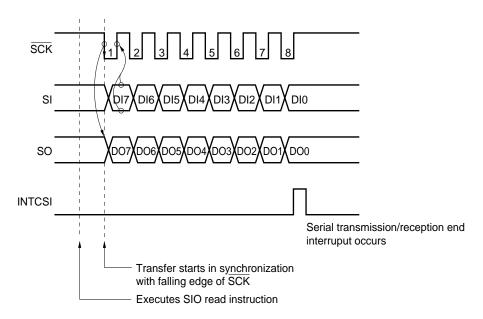

| 10-11      | Timing in Three-Wire Serial I/O Mode (transmission)                            | 264  |

| 10-12      | Setting of CSIM Register (transmission enabled)                                | 265  |

| 10-13      | Timing in Three-Wire Serial I/O Mode (reception)                               | 266  |

| 10-14      | Setting of CSIM Register (reception enabled)                                   | 267  |

### LIST OF FIGURES (5/6)

| Figure No. | Title                                                                    | Page |

|------------|--------------------------------------------------------------------------|------|

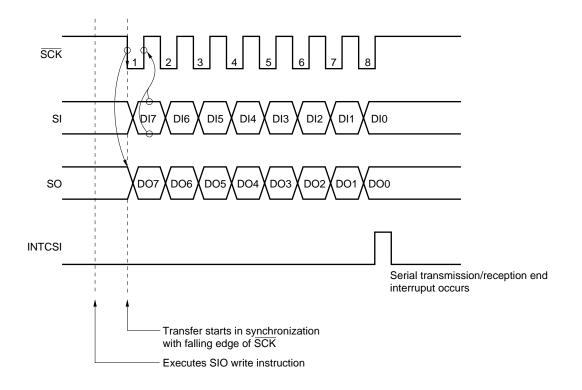

| 10-15      | Timing in Three-Wire Serial I/O Mode (transmission/reception)            |      |

| 10-16      | Setting of CSIM Register (transmission/reception enabled)                |      |

| 10-17      | Example of System Configuration of Serial Bus Interface (SBI)            |      |

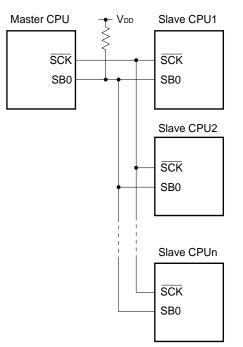

| 10-18      | Setting of CSIM Register (SBI mode)                                      |      |

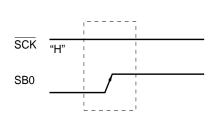

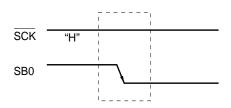

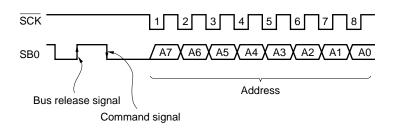

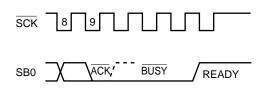

| 10-19      | Bus Release Signal                                                       |      |

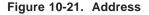

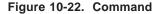

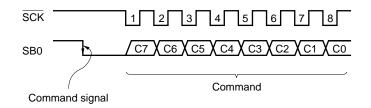

| 10-20      | Command Signal                                                           |      |

| 10-21      | Address                                                                  |      |

| 10-22      | Command                                                                  |      |

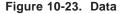

| 10-23      | Data                                                                     |      |

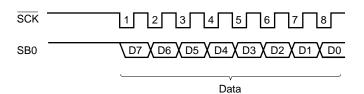

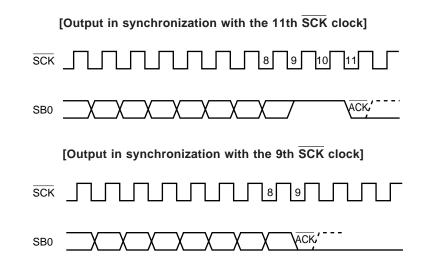

| 10-24      | Acknowledge Signal                                                       |      |

| 10-25      | Busy Signal and Ready Signal                                             |      |

| 10-26      | Format of Serial Bus Interface Control Register                          |      |

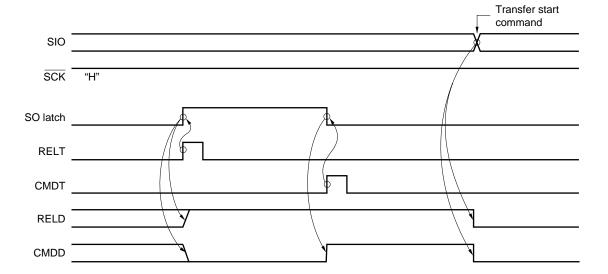

| 10-27      | Operations of RELT, CMDT, RELD, and CMDD                                 |      |

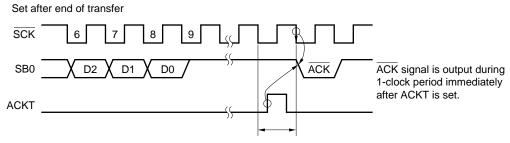

| 10-28      | Operation of ACKT                                                        |      |

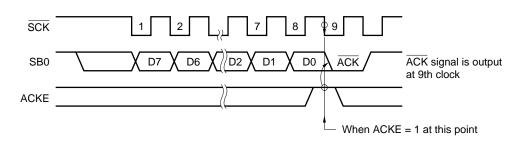

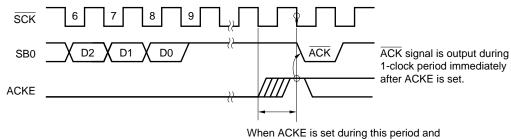

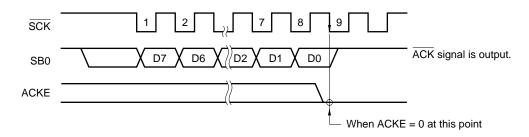

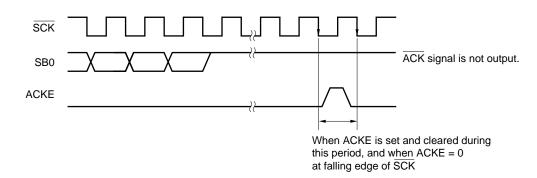

| 10-29      | Operation of ACKE                                                        |      |

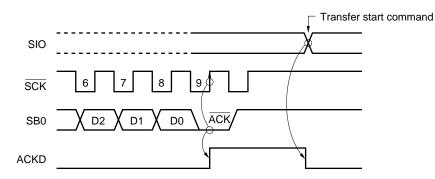

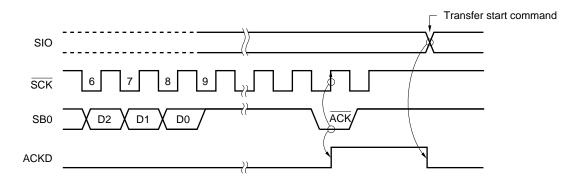

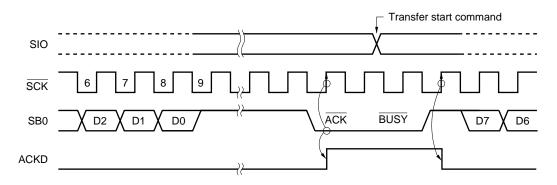

| 10-30      | Operation of ACKD                                                        |      |

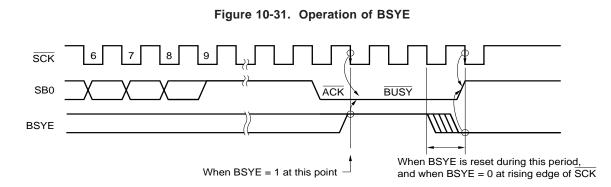

| 10-31      | Operation of BSYE                                                        |      |

| 10-32      | Setting of CSIM Register (transmission/reception enabled)                |      |

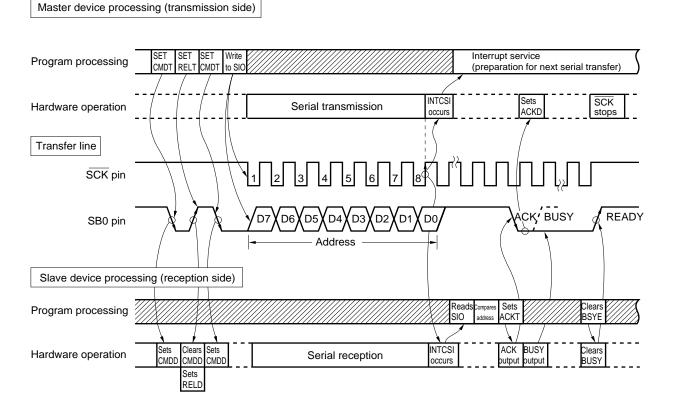

| 10-33      | Address Transfer from Master Device to Slave Device                      |      |

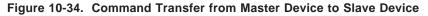

| 10-34      | Command Transfer from Master Device to Slave Device                      |      |

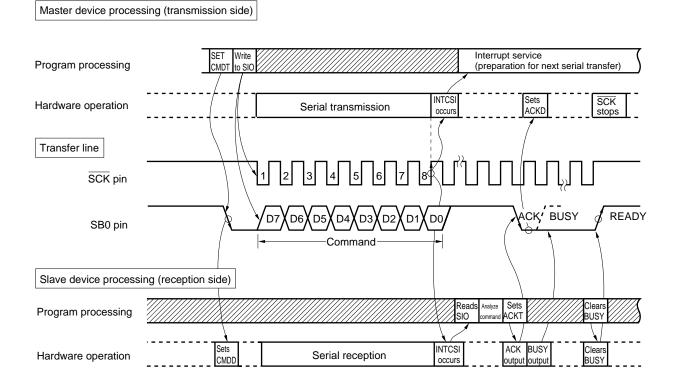

| 10-35      | Data Transfer from Master Device to Slave Device                         |      |

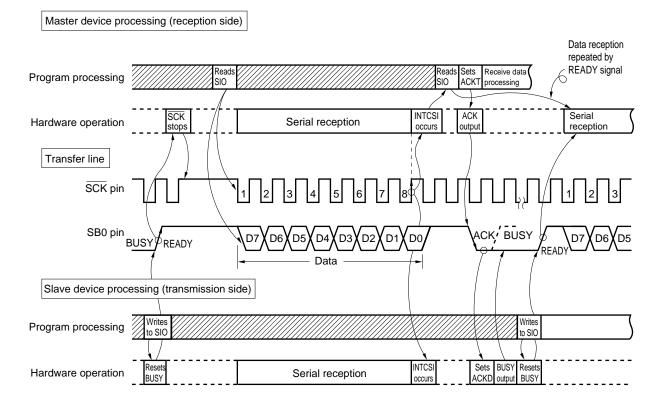

| 10-36      | Data Transfer from Slave Device to Master Device                         |      |

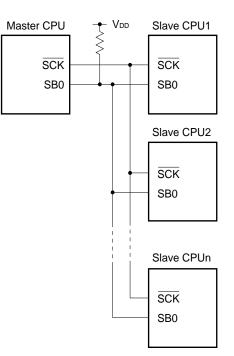

| 10-37      | Example of System Configuration of Serial Bus Interface (SBI)            |      |

| 10-38      | Setting of CSIM Register (wake-up function)                              |      |

| 11-1       | Block Diagram of PWM Unit                                                |      |

| 11-2       | Format of PWM Control Register 0                                         |      |

| 11-3       | Format of PWM Control Register 1                                         |      |

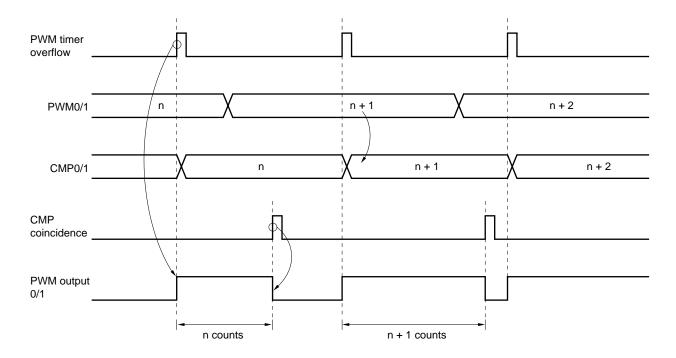

| 11-4       | Operation of PWM Output Function (high-active setting)                   |      |

| 12-1       | Block Diagram of Watchdog Timer                                          |      |

| 12-2       | Format of Watchdog Timer Mode Register                                   | 301  |

| 13-1       | Format of Interrupt Control Registers                                    |      |

| 13-2       | Format of Interrupt Mask Flag Register                                   |      |

| 13-3       | Format of Interrupt Mode Control Register                                |      |

| 13-4       | Format of In-service Priority Register                                   |      |

| 13-5       | Program Status Word (PSWL) Format                                        |      |

| 13-6       | Non-Maskable Interrupt Request Acknowledgment Operation                  |      |

| 13-7       | Interrupt Acknowledgment Service Algorithm                               |      |

| 13-8       | Context Switching Operation by Generation of Interrupt Request           |      |

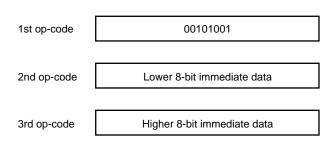

| 13-9       | RETCS Instruction Format                                                 |      |

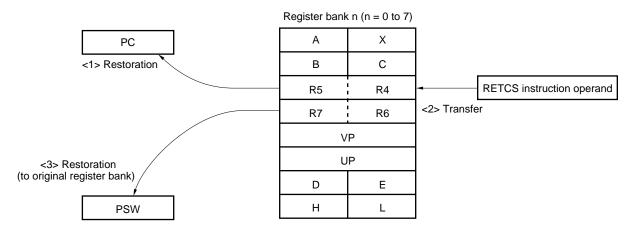

| 13-10      | Restoration Operation from Interrupt Using Context Switching Function by | -    |

|            | RETCS Instruction                                                        |      |

### LIST OF FIGURES (6/6)

| Figure No. | Title                                                                             | Page |

|------------|-----------------------------------------------------------------------------------|------|

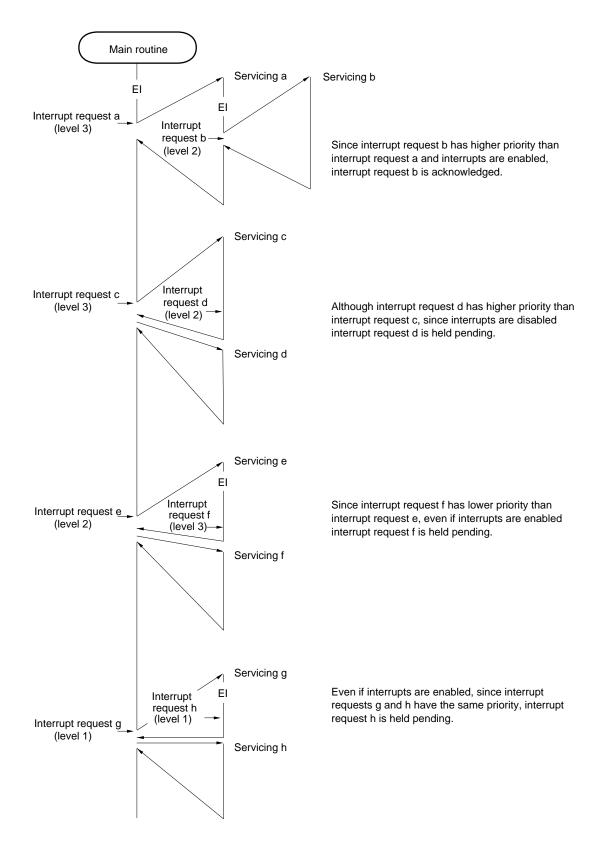

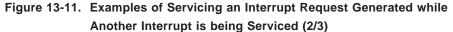

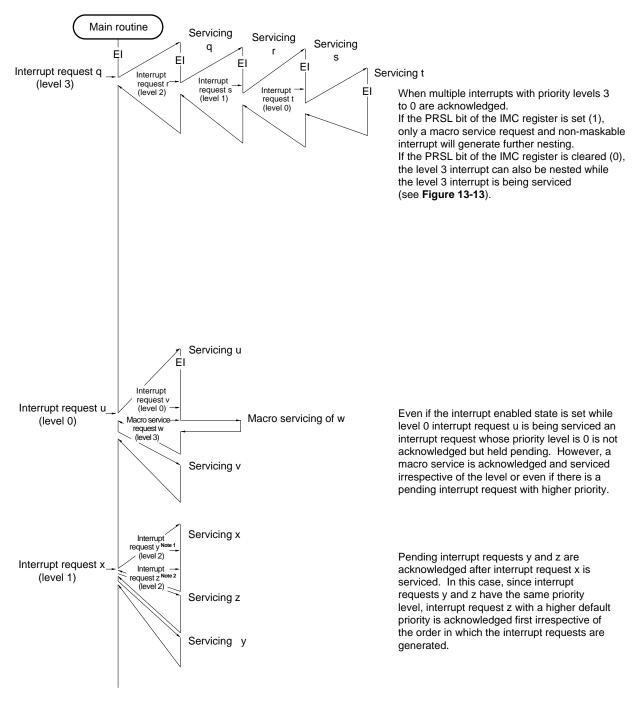

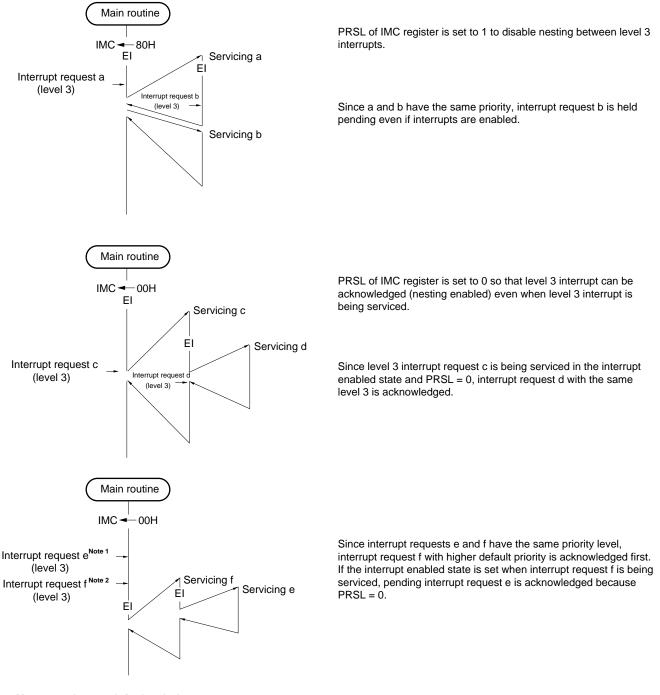

| 13-11      | Examples of Servicing an Interrupt Request Generated while                        |      |

| 10 11      | Another Interrupt is being Serviced                                               | 327  |

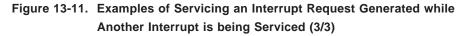

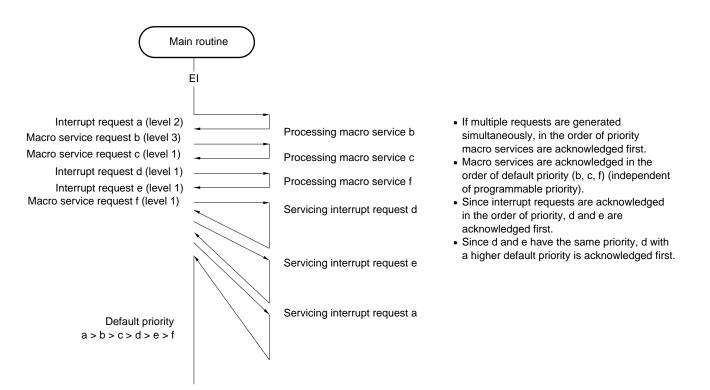

| 13-12      | Example of Servicing Interrupt Requests Generated Simultaneously                  | 330  |

| 13-13      | Differences in Level 3 Interrupt Acknowledgment Operation by Setting IMC Register | 331  |

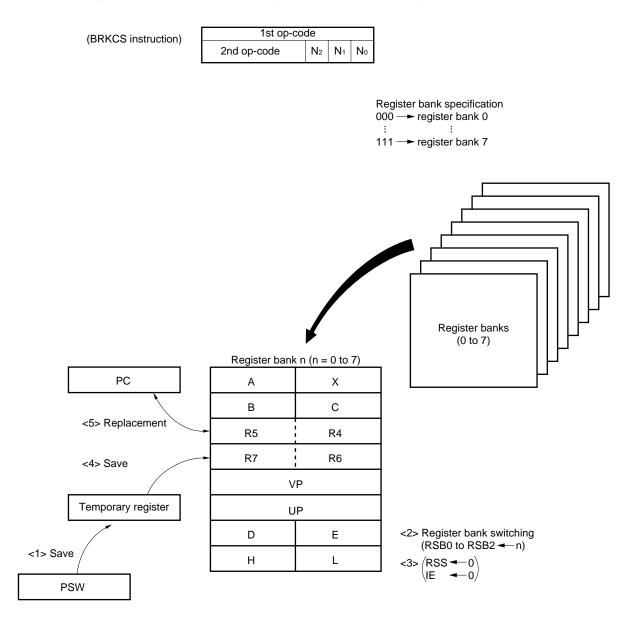

| 13-14      | Context Switching Operation by Executing BRKCS Instruction                        | 333  |

| 13-15      | RETCSB Instruction Format                                                         | 334  |

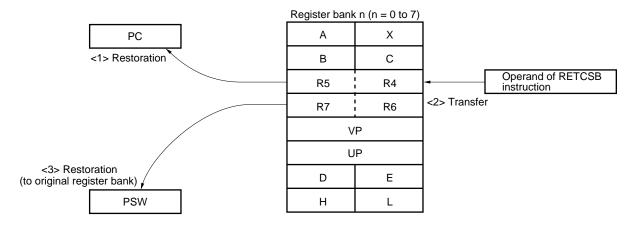

| 13-16      | Restoration Operation from Software Interrupt Executed by BRKCS Instruction       |      |

|            | (Operation of RETCSB Instruction)                                                 | 335  |

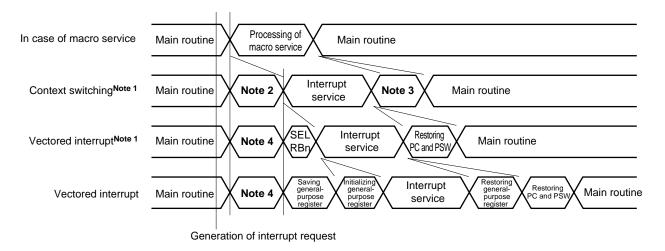

| 13-17      | Differences between Vectored Interrupt and Macro Service Processing               | 336  |

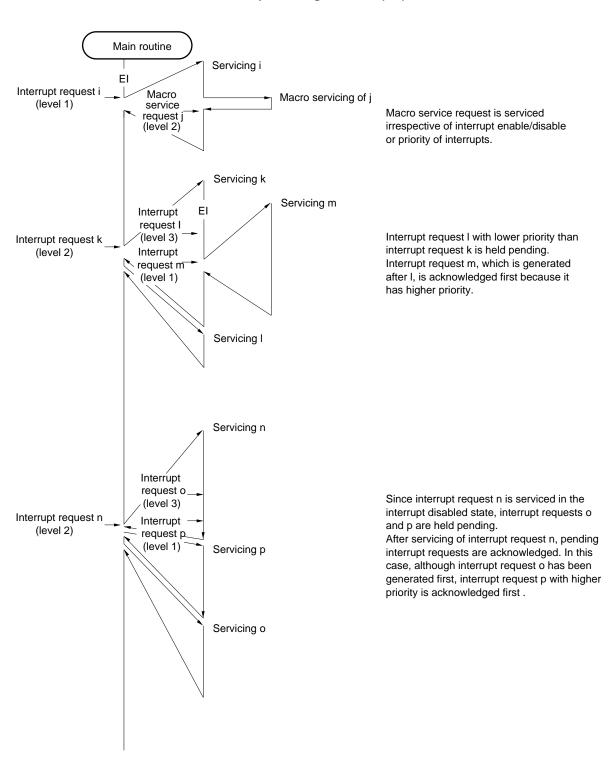

| 13-18      | Sequence Example of Macro Service Processing                                      | 339  |

| 13-19      | Operation at Completion of Macro Service                                          |      |

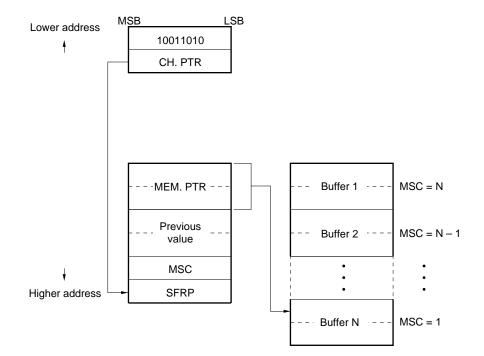

| 13-20      | Basic Structure of Macro Service Control Word                                     |      |

| 13-21      | Format of Macro Service Control Word                                              | 343  |

|            |                                                                                   |      |

| 14-1       | Transition Diagram of Standby Modes                                               | 357  |

| 14-2       | STBC Register Write Instruction                                                   | 358  |

| 14-3       | Format of Standby Control Register (STBC)                                         | 359  |

| 14-4       | Format of Watchdog Timer Mode Register                                            | 365  |

| 14-5       | Operation after Release of STOP Mode (1)                                          | 366  |

| 14-6       | Operation after Release of STOP Mode (2)                                          | 367  |

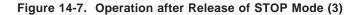

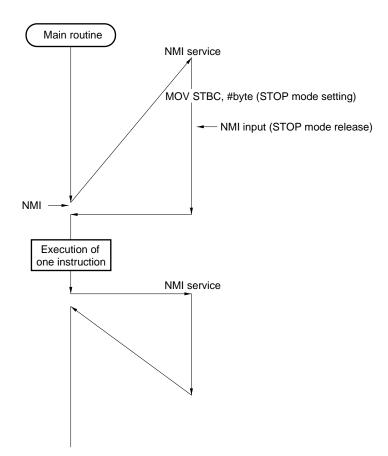

| 14-7       | Operation after Release of STOP Mode (3)                                          | 368  |

| 14-8       | Operation after Release of STOP Mode (4)                                          | 369  |

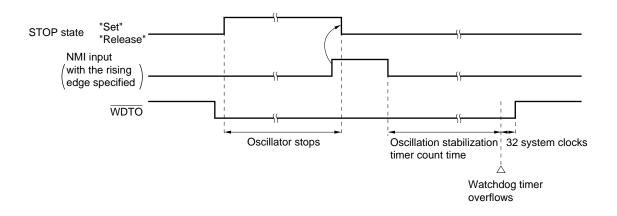

| 14-9       | Releasing STOP Mode by NMI Input (1)                                              | 370  |

| 14-10      | Releasing STOP Mode by NMI Input (2)                                              | 371  |

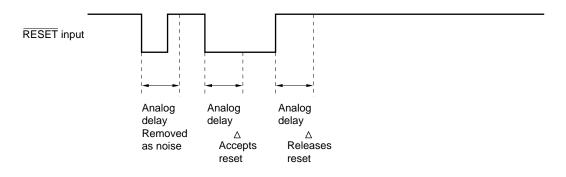

| 15-1       | Acceptance of RESET Signal                                                        | 373  |

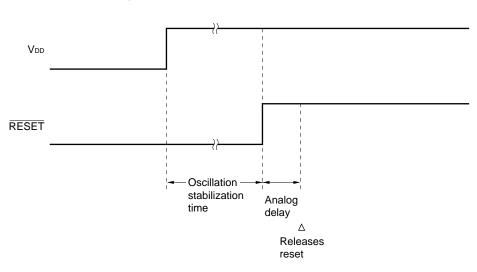

| 15-2       | Reset Operation at Power-On                                                       | 374  |

| 16-1       | Memory Map in Expansion Mode (µPD78368A)                                          | 379  |

| 16-2       | Memory Map in Expansion Mode (µPD78366A)                                          | 380  |

| 16-3       | Memory Map in Expansion Mode (µPD78363A)                                          | 381  |

| 16-4       | Memory Map in Expansion Mode (µPD78P368A)                                         | 382  |

| 16-5       | Memory Map of $\mu$ PD78365A                                                      | 383  |

| 16-6       | Format of Memory Expansion Mode Register                                          | 385  |

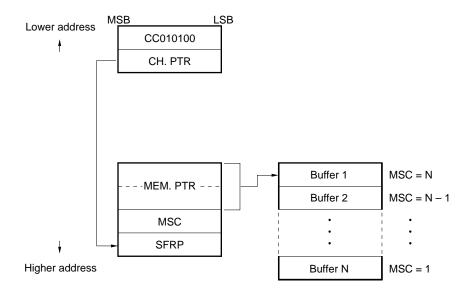

| 16-7       | Format of Programmable Wait Control Register                                      | 387  |