### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## RENESAS

### **User's Manual**

# **μPD78356**

16-bit Singlechip Microcontrollers

### Instructions

$\mu$ PD78352A Subseries  $\mu$ PD78356 Subseries  $\mu$ PD78366A Subseries  $\mu$ PD78372 Subseries

[MEMO]

Phase-out/Discontinued

#### NOTES FOR CMOS DEVICES -

#### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

QTOP is a trademark of NEC Corporation.

MS-DOS and Windows are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT and PC DOS are trademarks of International Business Machines Corporation.

SPARCstation is a trademark of SPARC International, Inc.

SunOS is a trademark of Sun Microsystems, Inc.

HP9000 series 700 and HP-UX are trademarks of Hewlett-Packard Company.

NEWS and NEWS-OS are trademarks of Sony Corporation.

TRON is an abbreviation of The Realtime Operating system Nucleus.

ITRON is an abbreviation of Industrial TRON.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

### **Major Revisions In This Edition**

| Page                          | Description                                                                                                                                                              |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout                    | Adding the following products $\mu$ PD78356(A), 78P356(A), 78361A, 78362A, 78P364A, 78363A, 78365A, 78366A, 78368A, 78P368A, 78372(A), 78372(A1), 78P372(A2), 78P372(A2) |

|                               | Deleting the following products $\mu$ PD78355A, 78356A, 78P356A, 78362, 78P364, 78365, 78366, 78P368, 78370, 78372, 78P372                                               |

|                               | Changing the status of the following products from developing to completed $\mu\text{PD78355}$ , 78356, 78P356                                                           |

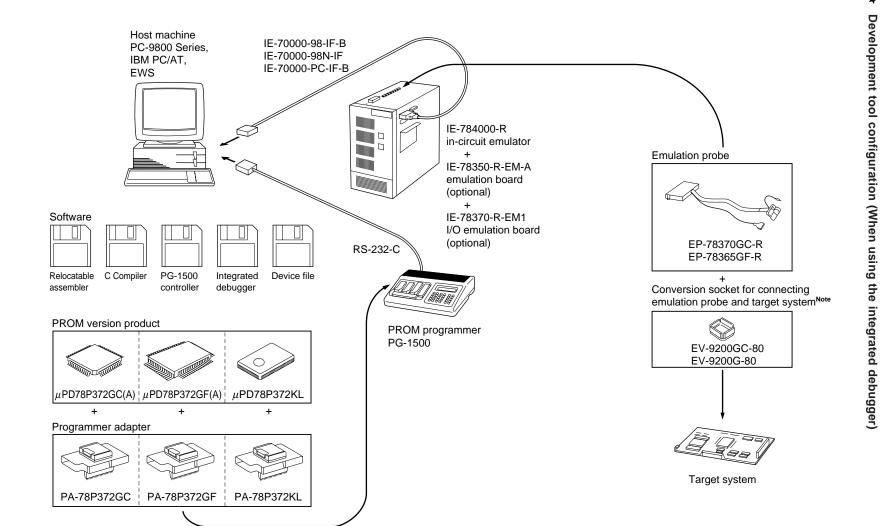

| p.329, 336, 341, 346<br>p.348 | Adding the description of the debugging tools at the use of integrated debugger in APPENDIX A TOOLS.  Adding Section A.6 Embedded Software                               |

| p.357                         | Adding APPENDIX D REVISION HISTORY                                                                                                                                       |

The mark ★ shows major revised points.

[MEMO]

Phase-out/Discontinued

#### **PREFACE**

#### Readers

This manual is intended for engineers of users who understand the functions of the 78K/III Series products and design application systems using the 78K/III Series.

The 78K/III Series covered in the manual includes the following products Note 1:

μPD78352A Subseries : μPD78350, 78350A, 78352A, 78P352

•  $\mu$ PD78356 Subseries :  $\mu$ PD78355, 78356, 78P356, 78356(A), 78P356(A) •  $\mu$ PD78366A Subseries :  $\mu$ PD78361A, 78362A, 78P364A, 78363A, 78365A,

78366A, 78368A, 78P368A

• μPD78372 Subseries Note 2: μPD78372(A), 78372(A1), 78372(A2), 78P372(A),

78P372(A1), 78P372(A2)

**Notes 1.** In addition to these products, the 78K/III Series provides the  $\mu$ PD78312A, 78322, 78328, and 78334 Subseries products. For details of each subseries, refer to their individual User's Manuals.

2. Other than the above members, the  $\mu$ PD78372 Subseries provides the  $\mu$ PD78P372KLS of EPROM version which can be used only for experiment of function evaluation. However, this document explains the  $\mu$ PD78P372(A) as a representative product as long as no special differences exist.

#### **Purpose**

The purpose of the manual is for the user to understand the instruction functions of the 78K/ III Series products.

#### Organization

The manual consists of the following main parts:

- · General description

- Target product list

- CPU architecture

- Addressing

- Instruction set list

- · Description of instructions

- · Cautions on use

#### Cautions on use -

Cautions regarding the use of the 78K/III Series instructions are collected in CHAPTER 7 CAUTIONS ON USE. Be sure to read this chapter.

Ask NEC or an NEC agent's salesperson for the latest information on the products.

## How to read this manual

The manual assumes that the reader has general knowledge of electricity, logical circuits, and microcomputers.

- · If the products are the same in function

- $\rightarrow$  This manual describes the  $\mu$ PD78356 as a typical product. To use this manual for other products, replace the  $\mu$ PD78356 with the appropriate product names in reading.

- · If the products differ in function

- ightarrow Functional differences are discussed for each product.

- To look up the instruction function in detail when you know the mnemonic of the instruction

- → Use APPENDIX B and APPENDIX C INSTRUCTION INDEX.

- To look up an instruction when you do not know its mnemonic, but know the rough function

- → Look up the mnemonic of the instruction in **CHAPTER 5 INSTRUCTION SET LIST**, then the instruction function in **CHAPTER 6 EXPLANATION OF INSTRUCTIONS**.

- To understand the instruction functions of the 78K/III Series products in a general way

- ightarrow Read the manual in the sequence of the table of contents.

- To learn the hardware functions of the 78K/III Series products

- → Refer to the following user's manuals:

| • | $\mu$ PD78352A | User's Manual | (IEU-781) |

|---|----------------|---------------|-----------|

| • | $\mu$ PD78356  | User's Manual | (U10669E) |

| • | $\mu$ PD78362A | User's Manual | (U10745E) |

| • | $\mu$ PD78366A | User's Manual | (U10205E) |

| • | μPD78372       | User's Manual | (U10642E) |

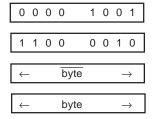

Legend

Data representation weight : High-order and low-order digits are indicated from

left to right.

Active low representation :  $\overline{\times\!\times\!\times}$  (pin or signal name is overlined)

Memory map address : Low-order part at upper stage, high-order part at

lower stage

Note : Explanation of (Note) in the text

Caution : Refers to contents that warrant special attention

Remark : Supplementary explanation to the text

Number representation : Binary number ...  $\times\!\times\!\times\!$ B or  $\times\!\times\!\times$

Decimal number ... ××××

Hexadecimal number ... ××××H

\* Related documents The related documents indicated in this publication may include preliminary version. However, preliminary version are not marked as such.

#### • Common Documents

| Document Name                                                         | Document No. |          |

|-----------------------------------------------------------------------|--------------|----------|

| Document Name                                                         | Japanese     | English  |

| μPD78356 User's Manual, Instruction                                   | U12117J      | IEU-1395 |

| 78K/III Series Application Note, Software Fundamental                 | U12118J      | IEA-1272 |

| 78K/III Series Application Note, Floating Point operation Programming | U12119J      | IEA-1291 |

| μPD78352A Instruction Set                                             | U11955J      | -        |

#### • Individual Documents

#### $\mu$ PD78352A Subseries

| Document Name                             | Document No. |          |

|-------------------------------------------|--------------|----------|

| Document Name                             | Japanese     | English  |

| μPD78352A Product Letter                  | IF-6335      | IF-2036  |

| μPD78350 Data Sheet                       | IC-8279      | IC-2845  |

| μPD78350A, 78352A Data Sheet              | IC-8823      | IC-3391  |

| μPD78P352 Data Sheet                      | IC-8423      | IC-2957  |

| μPD78352A User's Manual Hardware          | IEU-781      | IEU-1327 |

| μPD78352A Special Function Register Table | IEM-5540     | IEM-1215 |

#### $\mu$ PD78356 Subseries

| Document Name                                 | Document No. |          |

|-----------------------------------------------|--------------|----------|

| Document Name                                 | Japanese     | English  |

| μPD78356 Product Letter                       | IF-6298      | -        |

| μPD78355, 78356 Data Sheet                    | U10155J      | U10155E  |

| μPD78P356 Data Sheet                          | U10325J      | U10325E  |

| μPD78356(A) Data Sheet                        | U11148J      | U11148E  |

| μPD78P356(A) Data Sheet                       | U11149J      | U11149E  |

| μPD78356 User's Manual, Hardware              | U10669J      | U10669E  |

| $\mu$ PD78356 Special Function Register Table | IEM-5576     | IEM-1214 |

Caution The contents of the documents listed above are subject to change without prior notice to user's. Be sure to use the latest edition when starting design.

#### $\mu$ PD78366A Subseries

| Document Name                             | Docum    | ent No. |

|-------------------------------------------|----------|---------|

| Document Name                             | Japanese | English |

| μPD78362A Data Sheet                      | U10098J  | U10098E |

| μPD78P364A Data Sheet                     | U10106J  | U10106E |

| μPD78363A, 78365A, 78366A Data Sheet      | U11109J  | U11109E |

| μPD78P368A Data Sheet                     | U11373J  | U11373E |

| μPD78362A User's Manual, Hardware         | U10745J  | U10745E |

| μPD78366A User's Manual, Hardware         | U10205J  | U10205E |

| μΡD78362A Special Function Register Table | U10210J  | -       |

| μΡD78366A Special Function Register Table | U10107J  | _       |

#### $\mu$ PD78372 Subseries

| Document Name                            | Document No. |         |

|------------------------------------------|--------------|---------|

|                                          | Japanese     | English |

| μPD78372 Product letter                  | IF-6351      | _       |

| μPD78370(A), 78372(A) Data Sheet         | U10789J      | U10789E |

| μPD78P372(A) Data Sheet                  | U12029J      | U12029E |

| μPD78372 User's Manual, Hardware         | U10642J      | U10642E |

| μPD78372 Special Function Register Table | U10631J      | U10631E |

Caution The contents of the documents listed above are subject to change without prior notice to user's. Be sure to use the latest edition when starting design.

#### **CONTENTS**

| HAPTI | ER 1 G     | ENERAL DESCRIPTION                                                  |

|-------|------------|---------------------------------------------------------------------|

| 1.1   | 78K/II     | I Series Product Development                                        |

| 1.2   | $\mu$ PD78 | 8352A Subseries Products Overview                                   |

|       | 1.2.1      | Features                                                            |

|       | 1.2.2      | Application fields                                                  |

|       | 1.2.3      | Ordering information and quality grade                              |

|       | 1.2.4      | Function outline                                                    |

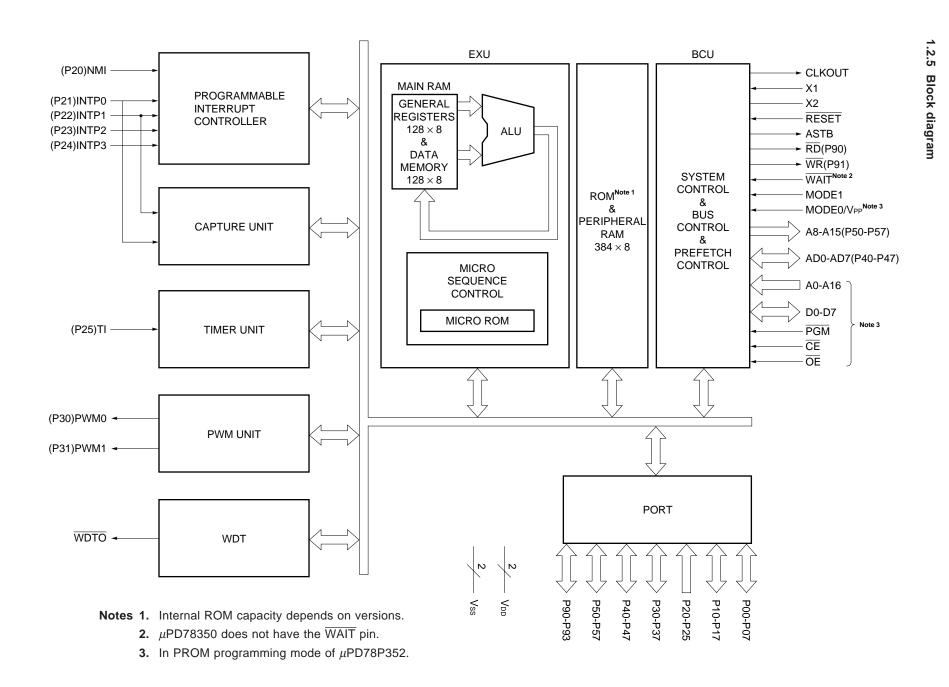

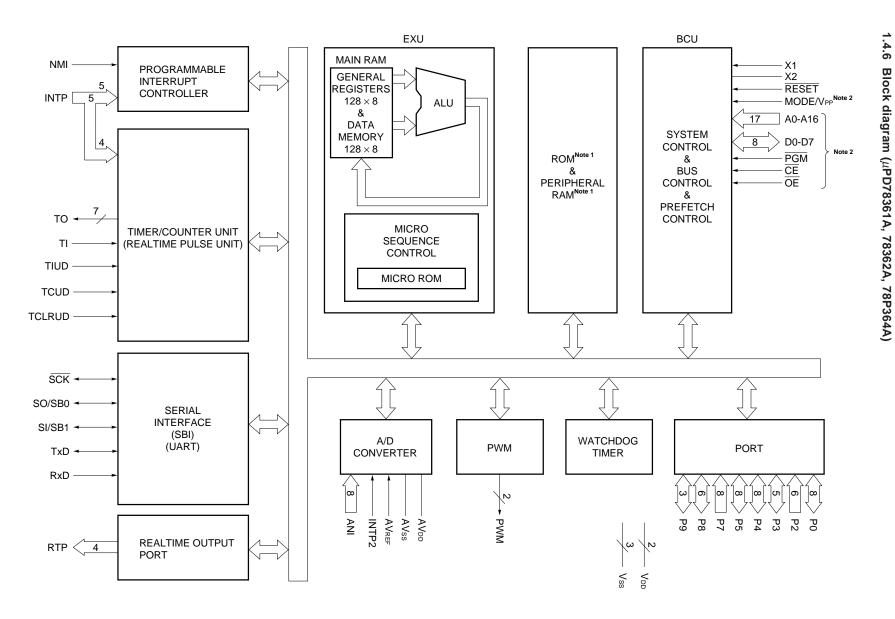

|       | 1.2.5      | Block diagram                                                       |

| 1.3   | Outlin     | ne of $\mu$ PD78356 Subseries Products                              |

|       | 1.3.1      | Features                                                            |

|       | 1.3.2      | Application fields                                                  |

|       | 1.3.3      | Ordering information and quality grade                              |

|       | 1.3.4      | Function outline                                                    |

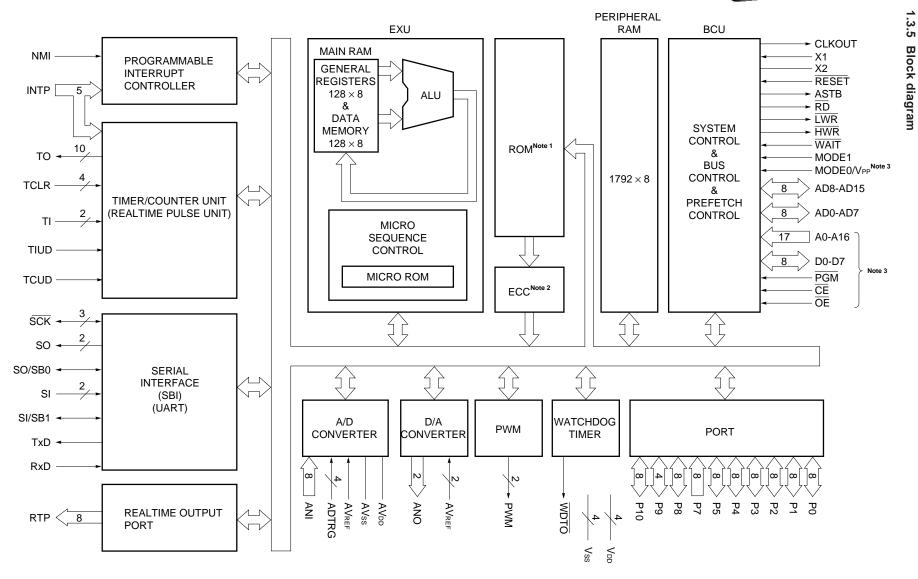

|       | 1.3.5      | Block diagram                                                       |

| 1.4   | $\mu$ PD7  | 8366 Subseries Products Overview                                    |

|       | 1.4.1      | Features                                                            |

|       | 1.4.2      | Application fields                                                  |

|       | 1.4.3      | Ordering information and quality grade                              |

|       | 1.4.4      | Function outline (μPD78361A, 78362A, 78P364A)                       |

|       | 1.4.5      | Function outline ( $\mu$ PD78363A, 78365A, 78366A, 78368A, 78P368A) |

|       | 1.4.6      | Block diagram (μPD78361A, 78362A, 78P364A)                          |

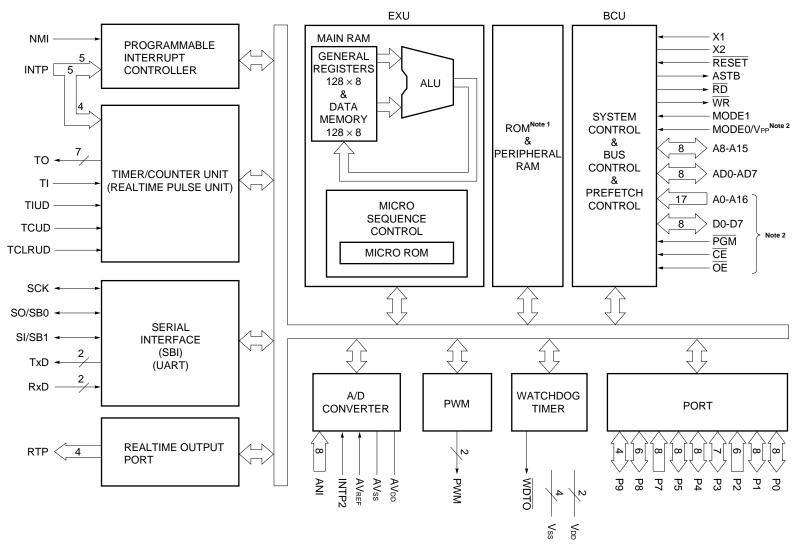

|       | 1.4.7      | Block diagram (μPD78363A, 78365A, 78366A, 78368A, 78P368A)          |

| 1.5   | $\mu$ PD7  | 8372 Subseries Products Overview                                    |

|       | 1.5.1      | Features                                                            |

|       | 1.5.2      | Application fields                                                  |

|       | 1.5.3      | Ordering information and quality grade                              |

|       | 1.5.4      | Function outline                                                    |

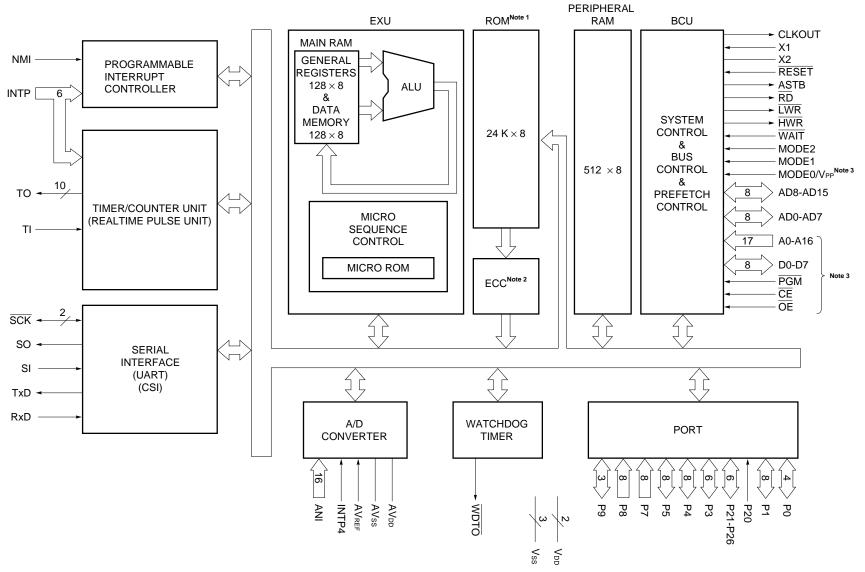

|       | 1.5.5      | Block diagram                                                       |

|       |            |                                                                     |

| IAPTI | ER 2 T     | ARGET PRODUCT LIST                                                  |

| LADTI | -D 0 0     | DIL ADCIUTECTUDE                                                    |

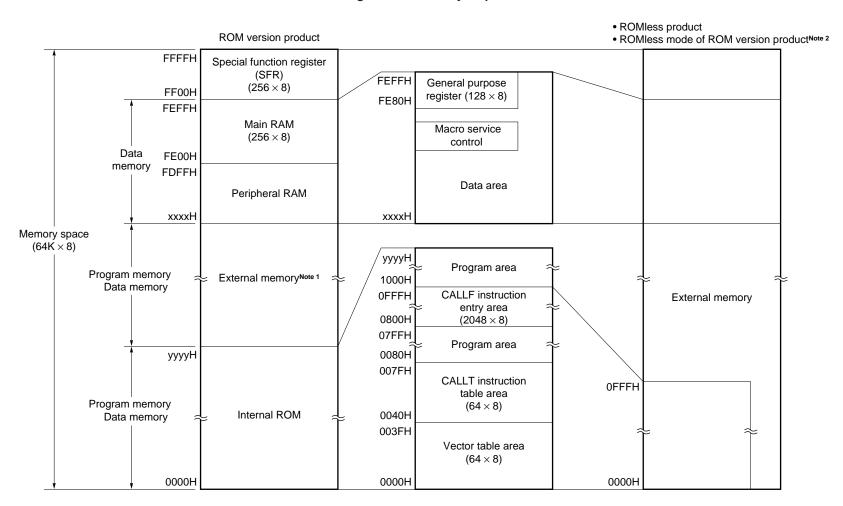

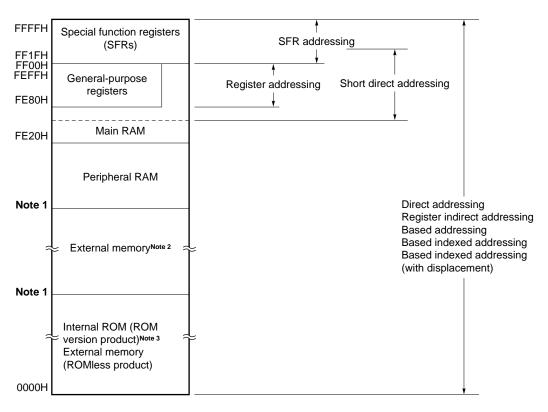

| 3.1   |            | PU ARCHITECTUREory Space                                            |

| 3.1   | 3.1.1      | Vector table area                                                   |

|       | 3.1.2      | CALLT instruction table area                                        |

|       | 3.1.2      | CALLF instruction entry area                                        |

|       | 3.1.4      | Internal RAM area                                                   |

|       | 3.1.4      | Special function register area                                      |

|       | 3.1.5      | External memory area                                                |

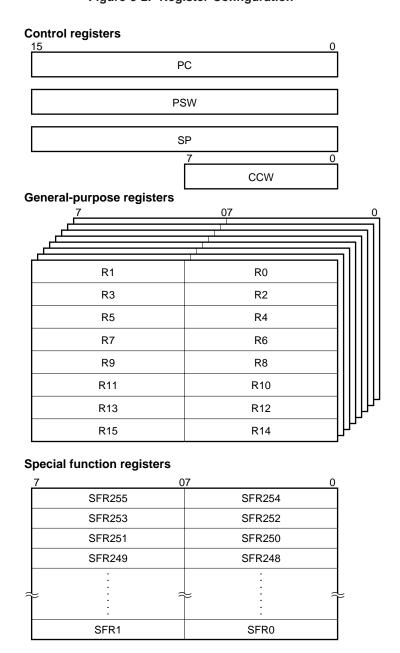

| 3.2   |            | essor Registers                                                     |

| J.Z   | 3.2.1      | Control registers                                                   |

|       | 3.2.1      | -                                                                   |

|       |            | General-purpose registers                                           |

|       | 3.2.3      | Opediai iuiidiidii teyisieis (OFNS)                                 |

| 3.3   | Data I                     | Memory Addressing                                         |

|-------|----------------------------|-----------------------------------------------------------|

|       | 3.3.1                      | General-purpose register addressing                       |

|       | 3.3.2                      | Short direct addressing                                   |

|       | 3.3.3                      | Special function register (SFR) addressing                |

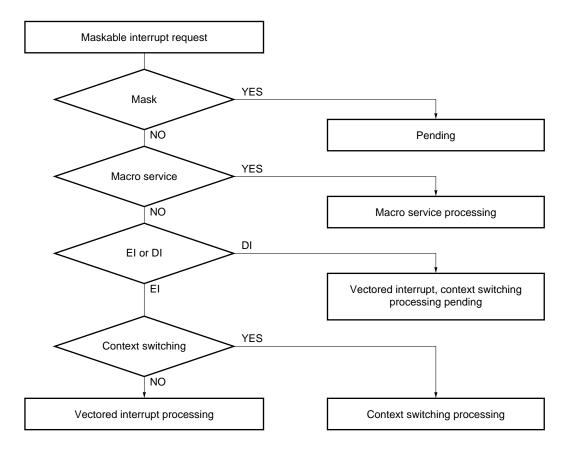

| 3.4   | Interru                    | upt Function                                              |

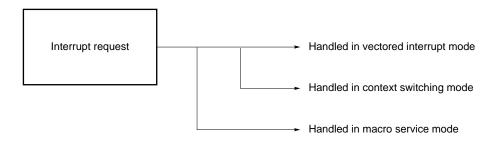

|       | 3.4.1                      | Interrupt request types                                   |

|       | 3.4.2                      | Interrupt processing modes                                |

|       | 3.4.3                      | Macro service function                                    |

|       | 3.4.4                      | Context switching function                                |

|       | 3.4.5                      | Interrupt execution rates                                 |

|       | 3.4.6                      | Control registers                                         |

| ∩⊔∧рт | ED 1 1                     | DDRESSING                                                 |

| 4.1   |                            | ction Addressing                                          |

| 7.1   | 4.1.1                      | Relative addressing                                       |

|       | 4.1.1                      | Immediate addressing                                      |

|       | 4.1.2                      | Table indirect addressing                                 |

|       | 4.1.3                      | Register addressing                                       |

|       | 4.1. <del>4</del><br>4.1.5 | Register indirect addressing                              |

| 4.2   | _                          | and Addressing                                            |

| -T.E  | 4.2.1                      | Register addressing                                       |

|       | 4.2.2                      | Immediate addressing                                      |

|       | 4.2.3                      | Direct addressing                                         |

|       | 4.2.4                      | Short direct addressing                                   |

|       | 4.2.5                      | Special function register (SFR) addressing                |

|       | 4.2.6                      | Short direct memory indirect addressing                   |

|       | 4.2.7                      | Register indirect addressing                              |

|       | 4.2.8                      | Based addressing                                          |

|       | 4.2.9                      | Indexed addressing                                        |

|       | 4.2.10                     | Based indexed addressing                                  |

|       |                            |                                                           |

|       |                            | STRUCTION SET LIST                                        |

| 5.1   |                            | Operations                                                |

|       | 5.1.1<br>5.1.2             | Operand identifier and description                        |

|       | 5.1.2                      | Legend                                                    |

|       | 5.1.3<br>5.1.4             | Notational symbols in flag operation field                |

|       | 5.1.4<br>5.1.5             | Instruction set differences among 78K/III Series products |

| 5.2   |                            | Operations of basic instructions                          |

| 5.2   |                            | Ction Codes                                               |

|       | 5.2.1                      | Symbols of instruction codes                              |

|       | 5.2.2                      | Instruction codes in various memory addressing modes      |

| 5.3   | 5.2.3                      | er of Clocks of the Instructions                          |

| 5.5   | 5.3.1                      | Description of clock columns                              |

|       | 5.3.1                      | Numbers of clocks                                         |

|       |                            |                                                           |

|   | CHAPTE | R 6 EXPLANATION OF INSTRUCTIONS                                      | 137 |

|---|--------|----------------------------------------------------------------------|-----|

|   | 6.1    | 8-Bit Data Transfer Instructions                                     | 139 |

|   | 6.2    | 16-Bit Data Transfer Instructions                                    | 142 |

|   | 6.3    | 8-Bit Operation Instructions                                         | 145 |

|   | 6.4    | 16-Bit Operation Instructions                                        | 156 |

|   | 6.5    | Multiplication and Division Instructions                             | 160 |

|   | 6.6    | Signed Multiplication Instruction                                    | 165 |

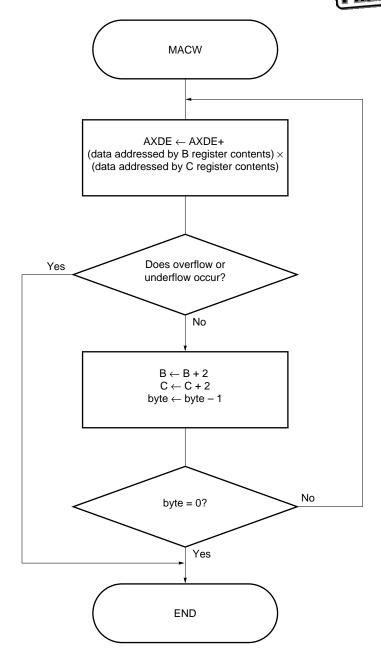

|   | 6.7    | Multiplication and Accumulation Instruction                          | 167 |

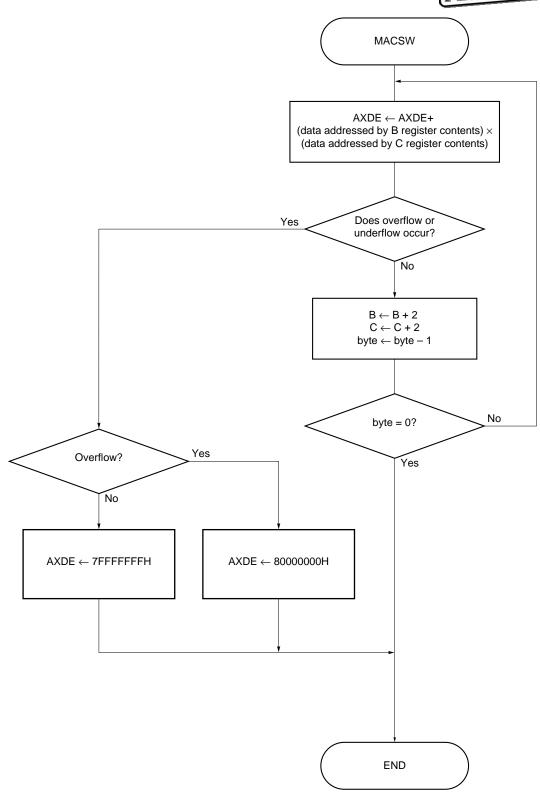

|   | 6.8    | Multiplication and Accumulation Instruction With Saturation Function | 170 |

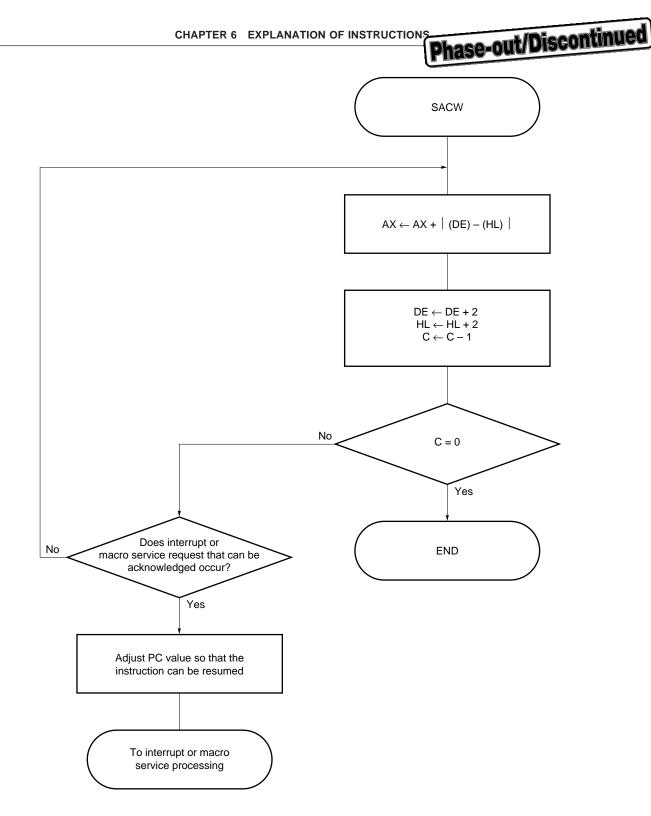

|   | 6.9    | Correlation Operation Instruction                                    | 173 |

|   | 6.10   | Table Shift Instruction                                              | 176 |

|   | 6.11   | Increment and Decrement Instructions                                 | 178 |

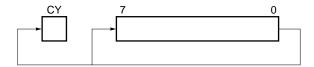

|   | 6.12   | Shift and Rotate Instructions                                        | 183 |

|   | 6.13   | BCD Adjustment Instruction                                           | 194 |

|   | 6.14   | Data Conversion Instruction                                          | 197 |

|   | 6.15   | Bit Manipulation Instructions                                        | 199 |

|   | 6.16   | Call and Return Instructions                                         | 207 |

|   | 6.17   | Stack Handling Instructions                                          | 215 |

|   | 6.18   | Special Instructions                                                 | 223 |

|   | 6.19   | Unconditional Branch Instruction                                     | 226 |

|   | 6.20   | Conditional Branch Instructions                                      | 228 |

|   | 6.21   | Context Switching Instructions                                       | 248 |

|   | 6.22   | String Instructions                                                  | 252 |

|   | 6.23   | CPU Control Instructions                                             | 273 |

|   | CHAPTE | R 7 CAUTIONS ON USE                                                  |     |

|   | 7.1    | Cautions on CHAPTER 3 CPU ARCHITECTURE                               | 283 |

|   | 7.2    | Cautions on CHAPTER 5 INSTRUCTION SET LIST                           | 284 |

|   | 7.3    | Cautions on CHAPTER 6 EXPLANATION OF INSTRUCTIONS                    | 284 |

|   | APPEND | DIX A TOOLS                                                          | 285 |

|   | A.1    | 78K/III Series Common Tools                                          | 285 |

|   | A.2    | $\mu$ PD78352A Subseries Tools                                       | 286 |

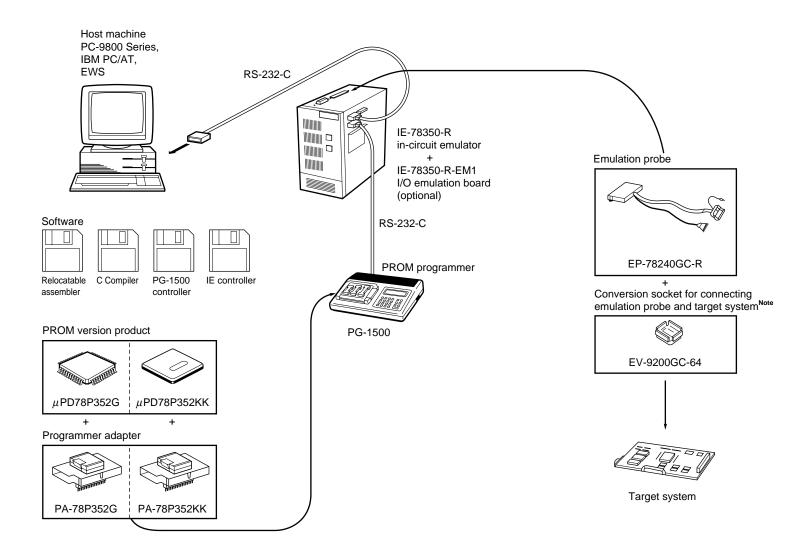

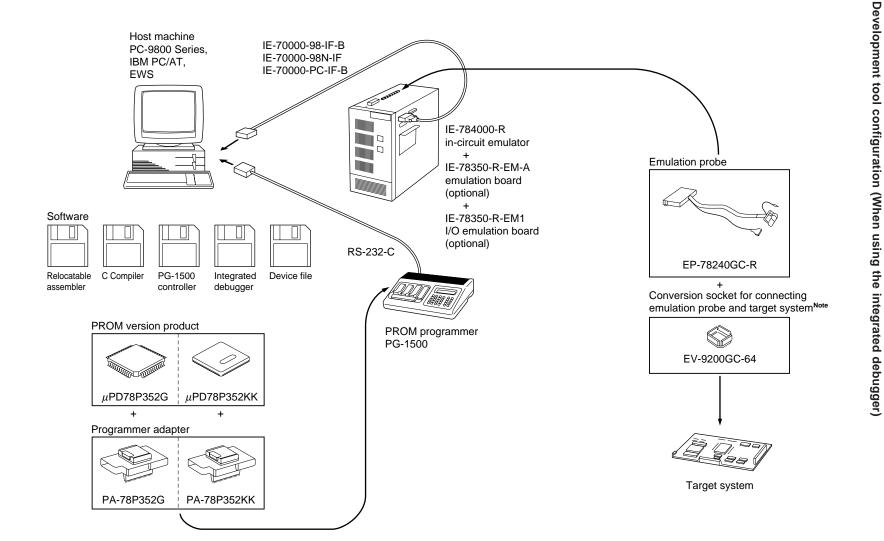

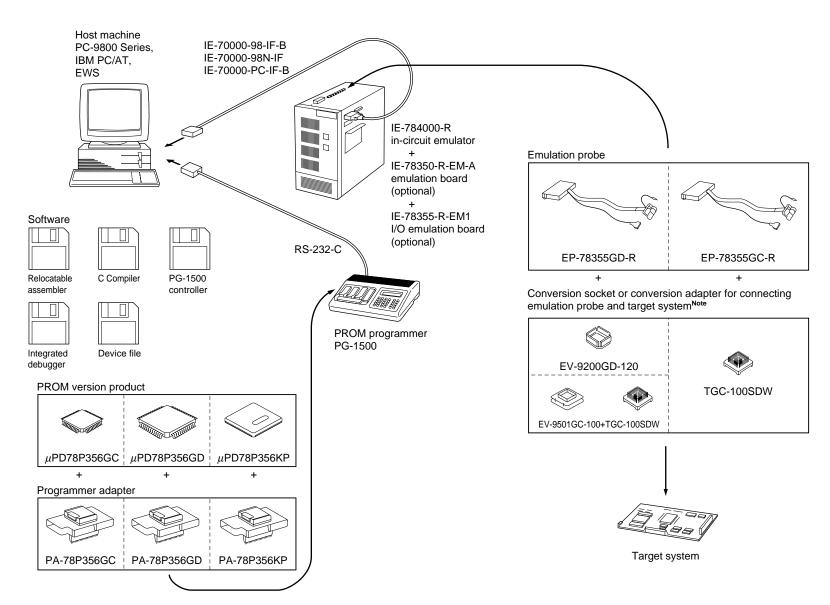

|   | A.3    | $\mu$ PD78356 Subseries Tools                                        | 292 |

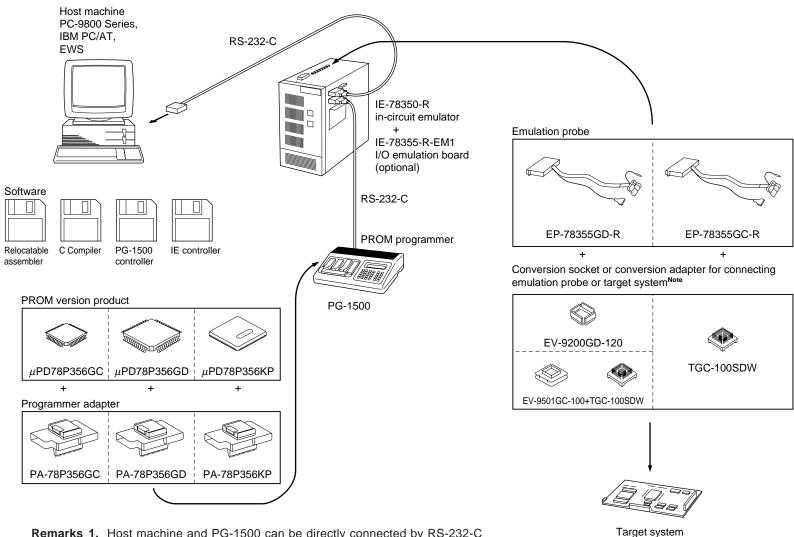

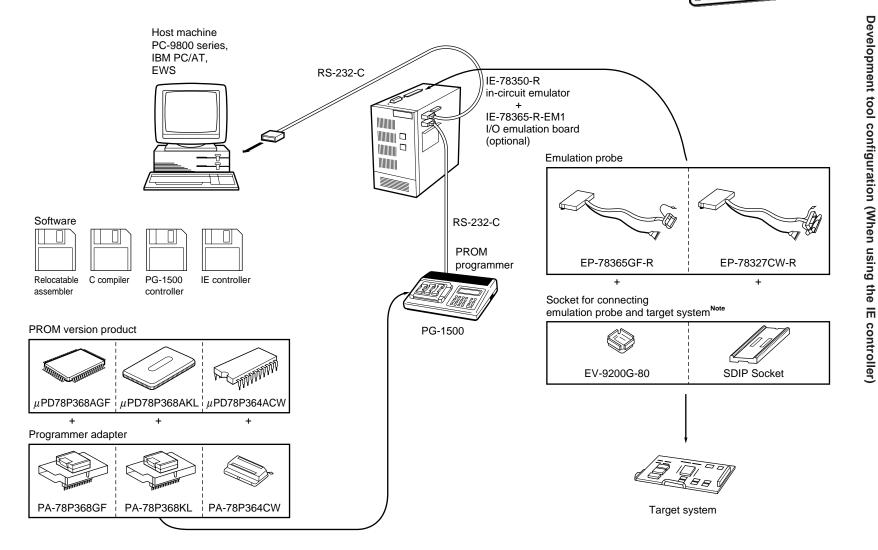

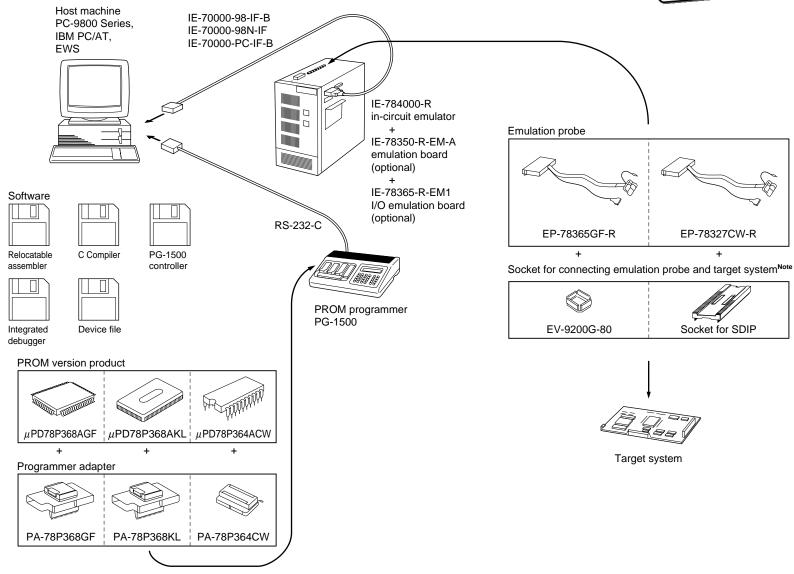

|   | A.4    | $\mu$ PD78366A Subseries Tools                                       | 298 |

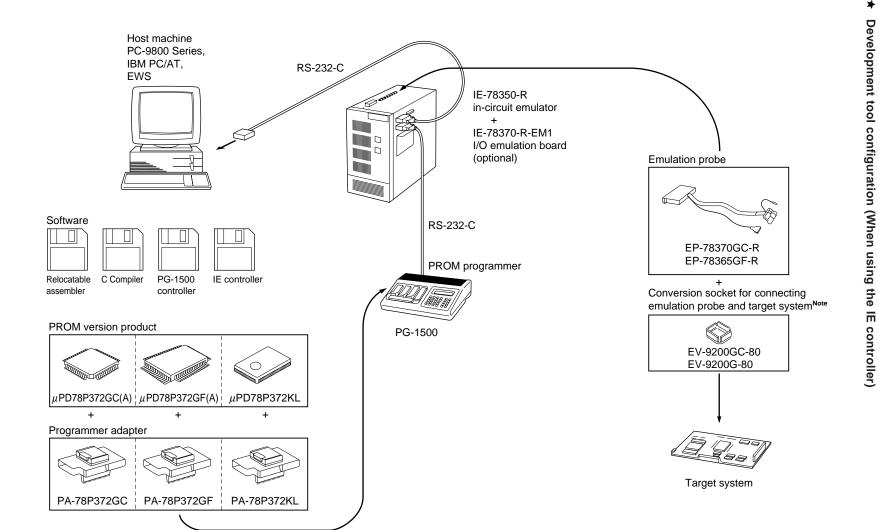

|   | A.5    | μPD78372 Subseries Tools                                             | 303 |

| * | A.6    | Embedded Software                                                    | 308 |

|   | APPEND | DIX B INSTRUCTION INDEX (MNEMONICS BY FUNCTION)                      | 311 |

|   | APPEND | DIX C INSTRUCTION INDEX (MNEMONICS BY ALPHABETICAL ORDER)            | 313 |

| * | APPEND | DIX D REVISION HISTORY                                               | 315 |

#### **LIST OF FIGURES**

| Figure No. | Title                                                            | Page |

|------------|------------------------------------------------------------------|------|

| 1-1        | Configurations of 78K Series and 78K/III Series                  | 1    |

| 3-1        | Memory Map                                                       | 30   |

| 3-2        | Register Configuration                                           | 40   |

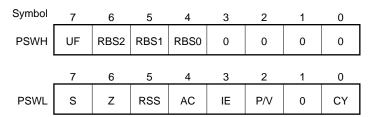

| 3-3        | Format of Program Status Word (PSW)                              | 41   |

| 3-4        | Format of CPU Control Word                                       | 44   |

| 3-5        | Process Bits of General-Purpose Registers                        | 45   |

| 3-6        | Data Memory Addressing                                           | 48   |

| 3-7        | Handling Interrupt Requests                                      | 50   |

| 3-8        | Process Flow of Maskable Interrupt                               | 52   |

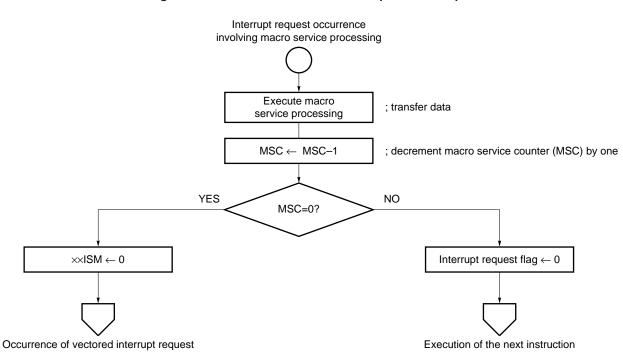

| 3-9        | Macro Service Process Sequence Example                           | 54   |

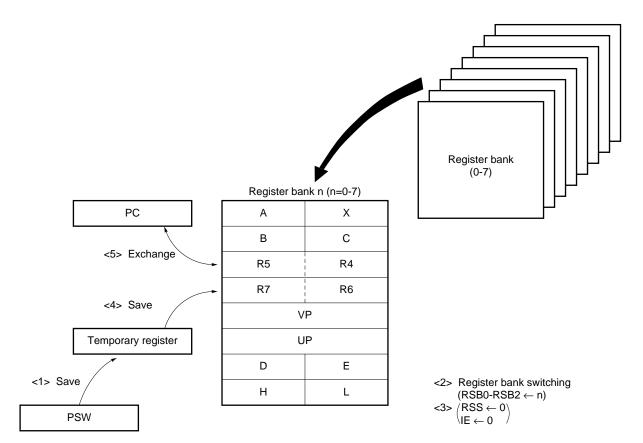

| 3-10       | Context Switching Operation when an Interrupt Request Occurs     | 55   |

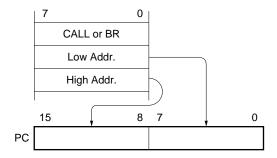

| 4-1        | Relative Addressing                                              | 59   |

| 4-2        | Immediate Addressing                                             | 60   |

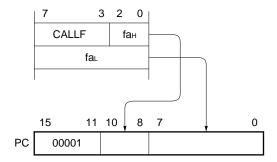

| 4-3        | Table Indirect Addressing                                        | 61   |

| 4-4        | Register Addressing                                              | 61   |

| 4-5        | Register Indirect Addressing                                     | 62   |

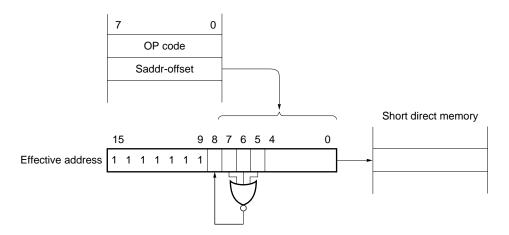

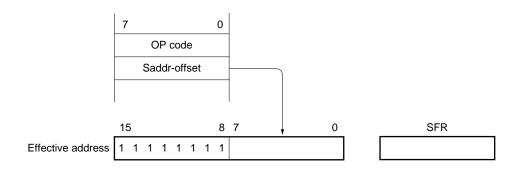

| 4-6        | Short Direct Addressing                                          | 66   |

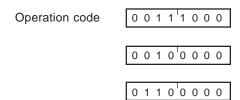

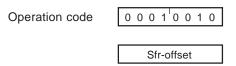

| 4-7        | Special Function Register Addressing                             | 67   |

| 4-8        | Short Direct Memory Indirect Addressing                          | 68   |

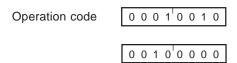

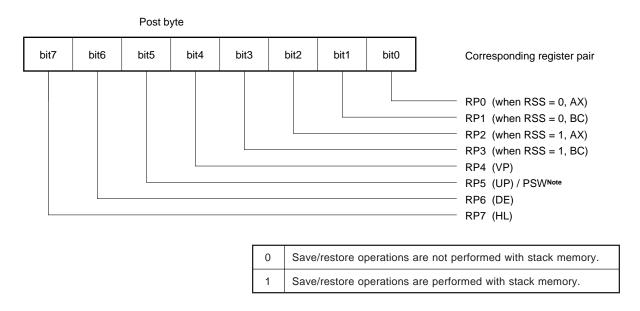

| 5-1        | 8-bit Data that Specifies the Register Pair which Performs Stack |      |

|            | Operations                                                       | 94   |

#### LIST OF TABLE

| Table No. | Title                                                                      | Page |

|-----------|----------------------------------------------------------------------------|------|

| 3-1       | Vector Table Area                                                          | 33   |

| 3-2       | Internal RAM Area List                                                     | 35   |

| 3-3       | Word Access Operation in Internal RAM Area                                 | 35   |

| 3-4       | External Memory Area List                                                  | 39   |

| 3-5       | Configuration of General-Purpose Registers                                 | 46   |

| 3-6       | Interrupt Requests and Processing Modes                                    | 50   |

| 3-7       | Control Register List (µPD78352A Subseries)                                | 57   |

| 3-8       | Control Register List (µPD78356 Subseries)                                 | 57   |

| 3-9       | Control Register List (µPD78366A Subseries)                                | 57   |

| 3-10      | Control Register List (μPD78372 Subseries)                                 | 57   |

| 5-1       | Operand Identifier and Description                                         | 73   |

| 5-2       | Absolute Names and Their Corresponding Function Names of an 8-bit Register | 74   |

| 5-3       | Absolute Names and Their Corresponding Function Names of a 16-bit Register | 74   |

| 5-4       | Notational Symbols in Flag Operation Field                                 | 76   |

| 5-5       | Instruction Set Differences among 78K/III Series Products                  | 77   |

| 5-6       | mod and mem Codes in the Instruction Code Field                            | 96   |

| 5-7       | Instruction Execution Cycles                                               | 132  |

[MEMO]

Phase-out/Discontinued

#### **CHAPTER 1 GENERAL DESCRIPTION**

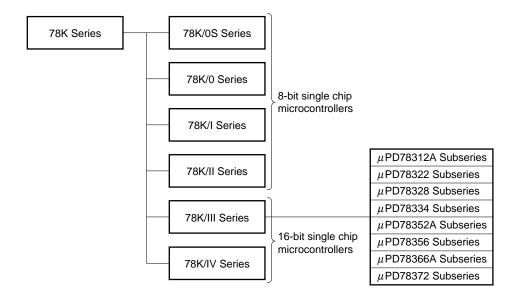

The 78K Series consists of six series as shown in Figure 1-1.

The 78K/III Series, which is one of the six series, provides products each containing a 16-bit CPU.

The on-chip CPU is a high-function CPU which has an instruction set and a high-speed interrupt controller appropriate for control application and comprises a memory space of a maximum of 64K bytes.

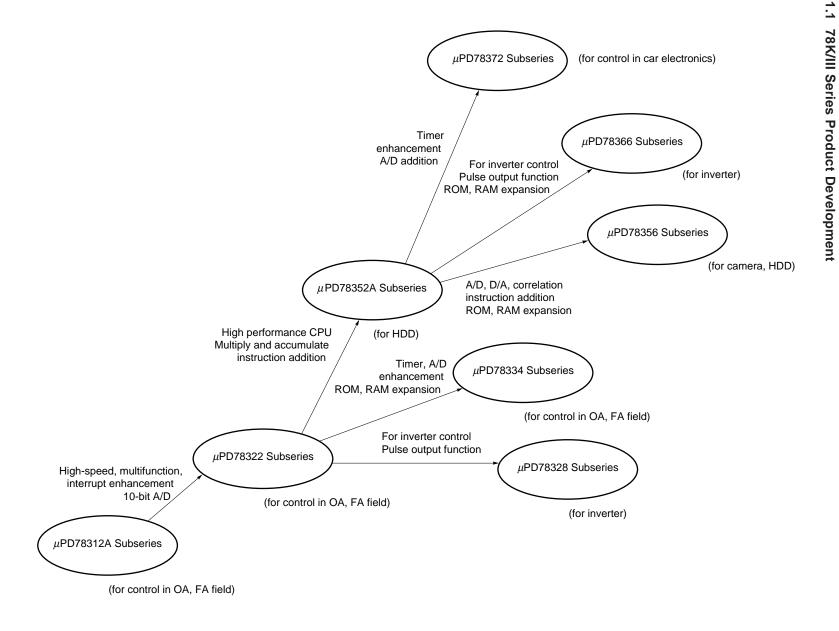

The 78K/III Series comprises eight subseries:  $\mu$ PD78312A, 78322, 78328, 78334, 78352A, 78356, 78366A, and 78372, from which the user can select the most appropriate subseries according to the application.

This manual covers only the four subseries of  $\mu$ PD78352A, 78356, 78366A, and 78372, which differ only in peripheral hardware and have the same CPU. Therefore, they have a common instruction set except that the  $\mu$ PD78352A Subseries does not have a multiply and accumulate instruction with a saturation function or a correlation operation instruction.

#### Figure 1-1. Configurations of 78K Series and 78K/III Series

CHAPTER 1

GENERAL DESCRIPTION

:

#### 1.2 $\mu$ PD78352A Subseries Products Overview

Applicable products:  $\mu$ PD78350, 78350A, 78352A, 78P352

#### 1.2.1 Features

- O Internal 16-bit architecture, external 8-bit data bus

- O Pipeline control system and high-speed operation clock for high-speed processing

Minimum instruction execution time: 160 ns (internal clock: 12.5 MHz, external clock: 25 MHz)

...μPD78350

125 ns (internal clock: 16 MHz, external clock: 32 MHz)

...μPD78350A, 78352A, 78P352

- O Instruction set of 113 types of instructions appropriate for control application

- $\bigcirc$  Bus cycle wait control can be performed externally (except for  $\mu$ PD78350)

- O 8-bit resolution PWM signal output function: Two channels

- O Internal high-speed interrupt controller

O Internal memory: 32-Kbyte ROM (μPD78352A)

None (μPD78350, 78350A) 32-Kbyte PROM (μPD78P352)

640-byte RAM

#### 1.2.2 Application fields

- Office automation (OA) field such as HDD and FDD

- O Factory automation (FA) field

#### 1.2.3 Ordering information and quality grade

#### (1) Ordering information

| Part number                        | Package                                                         | Internal ROM  |

|------------------------------------|-----------------------------------------------------------------|---------------|

| μPD78350GC-3BE                     | 64-pin plastic QFP (14 $\times$ 14 mm) (resin thickness 2.7 mm) | None          |

| μPD78350AG-22                      | 64-pin plastic QFP (14 $\times$ 14 mm) (resin thickness 1.5 mm) | None          |

| μPD78352AG-×××-22                  | 64-pin plastic QFP (14 $\times$ 14 mm) (resin thickness 1.5 mm) | Mask ROM      |

| μPD78P352G-22                      | 64-pin plastic QFP (14 × 14 mm) (resin thickness 1.5 mm)        | One-time PROM |

| $\mu$ PD78P352KK-S <sup>Note</sup> | 64-pin ceramic WQFN                                             | EPROM         |

Note Under development

Remark xxx is a ROM code number.

#### (2) Quality grade

Standard

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

#### 1.2.4 Function outline

|                                                                                                                                       | Part n   | umber   | μPD78350                                                                                                                                                                                                                                | μPD78350A                                             | μPD78352A                 | μPD78P352               |

|---------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------|-------------------------|

| Parameter                                                                                                                             |          |         | μΕΒ16330                                                                                                                                                                                                                                | με 07 6330Α                                           | με υτουσελ                | με υτο ε 352            |

| Minimum instruction execution time                                                                                                    |          |         | 160 ns internal clock: 12.5 MHz, external clock: 25.0 MHz                                                                                                                                                                               | 125 ns internal clock: 16 MHz, external clock: 32 MHz |                           | lz,<br>Hz               |

| Internal mem                                                                                                                          | nory     | ROM     | -                                                                                                                                                                                                                                       | -                                                     | 32 Kbytes                 | _                       |

|                                                                                                                                       |          | PROM    | -                                                                                                                                                                                                                                       | -                                                     | _                         | 32 Kbytes               |

|                                                                                                                                       |          | RAM     |                                                                                                                                                                                                                                         | 640 l                                                 | bytes                     |                         |

| Memory space                                                                                                                          | ice      |         | 64 Kbytes (external exp                                                                                                                                                                                                                 | pansion is enabled)                                   |                           |                         |

| General-purp                                                                                                                          | pose re  | gisters | 8 bits × 16 registers × 8                                                                                                                                                                                                               | 8 banks                                               |                           |                         |

| No. of basic                                                                                                                          | instruct | tions   | 113                                                                                                                                                                                                                                     |                                                       |                           |                         |

| Instruction se                                                                                                                        | et       |         | <ul> <li>16-bit transfer and operations</li> <li>Multiplication and division (16 bits × 16 bits, 32 bits ÷ 16 bits)</li> <li>Bit manipulation</li> <li>String</li> <li>Multiply and accumulate (16 bits × 16 bits + 32 bits)</li> </ul> |                                                       |                           |                         |

| Input/output                                                                                                                          | lines    | Input   | 6                                                                                                                                                                                                                                       |                                                       |                           |                         |

|                                                                                                                                       |          | I/O     | 24 44                                                                                                                                                                                                                                   |                                                       |                           | 4                       |

| Capture/time                                                                                                                          | er unit  |         | <ul> <li>16-bit timer × 1 16-bit capture regi</li> <li>16-bit timer × 1 16-bit compare regi</li> <li>16-bit timer × 1 16-bit compare region</li> </ul>                                                                                  | gister × 1                                            |                           |                         |

| PWM unit                                                                                                                              |          |         | 8-bit resolution PWM o                                                                                                                                                                                                                  | utput: Two channels                                   |                           |                         |

| Interrupt fund                                                                                                                        | ction    |         | <ul><li>External: 5, internal</li><li>Four priority levels c</li><li>One of three interrup</li></ul>                                                                                                                                    |                                                       | selected                  |                         |

| External wait                                                                                                                         | t pin    |         | None                                                                                                                                                                                                                                    | External                                              | bus cycle wait control is | enabled                 |

| Packages Without window 64-pin plastic QFP (14 × 14 mm) (resin thickness 2.7 mm) 64-pin plastic QFP (14 × 14 mm) (resin thickness 1.5 |          |         | ckness 1.5 mm)                                                                                                                                                                                                                          |                                                       |                           |                         |

| \                                                                                                                                     | With wi  | ndow    |                                                                                                                                                                                                                                         | _                                                     |                           | 64-pin ceramic WQFNNote |

| Others  • Watchdog timer is contained • Standby function (HALT mode, STOP mode)                                                       |          |         |                                                                                                                                                                                                                                         |                                                       |                           |                         |

#### 1.3 Outline of $\mu$ PD78356 Subseries Products

Applicable products:  $\mu$ PD78355, 78356, 78P356, 78355A, 78356A, 78P356A

|          | 1.3.1   | Features                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------|

|          | $\circ$ | Internal 16-bit architecture, external 16-bit or 8-bit data bus                                                          |

|          | $\circ$ | Pipeline control system and high-speed operation clock for high-speed processing                                         |

|          |         | Minimum instruction execution time: 125 ns (internal clock: 16 MHz, external clock: 32 MHz) $\mu$ PD78355, 78356, 78P356 |

| <b>k</b> |         | 160 ns (internal clock: 12.5 MHz, external clock: 25 MHz)μPD78356(A), 78P356(A)                                          |

|          | $\circ$ | Instruction set of 115 types of instructions appropriate for control application                                         |

|          | $\circ$ | Real-time pulse unit provided with various timer/counters                                                                |

|          | $\circ$ | Ultra high-speed 10-bit resolution A/D converter: 8 channels                                                             |

|          |         | A/D conversion time: About 2 $\mu$ s at 32-MHz operation for $\mu$ PD78355, 78356, and 78P356                            |

| k        |         | About 2 $\mu$ s at 25-MHz operation for $\mu$ PD78356(A), 78P356(A)                                                      |

|          | 0       | 8-bit resolution D/A converter: Two channels                                                                             |

|          | $\circ$ | 8-, 10-, 12-bit resolution variable PWM signal output function: Two channels                                             |

|          | 0       | Three independent channels of serial interface (containing dedicated baud rate generator)                                |

|          | 0       | Internal high-speed interrupt controller                                                                                 |

|          | 0       | Internal ECC circuit (µPD78P356 and 78P356(A))                                                                           |

|          |         | Internal PROM contents can be made highly reliable                                                                       |

|          | 0       | Internal memory: 48-Kbyte ROM (μPD78356, 78356(A))                                                                       |

|          |         | None ( $\mu$ PD78355)                                                                                                    |

|          |         | 48-Kbyte PROM (μPD78P356, 78P356(A))                                                                                     |

|          |         | 2-Kbyte RAM                                                                                                              |

#### 1.3.2 Application fields

#### Standard

- $\bigcirc$  For high-speed servo control of HDD, FDD, etc.

- $\ensuremath{\bigcirc}$  For auto focus control of camcorder, single-lens reflex camera, etc.

- O For motor control in factory automation (FA) field

#### ★ • Special

O For car electronics controller

#### 1.3.3 Ordering information and quality grade

#### $\star$ (1) $\mu$ PD78355, 78356, 78P356

#### · Ordering information

| Part number                             | Package                                 | Internal ROM  |

|-----------------------------------------|-----------------------------------------|---------------|

| μPD78355GC-7EA                          | 100-pin plastic QFP (14 × 14 mm)        | None          |

| $\mu$ PD78355GD-5BB                     | 120-pin plastic QFP (28 $\times$ 28 mm) | None          |

| $\mu$ PD78356GC- $\times$ $\times$ -7EA | 100-pin plastic QFP (14 $\times$ 14 mm) | Mask ROM      |

| $\mu$ PD78356GD- $\times\times$ -5BB    | 120-pin plastic QFP (28 × 28 mm)        | Mask ROM      |

| $\mu$ PD78P356GC-7EA                    | 100-pin plastic QFP (14 $	imes$ 14 mm)  | One-time PROM |

| $\mu$ PD78P356GD-5BB                    | 120-pin plastic QFP (28 $\times$ 28 mm) | One-time PROM |

| μPD78P356KP-S                           | 120-pin ceramic WQFN                    | EPROM         |

**Remark** ××× is a ROM code number.

#### · Quality grade

Standard

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

#### $\star$ (2) $\mu$ PD78356(A), 78P356(A)

#### Ordering information

| Part number          | Package                                 | Internal ROM  |

|----------------------|-----------------------------------------|---------------|

| μPD78356GD(A)-××-5BB | 120-pin plastic QFP (28 $\times$ 28 mm) | Mask ROM      |

| μPD78P356GD(A)-5BB   | 120-pin plastic QFP (28 × 28 mm)        | One-time PROM |

Remark xxx is a ROM code number.

#### · Quality grade

Special

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

#### 1.3.4 Function outline

(1/2)

| Part Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | number   | μPD78355                                                     | μPD78356                           | μPD78P356          | μPD78356(A)                                                  | μPD78P356(A)           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|------------------------------------|--------------------|--------------------------------------------------------------|------------------------|--|

| Minimum instruction execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 125 ns I                                                     | internal clock: ' external clock:  |                    | 160 ns                                                       | clock: 12.5 MHz        |  |

| Internal memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROM      | _                                                            | 48 Kbytes                          | _                  | 48 Kbytes                                                    | _                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PROM     | -                                                            | _                                  | 48 Kbytes          | _                                                            | 48 Kbytes              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RAM      |                                                              | ı                                  | 2 Kb               | ytes                                                         |                        |  |

| Memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 64 Kbytes (ext                                               | ernal expansion                    | is enabled)        |                                                              |                        |  |

| General-purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | egisters | 8 bits × 16 reg                                              | isters × 8 banks                   |                    |                                                              |                        |  |

| No. of basic instru                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ctions   | 115                                                          |                                    |                    |                                                              |                        |  |

| Instruction set  • 16-bit transfer and operations • Multiplication and division (16 bits × 16 bits, 32 bits ÷ 16 bits) • Bit manipulation • String • Multiply and accumulate (16 bits × 16 bits + 32 bits) • Correlation operation                                                                                                                                                                                                                                                         |          |                                                              |                                    |                    |                                                              |                        |  |

| Input/output lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input    |                                                              | 9 (eig                             | ht lines are also  | used for analog input)                                       |                        |  |

| ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I/O      | 48                                                           |                                    |                    | 67                                                           |                        |  |

| <ul> <li>16-bit timer × 1 16-bit compare register × 4 16-bit capture/compare register × 3 timer output × 6</li> <li>16-bit timer × 1 16-bit compare register × 2 timer output × 2</li> <li>16-bit timer × 1 16-bit compare register × 2 timer output × 2</li> <li>16-bit timer × 1 16-bit timer × 1 16-bit capture/compare register × 2</li> <li>10-bit timer × 1</li> <li>10-bit compare register × 1</li> <li>16-bit up/down counter × 1</li> <li>16-bit compare register × 2</li> </ul> |          |                                                              |                                    | it. Eight          |                                                              |                        |  |

| Real-time output p                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ort      | Pulse output associated with real-time pulse unit: Eight     |                                    |                    |                                                              |                        |  |

| PWM unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 8-, 10-, 12-bit resolution variable PWM output: Two channels |                                    |                    |                                                              |                        |  |

| A/D converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 10-bit resolution, eight channels                            |                                    |                    |                                                              |                        |  |

| D/A converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 8-bit resolution, two channels                               |                                    |                    |                                                              |                        |  |

| Serial interface  With dedicated baud rate generator  UART: One channel  Clocked serial interface/SBI: One channel  Clocked serial interface (with pin change function): One channel                                                                                                                                                                                                                                                                                                       |          |                                                              |                                    |                    |                                                              |                        |  |

| Interrupt function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | Four priority                                                | levels can be se interrupt service | pecified by softwa | for external interrupts)<br>are<br>selected (vectored interr | upt, macro service, or |  |

#### **CHAPTER 1 GENERAL DESCRIPTION**

(2/2)

| Pai | rameter            | Part number    | μPD78355                                                                                                                                 | μPD78356                                                | μPD78P356      | μPD78356(A)  | μPD78P356(A) |  |

|-----|--------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------|--------------|--------------|--|

| Bus | s sizing           | function       | 8-bit or 16-bit e                                                                                                                        | 8-bit or 16-bit external data bus width can be selected |                |              |              |  |

| EC  | CC circuit         |                | No                                                                                                                                       | ne                                                      | Available      | None         | Available    |  |

|     | erating p<br>Itage | power supply   | 5 V ± 10 %                                                                                                                               |                                                         |                |              |              |  |

| Pad | ckages             | Without window | <ul> <li>100-pin plastic QFP (14 × 14 mm)</li> <li>120-pin plastic QFP (28 × 28 mm)</li> <li>120-pin plastic QFP (28 × 28 mm)</li> </ul> |                                                         |                | (28 × 28 mm) |              |  |

|     |                    | With window    | _ 120-pin ceramic WQFN                                                                                                                   |                                                         |                | -            |              |  |

| Oth | hers               |                | ı                                                                                                                                        | mer is contained                                        | de, STOP mode) |              |              |  |

Notes 1. Internal ROM capacity depends on versions.

- 2. Only  $\mu \text{PD78P356}$  and  $\mu \text{PD78P356(A)}$  contain the ECC circuit.

- 3. In PROM programming mode of  $\mu$ PD78P356 and 78P356(A).

#### 1.4 $\mu$ PD78366 Subseries Products Overview

★ Applicable products: μPD78361A, 78362A, 78P364A, 78363A, 78365A, 78366A, 78368A, 78P368A

#### 1.4.1 Features

- O Internal 16-bit architecture, external 8-bit data bus

- Pipeline control system and high-speed operation clock for high-speed processing

Minimum instruction execution time: 125 ns (internal clock: 16 MHz, external clock: 8 MHz)

- Internal PLL control circuit (external 8 MHz → internal 16 MHz)

- O Instruction set of 115 types of instructions appropriate for control application

- O Real-time pulse unit appropriate for inverter control of 10-bit resolution A/D converter: Eight channels

- 8-, 9-, 10-, 12-bit resolution variable PWM signal output function: Two channels

- O Two independent channels of serial interface (containing dedicated baud rate generator)

- O Internal high-speed interrupt controller

- O Internal memory: 24-Kbyte ROM (μPD78362A, 78363A)

32-Kbyte ROM (μPD78361A, 78366A)

48-Kbyte ROM (μPD78368A)

None (μPD78365A)

48-Kbyte PROM (μPD78P364A, 78P368A) 768-byte RAM (μPD78362A, 78363A)

2-Kbyte RAM (µPD78361A, 78365A, 78366A, 78368A, 78P364A, 78P368A)

#### 1.4.2 Application fields

- O Inverter air conditioners

- O Factory automation (FA) field of robots, automatic machine tools, etc.

#### 1.4.3 Ordering information and quality grade

#### (1) Ordering information

| Part number                                              | Package                                | Internal ROM  |

|----------------------------------------------------------|----------------------------------------|---------------|

| $\mu$ PD78361ACW- $\times\times$                         | 64-pin plastic shrink DIP (750 mil)    | Mask ROM      |

| $\mu$ PD78362ACW- $\times\!\!\times\!\!$                 | 64-pin plastic shrink DIP (750 mil)    | Mask ROM      |

| $\mu$ PD78P364ACW                                        | 64-pin plastic shrink DIP (750 mil)    | One-time PROM |

| $\mu$ PD78363AGF-×××-3B9                                 | 80-pin plastic QFP (14 $\times$ 20 mm) | Mask ROM      |

| μPD78365AGF-3B9                                          | 80-pin plastic QFP (14 × 20 mm)        | None          |

| $\mu$ PD78366AGF- $\times$ $\times$ -3B9                 | 80-pin plastic QFP (14 × 20 mm)        | Mask ROM      |

| $\mu$ PD78368AGF- $\times$ $\times$ -3B9 <sup>Note</sup> | 80-pin plastic QFP (14 × 20 mm)        | Mask ROM      |

| μPD78P368AGF-3B9                                         | 80-pin plastic QFP (14 $\times$ 20 mm) | One-time PROM |

| μPD78P368AKL-S                                           | 80-pin ceramic WQFN                    | EPROM         |

Note Under development

Remark xxx is a ROM code number.

#### (2) Quality grade

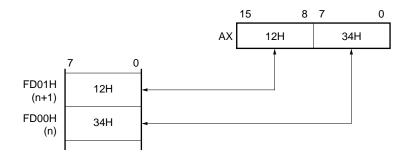

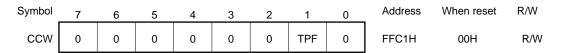

Standard