#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### USER'S MANUAL

## **μPD78138**

8-BIT SINGLE-CHIP MICROCOMPUTER

μPD78134A μPD78136 μPD78138 μPD78P138

## USER'S MANUAL

# μ**PD78138**8-BIT SINGLE-CHIP MICROCOMPUTER

μPD78134A μPD78136 μPD78138 μPD78P138

#### SUMMARY OF CONTENTS

| CHAPTER 1  | GENERAL                                              | T-T         |

|------------|------------------------------------------------------|-------------|

| CHAPTER 2  | PIN FUNCTIONS                                        | 2-1         |

| CHAPTER 3  | CPU FUNCTIONS                                        | 3-1         |

| CHAPTER 4  | CLOCK GENERATOR                                      | 4-1         |

| CHAPTER 5  | PORT FUNCTIONS                                       | 5-1         |

| CHAPTER 6  | REAL-TIME OUTPUT PORT (RTP)                          | 6-1         |

| CHAPTER 7  | SERIAL INTERFACE                                     | 7-1         |

| CHAPTER 8  | SUPER TIMER UNIT                                     | 8-1         |

| CHAPTER 9  | A/D CONVERTER                                        | 9-1         |

| CHAPTER 10 | CLOCK OUTPUT (CLO)                                   | 10-1        |

| CHAPTER 11 | INTERRUPT FUNCTION                                   | 11-1        |

| CHAPTER 12 | STANDBY FUNCTION                                     | 12-1        |

| CHAPTER 13 | RESET FUNCTION                                       | 13-1        |

| CHAPTER 14 | EXAMPLE OF APPLICATION                               | 14-1        |

| CHAPTER 15 | THE uPD78P138                                        | 15-1        |

| CHAPTER 16 | INSTRUCTION SET                                      | 16-1        |

| CHAPTER 17 | DIFFERENCES BETWEEN THE uPD78138 SERIES AND uPD78134 | 17-1        |

| APPENDIXES |                                                      | <b>A</b> -1 |

#### Cautions on CMOS Devices

- Countermeasures against static electricity for all MOSs Caution: When handling MOS devices, take care so that they are not electrostatically charged. Strong static electricity may cause dielectric breakdown in gates. When transporting or storing MOS devices, use conductive trays, magazine cases, shock absorbers, or metal cases that NEC uses for packaging and shipping. Be sure to ground MOS devices during assembling. Do not allow MOS devices to stand on plastic plates or do not touch pins.

Also handle boards on which MOS devices are mounted in the same way.

- (2) CMOS-specific handling of unused input pins Hold CMOS devices at a fixed input level. Caution: Unlike bipolar or NMOS devices, if a CMOS device is operated with no input, an intermediate-level input may be caused by This allows current to flow in the CMOS device, resulting in a malfunction. Use a pull-up or pull-down resistor to hold a fixed input level. Since unused pins may function as output pins at unexpected times, each unused pin should be separately connected to the  $V_{DD}$  or GND pin through a resistor. If handling of unused pins is documented, follow the instructions in the document.

- 3 Statuses of all MOS devices at initialization

Caution: The initial status of a MOS device is

unpredictable when power is turned on.

Since characteristics of a MOS device are

determined by the amount of ions implanted in

molecules, the initial status cannot be

determined in the manufacture process. NEC

has no responsibility for the output statuses

of pins, input and output settings, and the

contents of registers at power on. However,

NEC assures operation after reset and items

for mode setting if they are defined.

When you turn on a device having a reset

function, be sure to reset the device first.

#### MAJOR REVISIONS

| Page                                  | Description                                                                                                                                                           |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout                            | The uPD78134A and uPD78138 have already been developed.                                                                                                               |

| P.1-3                                 | The quality grade for the EPROM versions of the uPD78P138 has been changed from standard to not applied.                                                              |

| Preface,<br>PP.1-1, 1-7,<br>1-9, 15-1 | Caution on the EPROM versions of the uPD78P138 has been added.                                                                                                        |

| P.1-11                                | A product has been added to the list in Section 1.7.                                                                                                                  |

| P.5-9<br>P.5-21<br>P.5-32<br>P.5-38   | Caution on manipulating a port using an instruction such as a bit manipulation instruction has been added to: Section 5.3.2 Section 5.5.2 Section 5.7.2 Section 5.8.2 |

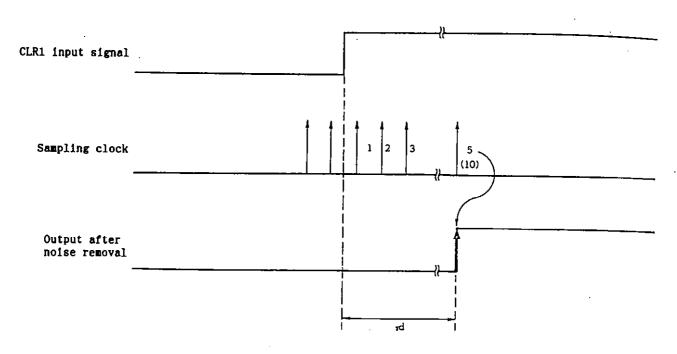

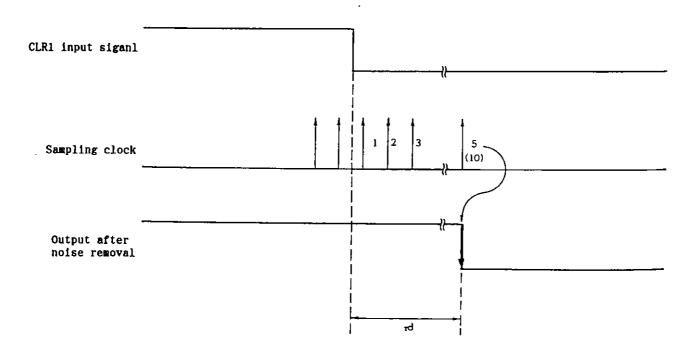

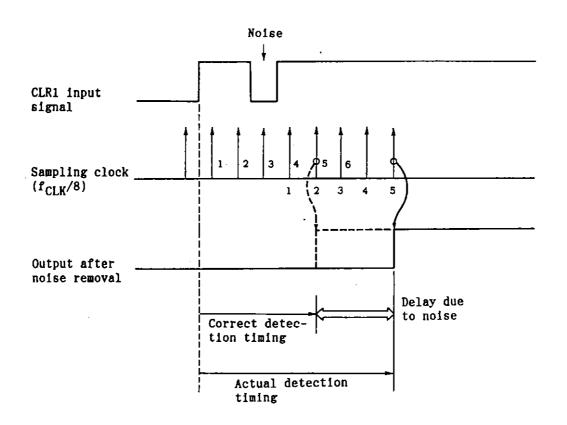

| P.8-51,<br>P.8-53                     | The delay between a CLR1 input signal and a signal output from the noise eliminator has been modified.                                                                |

| P.11-18 to<br>P.11-20                 | Section 11.4.2 has been added.                                                                                                                                        |

| P.16-61 to<br>P.16-188                | The examples of some instructions have been added to Section 16.6.                                                                                                    |

| P.17-1 to<br>P.17-3                   | Chapter 17 has been added.                                                                                                                                            |

| P.A-1 to<br>P.A-3                     | Appendix A has been modified.                                                                                                                                         |

#### **PREFACE**

Users:

This manual is for engineers who intend to learn the capabilities of the uPD78134A, uPD78136, uPD78138, and uPD78P138 for application program development.

The EPROM versions of the uPD78P138 are not intended for use in mass-produced products; they do not have reliability high enough for such purposes. use should be restricted to functional evaluation in experiment or trial manufacture.

Purpose:

The purpose of this manual is to help users understand the hardware capabilities of the uPD78134A, uPD78136, uPD78138, and uPD78P138.

#### Organization:

This manual includes the following items:

- General

- Pin functions

- CPU functions

- Peripheral functions

- Interrupt function

- Other built-in peripheral functions

- Standby function

- Reset function

- Applicable examples

- uPD78P138 (PROM product)

- Instruction functions

Guidance: Before using this manual, the user should have a general knowledge of the electronics, logical circuit, and microcomputer fields.

- . To use this manual as a uPD78134A, uPD78136, or uPD78P138 manual:

Where there is no functional difference, only the uPD78138 is described, and its descriptions are applicable to the uPD78134A, uPD78136, and uPD78P138.

- . To use this manual as a uPD78P138 manual:

In this manual, the description of the PROM is for both a one-time PROM and EPROM.

To use this manual as a uPD78P138 manual, each reference to PROM should be understood as a one-time PROM or EPROM.

- . To check the detailed functions of an instruction whose mnemonic is self-evident:

Look it up in Appendix B, "Instruction Index" (in alphabetic order).

- . To check an instruction whose mnemonic is not self-evident but whose functions are clear:

Check the mnemonic of the instruction in Section 16.1 and check the function of the instruction in Section 16.6.

- . To understand the general functions of the uPD78134A, uPD78136, uPD78138, and uPD78P138: Read the entire manual in the order of the table of contents.

For the electrical characteristics of the uPD78134A, uPD78136, uPD78138, and uPD78P138: See the separate Data Sheet.

For application examples of the functions of the uPD78134A, uPD78136, uPD78138, and uPD78P138: See the separate Application Note.

Notation: Data weight: Higher digits on the left side

Lower digits on the right side

Active low:  $\overline{xxx}$  (Pins and signal names are

overscored.)

Note: Explanation of the indicated part of

the text

Caution: Information requesting the user's

special attention

Remarks: Supplementary information

Numeric value: Binary: xxxxB or xxxx

Decimal: xxxx

Hexadecimal: xxxxH

#### Related publications:

| Product<br>Publication                        | uPD78134A   | uPD78136 | uPD78138 | uPD78P138   |

|-----------------------------------------------|-------------|----------|----------|-------------|

| Pamphlet                                      |             | IF-2     | 60       | <del></del> |

| Data sheet                                    |             | IC-8447  |          | IC-8051     |

| User's manual                                 | This manual |          |          |             |

| Mode register summary sheet                   | IEM-5529    |          |          |             |

| Instruction set                               | IEM-5530    |          |          |             |

| Instruction summary sheet                     | IEM-5531    |          |          |             |

| Application note<br>VCR servo program IEA-708 |             |          |          |             |

#### CONTENTS

| CHAPTER 1 | GENERAL                                     | 1-1  |

|-----------|---------------------------------------------|------|

| 1.1 Fea   | tures                                       | 1-2  |

| 1.2 App   | lications                                   | 1-3  |

| 1.3 Ord   | ering Information and Quality               |      |

| Gra       | de Standard                                 | 1-3  |

| 1.4 Fun   | ctional Overview                            | 1-4  |

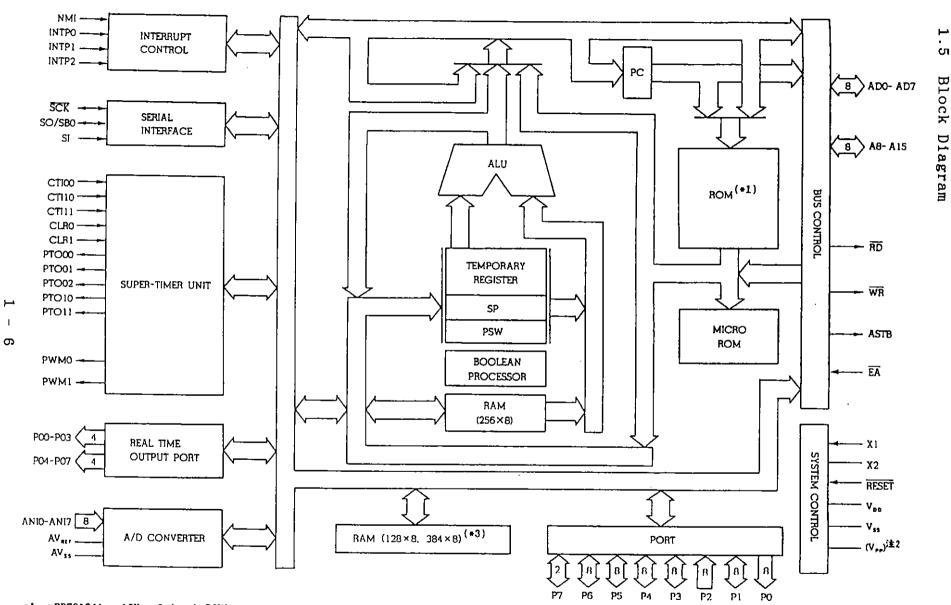

| 1.5 Blo   | ck Diagram                                  | 1-6  |

| 1.6 Pin   | Configuration (Top View)                    | 1-7  |

| 1.6.1     | Normal operation mode (uPD78134A, uPD78136, |      |

|           | uPD78138, and uPD78P138)                    | 1-7  |

| 1.6.2     | PROM programming mode (uPD78P138)           | 1-9  |

| 1.7 Fun   | ctions                                      | 1-11 |

| CHAPTER 2 | PIN FUNCTIONS                               | 2-1  |

| 2.1 Lis   | ts of Pin Functions                         | 2-1  |

| 2.1.1     | Normal operation mode                       | 2-1  |

| 2.1.2     | PROM programming mode (uPD78P138)           | 2-5  |

| 2.2 Pin   | Functions                                   | 2-6  |

| 2.2.1     | Normal operation mode                       | 2-6  |

| 2.2.2     | PROM programming mode (uPD78P138)           | 2-19 |

| 2.3 Inp   | ut/Output Circuits and Connection of        |      |

| Unus      | sed Pins                                    | 2-21 |

| CHAPTER 3 | CPU FUNCTIONS                               | 3-1  |

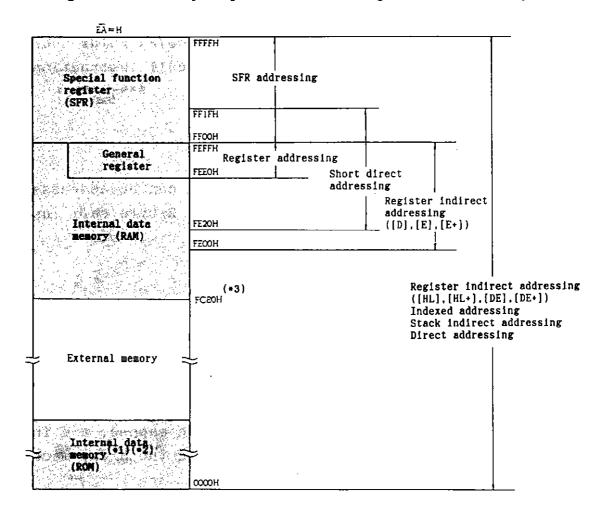

| 3.1 Memo  | ory Space                                   | 3-1  |

| 3.1.1     | Internal program memory space               | 3-6  |

| 3.1.2     | Internal data memory space                  | 3-7  |

| 3.1.3     | Special function register (SFR) space       | 3-7  |

| 3.1.4     | Data memory addressing                      | 3-7  |

| 3.2 Reg   | lsters                                      | 3-12 |

| 3.2.1     | Program counter (PC)                        | 3-12 |

| 3.2.2     | Program status word (PSW)                   | 3-12 |

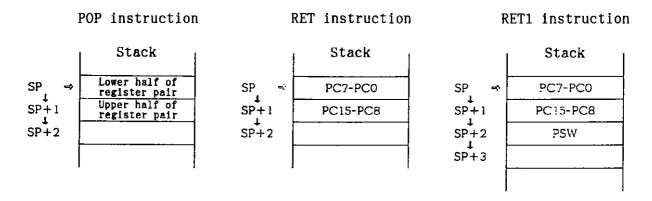

| 3.2.3     | Stack pointer (SP)                          | 3-15 |

| 3.2.4     | General registers                           | 3-17 |

| Phase-out/Discontinued |

|------------------------|

|------------------------|

| 3.2.5 Special function registers (SFRs)        | 3-19 |

|------------------------------------------------|------|

| 3.3 External Expansion Functions               | 3-27 |

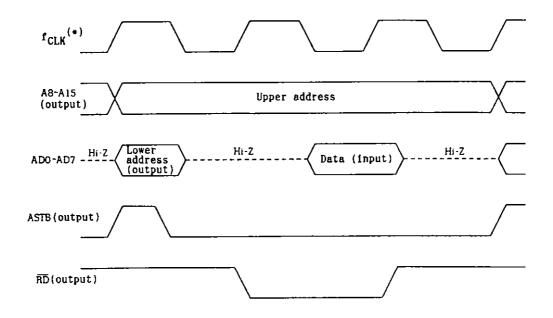

| 3.3.1 Bus interface function                   | 3-27 |

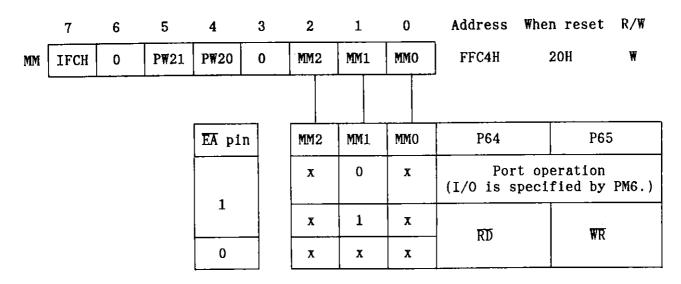

| 3.3.2 Memory mapping register (MM)             | 3-29 |

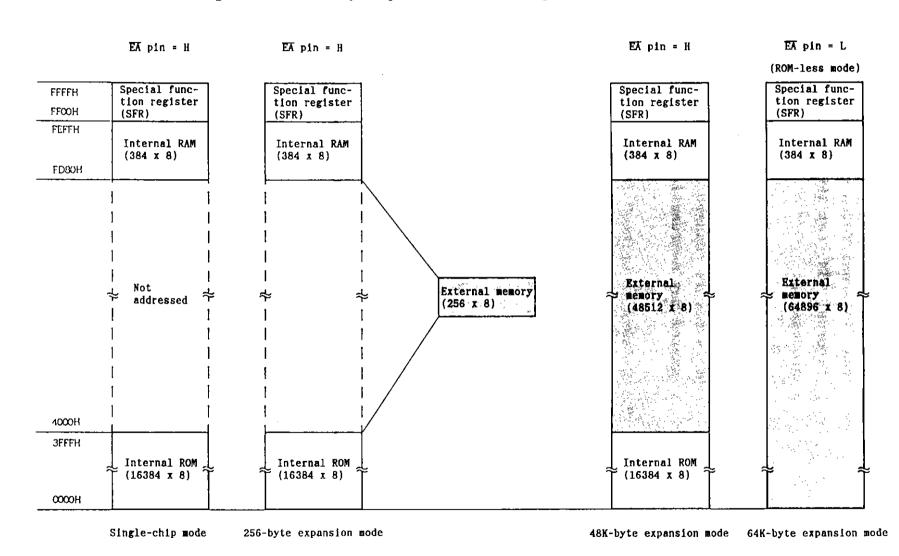

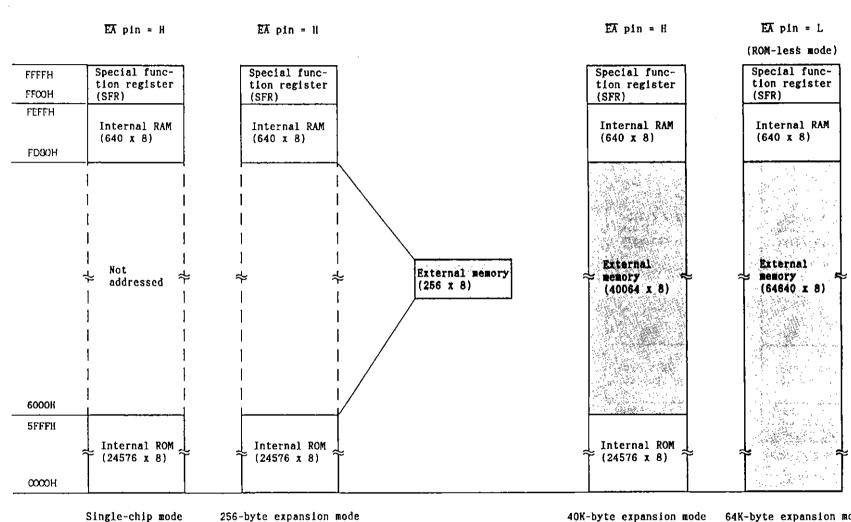

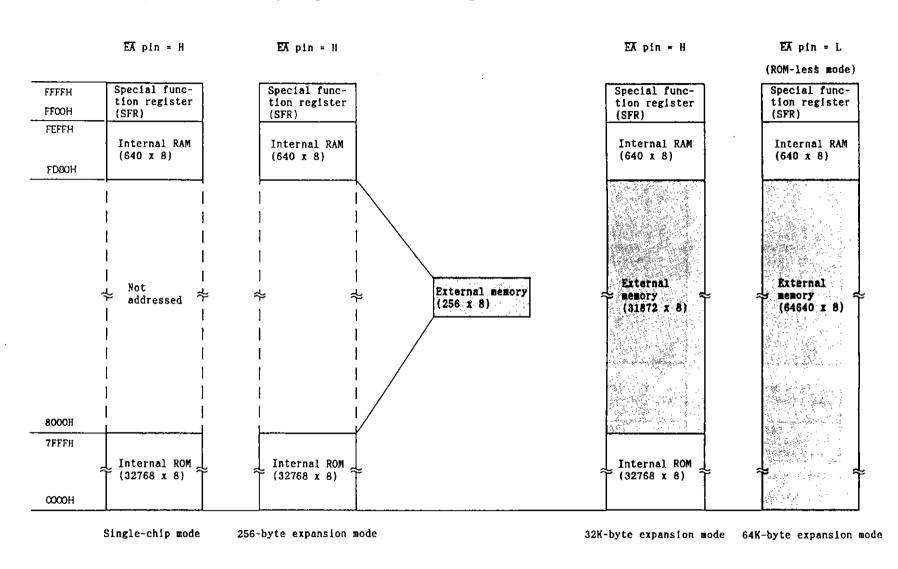

| 3.3.3 Memory map in external expansion         | 3-31 |

| CHAPTER 4 CLOCK GENERATOR                      | 4-1  |

| 4.1 Configuration and Functions                | 4-1  |

| 4.2 Cautions                                   | 4-3  |

| 4.2.1 When an external clock is applied        | 4-3  |

| 4.2.2 When crystal/ceramic oscillation is used | 4-4  |

| CHAPTER 5 PORT FUNCTIONS                       | 5-1  |

| 5.1 Functions and Outline of the Ports         | 5-1  |

| 5.2 Port 0 (P00-P07)                           | 5-4  |

| 5.2.1 Hardware configuration                   | 5-4  |

| 5.2.2 Setting the I/O mode and/or control mode | 5-5  |

| 5.2.3 Internal pull-up resistors               | 5-6  |

| 5.3 Port 1 (P10-P17)                           | 5-7  |

| 5.3.1 Hardware configuration                   | 5-8  |

| 5.3.2 Setting the I/O mode and/or control mode | 5-9  |

| 5.3.3 Internal pull-up resistor                | 5-10 |

| 5.4 Port 2 (P20-P27)                           | 5-12 |

| 5.4.1 Hardware configuration                   | 5-13 |

| 5.4.2 Setting the I/O mode and/or control mode | 5-13 |

| 5.4.3 Internal pull-up resistors               | 5-14 |

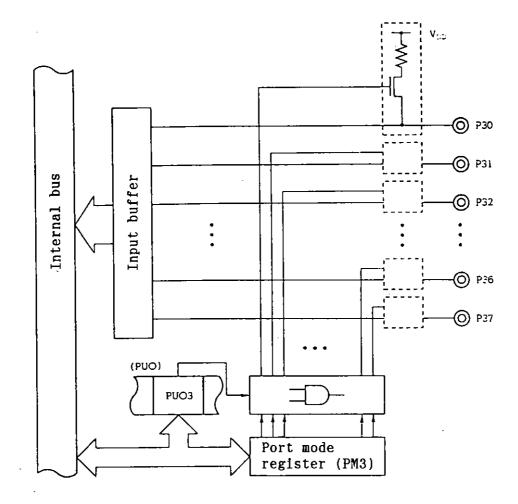

| 5.5 Port 3 (P30-P37)                           | 5-16 |

| 5.5.1 Hardware configuration                   | 5-17 |

| 5.5.2 Setting the I/O mode and/or control mode | 5-21 |

| 5.5.3 Internal pull-up resistors               | 5-23 |

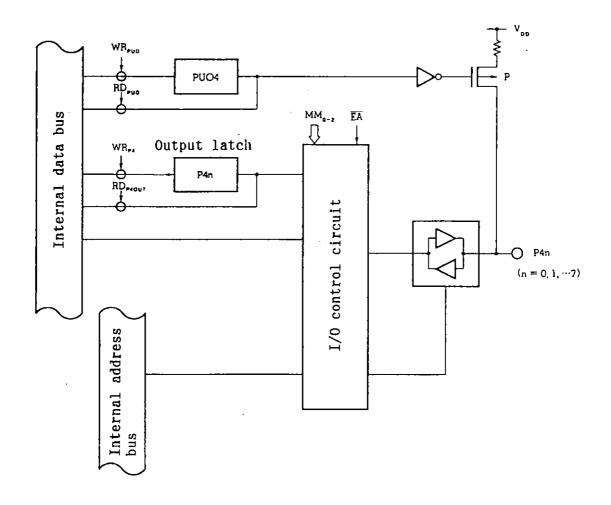

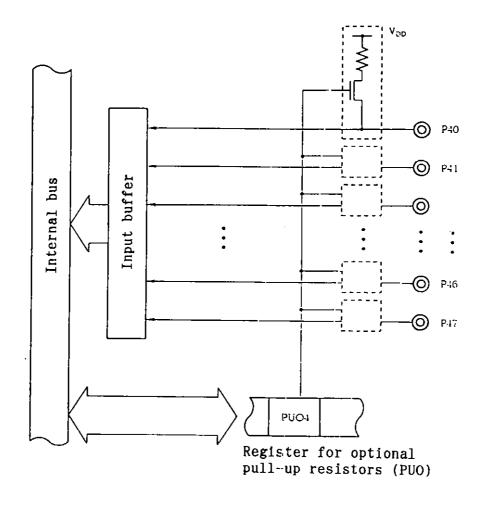

| 5.6 Port 4 (P40-P47)                           | 5-26 |

| 5.6.1 Hardware configuration                   | 5-27 |

| 5.6.2 Setting the I/O mode and/or control mode | 5-27 |

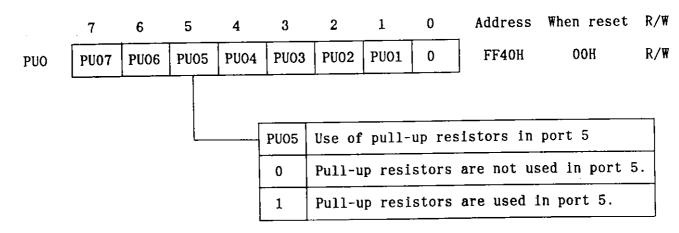

| 5.6.3 Internal pull-up resistors               | 5-29 |

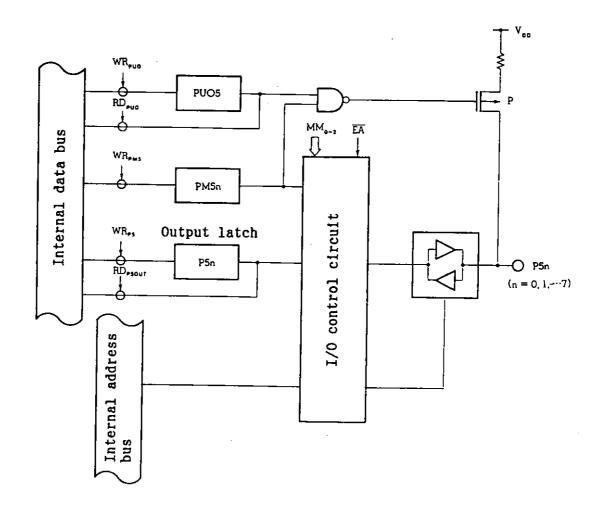

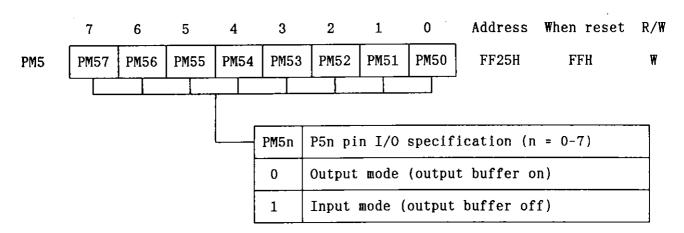

| 5.7 Port 5 (P50-P57)                           | 5-31 |

| 5 7 1 Hardware configuration                   | 5-32 |

| Phase-out/Discontinued | hase-out/Discontinued |

|------------------------|-----------------------|

|------------------------|-----------------------|

| 5.7.2 Setting the I/O mode and/or control mode | 5-32 |

|------------------------------------------------|------|

| 5.7.3 Internal pull-up resistors               | 5-34 |

| 5.8 Port 6 (P60-P67)                           | 5-36 |

| 5.8.1 Hardware configuration                   | 5-37 |

| 5.8.2 Setting the I/O mode and/or control mode | 5-38 |

| 5.8.3 Internal pull-up resistors               | 5-40 |

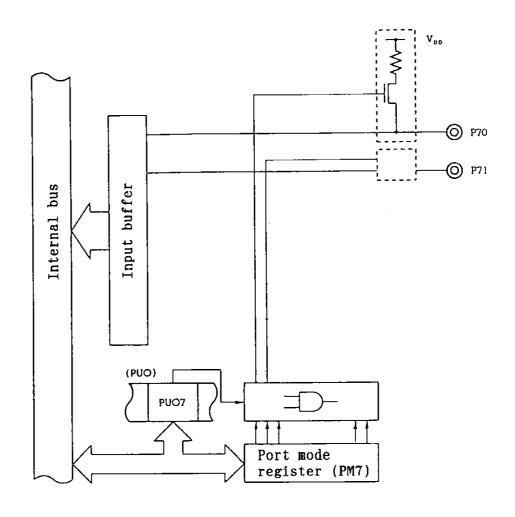

| 5.9 Port 7 (P70, P71)                          | 5-42 |

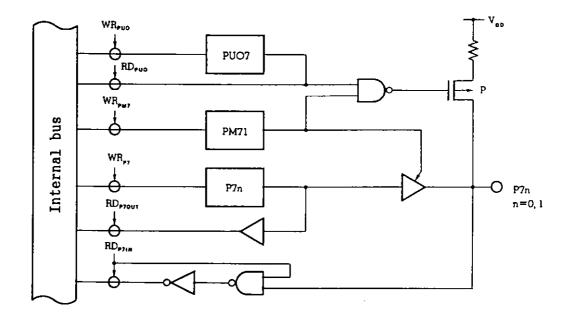

| 5.9.1 Hardware configuration                   | 5-42 |

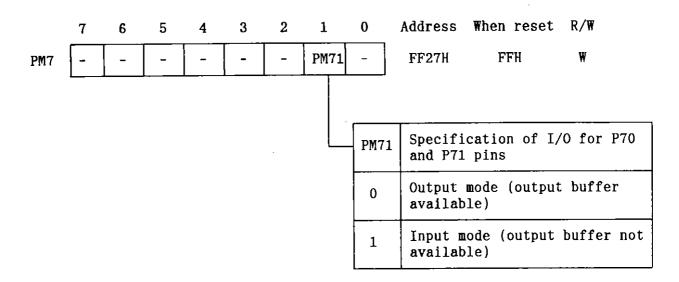

| 5.9.2 Setting the I/O mode and/or control mode | 5-43 |

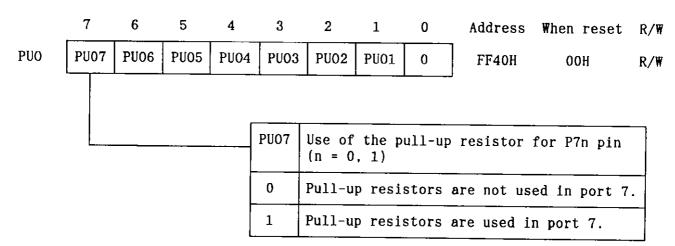

| 5.9.3 Internal pull-up resistors               | 5-44 |

| CHAPTER 6 REAL-TIME OUTPUT PORT (RTP)          | 6-1  |

| 6.1 Configuration and Functions of RTP         | 6-1  |

| 6.2 Hardware Configuration                     | 6-2  |

| 6.3 Structure of the Buffer Register           | 6-2  |

| 6.4 RTP Control Register                       | 6-4  |

| 6.5 RTP Operation                              | 6-6  |

| CHAPTER 7 SERIAL INTERFACE                     | 7-1  |

| 7.1 Functions                                  | 7-1  |

| 7.2 Configuration                              | 7-1  |

| 7.3 Control Registers                          | 7-5  |

| 7.3.1 Serial interface mode register (CSIM)    | 7-5  |

| 7.3.2 Serial bus interface control register    |      |

| (SBIC)                                         | 7-6  |

| 7.4 Three-wire Serial I/O Mode                 | 7-9  |

| 7.4.1 Basic operation timing                   | 7-9  |

| 7.4.2 When only send operation is enabled      | 7-11 |

| 7.4.3 When only receive operation is enabled   | 7-13 |

| 7.4.4 When send and receive operations         |      |

| are enabled                                    | 7-14 |

| 7.4.5 Action taken when shift operation is not |      |

| in phase with the serial clock                 | 7-16 |

| 7.5 SBI Mode                                   | 7-17 |

| 7.5.1 SBI features                             | 7-17 |

| 7.5.2 Serial interface configuration           | 7-19 |

| <b>Phase-out/Discontinued</b> |

|-------------------------------|

|-------------------------------|

| 7.5.3     | Address match detection method         | 7-22 |

|-----------|----------------------------------------|------|

| 7.5.4     | SBI mode control registers             | 7-22 |

| 7.5.5     | Shift register (SIO)                   | 7-27 |

| 7.6 Com   | nunication Operation and Signals       | 7-28 |

| 7.6.1     | Bus release signal (REL)               | 7-29 |

| 7.6.2     | Command signal (CMD)                   | 7-29 |

| 7.6.3     | Address                                | 7-30 |

| 7.6.4     | Command data                           | 7-31 |

| 7.6.5     | Acknowledge signal (ACK)               | 7-32 |

| 7.6.6     | Busy signal (BUSY) and ready signal    |      |

|           | (READY)                                | 7-33 |

| 7.6.7     | Signals                                | 7-33 |

| 7.6.8     | Communitation operation                | 7-43 |

| 7.6.9     | Clearing the busy signal               | 7-48 |

| 7.6.10    | Wake-up setting operation              | 7-48 |

| 7.6.11    | Starting send/receive operation        | 7-49 |

| 7.7 Cau   | tions                                  | 7-49 |

|           |                                        |      |

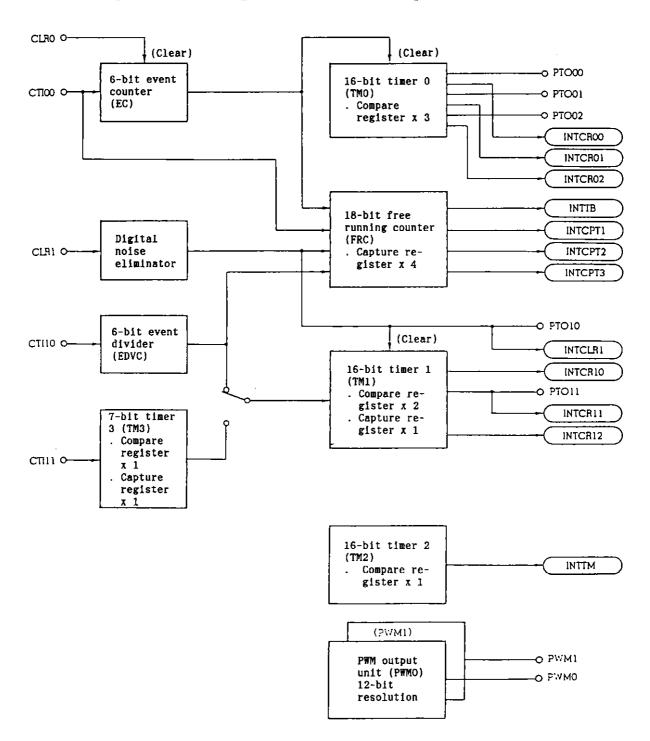

| CHAPTER 8 | SUPER TIMER UNIT                       | 8-1  |

| 8.1 Ove   | rview of the Super Timer Unit          | 8-2  |

| 8.1.1     | Configuration of the super timer unit  | 8-2  |

| 8.1.2     | Functional overview of the timer units | 8-6  |

| 8.2 Time  | er O Unit                              | 8-9  |

| 8.2.1     | Configuration of the timer 0 unit      | 8-9  |

| 8.2.2     | Event counter (EC)                     | 8-11 |

| 8.2.3     | Timer 0 (TMO)                          | 8-17 |

| 8.2.4     | Operating mode                         | 8-18 |

| 8.2.5     | Setting timer 0 unit control registers | 8-22 |

| 8.2.6     | Examples of using the timer 0 unit     | 8-29 |

| 8.3 Time  | er 1 Unit                              | 8-34 |

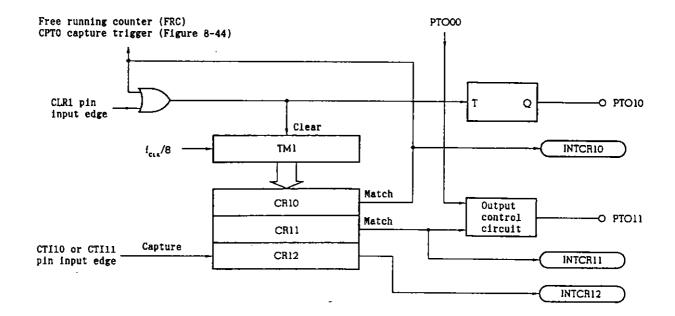

| 8.3.1     | Configuration of the timer 1 unit      | 8-34 |

| 8.3.2     | Event divider                          | 8-38 |

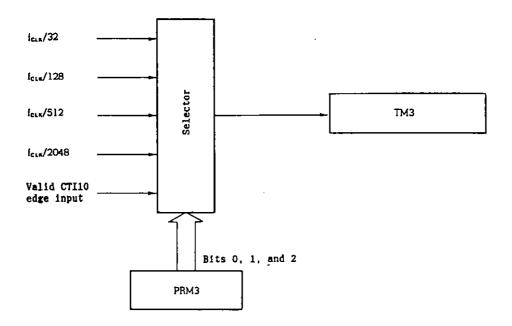

| 8.3.3     | Pulse width detection circuit (TM3)    | 8-38 |

| 8.3.4     | Configuration of timer 1 (TM1)         | 8-44 |

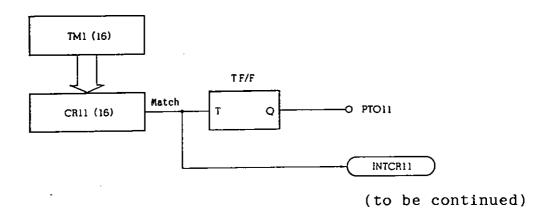

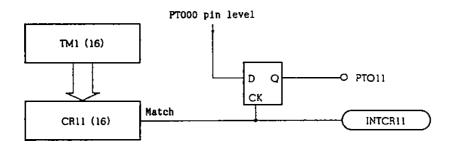

| 8.3.5     | Output modes of timer 1 output pins    | 8-45 |

| 8.3.6     | Operation of timer 1                   | 8-46 |

## Phase-out/Discontinued

| 8.3.7 Digital noise eliminator                  | 8-50  |

|-------------------------------------------------|-------|

| 8.3.8 Setting timer 1 unit control registers    | 8-66  |

| 8.4 Free Running Counter (FRC) Unit             | 8-74  |

| 8.4.1 Configuration of the free running         |       |

| counter unit                                    | 8-74  |

| 8.4.2 Capture register 2 (CPT2)                 | 8-76  |

| 8.4.3 Operation of the FRC                      | 8-79  |

| 8.4.4 Setting FRC unit control registers        | 8-80  |

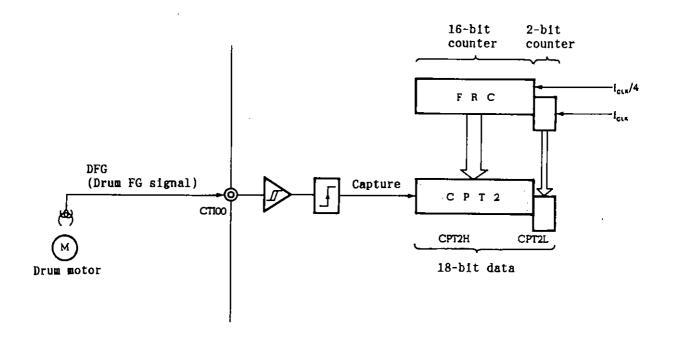

| 8.4.5 Application of the FRC to a VCR           | 8-82  |

| 8.5 Timer 2 Unit                                | 8-92  |

| 8.5.1 Configuration of the timer 2 unit         | 8-93  |

| 8.5.2 Setting the register to control the timer |       |

| 2 unit                                          | 8-94  |

| 8.6 PWM Output Unit                             | 8-95  |

| 8.6.1 Configuration of the PWM output unit      | 8-95  |

| 8.6.2 Operation of the PWM output unit          | 8-96  |

| 8.6.3 Setting the register to control PWM       |       |

| output unit                                     | 8-102 |

| 8.6.4 Registers other than the control register | 8-104 |

| 8.6.5 Application of the PWM output units       | 8-104 |

| CHAPTER 9 A/D CONVERTER                         | 9-1   |

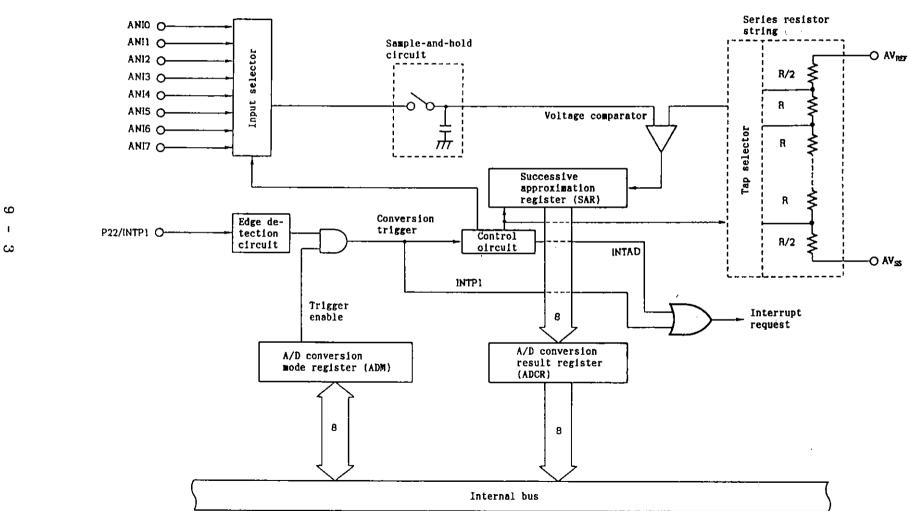

| 9.1 Functions of A/D Converter                  | 9-1   |

| 9.2 Hardware Configuration of A/D Converter     | 9-2   |

| 9.3 Control Register for the A/D Converter      | 9-6   |

| 9.4 A/D Converter Operation                     | 9-9   |

| 9.4.1 Basic operation of A/D converter          | 9-9   |

| 9.4.2 A/D converter operation mode              | 9-12  |

| 9.5 A/D Converter Interrupt Request             | 9-15  |

| CHAPTER 10 CLOCK OUTPUT (CLO)                   | 10-1  |

| 10.1 Configuration and Functions of CLO         | 10-1  |

| 10.2 CLO Control Register                       | 10-4  |

| Phase-out/Discontinued |

|------------------------|

| Phase-oug 2 is         |

| CHAPTER 11 INTERRUPT FUNCTION                   | 11-1  |

|-------------------------------------------------|-------|

| 11.1 Interrupt Request Sources                  | 11-2  |

| 11.1.1 Nonmaskable interrupt request            | 11-4  |

| 11.1.2 Maskable interrupt request               | 11-4  |

| 11.2 External Interrupt Request Functions       | 11-5  |

| 11.2.1 External interrupt control registers     | 11-5  |

| 11.3 Interrupt Processing Control Registers     | 11-9  |

| 11.4 Interrupt Processing                       | 11-15 |

| 11.4.1 Multiple interrupt processing            | 11-16 |

| 11.4.2 When interrupt requests and macro        |       |

| services are temporarily held                   | 11-18 |

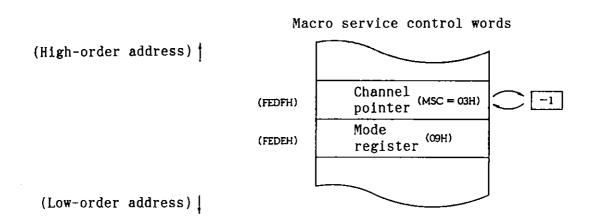

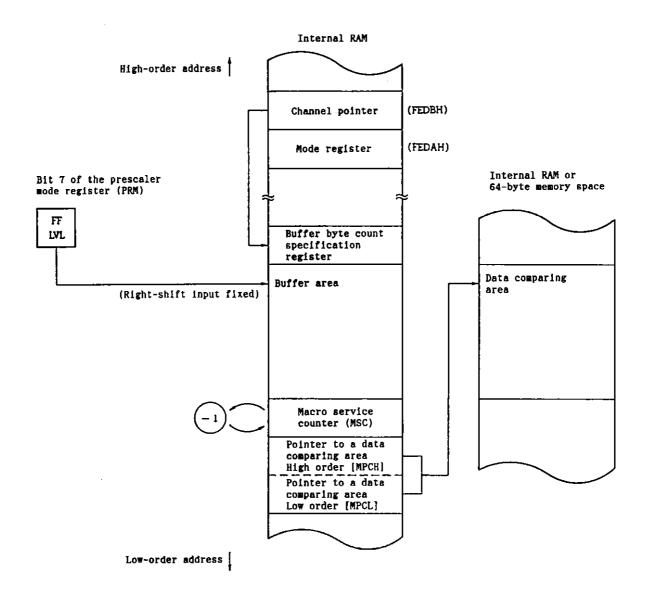

| 11.5 Macro Service Functions                    | 11-21 |

| 11.5.1 Overview of macro services               | 11-21 |

| 11.5.2 Macro service control register           | 11-22 |

| 11.5.3 Macro service modes and                  |       |

| interrupt requests                              | 11-27 |

| 11.5.4 Data transfer mode                       | 11-27 |

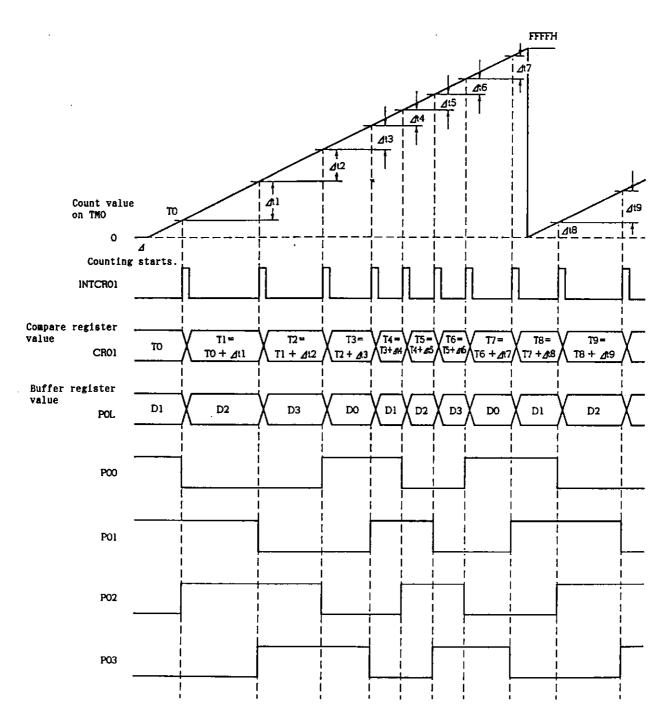

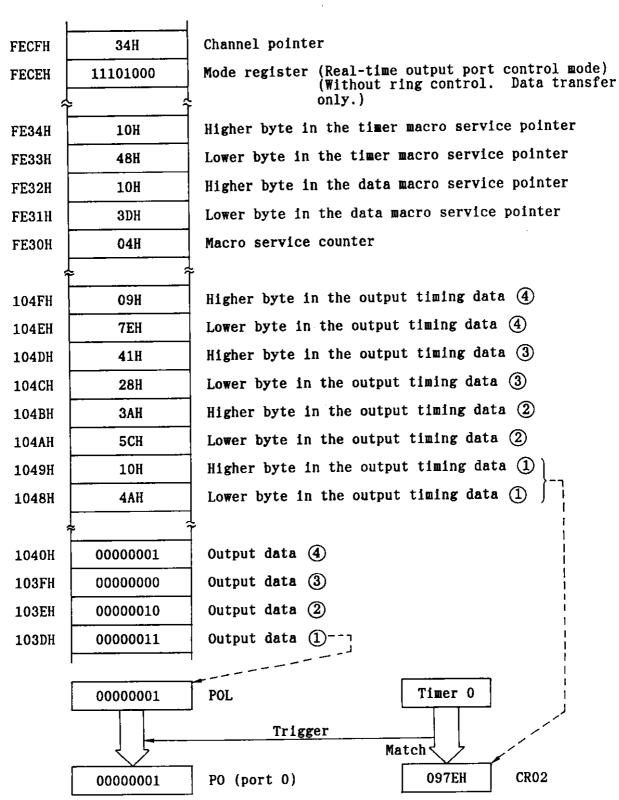

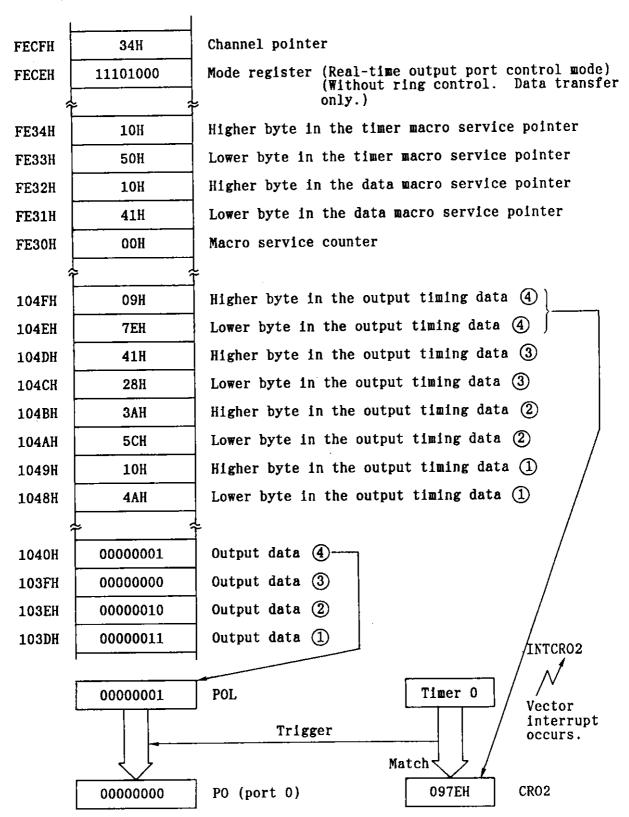

| 11.5.5 Real-time output port control mode       | 11-34 |

| 11.5.6 Counter mode                             | 11-58 |

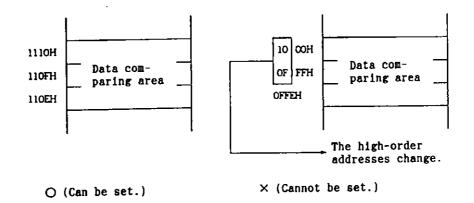

| 11.5.7 Data pattern identification mode         | 11-59 |

| 11.5.8 Points to be noted                       | 11-69 |

| CHAPTER 12 STANDBY FUNCTION                     | 12-1  |

| 12.1 Configuration of Standby Function          |       |

| Control Circuit                                 | 12-2  |

| 12.2 Setting the STOP Mode and Operation States |       |

| in the STOP Mode                                | 12-4  |

| 12.3 Releasing the STOP Mode                    | 12-5  |

| 12.3.1 Releasing the STOP mode by NMI input     | 12-5  |

| 12.3.2 Releasing the STOP mode by RESET input   | 12-6  |

| CHAPTER 13 RESET FUNCTION                       | 13-1  |

| CHAPTER 14 EXAMPLE OF APPLICATION               | 14-1  |

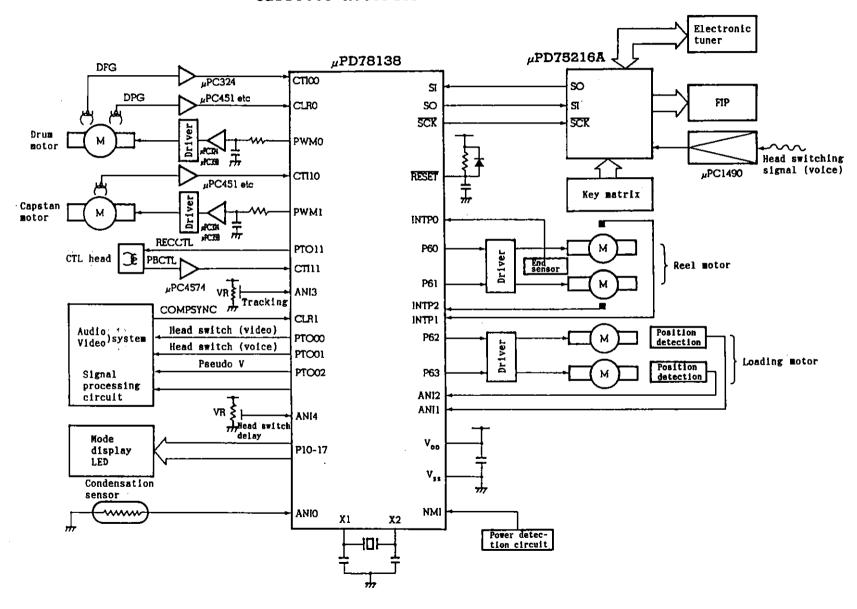

| 14.1 Example of Application to the Normal-type  |       |

| Video Cassette Recorder                         | 14-1  |

| Phase-out/Discontinued |

|------------------------|

|------------------------|

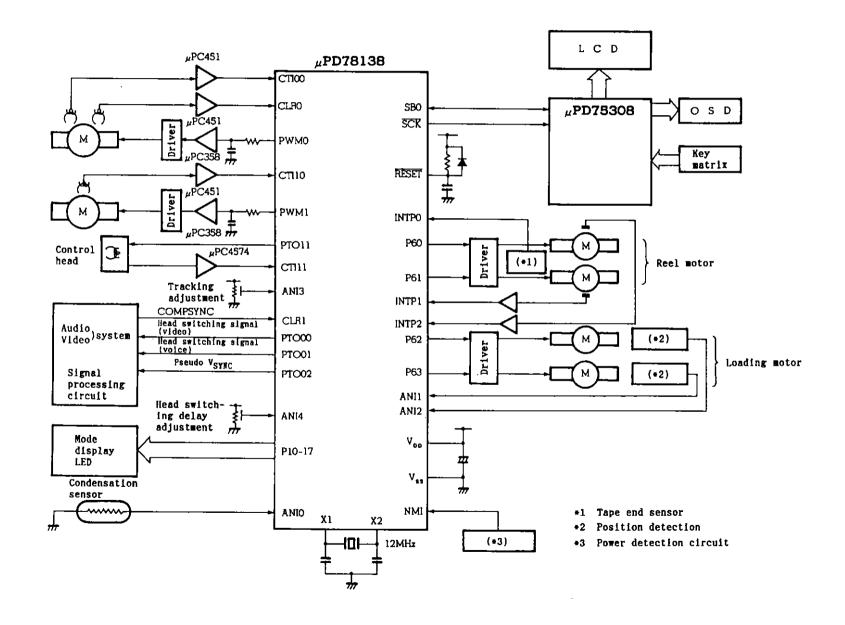

| 14.2 Example of Applicati  | on to the Camcoder 1     | L <b>4</b> -3 |

|----------------------------|--------------------------|---------------|

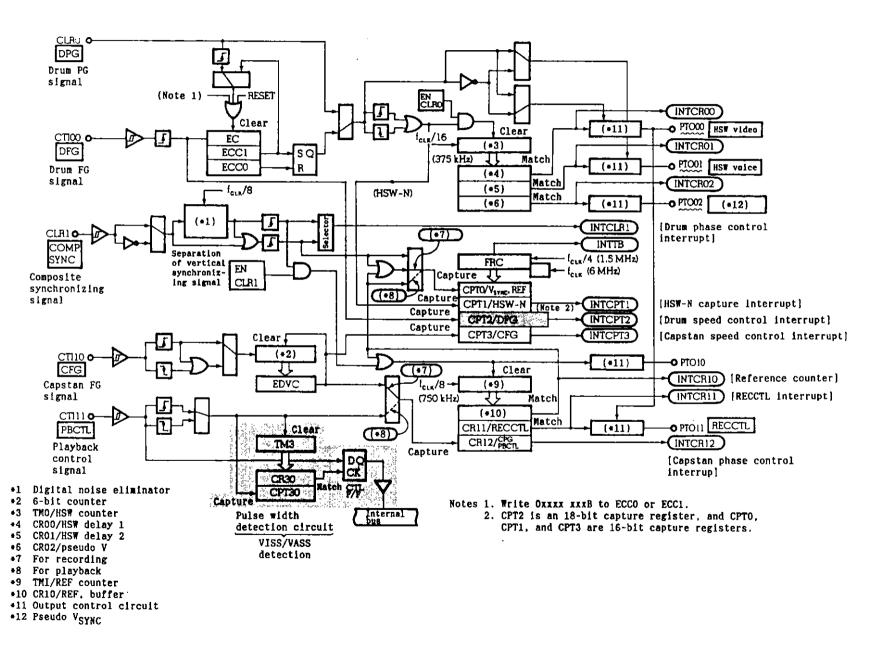

| 14.3 Using the Super Time  | er Unit in a VCR         |               |

| Servo System               |                          | L4-5          |

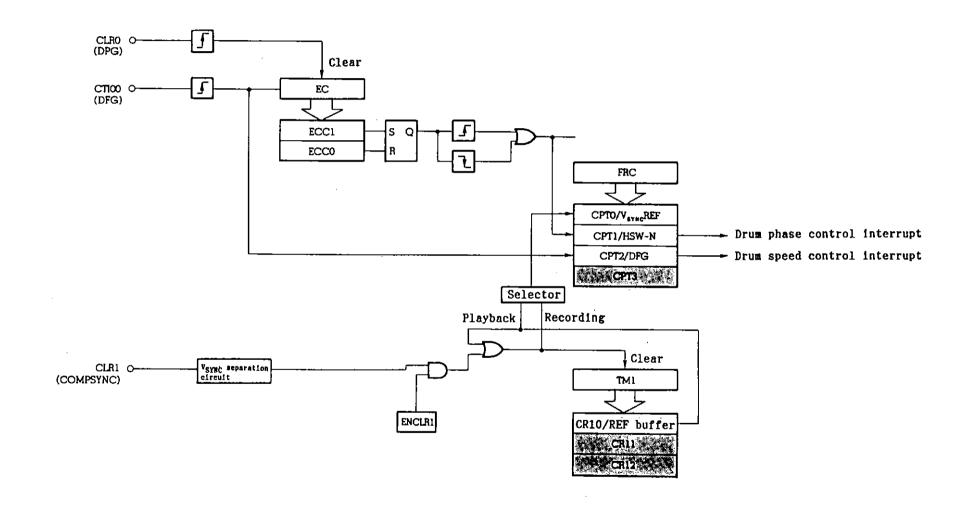

| 14.3.1 Controlling the     | drum motor               | L4-7          |

| 14.3.2 Controlling the     | capstan motor            | l <b>4-12</b> |

| 14.4 Block Diagram of the  | e Software Digital Servo |               |

| System in a VCR            |                          | 14-17         |

| CHAPTER 15 THE uPD78P138   | , <b></b>                | 15-1          |

| 15.1 Differences of uPD78  | 3P138 from uPD78134A,    |               |

| uPD78136, and uPD781       | 138                      | 15-2          |

| 15.1.1 Internal memory     |                          |               |

| (IMS)                      |                          | 15-3          |

| 15.2 Programming in the u  | ıPD78P138                | 15-5          |

|                            |                          | 15-5          |

|                            |                          | 15-6          |

| 15.2.3 Procedure for re    | eading from PROM         | 15-9          |

| 15.3 Erasure Characteris   | tics Only for            |               |

| the uPD78P138K             |                          | 15-10         |

| 15.4 Protective Film Cove  | ering the Erasure Window |               |

| Only for the uPD78P1       | 138К                     | 15-10         |

| CHAPTER 16 INSTRUCTION SET |                          | 16-1          |

|                            |                          | 16-1          |

|                            |                          | 16-1          |

| <del>-</del>               |                          | 16-5          |

|                            |                          | 16-21         |

|                            |                          | 16-21         |

|                            |                          | 16-24         |

| 16.3 Number of Clocks of   | the Instructions         | 16-35         |

| 16.3.1 Legend              |                          | 16-35         |

| 16.3.2 Numbers of clock    | ks of the instructions   | 16-37         |

| 16.4 Instruction Address   | ing                      | 16-49         |

| 16.4.1 Relative address    | sing                     | 16-49         |

| 16.4.2 Immediate addres    | ssing                    | <b>16-5</b> 0 |

| 16.4.3 Table indirect      | addressing               | 16-51         |

| Phase-out | <b>Discontinued</b> |

|-----------|---------------------|

|           |                     |

| 16.4.4     | Register addressing                     | 16-51  |

|------------|-----------------------------------------|--------|

| 16.5 Oper  | and Addressing                          | 16-52  |

| 16.5.1     | Register addressing                     | 16-52  |

| 16.5.2     | Immediate addressing                    | 16-53  |

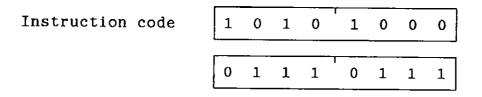

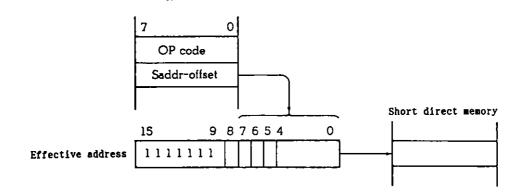

| 16.5.3     | Short direct addressing                 | 16-54  |

| 16.5.4     | Special function register               |        |

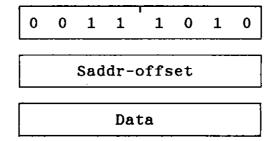

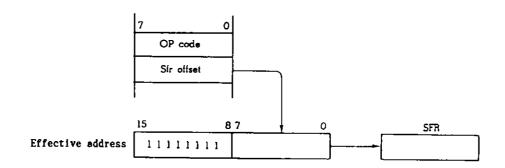

|            | (SFR) addressing                        | 16-56  |

| 16.5.5     | Register indirect addressing            | 16-57  |

| 16.5.6     | Indexed addressing                      | 16-59  |

| 16.6 Exp   | lanation of Instructions                | 16-61  |

| 16.6.1     | 8-bit data transfer instructions        | 16-61  |

| 16.6.2     | 16-bit data transfer instructions       | 16-73  |

| 16.6.3     | 8-bit arithmetic/logical instructions   | 16-76  |

| 16.6.4     | 16-bit arithmetic/logical instructions  | 16-117 |

| 16.6.5     | Multiply/divide instructions            | 16-123 |

| 16.6.6     | Increment/decrement instructions        | 16-125 |

| 16.6.7     | Shift/rotate instructions               | 16-127 |

| 16.6.8     | BCD correction instructions             | 16-135 |

| 16.6.9     | Bit manipulation instructions           | 16-136 |

| 16.6.10    | Call return instructions                | 16-158 |

| 16.6.11    | Stack manipulation instructions         | 16-162 |

| 16.6.12    | Unconditional branch instructions       | 16-164 |

| 16.6.13    | Conditional branch instructions         | 16-166 |

| 16.6.14    | CPU control instructions                | 16-187 |

|            |                                         |        |

| CHAPTER 17 | DIFFERENCES BETWEEN THE uPD78138 SERIES |        |

|            | AND uPD78134                            | 17-1   |

|            |                                         |        |

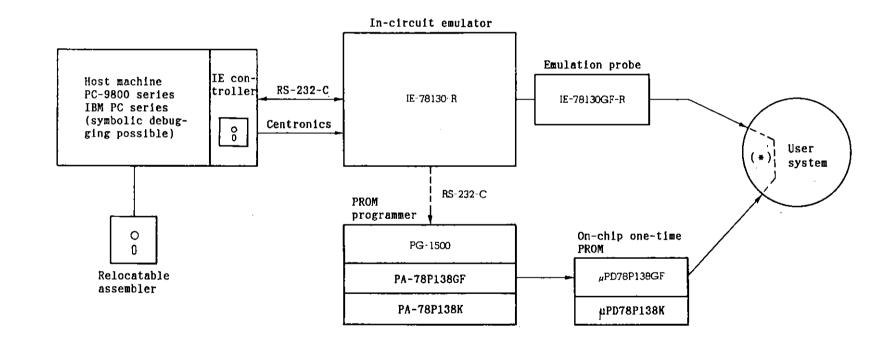

| APPENDIX A | DEVELOPMENT TOOLS                       | A-1    |

|            |                                         |        |

| APPENDIX B | INDEX OF INSTRUCTIONS                   | B-1    |

|            |                                         |        |

| APPENDIX C | INDEX OF REGISTERS                      | C-1    |

|            |                                         |        |

| APPENDIX D | INDEX OF REGISTER ABBREVIATIONS         | D-1    |

#### LIST OF FIGURES

| Figure | Title                                        | Page |

|--------|----------------------------------------------|------|

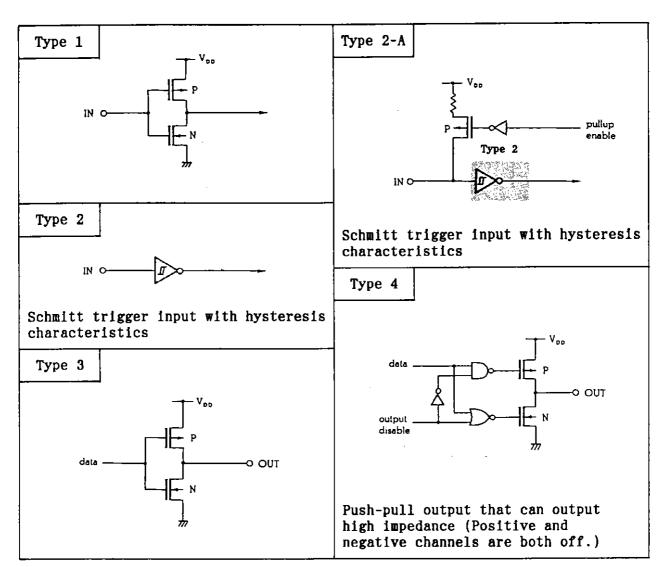

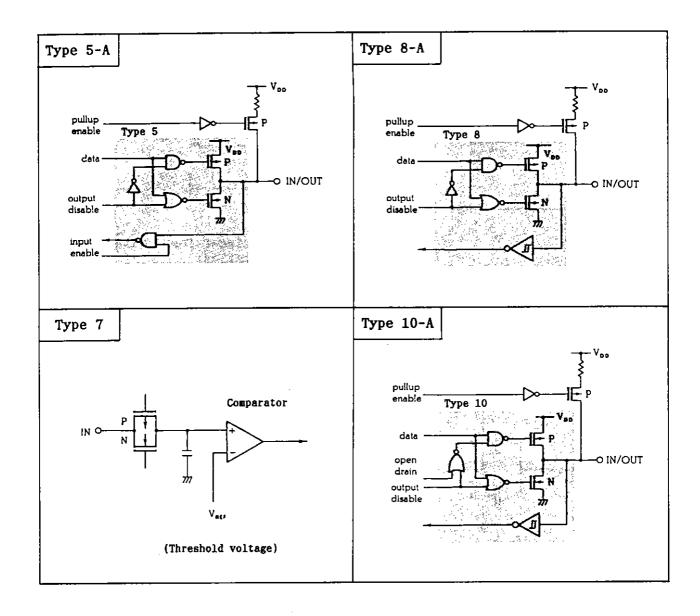

| 2-1    | Pin Input/Output Circuits                    | 2-23 |

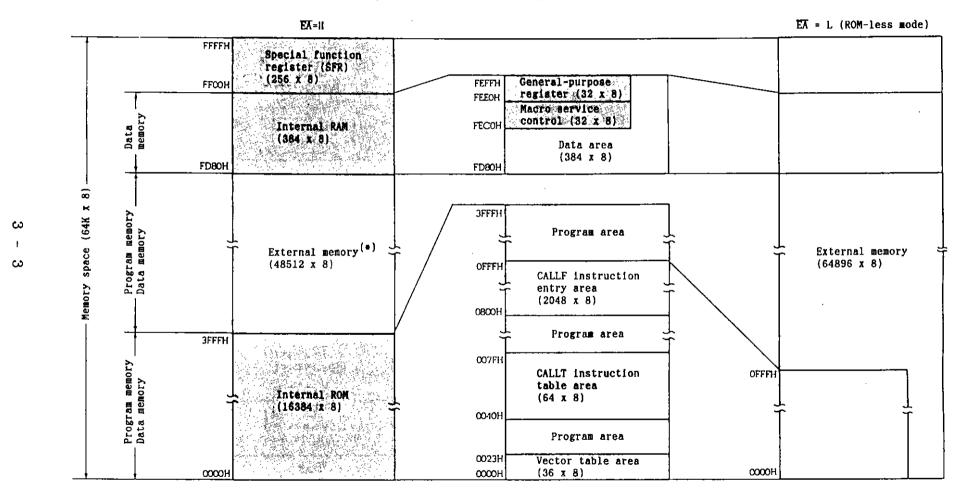

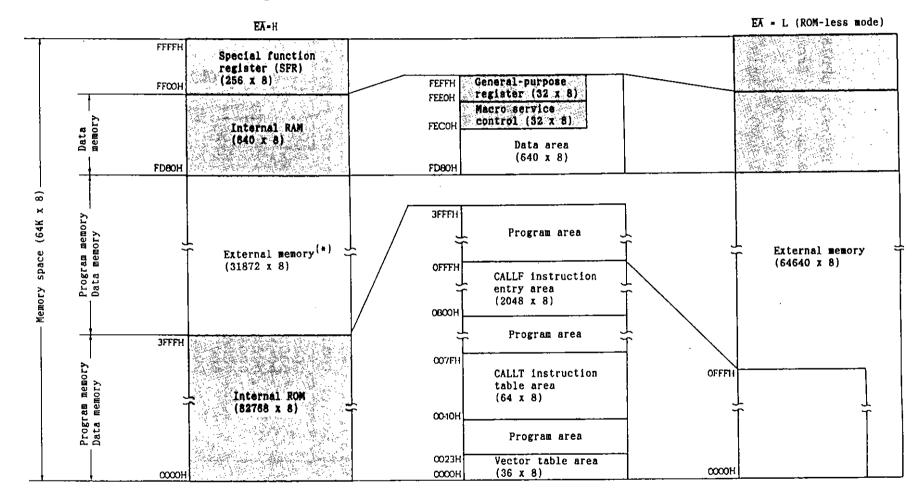

| 3-1    | Memory Map (uPD78134A)                       | 3-3  |

| 3-2    | Memory Map (uPD78136)                        | 3-4  |

| 3-3    | Memory Map (uPD78138 and uPD78P138)          | 3-5  |

| 3-4    | Memory Map and Addressing of Data Memory     | 3-8  |

| 3-5    | Format of Program Counter (PC)               | 3-12 |

| 3-6    | Program Status Word (PSW) Format             | 3-13 |

| 3-7    | Stack Pointer (SP) Format                    | 3-16 |

| 3-8    | Data Saved in Stack Memory                   | 3-16 |

| 3-9    | Data Restored from Stack Memory              | 3-16 |

| 3-10   | Format of General Registers                  | 3-18 |

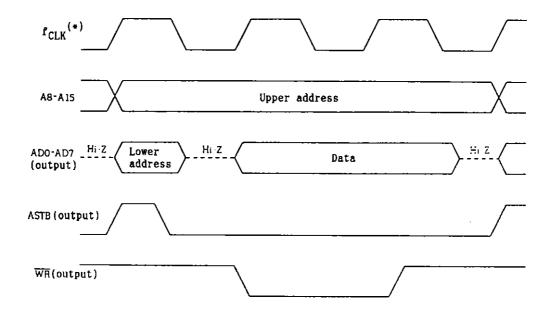

| 3-11   | Read Timing                                  | 3-28 |

| 3-12   | Write Timing                                 | 3-29 |

| 3-13   | Format of Memory Mapping Register (MM)       | 3-30 |

| 3-14   | Memory Map in External Expansion (uPD78134A) | 3-32 |

| 3-15   | Memory Map in External Expansion (uPD78136)  | 3-33 |

| 3-16   | Memory Map in External Expansion             |      |

|        | (uPD78138 and uPD78P138)                     | 3-34 |

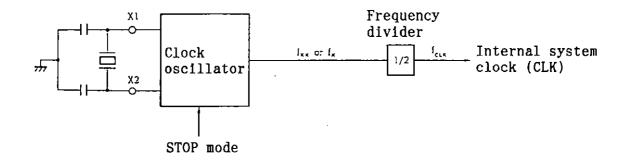

| 4-1    | Block Diagram of the Clock Generator         | 4-1  |

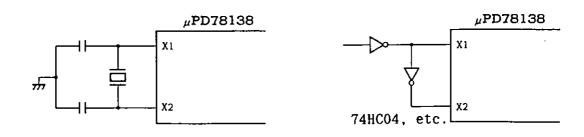

| 4-2    | External Circuitry of the Clock Oscillator   | 4-2  |

| 4-3    | Signal Extraction Point in External          |      |

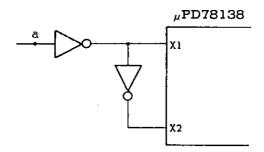

|        | Clock Input                                  | 4-3  |

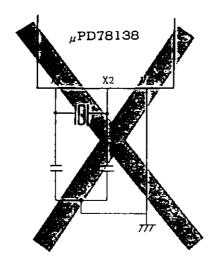

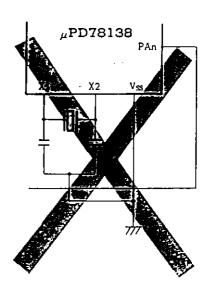

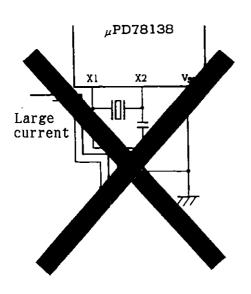

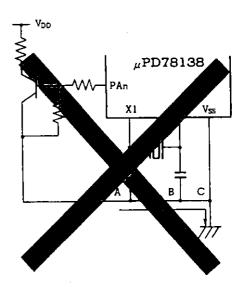

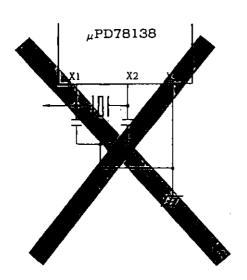

| 4-4    | Cautions for Resonator Connection Circuitry  | 4-5  |

| 4-5    | Examples of Wrong Resonator                  |      |

|        | Connection Circuitry                         | 4-5  |

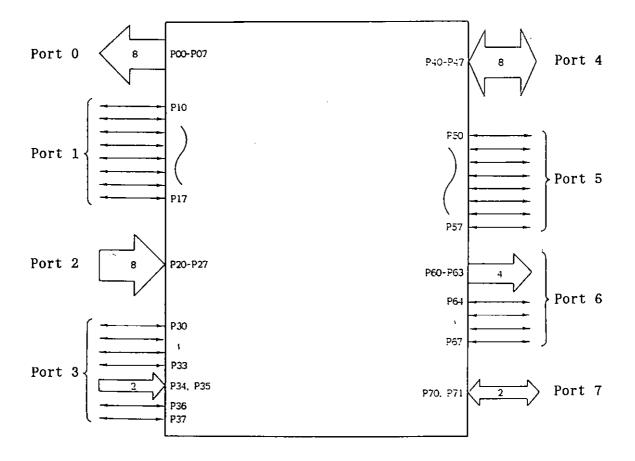

| 5-1    | Port Configuration                           | 5-1  |

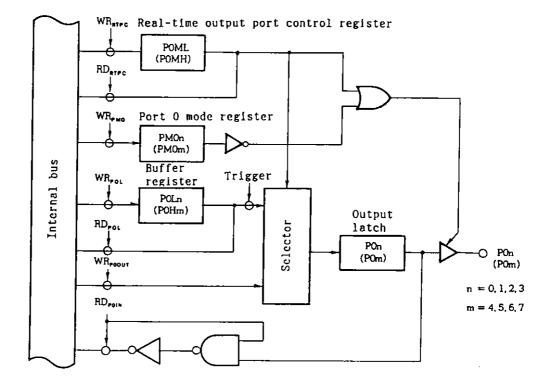

| 5-2    | Block Diagram of Port 0                      | 5-4  |

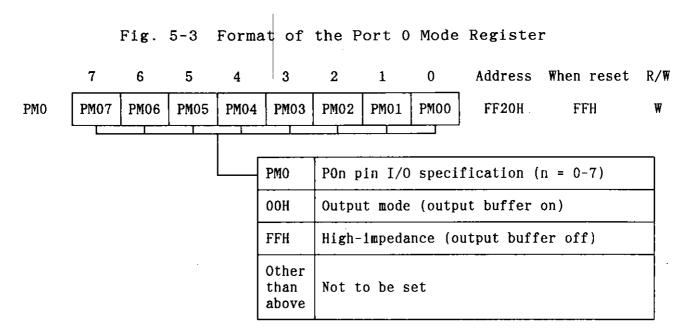

| 5-3    | Format of the Port 0 Mode Register           | 5-5  |

| <b>Phase-out/Discontinued</b> |

|-------------------------------|

|                               |

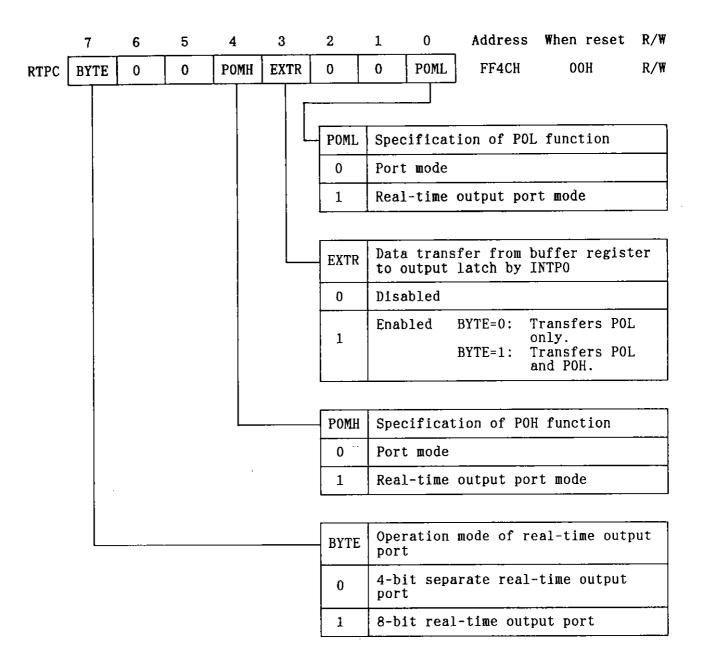

| 5-4  | Format of Real-time Output Port Control                          |      |

|------|------------------------------------------------------------------|------|

|      | Register (RTPC)                                                  | 5-6  |

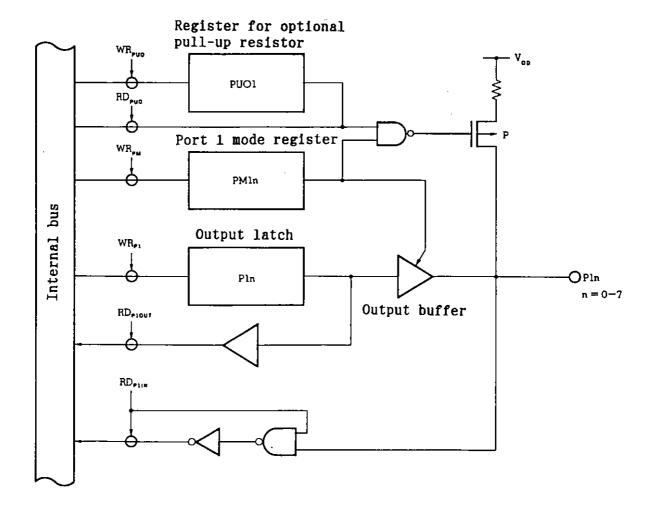

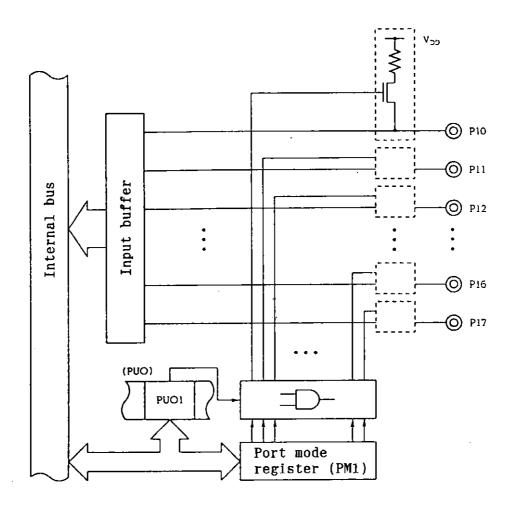

| 5-5  | Block Diagram of Port 1                                          | 5-8  |

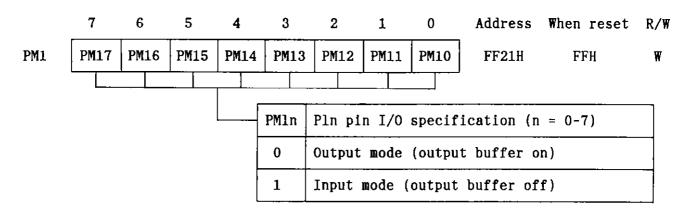

| 5-6  | Format of the Port 1 Mode Register                               | 5-9  |

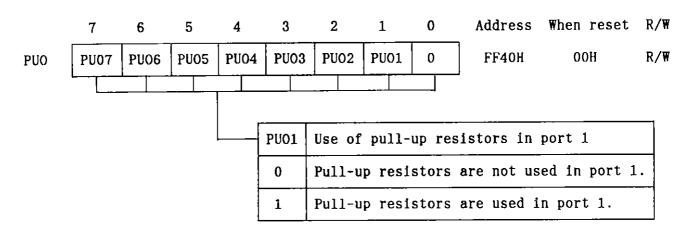

| 5-7  | Format of the Register for Optional                              |      |

|      | Pull-up Resistors                                                | 5-10 |

| 5-8  | Specification for Pulling Voltage in                             |      |

|      | Port 1 High                                                      | 5-11 |

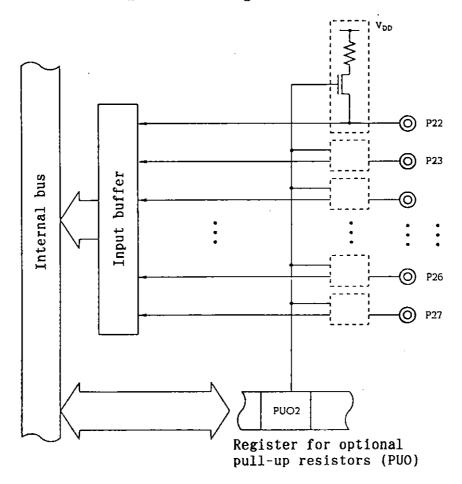

| 5-9  | Block Diagram of Port 2                                          | 5-13 |

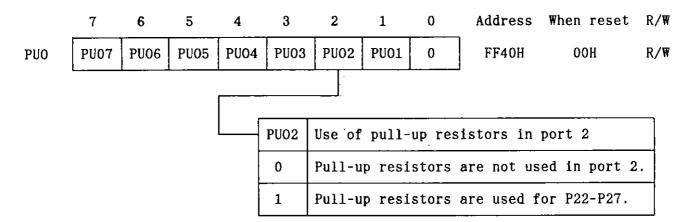

| 5-10 | Format of the Register for Optional                              |      |

|      | Pull-up Resistors                                                | 5-14 |

| 5-11 | Specification for Pulling Voltage in                             |      |

|      | Port 2 High                                                      | 5-15 |

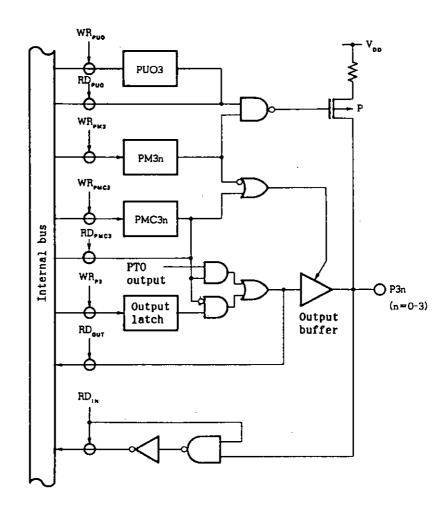

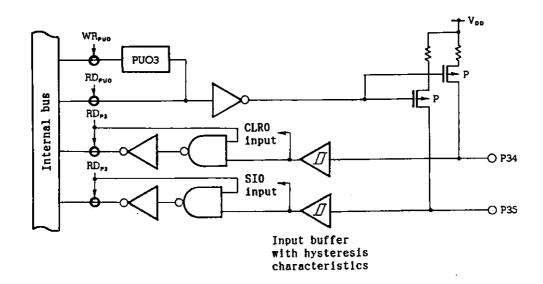

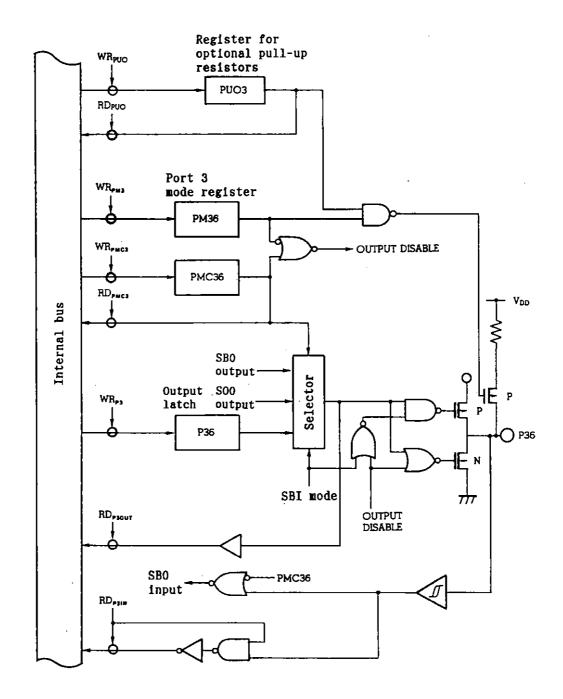

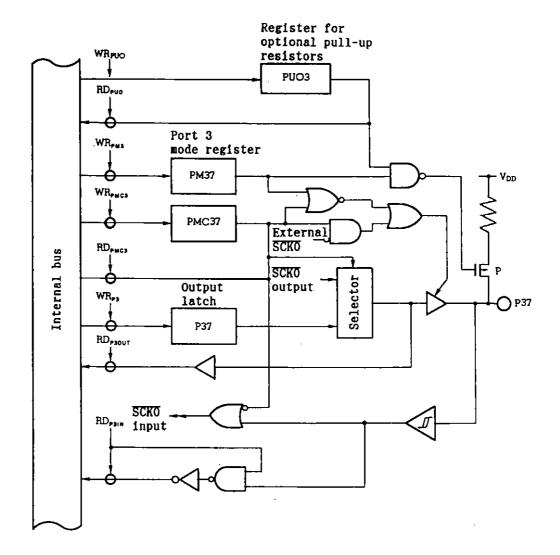

| 5-12 | Block Diagram of Port 3                                          | 5-17 |

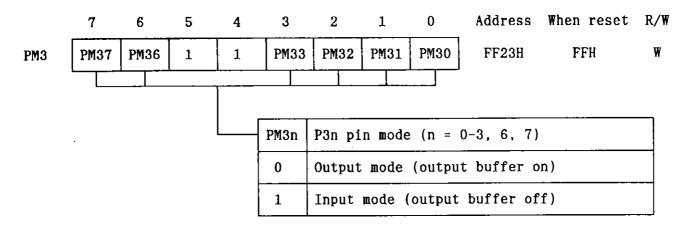

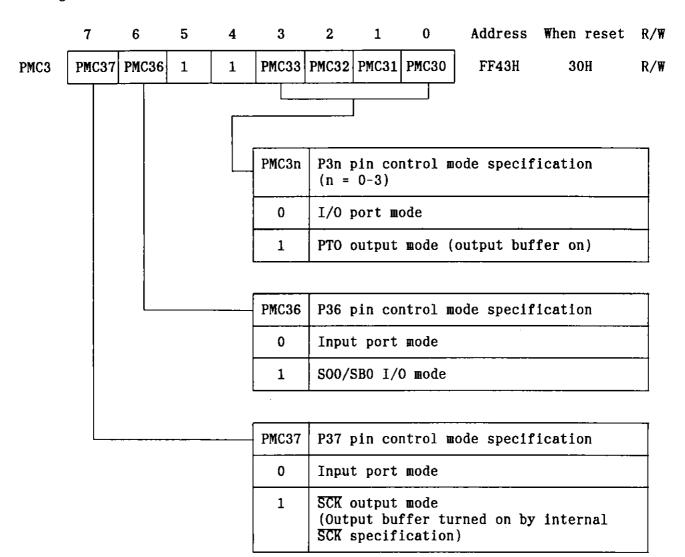

| 5-13 | Format of the Port 3 Mode Register                               | 5-21 |

| 5-14 | Format of the Port 3 Mode Control Register                       |      |

|      | (PMC3)                                                           | 5-22 |

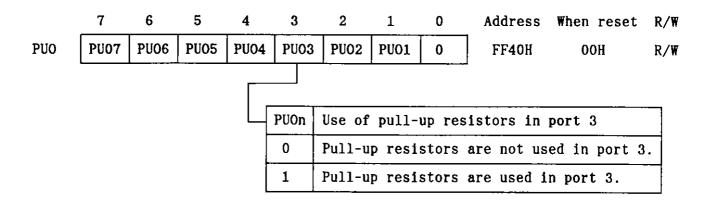

| 5-15 | Format of the Register for Optional                              |      |

|      | Pull-up Resistors                                                | 5-24 |

| 5-16 | Specification for Pulling Voltage in                             |      |

|      | Port 3 High                                                      | 5-25 |

| 5-17 | Block Diagram of Port 4                                          | 5-27 |

| 5-18 | Port 4 Operation Mode Set by $\overline{\text{EA}}$ and MM       | 5-28 |

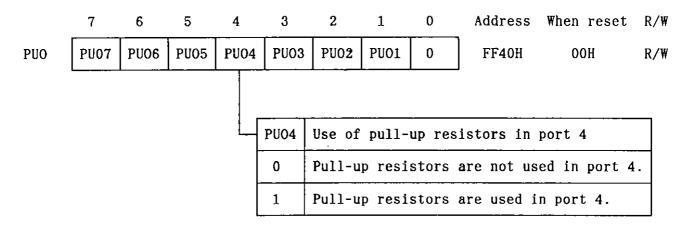

| 5-19 | Format of the Register for Optional                              |      |

|      | Pull-up Resistors                                                | 5-29 |

| 5-20 | Specification for Pulling Voltage in                             |      |

|      | Port 4 High                                                      | 5-30 |

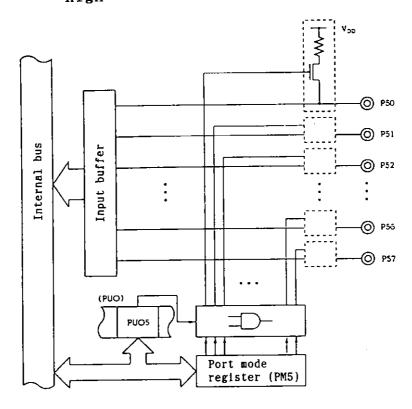

| 5-21 | Block Diagram of Port 5                                          | 5-32 |

| 5-22 | Port 5 Operation Mode Set by $\overline{\text{EA}}$ and MM       | 5-33 |

| 5-23 | Format of the Port 5 Mode Register (PM5)                         | 5-35 |

| 5-24 | Format of the Register for Optional                              |      |

|      | Pull-up Resistors                                                | 5-35 |

| 5-25 | Specification for Pulling Voltage in                             |      |

|      | Port 5 High                                                      | 5-35 |

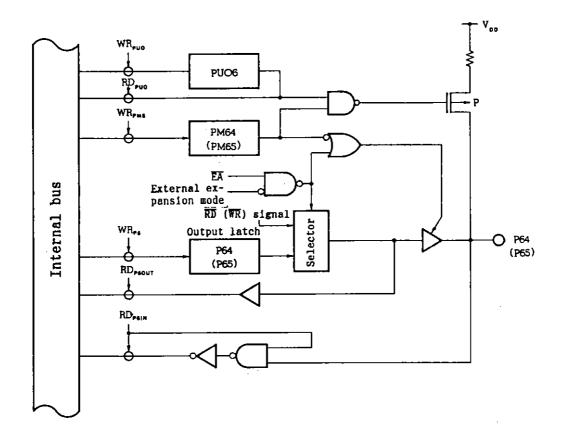

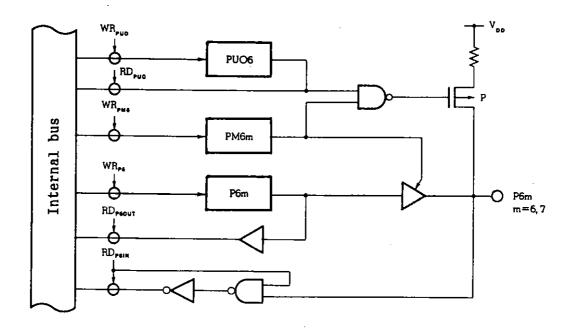

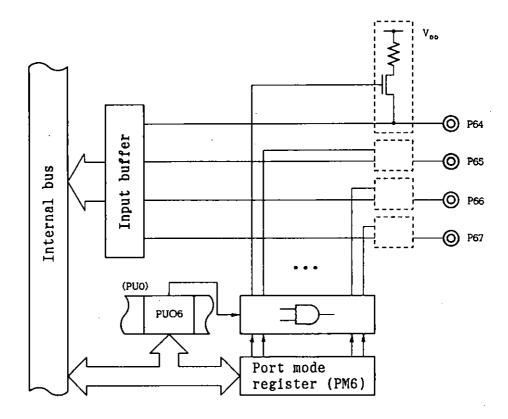

| 5-26 | Block Diagram of Port 6                                          | 5-37 |

| 5-27 | P64 and P65 Operation Modes Set by $\overline{\text{EA}}$ and MM | 5-39 |

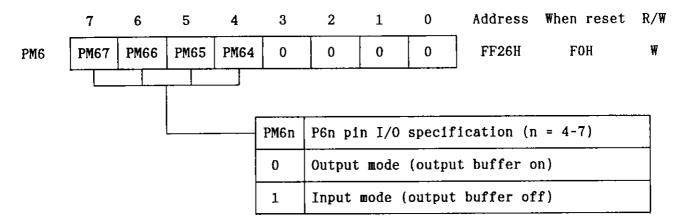

| 5-28 | Format of the Port 6 Mode Register        | 5-39 |

|------|-------------------------------------------|------|

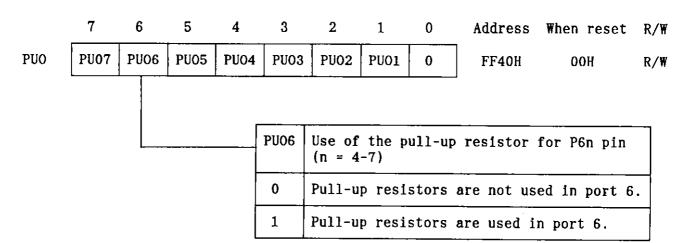

| 5-29 | Format of the Register for Optional       |      |

|      | Pull-up Resistors                         | 5-40 |

| 5-30 | Specification for Pulling Voltage in      |      |

|      | Port 6 High                               | 5-41 |

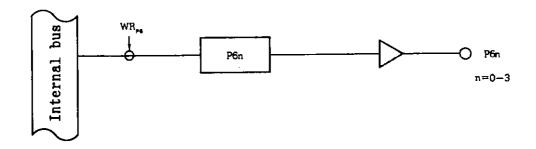

| 5-31 | Block Diagram of Port 7                   | 5-42 |

| 5-32 | Format of Port 7 Mode Register (PM7)      | 5-43 |

| 5-33 | Format of the Register for Optional       |      |

|      | Pull-up Resistors                         | 5-44 |

| 5-34 | Specification for Pulling Voltage in      |      |

|      | Port 7 High                               | 5-45 |

| 6-1  | Block Diagram of RTP                      | 6-2  |

| 6-2  | Structure of Buffer Registers POH and POL | 6-3  |

| 6-3  | Format of Real-time Output Port Control   |      |

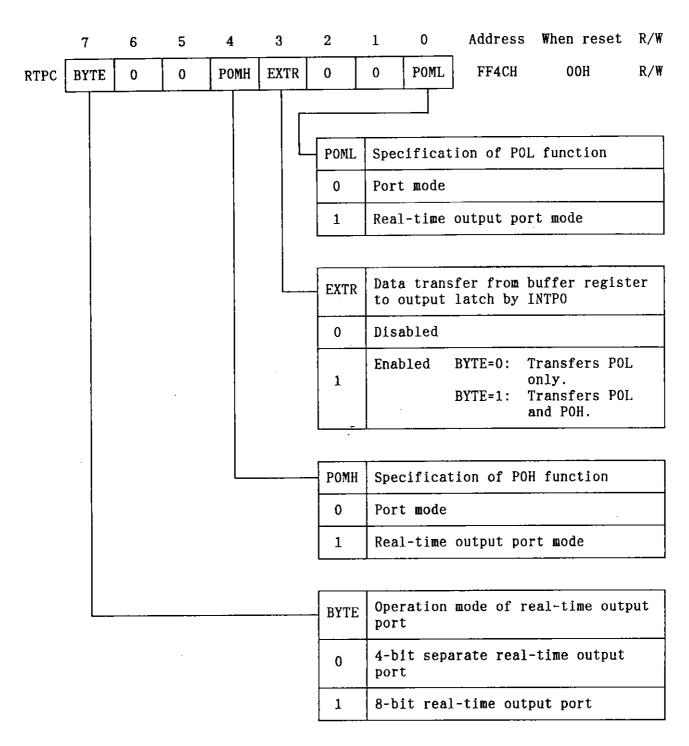

|      | Register (RTPC)                           | 6-5  |

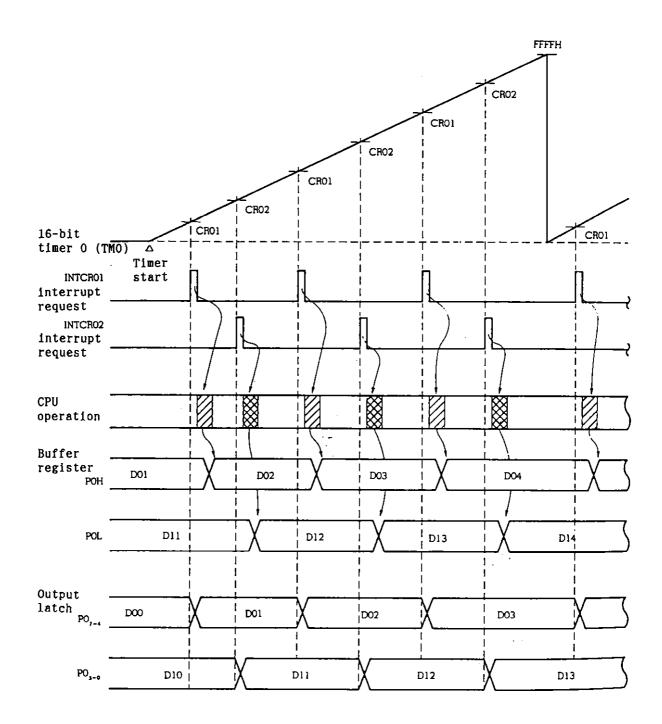

| 6-4  | Timing of RTP Operation                   | 6-8  |

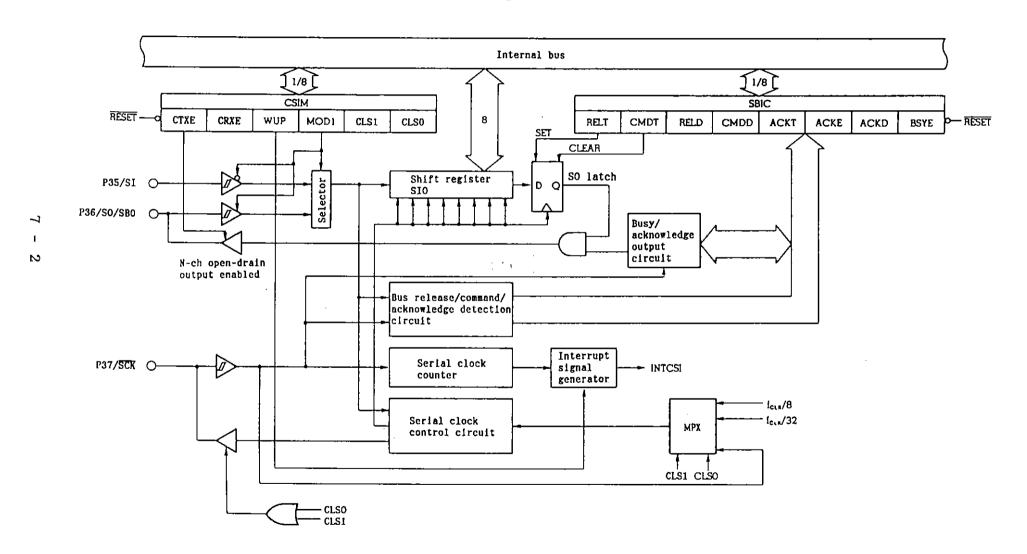

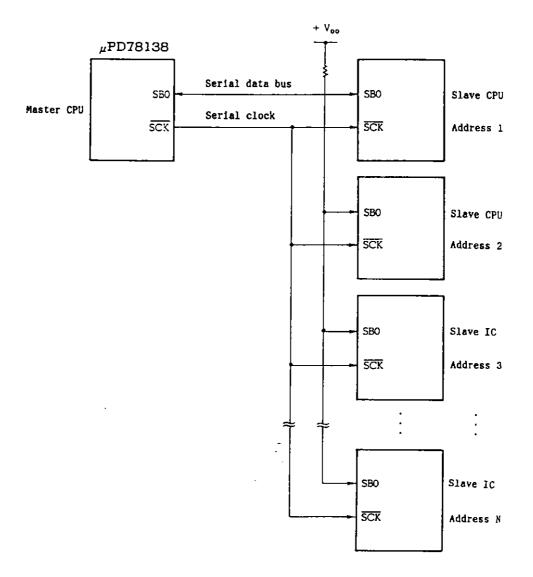

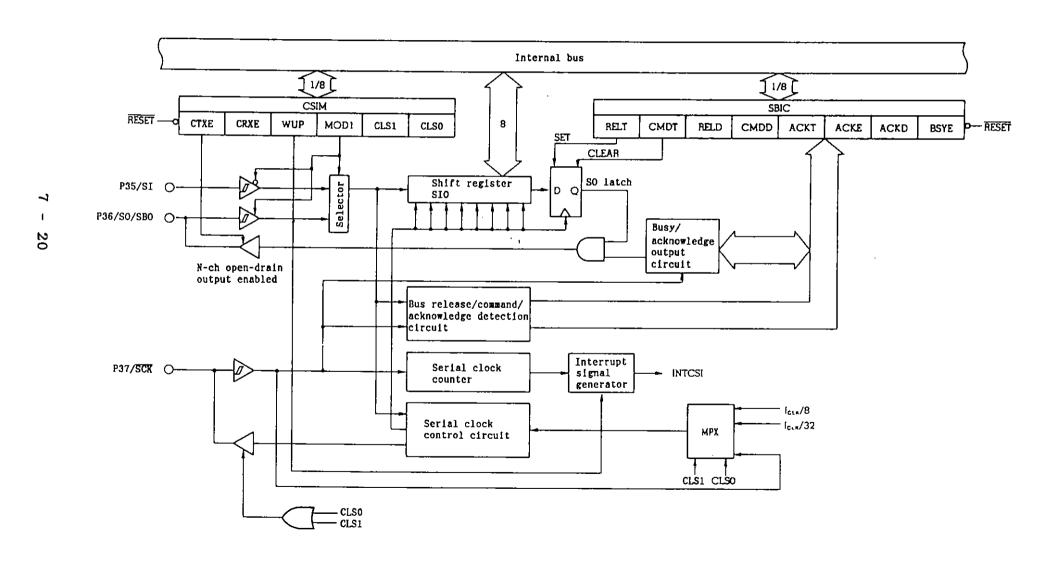

| 7-1  | Block Diagram of Serial Interface         | 7-2  |

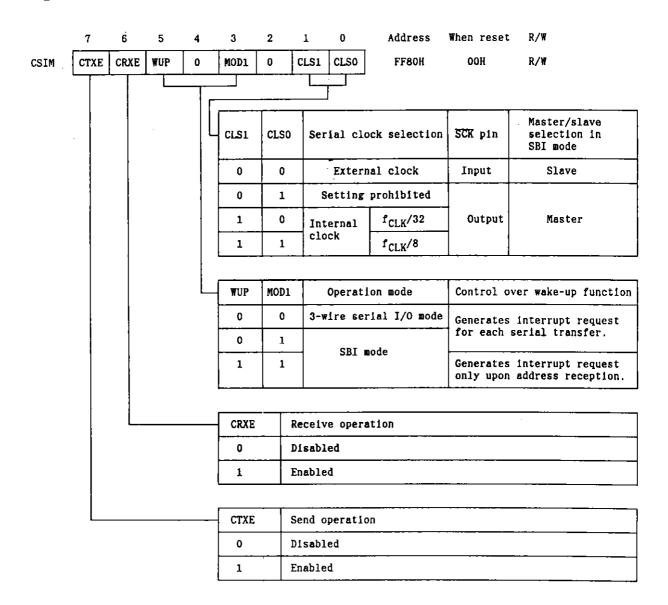

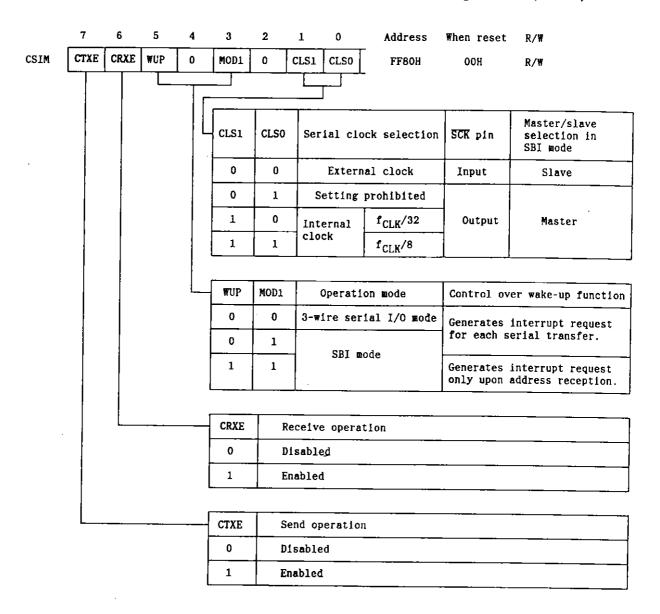

| 7-2  | Format of Serial Interface Mode Register  |      |

|      | (CSIM)                                    | 7-5  |

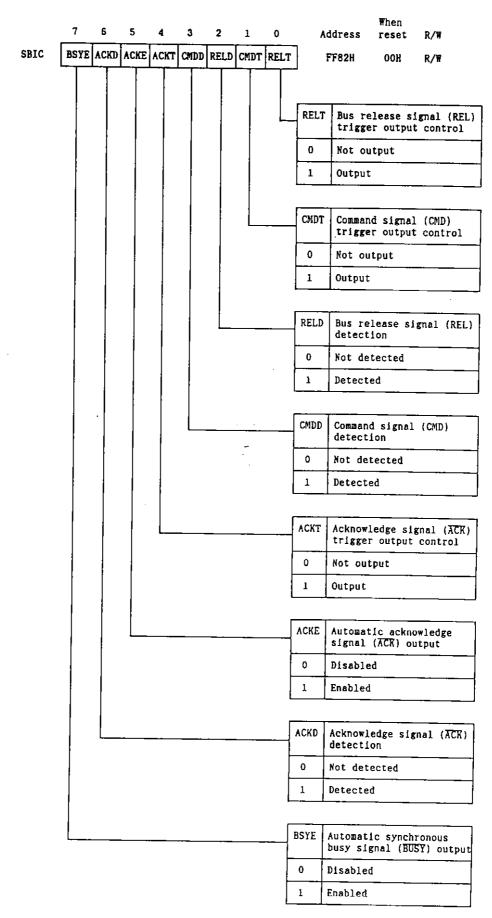

| 7-3  | Format of Serial Bus Interface Control    |      |

|      | Register (SBIC)                           | 7-8  |

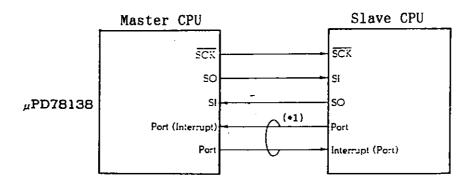

| 7-4  | Example of 3-Wire Serial I/O              |      |

|      | System Configuration                      | 7-9  |

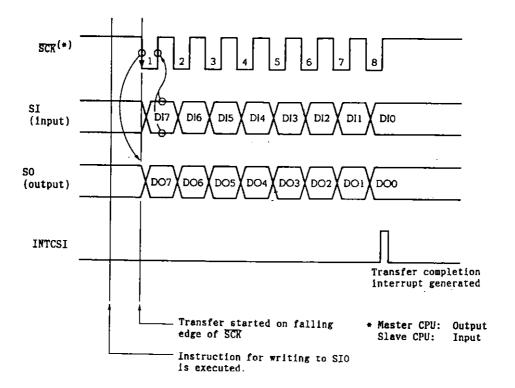

| 7-5  | Timing of 3-Wire Serial I/O Mode          | 7-10 |

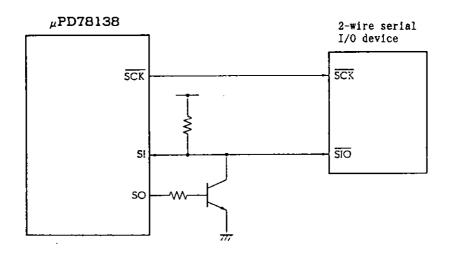

| 7-6  | Example of Connection with 2-Wire Serial  |      |

|      | I/O Device                                | 7-11 |

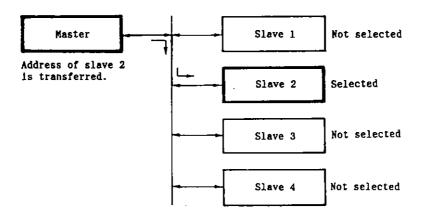

| 7-7  | Example of SBI-Based Serial               |      |

|      | Bus Configuration                         | 7-19 |

| 7-8  | Block Diagram of Serial Interface         | 7-20 |

| 7-9  | Pin Configuration                         | 7-21 |

| 7-10 | Format of Serial Interface Mode Register  |      |

|      | (CSIM)                                    | 7-23 |

| 7_11 | Format of SRIC Register                   | 7-24 |

| Phase-out/Discontinue |  |

|-----------------------|--|

| P1656-000 D-000       |  |

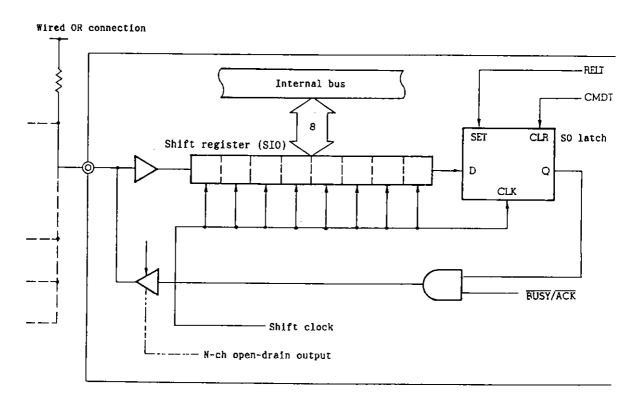

| 7-12 | Configuration of Shift Register and         |      |

|------|---------------------------------------------|------|

|      | Peripheral Circuitry                        | 7-27 |

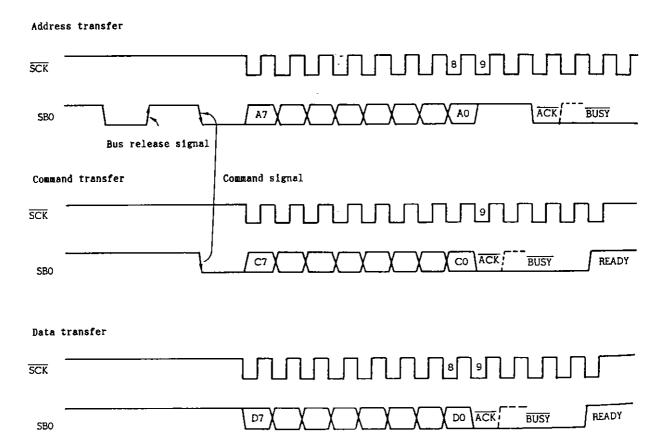

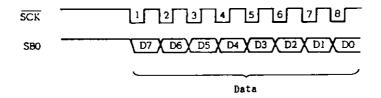

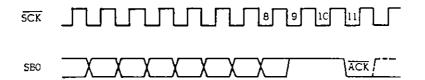

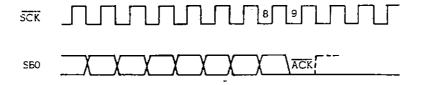

| 7-13 | Timing of SBI Transfer                      | 7-28 |

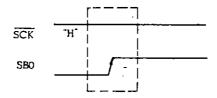

| 7-14 | Bus Release Signal                          | 7-29 |

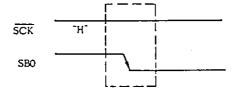

| 7-15 | Command Signal                              | 7-30 |

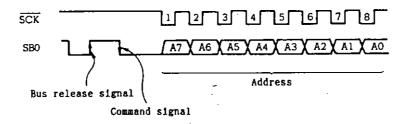

| 7-16 | Address                                     | 7-30 |

| 7-17 | Slave Selection Using an Address            | 7-31 |

| 7-18 | Command                                     | 7-31 |

| 7-19 | Data                                        | 7-31 |

| 7-20 | Acknowledge Signal                          | 7-32 |

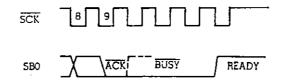

| 7-21 | Busy Signal and Ready Signal                | 7-33 |

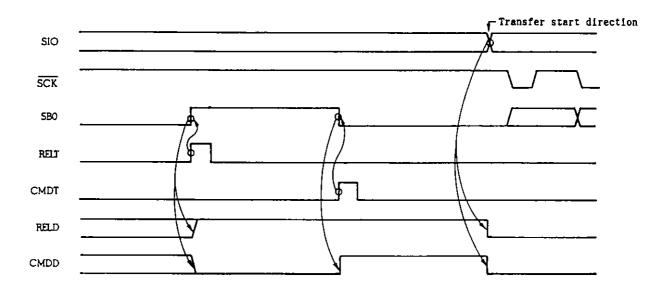

| 7-22 | Operation of RELT, CMDT, RELD, and CMDD     | 7-34 |

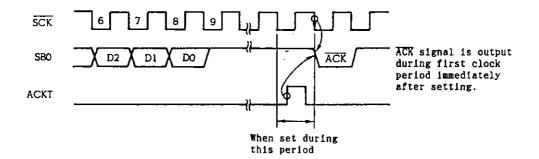

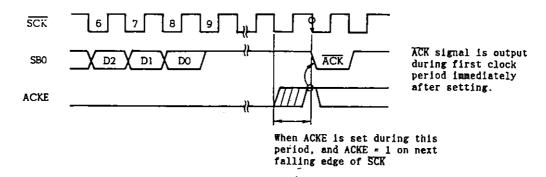

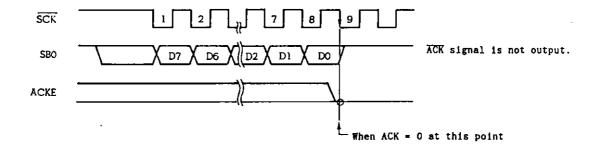

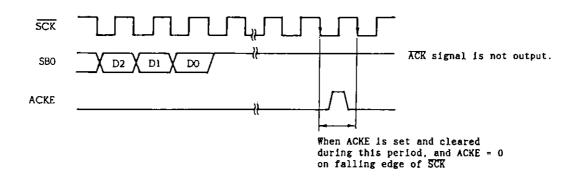

| 7-23 | Operation of ACKT                           | 7-34 |

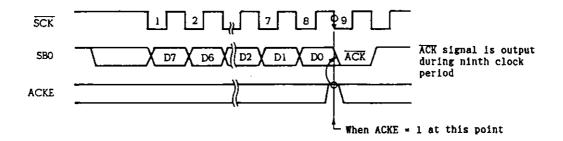

| 7-24 | Operation of ACKE                           | 7-35 |

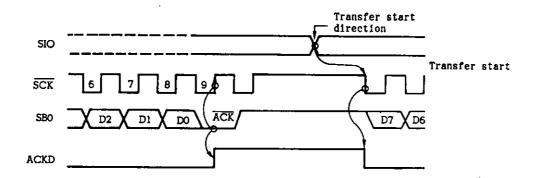

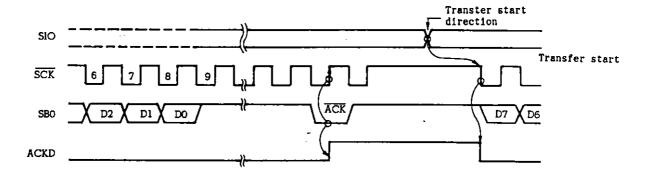

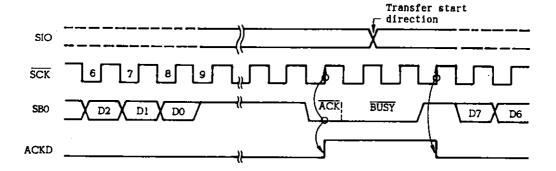

| 7-25 | Operation of ACKD                           | 7-36 |

| 7-26 | Operation of BSYE                           | 7-37 |

| 7-27 | Address Transfer Operation from Master      |      |

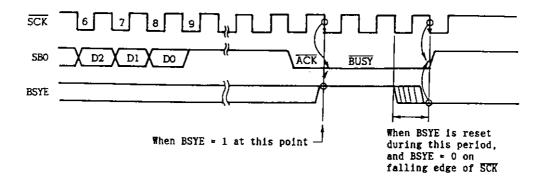

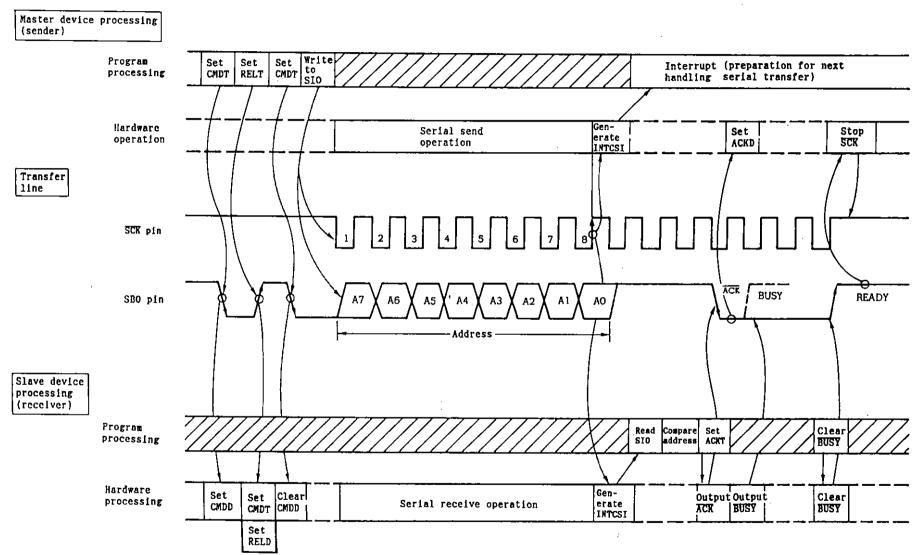

|      | Device to Slave Device                      | 7-44 |

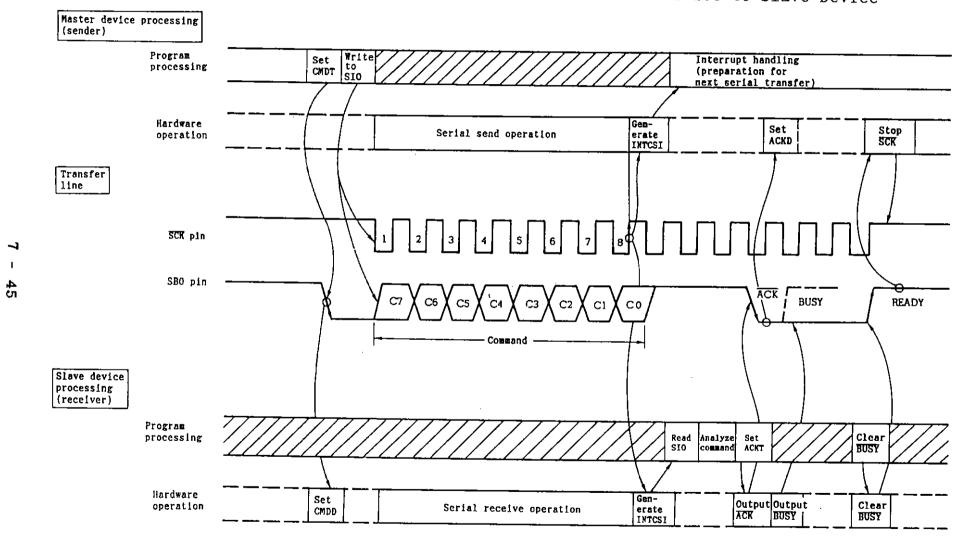

| 7-28 | Command Transfer Operation from Master      |      |

|      | Device to Slave Device                      | 7-45 |

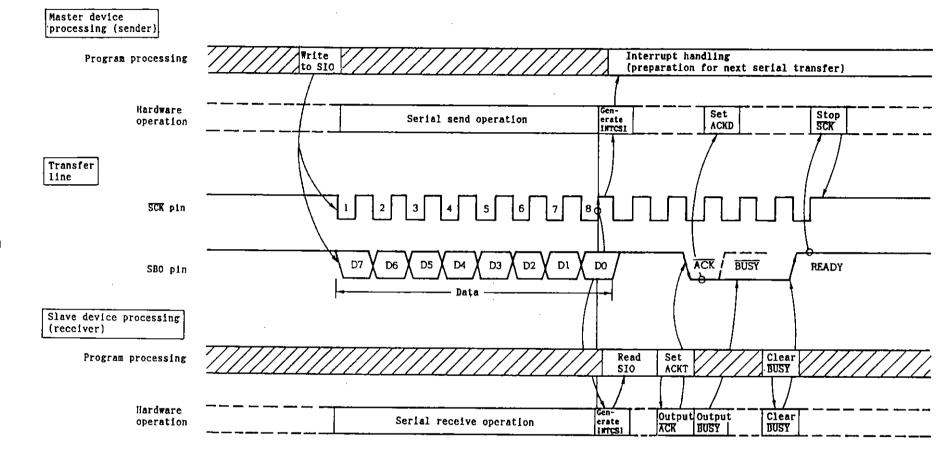

| 7-29 | Data Transfer Operation from Master Device  |      |

|      | to Slave Device                             | 7-46 |

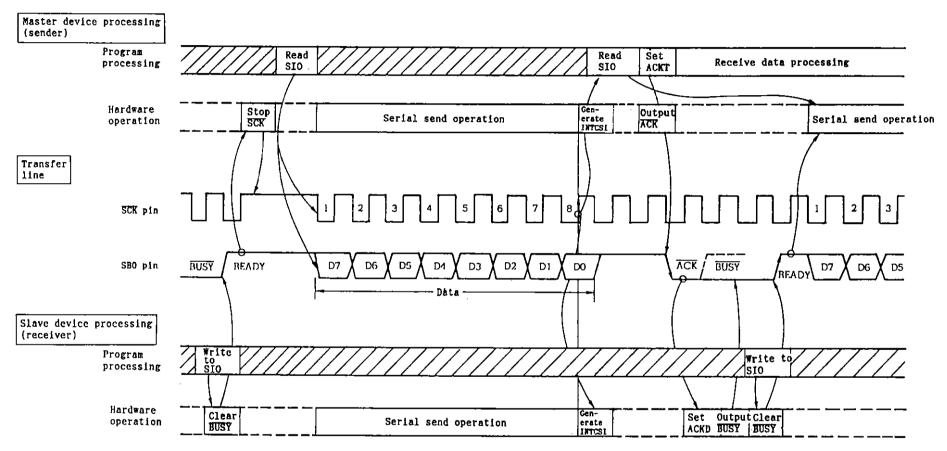

| 7-30 | Data Transfer Operation from Slave Device   |      |

|      | to Master Device                            | 7-47 |

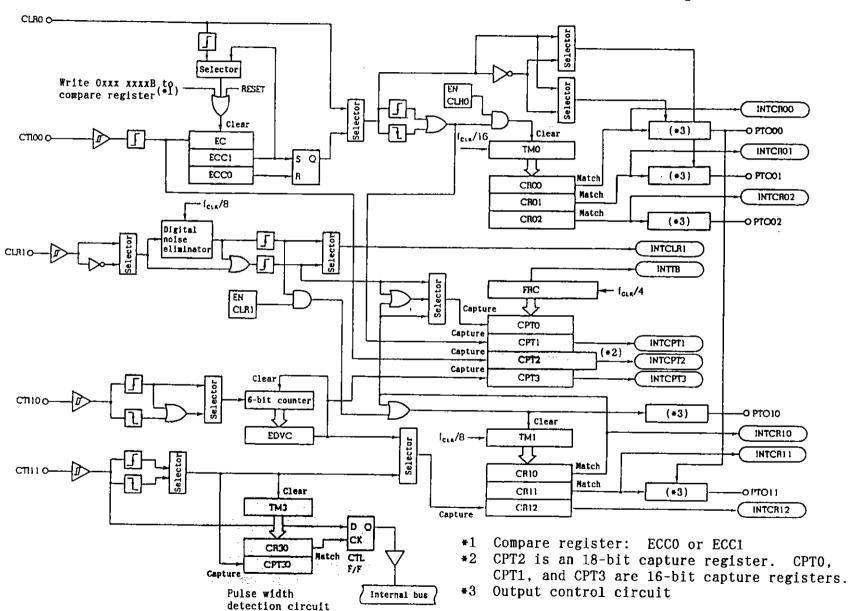

| 8-1  | Configuration of the Super Timer Unit       | 8-4  |

| 8-2  | Configuration of Timer 0, Timer 1, and Free |      |

|      | Running Counter                             | 8-5  |

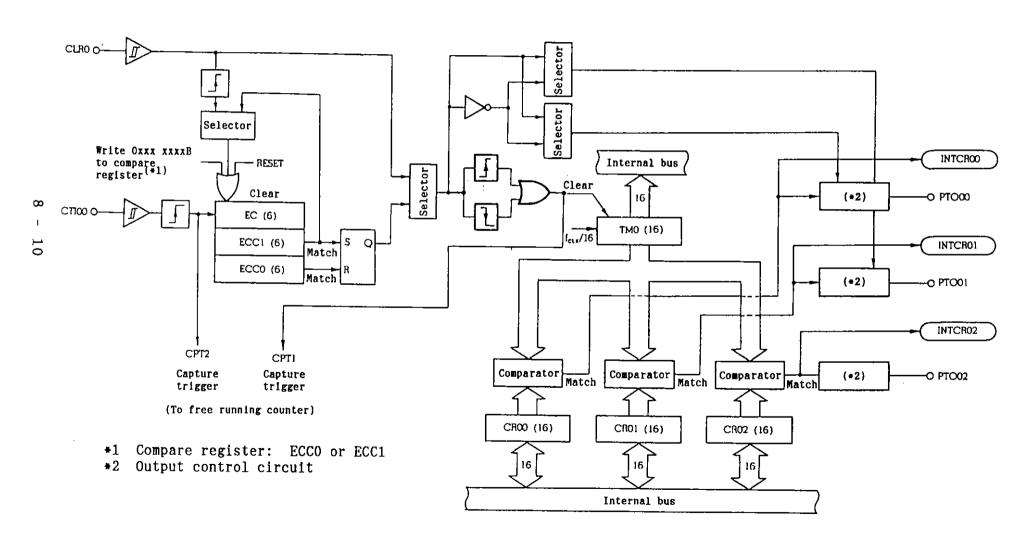

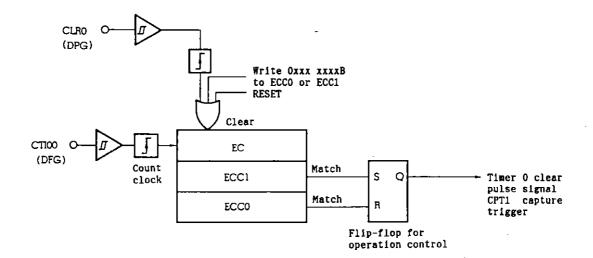

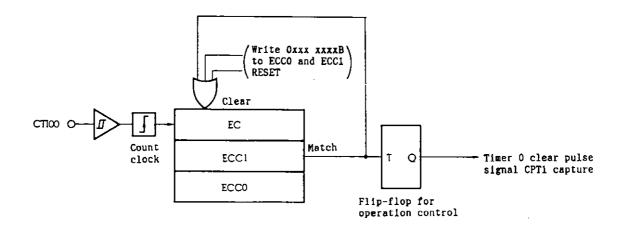

| 8-3  | Configuration of the Timer O Unit           | 8-10 |

| 8-4  | Configuration of the Event Counter in the   |      |

|      | Internal Pulse Generation Mode              | 8-11 |

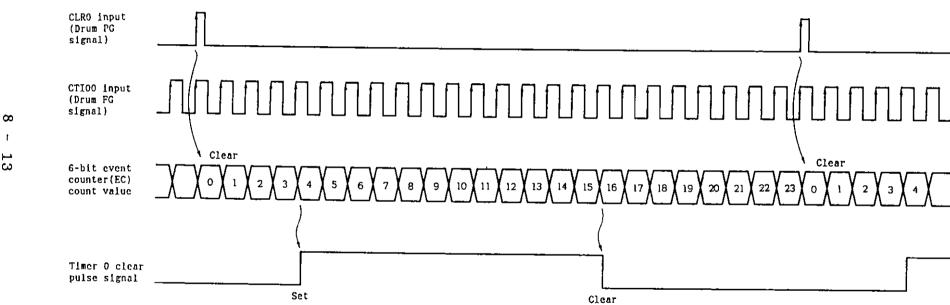

| 8-5  | Operation Timing in the Internal Pulse      |      |

|      | Generation Mode                             |      |

|      | (Generation of VCR Head Switching Signal)   | 8-13 |

| 8-6  | Configuration of the Event Counter in the   |      |

|      | General Event Divider Mode                  | 8-14 |

| Phase-out/Discontinued |

|------------------------|

|------------------------|

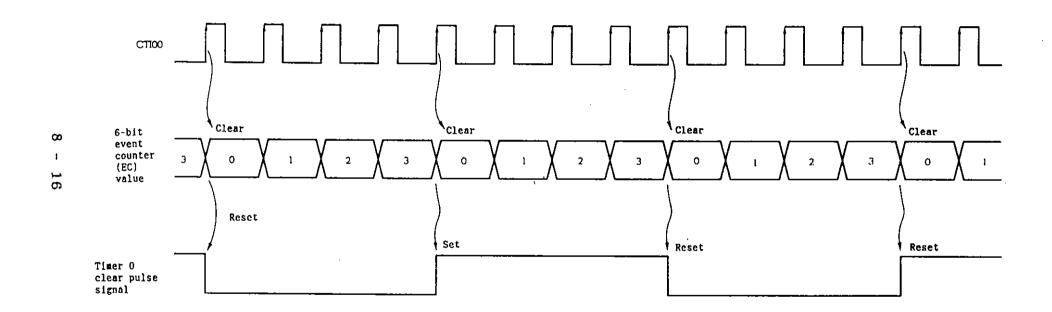

| 8-7  | Operation Timing in the General Event        |      |

|------|----------------------------------------------|------|

|      | Divider Mode                                 | 8-16 |

| 8-8  | Configuration of the Timer O General         |      |

|      | Output Mode                                  | 8-18 |

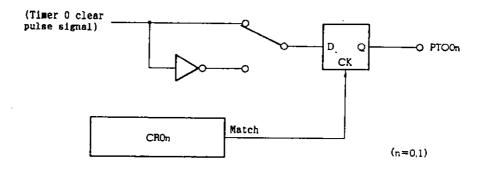

| 8-9  | Configuration of the Timer O RS Output Mode  | 8-19 |

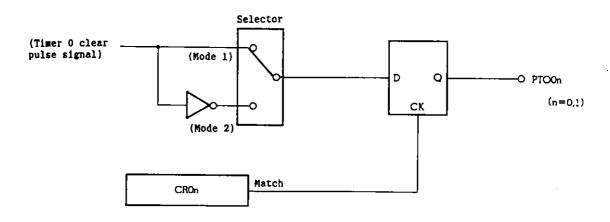

| 8-10 | Configuration of Timer O Delay Pulse Output  |      |

|      | Mode 1                                       | 8-19 |

| 8-11 | Configuration of Timer O Delay Pulse Output  |      |

|      | Mode 2                                       | 8-20 |

| 8-12 | Format of Input Control Register (ICR)       | 8-23 |

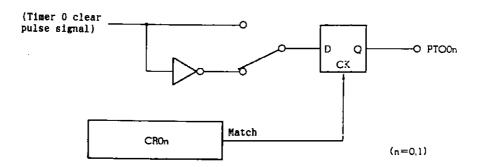

| 8-13 | Format of Timer Control Register 0 (TMC0)    | 8-24 |

| 8-14 | Format of Timer O Output Mode Register       |      |

|      | (TOMO)                                       | 8-25 |

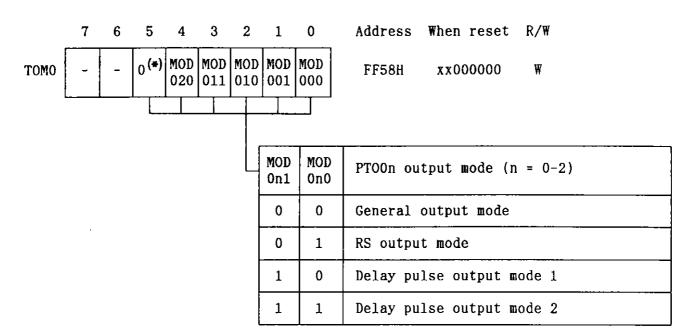

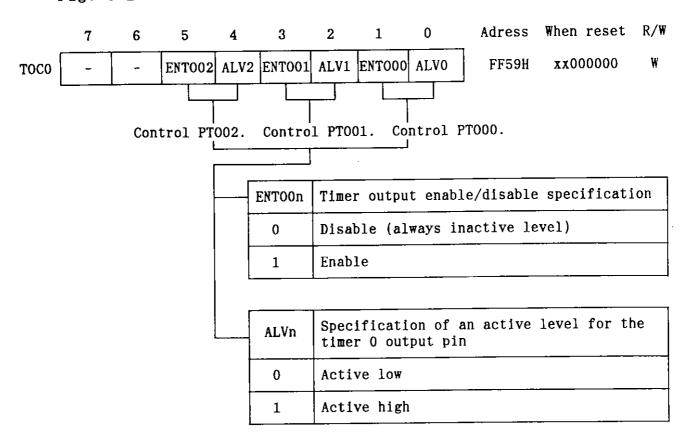

| 8-15 | Format of Timer O Output Control Register    |      |

|      | (TOCO)                                       | 8-27 |

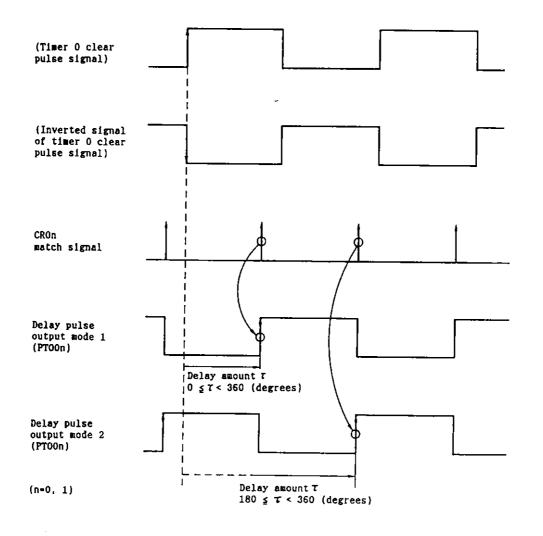

| 8-16 | Operation Timing of Timer O Delay Pulse      |      |

|      | Output Modes 1 and 2                         | 8-30 |

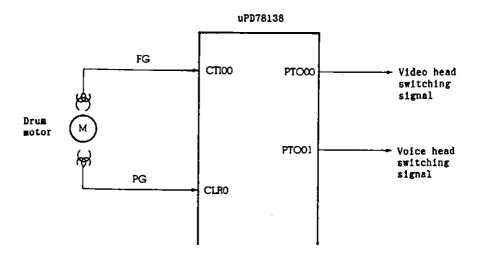

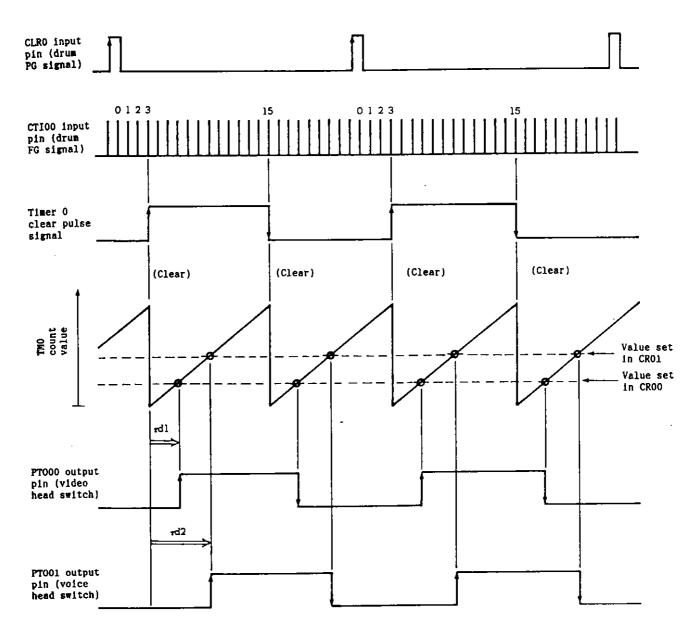

| 8-17 | Generating Head Switching Signals by Using   |      |

|      | the Timer O Unit                             | 8-32 |

| 8-18 | Timing Example of Head Switching Signals     |      |

| -    | with the Timer O Unit                        | 8-33 |

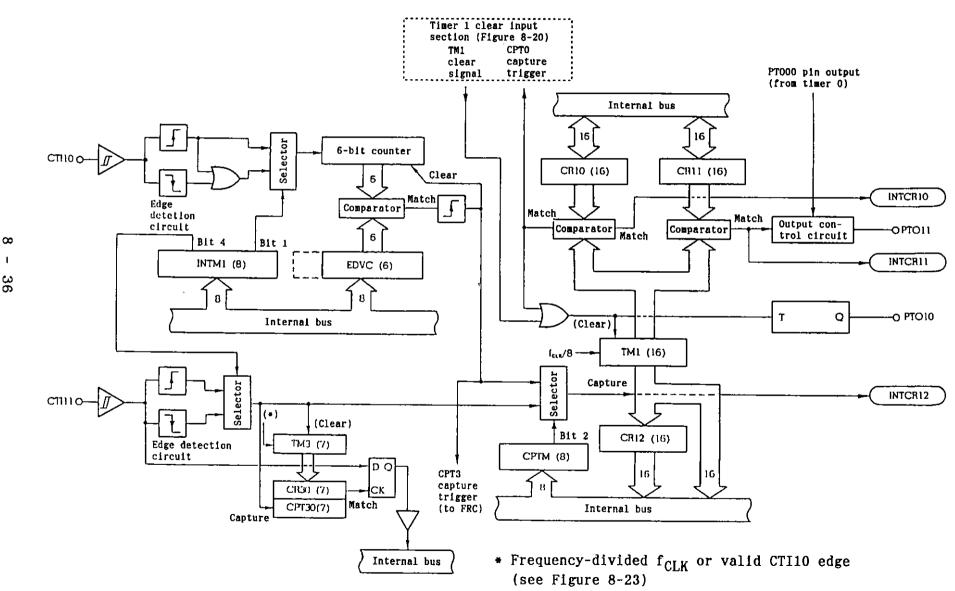

| 8-19 | Configuration of the Timer 1 Unit            | 8-36 |

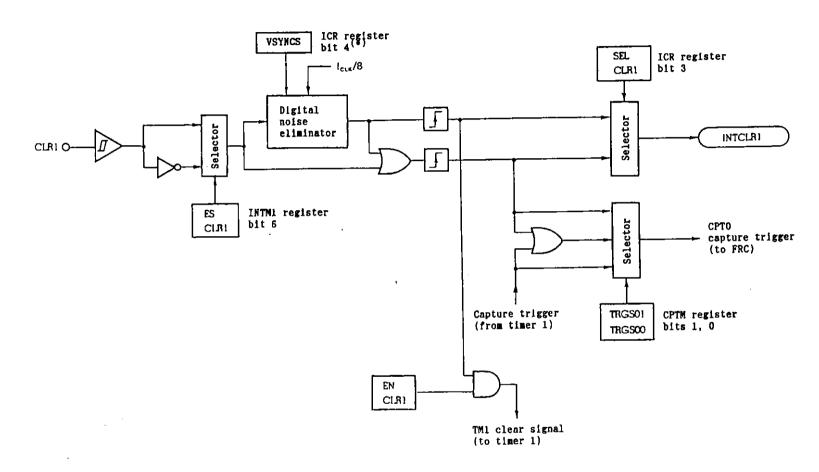

| 8-20 | Configuration of the Timer 1 Clear           |      |

|      | Input Section                                | 8-37 |

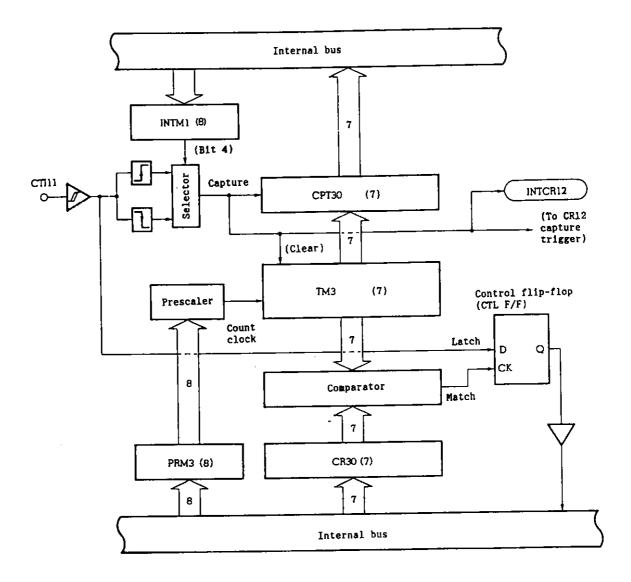

| 8-21 | Configuration of the Pulse Width Detection   |      |

|      | Circuit (TM3)                                | 8-41 |

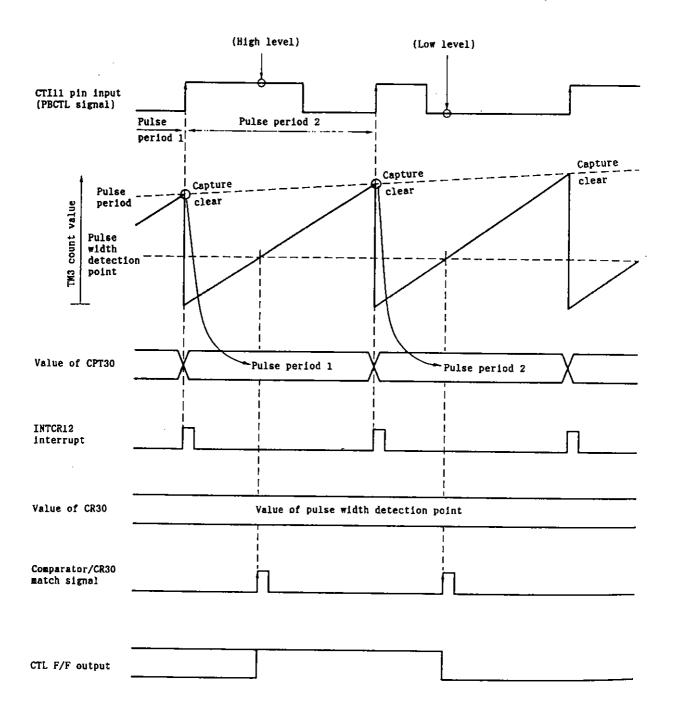

| 8-22 | Timing of Pulse Width Detection              |      |

|      | Circuit Operation                            | 8-42 |

| 8-23 | Configuration of the Prescaler               | 8-43 |

| 8-24 | Configuration of the Timer 1 (TM1)           | 8-44 |

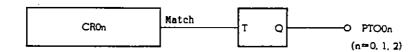

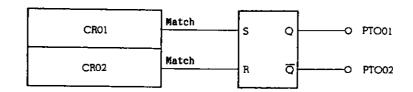

| 8-25 | Output Modes of PT011                        | 8-45 |

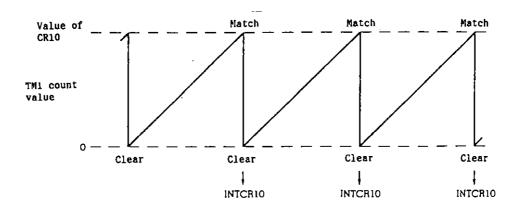

| 8-26 | Reference Counter Operation of Timer 1       | 8-47 |

| 8-27 | Programmable Timer Output Operation of       |      |

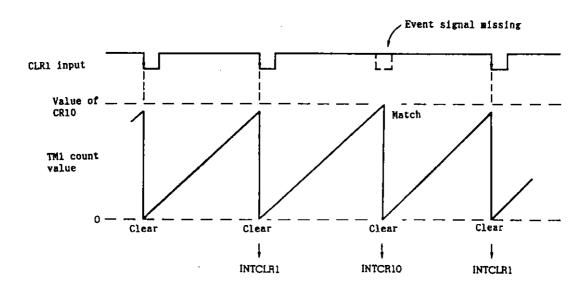

|      | Timer 1                                      | 8-49 |

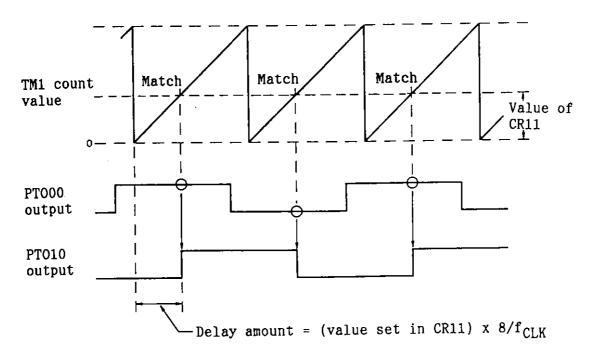

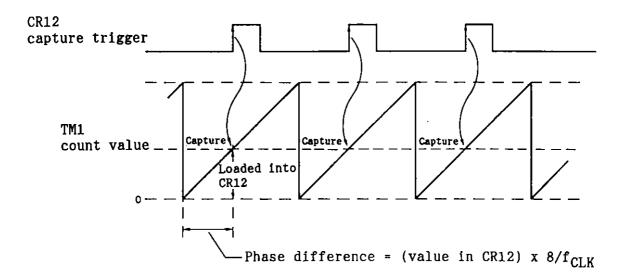

| 8-28 | Timer 1 Phase Difference Detection Operation | 8-50 |

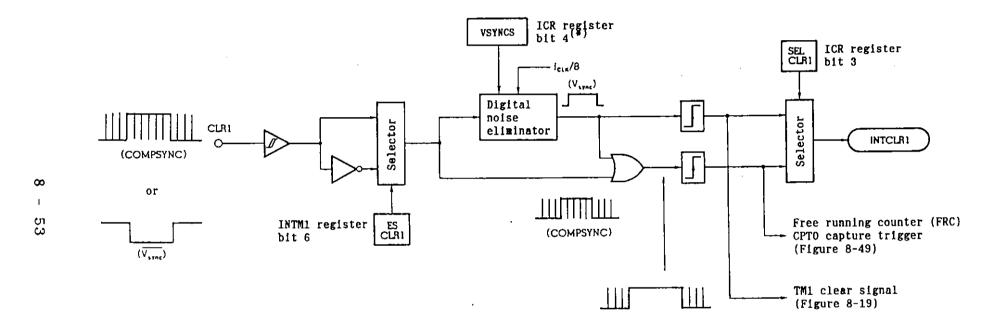

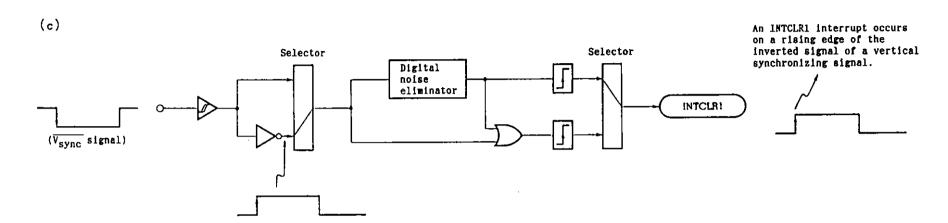

| 8-29 | Configuration of the CLR1 Input Section      |      |

|------|----------------------------------------------|------|

|      | (Digital Noise Eliminator)                   | 8-53 |

| 8-30 | Operation of the Digital Noise Eliminator    | 8-54 |

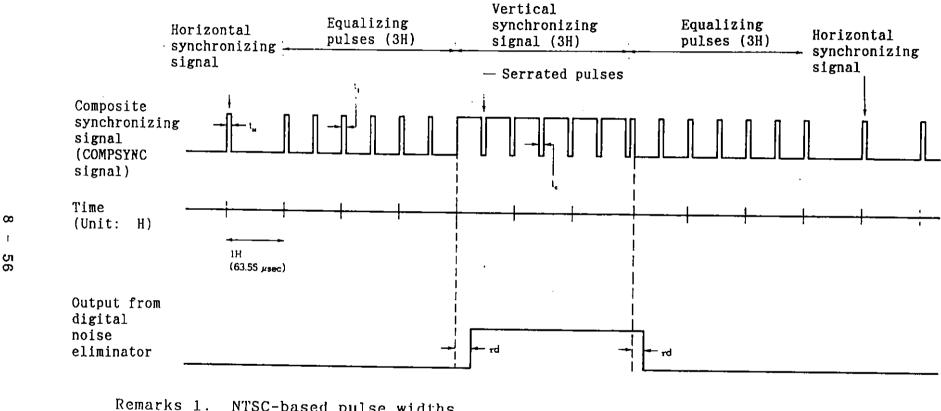

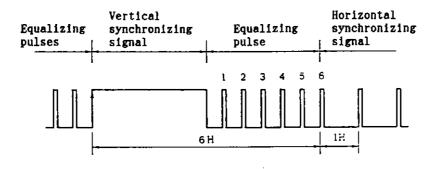

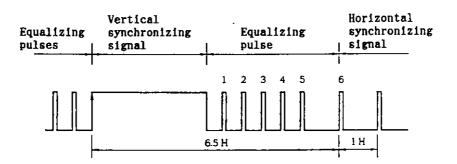

| 8-31 | Vertical Synchronizing Signal Extraction     |      |

|      | Using the Digital Noise Eliminator           | 8-56 |

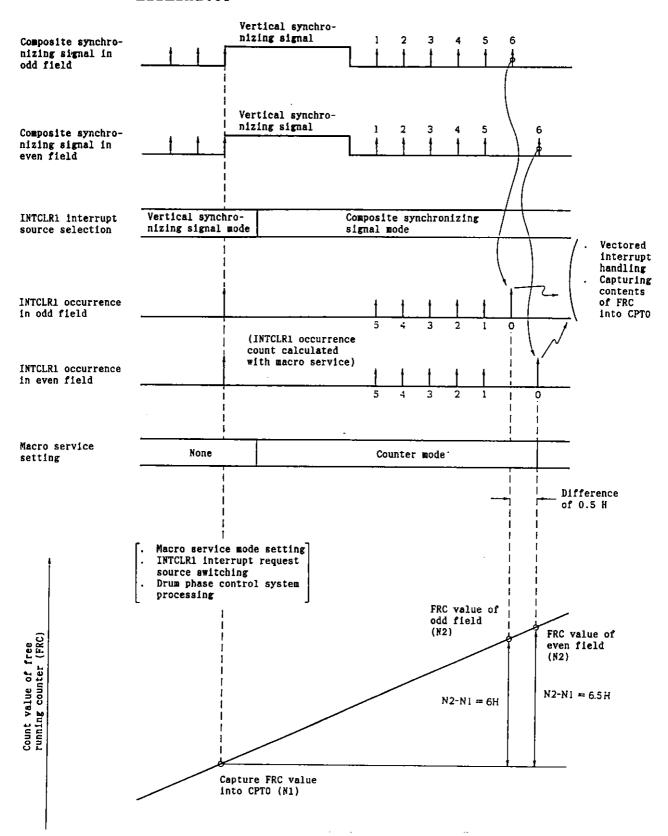

| 8-32 | COMPSYNC Signal Used for Even/Odd            |      |

|      | Field Determination                          | 8-58 |

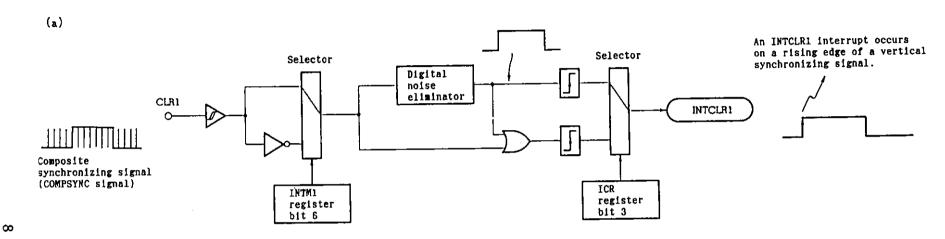

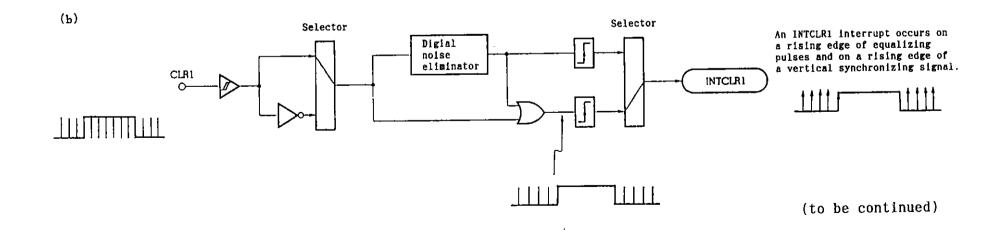

| 8-33 | Example of INTCLR1 Setting                   | 8-59 |

| 8-34 | Even/Odd Field Determination Using the       |      |

|      | Digital Noise Eliminator                     | 8-64 |

| 8-35 | Example of CLR1 Input Detection Error Due    |      |

|      | to Noise                                     | 8-65 |

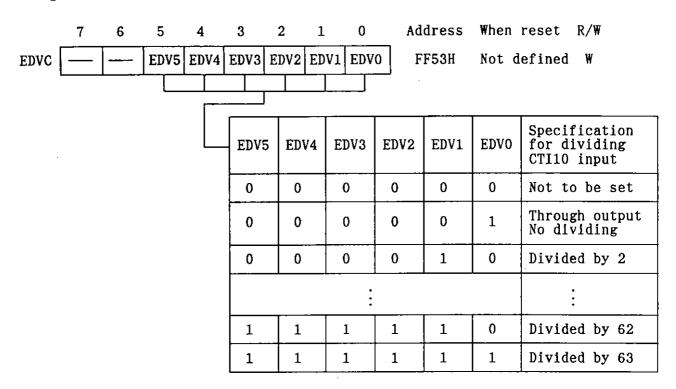

| 8-36 | Format of the Event Divider Control Register |      |

|      | (EDVC)                                       | 8-67 |

| 8-37 | Format of External Capture Input Mode        |      |

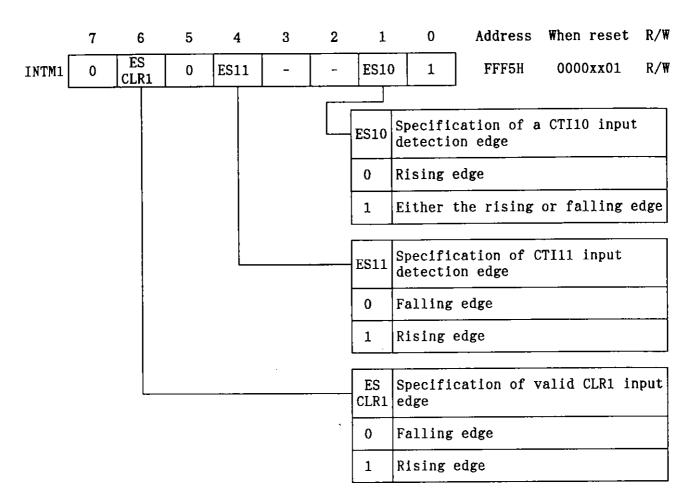

|      | Register 1 (INTM1)                           | 8-68 |

| 8-38 | Format of Prescaler Mode Register (PRM3)     | 8-69 |

| 8-39 | Format of Capture Mode Register (CPTM)       | 8-70 |

| 8-40 | Format of Timer Control Register 0 (TMC0)    | 8-71 |

| 8-41 | Format of Timer 1 Output Mode Register       |      |

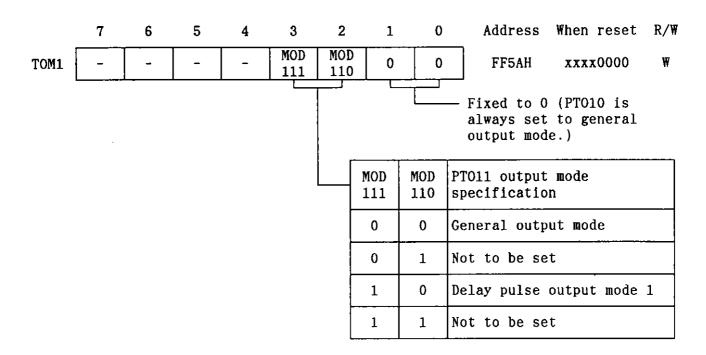

|      | (TOM1)                                       | 8-72 |

| 8-42 | Format of Timer 1 Output Control Register    |      |

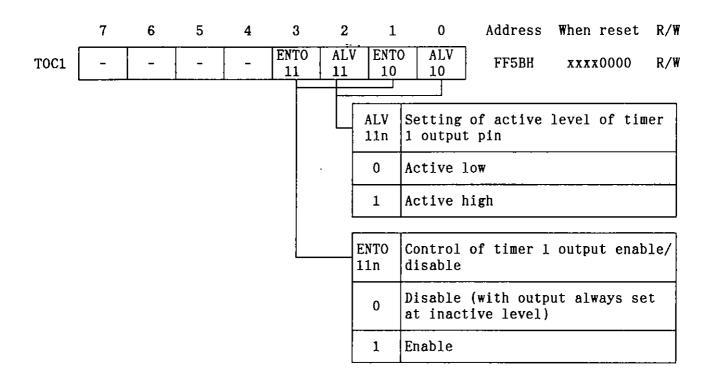

|      | (TOC1)                                       | 8-72 |

| 8-43 | Format of Input Control Register (ICR)       | 8-73 |

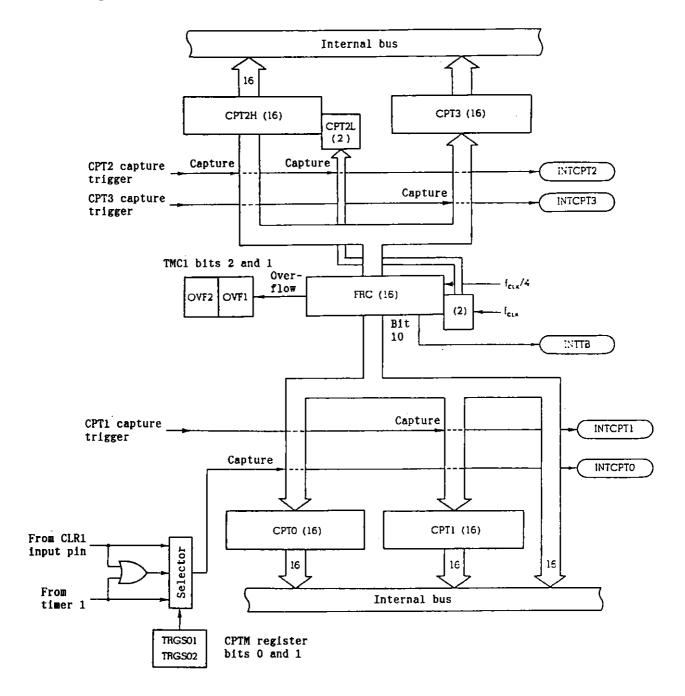

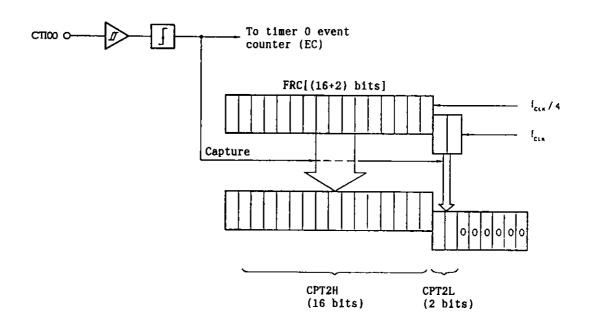

| 8-44 | Configuration of the Free Running Counter    | 8-75 |

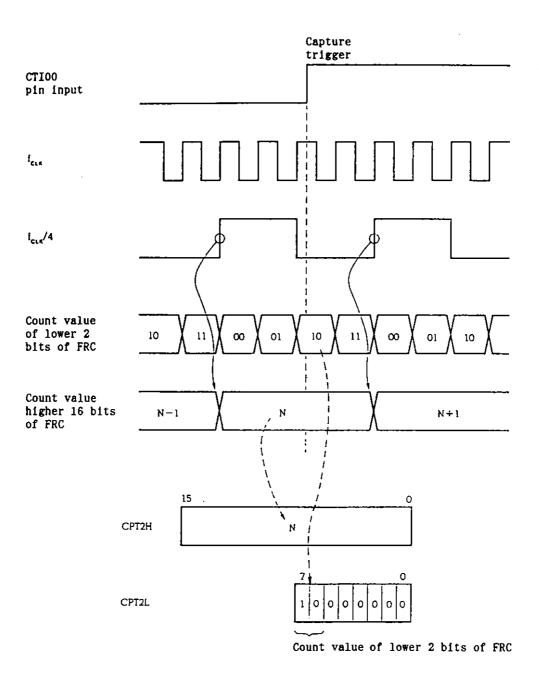

| 8-45 | Configuration of CPT2 (CPT2H, CPT2L)         | 8-77 |

| 8-46 | CPT2L Capture Data                           | 8-77 |

| 8-47 | Example of FRC Count Operation               | 8-78 |

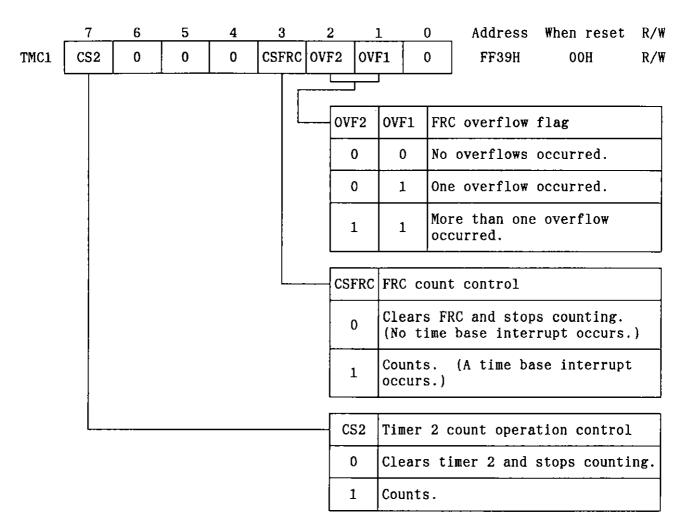

| 8-48 | Format of Timer Control Register 1 (TMC1)    | 8-80 |

| 8-49 | Format of Capture Mode Register (CPTM)       | 8-81 |

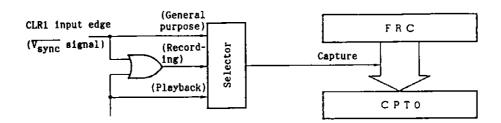

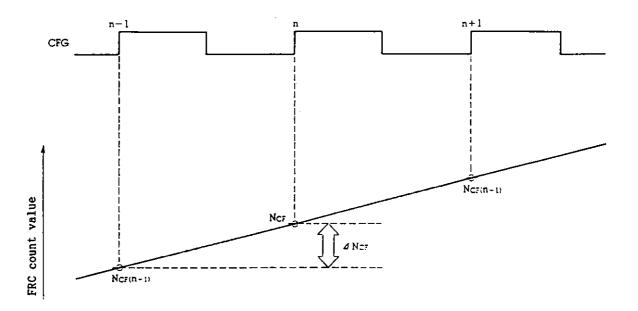

| 8-50 | Example of Using the FRC in a VCR            |      |

|      | (Detecting Drum Motor Speed Error Using      |      |

|      | Capture Register 2)                          | 8-82 |

| 8-51 | Example of Using FRC Capture Registers 0     |      |

|      | (CPTO)                                       | 8-83 |

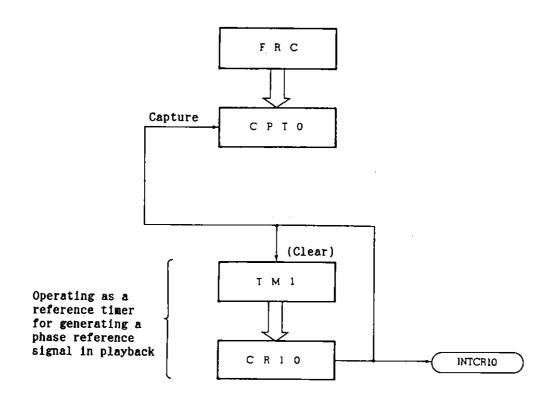

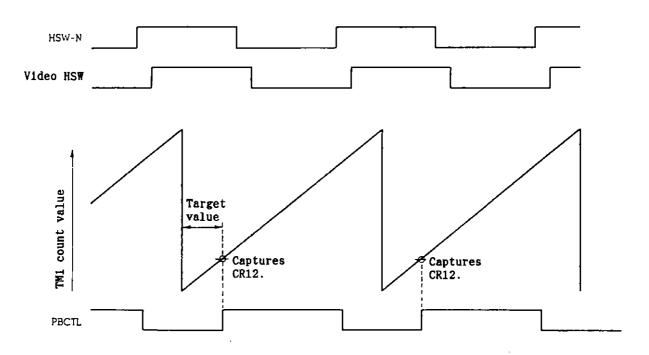

| 8-52 | Example of Using the FRC and TM1 in Playback                          |       |

|------|-----------------------------------------------------------------------|-------|

|      | (Operating TM1 as the Internal Phase                                  |       |

|      | Reference Timer)                                                      | 8-84  |

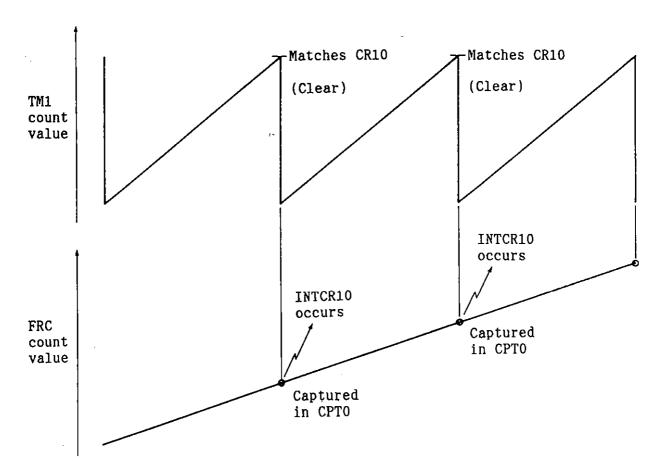

| 8-53 | Operation of the FRC and TM1 in Playback                              | 8-85  |

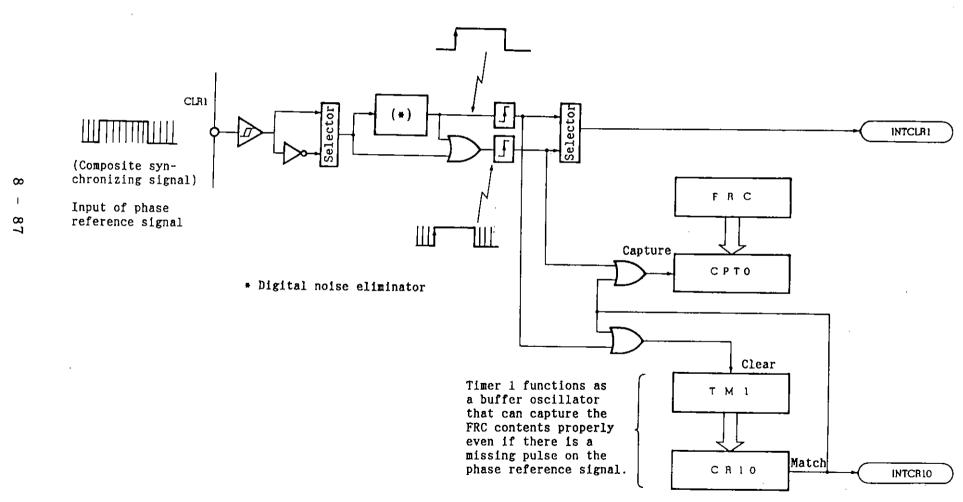

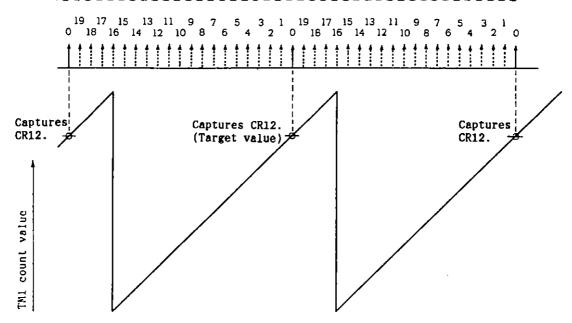

| 8-54 | Example of Using the FRC and TM1 in Recording                         |       |

|      | (Capturing the FRC Contents on Input of the                           |       |

|      | Phase Reference Signal)                                               | 8-87  |

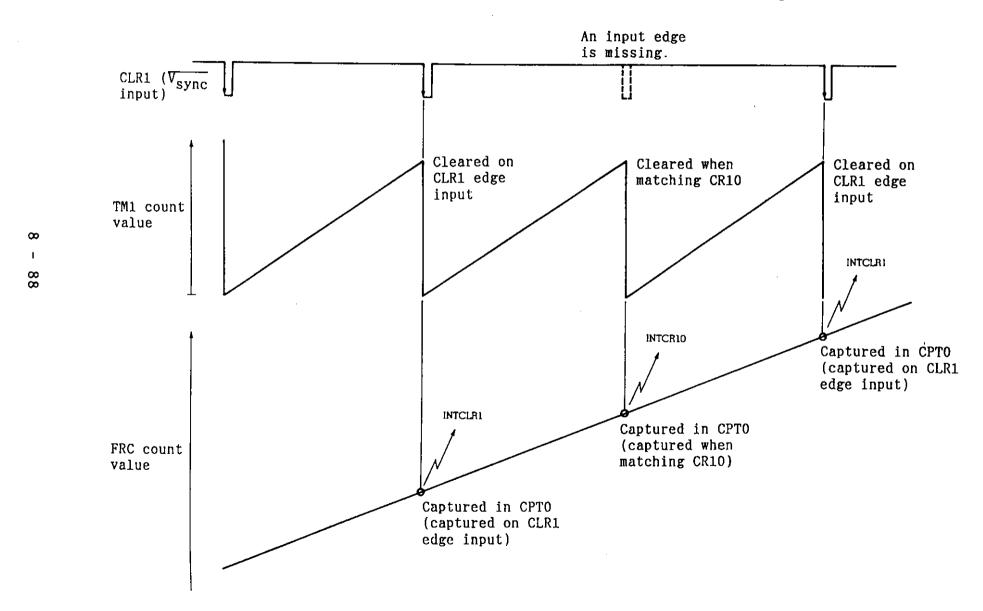

| 8-55 | Operation of the FRC and TM1 in Recording                             | 8-88  |

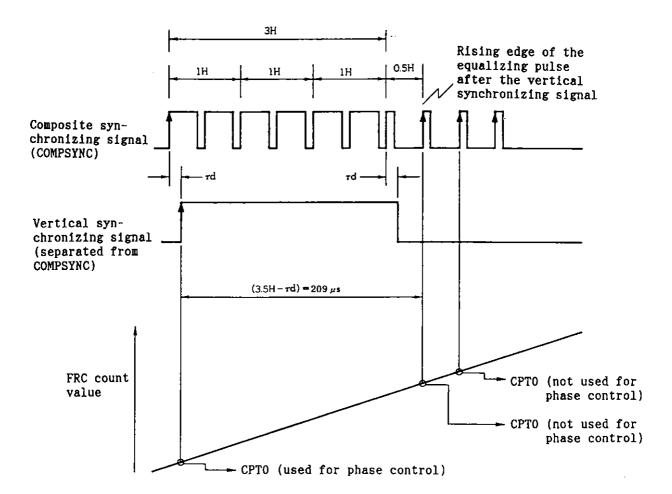

| 8-56 | FRC Capture Operation in Recording (CPTO)                             | 8-91  |

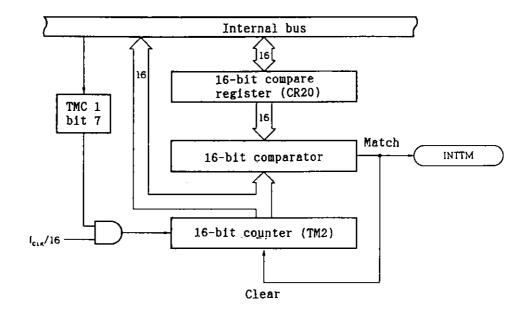

| 8-57 | Configuration of the Timer 2 Unit                                     | 8-93  |

| 8-58 | Format of Timer Control Register 1 (TMC1)                             | 8-94  |

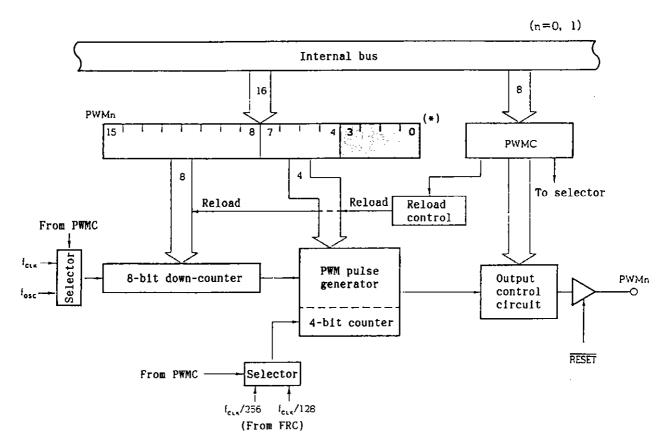

| 8-59 | Configuration of the PWM Output Unit                                  | 8-95  |

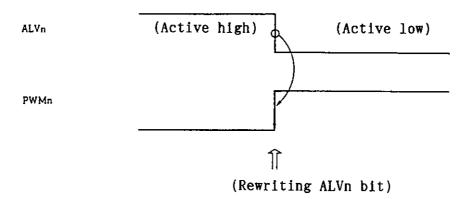

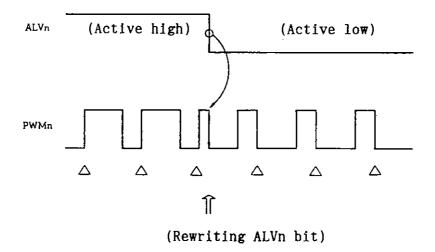

| 8-60 | Active Level Setting for PWM Output                                   | 8-98  |

| 8-61 | Example 1 of PWM Output Timing                                        |       |

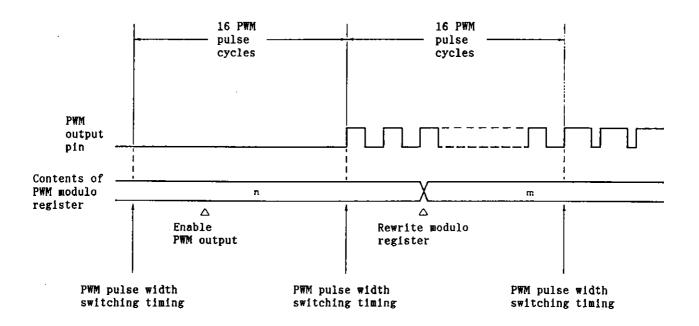

|      | (PWM Pulse Width Switching Cycle: 2 <sup>12</sup> /f <sub>CLK</sub> ) | 8-100 |

| 8-62 | Example 2 of PWM Output Timing                                        |       |

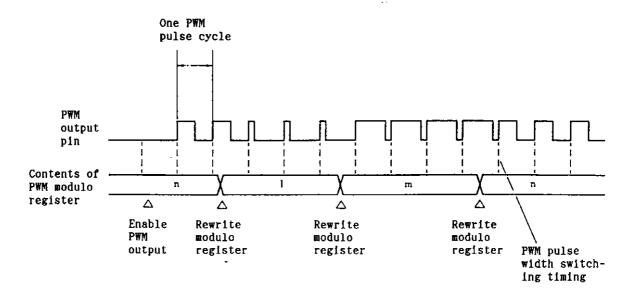

|      | (PWM Pulse Width Switching Cycle: 28/f <sub>CLK</sub> )               | 8-101 |

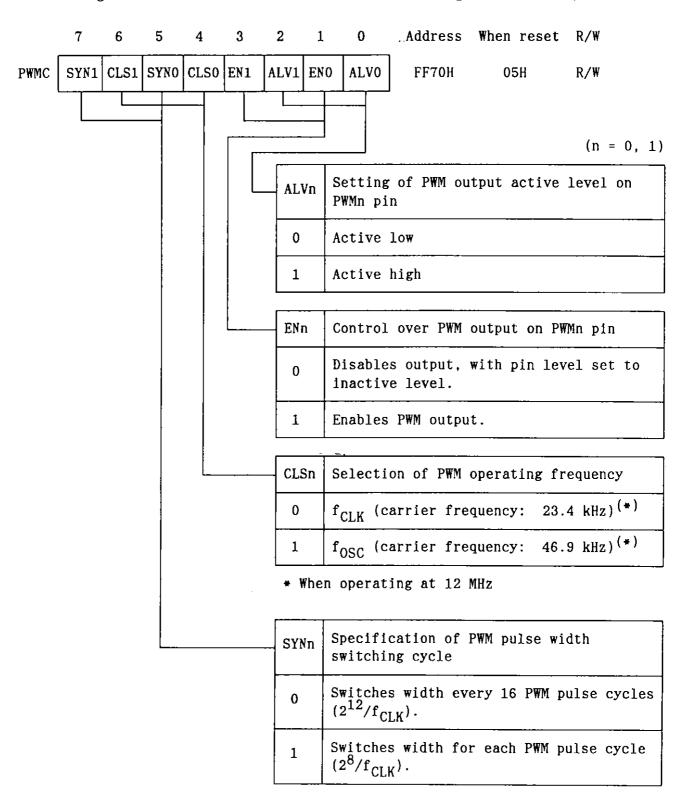

| 8-63 | Format of the PWM Control Register (PWMC)                             | 8-103 |

|      |                                                                       |       |

| 9-1  | Block Diagram of A/D Converter                                        | 9-3   |

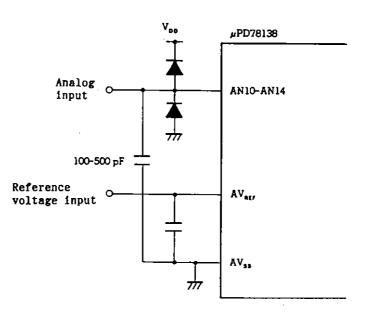

| 9-2  | Example of Connecting Capacitors to A/D                               |       |

|      | Converter Pins                                                        | 9-4   |

| 9-3  | Format of A/D Conversion Mode Register (ADM)                          | 9-8   |

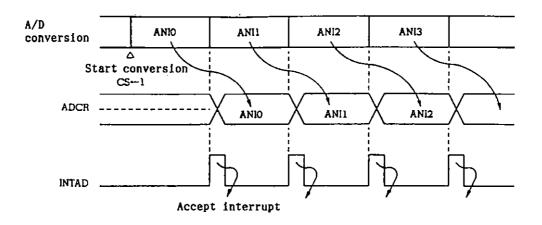

| 9-4  | Basic Operation of A/D Conversion                                     | 9-11  |

| 9-5  | A/D Conversion Started by Hardware                                    | 9-11  |

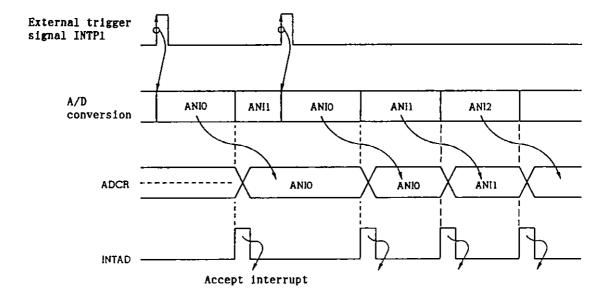

| 9-6  | Rewriting ADM Contents during A/D Conversion                          | 9-12  |

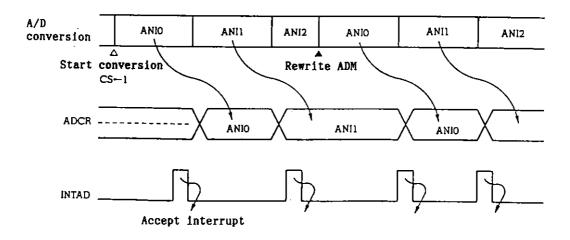

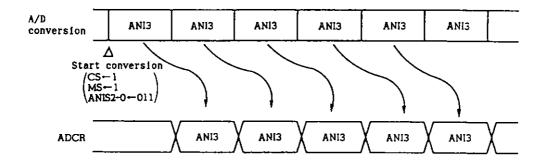

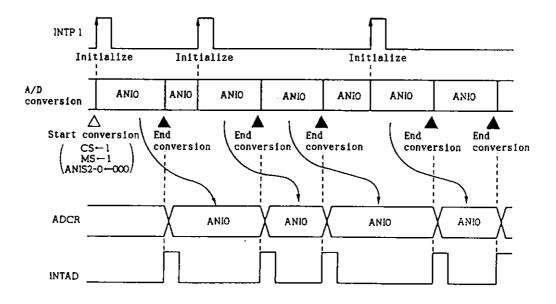

| 9-7  | Operation Timing in Select Mode                                       | 9-13  |

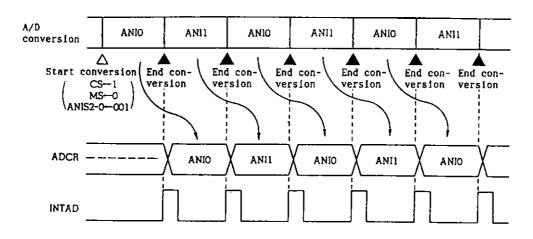

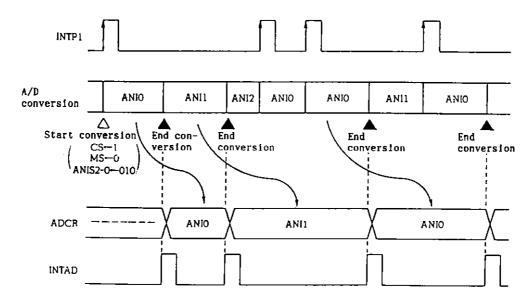

| 9-8  | Operation Timing in Scan Mode                                         | 9-14  |

|      |                                                                       |       |

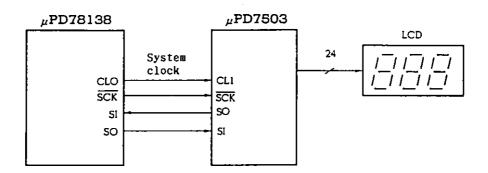

| 10-1 | Application Example for the Clock                                     |       |

|      | Output Function                                                       | 10-1  |

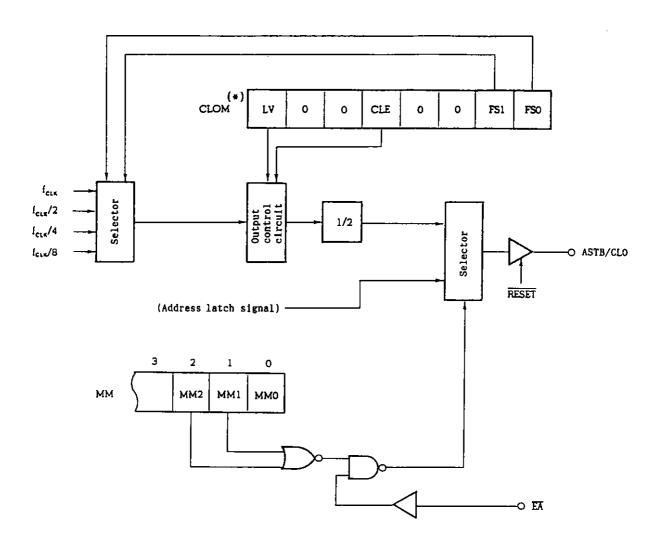

| 10-2 | Block Diagram of the Clock Output Circuit                             | 10-2  |

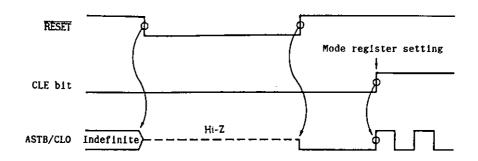

| 10-3 | CLO Pin at Initialization                                             | 10-3  |

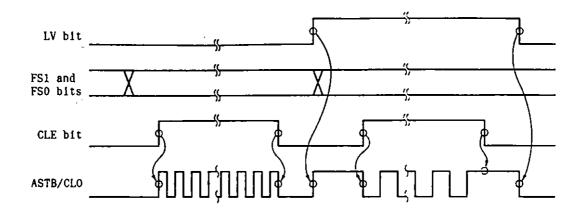

| 10-4 | Format of Clock Output Mode Register (CLOM)                           | 10-5  |

| 10-5 | Example of Setting the CLOM Register                                  | 10-6  |

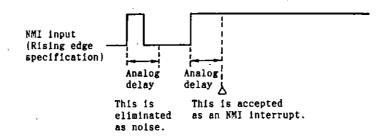

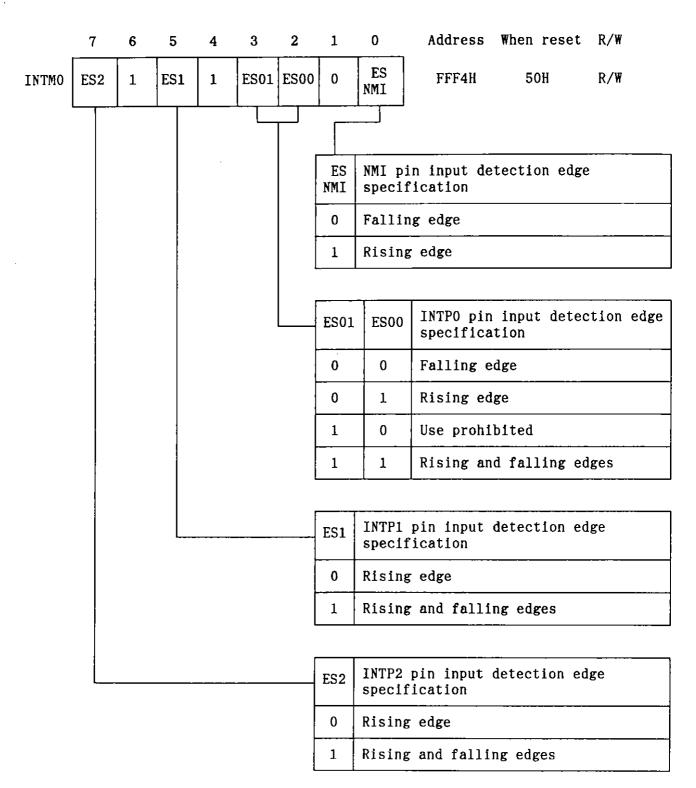

| 11-1  | Noise Elimination at an External Interrupt  |       |

|-------|---------------------------------------------|-------|

|       | Request Pin                                 | 11-5  |

| 11-2  | Format of the External Interrupt Mode       |       |

|       | Register 0 (INTMO)                          | 11-7  |

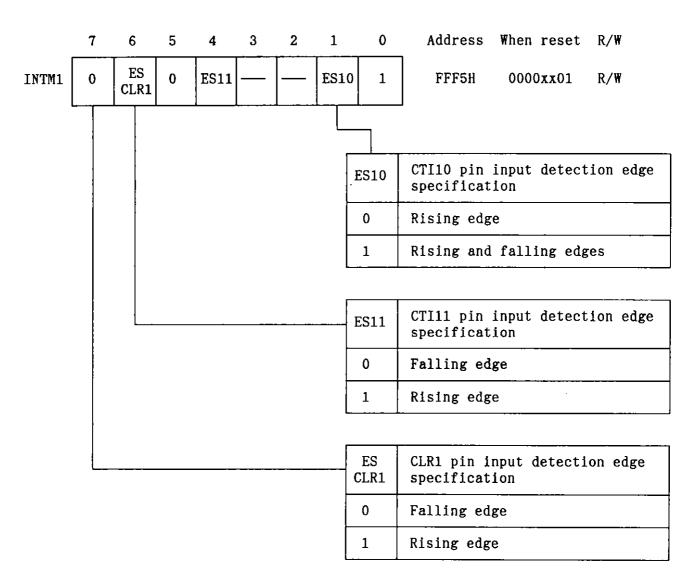

| 11-3  | Format of the External Capture Input Mode   |       |

|       | Register (INTM1)                            | 11-8  |

| 11-4  | Format of the Interrupt Request Flag        |       |

|       | Register (IF0)                              | 11-12 |

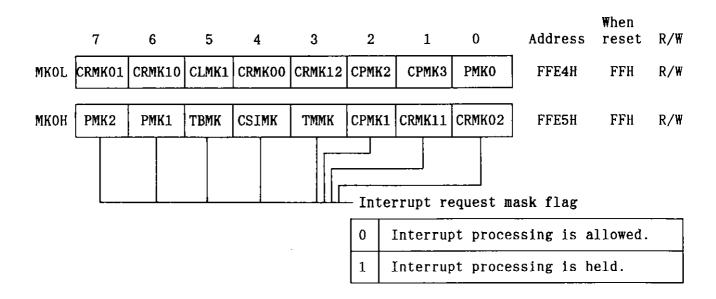

| 11-5  | Format of the Interrupt Mask Register (MKO) | 11-13 |

| 11-6  | Format of the Interrupt Service Mode        |       |

|       | Register (ISMO)                             | 11-13 |

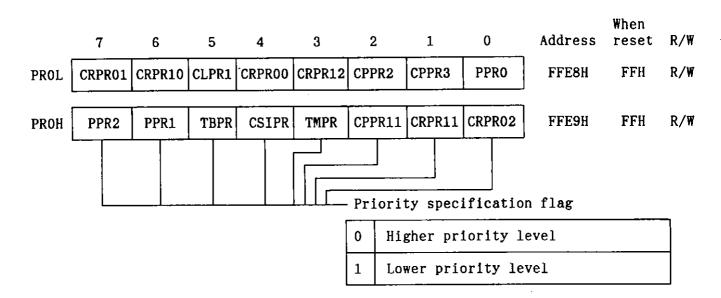

| 11-7  | Format of the Priority Specification Flag   |       |

|       | Register (PRO)                              | 11-14 |

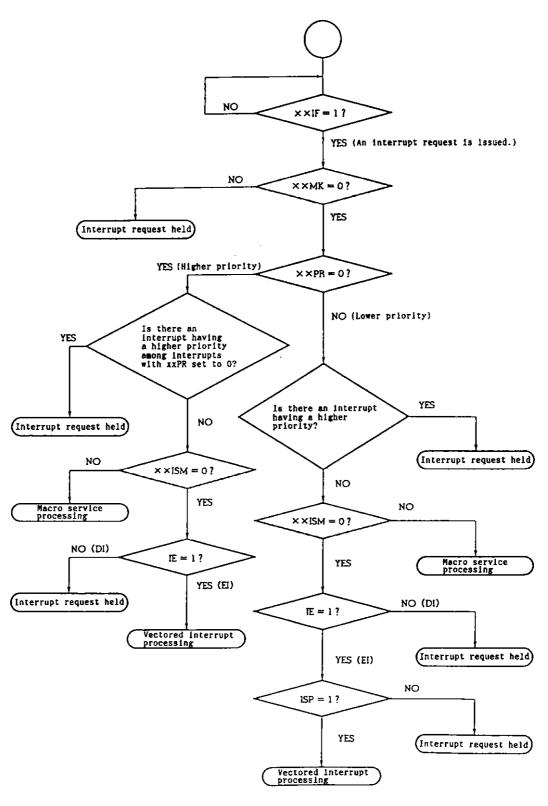

| 11-8  | Interrupt Processing Algorithm              | 11-15 |

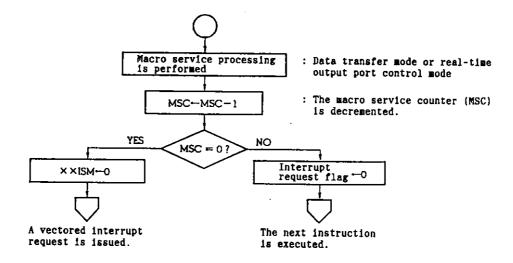

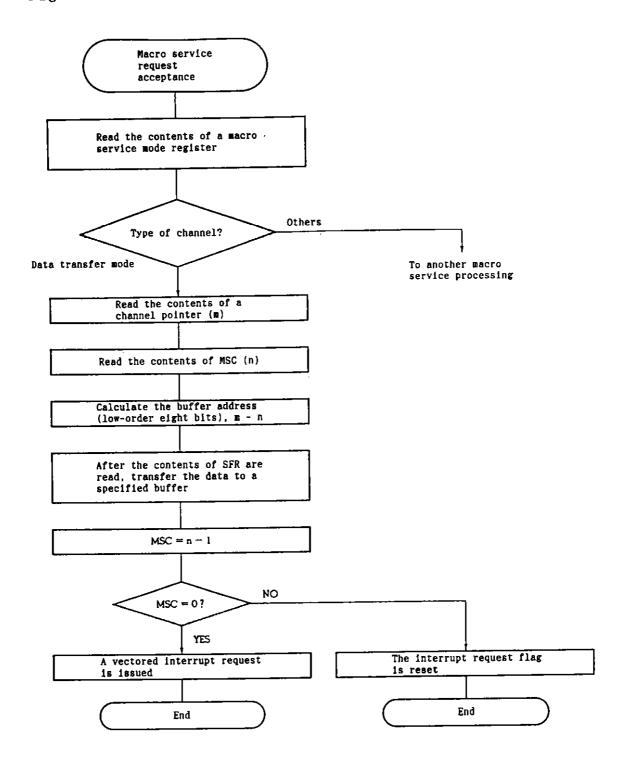

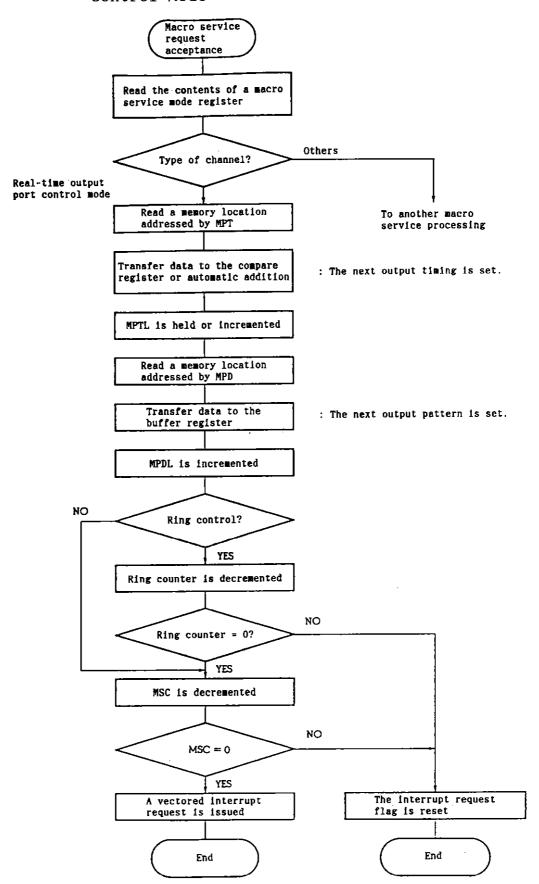

| 11-9  | Sequence of Macro Service Processing        | 11-22 |

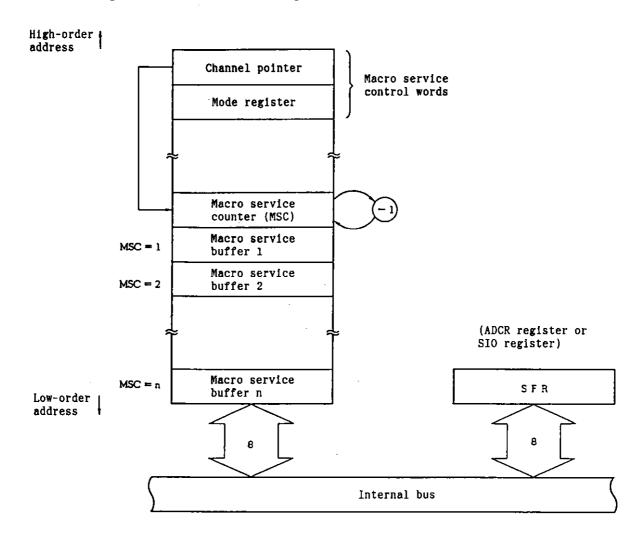

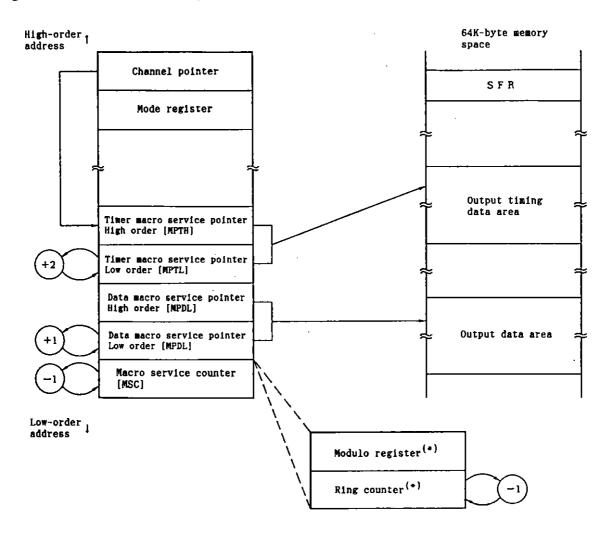

| 11-10 | Macro Service Control Words                 | 11-24 |

| 11-11 | Format of the Macro Service Mode Register   |       |

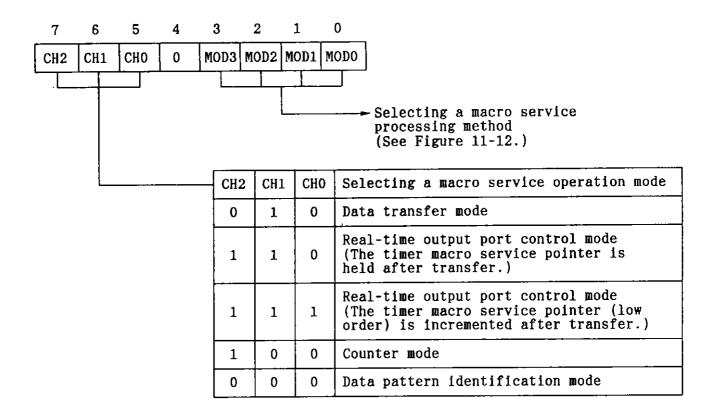

|       | (High-order Three Bits)                     | 11-25 |

| 11-12 | Format of a Macro Service Mode Register     | 11-26 |

| 11-13 | Setting of a Macro Service Mode Register    |       |

|       | in the Data Transfer Mode                   | 11-28 |

| 11-14 | Addressing in the Data Transfer Mode        | 11-30 |

| 11-15 | Processing Sequence in the Data             |       |

|       | Transfer Mode                               | 11-31 |

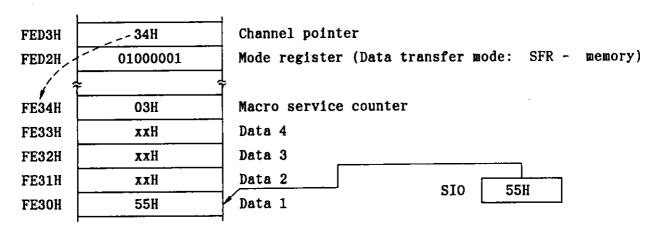

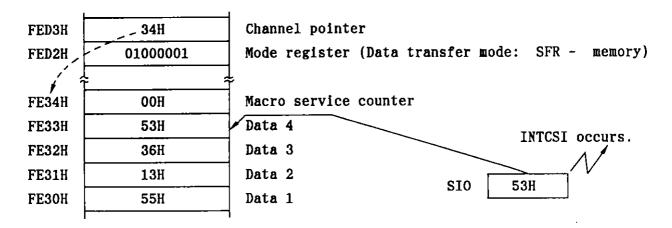

| 11-16 | Example of Data Transfer                    | 11-33 |

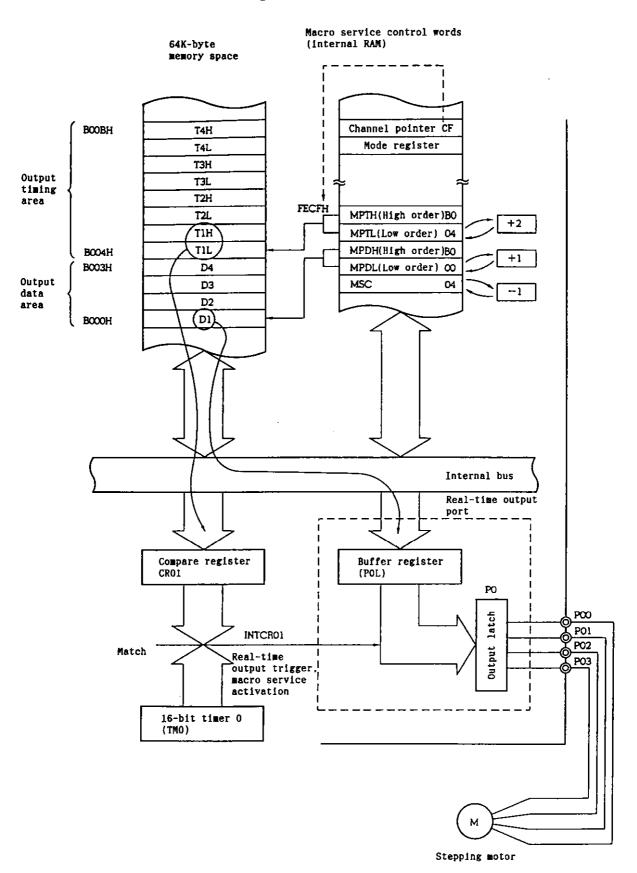

| 11-17 | Addressing in the Real-time Output Port     |       |

|       | Control Mode                                | 11-35 |

| 11-18 | Processing Sequence in the Real-time Output |       |

|       | Port Control Mode                           | 11-39 |

| 11-19 | Example of Setting the Macro Service Mode   |       |

|       | Register in the Basic Operation Mode        | 11-41 |

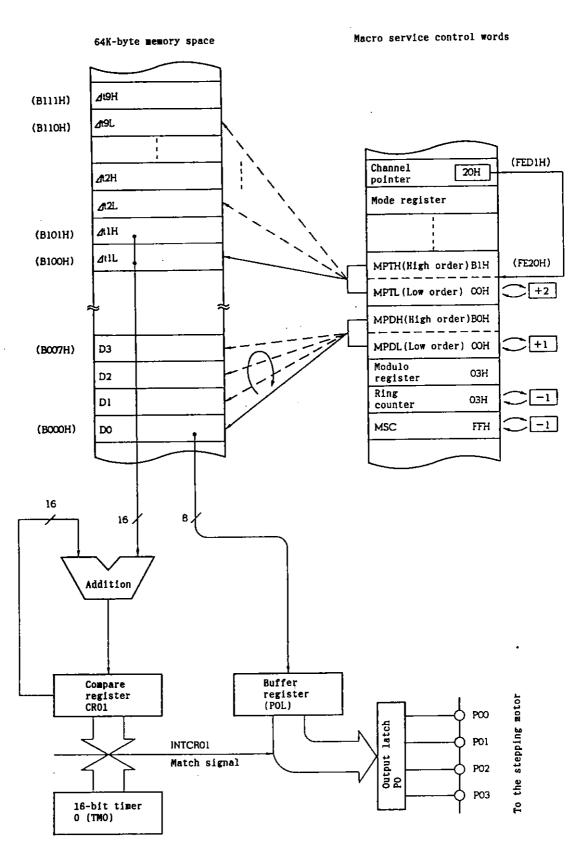

| 11-20 | Open-loop Control for the Stepping Motor    |       |

|       | via the Realtime Output Port                | 11-42 |

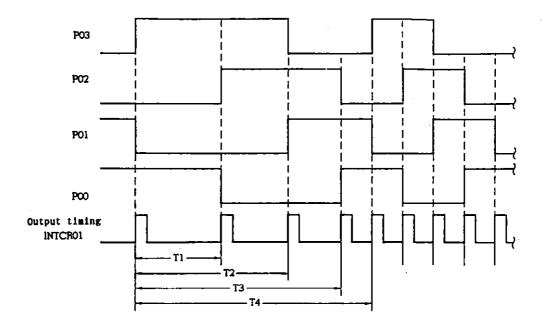

| 11-21 | Output Timing in the Real-time Output       |       |

|       | Port Mode                                   | 11-43 |

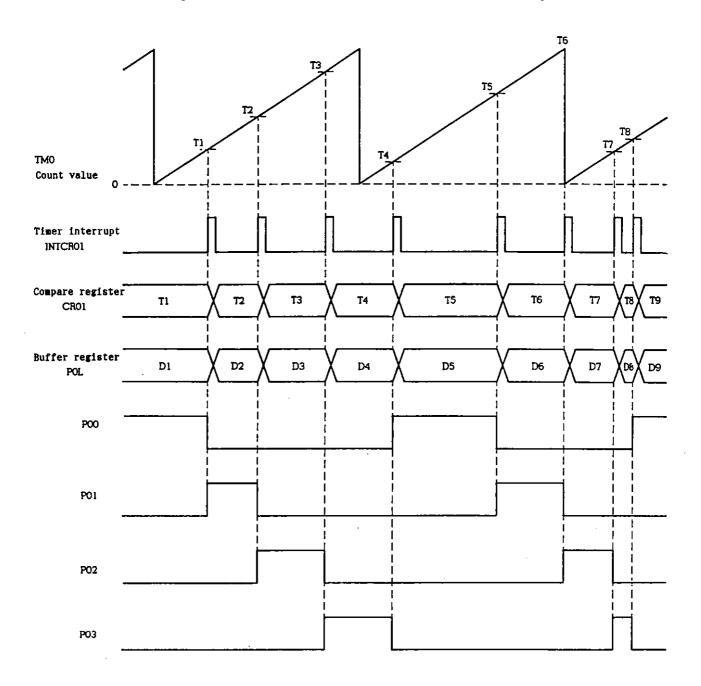

| 11_99 | Data Transfer Control Timing                | 11 44 |

| Phase-out/Discontinued |

|------------------------|

|                        |

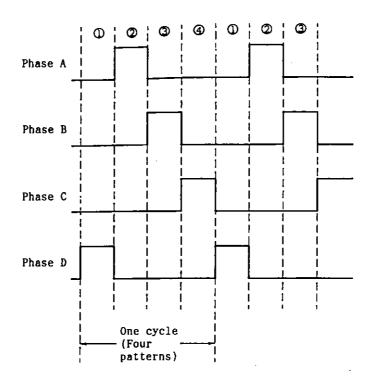

| 11-23 | 1-phase Excitation of a 4-phase              |       |

|-------|----------------------------------------------|-------|

|       | Stepping Motor                               | 11-46 |

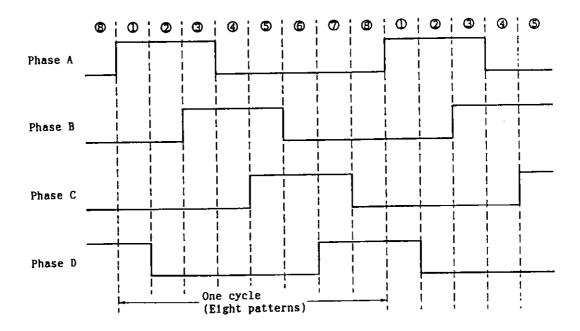

| 11-24 | 1-2 Phase Excitation of a 4-phase            |       |

|       | Stepping Motor                               | 11-47 |

| 11-25 | Example of Setting the Macro Service Mode    |       |

|       | Register for Automatic Addition Control Plus |       |

|       | Ring Control                                 |       |

|       | (1-2 Phase Excitation Uniform Motion)        | 11-49 |

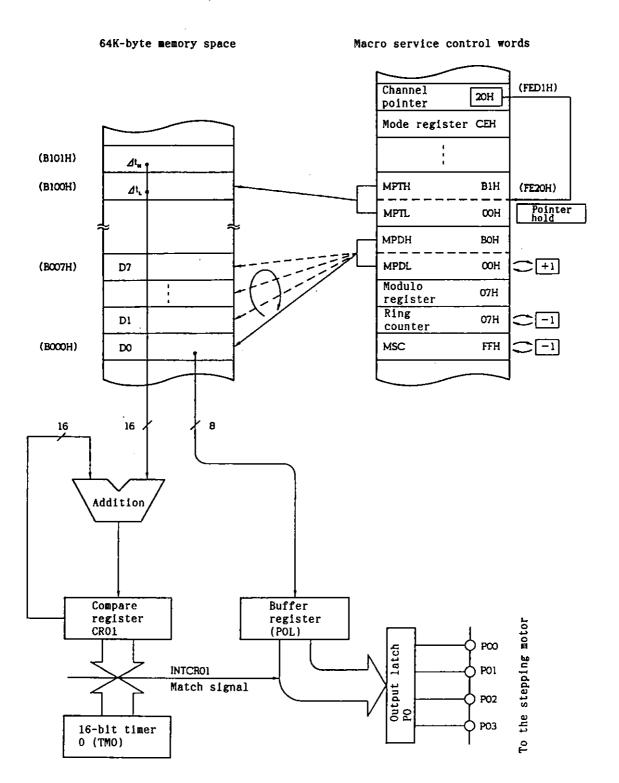

| 11-26 | Block Diagram for Automatic Addition Control |       |

|       | Plus Ring Control                            |       |

|       | (1-2 Phase Excitation Uniform Motion)        | 11-50 |

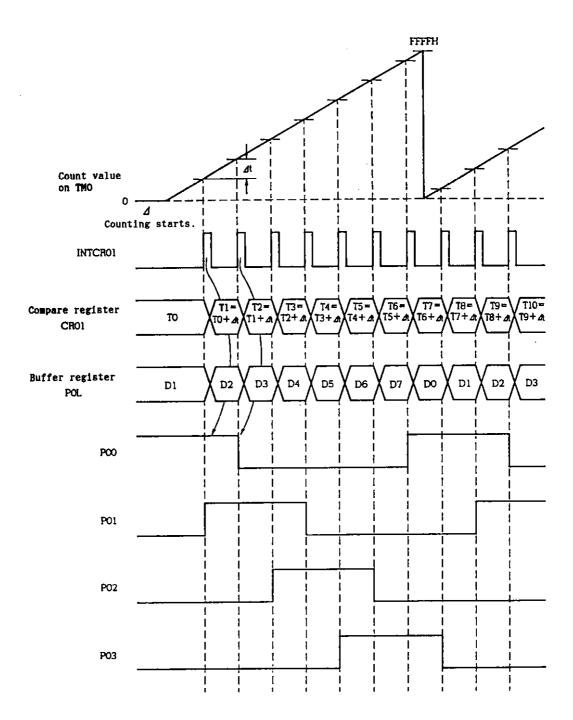

| 11-27 | Timing Diagram 1 for Automatic Addition      |       |

|       | Control Plus Ring Control                    |       |

|       | (1-2 Phase Excitation Uniform Motion)        | 11-51 |

| 11-28 | Example of Setting the Macro Service Mode    |       |

|       | Register for Automatic Addition Control Plus |       |

|       | Ring Control                                 |       |

|       | (2-phase Excitation at Varying Intervals)    | 11-52 |

| 11-29 | Block Diagram for Automatic Addition Control |       |

|       | Plus Ring Control                            |       |

|       | (2-phase Excitation at Varying Intervals)    | 11-53 |

| 11-30 | Timing Diagram 2 for Automatic Addition      |       |

|       | Control Plus Ring Control                    |       |

|       | (2-phase Excitation at Varying Intervals)    | 11-54 |

| 11-31 | Example of Macro Service Operation           | 11-55 |

| 11-32 | Example of a Counter Mode Operation          | 11-58 |

| 11-33 | Addressing in the Data Pattern               |       |

|       | Identification Mode                          | 11-60 |

| 11-34 | Note on Setting a Data Comparing Area        | 11-61 |

| 11-35 | Example of Setting the Macro Service Mode    |       |

|       | Register in the Data Pattern Identification  |       |

|       | Mode (with Comparison)                       | 11-63 |

| 11-36 | Example of an Application in the Data        |       |

|       | Pattern Identification Mode                  |       |

|       | (VCR Index Search Control)                   | 11-   |

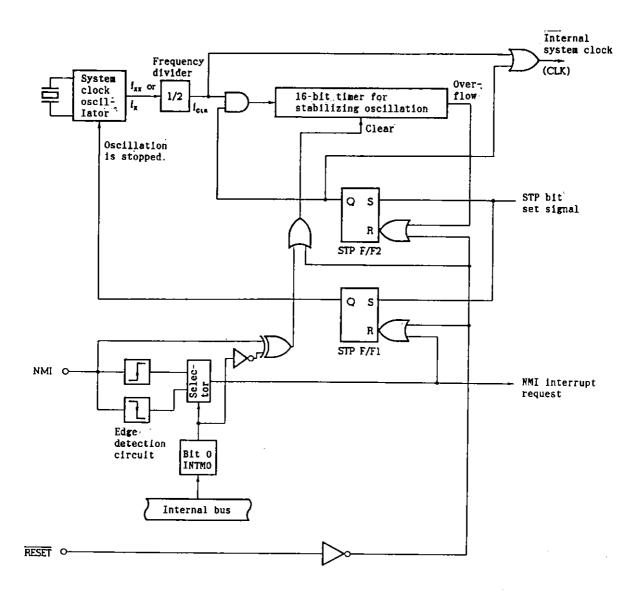

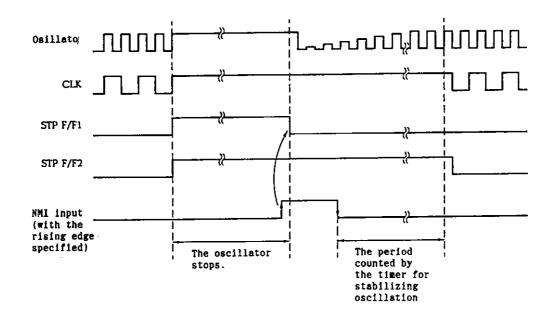

| 12-1  | Standby Status Transition                 | 12-1  |

|-------|-------------------------------------------|-------|

| 12-2  | Configuration of a Standby Function       |       |

|       | Control Circuit                           | 12-2  |

| 12-3  | Format of the Standby Control Register    |       |

|       | (STBC)                                    | 12-3  |

| 12-4  | Releasing the STOP Mode by NMI Input      | 12-5  |

|       |                                           |       |

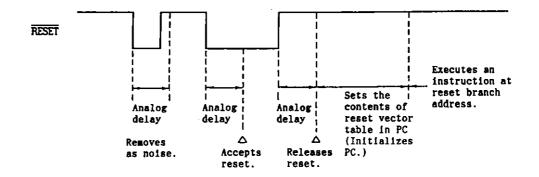

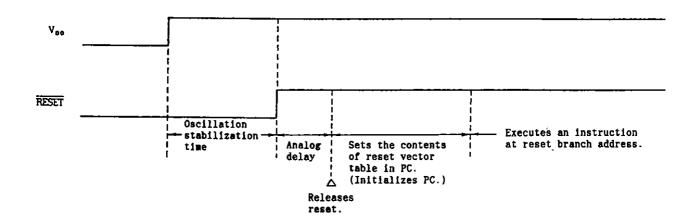

| 13-1  | Accepting a Reset Signal                  | 13-1  |

| 13-2  | Reset at Power-on                         | 13-2  |

|       |                                           |       |

| 14-1  | Example of Application to the Normal-type |       |

|       | Video Cassette Recorder                   | 14-2  |

| 14-2  | Example of Application to the Camcoder    | 14-4  |

| 14-3  | Using the Super Timer Unit in the VCR     |       |

|       | Servo System                              | 14-6  |

| 14-4  | Controlling the Drum Motor                | 14-9  |

| 14-5  | Drum Speed Control                        | 14-10 |

| 14-6  | Drum Phase Control                        | 14-11 |

| 14-7  | Controlling the Capstan Motor             | 14-14 |

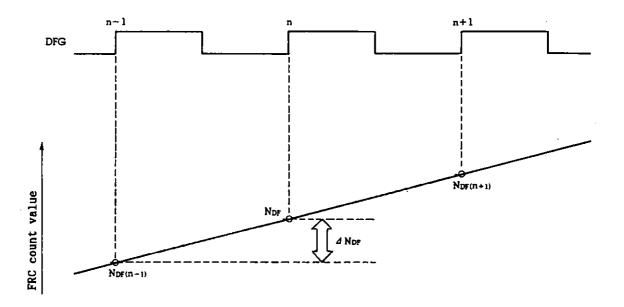

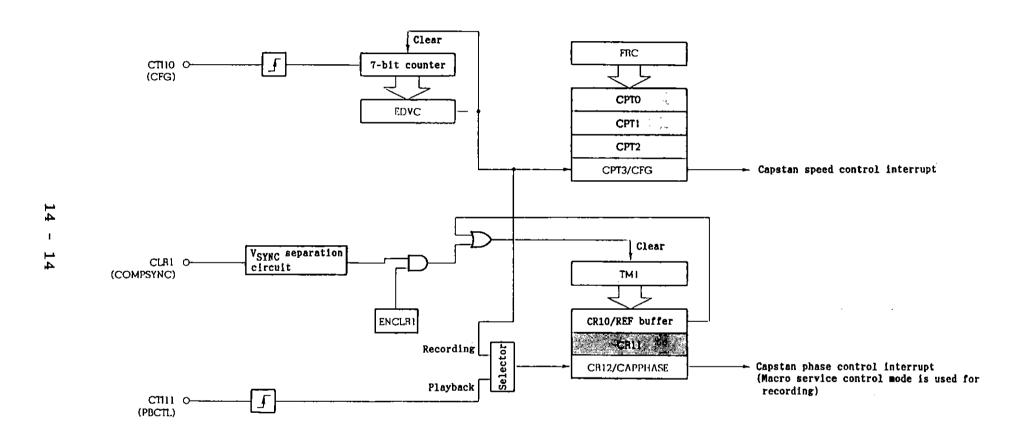

| 14-8  | Capstan Speed Control                     | 14-15 |

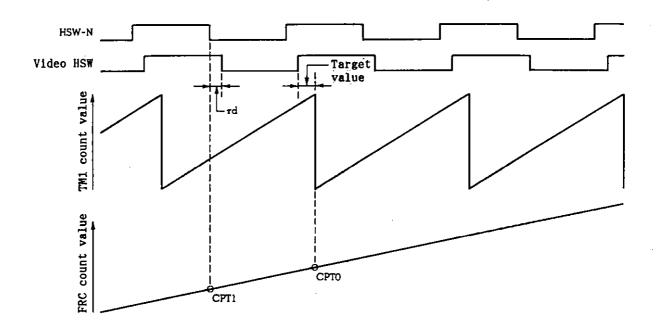

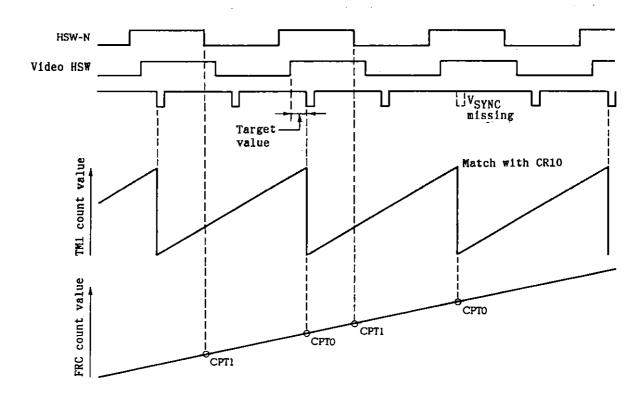

| 14-9  | Capstan Phase Control                     | 14-16 |

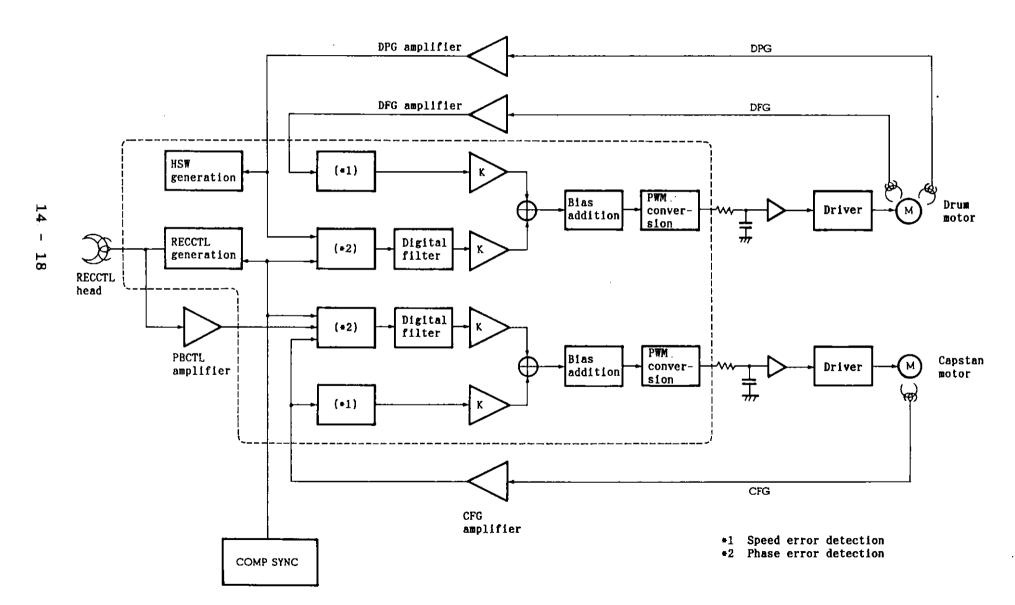

| 14-10 | Block Diagram of the VCR Servo System     | 14-18 |

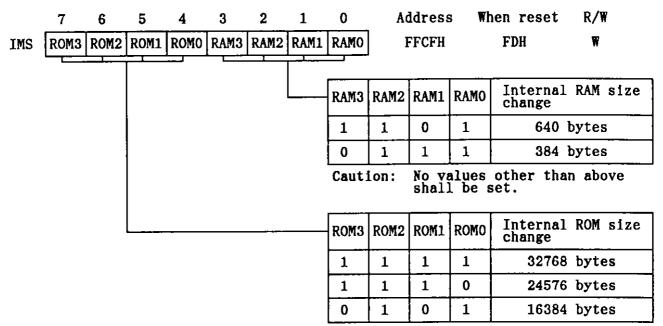

| 15-1  | Format of the Internal Memory Size Change |       |

|       | Register (IMS)                            | 15-4  |

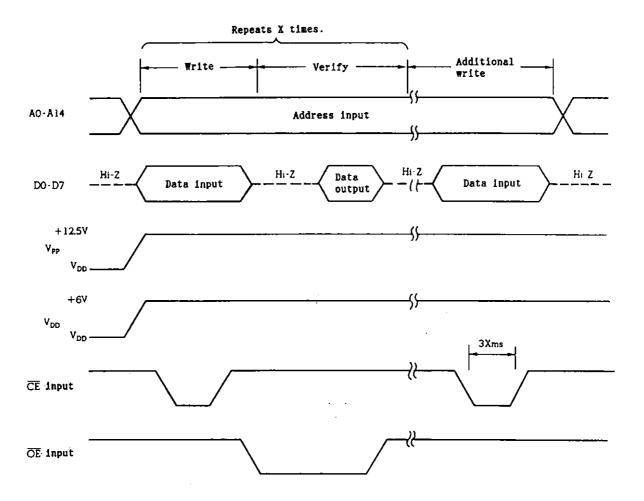

| 15-2  | PROM Write/Verify Timing Chart            | 15-7  |

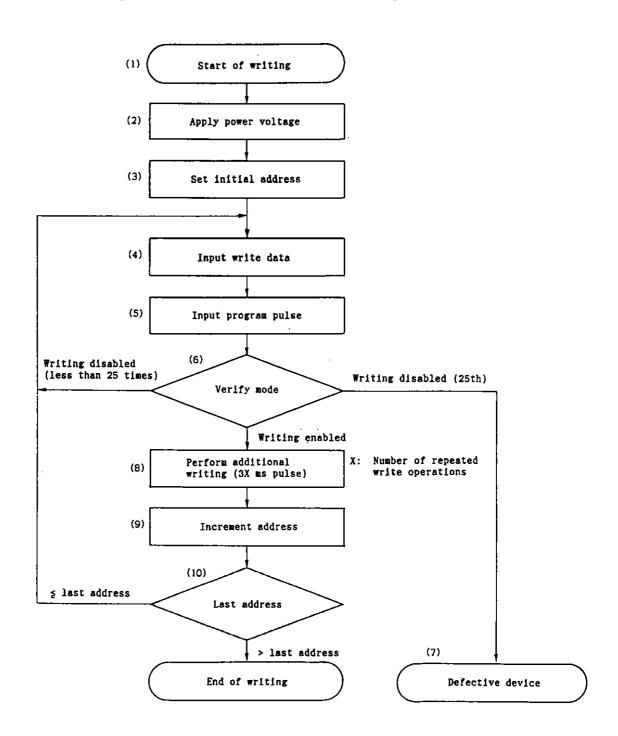

| 15-3  | Flowchart of Writing Procedure            | 15-8  |

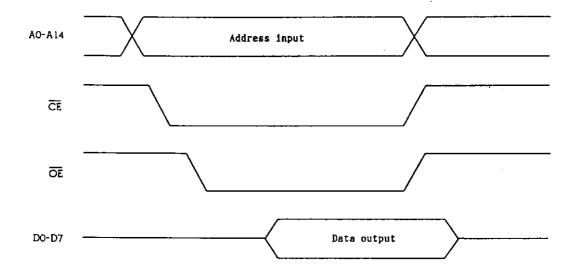

| 15-4  | PROM Read Timing Chart                    | 15-9  |

#### LIST OF TABLES

| Table | Title                                          | Page |

|-------|------------------------------------------------|------|

| 1-1   | Main Differences between the Products          | 1-1  |

| 1-2   | Functions                                      | 1-11 |

| 2-1   | Port 2 Dual-function Pins                      | 2-7  |

| 2-2   | Port 3 Modes                                   | 2-12 |

| 2-3   | Port 6 Operation Modes                         | 2-15 |

| 2-4   | I/O Circuit Type of Each Pin and Connection of |      |

|       | Unused Pins                                    | 2-21 |

| 3-1   | Memory Areas of Each Product                   | 3-1  |

| 3-2   | Vector Table                                   | 3-6  |

| 3-3   | ISP Flag Format                                | 3-13 |

| 3-4   | Specification of a Register Bank               | 3-14 |

| 3-5   | Correspondence between Function Names and      |      |

|       | Absolute Names                                 | 3-18 |

| 3-6   | Special Function Registers (SFRs)              | 3-21 |

| 3-7   | External Expansion Modes and Pin Functions     | 3-28 |

| 5-1   | Port Functions                                 | 5-2  |

| 5-2   | Function of Port 0                             | 5-4  |

| 5-3   | Functions of Port 1                            | 5-7  |

| 5-4   | Functions of Port 2                            | 5-12 |

| 5-5   | Functions of Port 3                            | 5-16 |

| 5-6   | Functions of Port 4                            | 5-26 |

| 5-7   | Functions of Port 5                            | 5-31 |

| 5-8   | Functions of Port 6                            | 5-36 |

| 5-9   | Functions of Port 7                            | 5-42 |

| 6-1   | Output Trigger for Real-time Output Port       |      |

|       | (When RTPC POMH = POML = 1)                    | 6-6  |

| <b>Phase-out/Discontinued</b> |

|-------------------------------|

|                               |

| 7-1  | Read/Write Operation of SBIC Register         | 7-7   |

|------|-----------------------------------------------|-------|

| 7-2  | Various Signals Used in SBI Mode              | 7-38  |

| 7-3  | Conditions for Clearing BUSY                  | 7-48  |

| 8-1  | Components of the Super Timer Unit            | 8-2   |

| 8-2  | Resolution and Maximum Count Time of Each     |       |

|      | Timer (at 12 MHz)                             | 8-8   |

| 8-3  | Resolution and Maximum Count Time of Timer 0  | 8-17  |

| 8-4  | Timer 0 Output Pins and Output Modes that     |       |

|      | can be Set                                    | 8-21  |

| 8-5  | TOMO Setting Values and Output Modes of       |       |

|      | Timer 0 Outputs                               | 8-21  |

| 8-6  | Resolution of Timer 1 (at 12 MHz)             | 8-45  |

| 8-7  | Digital Noise Eliminator Specification        | 8-51  |

| 8-8  | FRC Capture Registers and Capture Triggers    | 8-74  |

| 8-9  | Resolution of the FRC (at 12 MHz)             | 8-79  |

| 8-10 | Resolution of Timer 2 (at 12 MHz)             | 8-92  |

| 9-1  | Mode Generating INTAD                         | 9-2   |

| 9-2  | Conditions for Generating Interrupt Requests  |       |

|      | in Different A/D Converter Operating States   | 9-15  |

| 11-1 | Interrupt Request Processing Modes            | 11-1  |

| 11-2 | Interrupt Request Sources                     | 11-2  |

| 11-3 | Valid Edges and Control Registers of External |       |

|      | Interrupt Pins                                | 11-6  |

| 11-4 | Flags Corresponding to Each Interrupt         |       |

|      | Request Source                                | 11-9  |

| 11-5 | Multiple Interrupt Processing                 | 11-17 |

| 11-6 | Macro Service Modes and Interrupt             |       |

|      | Request Sources                               | 11-27 |

| 11-7 | Interrupt Requests Sources in the Data        |       |

|      | Transfer Mode and SFR                         | 11-28 |

| 11-8 | Functions of the Macro Service Pointers       |       |

| 11-9 | M. a                                          | 11_69 |

| 11-10 | Address Ranges that cannot be Used by the Macro Service Function | 11-69 |

|-------|------------------------------------------------------------------|-------|

| 12-1  | Operation States in the STOP Mode                                | 12-4  |

| 13-1  | Hardware Statuses after Reset                                    | 13-2  |

| 14-1  | Timer Functions in the VCR Servo System                          | 14-5  |

| 15-1  | Differences of uPD78P138 from uPD78134A, uPD78136, and uPD78138  | 15-2  |

| 15-2  | Operation Mode when Programming on the PROM                      | 15-5  |

#### CHAPTER 1 GENERAL

The uPD78138 is an 8-bit single-chip microcomputer. It contains a high-speed, high-performance 8-bit CPU.

With on-chip peripheral hardware, the uPD78138 can be used in VCRs and other devices that require digital servo control via the software.

By mass-storage built-in ROM, the uPD78138 can support system control on one chip in addition to servo control, thus further miniaturizing the application set.

The uPD78P138 with the PROM is also provided, which is suited for evaluation and trial manufacture during system development, early stage start-up of applications, and short-run and multiple-device production.

The EPROM versions of the uPD78P138 are not intended for use in mass-produced products; they do not have reliability high enough for such purposes. Their use should be restricted to functional evaluation in experiment or trial manufacture.

Table 1-1 Main Differences between the Products

| Product   | ROM         | RAM       | ROM type            |

|-----------|-------------|-----------|---------------------|

| uPD78134A | 16K bytes   | 384 bytes |                     |

| uPD78136  | 24K bytes   | CAO bytos | Mask ROM            |

| uPD78138  | 00V harton  | 640 bytes |                     |

| uPD78P138 | - 32K bytes |           | One-time PROM/EPROM |

#### 1.1 Features

- o High-speed instruction execution via internal multiplexed bus: 0.33 us (at 12 MHz)

- o Built-in super timer unit that best suits VCR servo control

- . Speed and phase control of drums, capstans, and motors

- . Head switch signal output of two channels including audio and video

- . Vertical synchronizing signal detection function

- . Input pulse duty ratio determining function

- . Built-in two-channel PWM output circuit that can specify active levels

- o Additional functions that improve responsibility of servo control

- . Signed multiply instruction

- . Variable PWM output carrier frequency (23.4/46.9 kHz)

- o Built-in real-time output port that can vary output patterns at any interval. (Suited for outputting the VCR head switch and controlling a step motor.)

- o Powerful interrupt functions providing two service modes

- . Vector interrupt function

- . Macro service function (Facilitates automatic data transfer and AMSS function on VCRs.)

- o Built-in pull-up resistor eliminating the need for external resistors

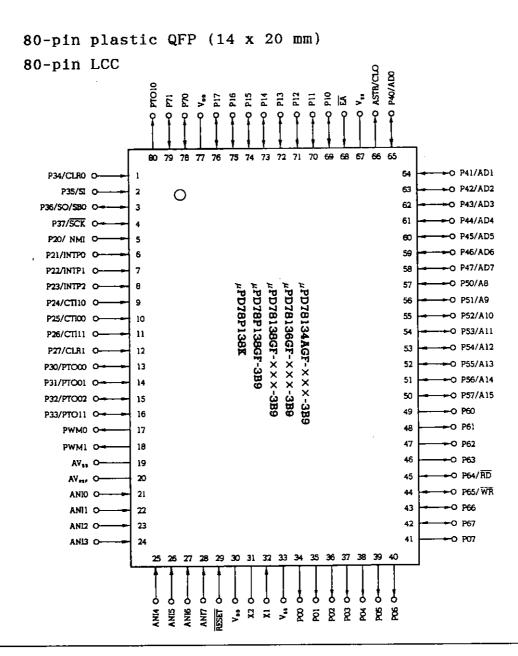

- o 80-pin plastic QFP (14 mm x 20 mm)

#### 1.2 Applications

The uPD78138 applies to servo controlling of VCRs (normal type and camcorder type), HDDs, FDDs, DATs, and CDPs.

VCR: Video Cassette Recorder

HDD: Hard Disc Drive

FDD: Floppy Disk Drive

DAT: Digital Audio Tape Recorder

CDP: Compact Disc Player

#### 1.3 Ordering Information and Quality Grade Standard

#### (1) Ordering information

| Part number         | Package                         | On-chip ROM   |

|---------------------|---------------------------------|---------------|

| uPD78134AGF-xxx-3B9 | 80-pin plastic QFP (14 x 20 mm) | Mask ROM      |

| uPD78136GF-xxx-3B9  | 80-pin plastic QFP (14 x 20 mm) | Mask ROM      |

| uPD78138GF-xxx-3B9  | 80-pin plastic QFP (14 x 20 mm) | Mask ROM      |

| uPD78P138GF-3B9     | 80-pin plastic QFP (14 x 20 mm) | One-time PROM |

| uPD78P138K          | 80-pin LCC                      | EPROM         |

Remark: xxx is a ROM code.

#### (2) Quality grade

| Part number         | Package                         | On-chip ROM |

|---------------------|---------------------------------|-------------|

| uPD78134AGF-xxx-3B9 | 80-pin plastic QFP (14 x 20 mm) | Standard    |

| uPD78136GF-xxx-3B9  | 80-pin plastic QFP (14 x 20 mm) | Standard    |

| uPD78138GF-xxx-3B9  | 80-pin plastic QFP (14 x 20 mm) | Standard    |

| uPD78P138GF-3B9     | 80-pin plastic QFP (14 x 20 mm) | Standard    |

| uPD78P138K          | 80-pin LCC                      | Not applied |

Please refer to "Quality Grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

#### 1.4 Functional Overview

| Item                               | Function                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of basic instructions       | 64                                                                                                                                                                                                                                                                                                                                                |  |

| Minimum instruction execution time | 0.33 us (at 12 MHz)                                                                                                                                                                                                                                                                                                                               |  |

| Internal memory                    | . Program memory: 16256 x 8 bits (mask ROM, uPD78134A) 24576 x 8 bits (mask ROM, uPD78136) 32768 x 8 bits (mask ROM, uPD78138) 32768 x 8 bits (PROM, uPD78P138) . Data memory: 384 x 8 bits (uPD78134A), 640 x 8 bits                                                                                                                             |  |

| Memory expansion                   | Externally expandable up to 64K bytes                                                                                                                                                                                                                                                                                                             |  |

| General register                   | 8 bits x 8 x 4 banks (memory mapping)                                                                                                                                                                                                                                                                                                             |  |

| Instruction set                    | <ul> <li>16-bit addition, subtraction, comparison</li> <li>Signed multiply instruction (signed 16 bits x unsigned 8 bits)</li> <li>Unsigned multiply/divide instruction (16 bits x 8 bits, 16 bits ÷ 8 bits)</li> <li>Bit manipulation instruction (transfer, Boolean operation, set, reset, test)</li> <li>BCD correction instruction</li> </ul> |  |

| I/O line                           | . 66 total Input port: 10 Output port: 12 I/O port: 36 Analog input: 8                                                                                                                                                                                                                                                                            |  |

| Super timer unit                   | . Timer:  16 bits x 3  7 bits x 1  Counter:  18 bits x 1  Capture register: 18 bits x 1  16 bits x 4  7 bits x 1  Compare register: 16 bits x 6  7 bits x 1  PWM output:  12 bits x 2  (variable active level, variable carrier frequency (23.4/46.9 kHz))                                                                                        |  |

(to be continued)

(Cont'd)

| Item                  | Function                                                                                                                                                                |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Real-time output port | . Timer-connected port output function . 4 bits x 2 or 8 bits x 1                                                                                                       |  |

| Serial interface      | . Either NEC format serial bus interface (SBI) or 3-wire serial interface can be selected.                                                                              |  |

| A/D converter         | . 8-bit resolution x 8 inputs . Conversion time: 30 us/1 analog input (at 12 MHz)                                                                                       |  |

| Interrupt             | . Interrupt source: 17 (5 external and 12 internal) . One of the two service modes can be selected (macro service/vector interrupt) Variable 2-level interrupt priority |  |

| Standby               | STOP mode                                                                                                                                                               |  |

| Pull-up resistor      | 44, built-in (Enable/disable built-in can be specified via software.)                                                                                                   |  |

# Phase-out/Discontinued

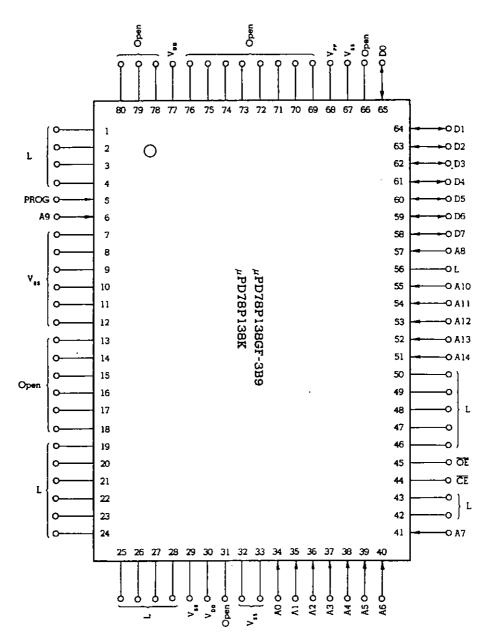

\*1 uPD78134A: 16K x 8 (mask ROM) uPD78136: 24K x 8 (mask ROM), uPD78138: 32K x 8 (mask ROM),

uPD78P138: 32K x 8 (PROM)

$\bullet 2$   $V_{pp}$  is a positive power supply pin for PROM and is only available on the uPD78P138.

\*3 uPD78134A: 128 x 8 bits, uPD78136, uPD78138, and uPD78P138: 384 x 8 bits

- 1.6 Pin Configuration (Top View)

- 1.6.1 Normal operation mode (uPD78134A, uPD78136, uPD78138, and uPD78P138)

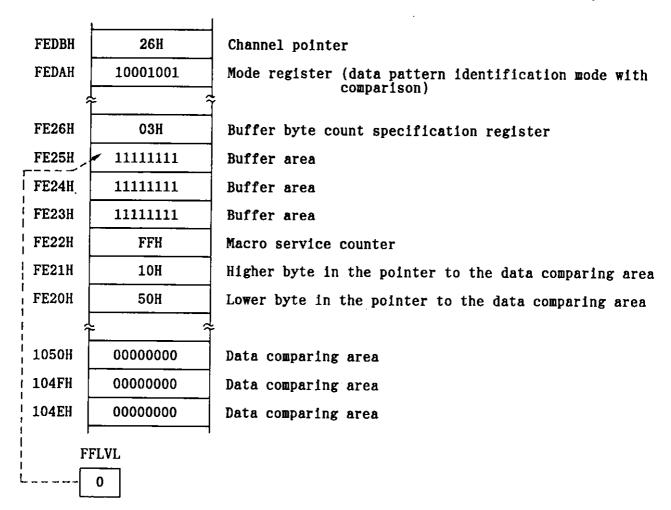

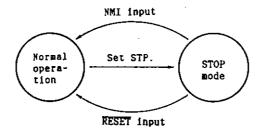

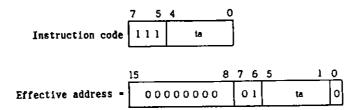

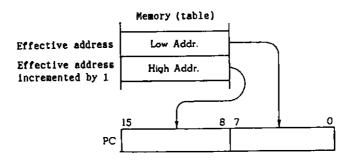

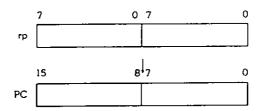

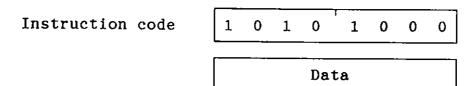

The EPROM versions of the uPD78P138 are not intended for use in mass-produced products; they do not have reliability high enough for such purposes. Their use should be restricted to functional evaluation in experiment or trial manufacture.