## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# SH7731

ハードウェアマニュアル ルネサス 32 ビット RISC マイクロコンピュータ SH7780 シリーズ

R8A7731

#### ■ 本資料ご利用に際しての留意事項。

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報 の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負い ません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行うもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10.弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が 発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作 が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において 冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウェアおよびソフトウェ ア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システム としての安全検証をお願いいたします。

- 11.本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の 事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、 お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故に つきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断りいたします。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会ください。

### 製品に関する一般的注意事項

#### 1. NC 端子の処理

【注意】NC端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC端子には、何も接続しないようにしてください。

2. 未使用入力端子の処理

【注意】未使用の入力端子は、ハイまたはローレベルに固定してください。

CMOS製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。

未使用の入力端子は、入力をプルアップかプルダウンによって、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は、製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は 不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシ ステムが誤動作を起こさないようにシステム設計を行ってください。

リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられて います

これらのレジスタをアクセスしたときの動作および継続する動作については、保証できませんので、アクセスしないようにしてください。

5. 各レジスタリザーブビットの読み出し/書き込み

各モジュールで使用されるレジスタのリザーブビットは、その説明記述中に読み出し/書き込み値の指定が特にない限り以下のように取り扱ってください。

読み出すと常に0が読み出されます。書き込む場合は、0を書き込むか、直前に読み出した値を書き込むかいずれかにしてください。

直前に読み出した値を書き込むようにしておくと、将来このビットに拡張機能を割り当てることがある場合、その拡張機能に影響を与えない利点があります。

# 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品に関する一般的注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- ・CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュール毎に異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認の上設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください(使用上の注意事項は必要により記載されます)。

- 7. レジスター覧

- 8. 電気的特性

- 9. 付録

- 10. 本版で改訂された箇所(改訂版のみ適用)

改定来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改定内容の全てについて記載したものではありませんので、詳細については、本書の本文上で ご確認ください。

11. 索引

# はじめに

本 LSI は、ルネサス テクノロジオリジナルの RISC 方式の CPU をコアにして、システム構成に必要な周辺機能を集積した RISC マイコンです。本 LSI は、SH4AL-DSP 拡張機能を備えており、SH4AL-DSP に対して機能的に上位互換です。

対象者 本マニュアルは、本 LSI を用いた応用システムを設計するユーザを対象としています。

本マニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する 基本的な知識を必要とします。

目的 本マニュアルは、本 LSI のハードウェア機能と電気的特性をユーザに理解していただくことを目的 としています。

#### 読み方

• 機能全体を理解しようとするとき

目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• SH4AL-DSP拡張機能の各命令の詳細を理解したいとき

別冊の「SH4AL-DSP拡張機能 ソフトウェアマニュアル」を参照してください。

#### 【凡例】

レジスタ表記: シリアルコミュニケーションなど、同一または類似した機能が複数チャネルに存在する

場合に、次の表記を使用します。

XXX\_N (XXX は基本レジスタ名称、N はチャネル番号)

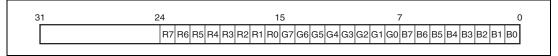

ビット表記: 左側が上位ビット、右側が下位ビットの順に表記します。

数字の表記: 2 進数は B'XXXX、16 進数は H'XXXX、10 進数は XXXX で表します。

記号の表記: ローアクティブの信号にはオーババー(XXXX)を付けます。

### 【略語の説明】

| ALU   | Arithmetic Logic Unit           |

|-------|---------------------------------|

|       | 演算論理回路                          |

| ASID  | Address Space Identifier        |

|       | アドレス空間識別子                       |

| BSC   | Bus State Controller            |

|       | バスステートコントローラ                    |

| CMT   | Compare Match Timer             |

|       | コンペアマッチタイマ                      |

| CPG   | Clock Pulse Generator           |

|       | クロックパルス発生器                      |

| CPU   | Central Processing Unit         |

|       | 中央制御装置                          |

| DMA   | Direct Memory Access            |

|       | ダイレクトメモリアクセス                    |

| DMAC  | Direct Memory Access Controller |

|       | ダイレクトメモリアクセスコントローラ              |

| DSP   | Digital Signal Processor        |

|       | デジタルシグナルプロセッサ                   |

| ETU   | Elementary time unit            |

|       | 1 ビットの転送時間                      |

| FIFO  | First-In First-Out              |

|       | 先入れ先出し                          |

| H-UDI | User Debugging Interface        |

|       | ユーザデバッグインタフェース                  |

| IIC   | Inter IC bus                    |

|       | I2C バス                          |

| INTC  | Interrupt Controller            |

|       | 割り込みコントローラ                      |

| IrDA  | Infrared Data Association       |

|       | 赤外線通信の規格名称                      |

| JTAG  | Joint Test Action Group         |

|       | バウンダリスキャン規格化 Gr                 |

| KEYSC | Keyscan Interface               |

|       | キースキャンインタフェース                   |

| LCDC  | LCD Controller                  |

LCD コントローラ

LRU Least Recently Used

(仮想記憶ページ置き換えアルゴリズムの名前)

LSB Least Significant Bit

最下位ビット

MMC Multi Media Card

マルチメディアカード

MMU Memory Management Unit

メモリマネジメントユニット

MSB Most Significant Bit

最上位ビット

PC Program Counter

プログラムカウンタ

PFC Pin Function Controller

ピンファンクションコントローラ

RISC Reduced Instruction Set Computer

縮小命令セットコンピュータ

RWDT RCLK Watch Dog Timer

RCLK ウォッチドッグタイマ

SBSC SDRAM Bus State Controller

SDRAM 用バスステートコントローラ

SCIF Serial Communication Interface with FIFO

FIFO 内蔵シリアルコミュニケーションインタフェース

SDHI SD Card Host Interface

SD カードホストインタフェース

SIM Smart Card Interface Module

スマートカードインタフェースモジュール

SIO Serial Interface

シリアル I/O

SIOF Serial Interface with FIFO

シリアル I/O FIFO 付き

TAP Test Access Port

テスト端子

TLB Translation Lookaside Buffer

変換ルックアサイドバッファ

TMU Timer Unit

タイマユニット

TPU Timer Pulse Unit

タイマパルスユニット

UART Universal Asynchronous Receiver/Transmitter

調歩同期インタフェース

UBC User Break Controller

ユーザブレークコントローラ

USB Universal Serial Bus

ユニバーサルシリアルバス

### 【登録商標・商標】

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 目次

| 1. 概  | 要                 | 1 1  |

|-------|-------------------|------|

|       |                   |      |

| 1.1   | 特長                |      |

| 1.2   | プロック図             |      |

| 1.3   | ピン配置図             |      |

| 1.3.1 |                   |      |

| 1.3.2 |                   |      |

| 1.4   | 端子の機能             | 1-35 |

| 2. プ  | ログラミングモデル         | 2-1  |

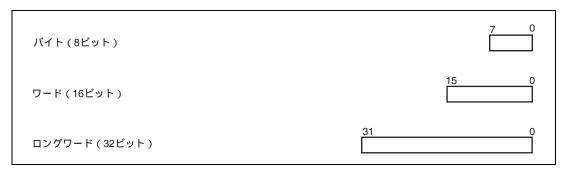

| 2.1   | データフォーマット         | 2-1  |

| 2.2   | レジスタの構成           | 2-1  |

| 2.2.1 | 特権モードとレジスタバンク     | 2-1  |

| 2.2.2 | 汎用レジスタ            | 2-5  |

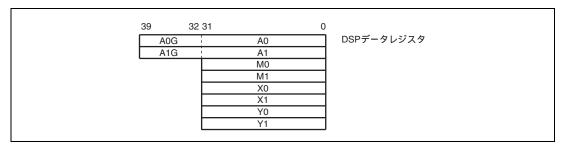

| 2.2.3 | DSP レジスタ          | 2-6  |

| 2.2.4 | コントロールレジスタ        | 2-6  |

| 2.2.5 | システムレジスタ          | 2-11 |

| 2.3   | メモリ割り付けレジスタ       | 2-15 |

| 2.4   | レジスタのデータ形式        | 2-15 |

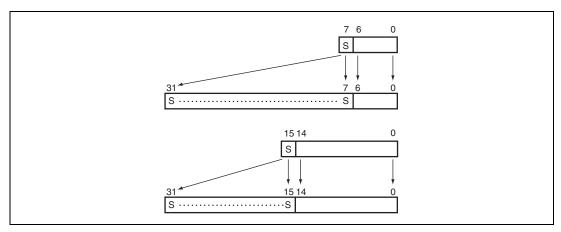

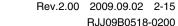

| 2.5   | メモリ上でのデータ形式       | 2-16 |

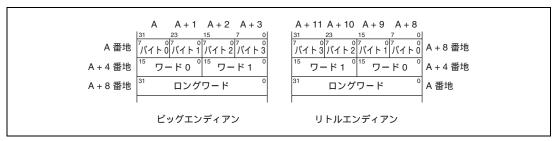

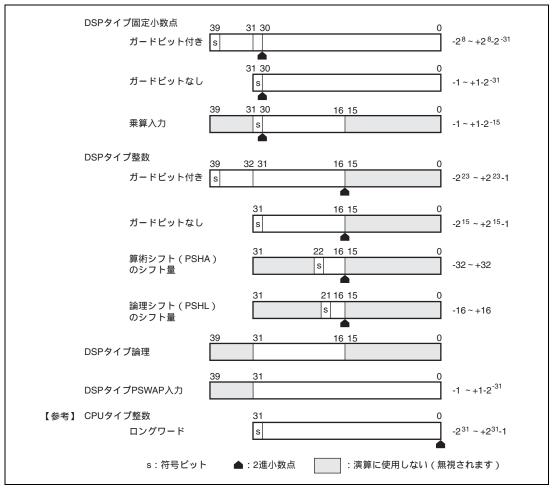

| 2.6   | DSPタイプデータ形式       | 2-16 |

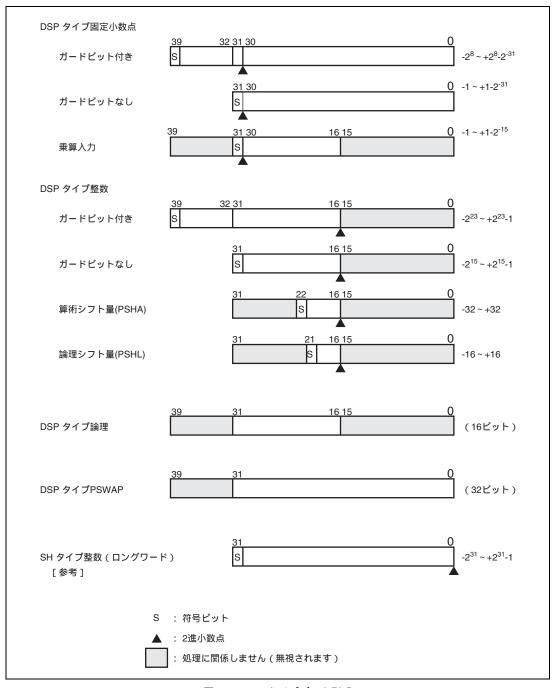

| 2.7   | 処理状態              | 2-18 |

| 2.8   | 使用上の注意事項          | 2-19 |

| 2.8.1 | 自己書き換えコードに対する注意事項 | 2-19 |

| 3. 命· | 令セット              | 3-1  |

| 3.1   | 実行環境              | 3-1  |

| 3.2   | アドレッシングモード        | 3-3  |

| 3.2.1 | CPU アドレッシングモード    | 3-3  |

| 3.2.2 | DSP データアドレッシング    | 3-6  |

| 3.2.3 |                   |      |

| 3.2.4 | シングルデータアドレッシング    | 3-8  |

| 3.2.5 |                   |      |

| 3.2.6 |                   |      |

| 3.3   | 命令セット             |      |

| 3.4   | DSPデータ転送命令の命令セット          | 3-22 |

|-------|---------------------------|------|

| 3.4.1 | ダブルデータ転送命令                | 3-22 |

| 3.5   | DSP演算命令の命令セット             | 3-27 |

| 3.5.1 | NOPX と NOPY の命令コード        | 3-38 |

| 4. パー | イプライン動作                   | 4-1  |

| 4.1   | パイプライン                    | 4-1  |

| 4.2   | 並列実行性                     | 4-10 |

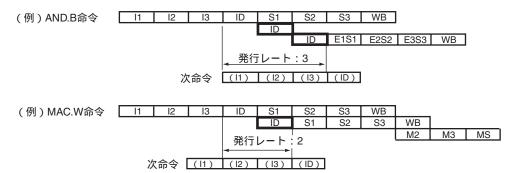

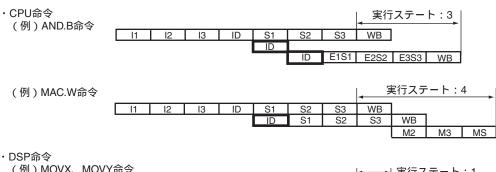

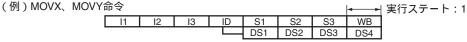

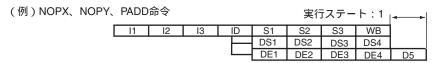

| 4.3   | 発行レートと実行ステート              | 4-12 |

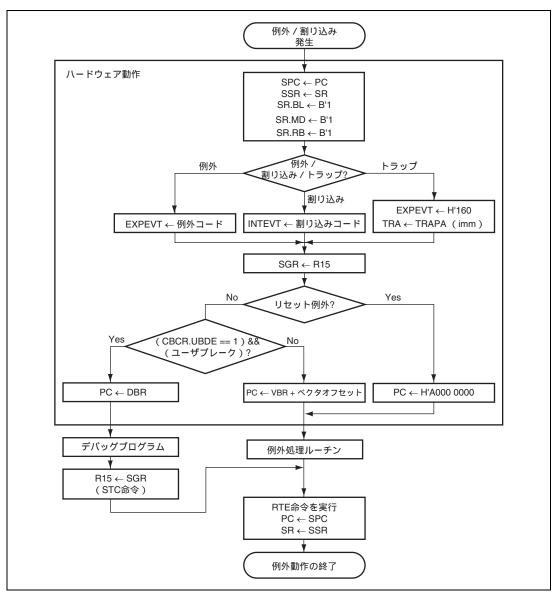

| 5. 例约 | 外処理                       | 5-1  |

| 5.1   | 概要                        | 5-1  |

| 5.2   | レジスタの説明                   | 5-1  |

| 5.2.1 | TRAPA 例外レジスタ(TRA)         | 5-2  |

| 5.2.2 | 例外事象レジスタ(EXPEVT)          | 5-3  |

| 5.2.3 | 割り込み事象レジスタ(INTEVT)        | 5-3  |

| 5.2.4 | 非サポート検出例外レジスタ ( EXPMASK ) | 5-4  |

| 5.3   | 例外処理の機能                   | 5-6  |

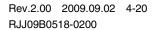

| 5.3.1 | 例外処理の流れ                   | 5-6  |

| 5.3.2 | 例外処理ベクタアドレス               | 5-6  |

| 5.4   | 例外の種類と優先順位                | 5-7  |

| 5.5   | 例外フロー                     | 5-8  |

| 5.5.1 | 例外フロー                     | 5-8  |

| 5.5.2 | 例外要因の受け付け                 | 5-9  |

| 5.5.3 | 例外要求と BL ビット              | 5-10 |

| 5.5.4 | 例外処理からの復帰                 | 5-10 |

| 5.6   | 各例外の説明                    | 5-11 |

| 5.6.1 | リセット                      | 5-11 |

| 5.6.2 | 一般例外                      | 5-12 |

| 5.6.3 | 互換リピート制御中の例外処理            | 5-22 |

| 5.6.4 | 拡張リピート制御中の例外処理            | 5-23 |

| 5.6.5 | 割り込み                      | 5-23 |

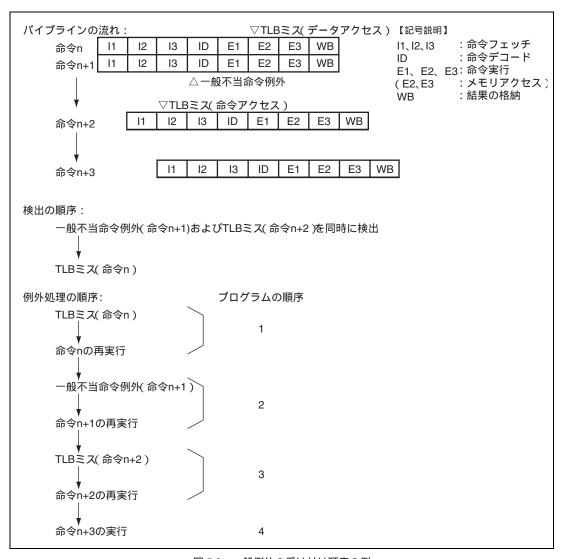

| 5.6.6 | 複数回の例外が発生する場合の優先順位        | 5-25 |

| 5.7   | 注意事項                      | 5-26 |

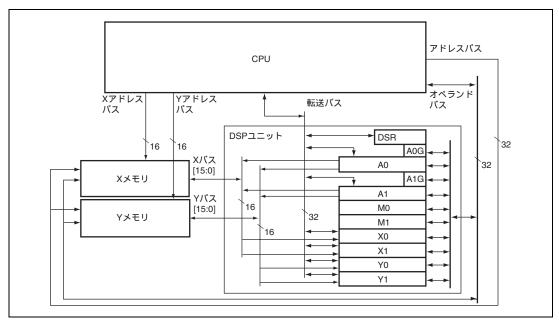

| 6. DS | SP ユニット                   | 6-1  |

| 6.1   | 概要                        | 6-1  |

| 6.2   | DSPモードのリソース               | 6-3  |

| 6.2.1 | 処理モード                     | 6-3  |

| 6.2.2 | DSP モードのメモリマップ            | 6-3  |

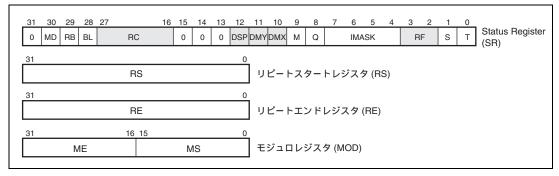

| 6.2.3  | CPU のレジスタセット                | 6-4  |

|--------|-----------------------------|------|

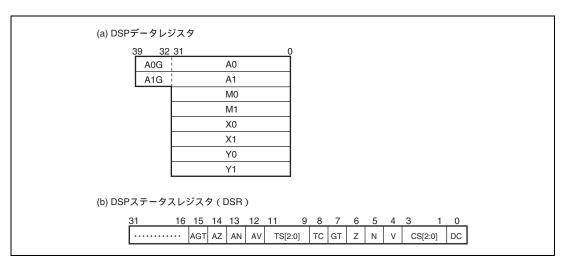

| 6.2.4  | DSP レジスタ                    | 6-7  |

| 6.3    | CPU拡張命令                     | 6-8  |

| 6.3.1  | 互換リピート制御命令                  | 6-8  |

| 6.3.2  | 拡張リピート制御命令                  | 6-16 |

| 6.4    | DSPデータ転送命令                  | 6-19 |

| 6.4.1  | 汎用レジスタ                      | 6-22 |

| 6.4.2  | DSP データアドレッシング              | 6-24 |

| 6.4.3  | モジュロアドレッシング                 | 6-26 |

| 6.4.4  | メモリのデータ形式                   | 6-28 |

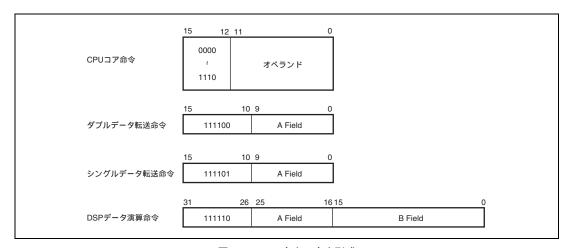

| 6.4.5  | ダブル、シングルデータ転送命令の命令フォーマット    | 6-28 |

| 6.5    | DSPデータ演算命令                  | 6-30 |

| 6.5.1  | DSP レジスタ                    | 6-30 |

| 6.5.2  | DSP データ演算命令の命令セット           | 6-36 |

| 6.5.3  | SP タイプデータ形式                 | 6-39 |

| 6.5.4  | ALU 固定小数点算術演算               | 6-40 |

| 6.5.5  | ALU 整数演算                    | 6-45 |

| 6.5.6  | ALU 論理演算                    | 6-46 |

| 6.5.7  | 固定小数点乗算                     | 6-48 |

| 6.5.8  | シフト演算                       | 6-49 |

| 6.5.9  | MSB 検出命令                    | 6-52 |

| 6.5.10 | 丸め演算                        | 6-55 |

| 6.5.11 | スワップ命令                      | 6-56 |

| 6.5.12 | オーバフロー防止機能                  | 6-58 |

| 6.5.13 | ローカルデータ移動命令                 | 6-59 |

| 6.5.14 | 並行処理命令の命令フォーマット             | 6-60 |

| 6.5.15 | オペランドの競合                    | 6-64 |

| 6.5.16 | プログラミング上の注意                 | 6-65 |

| 7.     | Eリマネジメントユニット(MMU)           | 7-1  |

| 7.1    | MMUの概要                      | 7-1  |

| 7.1.1  | アドレス空間                      | 7-3  |

| 7.2    | レジスタの説明                     | 7-8  |

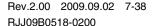

| 7.2.1  | ページテーブルエントリ上位レジスタ(PTEH)     | 7-9  |

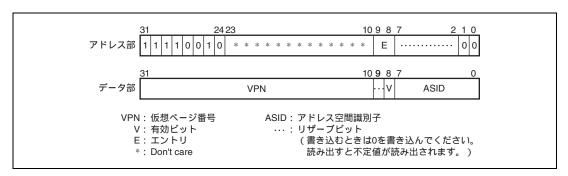

| 7.2.2  | ページテーブルエントリ下位レジスタ(PTEL)     | 7-10 |

| 7.2.3  | 変換テーブルベースレジスタ ( TTB )       |      |

| 7.2.4  | TLB 例外アドレスレジスタ(TEA)         |      |

| 7.2.5  | MMU 制御レジスタ ( MMUCR )        |      |

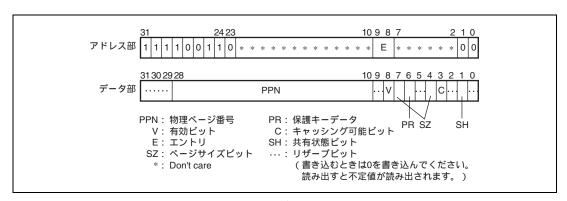

| 7.2.6  | ページテーブルエントリアシスタンスレジスタ(PTEA) |      |

| 7.2.7  | 物理アドレス空間制御レジスタ ( PASCR )    | 7-15 |

| 7.2.8 | 命令再フェッチ抑止制御レジスタ(IRMCR) | 7-16 |

|-------|------------------------|------|

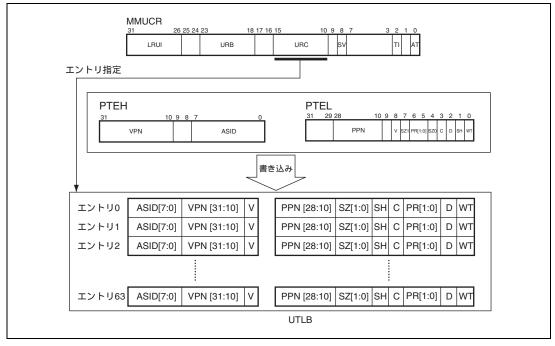

| 7.3   | TLBの機能(TLB互換モード)       | 7-18 |

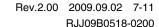

| 7.3.1 | 共用 TLB(UTLB)の構成        | 7-18 |

| 7.3.2 | 命令 TLB ( ITLB ) の構成    | 7-20 |

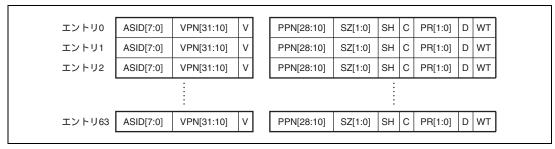

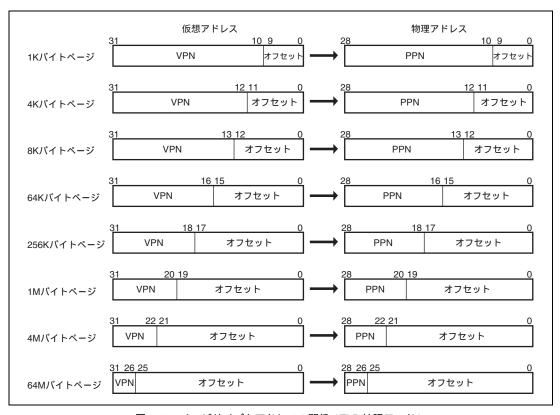

| 7.3.3 | アドレス変換方式               | 7-21 |

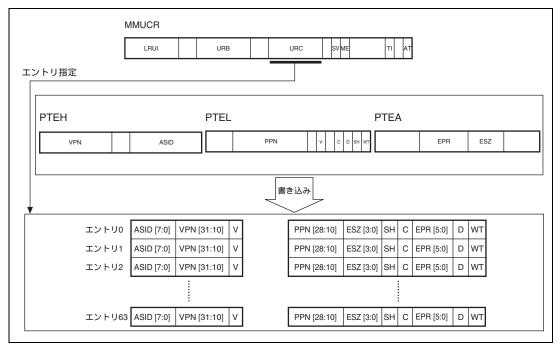

| 7.4   | TLBの機能 (TLB拡張モード)      | 7-23 |

| 7.4.1 | 共用 TLB(UTLB)の構成        | 7-23 |

| 7.4.2 | 命令 TLB ( ITLB ) の構成    | 7-26 |

| 7.4.3 | アドレス変換方式               | 7-26 |

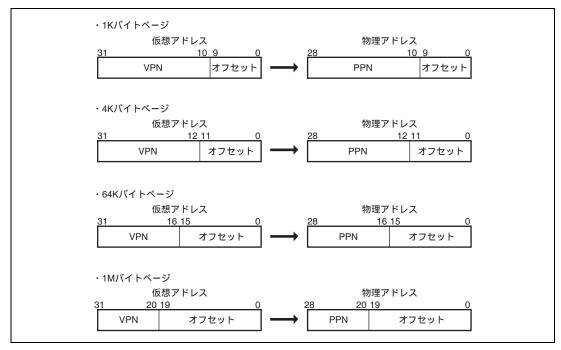

| 7.5   | MMUの機能                 | 7-29 |

| 7.5.1 | MMU のハードウェア管理          | 7-29 |

| 7.5.2 | MMU のソフトウェア管理          | 7-29 |

| 7.5.3 | MMU の命令(LDTLB)         | 7-30 |

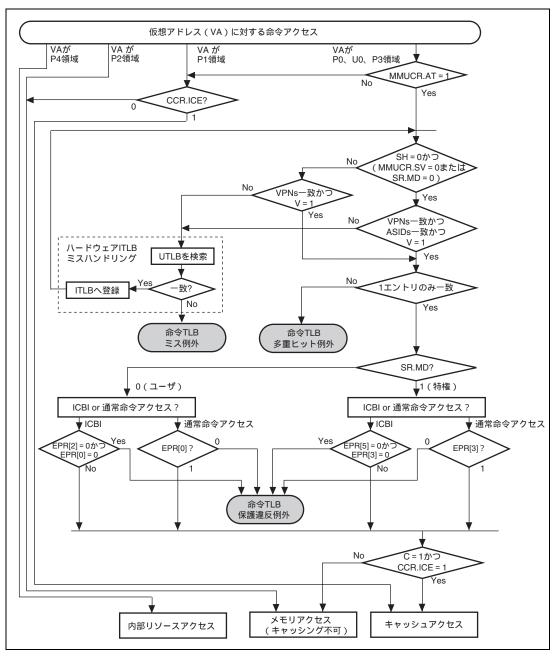

| 7.5.4 | ハードウェア ITLB ミスハンドリング   | 7-31 |

| 7.5.5 | シノニム問題の回避              | 7-32 |

| 7.6   | MMU例外                  | 7-33 |

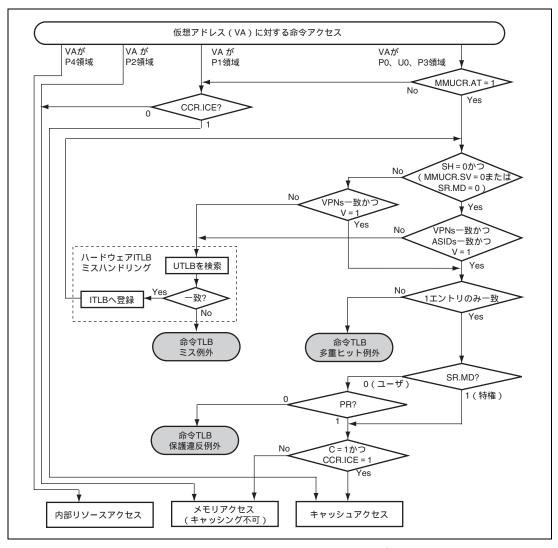

| 7.6.1 | 命令 TLB 多重ヒット例外         | 7-33 |

| 7.6.2 | 命令 TLB ミス例外            | 7-33 |

| 7.6.3 | 命令 TLB 保護違反例外          | 7-34 |

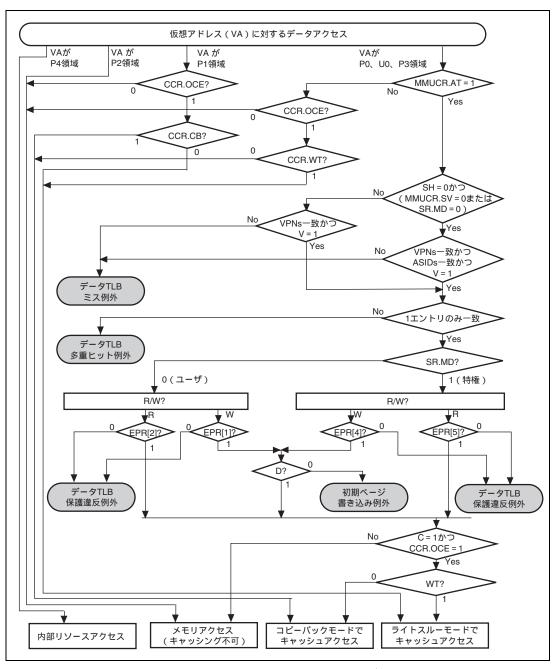

| 7.6.4 | データ TLB 多重ヒット例外        | 7-35 |

| 7.6.5 | データ TLB ミス例外           | 7-35 |

| 7.6.6 | データ TLB 保護違反例外         | 7-37 |

| 7.6.7 | 初期ページ書き込み例外            | 7-38 |

| 7.7   | メモリ割り付けTLBの構成          | 7-39 |

| 7.7.1 | ITLB アドレスアレイ           | 7-40 |

| 7.7.2 | ITLB データアレイ(TLB 互換モード) | 7-41 |

| 7.7.3 | ITLB データアレイ(TLB 拡張モード) | 7-42 |

| 7.7.4 | UTLB アドレスアレイ           | 7-43 |

| 7.7.5 | UTLB データアレイ(TLB 互換モード) | 7-45 |

| 7.7.6 | UTLB データアレイ(TLB 拡張モード) | 7-46 |

| 8. ++ | ァッシュ                   | 8-1  |

| 8.1   | 特長                     | 8-1  |

| 8.2   | レジスタの説明                | 8-4  |

| 8.2.1 | キャッシュ制御レジスタ(CCR)       | 8-5  |

| 8.2.2 | 内蔵メモリ制御レジスタ(RAMCR)     | 8-6  |

| 8.3   | オペランドキャッシュの動作説明        | 8-8  |

| 8.3.1 | 読み出し動作                 | 8-8  |

| 8.3.2 | プリフェッチ動作               | 8-9  |

| 8.3.3 | 書き込み動作                 | 8-10 |

| 8.3.4 | ライトバックバッファ                   | 8-11 |

|-------|------------------------------|------|

| 8.3.5 | ライトスルーバッファ                   | 8-11 |

| 8.3.6 | OC 2 ウェイモード                  | 8-11 |

| 8.4   | 命令キャッシュの動作説明                 | 8-12 |

| 8.4.1 | 読み出し動作                       | 8-12 |

| 8.4.2 | プリフェッチ動作                     | 8-12 |

| 8.4.3 | IC 2 ウェイモード                  | 8-13 |

| 8.4.4 | 命令キャッシュウェイ予測                 | 8-13 |

| 8.5   | キャッシュ操作命令                    | 8-14 |

| 8.5.1 | キャッシュと外部メモリとのコヒーレンシ          | 8-14 |

| 8.5.2 | プリフェッチ動作                     | 8-15 |

| 8.6   | メモリ割り付けキャッシュの構成              | 8-16 |

| 8.6.1 | IC アドレスアレイ                   | 8-16 |

| 8.6.2 | IC データアレイ                    | 8-18 |

| 8.6.3 | OC アドレスアレイ                   | 8-18 |

| 8.6.4 | OC データアレイ                    | 8-20 |

| 8.6.5 | メモリ割り付け連想ライトの動作              | 8-20 |

| 9. 内i | <b>載メモリ</b>                  | 9-1  |

| 9.1   | 特長                           | 9-1  |

| 9.2   | レジスタの説明                      | 9-5  |

| 9.2.1 | 内蔵メモリ制御レジスタ(RAMCR)           | 9-6  |

| 9.2.2 | X メモリ転送元アドレスレジスタ(XSA)        | 9-7  |

| 9.2.3 | Y メモリ転送元アドレスレジスタ(YSA)        | 9-8  |

| 9.2.4 | X メモリ転送先アドレスレジスタ(XDA)        | 9-9  |

| 9.2.5 | Y メモリ転送先アドレスレジスタ(YDA)        | 9-10 |

| 9.2.6 | X バス保護制御レジスタ ( XPR )         | 9-11 |

| 9.2.7 | Y バス保護制御レジスタ(YPR)            | 9-12 |

| 9.2.8 | X バス例外アドレスレジスタ(XEA)          | 9-13 |

| 9.2.9 | Y バス例外アドレスレジスタ(YEA)          | 9-14 |

| 9.3   | 動作説明                         | 9-15 |

| 9.3.1 | CPU からのオペランドアクセス             | 9-15 |

| 9.3.2 | CPU からの命令フェッチアクセス            | 9-16 |

| 9.3.3 | DSP からのアクセス                  | 9-18 |

| 9.3.4 | SuperHyway バスマスタモジュールからのアクセス | 9-19 |

| 9.3.5 | ブロック転送                       |      |

| 9.4   | 内蔵メモリの保護機能                   | 9-21 |

| 9.5   | 使用上の注意事項                     | 9-25 |

| 9.5.1 | ページ競合                        | 9-25 |

| 9.5.2 | バス競合                         | 0.25 |

| 9.5.3   | ページの切り替わり                             | 9-25  |

|---------|---------------------------------------|-------|

| 9.5.4   | MMU とキャッシュの設定                         | 9-26  |

| 9.5.5   | 内蔵メモリのコヒーレンシ                          | 9-27  |

| 9.5.6   | スリープモード                               | 9-27  |

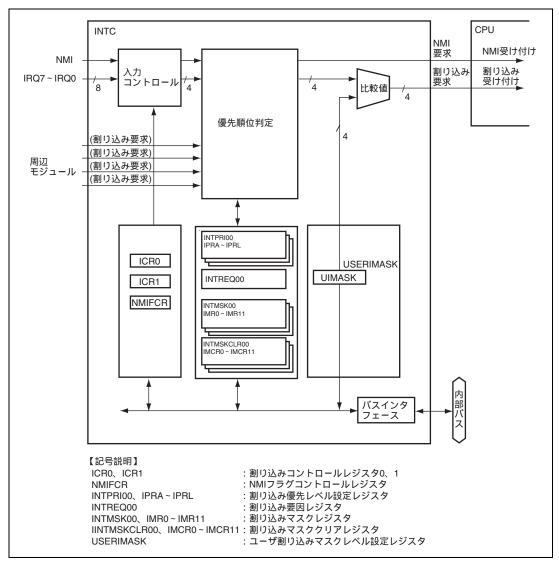

| 10. 割り  | 〕<br>込みコントローラ(INTC)                   | 10-1  |

| 10.1    | 特長                                    | 10-1  |

| 10.2    | 入出力端子                                 | 10-3  |

| 10.3    | レジスタの説明                               | 10-3  |

| 10.3.1  | 割り込みコントロールレジスタ 0 ( ICR0 )             | 10-6  |

| 10.3.2  | 割り込みコントロールレジスタ 1 ( ICR1 )             | 10-7  |

| 10.3.3  | 割り込み優先レベル設定レジスタ (INTPRI00)            | 10-8  |

| 10.3.4  | 割り込み優先レベル設定レジスタ A ~ L ( IPRA ~ IPRL ) | 10-9  |

| 10.3.5  | 割り込み要因レジスタ 00 ( INTREQ00 )            | 10-10 |

| 10.3.6  | 割り込みマスクレジスタ 00(INTMSK00)              | 10-11 |

| 10.3.7  | 割り込みマスククリアレジスタ 00 ( INTMSKCLR00 )     | 10-11 |

| 10.3.8  | 割り込みマスクレジスタ 0~11 (IMR0~IMR11)         | 10-12 |

| 10.3.9  | 割り込みマスククリアレジスタ 0~11 (IMCR0~IMCR11)    | 10-13 |

| 10.3.10 | ン ユーザ割り込みマスクレベル設定レジスタ(USERIMASK)      | 10-15 |

| 10.3.11 | NMI フラグコントロールレジスタ(NMIFCR)             | 10-16 |

| 10.4    | 割り込み要因                                | 10-17 |

| 10.4.1  | NMI 割り込み                              | 10-17 |

| 10.4.2  | IRQ 割り込み                              | 10-17 |

| 10.4.3  | 周辺モジュール割り込み                           | 10-18 |

| 10.4.4  | 割り込み例外処理と優先順位                         | 10-18 |

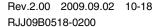

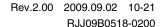

| 10.5    | 動作説明                                  | 10-21 |

| 10.5.1  | 割り込み動作の流れ                             | 10-21 |

| 10.5.2  | 多重割り込み                                | 10-24 |

| 10.5.3  | MAI ビットによる割り込みマスク                     | 10-24 |

| 10.5.4  | ユーザモードでの割り込み禁止機能                      | 10-25 |

| 10.6    | 割り込み応答時間                              | 10-26 |

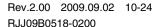

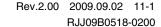

| 11. バス  | ステートコントローラ(BSC)                       | 11-1  |

| 11.1    | 特長                                    | 11-1  |

| 11.2    | 入出力端子                                 |       |

| 11.3    | エリアの概要                                |       |

| 11.3.1  | 空間分割                                  |       |

| 11.3.2  | シャドウ空間                                | 11-5  |

| 11.3.3  | アドレスマップ                               |       |

| 11.3.4  | メモリバス幅の設定                             | 11-7  |

| 11.3.5          | データアライメント                             | 11-8  |

|-----------------|---------------------------------------|-------|

| 11.4            | レジスタの説明                               | 11-8  |

| 11.4.1          | 共通コントロールレジスタ(CMNCR)                   | 11-10 |

| 11.4.2          | CSn 空間バスコントロールレジスタ(CSnBCR)            | 11-11 |

| 11.4.3          | CSn 空間ウェイトコントロールレジスタ ( CSnWCR )       | 11-14 |

| 11.4.4          | リセットバスウェイトカウンタ(RBWTCNT)               | 11-27 |

| 11.5            | 動作説明                                  | 11-28 |

| 11.5.1          | エンディアン / アクセスサイズとデータアライメント            | 11-28 |

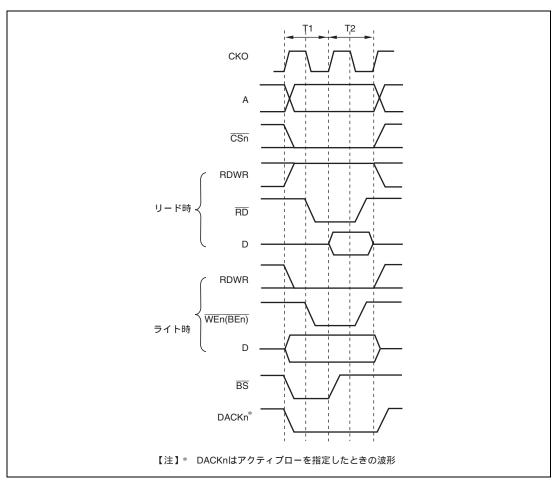

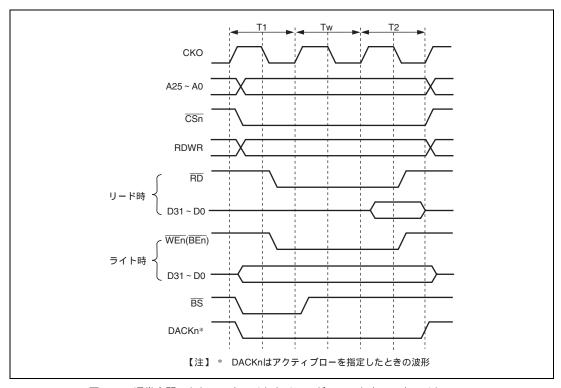

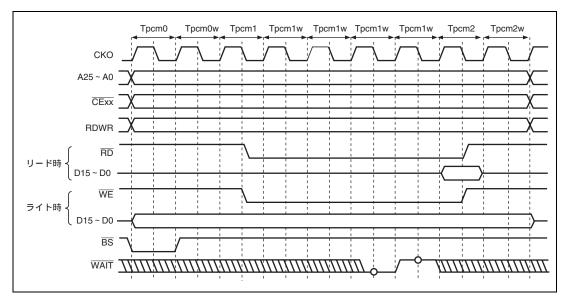

| 11.5.2          | 通常空間インタフェース                           | 11-33 |

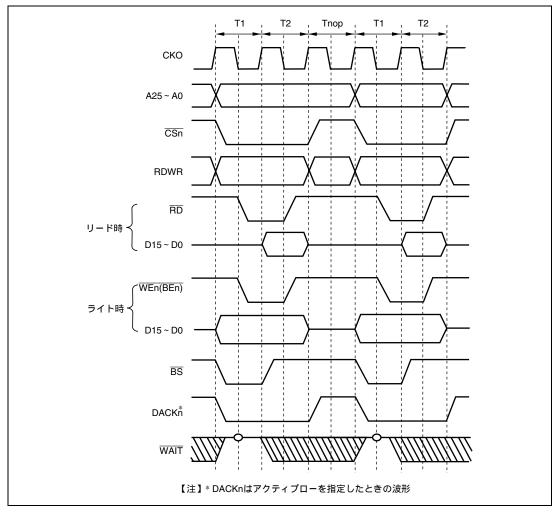

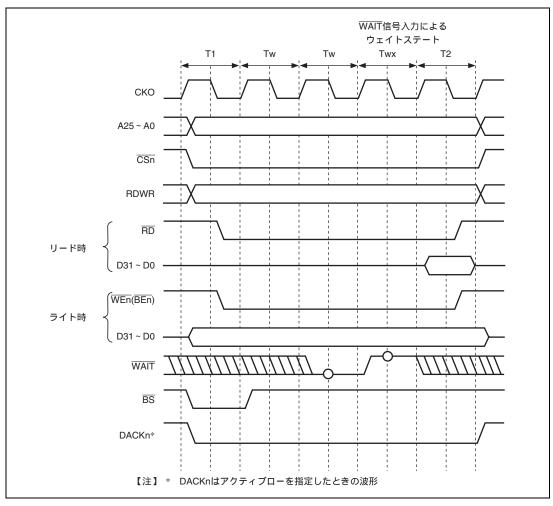

| 11.5.3          | アクセスウェイト制御                            | 11-38 |

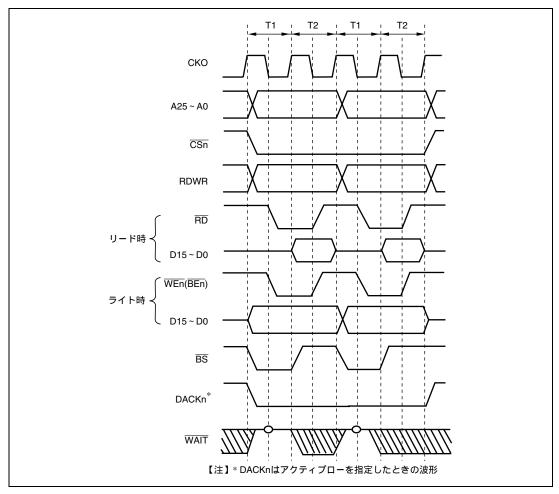

| 11.5.4          | <b>CSn</b> アサート期間拡張                   | 11-40 |

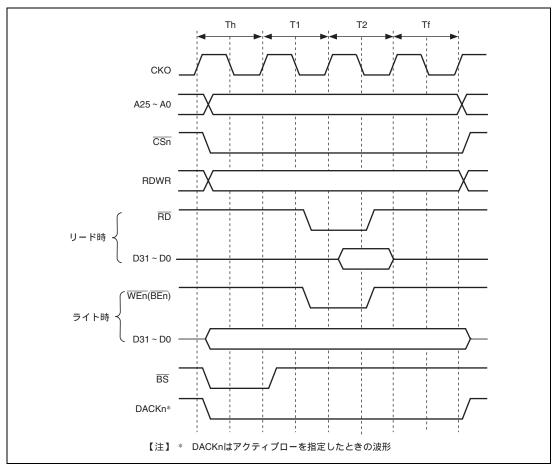

| 11.5.5          | バースト ROM(クロック非同期)インタフェース              | 11-41 |

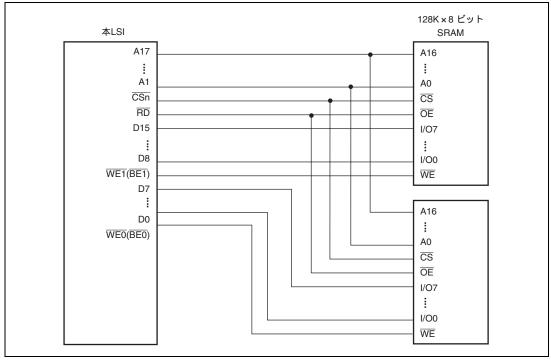

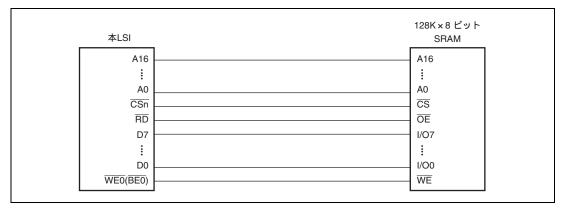

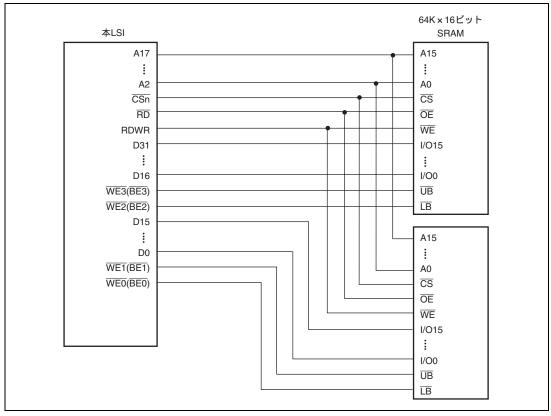

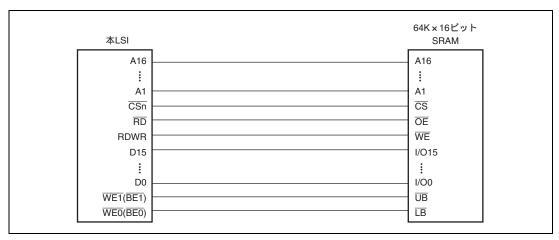

| 11.5.6          | バイト選択付き SRAM インタフェース                  | 11-42 |

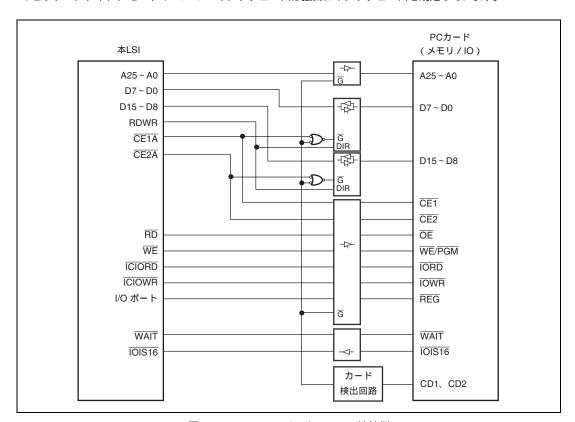

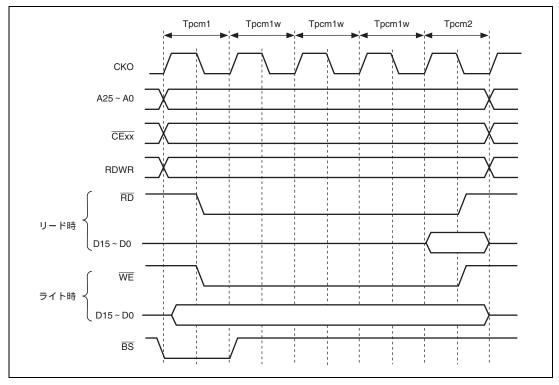

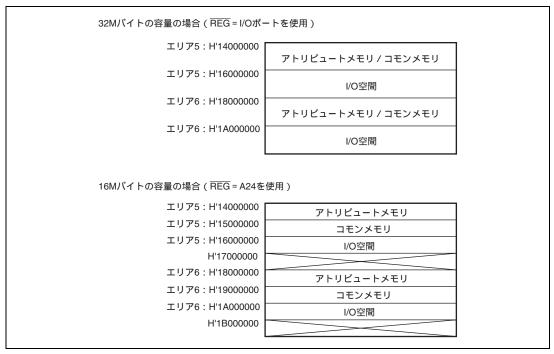

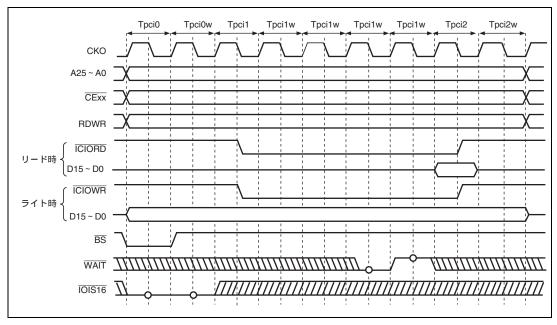

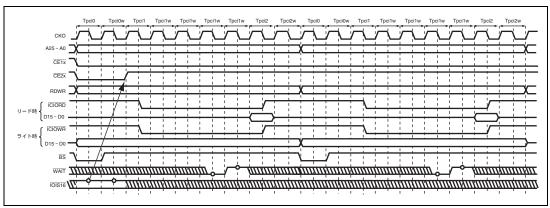

| 11.5.7          | PCMCIA インタフェース                        | 11-47 |

| 11.5.8          | アクセスサイクル間ウェイト                         | 11-53 |

| 11.6            | 使用上の注意事項                              | 11-54 |

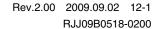

| 12. SDF<br>12.1 | RAM 用バスステートコントローラ(SBSC)特長             |       |

| 12.2            | 入出力端子                                 | 12-3  |

| 12.3            | エリアの概要                                | 12-4  |

| 12.3.1          | アドレスマップ                               | 12-4  |

| 12.3.2          | メモリバス幅                                | 12-4  |

| 12.3.3          | データアライメント                             | 12-5  |

| 12.4            | レジスタの説明                               | 12-5  |

| 12.4.1          | SDRAM コントロールレジスタ 0 ( SDCR0 )          | 12-6  |

| 12.4.2          | SDRAM コントロールレジスタ 1 ( SDCR1 )          | 12-10 |

| 12.4.3          | SDRAM ウェイトコントロールレジスタ ( SDWCR )        | 12-11 |

| 12.4.4          | SDRAM 端子コントロールレジスタ(SDPCR)             | 12-13 |

| 12.4.5          | リフレッシュタイマコントロール / ステータスレジスタ ( RTCSR ) | 12-14 |

| 12.4.6          | リフレッシュタイマカウンタ(RTCNT)                  | 12-16 |

| 12.4.7          | リフレッシュタイムコンスタントレジスタ(RTCOR)            | 12-17 |

| 12.4.8          | リフレッシュカウントレジスタ(RFCR)                  | 12-17 |

| 12.4.9          | SDRAM ウェイトコントロールレジスタ 2 ( SDWCR2 )     | 12-18 |

| 12.4.10         | SDRAM ライトプロテクトコントロールレジスタ ( SDWPCR )   | 12-19 |

| 12.4.11         | SDRAM モードレジスタ設定コントロールレジスタ(SDMRCR)     | 12-20 |

| 12.4.12         | バーストリフレッシュカウントレジスタ ( BSTRCNT )        | 12-21 |

| 12.5            | 動作説明                                  | 12-22 |

|                 | 200 11 M/O / (3                       |       |

| 12.5.1          | エンディアン / アクセスサイズとデータアライメント            |       |

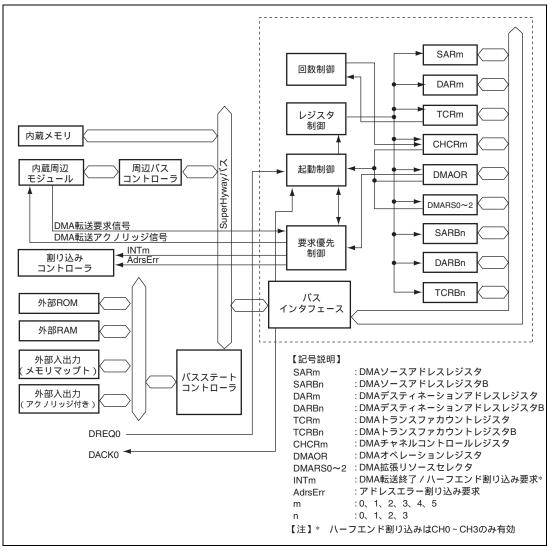

| 3. ダイ  | レクトメモリアクセスコントローラ(DMAC)                        | 13-1  |

|--------|-----------------------------------------------|-------|

| 13.1   | 特長                                            | 13-1  |

| 3.2    | 入出力端子                                         | 13-3  |

| 13.3   | レジスタの説明                                       | 13-3  |

| 13.3.1 | DMA ソースアドレスレジスタ_0~5(SAR_0~SAR_5)              | 13-6  |

| 13.3.2 | DMA ソースアドレスレジスタ B_0~3 ( SARB_0~ SARB_3 )      | 13-6  |

| 13.3.3 | DMA デスティネーションアドレスレジスタ_0~5(DAR_0~5)            | 13-7  |

| 13.3.4 | DMA デスティネーションアドレスレジスタ B_0~3 ( DARB_0~DARB_3 ) | 13-7  |

| 13.3.5 | DMA トランスファカウントレジスタ_0~5 ( TCR_0 ~ TCR_5 )      | 13-8  |

| 13.3.6 | DMA トランスファカウントレジスタ B_0~3 ( TCRB_0~ TCRB_3 )   | 13-8  |

| 13.3.7 | DMA チャネルコントロールレジスタ_0~5 ( CHCR_0 ~ CHCR_5 )    | 13-9  |

| 13.3.8 | DMA オペレーションレジスタ(DMAOR)                        | 13-14 |

| 13.3.9 | DMA 拡張リソースセレクタ 0~2 ( DMARS0~DMARS2 )          | 13-16 |

| 3.4    | 動作説明                                          | 13-18 |

| 13.4.1 | DMA 転送要求                                      | 13-18 |

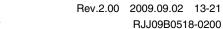

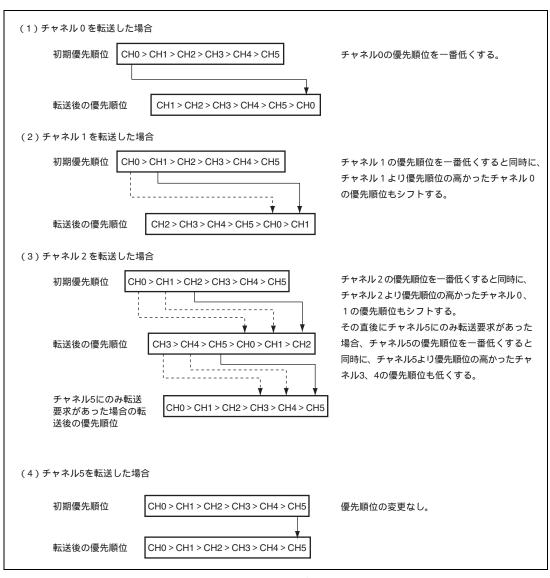

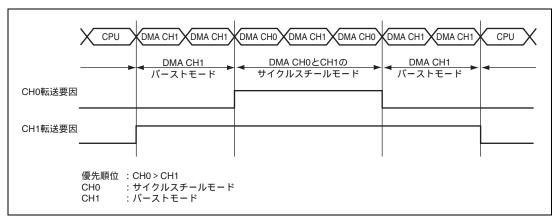

| 13.4.2 | チャネルの優先順位                                     | 13-21 |

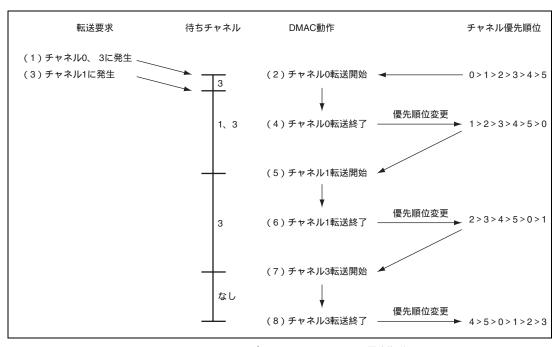

| 13.4.3 | DMA 転送の種類                                     | 13-24 |

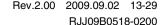

| 13.4.4 | 転送フロー                                         | 13-29 |

| 13.4.5 | リピートモード転送                                     | 13-31 |

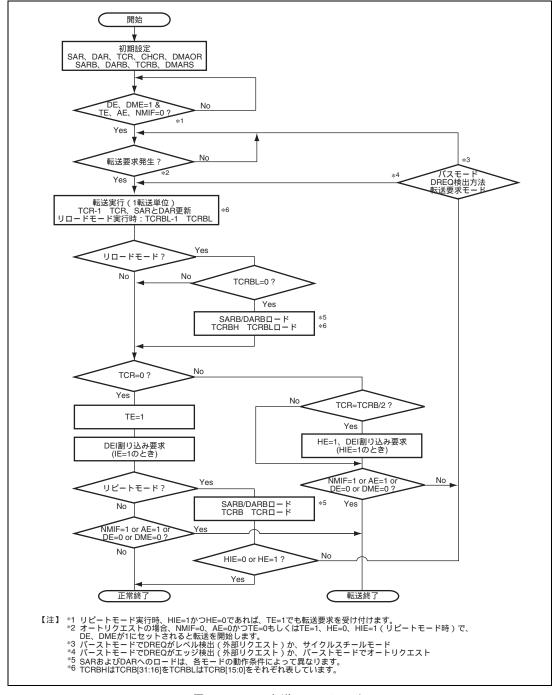

| 13.4.6 | リロードモード転送                                     | 13-32 |

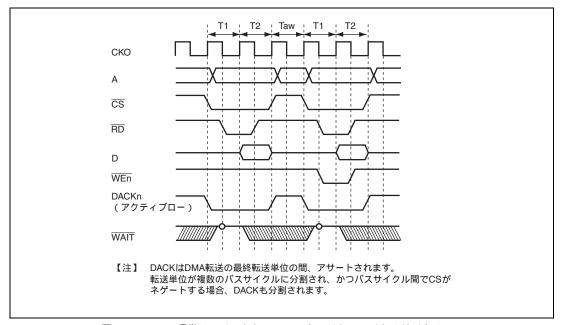

| 13.4.7 | DREQ 端子のサンプリングタイミング                           | 13-33 |

| 3.5    | 使用上の注意                                        | 13-36 |

| 13.5.1 | 周辺モジュールの DMA 転送について                           | 13-36 |

| 13.5.2 | モジュールストップについて                                 | 13-36 |

| 13.5.3 | アドレスエラーについて                                   | 13-36 |

| 13.5.4 | バーストモード転送時の注意                                 | 13-36 |

| 13.5.5 | HE、TE、AE、NMIF の各フラグビット使用上の注意事項                | 13-36 |

| 13.5.6 | バーストモードの使用上の注意事項                              | 13-37 |

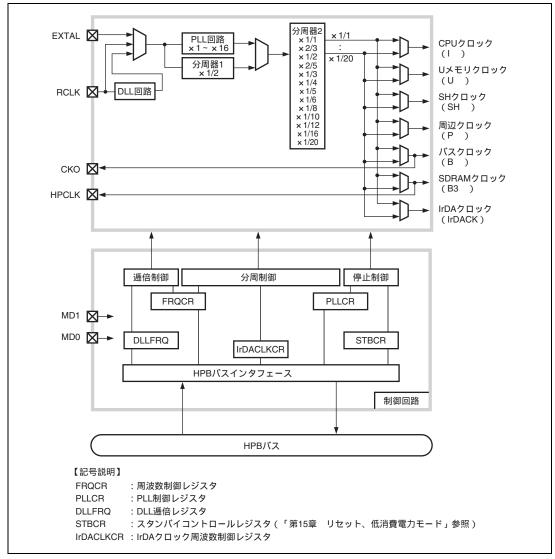

| クロ     | ックパルス発生器(CPG)                                 | 14-1  |

| 4.1    | 特長                                            | 14-1  |

| 4.2    | ブロック図                                         | 14-2  |

| 4.3    | 入出力端子                                         | 14-4  |

| 4.4    | クロック動作モード                                     | 14-4  |

| 4.5    | レジスタの説明                                       | 14-5  |

| 14.5.1 | 周波数制御レジスタ(FRQCR)                              | 14-5  |

| 14.5.2 | PLL 制御レジスタ ( PLLCR )                          | 14-10 |

| 14.5.3 | IrDA クロック周波数制御レジスタ(IrDACLKCR)                 | 14-11 |

| 14.5.4 | DLL 逓倍レジスタ(DLLFRQ)                            | 14-12 |

| 4.6    | 周波数变更方法                                       | 14-13 |

| 14.6.1  | PLL 回路逓倍率の変更                              | 14-13 |

|---------|-------------------------------------------|-------|

| 14.6.2  | 分周率の変更                                    | 14-13 |

| 14.6.3  | クロック動作モードの変更                              | 14-13 |

| 14.6.4  | PLL 回路の ON / OFF 切り替え                     | 14-13 |

| 14.6.5  | DLL 逓倍率の変更                                | 14-13 |

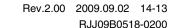

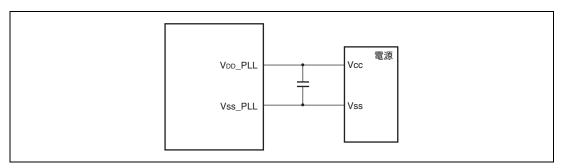

| 14.7    | ボード設計上の注意事項                               | 14-14 |

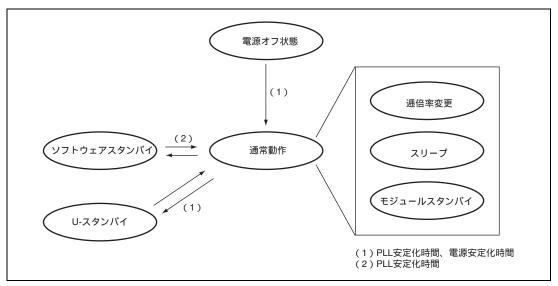

| 15. リセ  | :ット、低消費電力モード                              | 15-1  |

| 15.1    | 特長                                        | 15-1  |

| 15.1.1  | 電源領域の分離                                   | 15-1  |

| 15.1.2  | リセット、低消費電力モードの種類                          | 15-2  |

| 15.2    | 入出力端子                                     | 15-3  |

| 15.3    | レジスタの説明                                   | 15-4  |

| 15.3.1  | スタンバイコントロールレジスタ ( STBCR )                 | 15-4  |

| 15.3.2  | モジュールストップレジスタ 0 ( MSTPCR0 )               | 15-5  |

| 15.3.3  | モジュールストップレジスタ 1 ( MSTPCR1 )               | 15-10 |

| 15.3.4  | モジュールストップレジスタ 2 ( MSTPCR2 )               | 15-11 |

| 15.4    | 動作説明                                      | 15-13 |

| 15.4.1  | リセット                                      | 15-13 |

| 15.4.2  | スリープモード                                   | 15-14 |

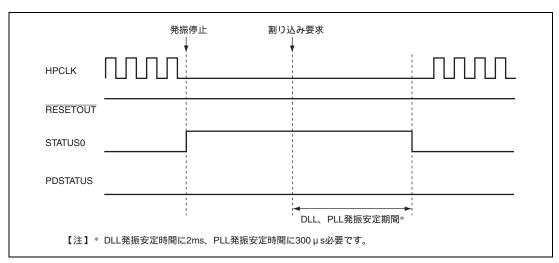

| 15.4.3  | ソフトウェアスタンバイモード                            | 15-15 |

| 15.4.4  | モジュールスタンバイ機能                              | 15-16 |

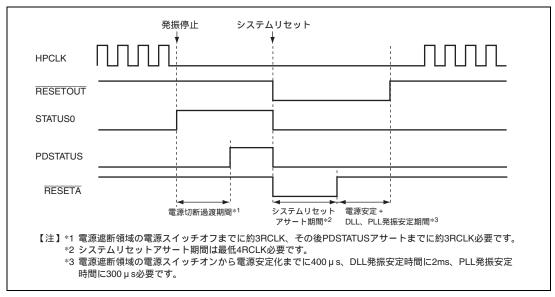

| 15.4.5  | U-スタンバイモード                                | 15-16 |

| 15.4.6  | 各種モード間の状態遷移                               | 15-17 |

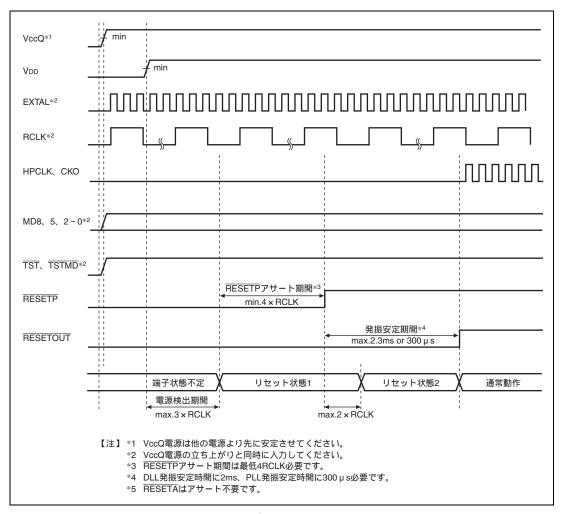

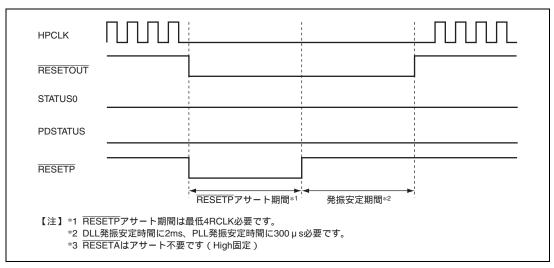

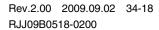

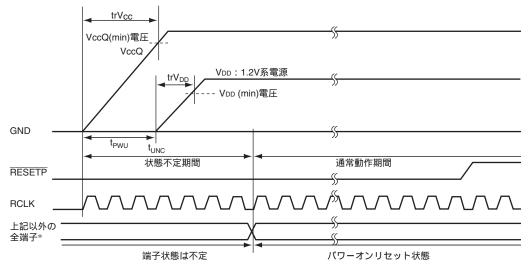

| 15.4.7  | パワーオンシーケンス                                | 15-18 |

| 15.4.8  | 出力端子の変化タイミング                              | 15-19 |

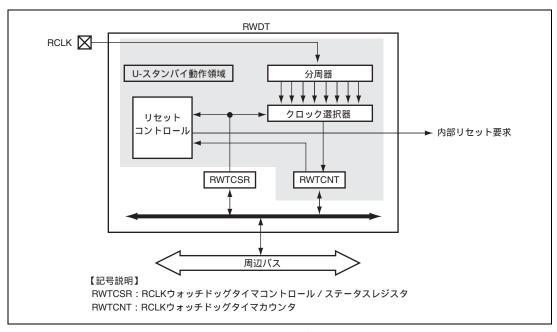

| 16. RCL | .K ウォッチドッグタイマ(RWDT)                       | 16-1  |

| 16.1    | 特長                                        | 16-1  |

| 16.2    | RWDTの入出力端子                                | 16-2  |

| 16.3    | レジスタの説明                                   | 16-2  |

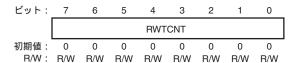

| 16.3.1  | RCLK ウォッチドッグタイマカウンタ(RWTCNT)               | 16-2  |

| 16.3.2  | RCLK ウォッチドッグタイマコントロール / ステータスレジスタ(RWTCSR) | 16-3  |

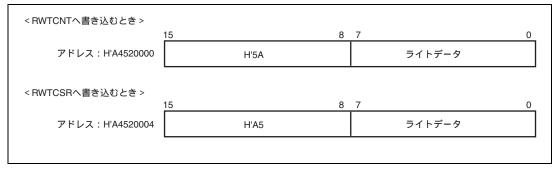

| 16.3.3  | レジスタアクセス時の注意                              | 16-4  |

| 16.4    | RWDTの使用方法                                 | 16-5  |

| 16.4.1  | 暴走制御                                      | 16-5  |

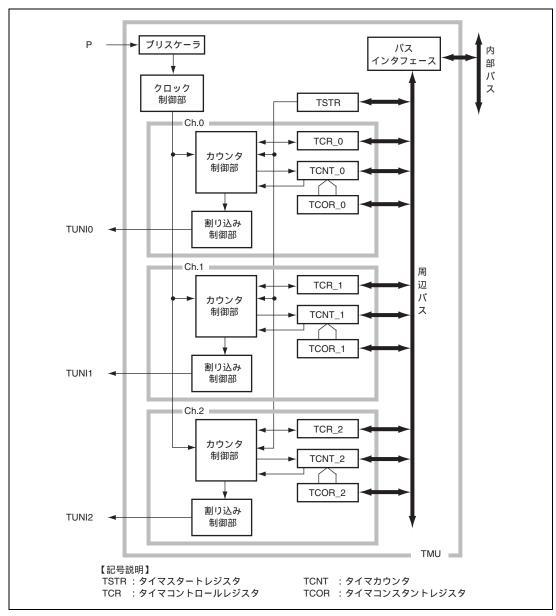

| 17. タイ  | マユニット ( TMU )                             | 17-1  |

| 17.1    | 特長                                        | 17-1  |

| 17.2    | レジスタの説明                                   | 17-3  |

| 17.2.1  | タイマスタートレジスタ ( TSTR )                   | 17-4  |

|---------|----------------------------------------|-------|

| 17.2.2  | タイマコントロールレジスタ(TCR)                     | 17-5  |

| 17.2.3  | タイマコンスタントレジスタ(TCOR)                    | 17-6  |

| 17.2.4  | タイマカウンタ ( TCNT )                       | 17-6  |

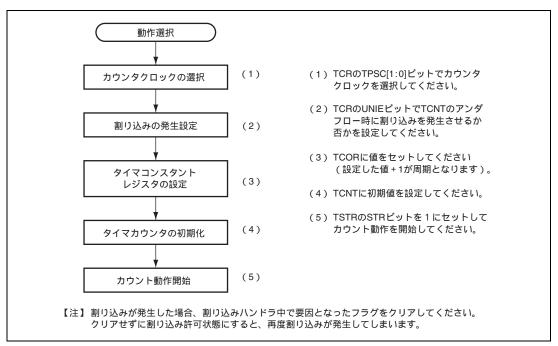

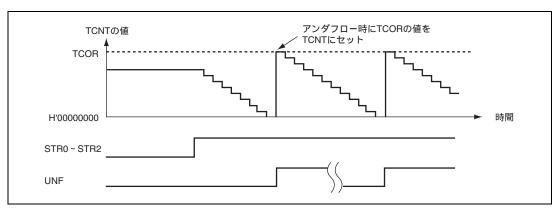

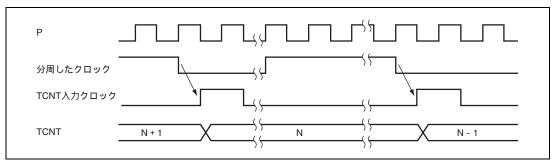

| 17.3    | 動作説明                                   | 17-7  |

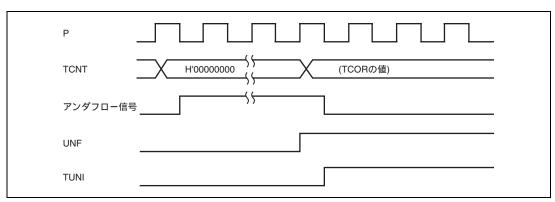

| 17.3.1  | カウンタの動作                                | 17-7  |

| 17.4    | 割り込み                                   | 17-9  |

| 17.4.1  | ステータスフラグのセットタイミング                      | 17-9  |

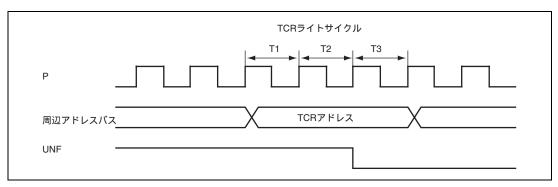

| 17.4.2  | ステータスフラグのクリアタイミング                      | 17-9  |

| 17.4.3  | 割り込み要因と優先順位                            | 17-10 |

| 17.5    | 使用上の注意事項                               | 17-10 |

| 17.5.1  | レジスタの書き込みについて                          | 17-10 |

| 17.5.2  | レジスタの読み出しについて                          | 17-10 |

| 10 10 1 | プットカノフパリファーット(TDU)                     | 40.4  |

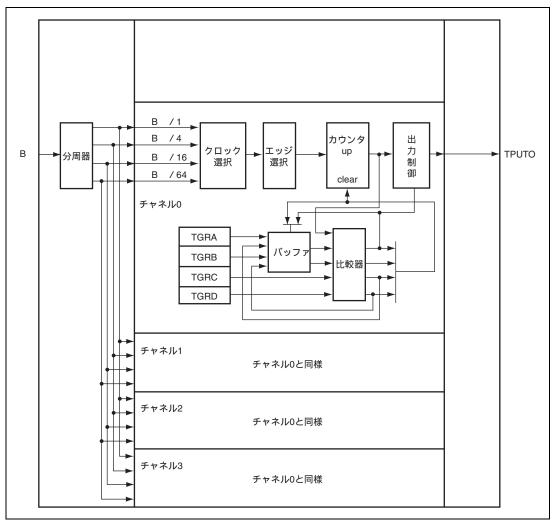

|         | ビットタイマパルスユニット(TPU)                     |       |

| 18.1    | 特長                                     |       |

| 18.2    | ブロック図                                  |       |

| 18.3    | 端子構成                                   |       |

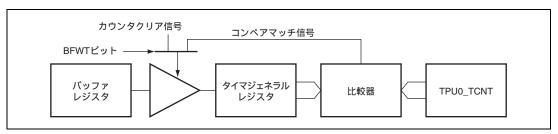

| 18.4    | レジスタの説明                                |       |

| 18.4.1  | タイマコントロールレジスタ(TPU_TCR)                 |       |

| 18.4.2  | タイマモードレジスタ ( TPU_TMDR )                |       |

| 18.4.3  | タイマ I/O コントロールレジスタ (TPU_TIOR)          |       |

| 18.4.4  | タイマインタラプトイネーブルレジスタ(TPU_TIER)           |       |

| 18.4.5  | タイマステータスレジスタ(TPU_TSR)                  |       |

| 18.4.6  | タイマカウンタ (TPU_TCNT)                     |       |

| 18.4.7  | タイマジェネラルレジスタ(TPU_TGR)                  |       |

| 18.4.8  | タイマスタートレジスタ (TPU_TSTR )                |       |

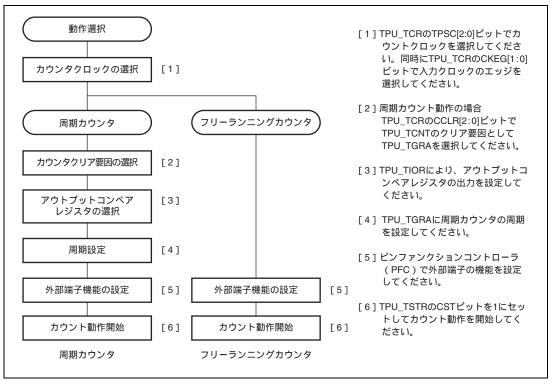

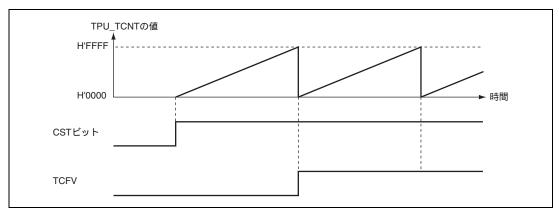

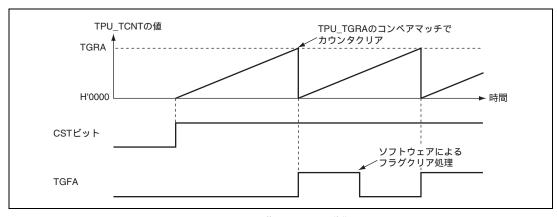

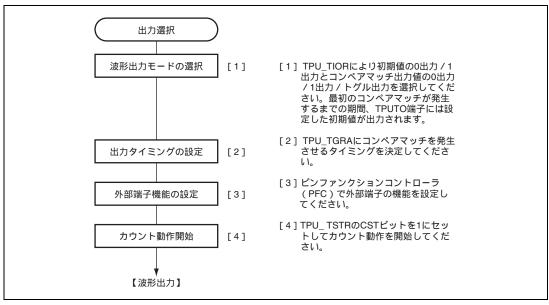

| 18.5    | 動作説明                                   |       |

| 18.5.1  | 概要                                     |       |

| 18.5.2  | 基本機能                                   |       |

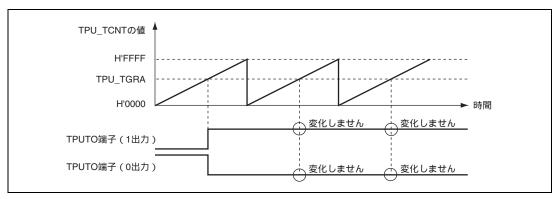

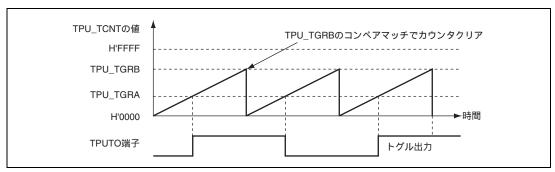

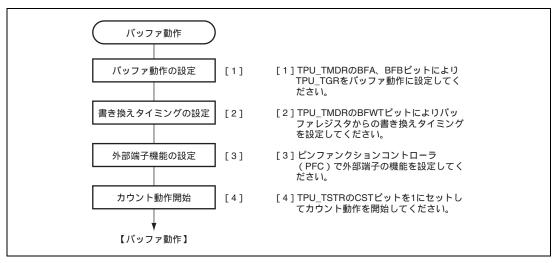

| 18.5.3  | バッファ動作                                 |       |

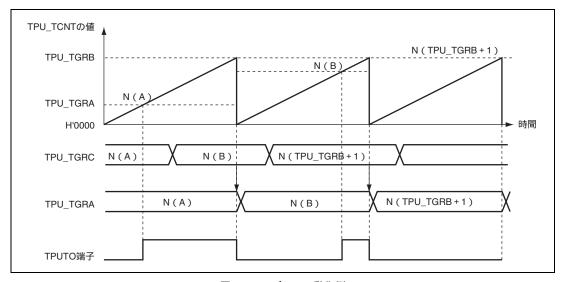

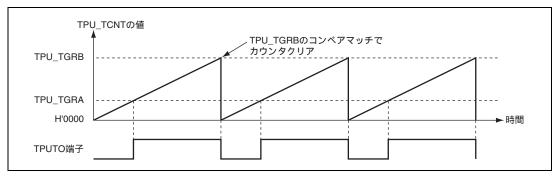

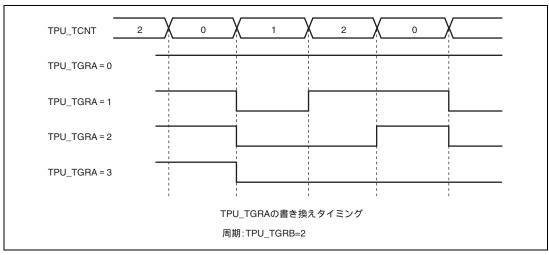

| 18.5.4  | PWM モード                                | 18-21 |

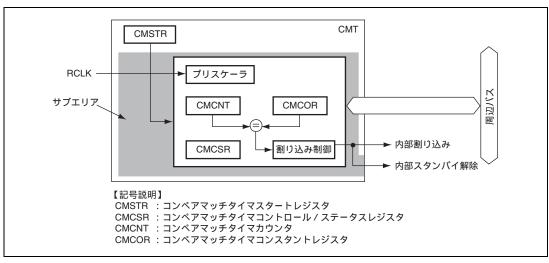

| 19. コン  | パプマッチタイマ(CMT)                          | 19-1  |

| 19.1    | 特長                                     | 19-1  |

| 19.2    | レジスタの説明                                | 19-2  |

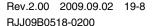

| 19.2.1  | コンペアマッチタイマスタートレジスタ(CMSTR)              | 19-2  |

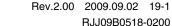

| 19.2.2  | コンペアマッチタイマコントロール / ステータスレジスタ ( CMCSR ) | 19-3  |

| 19.2.3  | コンペアマッチタイマカウンタ(CMCNT)                  | 19-5  |

| 19.2.4  | コンペアマッチタイマコンスタントレジスタ(CMCOR)            | 19-5  |

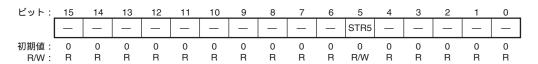

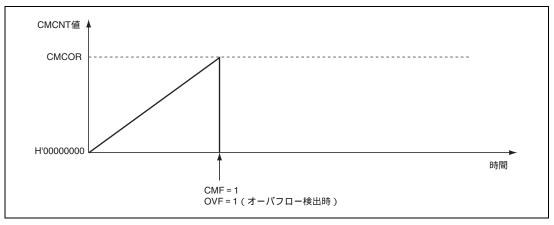

| 19.3   | 動作説明                                      | 19-6  |

|--------|-------------------------------------------|-------|

| 19.3.1 | カウンタ動作                                    |       |

| 19.3.2 | カウンタサイズ                                   |       |

| 19.3.3 | CMCNT カウントタイミング                           |       |

| 19.3.4 | CPU への内部割り込み要求                            |       |

| 19.3.5 | CMT の動作                                   |       |

| 19.3.6 | コンペアマッチフラグのセットタイミング                       |       |

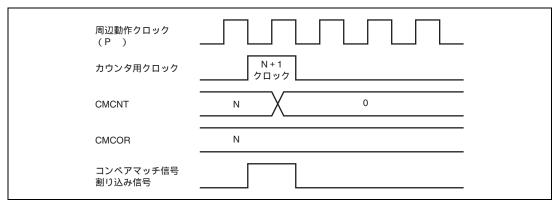

| 20. シリ | アル I/O ( SIO )                            | 20-1  |

| 20.1   | 特長                                        | 20-1  |

| 20.2   | 入出力端子                                     | 20-2  |

| 20.3   | レジスタの説明                                   | 20-3  |

| 20.3.1 | モードレジスタ ( SIOMDR )                        | 20-4  |

| 20.3.2 | コントロールレジスタ ( SIOCTR )                     | 20-5  |

| 20.3.3 | ストロープコントロールレジスタ 1、0 (SIOSTBCR1、SIOSTBCR0) | 20-7  |

| 20.3.4 | 送信データレジスタ ( SIOTDR )                      | 20-9  |

| 20.3.5 | 受信データレジスタ ( SIORDR )                      | 20-10 |

| 20.3.6 | ステータスレジスタ ( SIOSTR )                      | 20-11 |

| 20.3.7 | 割り込み許可レジスタ(SIOIER)                        | 20-14 |

| 20.3.8 | クロックセレクトレジスタ(SIOSCR)                      | 20-15 |

| 20.4   | 動作説明                                      | 20-16 |

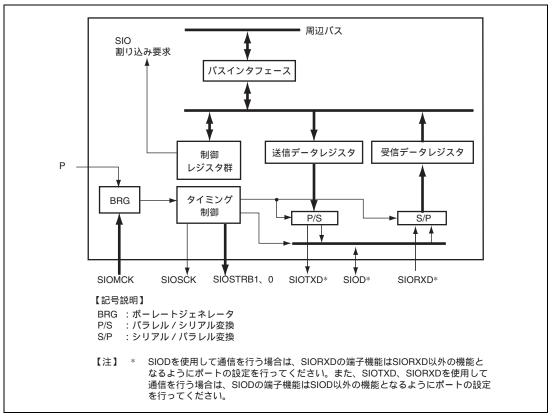

| 20.4.1 | シリアルクロック                                  | 20-16 |

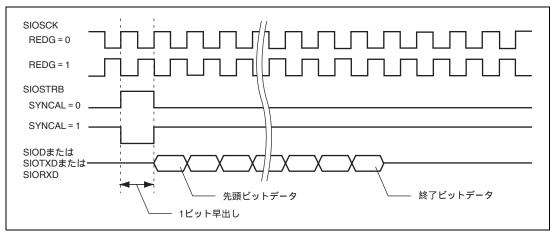

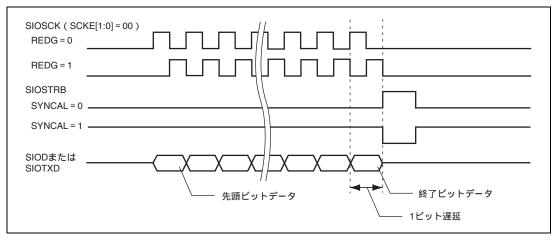

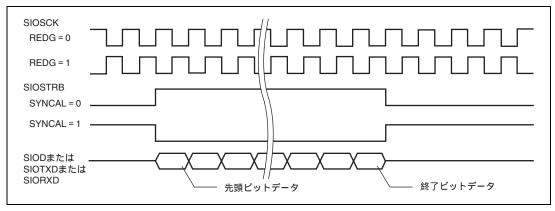

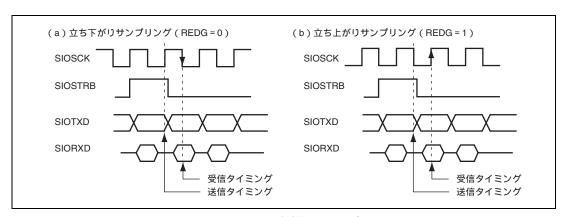

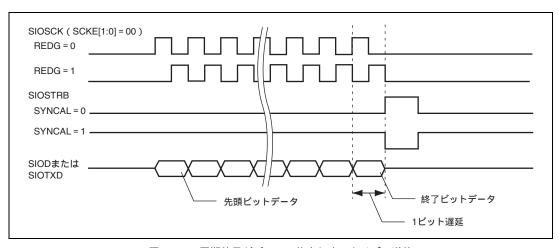

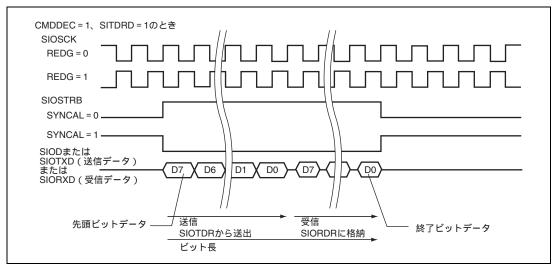

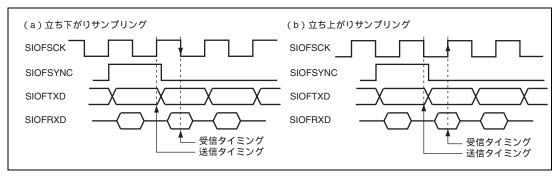

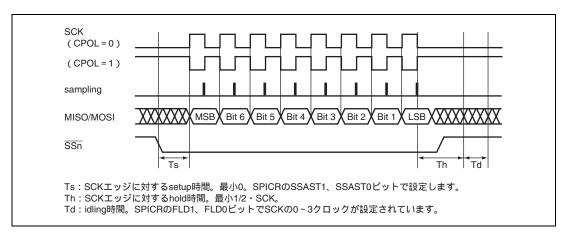

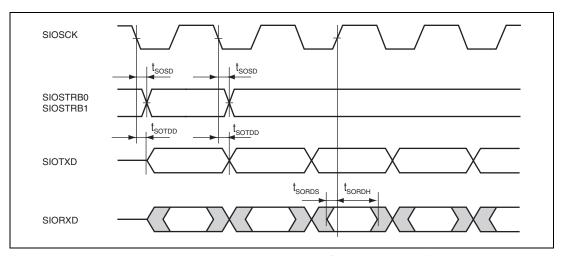

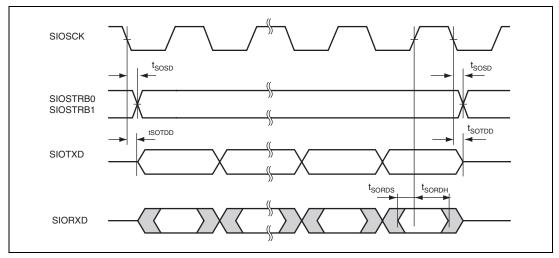

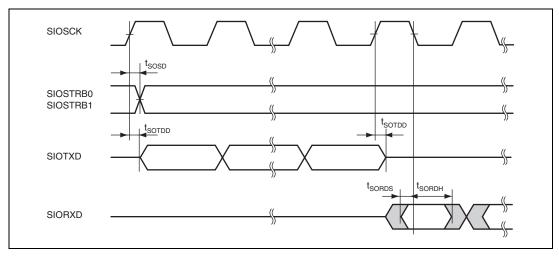

| 20.4.2 | シリアルタイミング                                 | 20-17 |

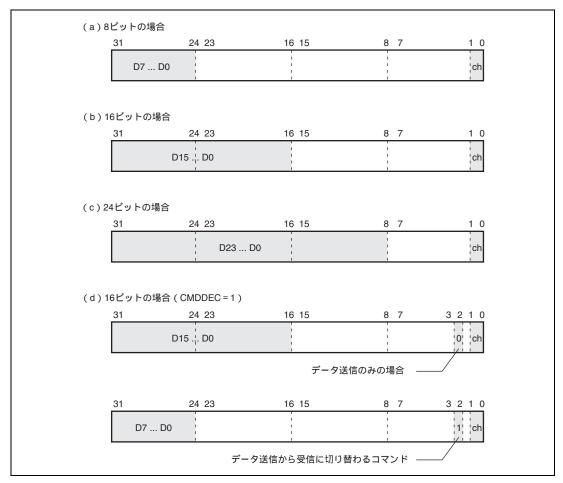

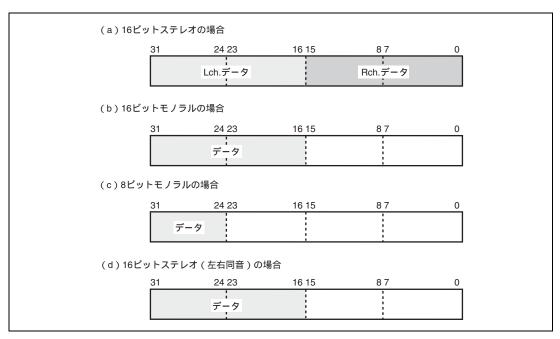

| 20.4.3 | 転送データフォーマット                               | 20-18 |

| 20.4.4 | 転送データのレジスタ割り付け                            | 20-19 |

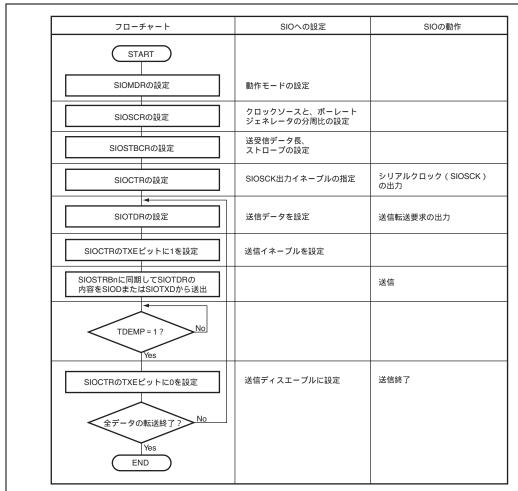

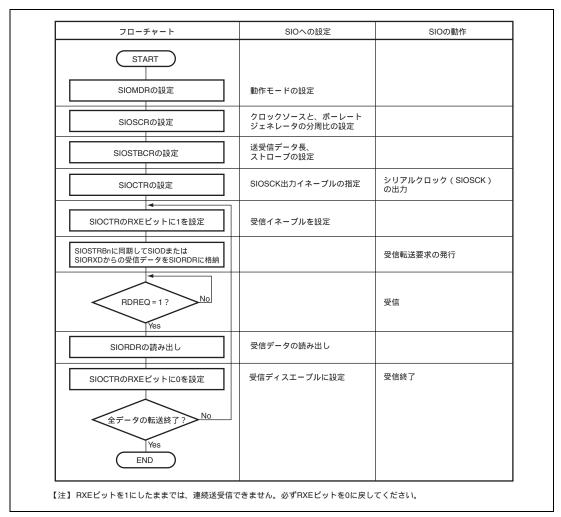

| 20.4.5 | 送受信手順                                     | 20-20 |

| 20.4.6 | 割り込み                                      | 20-22 |

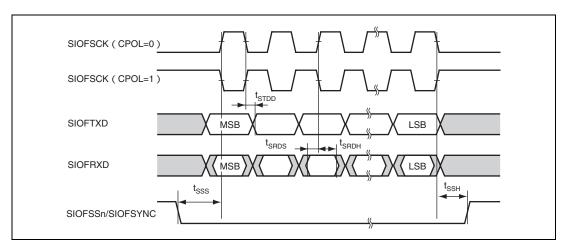

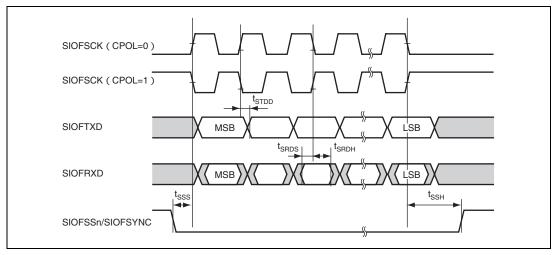

| 20.4.7 | 送受信タイミング                                  | 20-23 |

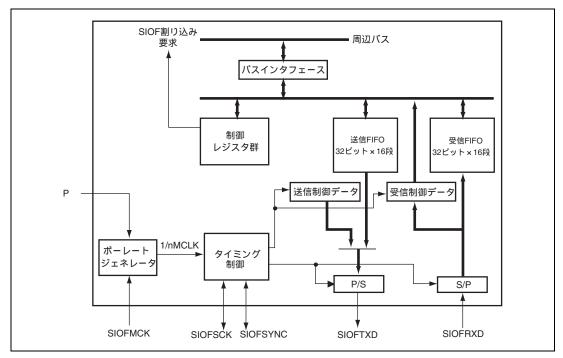

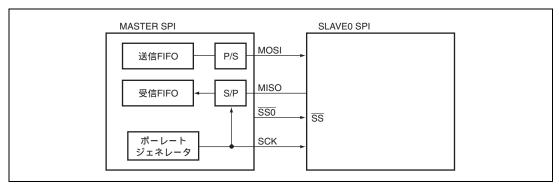

| 21. シリ | アル I/O FIFO 付き(SIOF)                      | 21-1  |

| 21.1   | 特長                                        | 21-1  |

| 21.2   | 入出力端子                                     | 21-3  |

| 21.3   | レジスタの説明                                   | 21-4  |

| 21.3.1 | モードレジスタ 0、1 (SIMDR0、SIMDR1)               | 21-6  |

| 21.3.2 | コントロールレジスタ 0、1 ( SICTR0、SICTR1 )          | 21-8  |

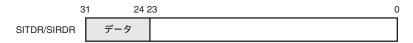

| 21.3.3 | 送信データレジスタ 0、1 (SITDR0、SITDR1)             | 21-10 |

| 21.3.4 | 受信データレジスタ 0、1 ( SIRDR0、SIRDR1 )           | 21-10 |

| 21.3.5 | 送信制御データレジスタ 0、1 (SITCR0、SITCR1)           | 21-11 |

| 21.3.6 | 受信制御データレジスタ 0、1 (SIRCRO、SIRCR1)           | 21-12 |

| 21.3.7 | ステータスレジスタ 0、1 (SISTR0、SISTR1)             | 21-12 |

| 21.3.8   | 割り込み許可レジスタ 0、1 ( SIIER0、 SIIER1 )         | 21-17 |

|----------|-------------------------------------------|-------|

| 21.3.9   | FIFO コントロールレジスタ 0、1 (SIFCTR0、SIFCTR1)     | 21-18 |

| 21.3.10  | クロックセレクトレジスタ 0、1 ( SISCR0、SISCR1 )        | 21-20 |

| 21.3.11  | 送信データアサインレジスタ 0、1(SITDAR0、SITDAR1)        | 21-21 |

| 21.3.12  | 受信データアサインレジスタ 0、1 ( SIRDAR0、SIRDAR1 )     | 21-22 |

| 21.3.13  | 制御データアサインレジスタ 0、1 ( SICDAR0、SICDAR1 )     | 21-23 |

| 21.3.14  | SPI 制御レジスタ 0、1 (SPICR0、SPICR1)            | 21-24 |

| 21.4     | 動作説明                                      | 21-26 |

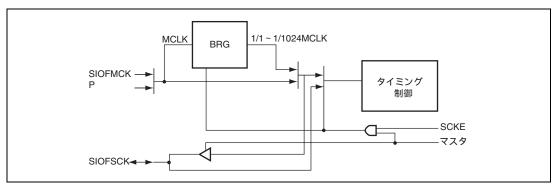

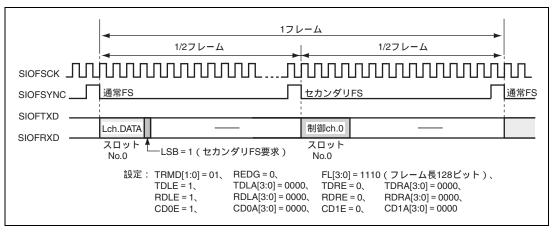

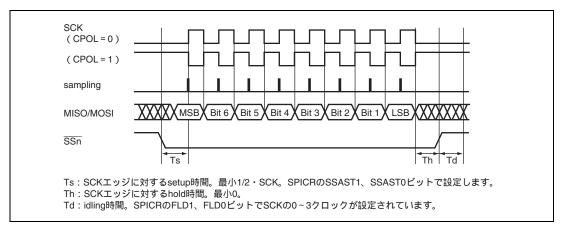

| 21.4.1   | シリアルクロック                                  | 21-26 |

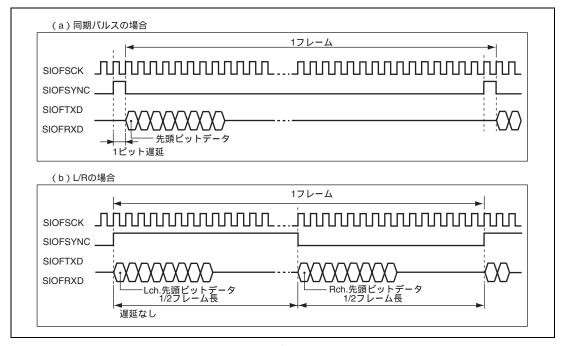

| 21.4.2   | シリアルタイミング                                 | 21-27 |

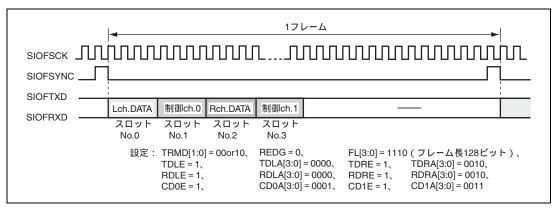

| 21.4.3   | 転送データフォーマット                               | 21-28 |

| 21.4.4   | 転送データのレジスタ割り付け                            | 21-30 |

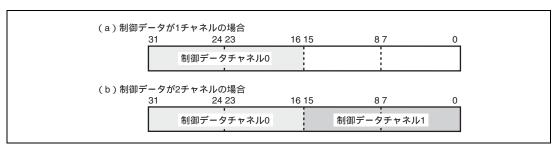

| 21.4.5   | 制御データインタフェース                              | 21-32 |

| 21.4.6   | FIFO                                      | 21-33 |

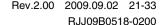

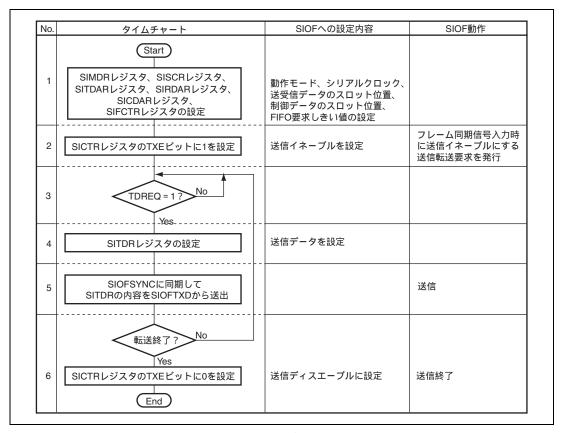

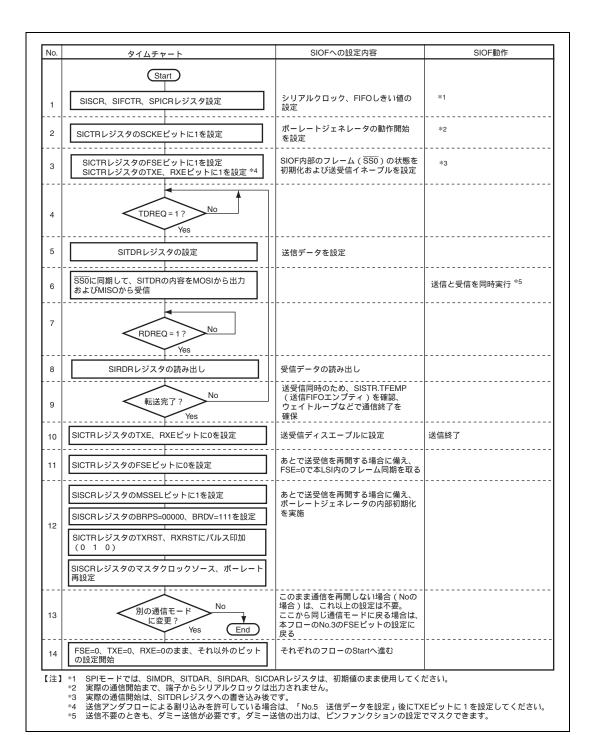

| 21.4.7   | 送受信手順                                     | 21-35 |

| 21.4.8   | 割り込み                                      | 21-39 |

| 21.4.9   | 送受信タイミング                                  | 21-41 |

| 21.4.10  | SPI モード                                   | 21-45 |

| 21.5     | 使用上の注意事項                                  | 21-48 |

| 21.5.1   | SPI モードについての注意事項                          | 21-48 |

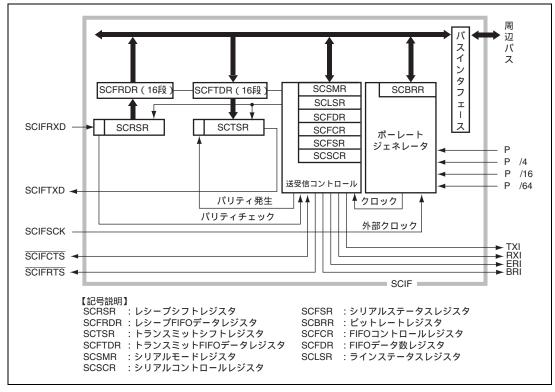

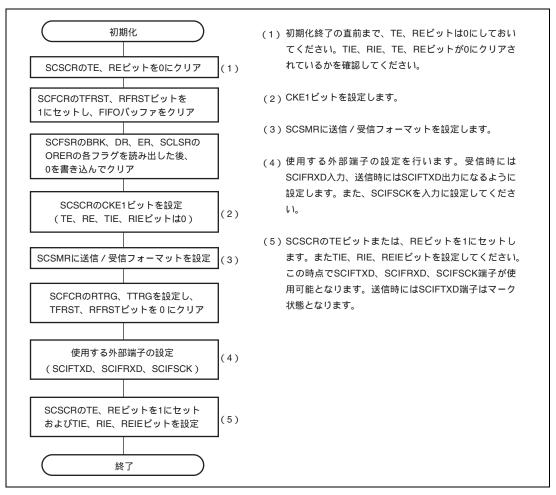

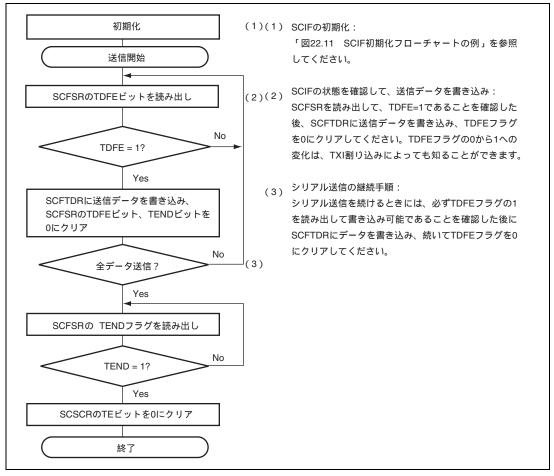

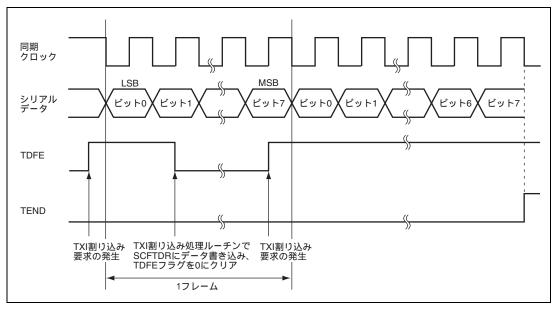

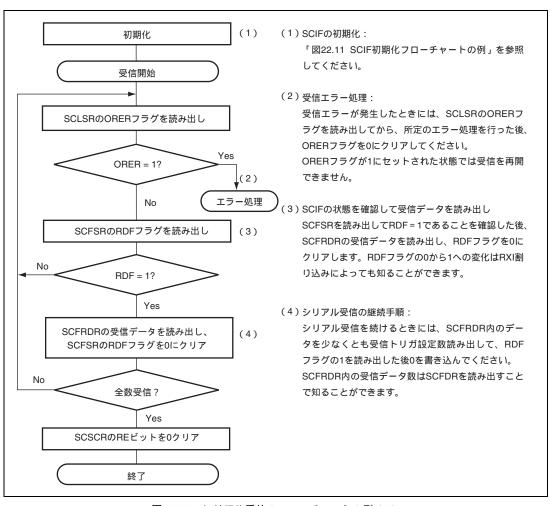

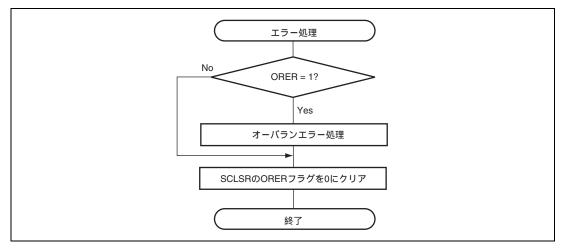

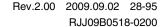

| 22. FIFO | 内蔵シリアルコミュニケーションインタフェース (SCIF)             | 22-1  |

| 22.1     | 特長                                        | 22-1  |

| 22.2     | 入出力端子                                     | 22-3  |

| 22.3     | レジスタの説明                                   | 22-4  |

| 22.3.1   | レシープシフトレジスタ 0~2 ( SCRSR0~SCRSR2 )         | 22-6  |

| 22.3.2   | レシープ FIFO データレジスタ 0~2 ( SCFRDR0~SCFRDR2 ) | 22-6  |

| 22.3.3   | トランスミットシフトレジスタ 0~2 ( SCTSR0~SCTSR2 )      | 22-6  |

| 22.3.4   | トランスミット FIFO データレジスタ 0~2(SCFTDR0~SCFTDR2) | 22-6  |

| 22.3.5   | シリアルモードレジスタ0~2(SCSMR0~SCSMR2)             | 22-7  |

| 22.3.6   | シリアルコントロールレジスタ 0~2 ( SCSCR0~SCSCR2 )      | 22-9  |

| 22.3.7   | シリアルステータスレジスタ 0~2 ( SCFSR0~SCFSR2 )       | 22-12 |

| 22.3.8   | ビットレートレジスタ0~2 ( SCBRR0~ SCBRR2 )          | 22-17 |

| 22.3.9   | FIFO コントロールレジスタ 0~2 ( SCFCR0~ SCFCR2 )    | 22-18 |

| 22.3.10  | FIFO データ数レジスタ 0~2 ( SCFDR0~SCFDR2 )       | 22-20 |

| 22.3.11  | ラインステータスレジスタ0~2(SCLSR0~SCLSR2)            | 22-21 |

| 22.4     | 動作説明                                      | 22-22 |

| 22.4.1   | 概要                                        | 22-22 |

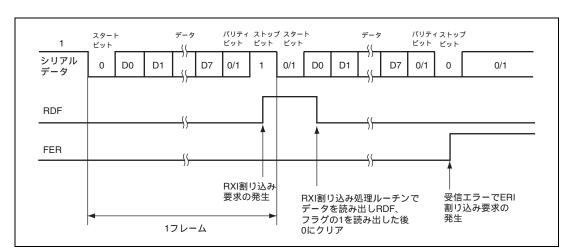

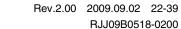

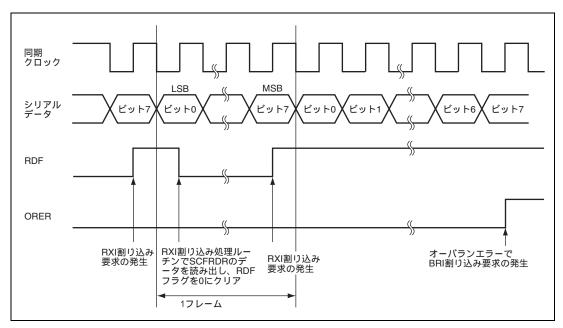

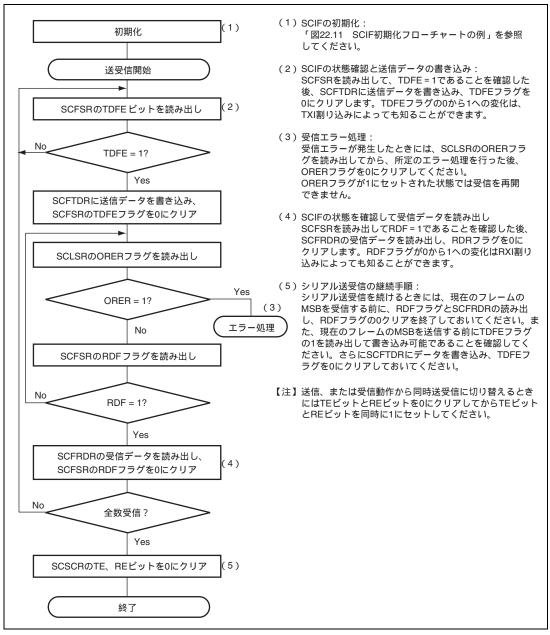

| 22.4.2   | 調歩同期式モードの動作                               | 22-24 |

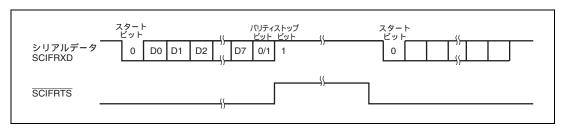

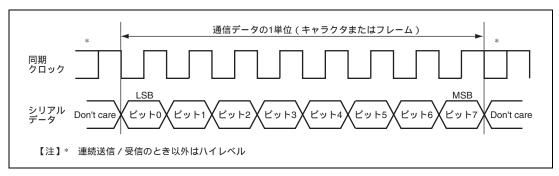

| 22.4.3   | クロック同期式モードの動作                             | 22-34 |

| 22.5    | SCIF割り込み要因とDMAC                       | 22-42 |

|---------|---------------------------------------|-------|

| 22.6    | 使用上の注意事項                              | 22-43 |

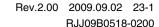

| 3. SIM  | カードモジュール(SIM)                         | 23-1  |

| 23.1    | 特長                                    | 23-1  |

| 23.2    | 入出力端子                                 | 23-2  |

| 23.3    | レジスタの説明                               | 23-3  |

| 23.3.1  | シリアルモードレジスタ ( SCSMR )                 | 23-4  |

| 23.3.2  | ビットレートレジスタ ( SCBRR )                  | 23-5  |

| 23.3.3  | シリアルコントロールレジスタ ( SCSCR )              | 23-5  |

| 23.3.4  | トランスミットシフトレジスタ ( SCTSR )              | 23-7  |

| 23.3.5  | トランスミットデータレジスタ ( SCTDR )              | 23-7  |

| 23.3.6  | シリアルステータスレジスタ ( SCSSR )               | 23-8  |

| 23.3.7  | レシープシフトレジスタ ( SCRSR )                 | 23-12 |

| 23.3.8  | レシーブデータレジスタ ( SCRDR )                 | 23-12 |

| 23.3.9  | スマートカードモードレジスタ ( SCSCMR )             | 23-12 |

| 23.3.10 | シリアルコントロール 2 レジスタ ( SCSC2R )          | 23-14 |

| 23.3.11 | ガードエクステンションレジスタ(SCGRD)                | 23-14 |

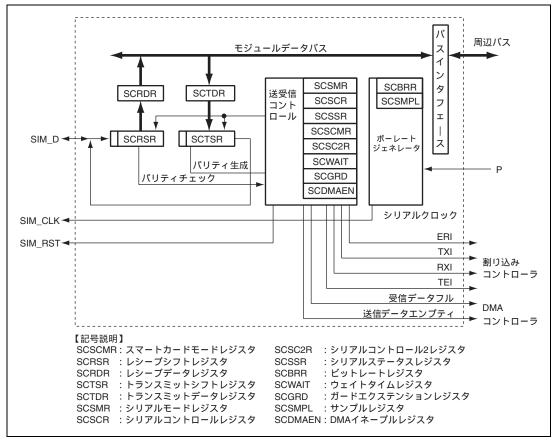

| 23.3.12 | 2 ウェイトタイムレジスタ ( SCWAIT )              | 23-15 |

| 23.3.13 | 3 サンプルレジスタ ( SCSMPL )                 | 23-15 |

| 23.3.14 | 1 DMA イネーブルレジスタ(SCDMAEN)              | 23-16 |

| 23.4    | 動作説明                                  | 23-16 |

| 23.4.1  | 概要                                    | 23-16 |

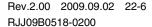

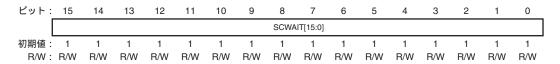

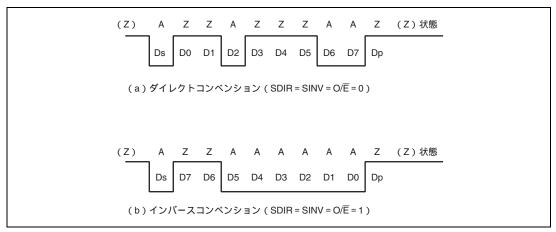

| 23.4.2  | データフォーマット                             | 23-17 |

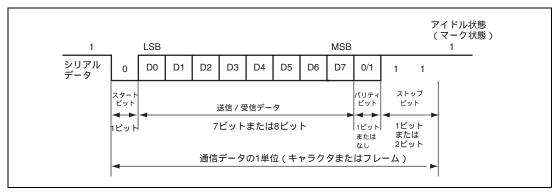

| 23.4.3  | レジスタ設定                                | 23-18 |

| 23.4.4  | クロック                                  | 23-20 |

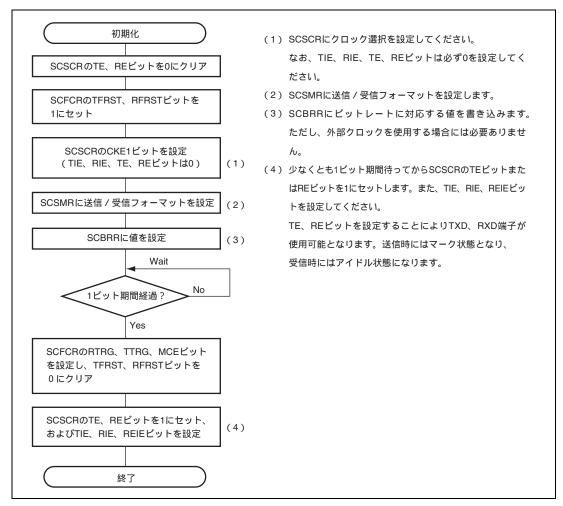

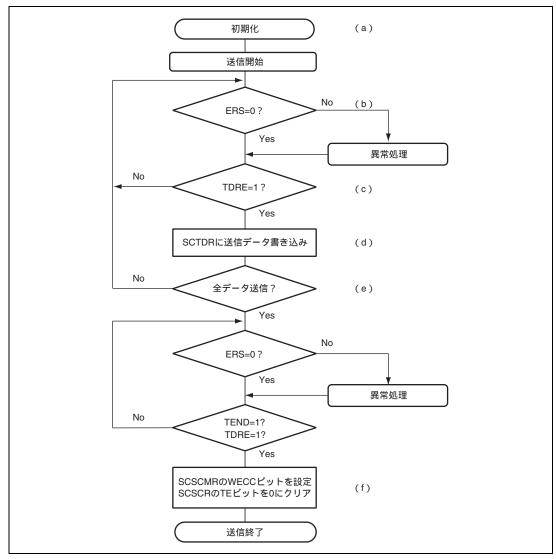

| 23.4.5  | データの送信 / 受信動作                         | 23-21 |

| 23.5    | 使用上の注意事項                              | 23-28 |

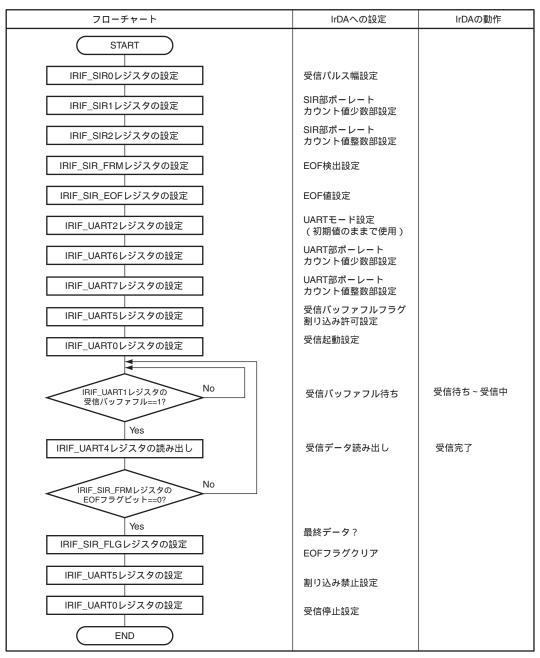

| 4. IrDA | 、インタフェース(IrDA)                        | 24-1  |

| 24.1    | 特長                                    | 24-1  |

| 24.2    | 入出力端子                                 | 24-2  |

| 24.3    | レジスタの説明                               | 24-3  |

| 24.3.1  | DMA 受信割り込み要因クリアレジスタ(IRIF_RINTCLR)     | 24-5  |

| 24.3.2  | DMA 送信割り込み要因クリアレジスタ(IRIF_TINTCLR)     | 24-5  |

| 24.3.3  | IrDA-SIR10 コントロールレジスタ(IRIF_SIR0)      | 24-5  |

| 24.3.4  | IrDA-SIR10 ボーレート誤差補正レジスタ(IRIF_SIR1)   | 24-6  |

| 24.3.5  | IrDA-SIR10 ボーレートカウント設定レジスタ(IRIF_SIR2) | 24-7  |

| 24.3.6  | IrDA-SIR10 ステータスレジスタ(IRIF_SIR3)       | 24-7  |

| 2437    | ハードウェアフレー人処理設定しジスタ(IRIE SIR FRM)      | 24.8  |

| 24.3.8               | EOF 値設定レジスタ(IRIF_SIR_EOF)               | 24-8  |

|----------------------|-----------------------------------------|-------|

| 24.3.9               | フラグクリアレジスタ(IRIF_SIR_FLG)                | 24-9  |

| 24.3.10              | 0 UART ステータスレジスタ 2(IRIF_UART_STS2)      | 24-9  |

| 24.3.11              | 1 UART コントロールレジスタ ( IRIF_UART0 )        | 24-10 |

| 24.3.12              | 2 UART ステータスレジスタ(IRIF_UART1)            | 24-11 |

| 24.3.13              | 3 UART モードレジスタ (IRIF_UART2)             | 24-13 |

| 24.3.14              | 4 UART 送信データレジスタ(IRIF_UART3)            | 24-14 |

| 24.3.15              | 5 UART 受信データレジスタ(IRIF_UART4)            | 24-14 |

| 24.3.10              | 6 UART 割り込みマスクレジスタ(IRIF_UART5)          | 24-15 |

| 24.3.17              | 7 UART ボーレート誤差補正レジスタ(IRIF_UART6)        | 24-16 |

| 24.3.18              | 8 UART ボーレートカウントレジスタ(IRIF_UART7)        | 24-16 |

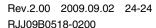

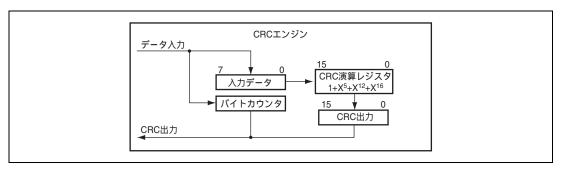

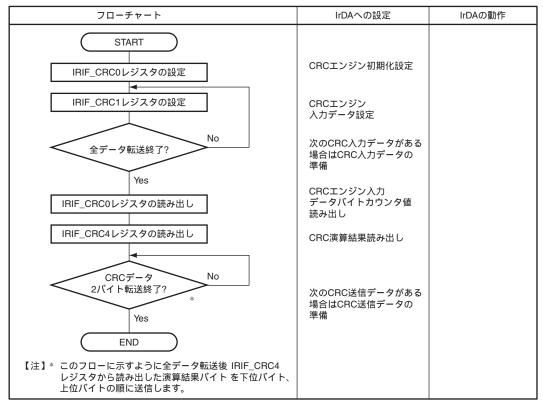

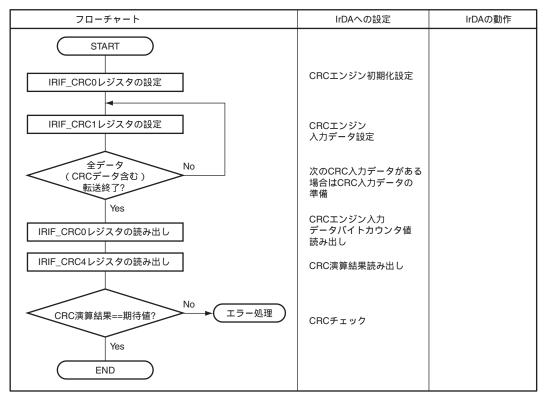

| 24.3.19              | 9 CRC エンジンコントロールレジスタ ( IRIF_CRC0 )      | 24-17 |

| 24.3.20              | 0 CRC エンジン入力データレジスタ(IRIF_CRC1)          | 24-17 |

| 24.3.21              | 1 CRC エンジン演算レジスタ(IRIF_CRC2)             | 24-18 |

| 24.3.22              | 2 CRC エンジン出力データレジスタ 1(IRIF_CRC3)        | 24-18 |

| 24.3.23              | 3 CRC エンジン出力データレジスタ 2(IRIF_CRC4)        | 24-18 |

| 24.4                 | 機能説明                                    | 24-19 |

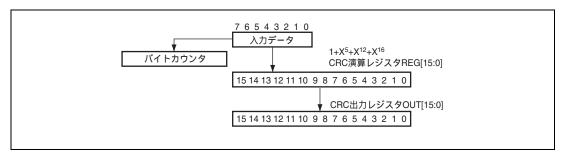

| 24.4.1               | UART                                    | 24-19 |

| 24.4.2               | 発受光パルス変復調動作                             | 24-22 |

| 24.4.3               | CRC エンジン                                | 24-25 |

| 24.4.4               | 送受信フロー                                  | 24-26 |

| 24.5                 | データ送受信における注意事項                          | 24-30 |

|                      |                                         |       |

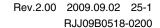

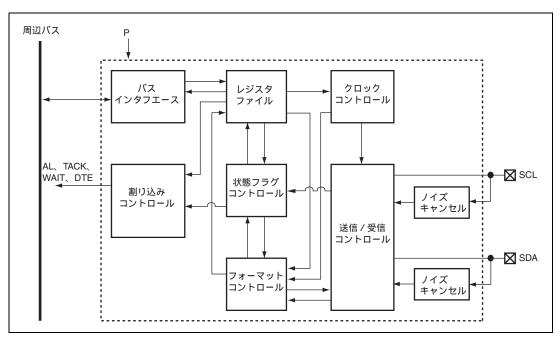

| 25. I <sup>*</sup> C | バスインタフェース(IIC)                          | 25-1  |

| 25.1                 | 特長                                      | 25-1  |

| 25.2                 | 入出力端子                                   | 25-3  |

| 25.3                 | レジスタの説明                                 | 25-4  |

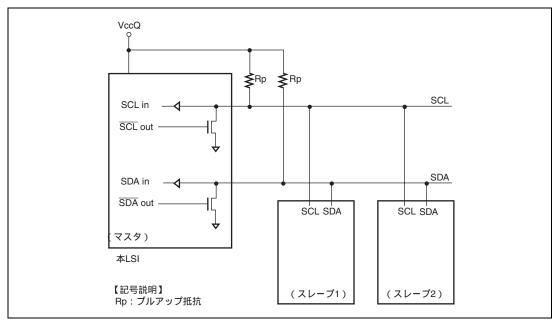

| 25.3.1               | I'C バスデータレジスタ(ICDR)                     | 25-5  |

| 25.3.2               | I <sup>2</sup> C バスコントロールレジスタ(ICCR)     | 25-5  |

| 25.3.3               | I <sup>2</sup> C バスステータスレジスタ(ICSR)      | 25-7  |

| 25.3.4               | I'C 割り込みコントロールレジスタ(ICIC)                | 25-10 |

| 25.3.5               | I'C クロックコントロールレジスタロー ( ICCL )           | 25-11 |

| 25.3.6               | I <sup>2</sup> C クロックコントロールレジスタハイ(ICCH) | 25-11 |

| 25.3.7               | 転送レート                                   | 25-12 |

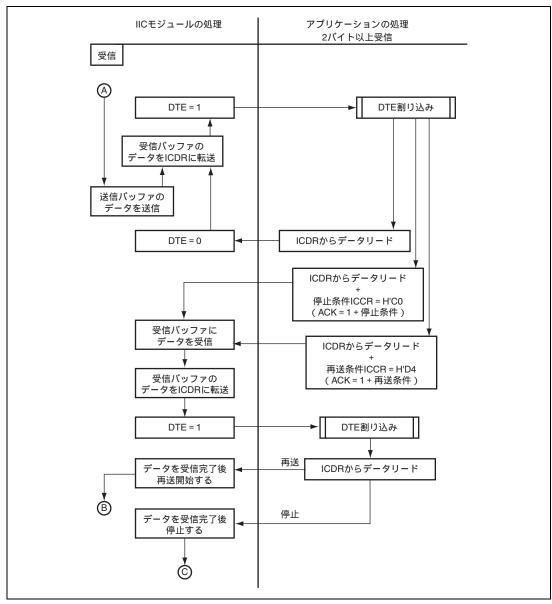

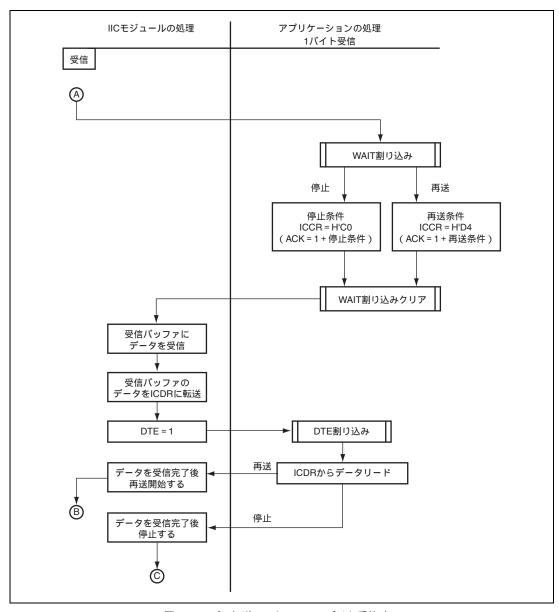

| 25.4                 | 動作説明                                    | 25-14 |

| 25.4.1               | I <sup>2</sup> C バスデータフォーマット            | 25-14 |

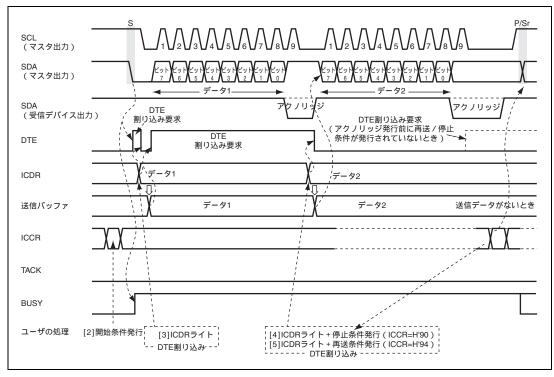

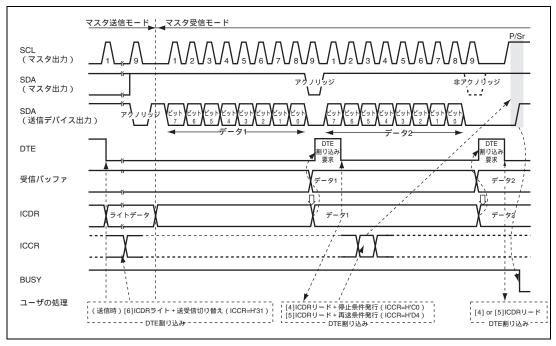

| 25.4.2               | マスタ送信動作                                 | 25-17 |

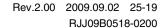

| 25.4.3               | マスタ受信動作                                 | 25-18 |

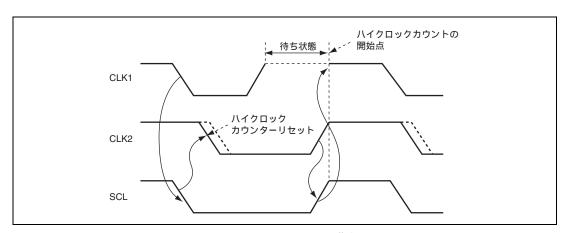

| 25.4.4               | SCL ラインの同期化                             | 25-24 |

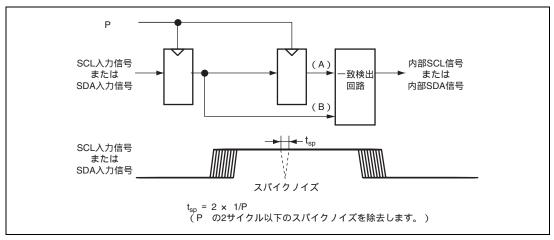

| 25.4.5               | ノイズ除去回路                                 | 25-25 |

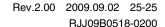

| 25.4.6  | アービトレーションロスト動作                       | 25-25 |

|---------|--------------------------------------|-------|

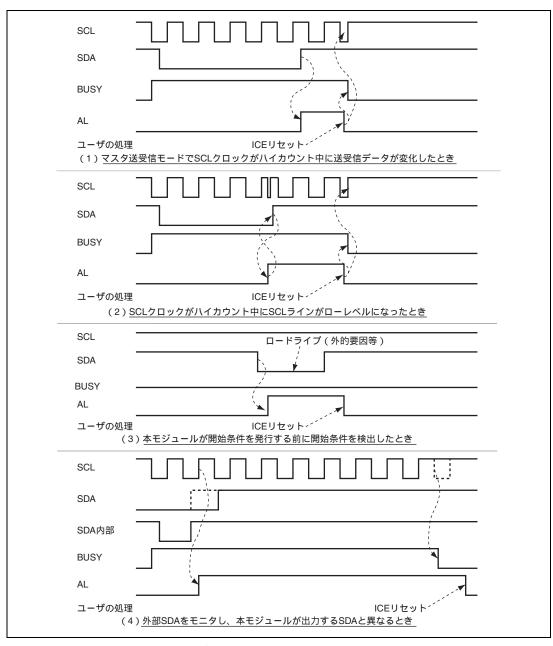

| 25.4.7  | 非アクノリッジ動作                            | 25-27 |

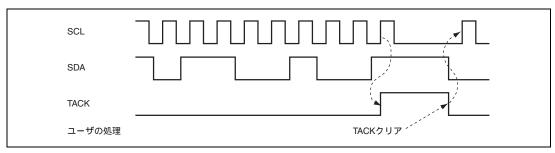

| 25.4.8  | ウェイト動作                               | 25-28 |

| 25.5    | 使用上の注意事項                             | 25-33 |

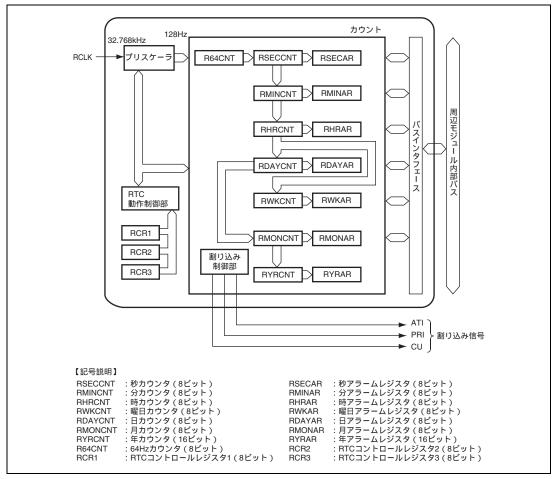

| 26. リア  | 'ルタイムクロック(RTC)                       | 26-1  |

| 26.1    | 特長                                   | 26-1  |

| 26.2    | 入出力端子                                | 26-3  |

| 26.3    | レジスタの説明                              | 26-3  |

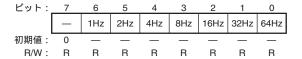

| 26.3.1  | 64Hz カウンタ(R64CNT)                    | 26-4  |

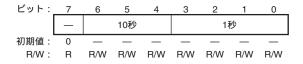

| 26.3.2  | 秒カウンタ(RSECCNT)                       | 26-5  |

| 26.3.3  | 分カウンタ(RMINCNT)                       | 26-6  |

| 26.3.4  | 時カウンタ(RHRCNT)                        | 26-6  |

| 26.3.5  | 曜日カウンタ(RWKCNT)                       | 26-7  |

| 26.3.6  | 日カウンタ(RDAYCNT)                       | 26-8  |

| 26.3.7  | 月カウンタ(RMONCNT)                       | 26-8  |

| 26.3.8  | 年カウンタ ( RYRCNT )                     | 26-9  |

| 26.3.9  | 秒アラームレジスタ ( RSECAR )                 |       |

| 26.3.10 |                                      |       |

| 26.3.11 |                                      |       |

| 26.3.12 |                                      |       |

| 26.3.13 |                                      |       |

| 26.3.14 |                                      |       |

| 26.3.15 |                                      |       |

| 26.3.16 |                                      |       |

| 26.3.17 |                                      |       |

| 26.3.18 |                                      |       |

| 26.4    | 動作説明                                 |       |

| 26.4.1  | 電源投入後のレジスタの初期設定                      |       |

| 26.4.2  | 時刻設定手順                               |       |

| 26.4.3  | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |       |

| 26.4.4  | アラーム機能                               | 26-19 |

| 26.5    | 使用上の注意事項                             | 26-20 |

| 26.5.1  | RTC カウント動作時のレジスタ書き込みについて             |       |

| 26.5.2  | リアルタイムクロック (RTC) の周期割り込みの使用について      |       |

| 26.5.3  | レジスタ設定後のスタンバイ遷移について                  |       |

| 26.5.4  | 30 秒アジャスト機能の使用について                   |       |

|         |                                      |       |

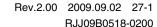

| 27. LCE | ) コントローラ (LCDC)                      |       |

| 27.1    | 特長                                   | 27-1  |

| 27.2   | 端子構成                                     | 27-5  |

|--------|------------------------------------------|-------|

| 27.3   | レジスタの説明                                  | 27-6  |

| 27.3.1 | LCDC パレットデータレジスタ 00~FF (LDPR00~LDPRFF)   | 27-11 |

| 27.3.2 | メイン LCD ドットクロックパターンレジスタ 1 (MLDDCKPATIR)  | 27-11 |

| 27.3.3 | メイン LCD ドットクロックパターンレジスタ 2(MLDDCKPAT2R)   | 27-12 |

| 27.3.4 | サブ LCD ドットクロックパターンレジスタ 1(SLDDCKPATIR)    | 27-12 |

| 27.3.5 | サブ LCD ドットクロックパターンレジスタ 2(SLDDCKPAT2R)    | 27-13 |

| 27.3.6 | LCDC ドットクロックレジスタ(LDDCKR)                 | 27-13 |

| 27.3.7 | ドットクロックストップレジスタ(LDDCKSTPR)               | 27-14 |

| 27.3.8 | メイン LCD モジュールタイプレジスタ 1(MLDMT1R)          | 27-15 |

| 27.3.9 | メイン LCD モジュールタイプレジスタ 2(MLDMT2R)          | 27-18 |

| 27.3.1 | 0 メイン LCD モジュールタイプレジスタ 3 (MLDMT3R)       | 27-19 |

| 27.3.1 | 1 メイン LCD データフォーマットレジスタ ( MLDDFR )       | 27-20 |

| 27.3.1 | 2 メイン LCD スキャンモードレジスタ 1 (MLDSMIR)        | 27-22 |

| 27.3.1 | 3 メイン LCD スキャンモードレジスタ 2 ( MLDSM2R )      | 27-23 |

| 27.3.1 | 4 メイン LCD 表示データ取り込み開始アドレスレジスタ 1(MLDSAIR) | 27-23 |

| 27.3.1 | 5 メイン LCD 表示データ取り込み開始アドレスレジスタ 2(MLDSA2R) | 27-24 |

| 27.3.1 | 6 メイン LCD 表示データ格納メモリラインサイズレジスタ(MLDMLSR)  | 27-24 |

| 27.3.1 | 7 メイン LCD 書き戻しデータフォーマットレジスタ(MLDWBFR)     | 27-25 |

| 27.3.1 | 8 メイン LCD 書き戻し制御レジスタ(MLDWBCNTR)          | 27-27 |

| 27.3.1 | 9 メイン LCD 書き戻し先開始アドレスレジスタ(MLDWBAR)       | 27-28 |

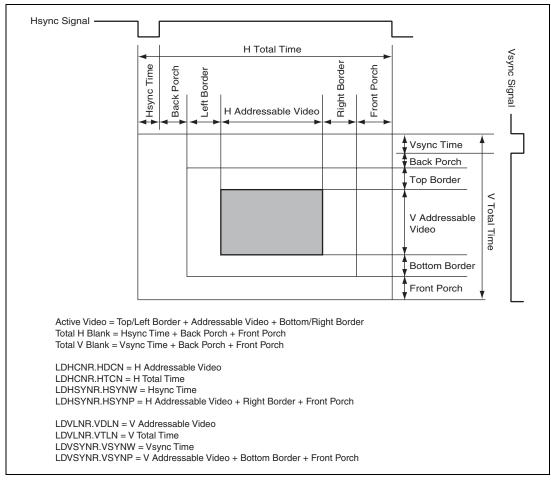

| 27.3.2 | 0 メイン LCD 水平キャラクタナンバーレジスタ(MLDHCNR)       | 27-28 |

| 27.3.2 | .1 メイン LCD 水平同期信号レジスタ(MLDHSYNR)          | 27-29 |

| 27.3.2 | 2 メイン LCD 垂直ラインナンバーレジスタ(MLDVLNR)         | 27-30 |

| 27.3.2 | 3 メイン LCD 垂直同期信号レジスタ(MLDVSYNR)           | 27-31 |

| 27.3.2 | 4 メイン LCD 水平パーシャル画面レジスタ(MLDHPDR)         | 27-32 |

| 27.3.2 | 5 メイン LCD 垂直パーシャル画面レジスタ(MLDVPDR)         | 27-33 |

| 27.3.2 | 6 メイン LCD パワーマネジメントレジスタ ( MLDPMR )       | 27-34 |

| 27.3.2 | 7 LCDC パレット制御レジスタ(LDPALCR)               | 27-36 |

| 27.3.2 | 8 LCDC 割り込みレジスタ(LDINTR)                  | 27-37 |

| 27.3.2 | 9 LCDC ステータスレジスタ ( LDSR )                | 27-40 |

| 27.3.3 | 0 LCDC 制御レジスタ 1 (LDCNT1R)                | 27-41 |

| 27.3.3 | 1 LCDC 制御レジスタ 2 (LDCNT2R)                | 27-42 |

| 27.3.3 | 2 LCDC レジスタ面切り替え制御レジスタ(LDRCNTR)          | 27-44 |

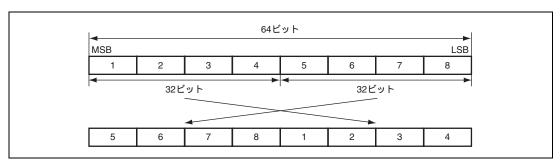

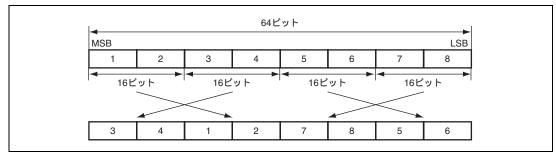

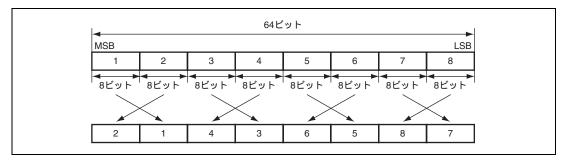

| 27.3.3 | 3 LCDC 入力画像データスワップレジスタ(LDDDSR)           | 27-45 |

| 27.3.3 | 4 LCDC レジスタ面強制指定レジスタ(LDRCR)              | 27-46 |

| 27.3.3 | 5 サブ LCD モジュールタイプレジスタ 1 ( SLDMT1R )      | 27-46 |

| 27.3.3 | 6 サブ LCD モジュールタイプレジスタ 2(SLDMT2R)         | 27-48 |

| 27.3.3 | 7 サブ LCD モジュールタイプレジスタ 3(SLDMT3R)         | 27-49 |

| 27.3.3 | 8 サブ LCD データフォーマットレジスタ ( SLDDFR )        | 27-50 |

| 27.3.3 | 9 サブ LCD スキャンモードレジスタ 1 ( SLDSM1R )       | 27-52 |

| 27.3.40 | , , , , , , , , , , , , , , , , , , , ,       |       |

|---------|-----------------------------------------------|-------|

| 27.3.41 | , , , , , , , , , , , , , , , , , , , ,       |       |

| 27.3.42 | , , , , , , , , , , , , , , , , , , , ,       |       |

| 27.3.43 |                                               |       |

| 27.3.44 |                                               |       |

| 27.3.45 | , , , , , , , , , , , , , , , , , , , ,       |       |

| 27.3.46 | 5 サブ LCD 垂直ラインナンバーレジスタ(SLDVLNR )              | 27-57 |

| 27.3.47 | ゲーサブ LCD 垂直同期信号レジスタ(SLDVSYNR)                 | 27-58 |

| 27.3.48 | B サブ LCD 水平パーシャル画面レジスタ(SLDHPDR )              | 27-58 |

| 27.3.49 | サブ LCD 垂直パーシャル画面レジスタ(SLDVPDR )                | 27-59 |

| 27.3.50 | , , , , , , , , , , , , , , , , , , , ,       |       |

| 27.3.51 | LCDC ドライバライトデータレジスタ 0~F ( LDDWD0R ~ LDDWDFR ) | 27-62 |

| 27.3.52 | LCDC ドライバリードデータレジスタ ( LDDRDR )                | 27-63 |

| 27.3.53 | LCDC ドライバライトアクセスレジスタ(LDDWAR)                  | 27-64 |

| 27.3.54 | LCDC ドライバリードアクセスレジスタ(LDDRAR)                  | 27-65 |

| 27.4    | 動作説明                                          | 27-66 |

| 27.4.1  | LCDC 表示性能                                     | 27-66 |

| 27.4.2  | カラーパレット仕様について                                 | 27-66 |

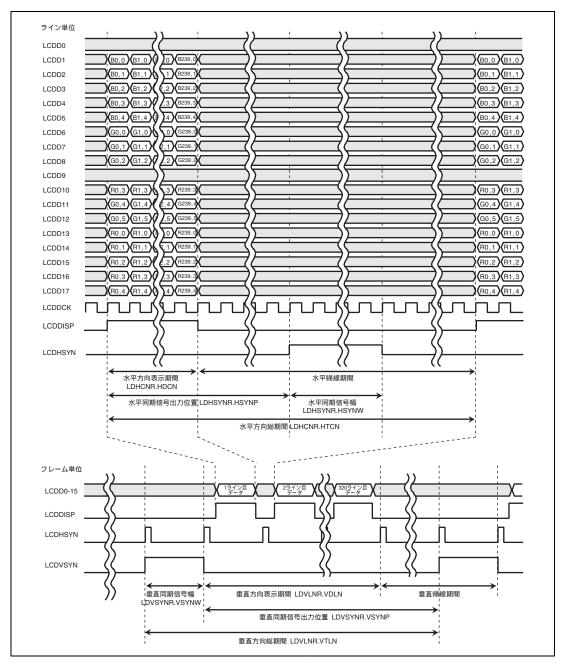

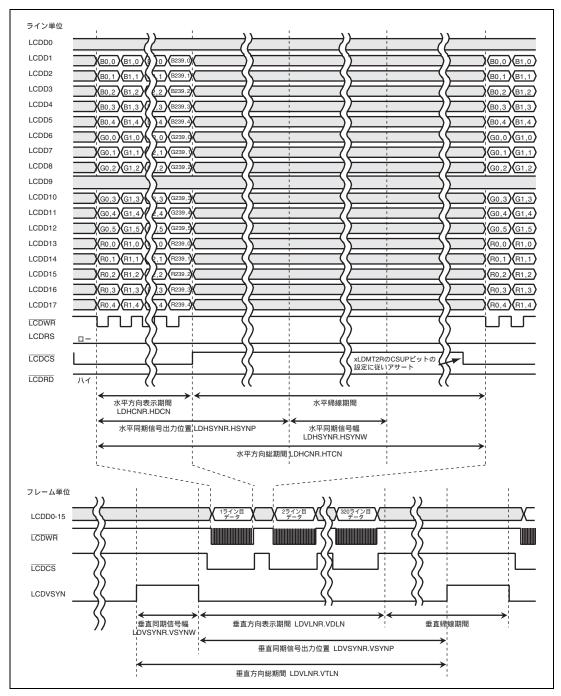

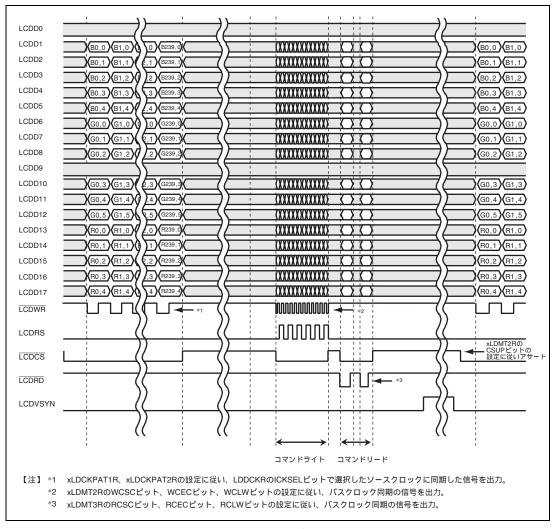

| 27.4.3  | 表示タイミングコントロール                                 | 27-67 |

| 27.4.4  | ワンショットモード                                     | 27-67 |

| 27.4.5  | パーシャル画面モード                                    | 27-68 |

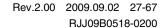

| 27.4.6  | パワーマネジメント                                     | 27-69 |

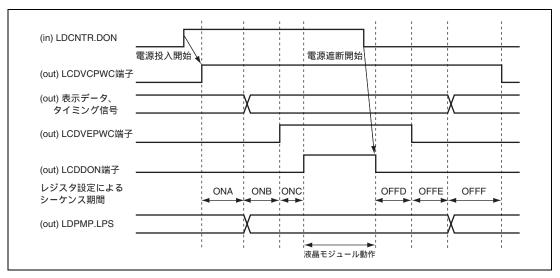

| 27.4.7  | ドットクロック設定例                                    | 27-70 |

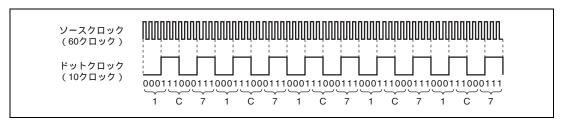

| 27.5    | レジスタ設定方法                                      | 27-71 |

| 27.5.1  | 2 面レジスタの切り替えタイミング                             | 27-71 |

| 27.6    | クロックストップ制御                                    | 27-71 |

| 27.6.1  | 自律クロックストップ                                    | 27-71 |

| 27.7    | クロックと液晶データ信号例                                 | 27-72 |

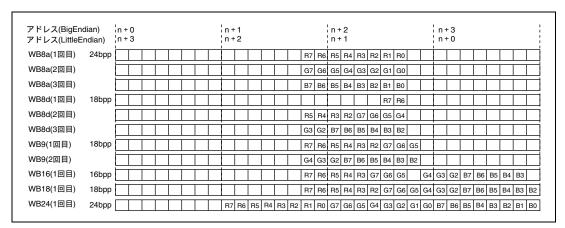

| 27.8    | データフォーマット                                     | 27-75 |

| 27.8.1  | メイン LCD 出力データフォーマット                           | 27-75 |

| 27.8.2  | サブ LCD 出力データフォーマット                            | 27-76 |

| 27.8.3  | 書き戻しデータフォーマット                                 | 27-77 |

| 27.9    | 使用上の注意事項                                      |       |

| 27.9.1  | アドレスレジスタの設定値について                              | 27-77 |

| 27.9.2  | 画像データ入力フォーマット YCbCr4:2:0 時のユーザ指定割り込みの発生について   | 27-77 |

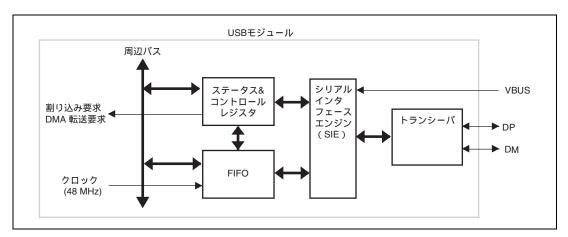

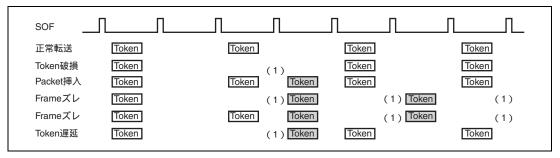

| 28. USE | 3 モジュール(USB)                                  | 28-1  |

| 28.1    | 特長                                            | 28-1  |

| 28.2    | 入出力端子                                         |       |

|         | レジスタの説明                                       | 28_4  |

| 28.3.1  | システムコンフィギュレーションコントロールレジスタ ( SYSCFG )       | 28-8  |

|---------|--------------------------------------------|-------|

| 28.3.2  | システムコンフィギュレーションステータスレジスタ ( SYSSTS )        | 28-10 |

| 28.3.3  | デバイスステートコントロールレジスタ ( DVSTCTR )             | 28-11 |

| 28.3.4  | テストモードレジスタ(TESTMODE)                       | 28-14 |

| 28.3.5  | FIFO バスコンフィギュレーションレジスタ ( CFBCFG、 D0FBCFG ) | 28-15 |

| 28.3.6  | FIFO ポートレジスタ ( CFIFO、 D0FIFO )             | 28-17 |

| 28.3.7  | FIFO ポート選択レジスタ ( CFIFOSEL、 D0FIFOSEL )     | 28-18 |

| 28.3.8  | FIFO ポートコントロールレジスタ ( CFIFOCTR、D0FIFOCTR )  | 28-21 |

| 28.3.9  | CFIFO ポート SIE レジスタ ( CFIFOSIE )            | 28-22 |

| 28.3.10 | D0 トランザクションカウンタレジスタ ( D0FIFOTRN )          | 28-23 |

| 28.3.11 | 割り込み許可レジスタ 0 ( INTENB0 )                   | 28-23 |

| 28.3.12 | 割り込み許可レジスタ 1(INTENB1)                      | 28-25 |

| 28.3.13 | BRDY 割り込み許可レジスタ(BRDYENB)                   | 28-27 |

| 28.3.14 | NRDY 割り込み許可レジスタ(NRDYENB)                   | 28-28 |

| 28.3.15 | BEMP 割り込み許可レジスタ(BEMPENB)                   | 28-29 |

| 28.3.16 | 割り込みステータスレジスタ 0 ( INTSTS0 )                | 28-30 |

| 28.3.17 | 割り込みステータスレジスタ 1(INTSTS1)                   | 28-32 |

| 28.3.18 | BRDY 割り込みステータスレジスタ(BRDYSTS)                | 28-34 |

| 28.3.19 | NRDY 割り込みステータスレジスタ(NRDYSTS)                | 28-35 |

| 28.3.20 | BEMP 割り込みステータスレジスタ(BEMPSTS)                | 28-36 |

| 28.3.21 | フレームナンバレジスタ(FRMNUM)                        | 28-37 |

| 28.3.22 | μ フレームナンバレジスタ(UFRMNUM)                     | 28-38 |

| 28.3.23 | USB アドレスレジスタ(RECOVER)                      | 28-39 |

| 28.3.24 | USB リクエストタイプレジスタ(USBREQ)                   | 28-39 |

| 28.3.25 | USB リクエストバリューレジスタ ( USBVAL )               | 28-40 |

| 28.3.26 | USB リクエストインデックスレジスタ(USBINDX)               | 28-40 |

| 28.3.27 | USB リクエストレングスレジスタ(USBLENG)                 | 28-41 |

| 28.3.28 | DCP コンフィギュレーションレジスタ ( DCPCFG )             | 28-41 |

| 28.3.29 | DCP マックスパケットサイズレジスタ(DCPMAXP)               | 28-42 |

| 28.3.30 | DCP コントロールレジスタ(DCPCTR)                     | 28-43 |

| 28.3.31 | パイプウィンドウ選択レジスタ(PIPESEL )                   | 28-44 |

| 28.3.32 | パイプコンフィギュレーションレジスタ(PIPECFG)                | 28-46 |

| 28.3.33 | パイプバッファ指定レジスタ(PIPEBUF)                     | 28-48 |

| 28.3.34 | パイプマックスパケットサイズレジスタ(PIPEMAXP)               | 28-49 |

| 28.3.35 | パイプ周期制御レジスタ ( PIPEPERI )                   | 28-49 |

| 28.3.36 | PIPEn コントロールレジスタ (PIPEnCTR) (n=1~7)        | 28-51 |

| 28.4    | 動作説明                                       | 28-54 |

| 28.4.1  | システム制御および発振制御                              | 28-54 |

| 28.4.2  | 割り込み機能                                     | 28-56 |

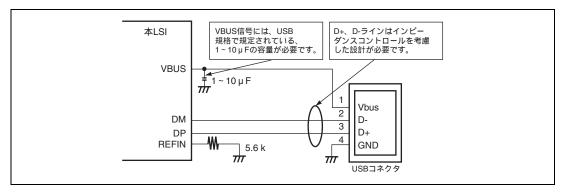

| 28.4.3  | パイプコントロール                                  | 28-69 |

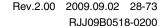

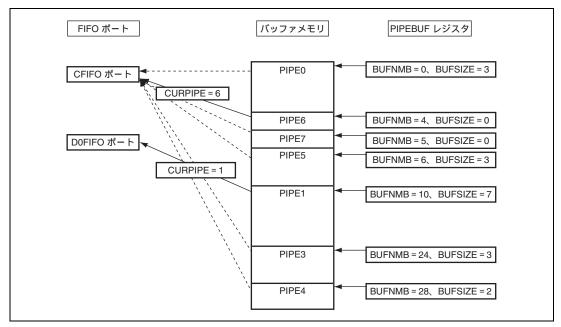

| 28.4.4  | バッファメモリ                                    | 28-74 |

| 28.4.5 | コントロール転送 ( DCP )                     | 28-85 |

|--------|--------------------------------------|-------|

| 28.4.6 | バルク転送(PIPE1~PIPE5)                   | 28-88 |

| 28.4.7 | インタラプト転送(PIPE6、PIPE7)                | 28-89 |

| 28.4.8 | アイソクロナス転送(PIPE1、PIPE2)               | 28-91 |

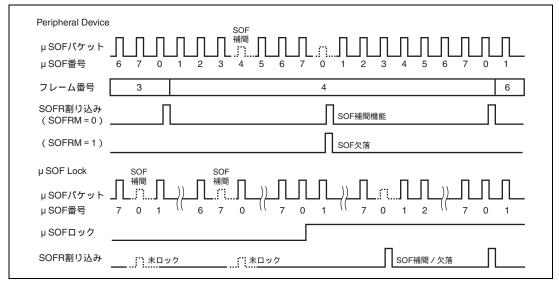

| 28.4.9 | SOF 補間機能                             | 28-96 |

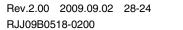

| 28.4.1 | 0 外部回路例                              | 28-97 |

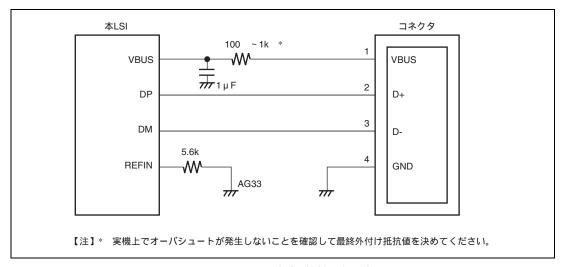

| 29. ‡- | - スキャンインタフェース(KEYSC)                 | 29-1  |

| 29.1   | 特長                                   | 29-1  |

| 29.2   | 入出力端子                                |       |

| 29.3   | レジスタの説明                              | 29-4  |

| 29.3.1 | キースキャンコントロールレジスタ 1(KYCR1)            | 29-5  |

| 29.3.2 | キースキャンコントロールレジスタ 2 ( KYCR2 )         | 29-6  |

| 29.3.3 | キースキャンインデータレジスタ(KYINDR)              | 29-7  |

| 29.3.4 | キースキャンアウトデータレジスタ(KYOUTDR)            | 29-8  |

| 29.4   | 動作説明                                 | 29-9  |

| 29.4.1 | チャタリング除去                             | 29-9  |

| 29.4.2 | キーの多重押し検出                            | 29-9  |

| 29.4.3 | レジスタアクセス                             | 29-9  |

| 29.5   | 使用例                                  | 29-10 |

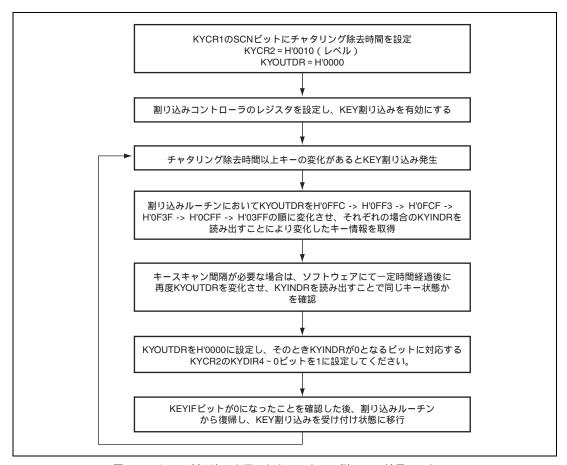

| 29.5.1 | レベル割り込み ( KYCPU_IE1、KYCPU_IE0 = 01 ) | 29-10 |

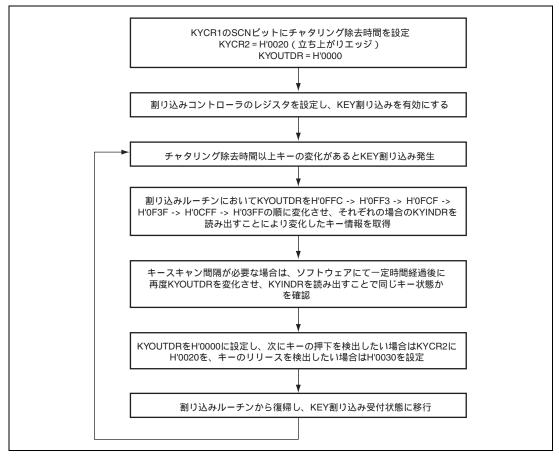

| 29.5.2 | エッジ割り込み(KYCPU_IE1、KYCPU_IE0 = 1x)    | 29-11 |

| 30. ピン | ンファンクションコントローラ(PFC)                  | 30-1  |

| 30.1   | 概要                                   | 30-1  |

| 30.2   | レジスタの説明                              | 30-6  |

| 30.2.1 | ポート A コントロールレジスタ(PACR)               | 30-8  |

| 30.2.2 | ポート B コントロールレジスタ ( PBCR )            | 30-9  |

| 30.2.3 | ポート C コントロールレジスタ(PCCR)               | 30-10 |

| 30.2.4 | ポート D コントロールレジスタ(PDCR)               | 30-12 |

| 30.2.5 | ポート E コントロールレジスタ(PECR)               | 30-13 |

| 30.2.6 | ポートFコントロールレジスタ(PFCR)                 | 30-14 |

| 30.2.7 | ポート G コントロールレジスタ(PGCR)               | 30-16 |

| 30.2.8 | ポート H コントロールレジスタ(PHCR)               | 30-17 |

| 30.2.9 | ポート J コントロールレジスタ ( PJCR )            | 30-18 |

| 30.2.1 | 0 ポート K コントロールレジスタ ( PKCR )          | 30-19 |

| 30.2.1 | 1 ポートLコントロールレジスタ(PLCR)               | 30-20 |

| 30.2.1 | 2 ポート M コントロールレジスタ ( PMCR )          | 30-22 |

| 30.2.1 | 3 ポート N コントロールレジスタ (PNCR)            | 30-23 |

| 30.2.1 | 4 ポート Q コントロールレジスタ ( PQCR )          | 30-24 |

| 30.2.15  | ポート R コントロールレジスタ(PRCR)            | 30-26 |

|----------|-----------------------------------|-------|

| 30.2.16  | ポート S コントロールレジスタ ( PSCR )         | 30-27 |

| 30.2.17  | ポートTコントロールレジスタ(PTCR)              | 30-28 |

| 30.2.18  | ポート U コントロールレジスタ ( PUCR )         | 30-29 |

| 30.2.19  | ポート V コントロールレジスタ(PVCR)            | 30-30 |

| 30.2.20  | ポート W コントロールレジスタ ( PWCR )         | 30-31 |

| 30.2.21  | ポート X コントロールレジスタ ( PXCR )         | 30-32 |

| 30.2.22  | ポート Y コントロールレジスタ ( PYCR )         | 30-33 |

| 30.2.23  | ポート Z コントロールレジスタ ( PZCR )         | 30-34 |

| 30.2.24  | ピンセレクトレジスタ A(PSELA)               | 30-36 |

| 30.2.25  | ピンセレクトレジスタ B ( PSELB )            | 30-37 |

| 30.2.26  | ピンセレクトレジスタ C ( PSELC )            | 30-38 |

| 30.2.27  | ピンセレクトレジスタ D ( PSELD )            | 30-39 |

| 30.2.28  | ピンセレクトレジスタE(PSELE)                | 30-40 |

| 30.2.29  | I/O バッファ Hi-Z 制御レジスタ A(HIZCRA)    | 30-41 |

| 30.2.30  | I/O バッファ Hi-Z 制御レジスタ B(HIZCRB)    | 30-42 |

| 30.2.31  | I/O バッファ Hi-Z 制御レジスタ C ( HIZCRC ) | 30-43 |

| 30.2.32  | モジュール機能選択レジスタ A(MSELCRA)          | 30-45 |

| 30.2.33  | モジュール機能選択レジスタ B ( MSELCRB )       | 30-45 |

| 30.2.34  | プルアップダウン制御レジスタ(PULCR )            | 30-46 |

| 30.2.35  | I/O バッファ Drive 制御レジスタ(DRVCR)      | 30-46 |

| 30.2.36  | SBSC タイミング制御レジスタ ( SBSCR )        | 30-48 |

| 30.2.37  | 端子毎設定一覧表                          | 30-49 |

| 31 1/0 ポ | - h                               | 31_1  |

|          |                                   |       |

|          | ノジスタの説明                           |       |

|          | パートA                              |       |

| 31.2.1   | ポート A データレジスタ(PADR)               |       |

|          | <b>代−</b> トB                      |       |

| 31.3.1   | ポート B データレジスタ ( PBDR )            |       |

|          | <b>K− F</b> C                     |       |

| 31.4.1   | ポート C データレジスタ(PCDR)               |       |

|          | <b>K− F</b> D                     |       |

| 31.5.1   | ポート D データレジスタ(PDDR)               |       |

|          | <b>代−</b> トE                      |       |

| 31.6.1   | ポート E データレジスタ(PEDR)               |       |

|          | <b>代−</b> FF                      |       |

| 31.7.1   | ポート F データレジスタ ( PFDR )            |       |

| 31.8 力   | <b>パー</b> ├ G                     |       |

| 31.8.1   | ポート G データレジスタ ( PGDR )            | 31-9  |

| 31.9 ポートH                               | 31-10 |

|-----------------------------------------|-------|

| 31.9.1 ポート H データレジスタ ( PHDR )           | 31-10 |

| 31.10 ポートJ                              | 31-11 |

| 31.10.1 ポート J データレジスタ ( PJDR )          | 31-11 |

| 31.11 ポートK                              | 31-12 |

| 31.11.1 ポート K データレジスタ ( PKDR )          | 31-12 |

| 31.12 ポートL                              | 31-13 |

| 31.12.1 ポート L データレジスタ ( PLDR )          | 31-13 |

| 31.13 ポートM                              | 31-14 |

| 31.13.1 ポート M データレジスタ ( PMDR )          | 31-14 |

| 31.14 ポートN                              | 31-15 |

| 31.14.1 ポート N データレジスタ ( PNDR )          | 31-15 |

| 31.15 ポートQ                              | 31-16 |

| 31.15.1 ポート Q データレジスタ ( PQDR )          | 31-16 |

| 31.16 ポートR                              | 31-17 |

| 31.16.1 ポート R データレジスタ ( PRDR )          | 31-17 |

| 31.17 ポートS                              | 31-18 |

| 31.17.1 ポート S データレジスタ ( PSDR )          | 31-18 |

| 31.18 ポートT                              | 31-19 |

| 31.18.1 ポート T データレジスタ ( PTDR )          | 31-19 |

| 31.19 ポートU                              | 31-20 |

| 31.19.1 ポート U データレジスタ ( PUDR )          | 31-20 |

| 31.20 ポートV                              | 31-21 |

| 31.20.1 ポート V データレジスタ (PVDR)            | 31-21 |

| 31.21 ポートW                              | 31-22 |

| 31.21.1 ポート W データレジスタ ( PWDR )          | 31-22 |

| 31.22 ポートX                              | 31-23 |

| 31.22.1 ポート X データレジスタ (PXDR)            | 31-23 |

| 31.23 ポートY                              | 31-24 |

| 31.23.1 ポート Y データレジスタ ( PYDR )          | 31-24 |

| 31.24 ポートZ                              | 31-25 |

| 31.24.1 ポート Z データレジスタ ( PZDR )          | 31-25 |

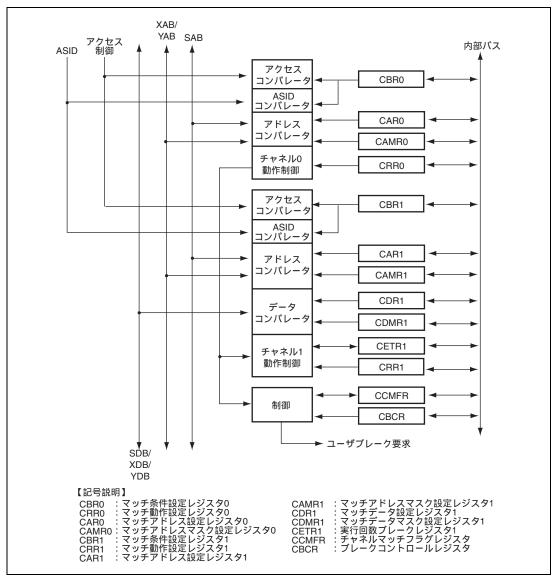

| 32. ユーザプレークコントローラ (UBC)                 | 32-1  |

| 32.1 特長                                 | 32-1  |

| 32.2 レジスタの説明                            |       |

| 32.2.1 マッチ条件設定レジスタ 0、1 (CBR0、CBR1)      | 32-4  |

| 32.2.2 マッチ動作設定レジスタ 0、1 (CRR0、CRR1)      |       |

| 32.2.3 マッチアドレス設定レジスタ 0、1 (CARO、CARI)    |       |

| 32.2.4 マッチアドレスマスク設定レジスタの 1(CAMRO CAMRI) | 32-13 |

| 32.2.5 | マッチデータ設定レジスタ 1 ( CDR1 )  | 32-14 |

|--------|--------------------------|-------|

| 32.2.6 | マッチデータマスク設定レジスタ 1(CDMR1) | 32-15 |

| 32.2.7 | 実行回数ブレークレジスタ 1 ( CETR1 ) | 32-15 |

| 32.2.8 | チャネルマッチフラグレジスタ(CCMFR)    | 32-16 |

| 32.2.9 | ブレークコントロールレジスタ(CBCR)     | 32-17 |

| 32.3   | 動作説明                     | 32-17 |

| 32.3.1 | アクセスに関する用語の説明            | 32-17 |

| 32.3.2 | ユーザブレーク動作の流れ             | 32-18 |

| 32.3.3 | 命令フェッチサイクルブレーク           | 32-19 |

| 32.3.4 | オペランドアクセスサイクルプレーク        | 32-20 |

| 32.3.5 | X メモリまたは Y メモリバスサイクルブレーク | 32-21 |

| 32.3.6 | シーケンシャルプレーク              | 32-22 |

| 32.3.7 | 退避されるプログラムカウンタの値         | 32-23 |

| 32.4   | ユーザブレークデバッグサポート機能        | 32-24 |

| 32.5   | ユーザブレーク使用例               | 32-25 |

| 32.6   | 使用上の注意事項                 | 32-30 |

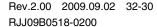

| 33. ユー | -ザデバッグインタフェース(H-UDI)     | 33-1  |

| 33.1   | 特長                       | 33-1  |

| 33.2   | 入出力端子                    | 33-3  |

| 33.3   | レジスタの説明                  | 33-4  |

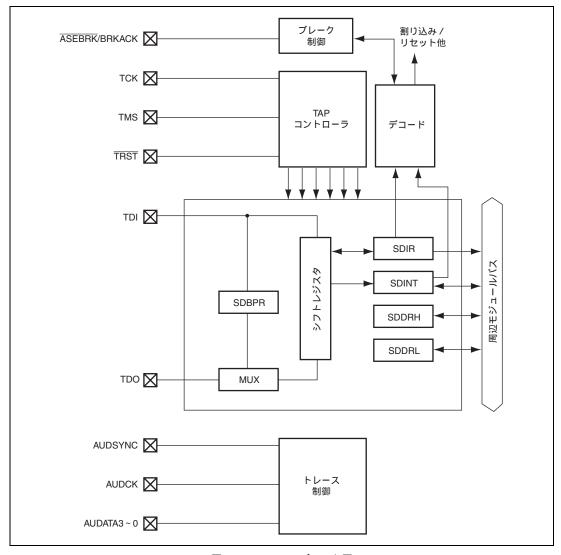

| 33.3.1 | インストラクションレジスタ(SDIR)      | 33-5  |

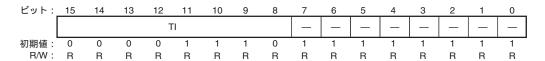

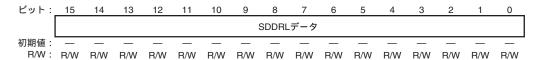

| 33.3.2 | データレジスタ H、L(SDDRH、SDDRL) | 33-5  |

| 33.3.3 | 割り込み要因レジスタ(SDINT)        | 33-6  |

| 33.4   | 動作説明                     | 33-7  |

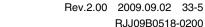

| 33.4.1 | TAP 制御                   | 33-7  |

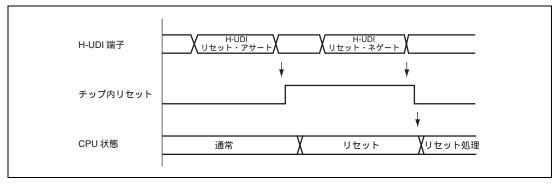

| 33.4.2 | H-UDI リセット               | 33-8  |

| 33.4.3 | H-UDI 割り込み               | 33-8  |

| 33.5   | 注意事項                     | 33-8  |

| 34. レシ | <sup>デ</sup> スター覧        | 34-1  |

| 34.1   | レジスタアドレス一覧               | 34-2  |

| 34.2   | 各動作モードにおけるレジスタの状態        | 34-18 |

| 35. 電気 | <b>贰的特性</b>              | 35-1  |

| 35.1   | 絶対最大定格                   | 35-1  |

| 35.2   | 推奨動作条件                   | 35-1  |

| 35.3   | 電源投入および切断順序              | 35-2  |

| 35.4   | DC特性                     | 35-4  |

| 35.5   | AC特性                     | 35-6  |

|        |                          |       |

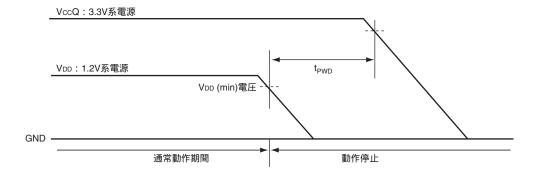

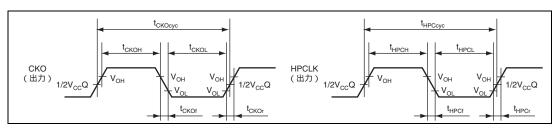

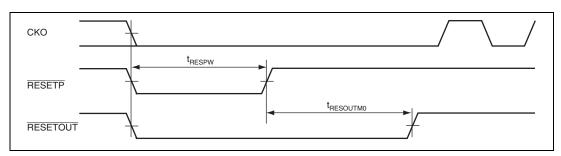

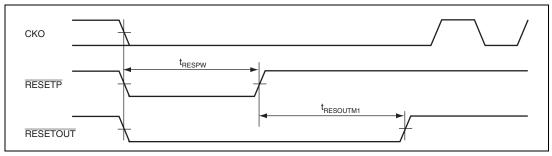

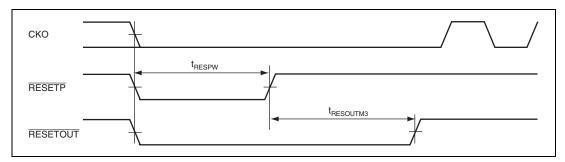

| 35.5. | 1 クロックタイミング                      | 35-7  |

|-------|----------------------------------|-------|

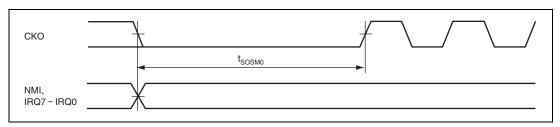

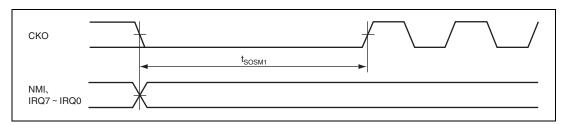

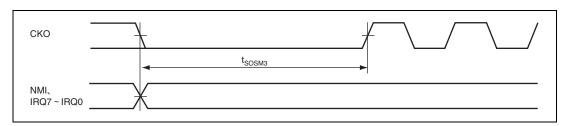

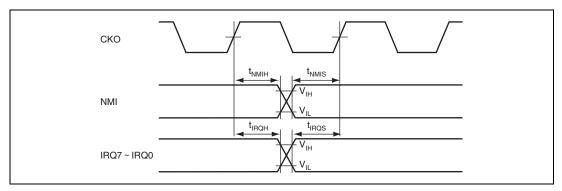

| 35.5. | 2 割り込み信号タイミング                    | 35-10 |

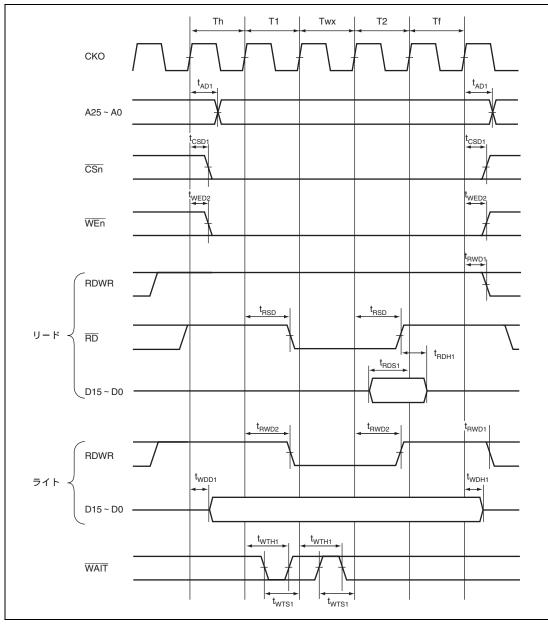

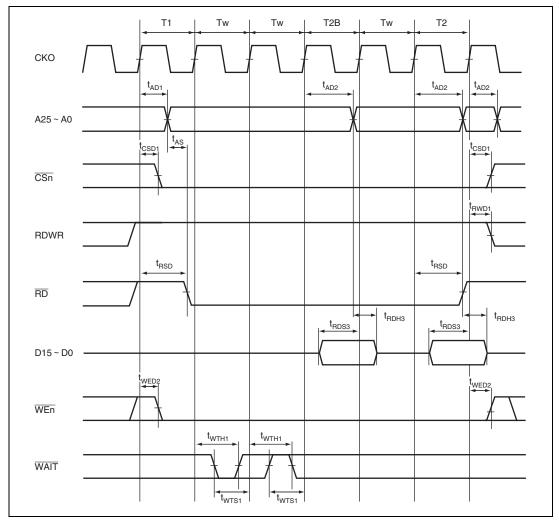

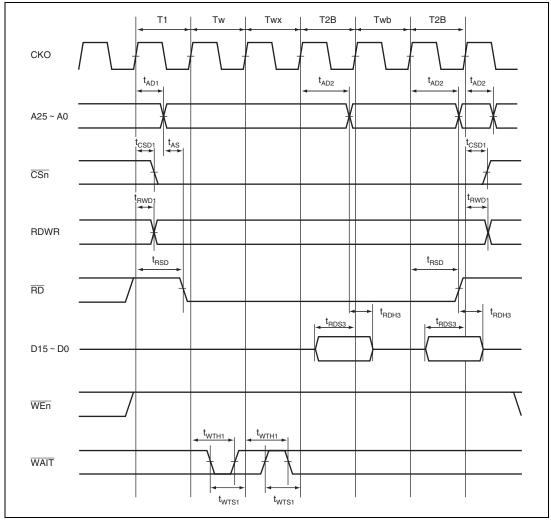

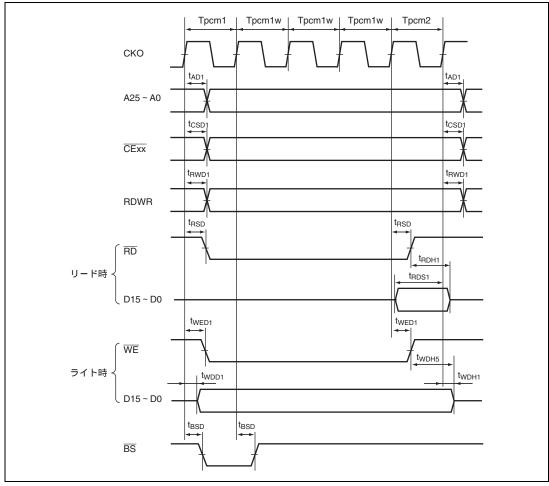

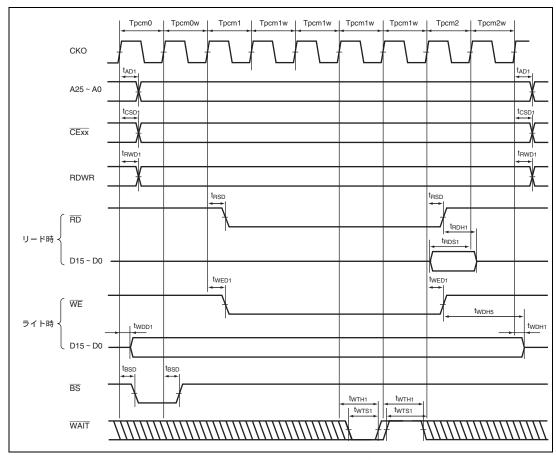

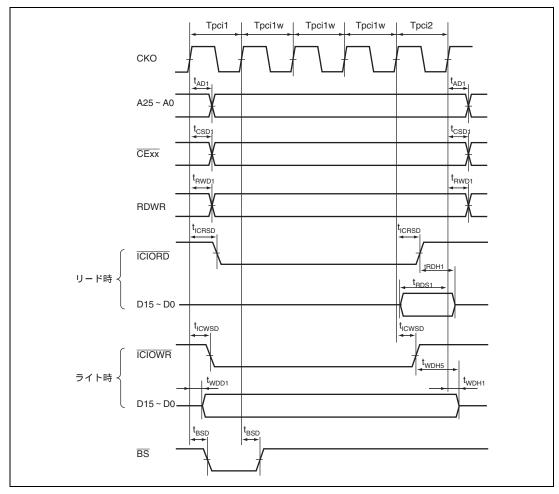

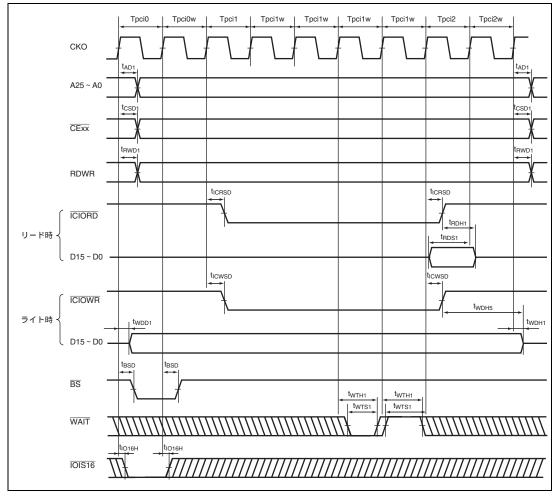

| 35.5. | 3 BSC バスタイミング仕様                  | 35-11 |

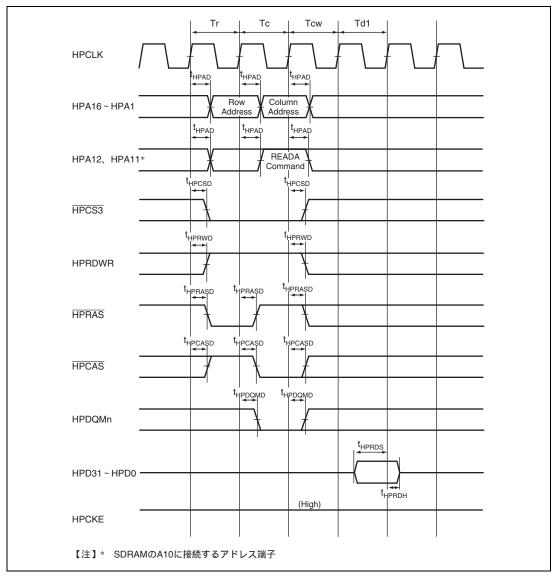

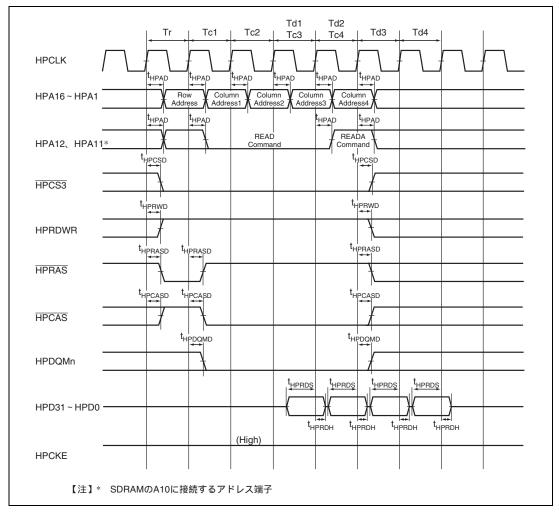

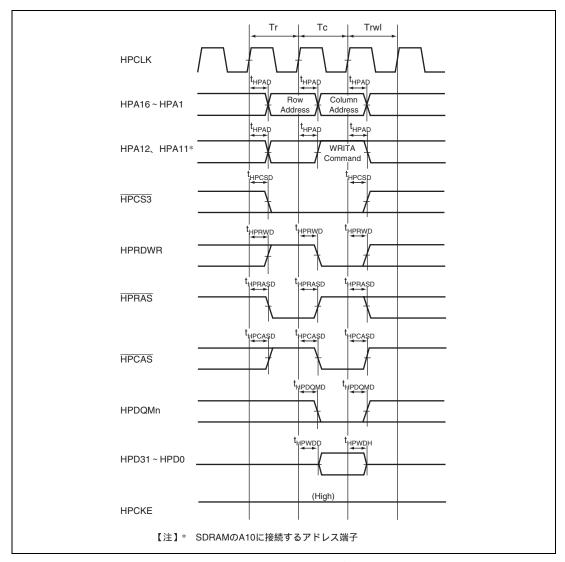

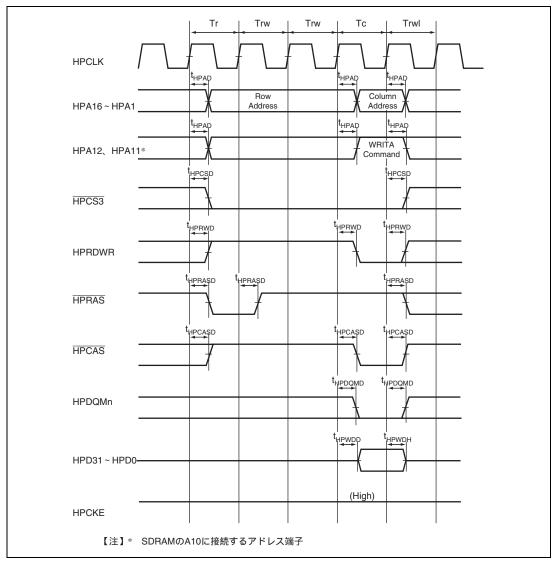

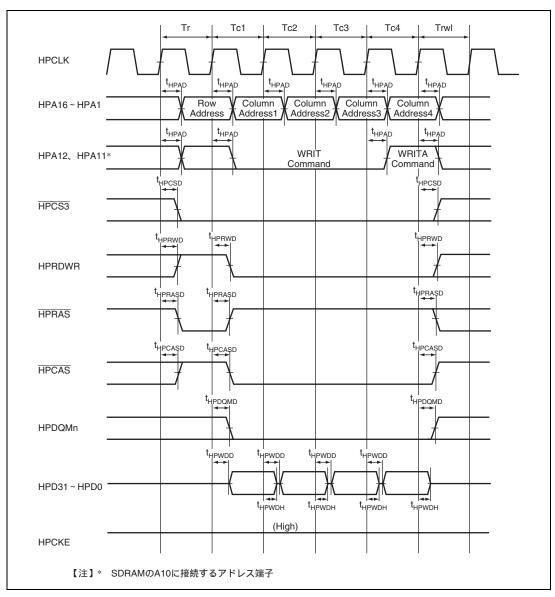

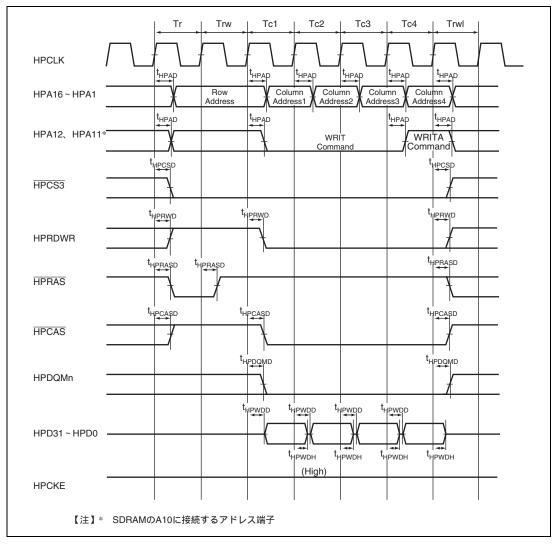

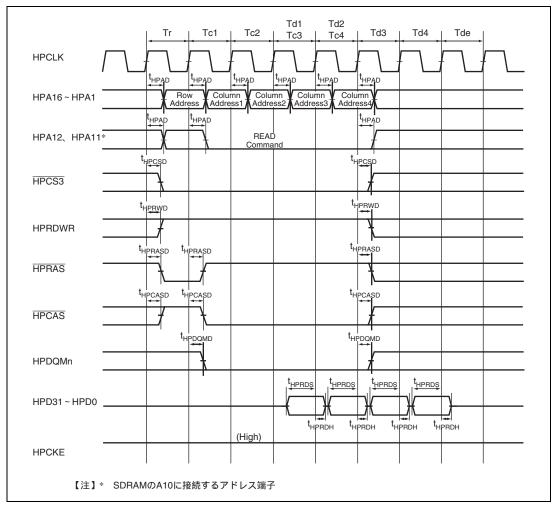

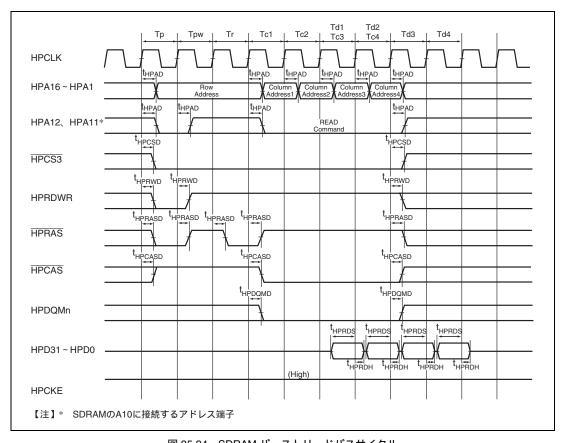

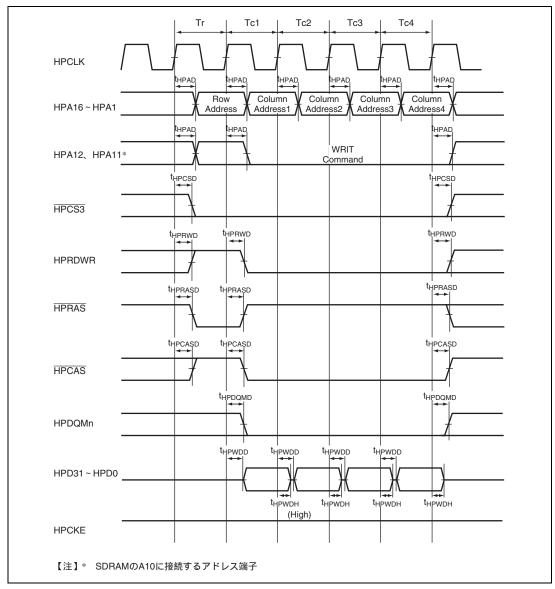

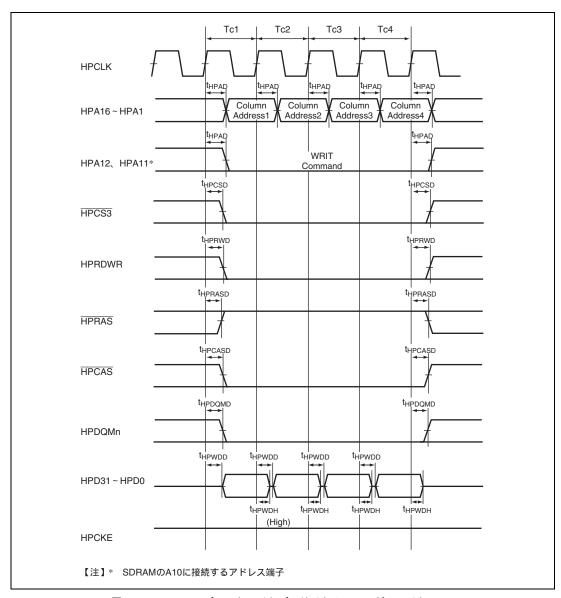

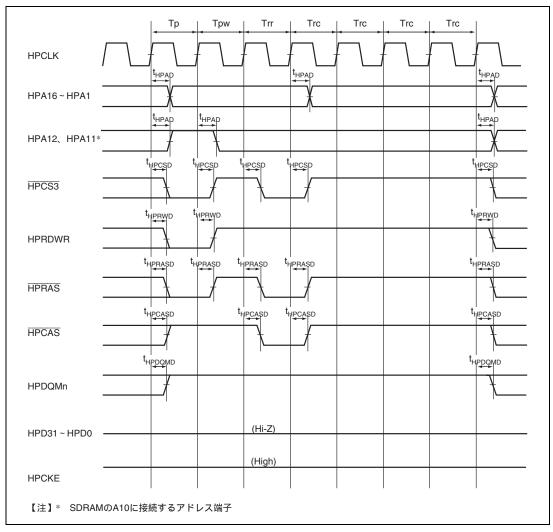

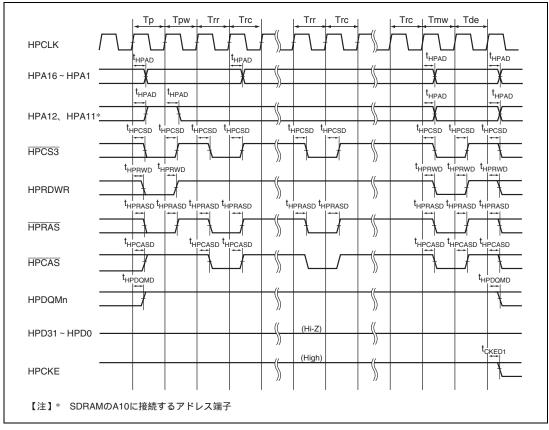

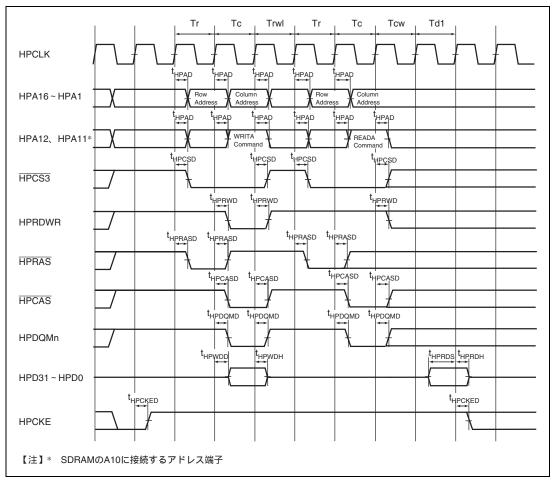

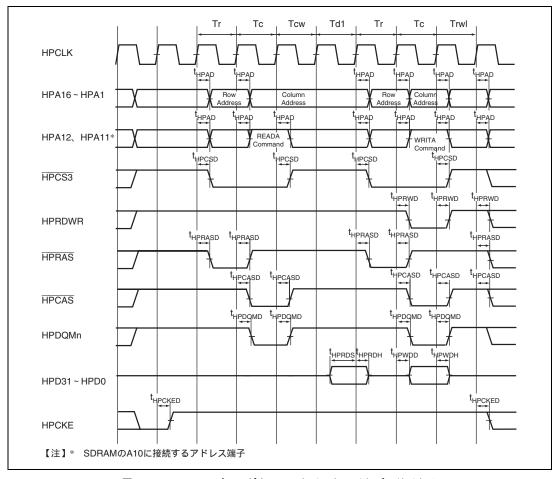

| 35.5. | 4 SDRAM タイミング(SDRAM 専用バス)        | 35-26 |

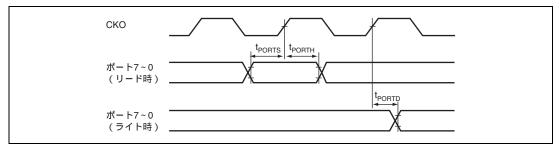

| 35.5. | 5 I/O ポート信号タイミング                 | 35-46 |

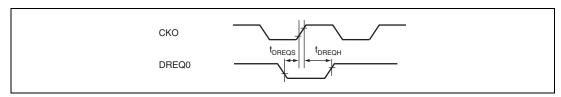

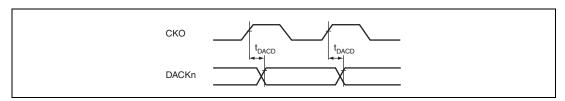

| 35.5. | 6 DMAC モジュール信号タイミング              | 35-46 |

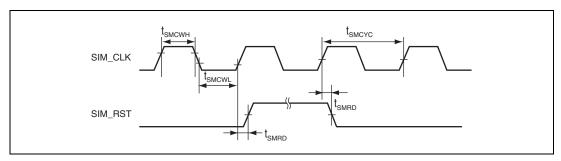

| 35.5. | 7 SIM モジュール信号タイミング               | 35-47 |

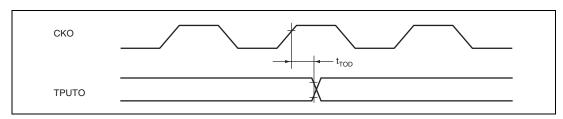

| 35.5. | 8 TPU モジュール信号タイミング               | 35-47 |

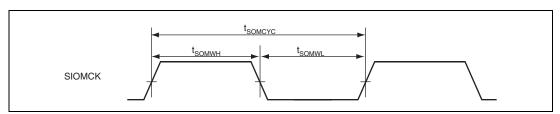

| 35.5. | 9 SIO モジュール信号タイミング               | 35-48 |

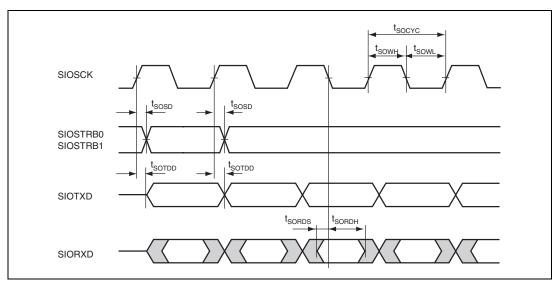

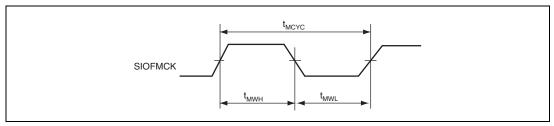

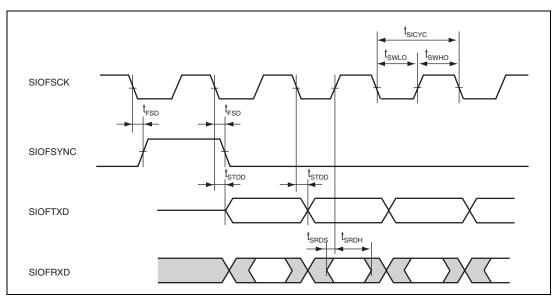

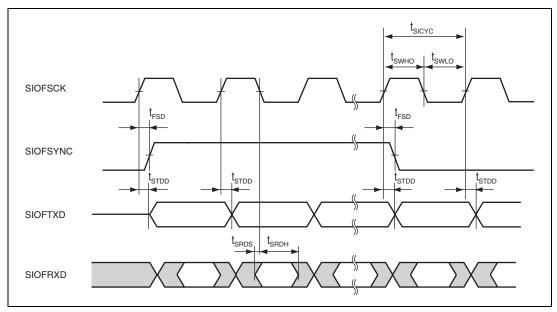

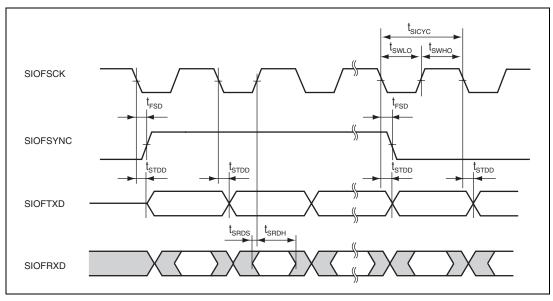

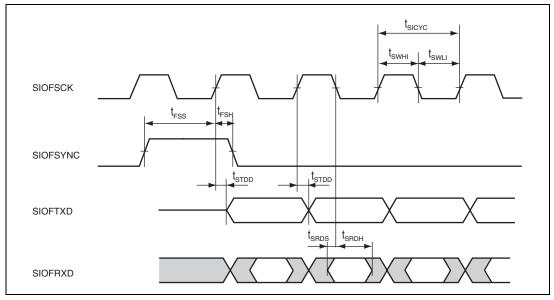

| 35.5. | 10 SIOF モジュール信号タイミング             | 35-51 |

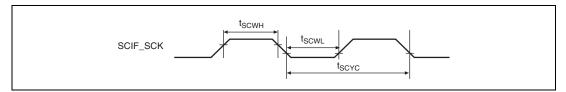

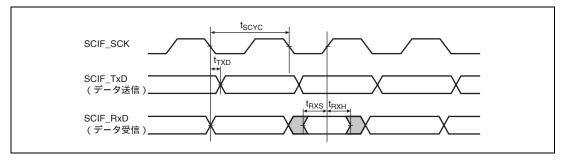

| 35.5. | 11 SCIF モジュール信号タイミング             | 35-55 |

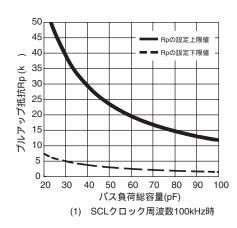

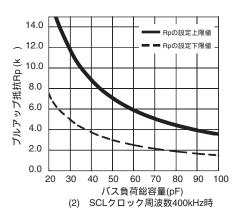

| 35.5. | 12 I <sup>2</sup> C モジュール信号タイミング | 35-57 |

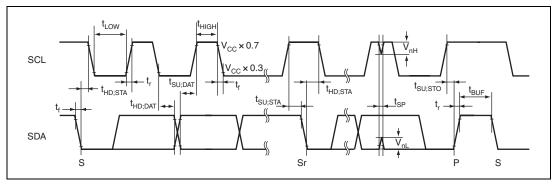

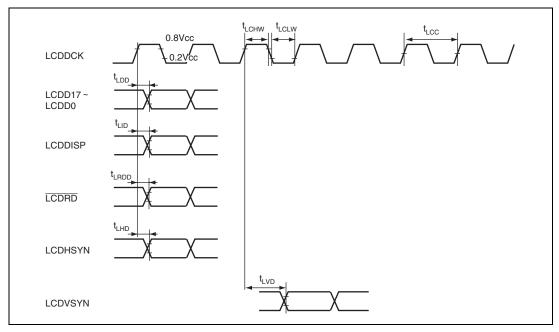

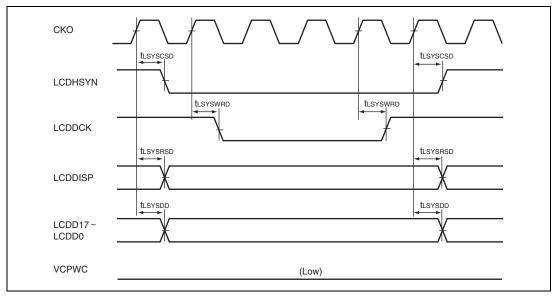

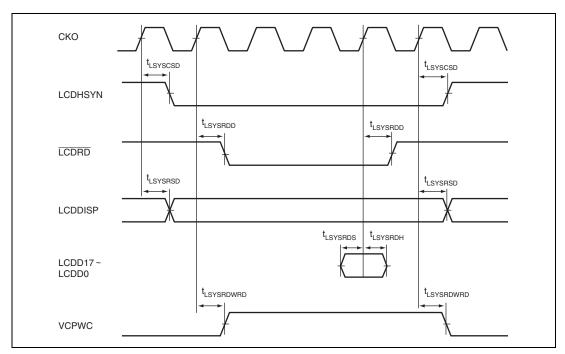

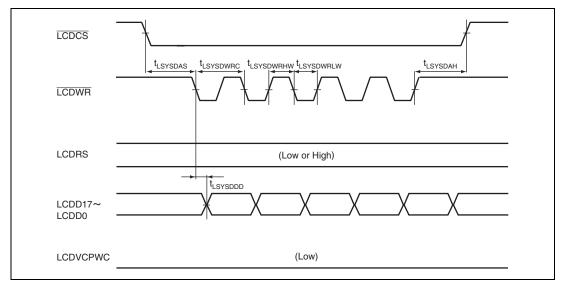

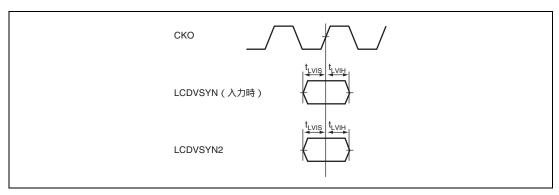

| 35.5. | 13 LCDC モジュール信号タイミング             | 35-58 |

| 35.5. | 14 USB トランシーバタイミング(フルスピード)       | 35-62 |

| 35.5. | 15 KEYSC モジュール信号タイミング            | 35-63 |

| 35.5. | 16 AC 特性測定条件                     | 35-64 |

| 付録    |                                  | 付録-1  |

| A.    | CPU動作モードレジスタ(CPUOPM)             | 付録-1  |

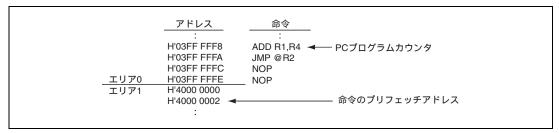

| B.    | 命令プリフェッチとその副作用について               | 付録-2  |

| C.    | リセット、低消費電力状態での端子状態               | 付録-3  |

| D.    | SH7731型名一覧                       | 付録-10 |

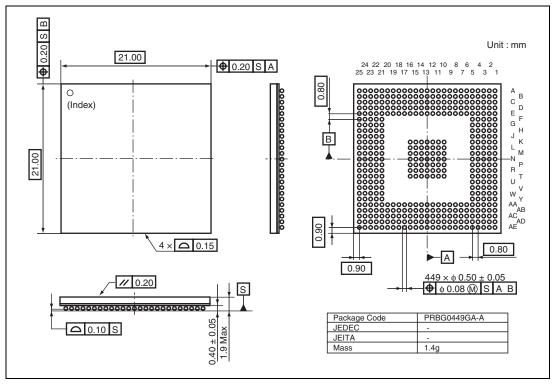

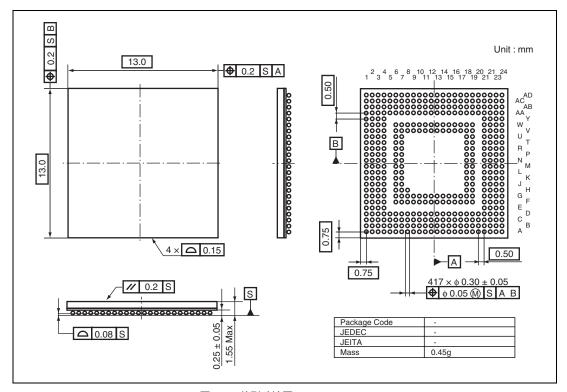

| E.    | 外形寸法図                            | 付録-10 |

| 本版で改  | <b>攻訂された箇所</b>                   | 改-1   |

| 索引    |                                  | 索引-1  |

# 1. 概要

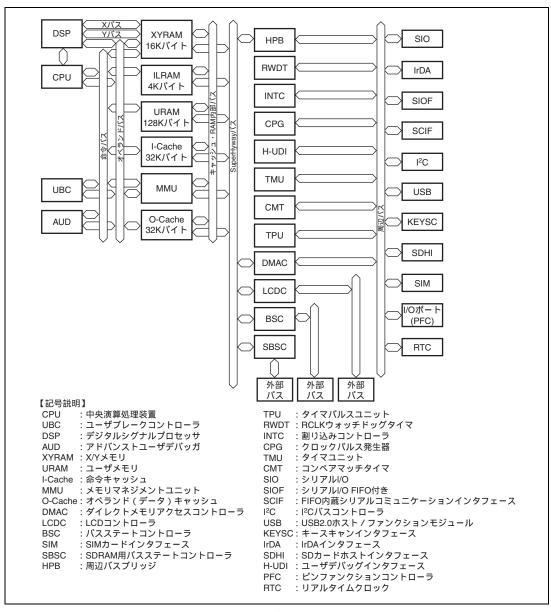

SH7731 は、最大 333MHz 動作可能な SH4AL-DSP をコアとして、システム構成に必要とされる周辺機能を内蔵した RISC マイクロプロセッサです。SH7731 は、64 ビット SDRAM インタフェース、128K バイトユーザメモリ、LCD コントローラ、USB2.0 ハイスピード対応ホスト / ファンクションをはじめとする豊富な周辺機能を搭載しています。

また、強力なパワーマネジメント機能により、動作電流や待機電流を低く抑えることが可能です。SH7731 は、 高性能、低電力を同時に要求される電子機器に最適な LSI です。

### 1.1 特長

SH7731 の特長を表 1.1 に示します。

表 1.1 本 LSI の特長

| 項目  | 特 長                                              |

|-----|--------------------------------------------------|

| CPU | • ルネサス テクノロジオリジナルアーキテクチャ                         |

|     | • SH-1、SH-2、SH-3、SH3-DSP と命令セットレベルで上位互換          |

|     | • 32 ビット内部データバス                                  |

|     | • 汎用レジスタファイル                                     |

|     | - 16 本の 32 ビット汎用レジスタ(8 本の 32 ビットシャドウレジスタ)        |

|     | - 7 本の 32 ビット制御レジスタ                              |

|     | - 4 本の 32 ビットシステムレジスタ                            |

|     | • RISC タイプ命令セット(SH-1、SH-2、SH-3、SH3-DSP と上位互換性あり) |

|     | - 命令長:コードの効率改善のための 16 ビット固定長                     |

|     | - ロードストアアーキテクチャ                                  |

|     | - 遅延分岐命令                                         |

|     | - 条件付き実行                                         |

|     | - C 言語に基づく命令セット                                  |

|     | • 2 命令同時実行型スーパスカラ                                |

|     | • 命令実行時間: 最大 2 命令 / サイクル                         |

|     | • 仮想アドレス空間: 4G バイト                               |

|     | ● 空間識別子 ASID:8 ビット、256 仮想アドレス空間                  |

|     | ● 乗算器内蔵                                          |

|     | •8段パイプライン                                        |

| 項目        | 特 長                                                                                                                |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DSP ユニット  | ● 16 ビット命令、32 ビット命令の混在可能                                                                                           |  |  |  |  |

|           | • 32 または 40 ビットの内部データバスを内蔵                                                                                         |  |  |  |  |

|           | • 乗算器、ALU、バレルシフタに対応                                                                                                |  |  |  |  |

|           | <ul> <li>16 ビット×16 ビットに対応する 32 ビット乗算器を内蔵</li> <li>大容量の DSP データレジスタファイルをサポート</li> <li>6 本の 32 ビットデータレジスタ</li> </ul> |  |  |  |  |

|           |                                                                                                                    |  |  |  |  |

|           |                                                                                                                    |  |  |  |  |

|           | - 2 本の 40 ビットデータレジスタ                                                                                               |  |  |  |  |

|           | • DSP データバス用の拡張ハーバードアーキテクチャをサポート                                                                                   |  |  |  |  |

|           | - 2 本のデータバス                                                                                                        |  |  |  |  |

|           | - 1 本の命令バス                                                                                                         |  |  |  |  |

|           | ● 最大 4 つの並列演算を実行可能                                                                                                 |  |  |  |  |

|           | - ALU、乗算、2つのロード/ストア                                                                                                |  |  |  |  |

|           | ● 2 つのメモリアクセス用のアドレスを生成するための 2 本のアドレスユニットを装備                                                                        |  |  |  |  |

|           | • DSP データアドレッシングモードをサポート                                                                                           |  |  |  |  |

|           | - インクリメント、およびインデクシング(モジュロアドレッシングあり/なし)                                                                             |  |  |  |  |

|           | • ゼロオーバヘッドリピートループ制御に対応                                                                                             |  |  |  |  |

|           | • 条件付き実行命令に対応                                                                                                      |  |  |  |  |

|           | • ユーザ DSP モードおよび特権 DSP モードをサポート                                                                                    |  |  |  |  |

| メモリ       | ● 4G バイトのアドレス空間、256 のアドレス空間(ASID8 ビット)                                                                             |  |  |  |  |

| マネジメント    | • 単一仮想記憶モードと多重仮想記憶モード                                                                                              |  |  |  |  |

| ユニット(MMU) | ● 複数のページサイズをサポート:1K、4K、8K、64K、256K、1M、4M、64M バイト                                                                   |  |  |  |  |

|           | • 命令に対する 4 エントリのフルアソシアティブ TLB                                                                                      |  |  |  |  |

|           | • 命令およびオペランドに対する 64 エントリのフルアソシアティブ TLB                                                                             |  |  |  |  |

|           | • ソフトウェアによる入換方法およびランダムカウンタ方式入換アルゴリズムをサポート                                                                          |  |  |  |  |

|           | • TLB の内容はアドレスマッピングにより直接アクセス可能                                                                                     |  |  |  |  |

|           | 【注】 本 LSI では、32 ビットアドレス拡張モードおよび 32 ビットブート機能はサポートしておりません。                                                           |  |  |  |  |

| キャッシュ     | • 命令キャッシュ (IC)                                                                                                     |  |  |  |  |

| メモリ       | - 32K バイト、4 ウェイセットアソシアティブ                                                                                          |  |  |  |  |

|           | - 32 バイトブロック長                                                                                                      |  |  |  |  |

|           | • オペランドキャッシュ ( OC )                                                                                                |  |  |  |  |

|           | - 32K バイト、4 ウェイセットアソシアティブ                                                                                          |  |  |  |  |

|           | - 32 バイトブロック長                                                                                                      |  |  |  |  |

|           | - 選択可能な書き込み方式(コピーバック/ライトスルー)                                                                                       |  |  |  |  |

| 項目               | 特 長                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| X/Y メモリ          | ● 4 本の独立した読み出し / 書き込みポート                                                                      |

|                  | - CPU から仮想アドレスによる 8/16/32 ビットオペランドアクセス                                                        |

|                  | - DSP からの最大 2 個の 16 ビットアクセス                                                                   |

|                  | - CPU から物理アドレスによる 8/16/32 ビットオペランドアクセスおよび CPU からの命令フェッチア<br>クセス                               |

|                  | - SuperHyway バスマスタからの 8 / 16 / 32 / 64 ビットおよび 16 / 32 バイトアクセス                                 |

|                  | <ul><li>◆ 容量 16K バイト</li></ul>                                                                |

|                  | • CPU アクセスでの記憶保護機構に加え、DSP アクセス専用の記憶保護機構をサポート                                                  |

| <b>リメモリ</b>      | ● 2 本の独立した読み出し / 書き込みポート                                                                      |

|                  | - CPU からの 8 / 16 / 32 ビットアクセス                                                                 |

|                  | - SuperHyway バスマスタからの 8 / 16 / 32 / 64 ビットおよび 16 / 32 バイトアクセス                                 |

|                  | • 128K バイトの大容量メモリを内蔵                                                                          |

| L メモリ            | ● 3 本の独立した読み出し / 書き込みポート                                                                      |

| (ILRAM)          | - CPU から仮想アドレスによる命令フェッチアクセス                                                                   |

|                  | - CPU から物理アドレスによる命令フェッチアクセスおよび 8/16/32 ビットオペランドアクセス                                           |

|                  | - SuperHyway バスマスタからの 8/16/32/64 ビットおよび 16/32 バイトアクセス                                         |

|                  | <ul><li>◆容量 4K バイト</li></ul>                                                                  |

| 割り込み             | ● 9 本の外部割り込み端子(NMI、IRQ7~IRQ0)                                                                 |

| コントローラ           | - NMI:立ち下がり/立ち上がり選択可能                                                                         |

| (INTC)           | - IRQ:立ち下がり / 立ち上がり / ハイレベル / ローレベル選択可能                                                       |

|                  | • 内蔵周辺割り込み:モジュールごとに優先順位を設定                                                                    |

| バスステート           | • SRAM、バースト ROM、PCMCIA インタフェース機能をサポート                                                         |

| コントローラ<br>(BSC)  | ● 物理アドレス空間:最大 64M バイトの 2 つの領域 (エリア 0、4)、および最大 32M バイトの 4 つの領域 (エリア 5A、5B、6A、6B)の合計 6 エリアをサポート |

|                  | • 各エリアには独立に以下の設定が可能                                                                           |

|                  | - メモリ種類:SRAM、NOR-Flash、パースト ROM、PCMCIA                                                        |

|                  | - データバス幅:16 ビット / 32 ビット切り替え可能(SBSC 用データバス幅 64 ビット選択時は 16 ビ                                   |

|                  | ット)                                                                                           |

|                  | - ウェイトサイクル数                                                                                   |

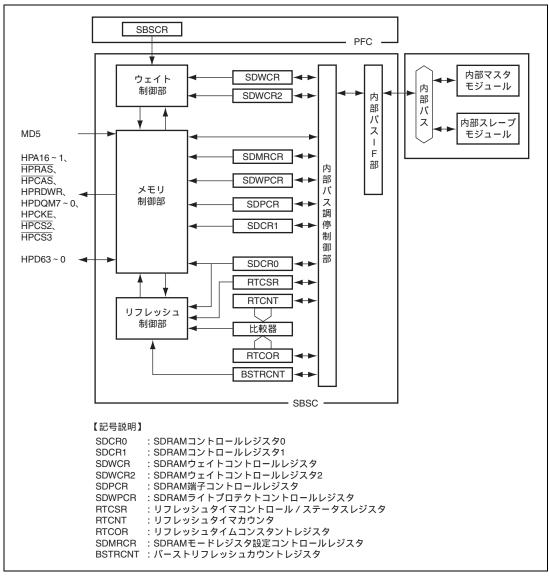

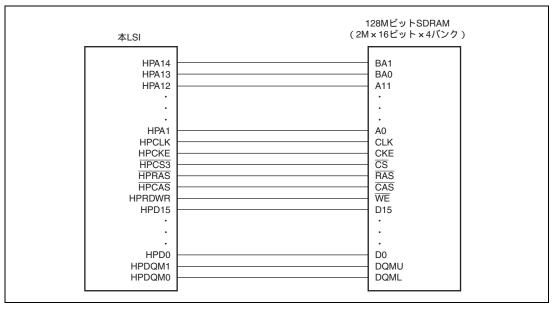

| SDRAM 用          | • 3.3V SDR-SDRAM を直結可能                                                                        |

| バスステート           | ● 物理アドレス空間:最大 64M バイトの 2 つの領域(エリア 2、3)をサポート                                                   |

| コントローラ<br>(SBSC) | 合計最大 128M バイトの SDRAM を接続可能                                                                    |

| (3630)           | ● データバス幅: 16 ビット / 32 ビット / 64 ビット切り替え可能                                                      |

|                  | ただし、BSC 用データバス幅 32 ビット選択時は 16 ビット / 32 ビットのみ                                                  |

|                  | • オートリフレッシュ / セルフリフレッシュをサポート                                                                  |

|                  | • オートプリチャージモード / バンクアクティブモード選択可能                                                              |

| 項目          | 特 長                                                    |  |  |

|-------------|--------------------------------------------------------|--|--|

| ダイレクト       | ● 6 チャネル内蔵、内 1 チャネルは外部リクエスト受け付け可能 (チャネル 0)             |  |  |

| メモリアクセス     | ● アドレス空間: アーキテクチャ上は 4G バイト                             |  |  |

| コントローラ      | ● データ転送長:バイト、ワード(2 バイト)、ロングワード(4 バイト)、16 バイト、32 バイト    |  |  |

| (DMAC)      | ● 最大転送回数:16,777,216 回                                  |  |  |

|             | • アドレスモード: デュアルアドレスモード                                 |  |  |

|             | <br>  転送要求:外部リクエスト、内蔵周辺モジュールリクエスト、オートリクエストの3種類から選択可能。  |  |  |

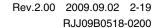

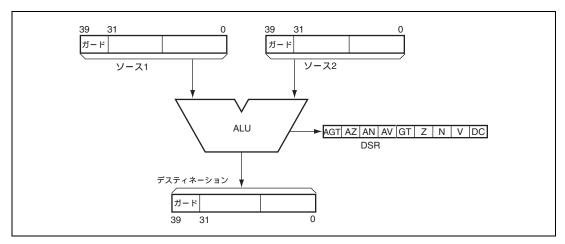

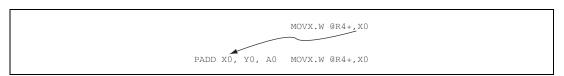

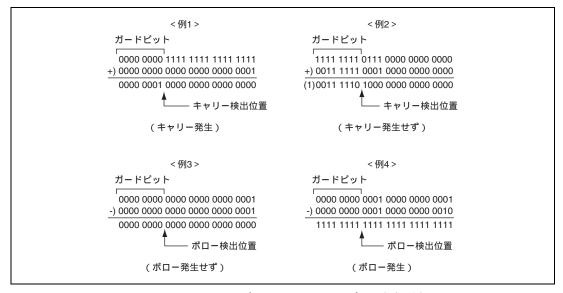

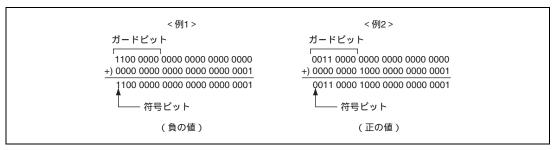

|             | <br>  ● バスモード:サイクルスチールモード(通常モードとインターミッテントモード)とバーストモードか |  |  |