# 32

# RH850G4MH

Virtualization

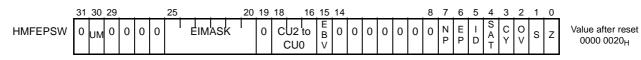

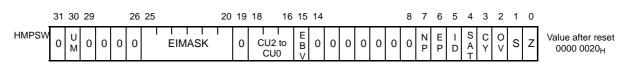

User's Manual: Hardware

Renesas microcontroller

RH850 Family

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Rev.1.40 Aug. 2023

## Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

# Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

# **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="http://www.renesas.com/contact/">www.renesas.com/contact/</a>

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

#### 1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

#### 2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power is supplied until the power reaches the level at which resetting is specified.

#### 3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

#### 4. Handling of unused pins

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to power supply or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### 5. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

#### 6. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

#### 7. Power ON/OFF sequence

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

# **Table of Contents**

| Sectio | n 1   | Virtualization support function                                            |    |

|--------|-------|----------------------------------------------------------------------------|----|

| 1.1    | Ou    | tline of virtualization support function                                   |    |

|        | 1.1.1 | Virtualization system                                                      | 9  |

|        | 1.1.2 | Paravirtualization and Partition Function                                  | 10 |

|        | 1.1.3 | Enabling virtualization support function                                   | 11 |

|        | 1.1.4 | Host mode and Guest mode                                                   | 11 |

| 1.2    | Oc    | cupied and Shared resources                                                | 12 |

| 1.3    | Fur   | nctional difference based on activation of Virtualization Support Function | 13 |

| Sectio | n 2   | Processor Model                                                            | 14 |

| 2.1    | CP    | U Operating Modes                                                          | 14 |

|        | 2.1.1 | Definition of CPU Operating Modes                                          | 15 |

|        | 2.1.2 | CPU Operating Mode Transition                                              | 16 |

|        | 2.1.3 | CPU Operating Mode and Privileges                                          |    |

|        | 2.1.4 | Halt State by a HALT Instruction                                           |    |

|        | 2.1.5 | Temporary Halt State by a SNOOZE instruction                               |    |

| 2.2    | Ins   | truction Execution                                                         |    |

| 2.3    | Exc   | ceptions and Interrupts                                                    |    |

|        | 2.3.1 | Types of Exceptions                                                        |    |

|        | 2.3.2 | Exception Level                                                            |    |

| 2.4    | Co    | processors                                                                 |    |

|        | 2.4.1 | Coprocessor Use Permissions                                                |    |

|        | 2.4.2 | Correspondences between Coprocessor Use Permissions and Coprocessors       |    |

|        | 2.4.3 | Coprocessor Unusable Exceptions                                            |    |

|        | 2.4.4 | System Registers                                                           | 27 |

| 2.5    | Re    | gisters                                                                    |    |

|        | 2.5.1 | Program Registers                                                          |    |

|        | 2.5.2 | System Registers                                                           |    |

|        | 2.5.3 | Register Updating                                                          |    |

|        | 2.5.4 | Accessing Undefined Registers                                              | 32 |

|        | 2.5.5 | Supervisor Lock Setting                                                    | 32 |

|        | 2.5.6 | Change in Register Model                                                   | 32 |

|        | 2.5.7 | System Register Multiplexing                                               | 35 |

| 2.6    | Dat   | a Types                                                                    |    |

|        | 2.6.1 | Data Formats                                                               |    |

|        | 2.6.2 | Data Representation                                                        |    |

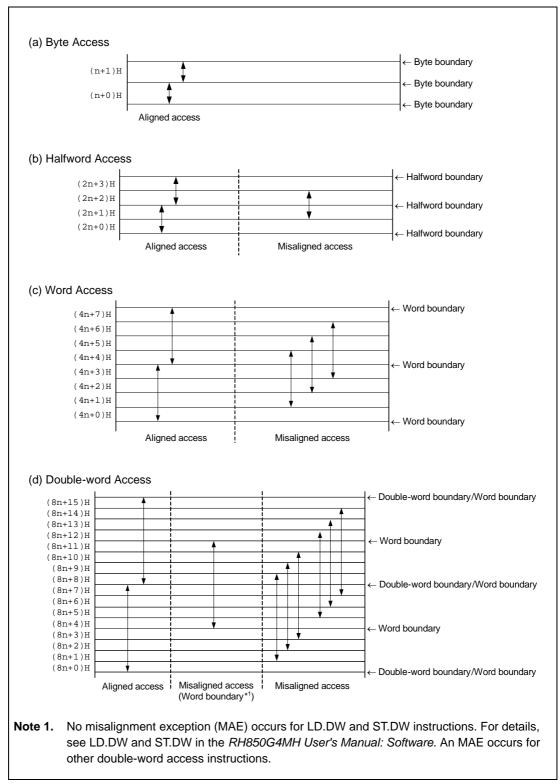

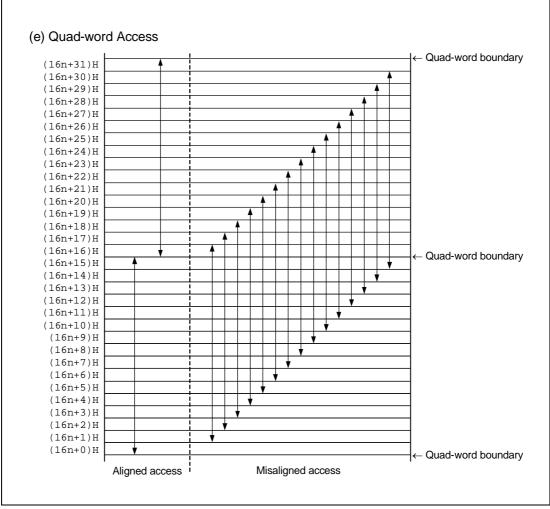

|        | 2.6.3 | Data Alignment                                                             |    |

| 2.7    | Ade   | dress Space                                                                | 40 |

|        | 2.7.1 | Memory Map                                                                 | 40 |

|        | 2.7.2 | Instruction Addressing                                                     |    |

|        | 2.7.3 | Data Addressing                                                            | 40 |

| 2.8    | Exe   | ecution Timing of a Store Instruction                                      | 41 |

| 2.9    |       | mory Ordering                                                              |    |

|    | 2.10       | Acquiring the CPU Numb      | er 4                                  | 11 |

|----|------------|-----------------------------|---------------------------------------|----|

|    | 2.11       | System Protection Identif   | er (SPID)                             | 41 |

|    | 2.12       | Timestamp Counter           |                                       | 12 |

|    | 2.1        | 2.1 How to Operate the      | e Timestamp Counter                   | 42 |

|    | 2.13       | Performance Measureme       | nt Function                           | 43 |

|    | 2.14       | Debug Target Limitation .   |                                       | 43 |

| ~  |            |                             |                                       |    |

| Se | ection 3   | Register Set                |                                       | -4 |

|    | 3.1        |                             |                                       |    |

|    | 3.2        |                             |                                       |    |

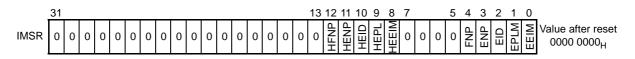

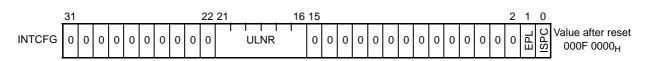

|    | 3.3        | Interrupt Function Registe  | ers                                   | 52 |

|    | 3.3        | 3.1 Interrupt Function      | system Registers                      | 52 |

|    | 3.4        | FPU Function Registers      | 6                                     | 30 |

|    | 3.5        | FXU Function Registers      | 6                                     | 31 |

|    | 3.6        | MPU Function Registers.     | 6                                     | 32 |

|    | 3.6        | 6.1 MPU Function Sys        | em Registers6                         | 32 |

|    | 3.7        | Cache Operation Functio     | n Registers6                          | 38 |

|    | 3.7        | 7.1 Cache Control Fun       | ction System Registers6               | 38 |

|    | 3.8        | Count Function Registers    |                                       | 70 |

|    | 3.8        | 3.1 Count Function Sys      | stem Registers                        | 70 |

|    | 3.9        | Hardware Function Regis     | ters                                  | 75 |

|    | 3.10       | Virtualization support fund | ction system registers                | 76 |

|    | 3.11       | Host Context Register       |                                       | 33 |

|    | 3.12       | Guest Context Register      |                                       | )3 |

| 9  | ection 4   | Excontions and In           | terrupts 11                           | 7  |

| 36 |            |                             | ·                                     |    |

|    | 4.1        | •                           |                                       |    |

|    | 4.1<br>4.1 | I                           | ist                                   |    |

|    | 4.<br>4.1  |                             | tion Causes                           |    |

|    | ۰.<br>4.   | 71 1                        | edgment Conditions and Priority Order |    |

|    | 4.1        | •                           | Priority and Priority Masking         |    |

|    | 4.1        |                             | ation                                 |    |

|    | 4.1        | .7 Context switching .      |                                       | 36 |

|    | 4.1        | .8 Exception to transi      | ion from guest mode to host mode13    | 39 |

|    | 4.1        | .9 Background Interru       | pts 14                                | 11 |

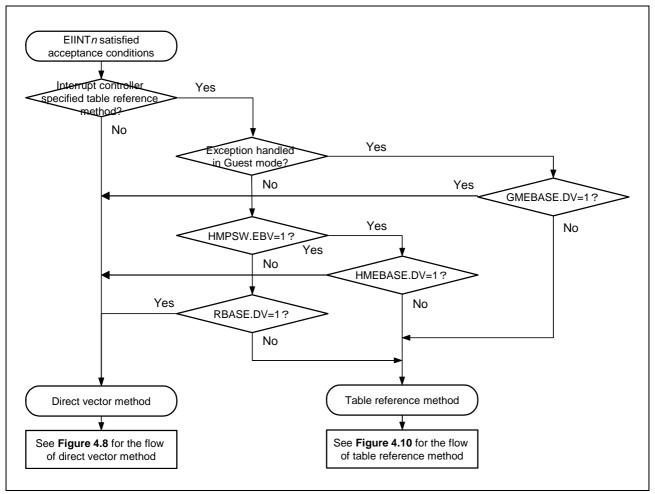

|    | 4.2        | Operation when Acknowl      | edging an Exception14                 | 14 |

|    | 4.2        | 2.1 Special Operations      |                                       | 16 |

|    | 4.3        | Return from Exception Ha    | andling14                             | 18 |

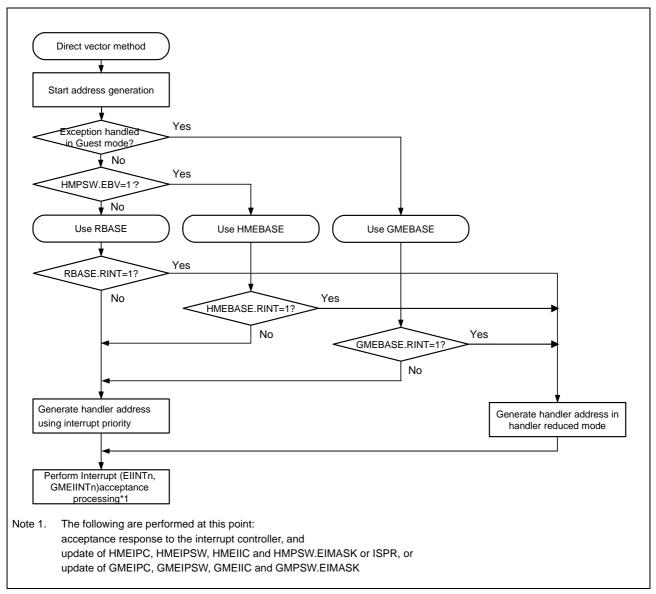

|    | 4.4        | Exception Handler Addre     | ss                                    | 50 |

|    | 4.4        | .1 Resets, Exceptions       | s, and Interrupts                     | 50 |

|    | 4.4        | .2 System Calls             |                                       | 59 |

| 4.5    | Re     | gister Bank Function                                              | 160 |

|--------|--------|-------------------------------------------------------------------|-----|

|        | 4.5.1  | Outline of the Register Bank Function                             | 160 |

|        | 4.5.2  | Automatic Context Saving                                          | 160 |

|        | 4.5.3  | Context Restoration                                               | 165 |

| 4.6    | Lis    | t of Memory Access Exceptions                                     | 168 |

| Sectio | n 5    | Memory Management                                                 | 169 |

| 5.1    | Me     | mory Protection Unit (MPU)                                        | 169 |

|        | 5.1.1  | Features                                                          | 169 |

|        | 5.1.2  | Protection Area Settings                                          | 170 |

|        | 5.1.3  | Precautions for Protection Area Setup                             | 171 |

|        | 5.1.4  | Access Control                                                    | 173 |

|        | 5.1.5  | Violations and Exceptions                                         | 174 |

|        | 5.1.6  | Memory Protection Setting Check Function                          | 177 |

|        | 5.1.7  | Layered Memory Protection Function                                | 180 |

|        | 5.1.8  | Memory Protection Setting Bank Function                           | 184 |

|        | 5.1.9  | Memory protection setting High speed save and restore function    | 185 |

| 5.2    | Ca     | che                                                               | 186 |

|        | 5.2.1  | Features                                                          | 186 |

|        | 5.2.2  | Cache Operation Registers                                         | 186 |

|        | 5.2.3  | Change Cache Use Mode                                             |     |

|        | 5.2.4  | Cache Operations Using CACHE Instruction                          | 186 |

|        | 5.2.5  | Cache Operation by the PREF Instruction                           | 186 |

|        | 5.2.6  | Cache Index Specification Method                                  | 186 |

|        | 5.2.7  | Execution Privilege of the CACHE/PREF Instruction                 | 187 |

|        | 5.2.8  | Memory Protection for the CACHE and PREF Instructions             | 188 |

|        | 5.2.9  | Example of Using the CACHE Instruction to Manipulate Cache Memory | 188 |

|        | 5.2.10 | Configuration of Instruction Cache                                | 188 |

|        | 5.2.11 | Data Buffer Function                                              | 188 |

| Sectio | n 6    | Coprocessor                                                       | 189 |

| 6.1    | Flo    | ating-Point Operation                                             | 189 |

| 6.2    | Ex     | ended Floating-Point Operation                                    | 189 |

| Sectio | n 7    | Hazard Control                                                    | 190 |

| 7.1    |        | nchronization Processing                                          |     |

| 7.2    | •      | aranteeing the Completion of Store Instruction                    |     |

|        |        |                                                                   |     |

| 7.3    |        | zard Management after System Register Update                      |     |

|        | 7.3.1  | Updating the Settings Related to Instruction Fetching             |     |

|        | 7.3.2  | Updating the Memory Protection Settings of MPU                    |     |

|        | 7.3.3  | Updating Interrupt-Related System Registers                       |     |

|        | 7.3.4  | Updating Register Bank Function-Related System Registers          |     |

|        | 7.3.5  | Reading a System Register by Using an STSR Instruction            |     |

|        | 7.3.6  | Referencing a System Register by the Subsequent Instruction       |     |

|        | 7.3.7  | Use of EIRET and FERET Instructions in Synchronization Process    |     |

| 7.3       | 3.8 Updating PSW.EBV and EBASE                                                   |       |

|-----------|----------------------------------------------------------------------------------|-------|

| 7.3       | 3.9 Synchronization processing of STM.MP, LDM.MP, STM.GSR, LDM.GSR instructions. | 193   |

| 7.4       | Synchronizing for restricted operating mode transition                           | 194   |

| Section 8 | 8 Reset                                                                          | . 195 |

| 8.1       | Status of Registers After Reset                                                  | 195   |

| Section 9 | 9 Virtualization of Interrupt                                                    | . 196 |

| 9.1       | Interrupt Binding                                                                | 196   |

| 9.2       | Notification of an Interrupt Request                                             | 196   |

| 9.3       | Restriction on IHVCFG.IHVE Operation                                             | 197   |

| 9.4       | Restriction on Operation in Guest Mode with Interrupt Controller INTC1           | 198   |

| 9.5       | Restriction on Operating EICn and EEICN Registers                                | 198   |

# Section 1 Virtualization support function

This CPU supports the Virtualization support function.

This section describes the characteristics of virtualization support function usable in this CPU.

# **1.1** Outline of virtualization support function

By using the virtualization support function of this CPU, it is easy to build a virtual machine with virtualization software.

#### CAUTIONS

- 1. In this document, the software that manages virtual machines is called virtualization software. It is also referred to as a hypervisor or a virtual machine monitor (VMM: Virtual Machine Monitor).

- 2. This document describes the operations in the Virtualization Support Function enabled state, unless it is explicitly noted as disabled.

# 1.1.1 Virtualization system

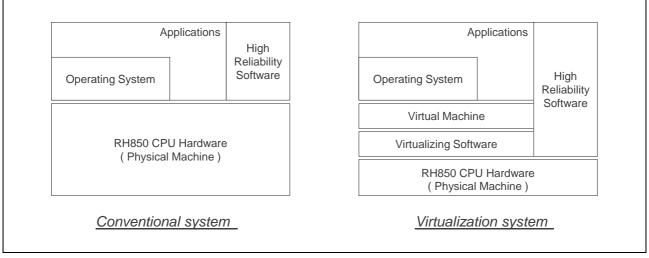

**Figure 1.1** shows an example of the software operation on this CPU when virtualization support function is not used (Conventional system) and an example of the software operation on this CPU when virtual machine is built using this CPU's virtualization support function (Virtualization system).

Figure 1.1 Comparison of Conventional system and Virtualization system

In a conventional system, management software such as operating system can operate all functions of CPU. Therefore, when the reliability of the management software is low (incomplete software, low level of security concerning external purchases, etc.), if the management software performs an illegal operation, not only the inside of the CPU becomes illegal, an illegal operation also spreads outside the CPU. As a result, it may be necessary to reset the control system that incorporates the CPU on which the management software is installed. This will adversely affect the stable operation of the system. As a result, a low reliability of the management software running on one of the CPUs constituting the control system reduces the reliability of the entire control system.

In one virtualization system, management software and application software that operates under its control operate on a virtual machine managed by virtualization software. From the management software running on the virtual machine, it looks like all the functions of the CPU can be operated like the conventional system. However, the virtualization software can use the virtualization support function to impose motion constraints on software running on the virtual machine. If the management software with low reliability does some illegal operations, the inside of the virtual machine is still in an incorrect state, but the influence of illegal operation to the outside of the CPU is suppressed by various constraints given by this virtualization software. Also, because the detected illegal operation is notified to the virtualization software, the virtualization software can take some actions such as stopping the management software that performed the illegal operation or restarting it. Resetting the system is unnecessary even if illegal operation is performed, leading to stable operation of the system. As a result, the unreliability of the management software running on the virtual machine of one of the CPUs constituting the control system does not affect the reliability of the entire control system.

In either system, software with high reliability that does not require operation constraints may be operating independently of management software and virtualization software.

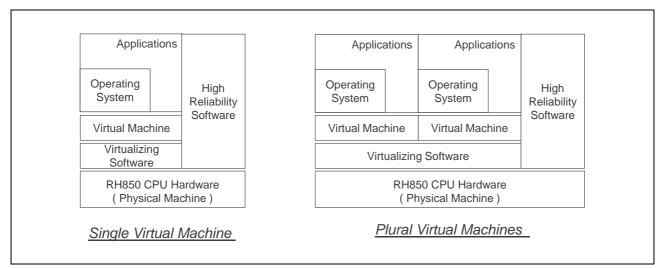

In addition, in this CPU, it is also possible to build multiple virtual machines on one CPU. **Figure 1.2** shows a case where one virtual machine is built on this CPU and another case where two virtual machines are built on this CPU.

Figure 1.2 Construction of multiple virtual machines

Multiple virtual machines can be executed in parallel by the virtualization software switching the context of the virtual machine. In order to easily realize this, the virtualization support function of this CPU consists of a hardware identifier that can identify up to eight virtual machines, a memory management function for sharing an address space among multiple virtual machines or for exclusive use, and a context switching support function.

# 1.1.2 Paravirtualization and Partition Function

The virtualization system realized using the virtualization support function of this CPU is paravirtualization. Therefore, in order for the management software running on the conventional system compatible with this CPU to operate on the virtualization system of this CPU, it may be necessary to change the software. The necessary changes are out of the scope of this document since they depend on the CPU function used by the software to be changed and the function of the virtual machine built by the virtualization software.

To realize paravirtualization (resource separation and sharing), this CPU provides a partition function as a virtualization support function. The partition function enables a virtualization software environment without interference between virtual machines to be realized.

The partition function of this CPU imposes hardware-based restrictions on software operating on this CPU for the use of CPU resources. Virtualization software can use this partition function to realize the virtual machine as the operating environment of the software under this constraint.

# 1.1.3 Enabling virtualization support function

The virtualization support function of this CPU can be enabled or disabled by system register setting.

When the virtualization support function is disabled, this CPU can be used as a conventional system. When the virtualization support function is enabled, this CPU can be used as a virtualization system. For details on enabling and disabling virtualization support function, see **Section 2.1, CPU Operating Modes**.

### 1.1.4 Host mode and Guest mode

When virtualization support function of this CPU is enabled, Host mode and Guest mode can be used as new CPU operation modes. When virtualization support function is enabled, the CPU is in either Host mode or Guest mode.

Host mode and Guest mode are defined independently of the supervisor mode and user mode available in the conventional system. Therefore, there are four combinations of operation modes.

In Host mode, it is possible to operate all CPUs resources including virtualization support function. In Guest mode, most of the CPUs resources equivalent to the conventional system can be operated, but the virtualization support function or resources not related to the virtual machine can not be operated. Also, Host mode can restrict some operations of Guest mode, with the partition function provided by the virtualization support function. A guest partition is defined as the operating environment of the software at the Guest mode, constrained by the partition function.

For details of operation modes including Host mode and Guest mode, see **Section 2.1, CPU Operating Modes**.

# **1.2** Occupied and Shared resources

The allocation method of each resources is determined by the specification of virtualization software. This CPU provides separation means to allocate each resource to virtual machines. For general-purpose registers and other resources for which the CPU has no separation means, it may be necessary to replace the context at virtual machine switching.

Table 1.1 shows a list of resources of this CPU.

| Table | 1.1 | Resource list  |

|-------|-----|----------------|

| IGNIC |     | 11000011001101 |

| Resources                 | Location <sup>*1</sup> | Separation means                                  |

|---------------------------|------------------------|---------------------------------------------------|

| Flash memory              | Outside CPU            | MPU* <sup>2</sup> , Guard mechanism* <sup>3</sup> |

| Local memory              | Inside CPU             | MPU* <sup>2</sup> , Guard mechanism* <sup>3</sup> |

| Cluster memory            | Outside CPU            | MPU* <sup>2</sup> , Guard mechanism* <sup>3</sup> |

| Peripheral IO             | Outside CPU            | MPU* <sup>2</sup> , Guard mechanism* <sup>3</sup> |

| Interrupt channels        | Outside CPU            | MPU*2, Guard mechanism*3, INTC1 function*4        |

| General purpose registers | Inside CPU             | None                                              |

| Vector registers          | Inside CPU             | Whether available or not can be specified*5       |

| System registers          | Inside CPU             | Partial multiplexing* <sup>6</sup>                |

Note 1. For resources inside of CPU, specifications are defined in this document. Resources outside of CPU are basic resources enumerated as RH850 products, and specifications including mounting feasibility are not defined in this document. For details, see the hardware manual of the product used.

Note 2. The MPU (memory protection function) can restrict the address space that can be accessed. For details, see Section 5, Memory Management.

Note 3. Guard mechanism for access restriction may be implemented as specification of product. For details, including occupied and shared methods, see the hardware manual of the product used.

Note 4. Interrupt channel separation method is implemented as INTC (interrupt controller) specifications. For details, see the "Interrupts" section in the hardware manual of the product used.

Note 5. Host mode can specify whether to use in Guest mode. For details, see Section 2.4.1, Coprocessor Use Permissions.

Note 6. Some system registers are multiplexed in Host mode only or in Guest mode only. For details, see **Section 2.5.7, System Register Multiplexing**.

# 1.3 Functional difference based on activation of Virtualization Support Function

When the virtualization support function is enabled, there will be some functional differences compared to the case in which the function is disabled. **Table 1.2** shows the details of these differences.

| Function                                        | Overview                                                                                                                                                  | Reference      |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CPU function mode                               | Host mode and Guest mode are available.                                                                                                                   | 2.1            |

| Access authority                                | HV privilege to operate virtualization support function are available.                                                                                    | 2.1.3          |

| Access authority of system registers            | There are the registers which access authority is changed.                                                                                                | 2.5.3          |

| Instruction execution authority                 | There are the instructions which execution authority is changed.                                                                                          | 5.2.6          |

| How to specify an exception handler address     | There are restrictions on how to use table reference method interrupts in Host mode. There is a restriction on how to set the base address in Guest mode. | 4.2.1<br>4.4.1 |

| Exception cause                                 | Exceptions for effectively using the partition function can be used.                                                                                      | 4.1.2          |

| Exception acceptance condition                  | Conditions for accepting the above exception causes                                                                                                       | 4.1.1          |

| Nesting memory protection function              | Memory protection function dedicated to Guest mode that can be changed<br>only in Host mode can be used.                                                  | 5.1.7          |

| Virtualization support function system register | System registers to control virtualization support functions can be used.                                                                                 | 3.10           |

| Host Context Register                           | Multiplexed system registers to improve efficiency of the context register                                                                                | 3.11           |

| Guest Context Register                          | switching when switching between Host mode and Guest mode can be used.                                                                                    | 3.12           |

| Memory protection function System register      | Memory protection function for realizing partition function can be used.                                                                                  | 3.6            |

| Virtualization support function instruction     | Instructions for efficiently realizing virtualization system can be used.                                                                                 | *1             |

Table 1.2

Functional difference based on activation of virtualization support function

Note 1. See the RH850G4MH Virtualization User's Manual: Software.

# Section 2 Processor Model

This CPU adopts a processor model that has basic operation functions, registers, and an exception management function.

This section describes the unique features of the processor model of this CPU.

# 2.1 CPU Operating Modes

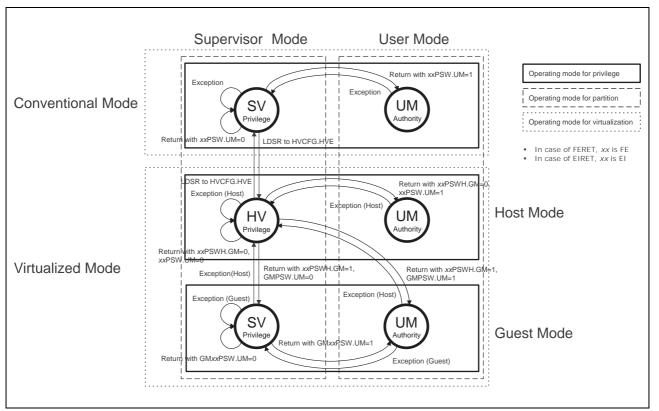

There are three independent operating modes in this CPU.

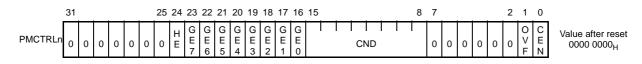

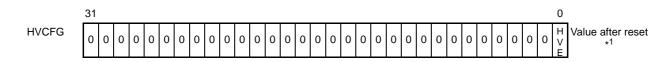

The first mode is the virtualization operating mode indicating the use state of the virtualization support function. The virtualization operating mode has two states: the conventional mode in which the virtualization support function is disabled and the virtualization mode in which the virtualization support function is enabled. The virtualization operating mode is indicated by the value of HVCFG.HVE.

- Conventional mode (HVCFG.HVE = 0): The virtualization support function is disabled.

- Virtualization mode (HVCFG.HVE = 1): The virtualization support function is enabled.

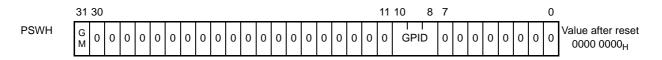

The second mode is the restricted operating mode indicating the operating state of the partition function. Restricted operating mode has two states: Host mode (HM) and Guest mode (GM). The restricted operating mode is indicated by the value of PSWH.GM.

| • | Host mode (PSWH.GM = 0): | Partition function is disabled. |

|---|--------------------------|---------------------------------|

|---|--------------------------|---------------------------------|

• Guest mode (PSWH.GM = 1): Partition function is enabled.

The third mode is the authority operating mode indicating the software operating authority. The authority operating mode has two states: Supervisor mode (SV) and User mode (UM). The authority operating mode is indicated by the value of PSW.UM.

- Supervisor mode (PSW.UM = 0): Access authority is high; CPU resources can be managed and operated.

- User mode (PSW.UM = 1): Access authority is low, and the use of CPU resources is restricted.

The restricted operating mode can be enabled only when the virtualization operating mode is virtualization mode. When the virtualization operating mode is the conventional mode, the function related to the state of the restricted operating mode can not be used. The authority operating mode can be enabled regardless of the state of other operating modes. However, detailed software operating authority is defined by combination with other operating modes. For details, see **Section 2.1.3, CPU Operating Mode and Privileges**.

# 2.1.1 Definition of CPU Operating Modes

#### 2.1.1.1 Virtualization operating mode

See the hardware manual of the product used for the virtualization operating mode after reset release.

#### (1) Conventional mode

In the conventional mode, the virtualization support function can not be used. The RIE exception occurs when an instruction of the virtualization support function is about to be executed. The system registers of the virtualization support function are handled as undefined registers and operations are impossible. However, the HVCFG register indicating the state of the virtualization operating mode can be operated.

#### (2) Virtualization mode

The virtualization mode is a state in which virtualization support function can be used. The function related to the restricted operating mode is enabled only when the virtualization operating mode is virtualization mode. The operating restrictions applied to the software operating in virtualization mode depends on the state of the restricted operating mode and the authority operating mode.

#### 2.1.1.2 Restricted operating mode

The initial mode of restricted operating mode is always Host mode.

#### (1) Host mode (HM)

In Host mode, the partition function is disabled. At this time, if the authority operating mode is supervisor mode, the software can operate all CPU resources including virtualization support function. In addition, it is possible to set an operating restriction that is enabled when changing to Guest mode.

#### (2) Guest mode (GM)

In Guest mode, the partition function is enabled. Operating restrictions which can not be changed from software running in Guest mode may be set.

#### 2.1.1.3 Authority operating mode

The authority operating mode after reset release is always Supervisor mode.

#### (1) Supervisor mode (SV)

In Supervisor mode, the access authority is high and CPU resource can be managed and operated. Operable CPU resources depend on the state of the virtualization operating mode and restricted operating mode. For details, see **Section 2.1.3, CPU Operating Mode and Privileges**. In addition, it is possible to set an operating restriction that is enabled when changing to user mode.

#### (2) User mode (UM)

In User mode, the access authority is low and operation of CPU resources is restricted. Operating restrictions which can not be changed from software operating in User mode may be set. Software running in User mode can use the instructions and system registers defined as user resources.

# 2.1.2 CPU Operating Mode Transition

The CPU operating mode changes due to three events.

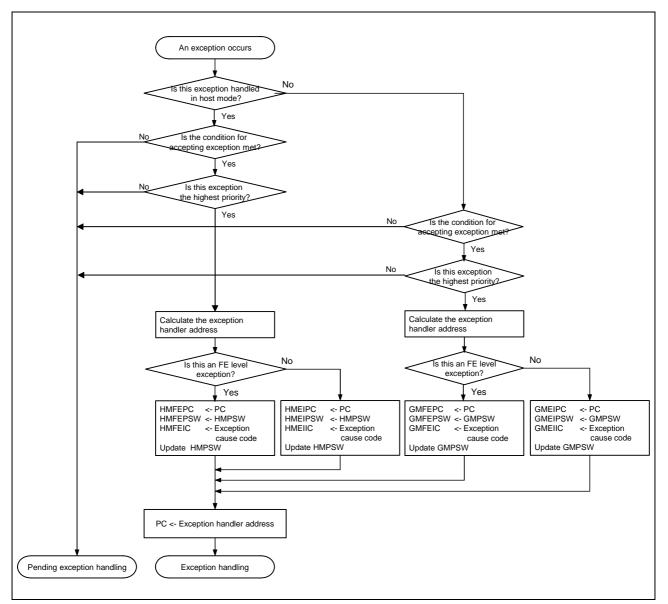

#### (1) Change due to Acknowledging an Exception

When an exception to change to Host mode is accepted in Guest mode, restricted operating mode transits to Host mode. In Guest mode, if an exception which does not change to the Host mode is accepted, the restricted operating mode will remain in Guest mode. In Host mode, if an exception is accepted, the restricted operating mode will remain in the Host mode. There is no exception to change from Host mode to Guest mode. See **Section 4.1.1, Exception Cause List** for details of exception to enter Host mode.

When an exception is acknowledged in User mode, the authority operating mode changes to Supervisor mode. When an exception is acknowledged in Supervisor mode, the authority operating mode remains in Supervisor mode. When accepting exceptions, the virtualization operating mode does not change.

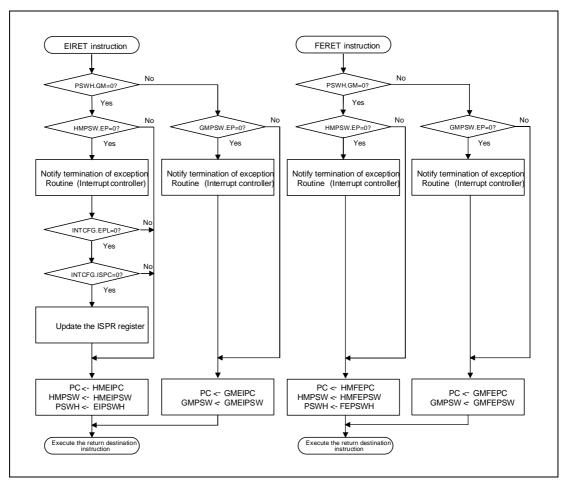

#### (2) Change due to a Return Instruction

By executing a return instruction, the value of PSWH is restored according to the value of the corresponding bit saved in EIPSWH, FEPSWH. Restoring PSWH by a return instruction is only possible when the restricted operating mode is Host mode. Therefore, only the change from Host mode to Guest mode is possible for the change of the restricted operating mode by a return instruction.

Also, by executing a return instruction, the value of PSW is restored according to the value of the corresponding bit saved in EIPSW, FEPSW. Execution of a return instruction is possible when the software operating authority is HV privilege or SV privilege. This means the authority operating mode is Supervisor mode. Therefore, it is only possible to change from Supervisor mode to User mode for the change of authority operating mode by a return instruction.

For details of operating authority, see **Section 2.1.3, CPU Operating Mode and Privileges**. Note that the virtualization operating mode does not change by execution of a return instruction.

#### (3) Change due to a System Register Instruction

The virtualization operating mode changes by directly rewriting HVCFG.HVE by the LDSR instruction. In the conventional mode, the virtualization operating mode can be changed when the operating privilege is SV privilege and in the virtualization mode, it can be changed when the operating privilege is HV privilege. The authority operating mode is changed by directly writing PSW.UM by the LDSR instruction. On the other hand, the restricted operating mode can not be changed by directly writing PSWH.GM by the LDSR instruction.

#### CAUTIONS

- 1. The state change in the virtualization operating mode has a big influence on the operation of software. Therefore, although HVCFG.HVE can be changed by the LDSR instruction, make the change immediately after reset release. Immediately after reset release is the first process in the reset handler, it indicates the timing before changing the setting of other system registers and memory access as an operand. The following operation is not supported: Dynamically changing HVCFG.HVE after this CPU completes the initialization process in the reset handler and the virtualization software or application software has started operating. Note that to change HVCFG.HVE by LDSR instruction, synchronization processing by SYNCI instruction is necessary. For details, see Section 7.3, Hazard Management after System Register Update.

- 2. In the state change of the restricted operating mode, synchronization processing similar to that of the SYNCM instruction is performed when accepting a cause exception and when executing a return instruction. As a result, state change is performed after all load and store operations which were executed before the state change are completed. For details of synchronization operation, see Section 7.3, Hazard Management after System Register Update.

- 3. The CPU operating mode cannot be changed in user mode because the higherorder 31 to 5 bits of the PSW register cannot be overwritten; it can be changed in supervisor mode. This CPU guarantees that if an LDSR instruction is used to update the PSW register, the new setting will be reflected when the subsequent instruction is executed. However, this CPU does not guarantee that the new setting will be reflected in the memory protection by the MPU for instruction fetch of the subsequent instruction. Therefore, for changing the higher-order 31 to 5 bits of the PSW register, it is recommended to use a return instruction. For details, see Section 7.3, Hazard Management after System Register Update.

# 2.1.3 CPU Operating Mode and Privileges

In this CPU, the usable functions can be restricted according to usage permission settings for specific resources and the CPU operating mode. The execution of certain instructions and the operation of certain system registers can only be performed when there is the permission required for it. The permissions necessary to execute these specific instructions are called "privileges". If the privilege for executing instructions or operating system registers is not given, these operations cannot be performed but an exception occurs.

The four types of authority defined by this CPU are as follows.

| Hypervisor (HV) privilege:   | HV privilege is the privilege required for execution of an instruction whose execution authority is HV privilege (HV privileged instruction) and operation of system registers whose access authority is HV privilege                                                                                                                                                                                                                       |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supervisor (SV) privilege:   | SV privilege is the privilege required for execution of an instruction whose execution authority is SV privilege (SV privileged instruction) and operation of system registers whose access authority is SV privilege. Execution of HV privileged instruction and operation of system registers whose access authority is HV privilege can not be performed when CPU authority is SV privilege.                                             |

| User (UM) authority:         | UM authority is an authority that enables execution of instructions (user instructions) whose execution authority is not specially specified, and operation of system registers whose access authority is UM authority. Execution of HV privileged instruction or SV privileged instruction or operation of system registers whose access authority is HV privilege or SV privilege can not be executed when CPU authority is UM authority. |

| Coprocessor use permissions: | Permissions necessary to use a coprocessor                                                                                                                                                                                                                                                                                                                                                                                                  |

#### CAUTION

HV privilege also includes authority of SV privilege. Therefore, when CPU authority is HV privilege, software can execute SV privileged instructions and operate system registers whose access authority is SV privilege. On the other hand, coprocessor use permissions are independent of HV privilege and SV privilege. Therefore, even if the CPU authority is HV privilege or SV privilege, you can not use the coprocessor unless you have coprocessor use permissions.

Figure 2.1 shows the CPU operating mode transition and CPU authority transition.

Figure 2.1 Relationship between CPU operating mode and privilege

**Table 2.1** shows the relationship between the CPU operating modes and the authorities of the CPU defined accordingly.

| CPU operating mode |         |        |                |

|--------------------|---------|--------|----------------|

| HVCFG.HVE          | PSWH.GM | PSW.UM | CPU authority  |

| 0                  | —       | 0      | SV privilege   |

| 0                  | —       | 1      | UM authority   |

| 1                  | 0       | 0      | HV privilege   |

| 1                  | 0       | 1      | UM authority*1 |

| 1                  | 1       | 0      | SV privilege   |

| 1                  | 1       | 1      | UM authority   |

Table 2.1 Definition of CPU operating mode and CPU authority

Note 1. It operates as host mode for the function to be applied according to the state of the restricted operating mode. It operates as UM authority for functions applied according to CPU authority.

#### CAUTION

HV privilege is enabled only when the virtualization operating mode is virtualization mode. When the virtualization operating mode is the conventional mode, if an HV privilege instruction is executed, there are cases where RIE exceptions occur and cases where the instruction can be executed if the SV privilege is enabled. And when the virtualization operating mode is the conventional mode, if a system register that requires HV privilege as the access authority is operated, it may be handled as an undefined register, or it may be operable if there is SV privilege. For details, see each instructions and system register specifications.

#### (1) Hypervisor privilege (HV privilege)

The privilege necessary for operation of the virtualization support function is called hypervisor privilege (HV privilege). When the restricted operating mode is Host mode and the privilege operating mode is Supervisor mode, CPU authority is HV privilege. It is a privilege necessary for building and managing virtual machines and managing CPU resources outside the virtual machine. In HV privilege, virtualization software is assumed to be executed.

#### (2) Supervisor Privilege (SV Privilege)

The privilege necessary to perform the operation for important system resources, fatal error processing, and user-mode program execution management is called the supervisor privilege (SV privilege). This privilege is available in supervisor mode. The SV privilege is generally necessary to execute instructions used to perform the operation for important system resources, and these instructions are sometimes called SV privileged instructions.

In SV privilege, operations of operating system, exception handler, interrupt handler and so on, are assumed to be executed.

#### (3) User authority (UM authority)

UM authority is a privilege that can not perform the operation of the virtualization support function and other important system resources.

It can not execute HV privileged instructions or SV privileged instructions to perform those operations.

In User authority, operation of application software is assumed to be executed.

#### (4) Coprocessor Use Permissions

Regardless of the CPU operating mode, it is possible to specify whether coprocessors can be used.

The CU2 to CU0 bits in the PSW register are used by a supervisor to specify whether coprocessors can be used by each program. If the CU 2 to CU0 bits are not set to 1, a coprocessor unusable exception occurs when the corresponding coprocessor instruction is executed or the system register is accessed.

If no coprocessor is installed, it is not possible to set the corresponding CU bits to 1. The setting of the CU2 to CU0 bits is valid regardless of the CPU operating mode, and, even if the CPU authority is HV privilege or SV privilege, if the supervisor accesses coprocessor system registers, they must be allowed to be used by the setting of CU2-0 bit.

There are restrictions for changing the CU2-0 bit. For details, see **Section 2.4.1, Coprocessor Use Permissions**

#### (5) Operation when there is a Privilege Violation

When a privileged instruction is executed by someone who does not have the required privilege, or when a system register for which access permission is specified is accessed by someone who does not have the required permission, a RIE exception, PIE exception or UCPOP exception occurs.

The **Table 2.2** shows whether instructions can be executed depends on operating mode and use permission. The **Table 2.3** shows whether system registers can be accessed depends on operating mode and use permission.

| Instruction             |                  | HVCFG | PSWH | PSW |     |     |     |                                      |

|-------------------------|------------------|-------|------|-----|-----|-----|-----|--------------------------------------|

| Execution<br>Permission | Classification   | HVE   | GM   | им  | CU2 | CU1 | CUO | Whether Instructions can be Executed |

| HV privilege*1          | *2               | 0     | _    | —   | —   | —   | —   | Impossible (RIE exception occurs)    |

|                         |                  | 1     | 0    | 0   | _   | —   | _   | Possible                             |

|                         |                  | 1     | 0    | 1   | _   | —   | _   | Impossible (PIE exception occurs)    |

|                         |                  | 1     | 1    | 0   | _   | —   | _   | Impossible (PIE exception occurs)    |

|                         |                  | 1     | 1    | 1   | _   | —   | _   | Impossible (PIE exception occurs)    |

| SV privilege            | *2               | —     | 0    | 0   | _   | —   | _   | Possible                             |

|                         |                  | —     | 0    | 1   | —   | —   | —   | Impossible (PIE exception occurs)    |

|                         |                  | —     | 1    | 0   | —   | —   | —   | Possible                             |

|                         |                  | —     | 1    | 1   | —   | —   | —   | Impossible (PIE exception occurs)    |

| User                    | Coprocessor 0    | —     | _    |     | —   | —   | 0   | Impossible (UCPOP exception occurs)  |

|                         | instruction      | —     | _    |     | —   | —   | 1   | Possible                             |

|                         | Coprocessor 1    | —     | _    |     | —   | 0   | —   | Impossible (UCPOP exception occurs)  |

|                         | instruction      | —     | _    |     | —   | 1   | —   | Possible                             |

|                         | Coprocessor 2    | —     | —    | —   | 0   | —   | —   | Impossible (UCPOP exception occurs)  |

|                         | instruction      | —     | —    | —   | 1   | —   | —   | Possible                             |

|                         | Other than above | —     | —    | —   | —   | —   | —   | Possible                             |

Table 2.2

Operation when Execution Permission is Violated

Note: -: 0 or 1

Note 1. Some operations of the CACHE instruction are HV privilege instructions when the virtualization operating mode is virtualization mode, but are SV privilege instructions when the virtualization operating mode is conventional mode. When these CACHE instructions are executed in the conventional mode, the RIE exception does not occur, and the execution authority is judged as the SV privileged instruction. For details, see Section 5.2.7, Execution Privilege of the CACHE/PREF Instruction.

Note 2. Coprocessor instructions with HV privilege or SV privilege are not defined in this CPU.

Та

| System Register      |                             | HVCFG | PSWH | PSW |                |   |          | Whether Instructions can be Executed  |

|----------------------|-----------------------------|-------|------|-----|----------------|---|----------|---------------------------------------|

| Access<br>Permission | Classification              | HVE   | GM   | υм  | UM CU2 CU1 CU0 |   | CU0      |                                       |

| HV privilege*1       | *2                          | 0     | —    | 0   | —              | — | <u> </u> | Accessible* <sup>3</sup>              |

|                      |                             | 0     | —    | 1   | —              | — | —        | Inaccessible (PIE exception occurs)*3 |

|                      |                             | 1     | 0    | 0   | —              | — | —        | Accessible                            |

|                      |                             | 1     | 0    | 1   | —              | — | —        | Inaccessible (PIE exception occurs)   |

|                      |                             | 1     | 1    | 0   | —              | — | —        | Inaccessible (PIE exception occurs)   |

|                      |                             | 1     | 1    | 1   | —              | — | —        | Inaccessible (PIE exception occurs)   |

| SV privilege         | Coprocessor 0               | —     | _    | 0   | —              | — | 0        | Inaccessible (UCPOP exception occurs) |

|                      | Permission                  |       | —    | 0   | —              | — | 1        | Accessible                            |

|                      |                             |       | —    | 1   | —              | — | 0        | Inaccessible (UCPOP exception occurs) |

|                      |                             |       | —    | 1   | —              | — | 1        | Inaccessible (PIE exception occurs)   |

|                      | Coprocessor 1<br>Permission | —     | —    | 0   | —              | 0 | —        | Inaccessible (UCPOP exception occurs) |

|                      |                             | _     | _    | 0   | —              | 1 | —        | Accessible                            |

|                      |                             | _     | _    | 1   | —              | 0 | —        | Inaccessible (UCPOP exception occurs) |

|                      |                             | _     | _    | 1   | —              | 1 | —        | Inaccessible (PIE exception occurs)   |

|                      | Coprocessor 2               | —     | _    | 0   | 0              | — | —        | Inaccessible (UCPOP exception occurs) |

|                      | Permission                  |       | —    | 0   | 1              | — | -        | Accessible                            |

|                      |                             | _     | —    | 1   | 0              | — | —        | Inaccessible (UCPOP exception occurs) |

|                      |                             |       | —    | 1   | 1              | — | -        | Inaccessible (PIE exception occurs)   |

|                      | Other than above            | —     | —    | 0   | —              | — | —        | Accessible                            |

|                      |                             | _     | _    | 1   | —              | — | —        | Inaccessible (PIE exception occurs)   |

| UM authority         | Coprocessor 0               | _     | —    | —   | —              | — | 0        | Inaccessible (UCPOP exception occurs) |

|                      | Permission                  | _     | _    | —   | —              | — | 1        | Accessible                            |

|                      | Coprocessor 1               | _     | _    | _   | —              | 0 | —        | Inaccessible (UCPOP exception occurs) |

|                      | Permission                  | —     | —    | —   | —              | 1 | _        | Accessible                            |

|                      | Coprocessor 2               | —     | —    | —   | 0              |   | —        | Inaccessible (UCPOP exception occurs) |

|                      | Permission                  | —     | —    | —   | 1              | — | _        | Accessible                            |

|                      | Other than above            | —     | —    | —   | —              | — | —        | Accessible                            |

| able 2.3 | Operation | When | Access | Permission <sup>•</sup> | to S | System | Registers | is \ | Violated |  |

|----------|-----------|------|--------|-------------------------|------|--------|-----------|------|----------|--|

|          |           |      |        |                         |      |        |           |      |          |  |

Note: -: 0 or 1

Note 1. In some system registers, the access authority is HV privilege when the virtualization operating mode is virtualization mode, but when the virtualization operating mode is conventional mode, the access authority is SV privilege. When these system registers are operated in the conventional mode, their execution authority is determined as system registers with access authority of the SV privilege. For details, see **Section 3, Register Set**.

Note 2. In this CPU, coprocessor system registers whose access authority is HV privilege are not defined.

Note 3. Operations on some system registers are handled as operations on undefined registers that require the SV privilege for accessing. For details, see **Section 3, Register Set**.

# 2.1.4 Halt State by a HALT Instruction

See the "CPU" section in the hardware manual of the product used.

# 2.1.5 Temporary Halt State by a SNOOZE instruction

See the "CPU" section in the hardware manual of the product used.

# 2.2 Instruction Execution

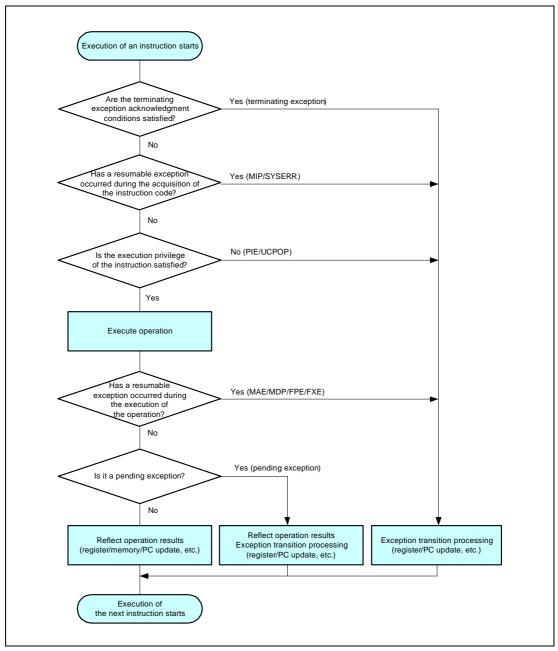

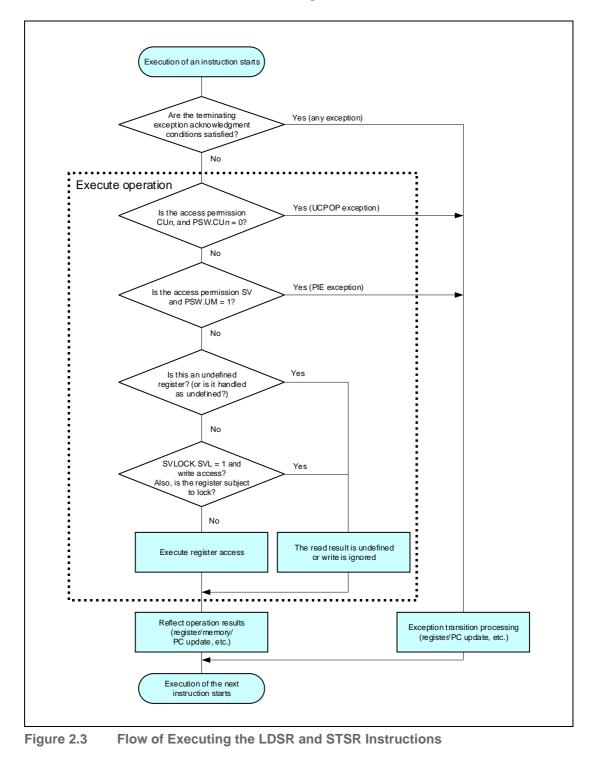

The instruction execution flow of this CPU is shown below.

Figure 2.2 Instruction Execution Flow

When terminating exceptions can be acknowledged, if an exception is detected during the acquisition of instruction code, or if the execution privilege of the instruction is not satisfied, an exception occurs before the instruction is executed. If a resumable exception occurs while the CPU is executing the operation, it interrupts the execution of the operation and acknowledges the exception. In these cases, the result of instruction operation is, in principle, not reflected in registers or memory and the CPU retains its state that is established before executing the instruction.\*<sup>1</sup>

For a pending exception such as a software exception, the exception is acknowledged after the result of instruction execution has been reflected.

For details of the types of exceptions, refer to Section 2.3, Exceptions and Interrupts.

- **Note 1.** If an exception is acknowledged during the execution of the following instructions, intermediate results may be applied to memory or general-purpose registers. However, SP/EP is not updated.

- PREPARE, DISPOSE, PUSHSP, POPSP, STM.MP, LDM.MP, STM.GSR, LDM.GSR

# 2.3 Exceptions and Interrupts

Exceptions and interrupts are exceptional events that cause the branch from the executing program to another program. Exceptions and interrupts are triggered by various causes, including interrupts from peripherals and program errors.

For details, see Section 4, Exceptions and Interrupts.

# 2.3.1 Types of Exceptions

The exceptions of this CPU are divided into the following three types according to the purpose of the exceptions.

- Terminating exception

- Resumable exception

- Pending exception

Also, exceptions classified into these types are further classified into the following two according to the restricted operating mode in which the exception handler is processed.

- Exceptions handled in Host mode

- Exceptions handled in Guest mode

#### (1) Terminating Exception

See the "CPU" section in the hardware manual of the product used.

#### (2) Resumable Exception

See the "CPU" section in the hardware manual of the product used.

#### (3) Pending Exception

See the "CPU" section in the hardware manual of the product used.

#### (4) Exceptions handled in Host mode

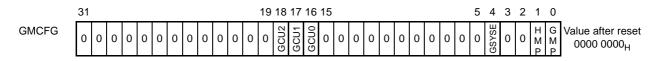

The exception handler is handled in Host mode. There are cases for which the exception cause belongs to the host mode and cases for which the processing is specified to be performed in Host mode but the exception causes belong to guest mode. Exceptions that belong to the host mode are the resumable exceptions which are caused by instructions executed in host mode, the pending exceptions, and the terminating exceptions which occur regardless of restricted operating mode. Exceptions that are handled in Host mode although the exception cause belongs to Guest mode are those that occur when an HVTRAP instruction is executed in guest mode or if MIP, MDP, or SYSERR exception occurs when transition to the host mode is specified by the corresponding bit in GMCFG.

#### (5) Exceptions handled in Guest mode

The exception handler is handled in Guest mode. This exception applies to the case for which the exception cause belongs to Guest mode or to the case in which MIP, MDP, or SYSERR exception occurs when processing in guest mode is specified by the corresponding bit in GMCFG.

# 2.3.2 Exception Level

See the "CPU" section in the hardware manual of the product used.

# 2.4 Coprocessors

In this CPU, single-precision and double-precision floating-point unit (FPU) and extended floating point operation unit (FXU) are incorporated. Note that these coprocessors may not be available depending on the specification of the product.

# 2.4.1 Coprocessor Use Permissions

To execute a coprocessor instruction, permission to use the corresponding coprocessor instruction is necessary. Coprocessor use permissions are specified by the PSW.CU2 to PSW.CU0 bits, and, if an attempt is made to execute an instruction for which the corresponding coprocessor use permission is cleared to 0, a coprocessor unusable exception (UCPOP) occurs.

In the following cases, the values of the PSW.CU2 to CU0 bits are fixed at 0 and cannot be changed.

- Coprocessor functions are not incorporated in the product

- Coprocessor functions are made unavailable according to the functions of the product

- In guest mode, GMCFG.GCU2-0 is cleared (0), making it impossible to change GMPSW.CU2-0.

# 2.4.2 Correspondences between Coprocessor Use Permissions and Coprocessors

See the "CPU" section in the hardware manual of the product used.

### 2.4.3 Coprocessor Unusable Exceptions

See the "CPU" section in the hardware manual of the product used.

#### 2.4.4 System Registers

See the "CPU" section in the hardware manual of the product used.

# 2.5 Registers

In this CPU, the program registers (general-purpose registers and the program counter PC) and system registers for controlling the status and storing exception information are defined.

# 2.5.1 **Program Registers**

The program registers include general-purpose registers (r0 to r31) and the program counter (PC).

In this CPU, the program registers are shared between Host mode and Guest mode, or between Guest partition. Therefore, when changing the restricted operating mode or changing Guest partition, proper replacement of program registers by software is required. For details, see **Section 4.1.7, Context switching**.

Table 2.4 Program Registers

| Category                  | Access Permission | Name      |  |

|---------------------------|-------------------|-----------|--|

| Program counter           | UM                | PC        |  |

| General-purpose registers | UM                | r0 to r31 |  |

Note: Access to the registers with UM (user mode) access permission is always allowed.

For details about program registers, see **Section 3.1, Program Registers**.

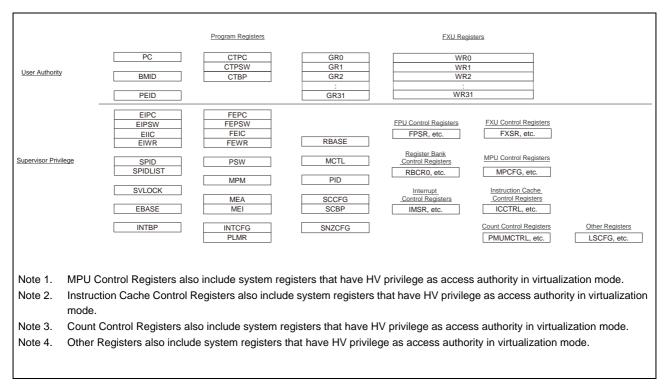

# 2.5.2 System Registers

System registers are placed in dedicated address spaces defined based on two types of address information: selection ID and register number. Up to 32 selection ID can be defined, and one selection ID includes up to 32 system registers. Therefore, up to 1024 system registers can be defined in the address spaces for system registers. Basically this CPU allocates selection ID as shown below:

| Selection ID 0 to 3, 10: | Registers related to basic functions                           |

|--------------------------|----------------------------------------------------------------|

| Selection ID 4 and 5:    | Registers related to the memory management function            |

| Selection ID 9:          | Guest context registers                                        |

| Selection ID 11, 14, 15  | Registers related to counter function                          |

| Selection ID 12, 13:     | Registers related to this CPU specific hardware functions      |

| Other ID:                | Reserved for future expansion of CPUs compatible with this CPU |

For details about system registers, see the relevant sections in Section 3, Register Set.

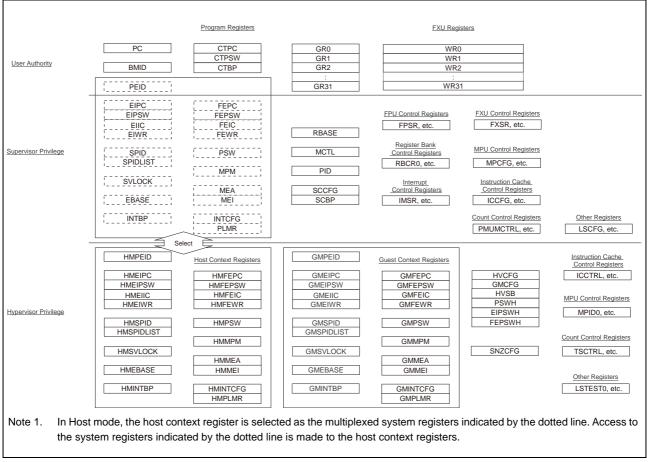

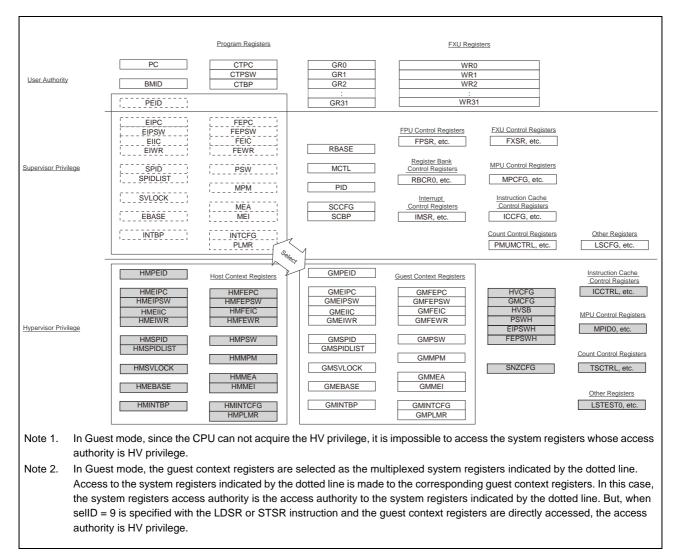

In this CPU, there are system registers that are shared between Host mode and Guest mode, and system registers that are multiplexed. For details, see **Section 4.1.7, Context switching**. For multiplexed system registers, corresponding registers are automatically switched when the restricted operating mode is changed. On the other hand, when changing Guest partition, it is necessary to properly replace the registers by the software. For details, see **Section 2.5.7, System Register Multiplexing**.

# 2.5.3 Register Updating

See the "CPU" section in the hardware manual of the product used.

#### (1) LDSR and STSR

See the "CPU" section in the hardware manual of the product used.

RENESAS

#### (2) Changing the access authority of system register

**Table 2.5** shows a list of system registers whose access authority is changed according to the state of the virtualization operating mode.

The setting of these system registers affects CPU operation, but they are not multiplexed. Also, when the virtualization operating mode is virtualization mode, SV privilege can be acquired on the guest partition side. Therefore, if these system registers are modified by the management software running on Guest partition, the virtualization software operating in host mode and the operation of other Guest partitions are affected. To prevent this, the access authority of these system registers is raised to HV privilege when the virtualization operating mode is virtualization mode. For multiplexing of the system registers, see **Section 2.5.7, System Register Multiplexing**.

|                 |          | Access authority  |                  |                      |                      |             |

|-----------------|----------|-------------------|------------------|----------------------|----------------------|-------------|

| Register number |          | Conventional mode |                  | Virtualization mode  |                      | 1           |

| (regID, seIID)  | Name     | Writing           | Reading          | Writing              | Reading              | Description |

| SR21,0          | SNZCFG   | SV                | SV               | HV                   | HV                   |             |

| SR17,5          | МРВК     | SV                | SV               | ΗV                   | HV                   |             |

| SR24,5          | MPID0    | SV                | SV               | HV* <sup>1</sup>     | SV*1                 |             |

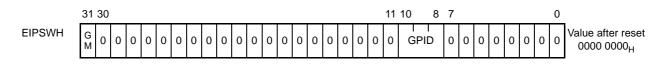

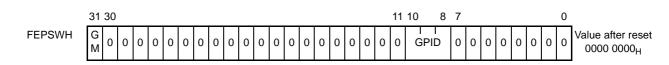

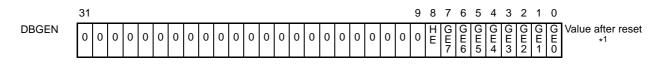

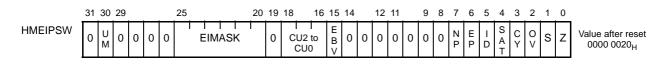

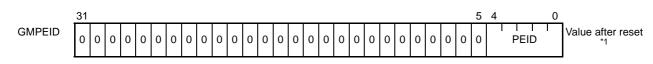

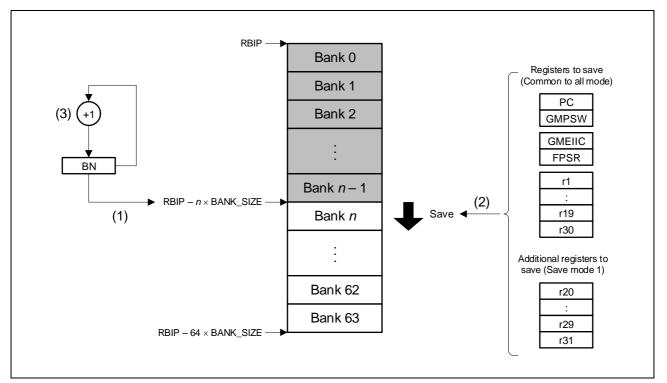

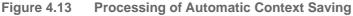

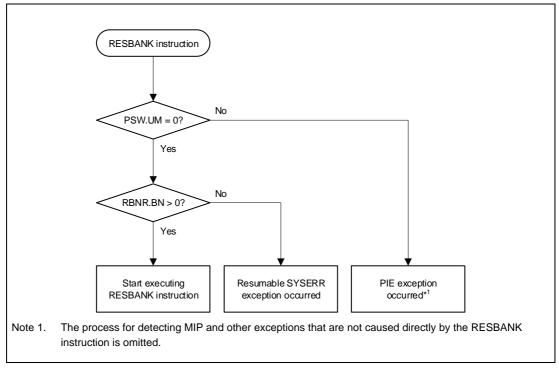

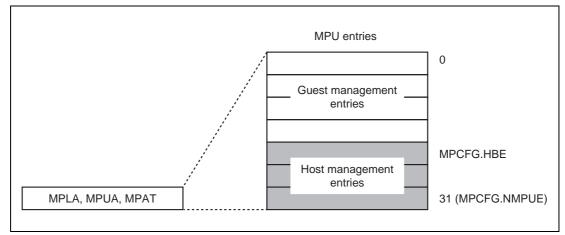

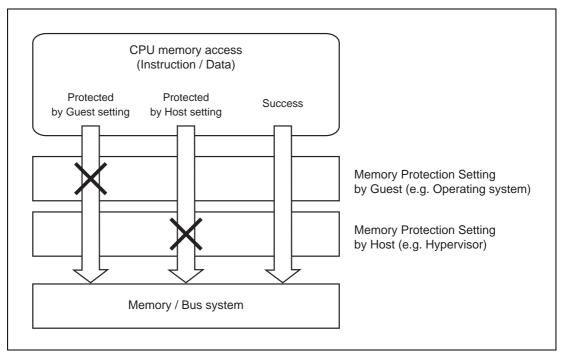

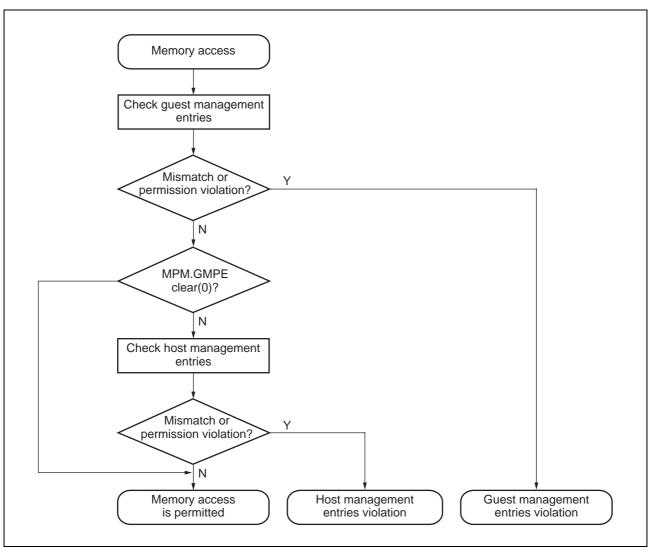

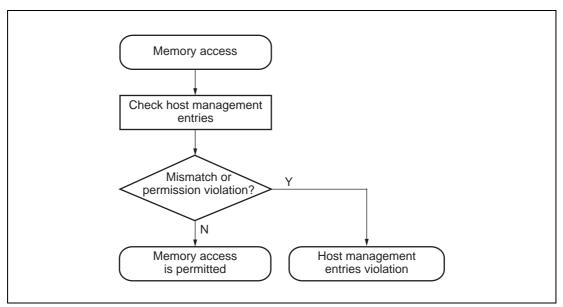

| SR25,5          | MPID1    | SV                | SV               | HV* <sup>1</sup>     | SV* <sup>1</sup>     |             |